(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6059439号

(P6059439)

(45) 発行日 平成29年1月11日(2017.1.11)

(24) 登録日 平成28年12月16日(2016.12.16)

(51) Int.Cl.

F 1

|              |           |      |       |         |

|--------------|-----------|------|-------|---------|

| HO1L 21/8242 | (2006.01) | HO1L | 27/10 | 6 7 1 A |

| HO1L 27/108  | (2006.01) | HO1L | 29/78 | 6 1 3 B |

| HO1L 29/786  | (2006.01) | HO1L | 29/78 | 6 1 8 B |

| HO1L 21/336  | (2006.01) | HO1L | 29/78 | 6 1 7 V |

| HO1L 27/105  | (2006.01) | HO1L | 29/78 | 6 2 6 A |

請求項の数 4 (全 31 頁) 最終頁に続く

(21) 出願番号 特願2012-49030 (P2012-49030)

(22) 出願日 平成24年3月6日 (2012.3.6)

(65) 公開番号 特開2012-256847 (P2012-256847A)

(43) 公開日 平成24年12月27日 (2012.12.27)

審査請求日 平成27年2月4日 (2015.2.4)

(31) 優先権主張番号 特願2011-52448 (P2011-52448)

(32) 優先日 平成23年3月10日 (2011.3.10)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2011-112648 (P2011-112648)

(32) 優先日 平成23年5月19日 (2011.5.19)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 松林 大介

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 加藤 俊哉

最終頁に続く

(54) 【発明の名称】メモリ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

トランジスタと、キャパシタとが積層されたメモリ装置であって、

前記トランジスタは、少なくとも、第1のビット線と、第2のビット線と、第1の半導

体層と、第2の半導体層と、ゲート絶縁層と、ワード線と、を有し、

前記第1の半導体層は、前記第1のビット線上に接して設けられ、

前記第2の半導体層は、前記第2のビット線上に接して設けられ、

前記ゲート絶縁層は、前記第1の半導体層の側面と、前記第1のビット線の側面と、前

記第2のビット線の側面と、前記第2の半導体層の側面とに接して設けられ、

前記ワード線は、前記第1の半導体層と前記第2の半導体層との間に位置し、且つ前記

ゲート絶縁層に接して設けられ、

前記キャパシタは、少なくとも、第1の容量電極と、第2の容量電極と、容量配線と、

前記第1及び前記第2の容量電極と前記容量配線との間の絶縁層と、を有し、

前記第1の容量電極は、前記第1の半導体層の上面に接して設けられ、

前記第2の容量電極は、前記第2の半導体層の上面に接して設けられ、

前記第1及び前記第2の半導体層の上面と前記ゲート絶縁層の上面と前記ワード線の上

面とは、同じ平面内に設けられ、

前記第1及び前記第2の半導体層は、シリコンよりもバンドギャップの広い半導体材料

を有するメモリ装置。

## 【請求項 2】

10

20

前記第1及び前記第2の半導体層は、バンドギャップが2.5電子ボルト以上4電子ボルト以下の材料を有する請求項1に記載のメモリ装置。

【請求項3】

前記第1及び前記第2の半導体層は、酸化物半導体を有する請求項1又は請求項2に記載のメモリ装置。

【請求項4】

前記第1及び前記第2のビット線の下に、前記トランジスタを駆動する駆動回路を有する請求項1乃至請求項3のいずれか一に記載のメモリ装置。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、半導体特性を利用したメモリ装置とその作製方法に関する。

【背景技術】

【0002】

1つのキャパシタと1つのトランジスタ(セルトランジスタともいう)から構成される、DRAM(Dynamic Random Access Memory)は、代表的なメモリ装置として広く用いられる。

【0003】

従来、DRAMはプレーナ型トランジスタを用いて形成されてきたが、回路の微細化に伴い、短チャネル効果によるリーク電流を防止するためにゲートを立体的に配置するRCAT(Recessed Channel Array Transistor)を用いる方法が採用されている(非特許文献1参照)。

20

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】Kim, "Technology for sub-50nm DRAM and NAND Flash Manufacturing" TECHNICAL DIGEST OF INTERNATIONAL ELECTRON DEVICES MEETING, pp333-336, 2005

30

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、従来のDRAMでは、情報を読み出すとキャパシタの電荷は失われるため、情報の読み込みの度に、再度書き込み動作を行う必要がある。また、記憶素子を構成するトランジスタにはリーク電流が存在し、トランジスタが選択されていない状況でもキャパシタの電荷が流出、またはキャパシタへ電荷が流入するため、データの保持期間が短い。このため、所定の周期で再度の書き込み動作(リフレッシュ動作)が必要であるといった問題があった。

【0006】

一方でメモリ装置の高集積化に伴い、メモリ素子の占有面積の縮小が求められている。しかし、上述のプレーナ型トランジスタ及びその変形であるRCATでは、回路の配線幅を小さくする以外には、これ以上の集積化は困難であり、このような従来の技術を用いた場合のメモリ素子の面積は8F<sup>2</sup>以上(Fは最小加工寸法)、又は6F<sup>2</sup>以上である。したがってより小さい面積、例えば4F<sup>2</sup>を実現する技術が求められている。

40

【0007】

本発明は、このような技術的背景のもとでなされたものである。したがって本発明の一態様は、可能な限り占有面積が削減され、データ保持期間の極めて長いメモリ装置を提供することを課題とする。

【課題を解決するための手段】

【0008】

50

上記目的を達成するために、本発明は、メモリ装置内のメモリ素子のセルトランジスタとして、リーク電流の極めて小さいトランジスタを用いることに着眼した。さらにメモリセルの占有面積を縮小するために、ビット線とワード線とが交差する領域に、当該トランジスタのソース及びドレインが縦方向に積層されるように形成すればよい。さらにキャパシタは、当該トランジスタの上方に積層すればよい。

【0009】

すなわち、本発明の一態様は、基板上にセルトランジスタと、キャパシタとが積層されたメモリ装置であって、セルトランジスタは、ビット線上に半導体層と、半導体層の側面と接するゲート絶縁層と、を有し、半導体層の側面の少なくとも一部は、ゲート絶縁層を介してワード線に覆われている。また、キャパシタは、半導体層の上面に接する容量電極と、容量電極上に絶縁層と、絶縁層上に容量配線と、を有する。さらにセルトランジスタの半導体層は、シリコンよりもバンドギャップの広い半導体材料で構成されている。

10

【0010】

このように、セルトランジスタはビット線とワード線とが交差する領域に形成され、さらにキャパシタが当該セルトランジスタと重畳するように形成されているため、基板面積に対するメモリ素子の占有面積を極めて低減することができる。さらにセルトランジスタのチャネルが形成される半導体層に、シリコンよりもバンドギャップの広い材料からなる半導体を適用することにより、セルトランジスタのオフ電流が低減され、データの保持期間を極めて長くすることができる。

【0011】

20

また、本発明の他の一態様は、上記メモリ装置における半導体層が、バンドギャップが2.5電子ボルト以上4電子ボルト以下の材料から構成される。

【0012】

また、本発明の他の一態様は、上記メモリ装置における半導体層が、酸化物半導体から構成される。

【0013】

特に、セルトランジスタのチャネルが形成される半導体層に、上記のようなバンドギャップの値を有する半導体を適用することにより、セルトランジスタのオフ電流を極めて低い値とすることが可能となる。

【0014】

30

また、本発明の他の一態様は、上記ビット線の下に、上記セルトランジスタを駆動する駆動回路を有することを特徴とする、メモリ装置である。

【0015】

このように、ビット線の下に駆動回路を設けることにより、メモリ素子の占有面積を削減することができる。駆動回路は、好ましくは単結晶半導体を用いて形成するとよい。

【0016】

また、本発明の一態様のメモリ装置の作製方法は、絶縁表面上にビット線を形成する工程と、ビット線上に、シリコンよりもバンドギャップの広い半導体材料からなる半導体層を形成する工程と、ビット線及び半導体層を覆うゲート絶縁層を形成する工程と、ゲート絶縁層を介して半導体層の側面の少なくとも一部を覆うワード線を形成する工程と、半導体層の上面を露出させるようにゲート絶縁層の一部を除去する工程と、半導体層の上面に接する容量電極を形成する工程と、容量電極上に、絶縁層と容量配線とを積層して形成する工程と、を有する。

40

【0017】

上記のような作製方法によれば、占有面積が極めて小さく、且つデータの保持期間の極めて長いメモリ素子を作製することができる。

【0018】

なお、本明細書等において、ビット線とはセンスアンプ等に接続した配線、あるいは、センスアンプ等により電位が増幅される配線という意味に解釈してもよい。また、ワード線とはセルトランジスタのゲートに接続する配線という意味に解釈してもよい。

50

## 【発明の効果】

## 【0019】

本発明によれば、可能な限り占有面積が削減され、データ保持期間の極めて長い半導体メモリ装置を提供できる。

## 【図面の簡単な説明】

## 【0020】

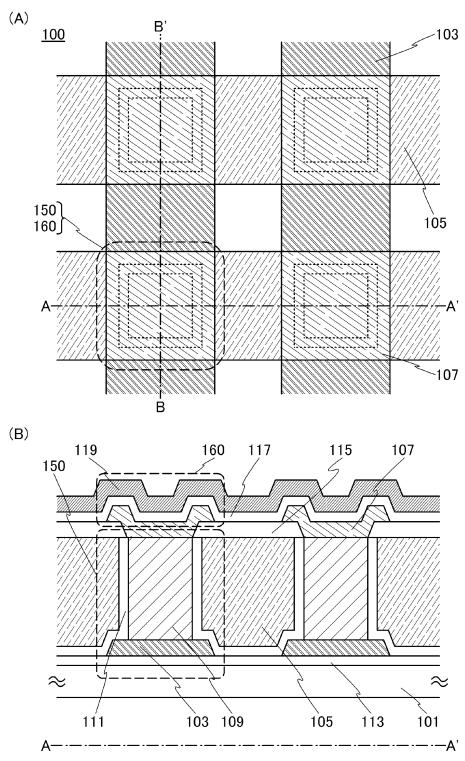

【図1】本発明の一態様の、メモリ装置を説明する図。

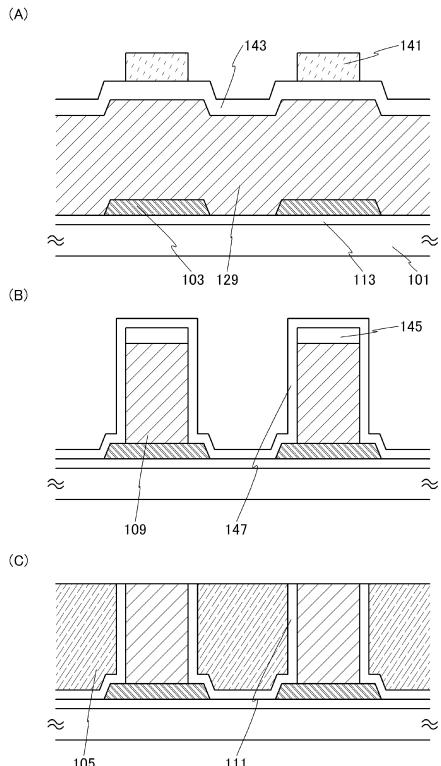

【図2】本発明の一態様の、メモリ装置の作製方法を説明する図。

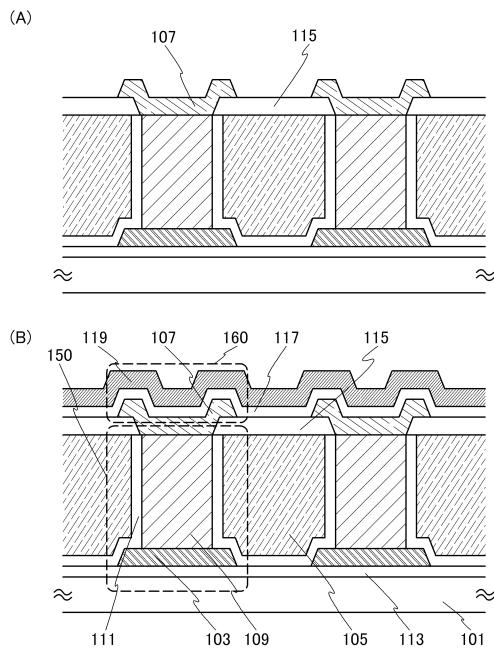

【図3】本発明の一態様の、メモリ装置の作製方法を説明する図。

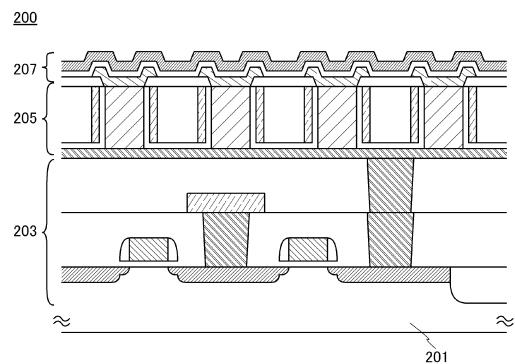

【図4】本発明の一態様の、メモリ装置を説明する図。

10

【図5】本発明の一態様の、メモリ装置を説明する図。

【図6】本発明の一態様の、メモリ装置を説明する図。

【図7】酸化物半導体の一例。

【図8】酸化物半導体の一例。

【図9】酸化物半導体の一例。

【図10】ゲート電圧と電界効果移動度の関係。

【図11】ゲート電圧とドレイン電流の関係。

【図12】ゲート電圧とドレイン電流の関係。

【図13】ゲート電圧とドレイン電流の関係。

【図14】トランジスタの特性。

20

【図15】トランジスタの特性。

【図16】トランジスタの特性。

【図17】トランジスタのオフ電流の温度依存性。

## 【発明を実施するための形態】

## 【0021】

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

30

## 【0022】

なお、本明細書で説明する各図において、各構成の大きさ、層の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

## 【0023】

また、本明細書においては、セルトランジスタのソースとはビット線側の電極あるいは領域を指し、セルトランジスタのドレインとはキャパシタ側の電極あるいは領域を指すものとする。

## 【0024】

40

## (実施の形態1)

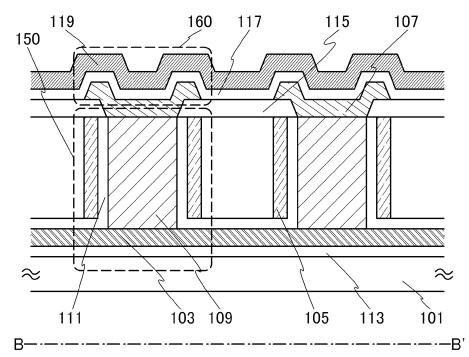

本実施の形態では、本発明の一態様である半導体メモリ装置の構成例について、図1及び図6を用いて説明する。

## 【0025】

図1(A)は、メモリ装置100の上面概略図であり、図1(B)は、図1(A)中の切断線A-A'に沿った断面概略図である。なお、明瞭化のため、図1(A)には容量線119は明示していない。

## 【0026】

メモリ装置100は、並行する複数のビット線103と、ビット線103と直交する複数のワード線105と、を有し、ビット線103とワード線105の重なる領域に、セル

50

トランジスタ 150 及びキャパシタ 160 が積層して形成されている。

【0027】

セルトランジスタ 150 は、基板 101 の表面を覆う下地絶縁層 113 上に形成される。セルトランジスタ 150 は、ビット線 103 上に半導体層 109 と容量電極 107 が積層されている。また半導体層 109 の側面は、ゲート絶縁層 111 を介してワード線 105 に覆われている。したがって、セルトランジスタ 150 は、半導体層 109 の側面を覆うワード線 105 がゲートとして機能し、その底面に接するビット線 103 がソース、また上面に接する容量電極 107 がドレインとして機能する、縦型のトランジスタである。

【0028】

図 6 には、図 1 (A) 中のビット線 103 に沿った切断線 B - B' に沿った断面概略図を示している。図 6 に示すように、ワード線 105 は、ゲート絶縁層 111 を介して半導体層 109 の側面を覆うように断線することなく形成されているため、一つのワード線 105 に接続され、一列に配置される複数のセルトランジスタ 150 のそれぞれに同じ電位を与えることが出来る。また、隣接するワード線 105 間は絶縁層により絶縁されている。

【0029】

キャパシタ 160 は、セルトランジスタ 150 の上方に積層して形成され、容量電極 107 と、容量線 119 と、これらに挟持された絶縁層 117 から構成される。

【0030】

データを書込む際には、セルトランジスタ 150 をオン状態とし、ビット線 103 と容量線 119 との電位差に応じた電流が半導体層 109 に形成されたチャネルを介して容量電極 107 に流れることにより、キャパシタ 160 に電荷が保持される。その後セルトランジスタ 150 をオフ状態とすることにより、書込まれたデータを保持することができる。

【0031】

また、データを読み出す際は、セルトランジスタ 150 をオン状態とすることにより、キャパシタ 160 に保持された電荷に応じた電流が半導体層 109 に形成されたチャネルを介してビット線 103 に流れれる。したがってこの際のビット線 103 の電位の変化を、当該ビット線 103 に接続されたセンスアンプなどの読み出し回路で検知することにより、読み出しを行うことができる。

【0032】

ここで、セルトランジスタ 150 、及びキャパシタ 160 のワード線 105 方向の幅は、ビット線 103 の幅と概略一致させることができる。さらにこれらのビット線 103 方向の幅は、ワード線 105 の幅と概略一致させることができる。したがって、セルトランジスタ 150 及びキャパシタ 160 の基板 101 表面における占有面積は、極めて小さいものとすることが可能となる。

【0033】

また、セルトランジスタ 150 のチャネル長は、半導体層 109 の厚さを変えることにより制御することができる。したがって、微細化に伴いビット線 103 やワード線 105 などの線幅が極めて小さくなつた場合でも、任意のチャネル長とすることができるため、短チャネル効果を抑制することができる。

【0034】

セルトランジスタ 150 のチャネル長は、ゲート絶縁層 111 の厚さにもよるが、例えば半導体層 109 の対角の長さまたは直径に対して 10 倍以上、好ましくは 20 倍以上とすると、短チャネル効果を抑制できるため好ましい。

【0035】

また、図 1 及び図 6 において、半導体層 109 を角柱形状として明示したが、円柱形状としてもよい。例えば半導体層 109 が角柱形状であれば、その側面近傍に形成されるチャネルの実効的な幅を大きくとれるため、セルトランジスタ 150 のオン電流を高くすることができる。また、円柱形状とするとその側面に突出した部分がなく、その側面にゲー

10

20

30

40

50

ト電界が均一に印加されるため、信頼性の高いセルトランジスタ 150 とすることができます。例えばさらにオン電流を高くしたい場合には、半導体層 109 の底面の形状を例えば星型多角形のように、少なくともひとつの内角が 180° を超える多角形（凹多角形）としてもよい。

【0036】

また、図 1 及び図 6 において、ワード線 105 はゲート絶縁層 111 を介して半導体層 109 の側面を覆う構成としたが、少なくとも半導体層 109 の側面の一部を覆って形成されればよい。例えば半導体層 109 のワード線 105 に沿った片側の側面にのみ、ワード線 105 を設ける構成とすれば、ピット線 103 方向の集積度を高くすることができる。一方で図 1 及び図 6 のように半導体層 109 の側面を覆う構成とすれば、セルトランジスタ 150 の実効的なチャネル幅を大きくとれるためオン電流を高くすることが出来る。

10

【0037】

ここで、セルトランジスタ 150 にはオフ電流が極めて小さいトランジスタを用いることによって、キャパシタ 160 に長期間に渡って保持することが可能となる。したがってメモリ装置 100 において、定期的なデータの再書き込み動作（以下、リフレッシュ動作とも呼ぶ。）が不要、若しくはリフレッシュ動作を行う頻度を極めて低くすることが可能となり、実質的に不揮発性のメモリ装置 100 として機能させることが可能となる。

【0038】

オフ電流が極めて小さいトランジスタとしては、チャネルが形成される半導体層にシリコンよりも広いバンドギャップを有する半導体を適用したトランジスタが挙げられる。シリコンよりも広いバンドギャップを有する半導体として化合物半導体があり、例えば、酸化物半導体、窒化物半導体などがある。

20

【0039】

具体的には、非常に高いオフ抵抗を得るためにには、シリコン（バンドギャップ 1.1 電子ボルト）では不十分で、バンドギャップが 2.5 電子ボルト以上 4 電子ボルト以下、好みしくは 3 電子ボルト以上 3.8 電子ボルト以下のワイドバンドギャップ半導体を使用することが必要となる。例えば、酸化インジウム、酸化亜鉛等の酸化物半導体、窒化ガリウム等の窒化物半導体、硫化亜鉛等の硫化物半導体等を用いればよい。

【0040】

30

例えば、セルトランジスタ 150 として、チャネルが形成される半導体層 109 に酸化物半導体を適用したトランジスタを用いることができる。

【0041】

また、セルトランジスタ 150 はオフ電流が極めて小さいトランジスタであるため、電荷を保持するキャパシタ 160 のサイズを縮小することができる。また、キャパシタ 160 のサイズの縮小に伴い、書き込み、読み出しに要する時間を短縮でき、高速動作が可能なメモリ装置 100 とすることができます。

【0042】

以上のように本実施の形態で例示したメモリ装置 100 は、基板 101 の表面に対して極めて占有面積が小さいセルトランジスタ 150 及びキャパシタ 160 からなるメモリ素子を有するメモリ装置である。また、当該セルトランジスタ 150 をオフ電流の極めて小さいトランジスタとすることにより、データ保持期間の極めて長いメモリ装置 100 とすることが可能となる。

40

【0043】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0044】

（実施の形態 2）

本実施の形態では、実施の形態 1 で例示したメモリ装置 100 の作製方法について、図 2 及び図 3 を用いて説明する。

50

## 【0045】

なお、本実施の形態では、一部を除いて、概略を示すにとどめる。詳細は、公知の半導体集積回路作製技術を参照すればよい。

## 【0046】

まず、基板101上に下地絶縁層113を形成する。

## 【0047】

基板101として使用することができる素材に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、基板101には、フュージョン法やフロート法で作製されるガラス基板、石英基板、半導体基板、セラミック基板等を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730以上の中を用いると良い。

10

## 【0048】

下地絶縁層113は、基板101からの不純物の拡散を抑制する機能を有する。例えば酸化物絶縁膜、窒化物絶縁膜などを、CVD法やスパッタリング法などの各種成膜方法で形成すればよい。また基板101に半導体基板を用いる場合には、その表面を熱酸化して形成してもよい。また、下地絶縁層113は必要なければ形成しなくても良い。

## 【0049】

続いて、下地絶縁層113上にピット線103を形成する。ピット線103はスパッタリング法やCVD法などの成膜方法により導電膜を形成した後、公知のフォトリソグラフィ法を用いて加工することにより形成される。

20

## 【0050】

導電膜に用いられる材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクスチレン等から選ばれた元素、又は上述した元素を成分とする合金、又は上述した元素を組み合わせた合金などが挙げられる。また、当該導電膜は単層でも2層以上の積層としてもよい。特に、アルミニウムや銅などの金属膜の下側、又は上側、若しくはその両方にクロム、タンタル、チタン、モリブデン、タンクスチレン等の高融点金属膜を積層してもよい。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、又はこれらを複数組み合わせた材料を用いてもよい。

## 【0051】

その後、下地絶縁層113及びピット線103を覆うように、半導体膜129を形成する。ここで半導体膜129のピット線103上の厚さは、後の平坦化工程で膜厚が減少してしまうことを考慮して、あらかじめセルトランジスタのチャネル長よりも厚くなるように形成することが好ましい。本実施の形態では、半導体膜129として酸化物半導体膜をスパッタリング法により形成する。具体的には、In-Ga-Zn系酸化物半導体ターゲットを用いてスパッタリング法により形成する。

30

## 【0052】

なお、酸化物半導体膜として用いることのできる材料は上記に限定されない。酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。

## 【0053】

40

また、酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)、スズ(Sn)、ハフニウム(Hf)、アルミニウム(Al)、又はランタノイドから選ばれた一種又は複数種を有することが好ましい。

## 【0054】

ランタノイドとして、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)がある。

## 【0055】

50

例えば、一元系金属の酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛等を用いることができる。

【0056】

また、例えば、二元系金属の酸化物半導体として、In-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物等を用いることができる。

【0057】

また、例えば、三元系金属の酸化物半導体として、In-Ga-Zn系酸化物（IGZOとも表記する）、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、In-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物等を用いることができる。

【0058】

また、例えば、四元系金属の酸化物半導体として、In-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物等を用いることができる。

【0059】

なお、ここで、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素を含有させても良い。

【0060】

また、上記金属酸化物にSiO<sub>2</sub>を含ませた酸化物半導体で酸化物半導体膜を形成することもできる。

【0061】

また、酸化物半導体膜を、InMO<sub>3</sub>(ZnO)<sub>m</sub>(m>0)で表記される酸化物半導体で形成することができる。ここで、Mは、Ga、Al、Mn、及びCoから選ばれた一つ又は複数の金属元素を示す。

【0062】

例えば、In:Ga:Zn=1:1:1あるいはIn:Ga:Zn=2:2:1の原子比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。

【0063】

あるいは、In:Sn:Zn=1:1:1、In:Sn:Zn=2:1:3あるいはIn:Sn:Zn=2:1:5の原子比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いても良い。

【0064】

しかし、これらに限られず、必要とする半導体特性（移動度、しきい値、ばらつき等）に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0065】

例えば、In-Sn-Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In-Ga-Zn系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

【0066】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物の組成が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)

10

20

30

40

50

$C = 1$  の酸化物の組成の近傍であるとは、 $a$ 、 $b$ 、 $c$  が、 $(a - A)^2 + (b - B)^2 + (c - C)^2 = r^2$  を満たすことをいい、 $r$  は、例えば、0.05 とすればよい。他の酸化物でも同様である。

【0067】

酸化物半導体は単結晶でも、非単結晶でもよい。

【0068】

非単結晶の場合、非晶質でも、多結晶でもよい。また、非晶質中に結晶性を有する部分を含む構造でもよい。なお、アモルファスは欠陥が多いため、非アモルファスが好ましい。

【0069】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0070】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することができる。具体的には、平均面粗さ ( $R_a$ ) が  $1 \text{ nm}$  以下、好ましくは  $0.3 \text{ nm}$  以下、より好ましくは  $0.1 \text{ nm}$  以下の表面上に形成するとよい。

【0071】

なお、 $R_a$  は、JIS B 0601 で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、式 (1) にて定義される。

【0072】

【数1】

$$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy \quad \dots \quad (1)$$

10

20

30

【0073】

なお、式 (1) において、 $S_0$  は、測定面 (座標  $(x_1, y_1)$ 、 $(x_1, y_2)$ 、 $(x_2, y_1)$ 、 $(x_2, y_2)$ ) で表される 4 点によって囲まれる長方形の領域) の面積を指し、 $Z_0$  は測定面の平均高さを指す。 $R_a$  は原子間力顕微鏡 (AFM: Atomic Force Microscope) にて評価可能である。

【0074】

ここで、酸化物半導体膜にはアルカリ金属、水素原子、水素分子、水、水酸基、又は水素化合物などの不純物ができるだけ混入しないように形成することができる。例えばスパッタリングターゲットや成膜に用いるガスに上記不純物が混入しないようにする。また、成膜の際、成膜装置内を十分排気し、成膜時に基板を加熱しながら成膜することにより、成膜された酸化物半導体膜に含まれる不純物濃度を低減することができる。また、酸化物半導体膜を成膜後に、加熱処理をして酸化物半導体膜中の水分、又は水素を脱離しても良い。当該加熱処理は、酸化物半導体膜の成膜後であれば、どの時点で行っても良い。

40

【0075】

次に、半導体膜 129 上に絶縁膜 143 を形成する。絶縁膜 143 は後に半導体膜 129 をエッティングして半導体層 109 とする際のハードマスクとして用いる膜であるため、半導体膜 129 とエッティングの選択比が大きい材料を用い、また当該エッティングに耐えうる厚さに形成する。

【0076】

その後、絶縁膜 143 上に接し、後の半導体層 109 となる領域と重なるように、レジ

50

スト 141 を形成する。この時点での断面概略図が図 2 (A) に相当する。

【0077】

続いて、レジスト 141 に覆われていない領域の絶縁膜 143 をエッチングしてハードマスク 145 を形成する。ハードマスク 145 を形成後、レジスト 141 を除去してもよい。その後、ハードマスク 145 に覆われていない領域の半導体膜 129 に対し、異方性のエッチングを行うことにより、半導体層 109 を得る。ここでエッチングの際に、ハードマスク 145、ビット線 103 及び下地絶縁層 113 がほとんどエッチングされない条件を選択する。

【0078】

なお、半導体膜 129 のエッチングの際、ハードマスク 145 がエッチングされないような条件で異方性エッチングを行い、形成後の半導体層 109 の形状が、概略柱状（円柱状、多角柱状を含む。）になるように形成することが好ましい。ここで例えば半導体層 109 の形状が錐状であった場合、形成されるセルトランジスタ 150 の実効的なチャネル幅がドレイン（容量電極）に近づくほど小さくなってしまうためオン電流が低下してしまう。

【0079】

ここでハードマスク 145 の形成後にレジスト 141 を除去していない場合は、半導体層 109 の形成後にレジスト 141 を除去する。

【0080】

続いて、下地絶縁層 113、ビット線 103、半導体層 109 及びハードマスク 145 の露出している部分を覆う絶縁膜 147 を形成する。絶縁膜 147 の一部は後のゲート絶縁層 111 となるため、半導体層 109 の側壁に接する部分は均一な膜厚になるように成膜する。絶縁膜 147 は、CVD 法、スパッタリング法などの成膜方法によって形成することができる。なお、ここで絶縁膜 147 の膜中及び半導体層 109 との界面には水、水素、水素化合物などの水素原子を含む不純物が十分低減されていることが好ましい。

【0081】

絶縁膜 147 としては、例えば酸化珪素、窒化酸化珪素、酸化窒化珪素、窒化珪素、酸化ハフニウム、酸化アルミニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0, y > 0$ ))、窒素が添加されたハフニウムシリケート ( $HfSi_xO_yN_z$  ( $x > 0, y > 0, z > 0$ ))、窒素が添加されたハフニウムアルミニート ( $HfAl_xO_yN_z$  ( $x > 0, y > 0, z > 0$ )) 等を含む膜を、単層で、又は積層させることで、形成することができる。

【0082】

この段階における断面概略図が図 2 (B) に相当する。

【0083】

次に、ワード線 105 を形成する。まず、半導体層 109 が形成されていない領域を埋めるように厚い導電膜を成膜する。当該導電膜はスパッタリング法や CVD 法などの成膜方法により成膜できる。導電膜に用いる材料としては、ビット線 103 を構成する導電膜と同様の材料を用いることができる。その後、当該導電膜の表面を平坦化する。ここで、平坦化工程は、絶縁膜 147、又はハードマスク 145 が露出した時点で停止する。

【0084】

続いて公知のフォトリソグラフィ法を用いて導電膜を選択的にエッチングすることにより、ビット線 103 と直交するワード線 105 のパターンを形成する。

【0085】

その後、ワード線 105 のパターン間（図示しない）を埋めるように厚い絶縁膜を形成した後、当該絶縁膜の表面を平坦化する。当該平坦化工程は、半導体層 109 が露出した時点で停止する。したがって、半導体層 109 の上部に形成された絶縁膜 147 の一部、及びハードマスク 145 は当該平坦化工程により除去される。

【0086】

以上の工程により、ワード線 105、及びゲート絶縁層 111 が形成される。この段階

10

20

30

40

50

における断面概略図が図2(C)に相当する。

【0087】

続いて、ワード線105の表面及びゲート絶縁層111の上部表面を覆う絶縁層115を形成する。絶縁層115はCVD法やスパッタリング法などの成膜方法により絶縁膜を成膜した後に半導体層109が露出するように選択的にエッチングして形成する。

【0088】

その後、半導体層109の上表面に接する容量電極107を形成する。容量電極107は、絶縁層115及び半導体層109を覆う導電膜をCVD法やスパッタリング法などの成膜方法により成膜した後、選択的にエッチングすることにより形成できる。この段階における断面概略図が、図3(A)に相当する。容量電極107を構成する導電膜に用いる材料としては、ビット線103を構成する導電膜と同様の材料を用いることができる。10

【0089】

続いて、絶縁層117及び容量線119を形成して、半導体層109上にキャパシタ160を形成する(図3(B)参照)。

【0090】

まず、絶縁層117をCVD法などの成膜方法により形成し、これと接する容量線119を形成する。ここで容量線119を構成する導電膜に用いる材料としては、ビット線103を構成する導電膜と同様の材料を用いることができる。ここで、絶縁層117の膜厚が薄いほど、また絶縁層117に用いる材料の誘電率が高いほど、キャパシタ160の容量を大きくできる。しかし本実施の形態で作製するセルトランジスタ150はオフ電流が極めて小さいため、キャパシタ160をその容量が比較的小さくなるように形成してもよい。20

【0091】

キャパシタ160の容量は、セルトランジスタ150のオフ電流が低いほど、言い換えるとセルトランジスタの150のオフ抵抗が高いほど小さくすることができる。例えば通常のシリコンを用いたDRAMよりもオフ抵抗が100倍高ければ、キャパシタ160の容量を100分の1としても同じリフレッシュ頻度で動作させることが可能である。一方、従来のDRAMと同じキャパシタ容量であれば、リフレッシュ頻度を100分の1まで低減できるため、デバイスとしての消費電力を極めて低減することができる。

【0092】

セルトランジスタ150のオフ抵抗は、チャネルが形成される半導体層109における熱的に励起するキャリアの濃度に反比例する。ドナーやアクセプタによるキャリアが全く存在しない状態(真性半導体)であっても、シリコンの場合にはバンドギャップが1.1電子ボルトであるため、室温(300K)での熱励起キャリアの濃度は $1 \times 10^{11} \text{ cm}^{-3}$ 程度である。

【0093】

一方、例えばバンドギャップが3.2電子ボルトの半導体の場合では熱励起キャリアの濃度は $1 \times 10^{-7} \text{ cm}^{-3}$ 程度となる。電子移動度が同じ場合、抵抗率は、キャリア濃度に反比例するので、バンドギャップ3.2電子ボルトの半導体の抵抗率は、シリコンより18桁も大きい。

【0094】

このようなバンドギャップの広い半導体が適用されたセルトランジスタ150は、極めて低いオフ電流とすることができるため、キャパシタ160に保持される電荷は、極めて長い期間保持させることができるとなる。したがって、キャパシタ160を小さくできると共に、リフレッシュ動作を無くす、若しくはその頻度を極めて低くすることができる。

【0095】

以上の工程により、基板表面に対する占有面積が極めて低減された複数のメモリ素子を有するメモリ装置100を形成することができる。またこのような工程を経て作製されたメモリ装置100は、データ保持期間を極めて長くすることができるため、データのリフレッシュ動作が不要、若しくはその頻度の極めて低いメモリ装置100とすることが4050

できる。

【0096】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0097】

(実施の形態3)

結晶性部分と非結晶性部分とを有し、結晶性部分の配向がc軸配向に揃っている酸化物半導体であるC AAC - OS (C Axis Aligned Crystalline Oxide Semiconductor)について説明する。

【0098】

C AAC - OS は新規な酸化物半導体である。

10

【0099】

C AAC - OS は、c軸配向し、かつa b面、表面または界面の方向から見て三角形状または六角形状の原子配列を有する。

【0100】

そして、C AAC - OS は、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列している。

【0101】

さらに、C AAC - OS は、a b面においてはa軸またはb軸の向きが異なる(c軸を中心回転している)。

20

【0102】

C AAC - OS とは、広義には、非単結晶である。

【0103】

そして、C AAC - OS は、a b面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有する。

【0104】

さらに、C AAC - OS は、c軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む酸化物である。

【0105】

C AAC - OS は単結晶ではないが、非晶質のみから形成されているものでもない。

30

【0106】

また、C AAC - OS は結晶化した部分(結晶部分)を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できることもある。

【0107】

C AAC - OS を構成する酸素の一部は窒素で置換されてもよい。

【0108】

また、C AAC - OS を構成する個々の結晶部分のc軸は一定の方向(例えば、C AAC - OS が形成される基板面、C AAC - OS の表面などに垂直な方向)に揃っていてよい。

【0109】

若しくは、C AAC - OS を構成する個々の結晶部分のa b面の法線は一定の方向(例えば、C AAC - OS が形成される基板面、C AAC - OS の表面などに垂直な方向)を向いていてよい。

40

【0110】

C AAC - OS は、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

【0111】

例えば、膜状に形成されたC AAC - OS を、膜表面または基板面に垂直な方向から電子顕微鏡で観察すると三角形または六角形の原子配列が認められる。

50

## 【0112】

さらに、電子顕微鏡で膜断面を観察すると金属原子または金属原子および酸素原子（または窒素原子）の層状配列が認められる。

## 【0113】

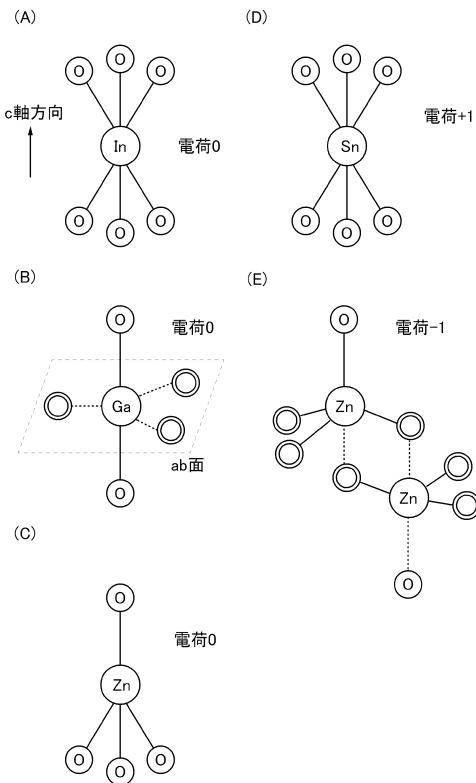

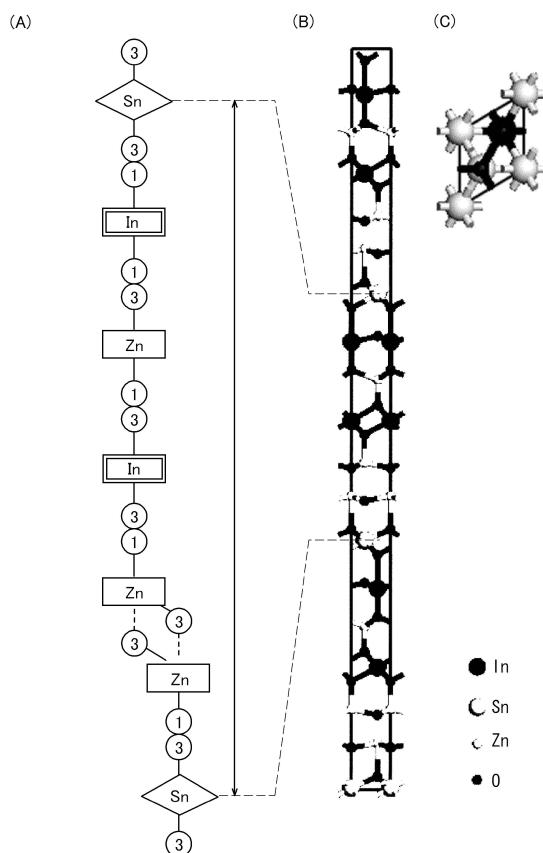

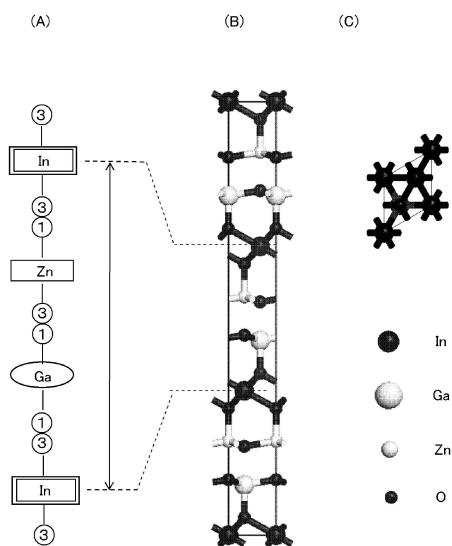

図7乃至図9を用いて、CAC-O-Sに含まれる結晶構造の一例について説明する。

## 【0114】

なお、図7乃至図9において、上方向がc軸方向であり、c軸方向と直交する面がab面である。

## 【0115】

本実施の形態において、上半分、下半分とは、ab面を境にした場合の上半分、下半分をいう。

10

## 【0116】

図7(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子（以下4配位のO）と、を有する構造Aを示す。

## 【0117】

ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。

20

## 【0118】

構造Aは、八面体構造をとるが、簡単のため平面構造で示している。

## 【0119】

なお、構造Aは上半分および下半分にはそれぞれ3個ずつ4配位のOがある。構造Aに示す小グループは電荷が0である。

## 【0120】

図7(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子（以下3配位のO）と、Gaに近接の2個の4配位のOと、を有する構造Bを示す。

30

## 【0121】

3配位のOは、いずれもab面に存在する。構造Bの上半分および下半分にはそれぞれ1個ずつ4配位のOがある。

## 【0122】

また、Inも5配位をとるため、構造Bをとりうる。構造Bの小グループは電荷が0である。

30

## 【0123】

図7(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造Cを示す。

## 【0124】

構造Cの上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。構造Cの小グループは電荷が0である。

40

## 【0125】

図7(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造Dを示す。

## 【0126】

構造Dの上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。

40

## 【0127】

構造Dの小グループは電荷が+1となる。

## 【0128】

図7(E)に、2個のZnを含む構造Eを示す。

## 【0129】

構造Eの上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。構造Eの小グループは電荷が-1となる。

## 【0130】

50

本実施の形態では複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ（ユニットセルともいう。）と呼ぶ。

【0131】

ここで、これらの小グループ同士が結合する規則について説明する。

【0132】

図7（A）に示す6配位のInの上半分の3個のOは下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Inを有する。

【0133】

図7（B）に示す5配位のGaの上半分の1個のOは、下方向に1個の近接Gaを有し、下半分の1個のOは、上方向に1個の近接Gaを有する。

10

【0134】

図7（C）に示す4配位のZnの上半分の1個のOは、下方向に1個の近接Znを有し、下半分の3個のOは、上方向にそれぞれ3個の近接Znを有する。

【0135】

この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。

【0136】

Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。

20

【0137】

従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。

【0138】

その理由を以下に示す。例えば、6配位の金属原子（InまたはSn）が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子（GaまたはIn）または4配位の金属原子（Zn）のいずれかと結合することになる。

【0139】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。

30

【0140】

また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

【0141】

図8（A）に、In-Sn-Zn-O系の層構造を構成する中グループAのモデル図を示す。

【0142】

図8（B）に、3つの中グループで構成される大グループBを示す。

【0143】

なお、図8（C）は、図8（B）の層構造をc軸方向から観察した場合の原子配列を示す。

40

【0144】

中グループAでは、3配位のOは省略し、4配位のOは個数のみである。

【0145】

例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。

【0146】

同様に、中グループAにおいて、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。

50

## 【0147】

また、中グループAにおいて、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZ<sub>n</sub>と、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZ<sub>n</sub>とを示している。

## 【0148】

中グループAは、In - Sn - Zn - O系の層構造を構成し、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合する。

## 【0149】

そのInが、上半分に3個の4配位のOがあるZ<sub>n</sub>と結合する。

10

## 【0150】

そのZ<sub>n</sub>の下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合する。

## 【0151】

そのInが、上半分に1個の4配位のOがあるZ<sub>n</sub>2個からなる小グループと結合する。

## 【0152】

この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。

## 【0153】

この中グループが複数結合して大グループを構成する。

20

## 【0154】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ-0.667、-0.5と考えることができる。

## 【0155】

例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。

## 【0156】

そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷-1が必要となる。

30

## 【0157】

電荷-1をとる構造として、構造Eに示すように、2個のZnを含む小グループが挙げられる。

## 【0158】

例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができます。

## 【0159】

具体的には、大グループBが繰り返されることで、In - Sn - Zn - O系の結晶(In<sub>2</sub>SnZn<sub>3</sub>O<sub>8</sub>)を得ることができる。

40

## 【0160】

得られるIn - Sn - Zn - O系の層構造は、In<sub>2</sub>SnZn<sub>2</sub>O<sub>7</sub>(ZnO)<sub>m</sub>(mは0または自然数。)とする組成式で表すことができる。

## 【0161】

In - Sn - Zn - O系の結晶は、mの数が大きいと結晶性が向上するため、好ましい。

## 【0162】

In - Sn - Zn - O系以外の酸化物半導体を用いた場合も同様である。

## 【0163】

例えば、図9(A)に、In - Ga - Zn - O系の層構造を構成する中グループLのモデル図を示す。

50

## 【0164】

中グループLにおいて、In-Ga-Zn-O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合する。

## 【0165】

そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合する。

## 【0166】

そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合する。

10

## 【0167】

この中グループが複数結合して大グループを構成する。

## 【0168】

図9(B)に3つの中グループで構成される大グループMを示す。

## 【0169】

なお、図9(C)は、図9(B)の層構造をc軸方向から観察した場合の原子配列を示している。

## 【0170】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。

20

## 【0171】

そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

## 【0172】

また、In-Ga-Zn-O系の層構造を構成する中グループは、中グループLに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

## 【0173】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

30

## 【0174】

## (実施の形態4)

酸化物半導体に限らず、実際に測定される絶縁ゲート型トランジスタの電界効果移動度は、さまざまな理由によって本来の移動度よりも低くなる。

## 【0175】

移動度を低下させる要因としては半導体内部の欠陥や半導体と絶縁膜との界面の欠陥があるが、Levinsonモデルを用いると、半導体内部に欠陥がないと仮定した場合の電界効果移動度を理論的に導き出せる。

## 【0176】

40

半導体本来の移動度を $\mu_0$ 、測定される電界効果移動度を $\mu$ とし、半導体中に何らかのポテンシャル障壁(粒界等)が存在すると仮定すると、式(2)で表される。

## 【0177】

## 【数2】

$$\mu = \mu_0 \exp\left(-\frac{E}{kT}\right) \quad \dots \quad (2)$$

## 【0178】

Eはポテンシャル障壁の高さであり、kがボルツマン定数、Tは絶対温度である。

50

## 【0179】

また、ポテンシャル障壁が欠陥に由来すると仮定すると、Levinsonモデルでは、数式(3)で表される。

## 【0180】

## 【数3】

$$E = \frac{e^2 N^2}{8 \epsilon n} = \frac{e^3 N^2 t}{8 \epsilon C_{ox} V_g} \quad \dots \quad (3)$$

## 【0181】

$e$  は電気素量、 $N$  はチャネル内の単位面積当たりの平均欠陥密度、 $\epsilon$  は半導体の誘電率、 $n$  は単位面積当たりのチャネルに含まれるキャリア数、 $C_{ox}$  は単位面積当たりの容量、 $V_g$  はゲート電圧、 $t$  はチャネルの厚さである。

## 【0182】

なお、厚さ 30 nm 以下の半導体層であれば、チャネルの厚さは半導体層の厚さと同一として差し支えない。

## 【0183】

線形領域におけるドレイン電流  $I_d$  は、数式(4)で表される。

## 【0184】

## 【数4】

$$I_d = \frac{W \mu V_g V_d C_{ox}}{L} \exp\left(-\frac{E}{kT}\right) \quad \dots \quad (4)$$

## 【0185】

ここで、 $L$  はチャネル長、 $W$  はチャネル幅であり、ここでは、 $L = W = 10 \mu m$  である。

## 【0186】

また、 $V_d$  はドレイン電圧である。

## 【0187】

数式(4)の両辺を  $V_g$  で割り、更に両辺の対数を取ると、数式(5)で表される。

## 【0188】

## 【数5】

$$\ln\left(\frac{I_d}{V_g}\right) = \ln\left(\frac{W \mu V_d C_{ox}}{L}\right) - \frac{E}{kT} = \ln\left(\frac{W \mu V_d C_{ox}}{L}\right) - \frac{e^3 N^2 t}{8 k T \epsilon C_{ox} V_g} \quad \dots \quad (5)$$

## 【0189】

数式(5)の右辺は  $V_g$  の関数である。

## 【0190】

上の式からわかるように、縦軸を  $1 n (I_d / V_g)$  、横軸を  $1 / V_g$  とする直線の傾きから平均欠陥密度  $N$  が求められる。

## 【0191】

すなわち、トランジスタの  $I_d - V_g$  特性から、平均欠陥密度を評価できる。

## 【0192】

酸化物半導体としては、インジウム( $In$ )、スズ( $Sn$ )、亜鉛( $Zn$ )の比率が、 $In : Sn : Zn = 1 : 1 : 1$  のものでは平均欠陥密度  $N$  は  $1 \times 10^{12} / cm^2$  程度である。

## 【0193】

このようにして求めた欠陥密度等をもとに  $\mu_0 = 120 \text{ cm}^2 / \text{Vs}$  が導出される。

## 【0194】

10

20

30

40

50

欠陥のある In - Sn - Zn 酸化物で測定される移動度は  $35 \text{ cm}^2 / \text{V s}$  程度である。

【0195】

しかし、半導体内部および半導体と絶縁膜との界面の欠陥が無い酸化物半導体の移動度  $\mu_0$  は  $120 \text{ cm}^2 / \text{V s}$  となると予想できる。

【0196】

ただし、半導体内部に欠陥がなくても、チャネルとゲート絶縁層との界面での散乱によってトランジスタの輸送特性は影響を受ける。すなわち、ゲート絶縁層界面から  $x$  だけ離れた場所における移動度  $\mu_1$  は、数式(6)で表される。

【0197】

【数6】

$$\frac{1}{\mu_1} = \frac{1}{\mu_0} + \frac{D}{B} \exp\left(-\frac{x}{G}\right) \quad \dots \quad (6)$$

【0198】

D はゲート方向の電界、B、G は定数である。B および G は、実際の測定結果より求めることができ、上記の測定結果からは、 $B = 4.75 \times 10^7 \text{ cm/s}$ 、 $G = 10 \text{ nm}$  (界面散乱が及ぶ深さ) である。

【0199】

D が増加する (すなわち、ゲート電圧が高くなる) と数式(6)の第2項が増加するため、移動度  $\mu_1$  は低下することがわかる。

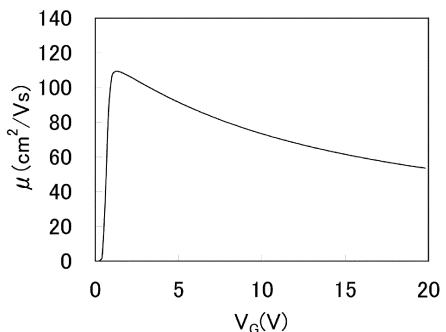

【0200】

半導体内部の欠陥が無い理想的な酸化物半導体をチャネルに用いたトランジスタの移動度  $\mu$  の計算結果 E を図 10 に示す。

【0201】

なお、計算にはシノプシス社製のデバイスシミュレーションソフトである Sentaurus Device を使用した。

【0202】

計算において、酸化物半導体のバンドギャップ、電子親和力、比誘電率、厚さをそれぞれ、2.8 電子ボルト、4.7 電子ボルト、15、15 nm とした。

【0203】

これらの値は、スパッタリング法により形成された薄膜を測定して得られたものである。

【0204】

さらに、ゲート、ソース、ドレインの仕事関数をそれぞれ、5.5 電子ボルト、4.6 電子ボルト、4.6 電子ボルトとした。

【0205】

また、ゲート絶縁層の厚さは 100 nm、比誘電率は 4.1 とした。チャネル長およびチャネル幅はともに 10  $\mu\text{m}$ 、ドレイン電圧  $V_d$  は 0.1 V である。

【0206】

計算結果 E で示されるように、ゲート電圧 1 V 強で移動度  $100 \text{ cm}^2 / \text{V s}$  以上のピークをつけるが、ゲート電圧がさらに高くなると、界面散乱が大きくなり、移動度が低下する。

【0207】

なお、界面散乱を低減するためには、半導体層表面を原子レベルで平坦にすること (Atomic Layer Flatness) が望ましい。

【0208】

このような移動度を有する酸化物半導体を用いて微細なトランジスタを作製した場合の

10

20

30

40

50

特性を計算した。

【0209】

なお、計算に用いたトランジスタは酸化物半導体膜に一対のn型半導体領域にチャネル形成領域が挟まれたものを用いた。

【0210】

一対のn型半導体領域の抵抗率は $2 \times 10^{-3}$  cmとして計算した。

【0211】

また、チャネル長を33 nm、チャネル幅を40 nmとして計算した。

【0212】

また、ゲート電極の側壁にサイドウォールを有する。

10

【0213】

サイドウォールと重なる半導体領域をオフセット領域として計算した。

【0214】

計算にはシノプシス社製のデバイスシミュレーションソフト、Santaurus Deviceを使用した。

【0215】

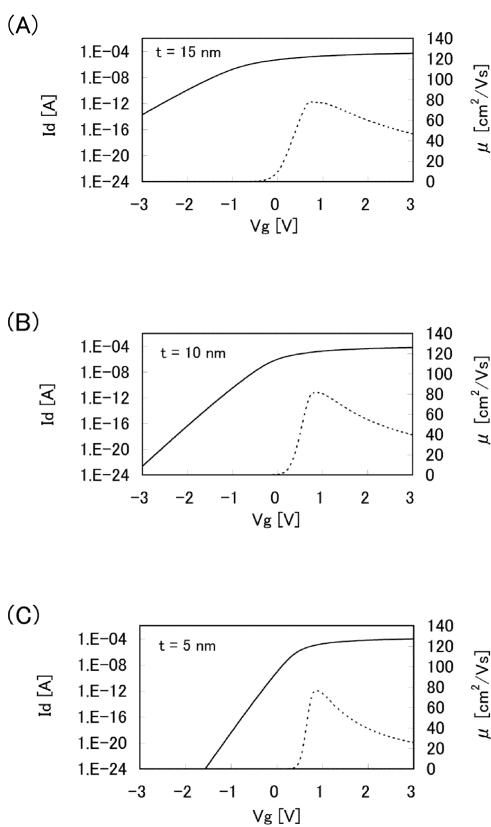

図11は、トランジスタのドレイン電流( $I_d$ 、実線)および移動度( $\mu$ 、点線)のゲート電圧( $V_g$ 、ゲートとソースの電位差)依存性の計算結果である。

【0216】

ドレイン電流 $I_d$ は、ドレイン電圧(ドレインとソースの電位差)を+1 Vとし、移動度 $\mu$ はドレイン電圧を+0.1 Vとして計算したものである。

20

【0217】

図11(A)はゲート絶縁層の厚さを15 nmとして計算したものである。

【0218】

図11(B)はゲート絶縁層の厚さを10 nmとして計算したものである。

【0219】

図11(C)はゲート絶縁層の厚さを5 nmとして計算したものである。

【0220】

ゲート絶縁層が薄くなるほど、特にオフ状態でのドレイン電流 $I_d$ (オフ電流)が顕著に低下する。

30

【0221】

一方、移動度 $\mu$ のピーク値やオン状態でのドレイン電流 $I_d$ (オン電流)には目立った変化が無い。

【0222】

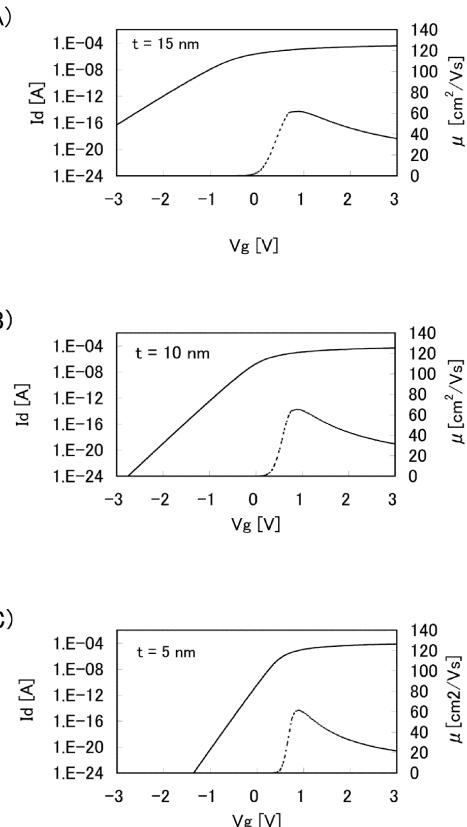

図12は、オフセット長(サイドウォール長) $L_{off}$ を5 nmとしたもののドレイン電流 $I_d$ (実線)および移動度 $\mu$ (点線)のゲート電圧 $V_g$ 依存性を示す。

【0223】

ドレイン電流 $I_d$ は、ドレイン電圧を+1 Vとし、移動度 $\mu$ はドレイン電圧を+0.1 Vとして計算したものである。

【0224】

40

図12(A)はゲート絶縁層の厚さを15 nmとして計算したものである。

【0225】

図12(B)はゲート絶縁層の厚さを10 nmとして計算したものである。

【0226】

図12(C)はゲート絶縁層の厚さを5 nmとして計算したものである。

【0227】

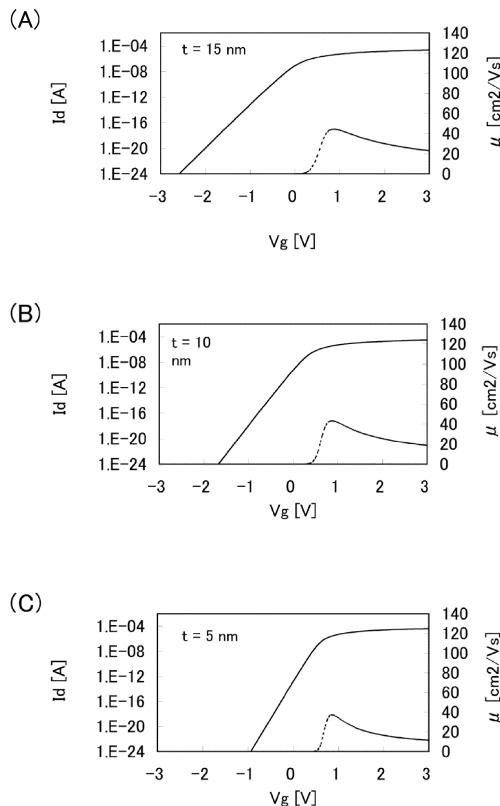

図13は、オフセット長(サイドウォール長) $L_{off}$ を15 nmとしたもののドレイン電流 $I_d$ (実線)および移動度 $\mu$ (点線)のゲート電圧依存性を示す。

【0228】

ドレイン電流 $I_d$ は、ドレイン電圧を+1 Vとし、移動度 $\mu$ はドレイン電圧を+0.1

50

Vとして計算したものである。

【0229】

図13(A)はゲート絶縁層の厚さを15nmとして計算したものである。

【0230】

図13(B)はゲート絶縁層の厚さを10nmとして計算したものである。

【0231】

図13(C)はゲート絶縁層の厚さを5nmとして計算したものである。

【0232】

いずれもゲート絶縁層が薄くなるほど、オフ電流が顕著に低下する一方、移動度 $\mu$ のピーク値やオン電流には目立った変化が無い。

10

【0233】

なお、移動度 $\mu$ のピークは、図11では $80\text{ cm}^2/\text{Vs}$ 程度であるが、図12では $60\text{ cm}^2/\text{Vs}$ 程度、図13では $40\text{ cm}^2/\text{Vs}$ と、オフセット長 $L_{off}$ が増加するほど低下する。

10

【0234】

また、オフ電流も同様な傾向がある。

【0235】

一方、オン電流にはオフセット長 $L_{off}$ の増加にともなって減少するが、オフ電流の低下に比べるとはるかに緩やかである。

20

【0236】

また、いずれもゲート電圧1V前後で、ドレイン電流はメモリ素子等で必要とされる10 $\mu\text{A}$ を超えることが示された。

【0237】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0238】

(実施の形態5)

In、Sn、Znを含有する酸化物半導体を用いたトランジスタは、酸化物半導体を形成する際に基板を加熱して成膜すること、或いは酸化物半導体膜を形成した後に熱処理を行うことで良好な特性を得ることができる。

30

【0239】

なお、In、Sn、Znは組成比でそれぞれ5atomic%以上含まれていると好ましい。

【0240】

In、Sn、Znを含有する酸化物半導体膜の成膜後に基板を意図的に加熱することで、トランジスタの電界効果移動度を向上させることができるとなる。

【0241】

また、nチャネル型のトランジスタのしきい値電圧をプラスシフトさせることができる。

【0242】

nチャネル型のトランジスタのしきい値電圧をプラスシフトさせることにより、nチャネル型のトランジスタのオフ状態を維持するための電圧の絶対値を低くすることができ、低消費電力化が可能となる。

40

【0243】

さらに、nチャネル型のトランジスタのしきい値電圧をプラスシフトさせて、しきい値電圧を0V以上にすれば、ノーマリーオフ型のトランジスタを形成することが可能となる。

【0244】

以下In、Sn、Znを含有する酸化物半導体を用いたトランジスタの特性を示す。

【0245】

50

## (サンプルA～C共通条件)

組成比として  $I_n : S_n : Z_n = 1 : 1 : 1$  のターゲットを用いて、ガス流量比を  $A_r / O_2 = 6 / 9$  sccm、成膜圧力を 0.4 Pa、成膜電力 100 W として、15 nm の厚さとなるように基板上に酸化物半導体膜を成膜した。

## 【0246】

次に、酸化物半導体膜を島状になるようにエッティング加工した。

## 【0247】

そして、酸化物半導体膜上に 50 nm の厚さとなるようにタンゲステン層を成膜し、これをエッティング加工してソース電極及びドレイン電極を形成した。

## 【0248】

次に、プラズマ CVD 法を用いて、シランガス ( $SiH_4$ ) と一酸化二窒素 ( $N_2O$ ) を用いて 100 nm の厚さとなるように酸化窒化珪素膜 ( $SiON$ ) を形成してゲート絶縁層とした。

## 【0249】

次に、15 nm の厚さとなるように窒化タンタルを形成し、135 nm の厚さとなるようにタンゲステンを形成し、これらをエッティング加工してゲート電極を形成した。

## 【0250】

さらに、プラズマ CVD 法を用いて、300 nm の厚さとなるように酸化窒化珪素膜 ( $SiON$ ) を形成し、1.5  $\mu m$  の厚さとなるようにポリイミド膜を形成し層間絶縁膜とした。

## 【0251】

次に、層間絶縁膜にコンタクトホールを形成し、50 nm の厚さとなるように第 1 のチタン膜を形成し、100 nm の厚さとなるようにアルミニウム膜を形成し、50 nm の厚さとなるように第 2 のチタン膜を形成し、これらをエッティング加工して測定用のパッドを形成した。

## 【0252】

以上のようにしてトランジスタを有する半導体装置を形成した。

## 【0253】

## (サンプルA)

サンプル A は酸化物半導体膜の成膜中に基板に意図的な加熱を施さなかった。

## 【0254】

また、サンプル A は酸化物半導体膜の成膜後であって、酸化物半導体膜のエッティング加工前に加熱処理を施さなかった。

## 【0255】

## (サンプルB)

サンプル B は基板を 200 になるように加熱した状態で酸化物半導体膜の成膜を行った。

## 【0256】

また、サンプル B は酸化物半導体膜の成膜後であって、酸化物半導体膜のエッティング加工前に加熱処理を施さなかった。

## 【0257】

基板を加熱した状態で成膜を行った理由は、酸化物半導体膜中でドナーとなる水素を追い出すためである。

## 【0258】

## (サンプルC)

サンプル C は基板を 200 になるように加熱した状態で酸化物半導体膜の成膜を行った。

## 【0259】

さらに、サンプル C は酸化物半導体膜の成膜後であって、酸化物半導体膜のエッティング加工前に窒素雰囲気で 650 1 時間の加熱処理を施した後、酸素雰囲気で 650 1 時

10

20

30

40

50

間の加熱処理を施した。

【0260】

窒素雰囲気で650 1時間の加熱処理を施した理由は、酸化物半導体膜中でドナーとなる水素を追い出すためである。

【0261】

ここで、酸化物半導体膜中でドナーとなる水素を追い出すための加熱処理で酸素も離脱し、酸化物半導体膜中でキャリアとなる酸素欠損も生じてしまう。

【0262】

そこで、酸素雰囲気で650 1時間の加熱処理を施すことにより、酸素欠損を低減する効果を狙った。

10

【0263】

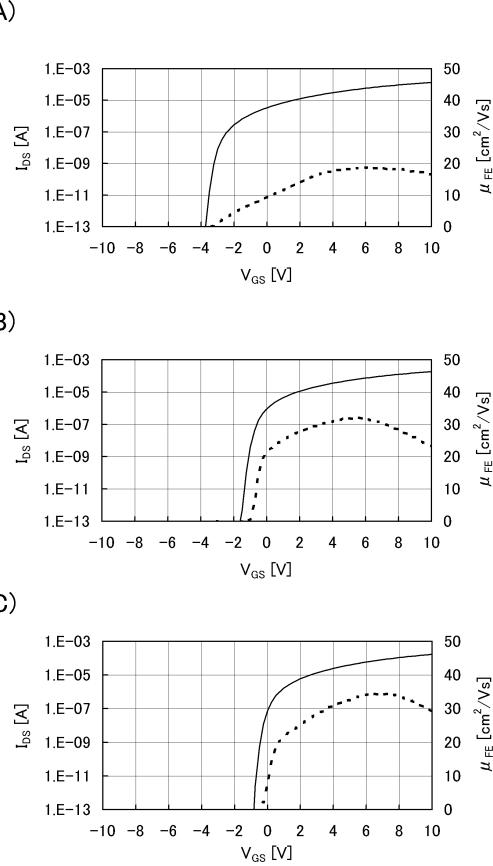

(サンプルA～Cのトランジスタの特性)

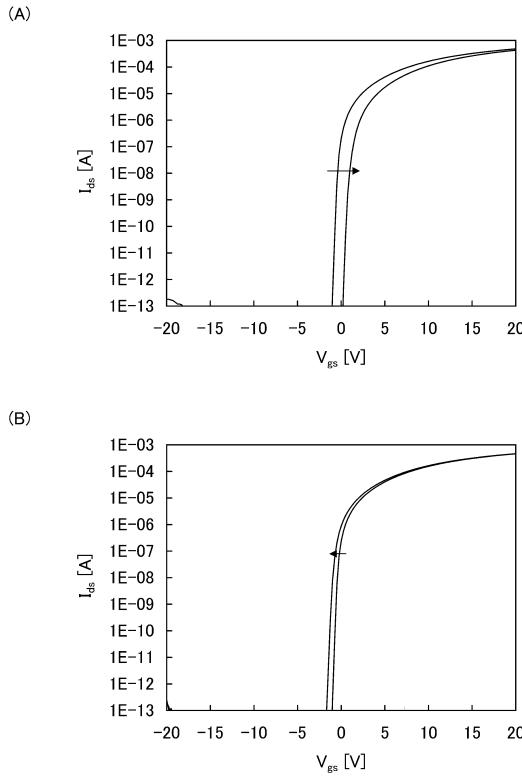

図14(A)にサンプルAのトランジスタの初期特性を示す。

【0264】

図14(B)にサンプルBのトランジスタの初期特性を示す。

【0265】

図14(C)にサンプルCのトランジスタの初期特性を示す。

【0266】

サンプルAのトランジスタの電界効果移動度は $18.8 \text{ cm}^2/\text{V sec}$ であった。

【0267】

サンプルBのトランジスタの電界効果移動度は $32.2 \text{ cm}^2/\text{V sec}$ であった。

20

【0268】

サンプルCのトランジスタの電界効果移動度は $34.5 \text{ cm}^2/\text{V sec}$ であった。

【0269】

ここで、サンプルA～Cと同様の成膜方法で形成した酸化物半導体膜の断面を透過型顕微鏡(TEM)で観察したところ、成膜時に基板加熱を行ったサンプルB及びサンプルCと同様の成膜方法で形成したサンプルには結晶性が確認された。

【0270】

そして、驚くべきことに、成膜時に基板加熱を行ったサンプルは、結晶性部分と非結晶性部分とを有し、結晶性部分の配向がc軸配向に揃っている結晶性であった。

30

【0271】

通常の多結晶では結晶性部分の配向が揃っておらず、ばらばらの方向を向いているため、成膜時に基板加熱を行ったサンプルは新しい構造を有している。

【0272】

また、図14(A)～(C)を比較すると、成膜時に基板加熱を行うこと、又は、成膜後に加熱処理を行うことにより、ドナーとなる水素元素を追い出すことができるため、nチャネル型トランジスタのしきい値電圧をプラスシフトできることが理解できる。

【0273】

即ち、成膜時に基板加熱を行ったサンプルBのしきい値電圧は、成膜時に基板加熱を行っていないサンプルAのしきい値電圧よりもプラスシフトしている。

40

【0274】

また、成膜時に基板加熱を行ったサンプルB及びサンプルCを比較した場合、成膜後に加熱処理を行ったサンプルCの方が、成膜後に加熱処理を行っていないサンプルBよりもプラスシフトしていることがわかる。

【0275】

また、水素のような軽元素は加熱処理の温度が高いほど離脱しやすいため、加熱処理の温度が高いほど水素が離脱しやすい。

【0276】

よって、成膜時又は成膜後の加熱処理の温度を更に高めればよりプラスシフトが可能であると考察した。

50

## 【0277】

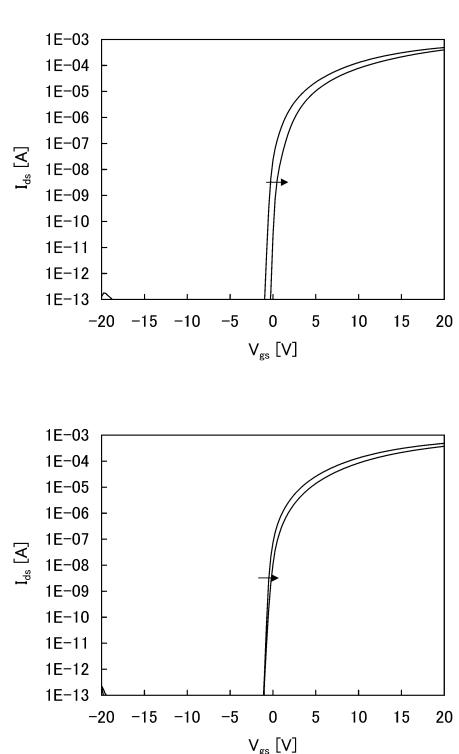

(サンプルBとサンプルCのゲートBTストレス試験結果)

サンプルB(成膜後加熱処理なし)及びサンプルC(成膜後加熱処理あり)に対してゲートBTストレス試験を行った。

## 【0278】

まず、基板温度を25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 特性の測定を行い、加熱及びプラスの高電圧印加を行う前のトランジスタの特性を測定した。

## 【0279】

次に、基板温度を150とし、 $V_{ds}$ を0.1Vとした。

10

## 【0280】

次に、ゲート絶縁層に印加される $V_{gs}$ に20Vを印加し、そのまま1時間保持した。

## 【0281】

次に、 $V_{gs}$ を0Vとした。

## 【0282】

次に、基板温度25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 特性の測定を行い、加熱及びプラスの高電圧印加を行った後のトランジスタの特性を測定した。

## 【0283】

以上のようにして、加熱及びプラスの高電圧印加を行う前後のトランジスタの特性を比較することをプラスBT試験と呼ぶ。

20

## 【0284】

一方、まず基板温度を25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 特性の測定を行い、加熱及びマイナスの高電圧印加を行う前のトランジスタの特性を測定した。

## 【0285】

次に、基板温度を150とし、 $V_{ds}$ を0.1Vとした。

## 【0286】

次に、ゲート絶縁層に印加される $V_{gs}$ に-20Vを印加し、そのまま1時間保持した。

30

## 【0287】

次に、 $V_{gs}$ を0Vとした。

## 【0288】

次に、基板温度25とし、 $V_{ds}$ を10Vとし、トランジスタの $V_{gs}$ - $I_{ds}$ 特性の測定を行い、加熱及びマイナスの高電圧印加を行った後のトランジスタの特性を測定した。

## 【0289】

以上のようにして、加熱及びマイナスの高電圧印加を行う前後のトランジスタの特性を比較することをマイナスBT試験と呼ぶ。

## 【0290】

40

図15(A)はサンプルBのプラスBT試験結果であり、図15(B)はサンプルBのマイナスBT試験結果である。

## 【0291】

図16(A)はサンプルCのプラスBT試験結果であり、図16(B)はサンプルCのマイナスBT試験結果である。

## 【0292】

プラスBT試験及びマイナスBT試験はトランジスタの劣化具合を判別する試験であるが、図15(A)及び図16(A)を参照すると少なくともプラスBT試験の処理を行うことにより、しきい値電圧をプラスシフトさせることができることがわかった。

## 【0293】

50

特に、図15(A)ではプラスBT試験の処理を行うことにより、トランジスタがノーマリーオフ型になったことがわかる。

【0294】

よって、トランジスタの作製時の加熱処理に加えて、プラスBT試験の処理を行うことにより、しきい値電圧のプラスシフト化を促進でき、ノーマリーオフ型のトランジスタを形成することができることがわかった。

【0295】

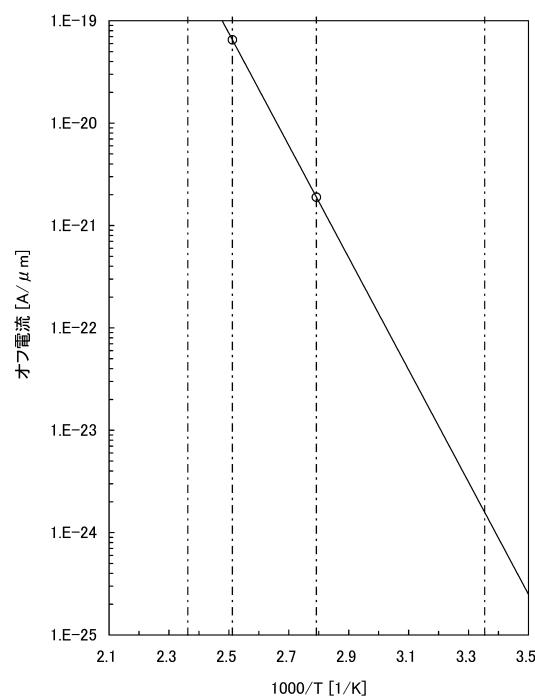

図17はサンプルAのトランジスタのオフ電流と測定時の基板温度(絶対温度)の逆数との関係を示す。

【0296】

ここでは、測定時の基板温度の逆数に1000を掛けた数値( $1000/T$ )を横軸としている。

【0297】

なお、図17ではチャネル幅1μmの場合における電流量を図示している。

【0298】

基板温度が125( $1000/T$ が約2.51)のとき $1 \times 10^{-19} A$ 以下となっていた。

【0299】

基板温度が85( $1000/T$ が約2.79)のとき $1 \times 10^{-20} A$ 以下となっていた。

【0300】

つまり、シリコン半導体を用いたトランジスタと比較して極めて低いオフ電流であることがわかった。

【0301】

なお、温度が低いほどオフ電流が低下するため、常温であればより低いオフ電流であることは明らかである。

【0302】

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0303】

(実施の形態6)

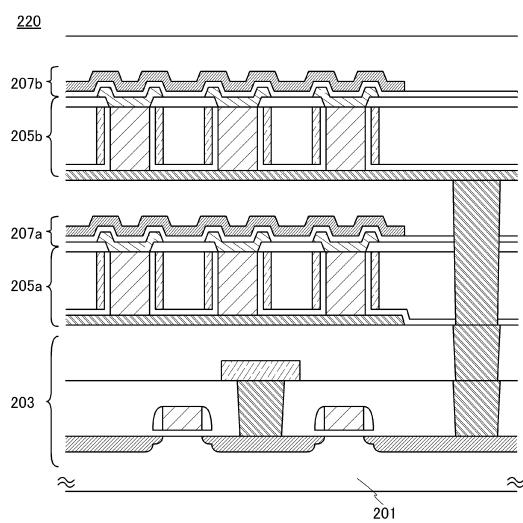

本実施の形態では、半導体回路が形成された基板上にメモリ素子が積層されたメモリ装置の例について図4及び図5を用いて説明する。

【0304】

図4はメモリ装置200の断面概略図である。メモリ装置200は、センスアンプや、デコーダ等の、メモリ素子を駆動するための回路(駆動回路203)が、単結晶半導体基板201表面に公知の半導体集積回路技術を用いて形成されている。その上にセルトランジスタ層205が設けられ、さらにその上にキャパシタ層207が形成されている。

【0305】

図4に示されるセルトランジスタ、及びキャパシタは、実施の形態2を参照して作製できる。

【0306】

セルトランジスタのビット線は、コンタクトプラグを介してその下層に設けられた駆動回路203と電気的に接続される。したがって、駆動回路203から出力された電位信号は、共通するビット線を介して各セルトランジスタに入力される。

【0307】

またここでは図示しないが、セルトランジスタ層205のワード線はそれぞれ同様にコンタクトプラグ等を介して駆動回路203に電気的に接続されている。したがって、駆動回路203から出力される電位に応じて、セルトランジスタのオン、オフを制御することができる。

10

20

30

40

50

## 【0308】

このような構成とすることにより、メモリ装置200は、駆動回路203によってその上方に設けられるセルトランジスタを制御することにより、書き込み、読み出し動作を行うことができる。

## 【0309】

以上のように、単結晶半導体基板201上に、集積化されたセルトランジスタ層205及びキャパシタ層207を積層することにより、基板表面に対する占有面積が縮小され、より集積化されたメモリ装置200とすることができます。

## 【0310】

ここで、セルトランジスタ層205及びキャパシタ層207上に形成された絶縁層を介して、さらに上方にセルトランジスタ層及びキャパシタ層を積層することもできる。 10

## 【0311】

セルトランジスタ層を積層した構成の一例として、図5にメモリ装置220の断面概略図を示す。

## 【0312】

メモリ装置220は、単結晶半導体基板201表面に形成された駆動回路203上に、セルトランジスタ層205a、キャパシタ層207a、セルトランジスタ層205b、及びキャパシタ層207bが順に積層されている。

## 【0313】

図5には、基板側から2層目となるセルトランジスタ層205bのビット線と、駆動回路203とがコンタクトプラグを介して電気的に接続される領域を含む断面概略図を示している。 20

## 【0314】

また、キャパシタ層207aとセルトランジスタ層205bとの間には絶縁層が設けられている。当該絶縁層は、キャパシタ層の容量配線とビット線やワード線との間に形成される寄生容量を緩和するため、膜厚を十分厚くするか、低誘電率の絶縁材料を用いて形成してもよい。

## 【0315】

なお、本実施の形態では、セルトランジスタ及びキャパシタからなるメモリ素子を2層積層する構成を例示したが、これに限られず3層以上の積層とすることができます。また、ここでは1層目のセルトランジスタの直上に2層目のセルトランジスタを設ける構成としているが、2層目のセルトランジスタを基板表面と平行な向きにずらして形成してもよい。 30

## 【0316】

以上のように、絶縁層を介して多層構造としたメモリ装置220は、メモリセルの基板表面に対する占有面積がより縮小され、高集積化されたメモリ装置220とすることができます。

## 【0317】

本実施の形態は、本明細書等で例示する他の実施の形態と適宜組み合わせて実施することができる。 40

## 【符号の説明】

## 【0318】

|     |        |

|-----|--------|

| 100 | メモリ装置  |

| 101 | 基板     |

| 103 | ビット線   |

| 105 | ワード線   |

| 107 | 容量電極   |

| 109 | 半導体層   |

| 111 | ゲート絶縁層 |

| 113 | 下地絶縁層  |

|         |           |    |

|---------|-----------|----|

| 1 1 5   | 絶縁層       |    |

| 1 1 7   | 絶縁層       |    |

| 1 1 9   | 容量線       |    |

| 1 2 9   | 半導体膜      |    |

| 1 4 1   | レジスト      |    |

| 1 4 3   | 絶縁膜       |    |

| 1 4 5   | ハードマスク    | 10 |

| 1 4 7   | 絶縁膜       |    |

| 1 5 0   | セルトランジスタ  |    |

| 1 6 0   | キャパシタ     |    |

| 2 0 0   | メモリ装置     |    |

| 2 0 1   | 単結晶半導体基板  |    |

| 2 0 3   | 駆動回路      |    |

| 2 0 5   | セルトランジスタ層 |    |

| 2 0 5 a | セルトランジスタ層 |    |

| 2 0 5 b | セルトランジスタ層 |    |

| 2 0 7   | キャパシタ層    |    |

| 2 0 7 a | キャパシタ層    |    |

| 2 0 7 b | キャパシタ層    |    |

| 2 2 0   | メモリ装置     | 20 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【 図 8 】

【 四 9 】

---

フロントページの続き

|               |           |               |         |

|---------------|-----------|---------------|---------|

| (51)Int.Cl.   | F I       |               |         |

| C 2 3 C 14/08 | (2006.01) | H 0 1 L 27/10 | 4 4 1   |

|               |           | H 0 1 L 27/10 | 6 2 1 Z |

|               |           | C 2 3 C 14/08 | K       |

(56)参考文献 特開2010-282173 (JP, A)

特開2010-020863 (JP, A)

米国特許出願公開第2009/0197379 (US, A1)

特開2009-246383 (JP, A)

特開2009-016368 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

|         |               |

|---------|---------------|

| H 0 1 L | 2 1 / 8 2 4 2 |

| C 2 3 C | 1 4 / 0 8     |

| H 0 1 L | 2 1 / 3 3 6   |

| H 0 1 L | 2 7 / 1 0 5   |

| H 0 1 L | 2 7 / 1 0 8   |

| H 0 1 L | 2 9 / 7 8 6   |