등록특허 10-2471135

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년11월28일

(11) 등록번호 10-2471135

(24) 등록일자 2022년11월22일

(51) 국제특허분류(Int. Cl.)

*H03K 23/00* (2006.01) *H03L 7/16* (2006.01)

(52) CPC특허분류

*H03K 23/00* (2013.01)

*H03L 7/16* (2013.01)

(21) 출원번호 10-2019-7012773

(22) 출원일자(국제) 2017년11월08일

심사청구일자 2020년11월06일

(85) 번역문제출일자 2019년05월02일

(65) 공개번호 10-2019-0090787

(43) 공개일자 2019년08월02일

(86) 국제출원번호 PCT/US2017/060658

(87) 국제공개번호 WO 2018/089509

국제공개일자 2018년05월17일

(30) 우선권주장

15/346,524 2016년11월08일 미국(US)

(56) 선행기술조사문헌

JP09153773 A\*

US08063686 B1\*

US20130207707 A1\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 13 항

심사관 : 최규돈

## (54) 발명의 명칭 고 선형성 위상 보간기

## (57) 요 약

고 선형성 위상 보간기(PI)(107)의 설명된 예들에서, 제어 로직은 출력 신호와 입력 클록 신호에 사이의 원하는 위상 차이를 나타내는 위상 값 파라미터( $\alpha$ )를 제공할 수 있다. 제1 커패시터(C1)는 위상 값 파라미터에 비례하는 커패시터 상의 제1 전압을 생성하기 위해 위상 값 파라미터에 비례하는 제1 전류(401)로 제1 기간 동안 충전될 수 있다. 제1 커패시터(C1)는 제1 전압에 의해 오프셋된 전압 램프를 형성하기 위해 일정한 값을 갖는 제2 전류(402)로 제2 기간 동안 추가로 충전될 수 있다. 기준 전압(Vref)은 제2 기간 동안 전압 램프(PIout)와 비교될 수 있다(110). 출력 신호(120)는 전압 램프가 기준 전압과 동일한 시간에 표명될 수 있다.

## 대 표 도

(72) 발명자

탐, 카이, 이유

미국 95050 캘리포니아주 산타 클라라 에이피티. 3

프룬레지 애비뉴 2354

호쉬야르, 레자

미국 95135 캘리포니아주 산 호세 브룩 에스테이츠

코트 3011

---

키아에이, 알리

미국 95129 캘리포니아주 산 호세 버켓 드라이브

1282

## 명세서

### 청구범위

#### 청구항 1

위상 보간을 수행하는 방법으로서,

출력 신호와 입력 클록 에지 사이의 원하는 위상 차이를 나타내는 위상 값 파라미터를 생성하는 단계;

상기 위상 값 파라미터에 비례하는 제1 전류로 제1 기간 동안 제1 커패시터를 충전시켜, 상기 위상 값 파라미터에 비례하는 상기 커패시터 상의 제1 전압을 생성하는 단계;

상기 제1 전압에 의해 오프셋된 전압 램프를 형성하기 위해 일정한 값을 갖는 제2 전류로 상기 입력 클록 에지에 관한 제2 기간 동안 상기 제1 커패시터를 충전시키는 단계;

상기 제2 기간 동안 기준 전압과 상기 전압 램프를 비교하는 단계; 및

상기 전압 램프가 상기 기준 전압과 동일할 때 상기 출력 신호를 표명하는 단계

를 포함하고,

상기 기준 전압은, 일정한 값을 갖는 제3 전류로 제3 기간 동안 제2 커패시터를 충전시킴으로써; 그리고

상기 제2 기간 후 상기 제1 커패시터 및 상기 제2 커패시터를 리셋시킴으로써 생성되는, 방법.

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

제1항에 있어서, 상기 제2 전류는  $I_{-total}$ 의 값을 가지고 상기 제1 전류는  $(1-a)I_{-total}$ 의 값을 가지며,  $a$ 는 상기 위상 값 파라미터에 비례하는 방법.

#### 청구항 5

제1항에 있어서, 상기 제3 전류는 상기 제2 전류 값과 동일한 값을 가지는 방법.

#### 청구항 6

제1항에 있어서, 추가적인 일정 값 페데스탈 전류로 상기 제1 기간 동안 상기 제1 커패시터를 충전시키는 단계를 더 포함하는 방법.

#### 청구항 7

제1항에 있어서, 추가적인 일정 값 페데스탈 전류로 상기 제2 기간 동안 상기 제1 커패시터를 충전시키는 단계를 더 포함하는 방법.

#### 청구항 8

위상 보간 회로로서,

위상 값 파라미터에 비례하는 제1 정전류를 생성하도록 구성되는 제1 가변 전류원;

상기 제1 정전류와 제2 정전류의 합이 미리 정의된 고정 값이 되도록 하는 상기 제2 정전류를 생성하도록 구성되는 제2 가변 전류원;

상기 제1 가변 전류원에 제1 스위치 디바이스에 의해 그리고 상기 제2 가변 전류원에 제2 스위치 디바이스에 의해

해 커플링되는 램프 커패시터 - 상기 램프 커패시터는 상기 제1 정전류로 제1 기간 동안 충전되며, 상기 제1 정전류와 상기 제2 정전류의 합으로 제2 기간 동안 충전됨 -;

상기 제1 가변 전류원 및 상기 제2 가변 전류원에 의해 상기 램프 커패시터 상에서 생성된 전압을 수신하도록 커플링된 제1 입력, 기준 전압에 커플링된 제2 입력, 및 위상 시프트된 출력 신호를 제공하기 위한 출력을 갖는 비교기 회로 - 상기 비교기 회로는 상기 제2 기간 동안 상기 기준 전압과 상기 램프 커패시터 상에서 생성된 전압을 비교함 -;

제3 스위치 디바이스에 의해 전류원에 커플링된 기준 커패시터;

상기 램프 커패시터 및 접지 기준에 커플링되어 상기 램프 커패시터를 주기적으로 리셋하는 제4 스위치 디바이스; 및

상기 기준 커패시터 및 접지 기준에 커플링되어 상기 기준 커패시터를 주기적으로 리셋하는 제5 스위치 디바이스

를 포함하고,

상기 기준 전압은, 일정한 값을 갖는 제3 전류로 제3 기간 동안 상기 기준 커패시터를 충전시킴으로써; 그리고 상기 제2 기간 후 상기 램프 커패시터 및 상기 기준 커패시터를 리셋시킴으로써 생성되는, 위상 보간 회로.

#### 청구항 9

제8항에 있어서, 상기 제1 가변 전류원은  $(1-\alpha)I_0$ 와 동일한 전류를 생성하도록 구성되고, 상기 제2 가변 전류원은  $(\alpha)I_0$ 와 동일한 전류를 생성하도록 구성되며,  $\alpha$ 는 상기 출력 신호와 입력 클록 에지 사이의 원하는 위상 차이를 나타내는 위상 값 파라미터인 위상 보간 회로.

#### 청구항 10

삭제

#### 청구항 11

삭제

#### 청구항 12

삭제

#### 청구항 13

제8항에 있어서, 다른 스위치 디바이스에 의해 상기 램프 커패시터에 커플링되고 일정한 페데스탈 전류를 생성하도록 구성되는 제3 전류원을 더 포함하는 위상 보간 회로.

#### 청구항 14

제13항에 있어서, 다른 스위치 디바이스에 의해 상기 램프 커패시터에 커플링되고 다른 일정한 페데스탈 전류를 생성하도록 구성되는 제4 전류원을 더 포함하는 위상 보간 회로.

#### 청구항 15

시스템으로서,

출력 클록 신호의 각각의 위상이 입력 클록 신호의 위상들의 분수와 동일한 상기 출력 클록 신호를 생성하도록 구성되는 분수형 주파수 분할기(fractional frequency divider)(FFD) 모듈

을 포함하며, 상기 FFD는,

상기 출력 클록 신호의 위상을 정의하는데 필요한 상기 입력 클록 신호의 전체 위상 수를 나타내는 수(N)를 제공하도록 구성되고, 상기 출력 클록 신호의 위상을 정의하는데 필요한 상기 입력 클록 신호의 분수 위상을 나타내는 위상 값 파라미터를 제공하도록 구성되는 제어 로직;

상기 입력 클록 신호를 수신하도록 커플링되고 상기 제어 로직에 커플링되어 상기 수(N)를 수신하는 카운터 - 상기 카운터는 상기 카운터가 상기 입력 클록의 N 개 위상들을 카운트할 때마다 N번째 클록 신호를 표명하도록 구성되는 출력을 가짐 -;

상기 제어 로직으로부터 상기 위상 값 파라미터를 수신하고 상기 카운터로부터 상기 N번째 클록 신호를 수신하도록 커플링된 위상 보간기 모듈(PI)

을 포함하며, 상기 PI 모듈은,

상기 위상 값 파라미터에 비례하는 제1 정전류를 생성하도록 구성되는 제1 가변 전류원;

상기 제1 정전류와 제2 정전류의 합이 미리 정의된 고정 값이 되도록 하는 상기 제2 정전류를 생성하도록 구성되는 제2 가변 전류원;

상기 제1 가변 전류원에 제1 스위치 디바이스에 의해 그리고 상기 제2 가변 전류원에 제2 스위치 디바이스에 의해 커플링되는 램프 커패시터 - 상기 램프 커패시터는 상기 제1 정전류로 제1 기간 동안 충전되며, 상기 제1 정전류와 상기 제2 정전류의 합으로 제2 기간 동안 충전됨 -; 및

상기 제1 가변 전류원 및 상기 제2 가변 전류원에 의해 상기 램프 커패시터 상에서 생성된 전압을 수신하도록 커플링된 제1 입력, 기준 전압에 커플링된 제2 입력, 및 위상 시프트된 출력 클록 신호를 제공하기 위한 출력을 갖는 비교기 회로 - 상기 비교기 회로는 상기 제2 기간 동안 상기 기준 전압과 상기 램프 커패시터 상에서 생성된 전압을 비교함 -;

제3 스위치 디바이스에 의해 전류원에 커플링된 기준 커패시터;

상기 램프 커패시터 및 접지 기준에 커플링되어 상기 램프 커패시터를 주기적으로 리셋하는 제4 스위치 디바이스; 및

상기 기준 커패시터 및 접지 기준에 커플링되어 상기 기준 커패시터를 주기적으로 리셋하는 제5 스위치 디바이스

를 포함하고,

상기 기준 전압은, 일정한 값을 갖는 제3 전류로 제3 기간 동안 상기 기준 커패시터를 충전시킴으로써; 그리고

상기 제2 기간 후 상기 램프 커패시터 및 상기 기준 커패시터를 리셋시킴으로써 생성되는, 시스템.

## 청구항 16

제15항에 있어서, 상기 카운터에 커플링되어 상기 입력 클록 신호를 제공하는 출력을 갖는 발진기 회로를 더 포함하는 시스템.

## 청구항 17

제15항에 있어서, 상기 입력 클록 신호를 수신하도록 커플링되는 복수의 FFD 모듈들을 더 포함하는 시스템.

## 청구항 18

제17항에 있어서, 상기 시스템은 단일 접적 회로 상에 형성되는 시스템.

## 발명의 설명

## 기술 분야

[0001] 이는 대체로 위상 보간기(phase interpolator)들에 관한 것이고, 더 상세하게는 전체 동작 범위에 걸쳐 고 선형성을 가지는 위상 보간기들에 관한 것이다.

## 배경 기술

[0002] 위상 보간기(PI)가 기준 클록 신호의 에지로부터 특정된 양의 시간을 보간함으로써 기준 클록 신호로부터 위상 시프트된 클록 신호를 생성하는데 사용될 수 있다.

[0003] 예를 들어, 위상 보간기가 직렬화기/직렬화해제기(serializer/deserializer)(SerDes) 통신 인터페이스의 클록

및 데이터 복원(clock and data recovery)(CDR) 루프에서 사용될 수 있다. PI는 복원된 클록 위상을 데이터 샘플링 윈도우에서 적절한 포지션으로 시프트시키기 위하여 위상 잡금 루프(phase locked loop)(PLL)와 데이터 샘플러들 사이에 개재될 수 있다. 그것은 각각 동위상 및 직교 위상(I-Q)인 동일한 주파수의 두 개의 클록들을 수신하고, 위상이 두 개의 입력 위상들의 가중된 합인 클록 출력을 생성할 수 있다. 이상적인 PI는 0도부터 360 도까지의 전체 사이클에 대해 다수의 동일하게 이격된 위상 스텝들을 생성할 수 있다.

[0004] 통상적으로, SerDes 애플리케이션들은 고도로 선형적인 PI가 올바르게 동작할 것을 요구하지 않는다.

### 발명의 내용

[0005] 고 선형성 위상 보간기의 설명된 예들에서, 제어 로직이 출력 신호와 입력 클록 신호 예지 사이에 원하는 위상 차이를 나타내는 위상 값 파라미터를 제공할 수 있다. 제1 커페시터가 위상 값 파라미터에 비례하는 커페시터 상의 제1 전압을 생성하기 위해 위상 값 파라미터에 비례하는 제1 전류로 제1 기간 동안 충전될 수 있다. 제1 커페시터는 제1 전압에 의해 오프셋된 전압 램프를 형성하기 위해 일정한 값을 갖는 제2 전류로 제2 기간 동안 더 충전될 수 있다. 기준 전압이 제2 기간 동안 전압 램프와 비교될 수 있다. 출력 신호는 전압 램프가 기준 전압과 동일한 시간에 표명(assertion)될 수 있다.

### 도면의 간단한 설명

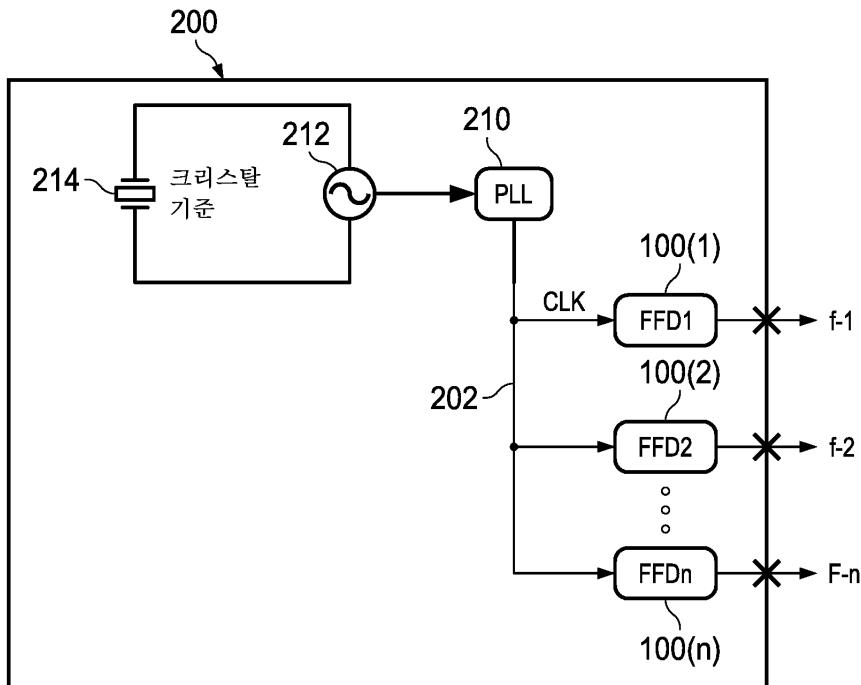

[0006] 도 1a 및 도 1b는 예시적인 분수형 주파수 분할기(fractional frequency divider)의 동작을 예시하는 블록도 및 타이밍 도이다.

도 2는 다수의 분수형 주파수 분할기들을 포함하는 예시적인 클록 발생기 시스템의 블록도이다.

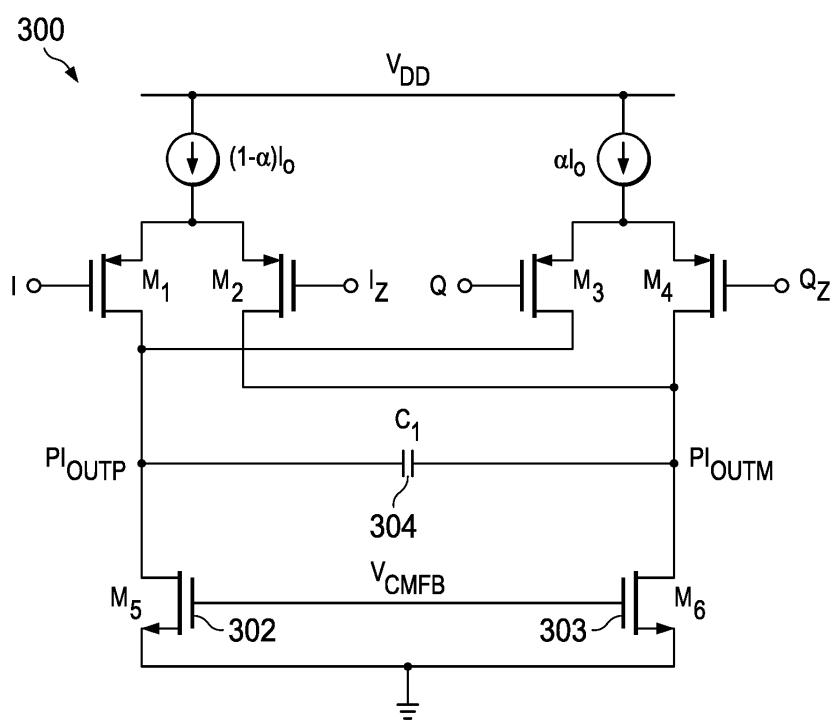

도 3은 기존의 위상 보간기의 개략도이다.

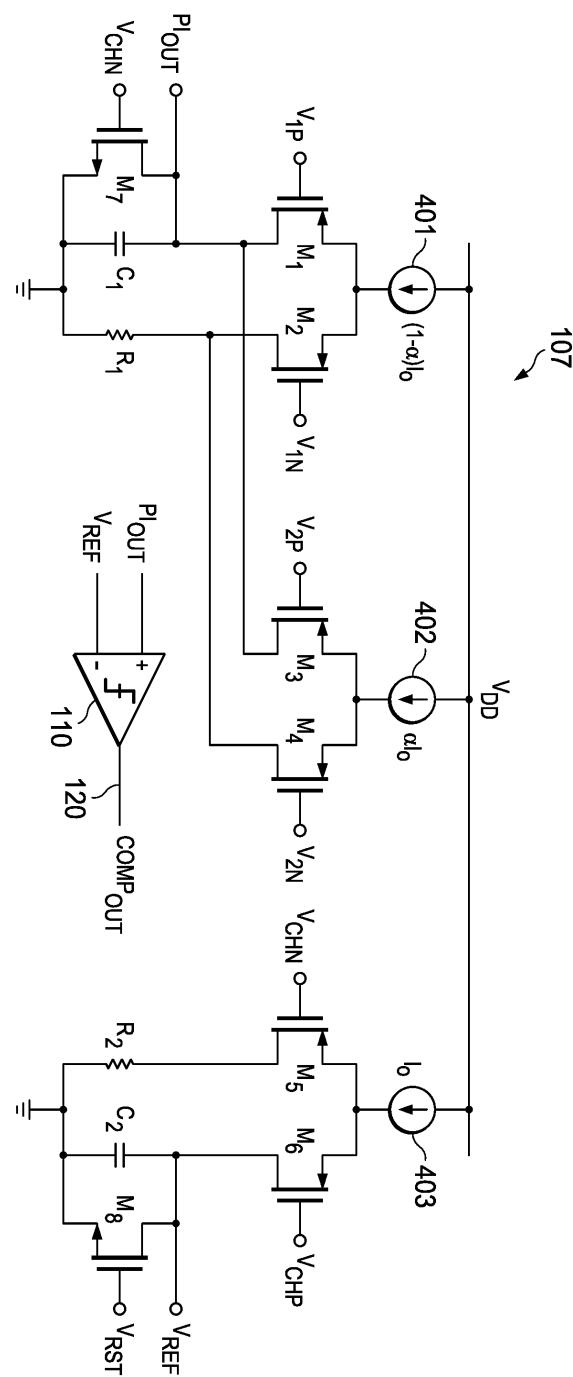

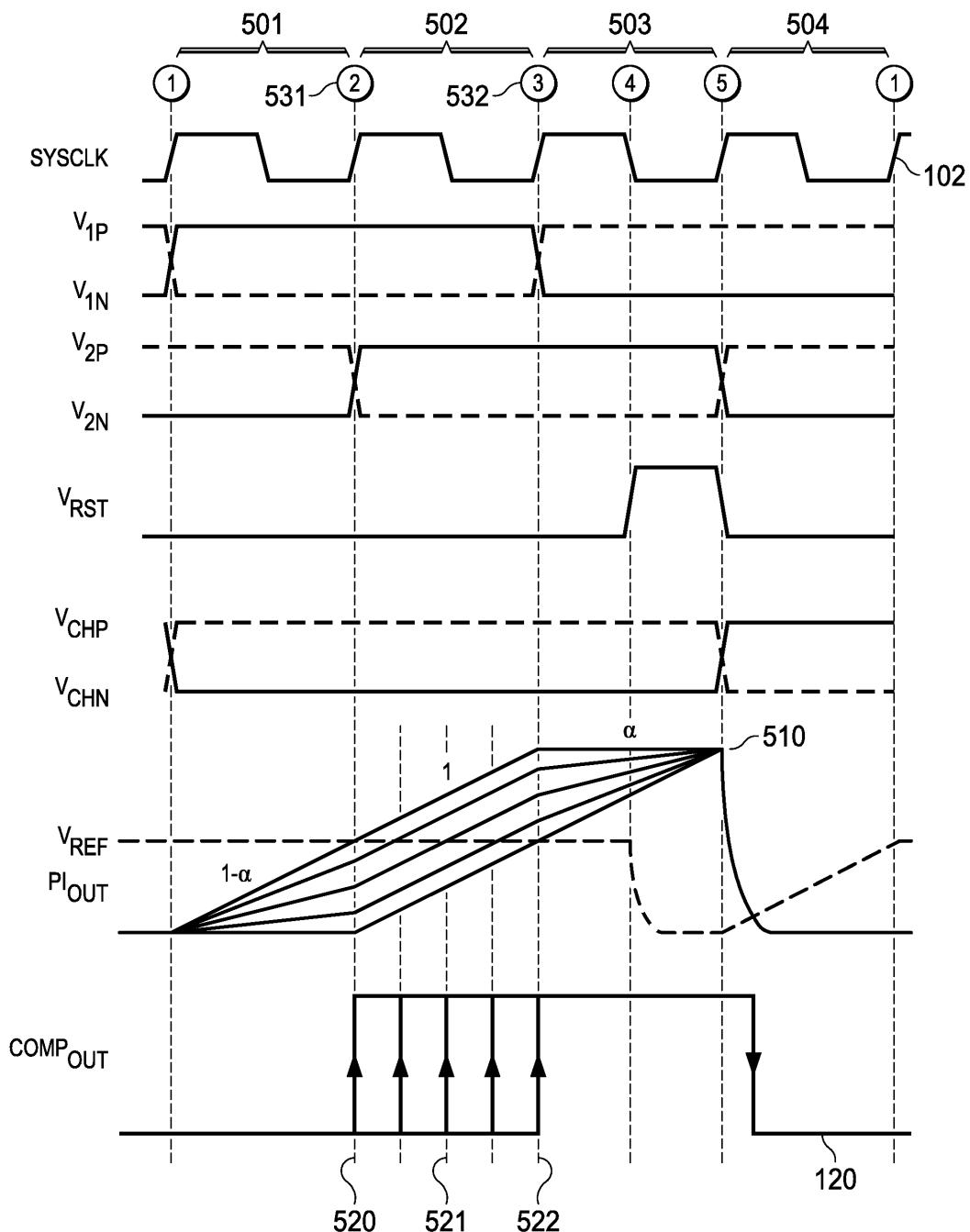

도 4 내지 도 7은 개선된 위상 보간기들의 실시예들을 예시하는 개략도들 및 타이밍 도들이다.

도 8은 비선형성에서의 추가의 개선을 예시하는 플롯이다.

도 9는 위상 보간기의 다른 실시예를 예시하는 개략도이다.

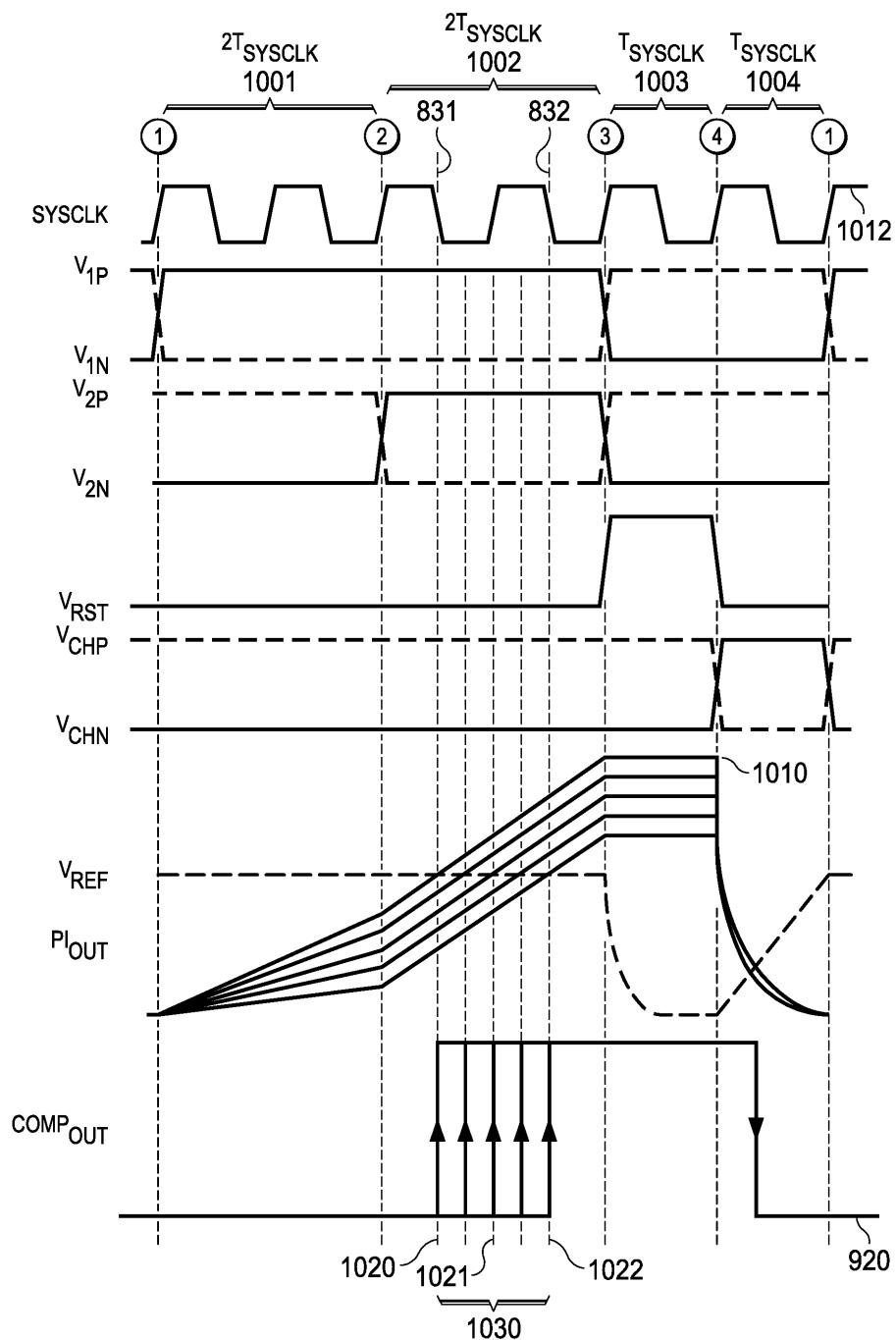

도 10은 도 9의 PI의 동작을 예시하는 타이밍 도이다.

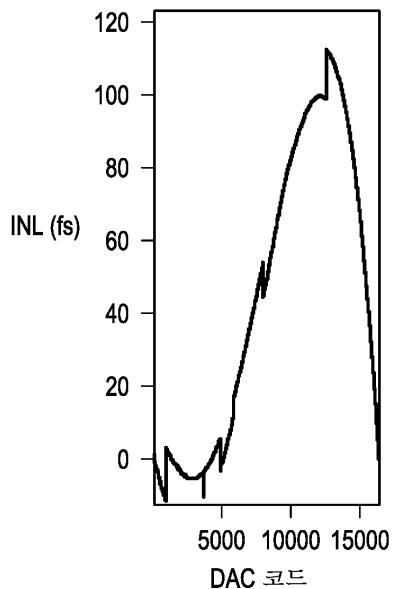

도 11은 도 9의 PI의 동작을 예시하는 플롯이다.

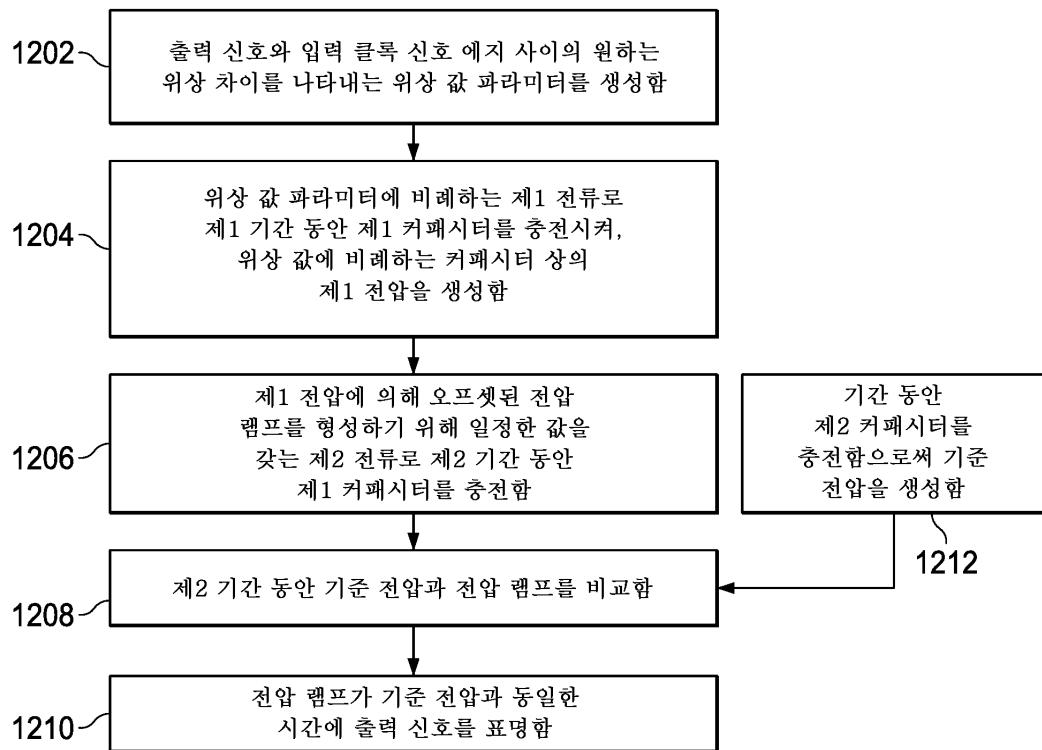

도 12는 고 선형성 위상 보간기의 동작을 예시하는 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

[0007] 도면들에서, 유사한 엘리먼트들은 일관성을 위해 유사한 참조 번호들에 의해 표시된다.

[0008] 예시적인 실시예들은 기존의 SerDes 애플리케이션보다 더 나은 선형성을 요구하는 애플리케이션들에 고 분해능, 고 선형성 위상 보간기를 제공할 수 있다. 예를 들어, 이러한 애플리케이션은 정밀 클록 발생기들을 포함할 수 있다.

[0009] 예시적인 실시예들에서, 개선된 위상 보간기가 직교 입력 신호들 및 공통 모드 피드백의 필요성을 제거한다. 요구된 입력 및 제어 신호들은 디지털 로직에 의해 쉽게 생성될 수 있다.

[0010] 하나의 실시예에서, 대략 97.6fs (펨토초)의 시간 분해능을 생성하기 위해 200ps(피코초)의 한 주기에 걸쳐 11 비트의 분해능을 가지는 위상 보간기가 제공될 수 있다. 예를 들어, 이러한 분해능은 SerDes 애플리케이션들에서 사용된 기존의 위상 보간기들의 정수 비선형성(integer nonlinearity)(INL)보다 40배 더 나을 수 있다.

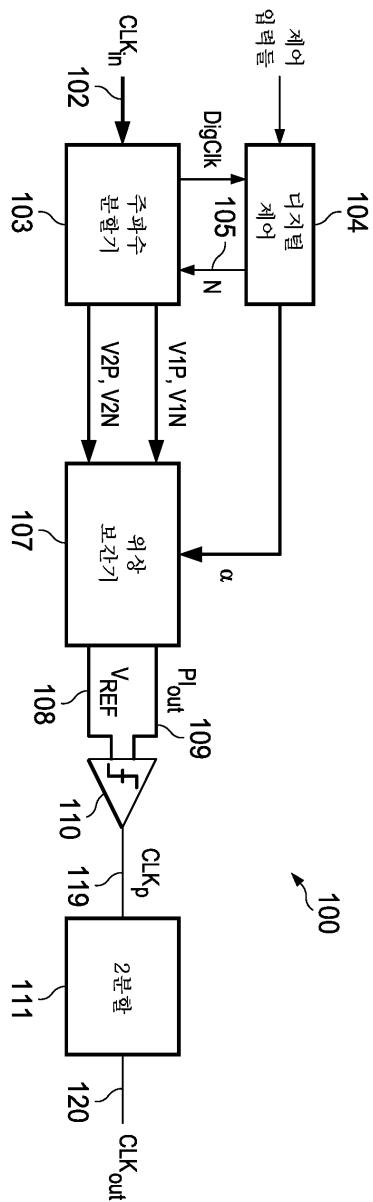

[0011] 도 1a는 고 선형성 위상 보간기(107)를 포함하는 예시적인 분수형 주파수 분할기(FFD)(100)의 블록도이다. FFD(100)는 입력 클록 신호(102)의 특정된 분수와 동일한 주파수를 갖는 출력 클록 신호(120)를 생성하도록 동작 가능하다. 입력 클록 신호(102)는 이 예시적인 실시예에서 10MHz 내지 10GHz 사이의 범위에 있는 값을 가지도록 선택될 수 있다. 다른 실시예들에서, 상이한 범위의 입력 클록 주파수들이 지원될 수 있다. 출력 클록 신호(120)는 이 예에서 대략 100 Hz 내지 1 GHz의 범위로부터 선택될 수 있는 주파수로 생성될 수 있다.

[0012] 디지털 제어 회로부(104)는 출력 클록 신호(120)와 입력 클록 신호(102) 사이에서 특정 분할 비율을 선택하기 위해 하드웨어 방식 또는 프로그램가능 방식 중 어느 하나로 구성될 수 있다. 예를 들어, 제어 회로부

(104)는 FFD(100)에 커플링되는 프로세서 상에서 실행되는 소프트웨어 또는 펌웨어에 의해 로딩되는 레지스터들을 포함할 수 있다.

[0013] FFD(100)는 출력 클록 신호(120)의 원하는 근사 주기인 입력 클록(102)의 클록 주기들의 특정된 수를 카운팅한 다음, 클록 신호(102)의 에지들 사이의 시간량을 보간하여 출력 클록 신호(120)의 에지들 사이의 정확한 기간 길이를 생성함으로써 동작한다. FFD(100)의 동작은 본 명세서에서 간단히 설명되며; FFD(100)와 같은 FFD의 동작의 상세한 설명은 "Fractional Frequency Clock Divider with Direct Division"이라는 명칭으로 Hoshyar 등이 2016년 9월 30일자로 출원한 특허 출원 US 15/281,617호에서 제공되며, 이 문헌은 본 명세서에 참조로 포함된다.

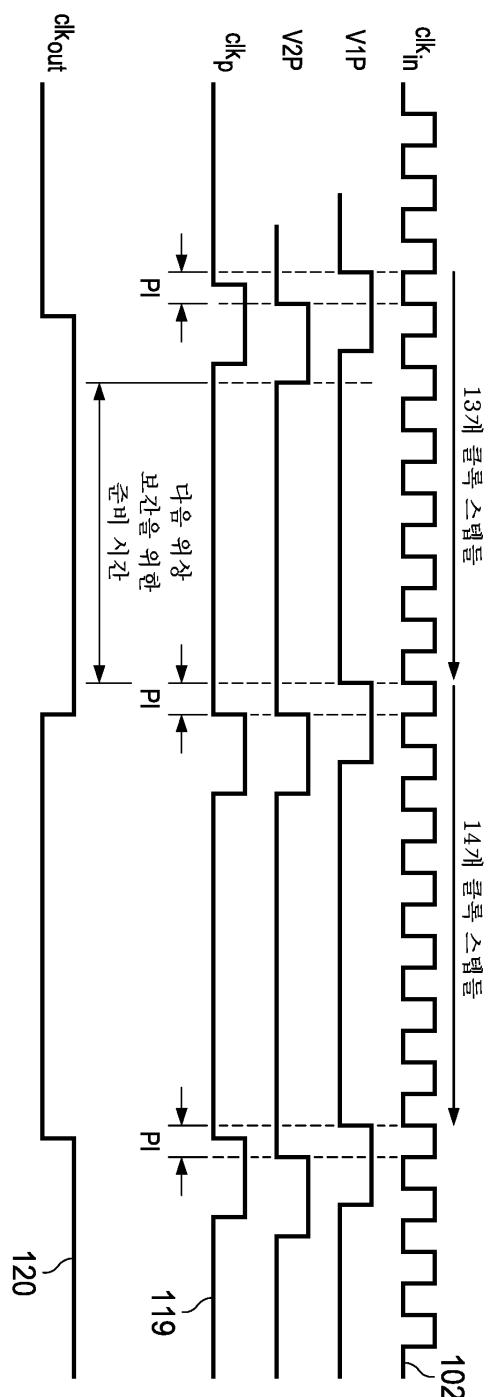

[0014] 도 1b는 13.75의 예시적인 분할 비율에 대한 FFD(100)의 동작을 예시하는 타이밍 도이다. 주파수 분할기(103)는 디지털 제어 로직(104)에 의해 제공되는 제어 파라미터(N)(105)에 응답하여 입력 클록 신호(102)의 에지들의 수(N)를 카운트하고 "N번째 클록" 신호들(V1P, V2P)을 생성하도록 구성된다. 이 실시예에서, 주파수 분할기는 입력 클록 신호(102)의 상승 및 하강 에지들 모두를 카운트한다. 위상 보간기(107)는 위상 파라미터( $\alpha$ )에 의해 특정된 바와 같은 입력 클록(102)의 두 개의 에지들 사이를 보간하도록 구성된다. 예를 들어, 13.75의 분할 비율이 특정되면, 제어 로직(104)은 입력 클록(102)의 13 개 에지들( $N = 13$ )을 카운트할 것을 카운터(103)에 지시한 다음, 중간 클록 신호 CLKp(119)를 표명하기 전에 입력 클록(102)의 한 주기의 0.75( $\alpha = 0.75$ )를 보간할 것을 PI(107)에 지시할 수 있다. 다음의 출력 기간에, 제어 로직은 그러면 13 개의 입력 주기들을 카운트할 것을 카운터(103)에 지시한 다음, 입력 클록(102)의 한 주기의 절반을 보간할 것을 PI(107)에 지시할 수 있다. 중간 클록 신호(119)는 그러면 50% 뉴티 사이클을 갖는 그리고 입력 클록(102)의 13.75 주기들로 된 한 주기를 갖는 출력 클록 신호(120)를 형성하기 위해 111에 의해 주파수에서 2로 나누어질 수 있다. 이 공정은 그 다음에 출력 클록 신호(120)의 각각의 주기 동안 반복된다. 일반적으로, 각각의 주기는 상이한 위상 보간량을 요구할 것인데 왜냐하면 분수형 주파수 비율이 출력 클록 신호와 입력 클록 신호 사이의 에지 관계들이 계속해서 변화되게 하기 때문이다.

[0015] 이 예에서, 파라미터( $\alpha$ )는 11-비트 디지털 값(0~2047)이다. 다른 예에서,  $\alpha$ 는 11 비트보다 더 높거나 또는 더 낮은 분해능을 가질 수 있다. 위상 보간기(107)는 파라미터( $\alpha$ )에 의해 표시되는 요청된 위상 변이량에 상관되는 전압(PIout)(109)을 생성한다. PIout(109)은 비교기(110)에 의해 기준 전압(Vref)(108)과 비교될 수 있다. 이하에서 더 상세히 설명될 바와 같이, PIout이 Vref와 동일할 때 출력 클록 신호(120) 상의 전이가 비교기(110)에 의해 생성된다.

[0016] 도 2는 하나 이상의 분수형 주파수 분할기들(100(1) 내지 100(n))을 포함하는 예시적인 클록 발생기 시스템(200)의 블록도이다. 예를 들어, 시스템(200)은 공지되거나 또는 나중에 개발되는 반도체 가공 기법들을 사용하여 단일 집적 회로(IC) 상에 제작될 수 있다. 또한, 예를 들어, 위상 잠금 루프(PLL) 회로(210)가 크리스탈(214) 제어식 발진기(212)의 제어 하에 고정된 주파수 기준 클록 신호(202)를 생성하는데 사용될 수 있다. 일부 예들에서, 크리스탈(214)은 IC(200) 외부에 위치될 수 있다. 다른 실시예들에서, MEMs 공진기를 갖는 발진기, 다중진동기, 링 발진기, 지연선 발진기 등과 같이, 다른 유형들의 공지되거나 또는 나중에 개발되는 클록 생성 회로들이 사용될 수 있다. 다른 예에서, 기준 클록(202)은 온-칩 소스로부터 대신에 외부 소스로부터 제공될 수 있다.

[0017] 이러한 방식으로, 단일 IC가 단일 기준 클록 신호로부터 모두가 합성되는 상이한 주파수들의 다수의 클록 신호들을 제공할 수 있다.

[0018] 이하에서 더 상세히 설명되는 바와 같이, 위상 보간기(107)는, 도 1을 다시 참조하여, 고도로 선형인 방식으로 값들의 범위 전체에 걸쳐 파라미터( $\alpha$ )에 응답하여 위상 변이를 생성한다. 이 설명에서, "비선형성"은 아날로그 디지털 변환기들(ADC)를 위해 흔히 사용되는 것과 유사한 방식으로 설명될 수 있다. ADC의 비선형성을 표준 방식으로 표현하기 위해, 제조자들은 최적합 라인(best fit line)이라 불리는 ADC 전달 함수를 통과하는 선을 그릴 수 있다. 이 선으로부터의 최대 편차는 전체 스케일의 백분율로 또는 LSB들(최소 유효 비트)로 표현될 수 있는 "통합 비선형성(integral nonlinearity)(INL)"이라 불린다. INL은 각각의 스텝의 중앙부터 선 상의 해당 점까지 측정되며, 스텝의 중앙은 ADC가 이상적이었다면 그러한 중앙이 될 것이다. "차분"은 ADC가 두 개의 연속적인 값들 사이에서 취하는 값을 말한다. 변경 입력 신호에 응답하여, ADC는 신호들을 샘플링하고 ADC의 출력은 이진수들의 스트림이 된다. 이상적인 ADC는 임의의 레벨을 스kip하는 일 없이 그리고 둘 또는 세 개의 LSB들을 넘어서 동일한 삽진수를 보유하는 일 없이 하나의 최소 유효 비트(LSB)를 올리거나 또는 내릴 것이다. 차분 비선형성(differential nonlinearity)(DNL)이 전체 전달 함수에 대해, 두 개의 연속 레벨들 사이의 하나의

LSB로부터의 최대 편차로서 정의된다.

[0019] 도 3은 기준의 위상 보간기(PI)(300)의 개략도이다. 위상 보간기들의 일반적인 동작은, 이를테면 "Phase Interpolator with Improved Linearity," Soulis et al, May 2015에서 설명된 바와 같이, 알려져 있다. 기준의 PI들은 충전 전류를 커패시터(304)에 제공하는 합산 회로들의 동작을 제어하기 위해 직교 제어 신호들 (I, Iz, Q, 및 Qz)을 요구할 수 있다. 이것과 같은 일부 구현 예들은, 공통 모드 피드백(common mode feedback)(CMFB)을 또한 요구한다. 그러나, 충전 전류의 부분이 디바이스들(302, 303)에서 없어짐으로써, 비선형성을 생성할 수 있다. PI(300)와 같은 간단한 PI 회로들이, 하나의 LSB가 100 fs일 때 6000 fs보다 더 클 수 있는 60 LSB 이상의 INL 에러를 가질 수 있다.

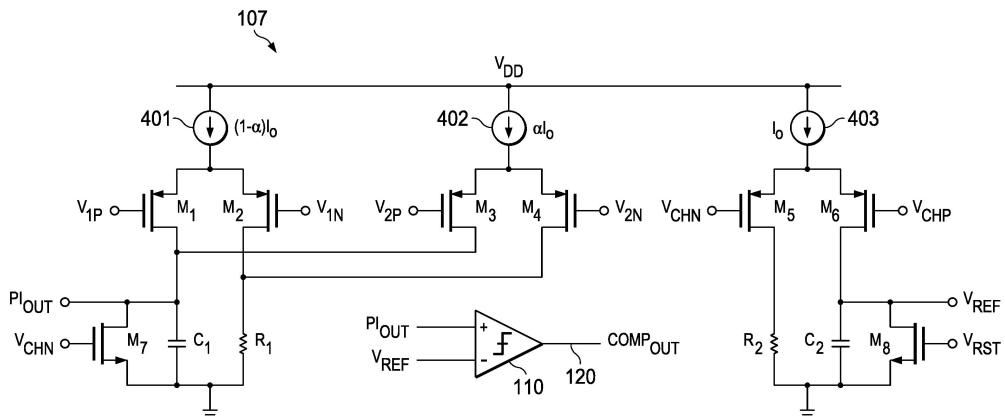

[0020] 도 4는 도 1을 다시 참조하여 PI(107)에 사용될 수 있는 개선된 위상 보간기(400)를 더 상세히 예시하는 개략도이다. 도 5는 PI(400)의 동작을 예시하는 타이밍 도이다. 이상에서 설명된 바와 같이, 파라미터( $\alpha$ )가 제어 회로부, 이를테면 도 1의 제어 회로부(104)에 의해 제공될 수 있다. 파라미터( $\alpha$ )는, 이를테면 명령들의 실행에 의해, 다른 제어 로직에 의해, 초기화 회로부에 의해, 하드웨어드 제어 로직에 의해 등으로, 제어 로직(104) 내의 또는 그 제어 로직에 커플링된 레지스터 안으로 로딩될 수 있다. 이 예에서, 파라미터( $\alpha$ )는 입력 클록 신호(102)에 대해 출력 클록 신호(120)의 위상을 시프트시키기 위한 기간의 백분율을 나타내는 0.0 내지 1.0의 범위의 값을 갖는 분수 값이다.

[0021] 각각의 보간 사이클 동안, 제1 전류원(401)이  $(1 - \alpha)$ 에 비례하는 전류를 생성하도록 구성되고 제2 전류원(402)이  $(\alpha)$ 에 비례하는 전류를 생성하도록 구성된다. 예를 들어, 전류원들(401, 402)은 디지털-아날로그 변환기들(DAC)을 사용하여 구현될 수 있다. 이 예에서, 열두 비트의 분해능을 갖는 DAC들이 사용될 수 있으며; 다른 실시예들이 더 높거나 또는 더 낮은 분해능을 갖는 DAC들을 사용할 수 있다. 그 전류원들은 제어 회로부, 이를테면 도 1을 다시 참조하여 제어 회로부(104)에 의해 제어될 수 있다.

[0022] 제1 기간(501) 동안, 전류원(401)으로부터의 전류는 MOS 디바이스(M1)를 통해 램프 커패시터(C1)에 제공되는 한편 전류원(402)으로부터의 전류는 MOS 디바이스(M4)를 통해 저항기(R1)에 의해 소비된다. 전류원(401)으로부터의 전류는 램프 커패시터(C1)를 충전시키고 제1 기간(501) 동안  $(1 - \alpha)$ 에 비례하는 기울기로 램프 업하는 전압(PIout)을 생성하여 요청된 위상 변이에 비례하는 PIout 전압을 시간 531에 생성시킨다.

[0023] 제2 기간(502) 동안, 전류원(402)으로부터의  $(\alpha)$ 에 비례하는 전류는 MOS 디바이스(M3)를 통해 램프 커패시터(C1)에 또한 제공되어서, 기간(502) 동안 커패시터(C1)에 제공된 총 전류는  $(\alpha) + (1 - \alpha) = 1$ 에 비례한다. 따라서, 기간(502) 동안 파라미터( $\alpha$ )와는 독립적인 일정한 충전 레이트가 생성된다. 따라서, 전압(PIout)은 기간(502) 동안 파라미터( $\alpha$ )와는 독립적인 기울기로 램프 업되고 시간 531에 PIout 전압만큼 오프셋된다. 이런 방식으로, 제1 스텝이 시간 531의 요청된 위상 변이에 비례하는 전압 크기를 생성하고 제2 스텝이 요청된 위상 변이를 갖는 출력 신호가 시간 531에서의 전압 크기에 기초하여 생성되는 것을 허용하는 두 스텝 전압 램프 신호가 생성된다.

[0024] 제3 기간(503) 동안, 전류원(401)으로부터의 전류는 램프 커패시터(C1)가 기간(503) 동안  $(\alpha)$ 에 비례하는 레이트로 충전하도록 MOS 디바이스(M2)에 의해 저항기(R1)로 향하게 될 수 있다. 이런 방식으로, 램프 커패시터(C1)는 파라미터( $\alpha$ )의 값에 상관없이 보간 사이클의 각각의 반복 동안 510으로 표시된 바와 동일한 완전 충전 전압 레벨로 충전된다.

[0025] 완전 충전 전압(510)의  $\frac{1}{2}$ 의 값을 가지는 기준 전압(Vref)이 제공될 수 있으며, 이 전압은 531에서의 최대 전압에 해당한다. 제2 기간(502) 동안 PIout과 Vref를 비교함으로써, 파라미터( $\alpha$ )에 대하여 극도로 선형인 입력 클록(102)에 관한 위상 변이를 갖는 클록 신호(120)가 생성될 수 있다. 예를 들어,  $\alpha = 0$ 일 때, 클록 신호(120)가 시간 520에 표명되는데, 이는 입력 클록 신호(102)에 비하여 0 도의 위상 변이를 가진다.  $\alpha = 0.5$ 일 때, 클록 신호(120)가 시간 521에 표명되는데, 이는 입력 클록 신호(102)에 비하여 180 도의 위상 변이를 가진다. 마찬가지로,  $\alpha = 1.0$ 일 때, 클록 신호(120)가 시간 522에 표명되는데, 이는 입력 클록 신호(102)에 비하여 360 도의 위상 변이를 가진다. 따라서, 0 도와 360 도 사이의 임의의 위상 변이량이 파라미터( $\alpha$ )의 대응하는 선택에 의해 생성될 수 있다.

[0026] 기간(504) 동안, 램프 커패시터(C1)가 MOS 디바이스(M7)에 의해 방전될 수 있다.

[0027] 이 예에서, 기준 전압(Vref)은 기간(504) 동안 커패시터(C2)를 충전하도록 구성되는 제3 전류원(403)에 의해 생성된다. 커패시터(C2)는 기간(503)의 후반 동안 리셋될 수 있다. 이런 방식으로, 기준 전압(Vref)은 공정 변동(process variation)에 의해 야기되는 부정합들이 제거되도록 PI 회로(400)의 나머지와 동일한 조건들 하에서

생성된다.

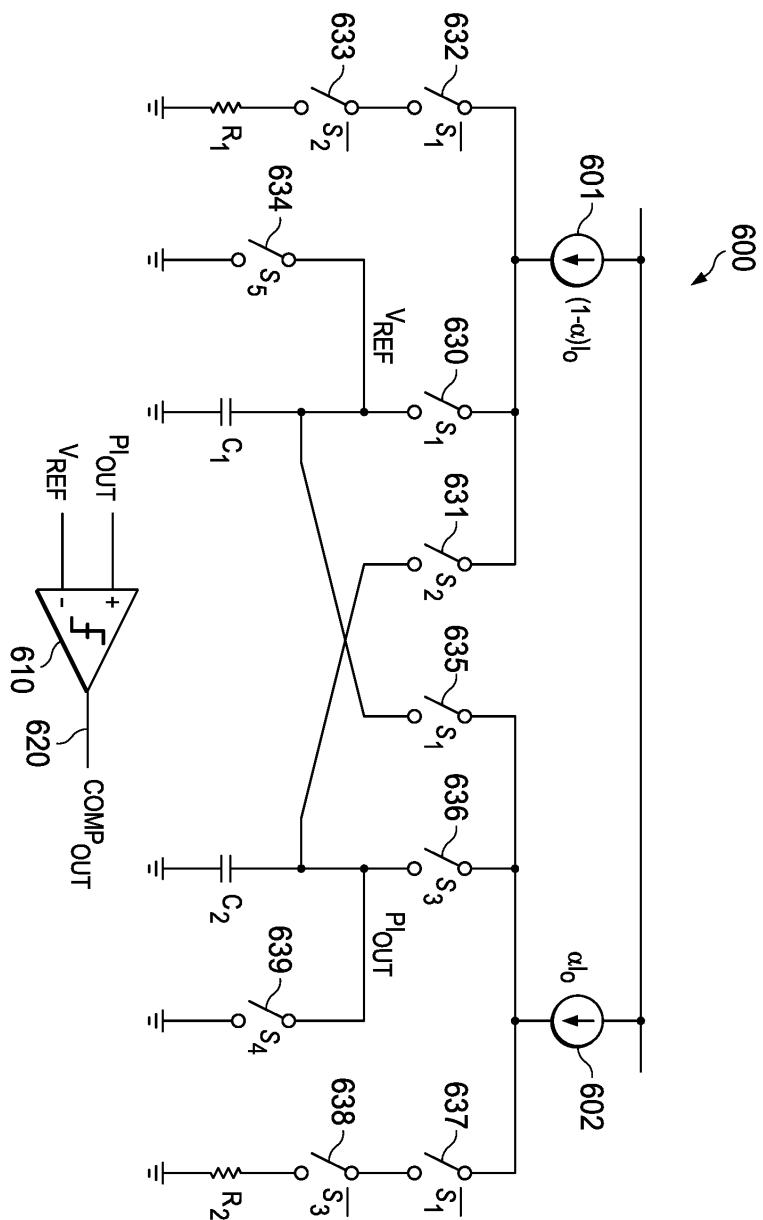

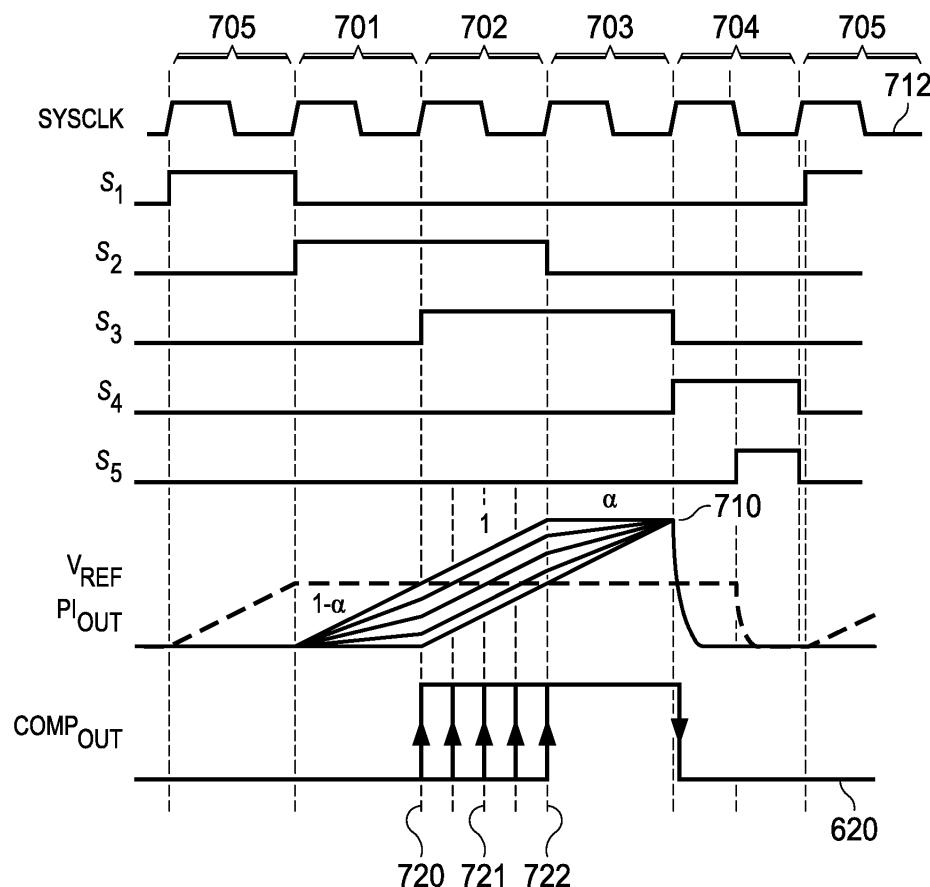

[0028] 도 6은 도 1을 다시 참조하여 PI(107)로서 사용될 수 있는 개선된 위상 보간기(600)의 다른 구현예를 예시하는 개략도이다. 도 7은 PI(600)의 동작을 예시하는 타이밍 도이다. PI(600)는 도 7에서 타이밍 신호들(S1~S5)에 의해 표시된 바와 같이 제어되는 한 세트의 스위치 디바이스들(630~639)로 구현될 수 있다. PI(600)의 동작은 도 4 및 도 5에 관해 설명된 바와 같은 PI(400)의 동작과 유사하다. 스위치들(630~639)이 공지되거나 또는 나중에 개발되는 디바이스들, 이를테면 바이폴라 반도체 디바이스들, 전계 효과 디바이스들 등을 사용하여 구현될 수 있다.

[0029] 각각의 보간 사이클 동안, 제1 전류원(601)이  $(1 - \alpha)$ 에 비례하는 전류를 생성하도록 구성되고 제2 전류원(602)이  $(\alpha)$ 에 비례하는 전류를 생성하도록 구성된다. 제1 기간(701) 동안, 전류원(601)으로부터의 전류는 스위치 디바이스(631)를 통해 램프 커패시터(C2)에 제공되는 한편 전류원(602)으로부터의 전류는 스위치 디바이스들(637 및 638)을 통해 저항기(R2)에 의해 소비된다. 전류원(601)으로부터의 전류는 램프 커패시터(C2)를 충전시키고 제1 기간(701) 동안  $(1 - \alpha)$ 에 비례하는 기울기로 램프 업하는 전압(PIout)을 생성하여 요청된 위상 변이에 비례하는 PIout 전압을 기간(701)의 끝에서 생성시킨다.

[0030] 제2 기간(702) 동안, 전류원(602)으로부터의  $(\alpha)$ 에 비례하는 전류는 스위치 디바이스(636)를 통해 램프 커패시터(C2)에 또한 제공되어서, 기간(702) 동안 커패시터(C2)에 제공된 총 전류는  $(\alpha) + (1 - \alpha) = 1$ 에 비례한다. 따라서, 기간(702) 동안 파라미터( $\alpha$ )와는 독립적인 일정한 충전 레이트가 생성된다. 따라서, 전압(PIout)은 기간(702) 동안 파라미터( $\alpha$ )와는 독립적인 기울기로 램프 업된다.

[0031] 제3 기간(703) 동안, 전류원(601)으로부터의 전류는 커패시터(C2)가 기간(703) 동안  $(\alpha)$ 에 비례하는 레이트로 충전하도록 스위치 디바이스들(632 및 633)에 의해 저항기(R1)로 향하게 될 수 있다. 이런 방식으로, 램프 커패시터(C2)는 파라미터( $\alpha$ )의 값에 상관없이 보간 사이클의 각각의 반복 동안 710으로 표시된 바와 동일한 완전 충전 전압 레벨로 충전된다.

[0032] 완전 충전 전압(710)의  $\frac{1}{2}$ 의 값을 가지는 기준 전압(Vref)이 제공될 수 있다. 제2 기간(702) 동안 PIout과 Vref를 비교함으로써, 파라미터( $\alpha$ )에 대하여 극도로 선형인 입력 클록(712)에 관한 위상 변이를 갖는 클록 신호(620)가 생성될 수 있다. 예를 들어,  $\alpha = 0$ 일 때, 클록 신호(620)가 시간 720에 표명되는데, 이는 입력 클록 신호(712)에 비하여 0 도의 위상 변이를 가진다.  $\alpha = 0.5$ 일 때, 클록 신호(620)가 시간 721에 표명되는데, 이는 입력 클록 신호(712)에 비하여 180 도의 위상 변이를 가진다. 마찬가지로,  $\alpha = 1.0$ 일 때, 클록 신호(620)가 시간 722에 표명되는데, 이는 입력 클록 신호(712)에 비하여 360 도의 위상 변이를 가진다. 따라서, 0 도와 360 도 사이의 임의의 위상 변이량이 파라미터( $\alpha$ )의 대응하는 선택에 의해 생성될 수 있다.

[0033] 기간(704) 동안, 커패시터(C2)는 스위치 디바이스(639)에 의해 방전된다.

[0034] 이 예에서, 기준 전압(Vref)은 스위치들(630 및 635)을 통해 기간(705) 동안 커패시터(C1)를 충전하도록 구성되는 전류원들(601 및 602) 둘 다에 의해 생성된다. 커패시터(C1)는 이 예에서 스위치(634)에 의해 기간(704)의 후반 동안 리셋된다. 다른 예에서, 커패시터(C1)는 기간(703)의 후반 동안 리셋되고 기간(704) 동안 충전될 수 있다. 이런 방식으로, 기준 전압(Vref)은 PI 회로(600)의 나머지와 동일한 조건들 하에서 생성되어서, 공정 변동에 의해 야기되는 부정합들이 제거된다.

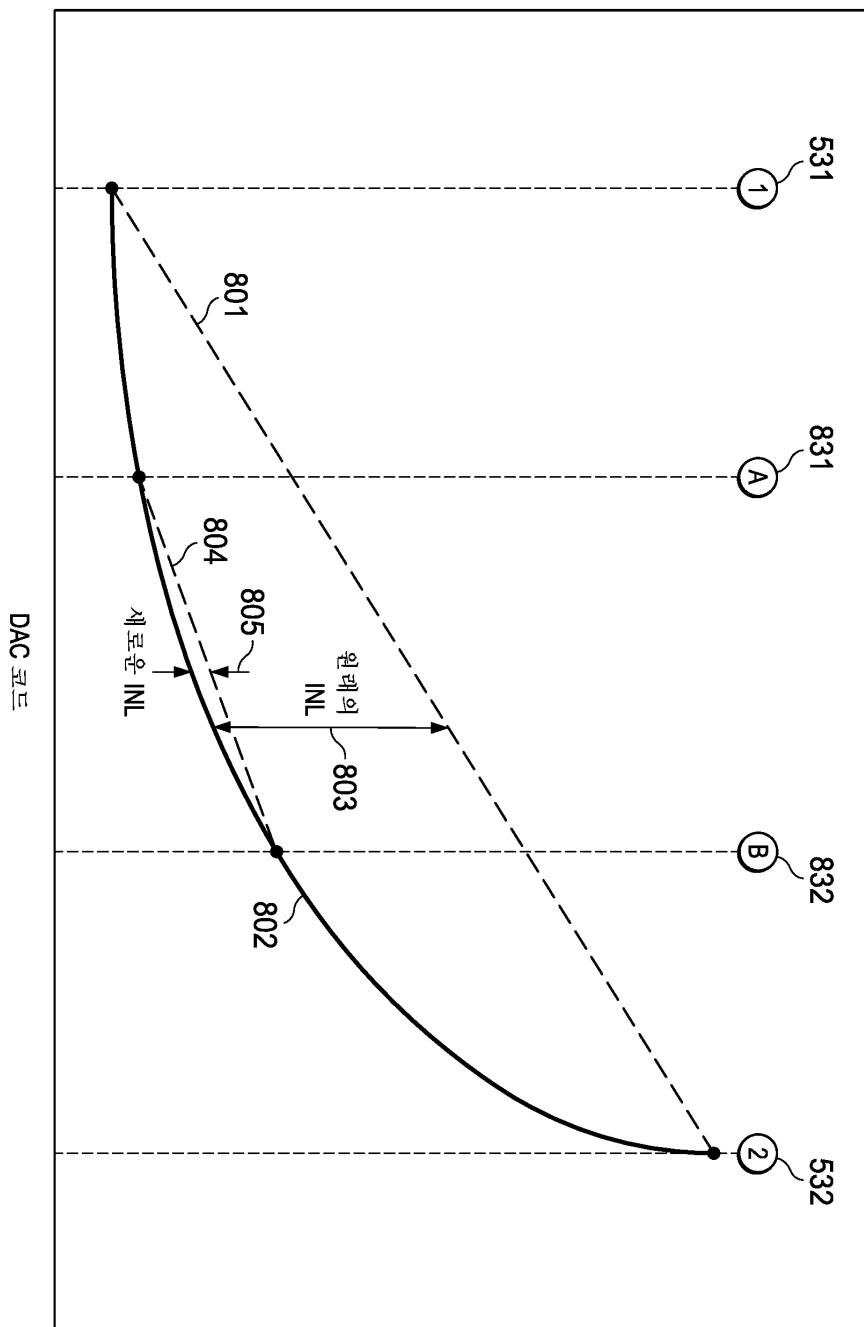

[0035] 도 8은 도 4의 PI 회로(107) 및 도 6의 PI 회로(600)에서 발생할 수 있는 비선형성을 예시하는 플롯이다. 타이밍도인 도 5를 다시 참조하면, 타이밍 포인트들(531 및 532)에서의 신호 스위칭에 의해 야기되는 글리치 간섭은 각각 자신의 최소 또는 최대에 가까운 값을 파라미터( $\alpha$ )가 가질 때 비선형 예러들을 야기할 수 있다. 플롯 라인(801)은 타이밍 포인트들(531 및 532) 사이의 이상적인 선형 응답 곡선을 나타낸다. 플롯 라인(802)은 타이밍 포인트들(531 및 532) 주위의 신호 글리치들로 인한 가능한 응답 곡선을 나타낸다. 803에 표시된 INL 크기가 초래될 수 있다. 예시적인 실시예들은 위상 보간기가 더 많은 선형 영역, 이를테면 타이밍 포인트들(831 및 832) 사이의 영역에서 동작되는 것을 허용한다. 이 경우, 이 영역에서의 이상적인 선형 응답(804)이, 805에 표시된 바와 같이, 훨씬 더 낮은 INL 크기를 초래할 것이다.

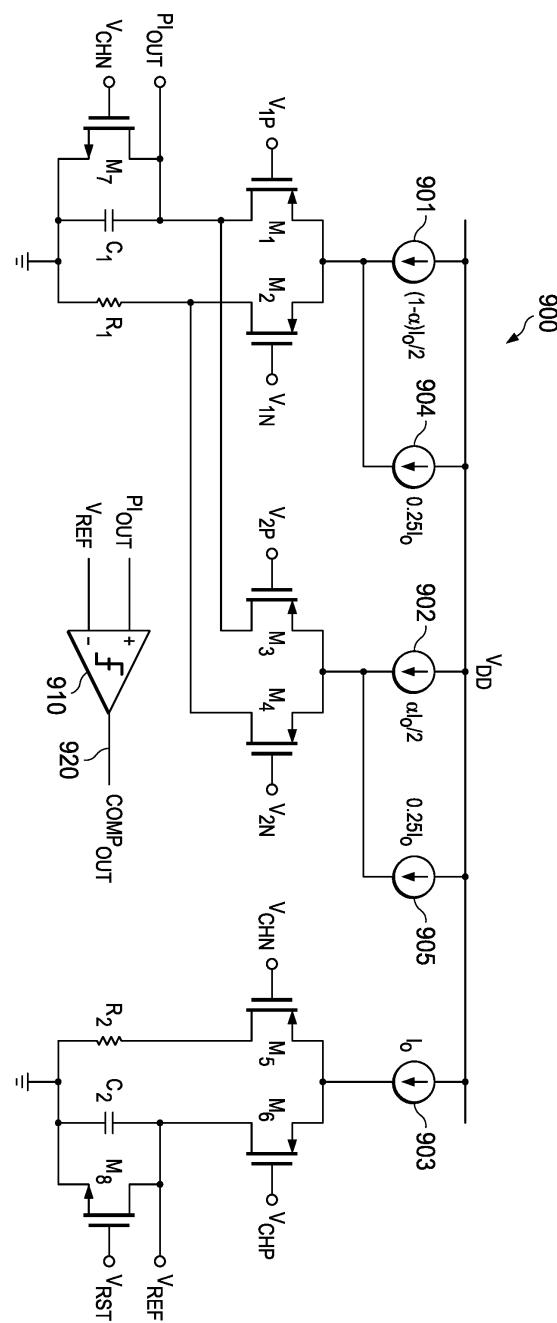

[0036] 도 9는 도 1을 다시 참조하여 PI(107)로서 사용될 수 있는 위상 보간기(900)의 다른 실시예를 예시하는 개략도이다. 도 10은 PI(900)의 동작을 예시하는 타이밍 도이다. PI(900)는, 도 4를 다시 참조하여, 그것이  $(1 - \alpha)$ 에 비례하는 전류를 생성하도록 구성되는 제1 전류원(901)을 가지고 제2 전류원(902)이  $(\alpha)$ 에 비례하는 전류를 생성하도록 구성된다는 점에서 PI(400)와 유사하다. 그러나, 전류원(901 및 902) 각각은 0.5 I(0)의 값을 갖는 기준 전류를 사용한다. 더 낮은 전류 값을 보상하기 위해, 제1 기간(1001) 및 제2 기간(1002)은 입력 클록

(1012)의 두 개의 기간들에 걸쳐 있다.

[0037] 제2 세트의 전류원들(904, 905)이 커패시터(C1)를 추가적인 일정량만큼 충전시킴으로써 생성되는 PIout의 전압 램프를 시프트시키는 "페데스탈 전류"를 제공하기 위해 포함된다. 이 실시예에서, 전류원들(904, 905)은 0.25 I(0)의 정전류를 제공한다.

[0038] 제1 기간(1001) 동안, 전류원(901 및 904)으로부터의 전류는 MOS 디바이스(M1)를 통해 램프 커패시터(C1)에 제공되는 한편 전류원(902 및 905)으로부터의 전류는 MOS 디바이스(M4)를 통해 저항기(R1)에 의해 소비된다. 전류원(901, 904)으로부터의 전류는 램프 커패시터(C1)를 충전시키고 입력 클록(1012)의 두 주기들인 제1 기간(1001) 동안  $(1 - \alpha)$ 에 비례하는 기울기로 램프 업하는 전압(PIout)을 생성하여, 요청된 위상 변이에 비례하는 PIout 전압을 시간 1031에 생성시킨다.

[0039] 제2 기간(1002) 동안, 전류원(902)으로부터의  $(\alpha)$ 에 비례하는 전류와 전류원(905)으로부터의 고정된 전류는 MOS 디바이스(M3)를 통해 램프 커패시터(C1)에 또한 제공되어서, 기간(1002) 동안 램프 커패시터(C1)에 제공되는 총 전류는  $(\alpha) + (1 - \alpha) = 1$ 에 비례한다. 따라서, 기간(1002) 동안 파라미터( $\alpha$ )와는 독립적인 일정한 충전 레이트가 생성된다. 따라서, 전압(PIout)은 기간(1002) 동안 파라미터( $\alpha$ )와는 독립적인 기울기로 램프 업된다.

[0040] 완전 충전 전압(1010)의 대략 0.5의 값을 가지는 기준 전압(Vref)이 제공될 수 있다. 제2 기간(1002)의 단지 중앙 부분인 샘플링 기간(1030) 동안에만 PIout과 Vref를 비교함으로써, 파라미터( $\alpha$ )에 대하여 극도로 선형인 입력 클록(1012)의 하강 에지에 관한 위상 변이를 갖는 클록 신호(920)가 생성될 수 있다. 예를 들어,  $\alpha = 0$  일 때, 클록 신호(920)가 시간 1020에 표명되는데, 이는 입력 클록 신호(1012)의 하강 에지에 비하여 0 도의 위상 변이를 가진다.  $\alpha = 0.5$  일 때, 클록 신호(1020)가 시간 1021에 표명되는데, 이는 입력 클록 신호(1012)의 하강 에지에 비하여 180 도의 위상 변이를 가진다. 마찬가지로,  $\alpha = 1.0$  일 때, 클록 신호(920)가 시간 1022에 표명되는데, 이는 입력 클록 신호(102)의 하강 에지에 비하여 360 도의 위상 변이를 가진다. 따라서, 0 도와 360 도 사이의 임의의 위상 변이량이 파라미터( $\alpha$ )의 대응하는 선택에 의해 생성될 수 있다. 더욱이, 감소된 샘플링 기간(1030)이 제어 신호들의 스위칭에 의해 야기될 수 있는 글리칭을 피한다.

[0041] 기간(1003) 동안, 커패시터(C1)가 MOS 디바이스(M7)에 의해 방전될 수 있다.

[0042] 이 예에서, 기준 전압(Vref)은 기간(1004) 동안 커패시터(C2)를 충전하도록 구성되는 제3 전류원(903)에 의해 생성된다. 커패시터(C2)는 MOS 디바이스(M8)에 의해 기간(1003) 동안 리셋될 수 있다. 이런 방식으로, 기준 전압(Vref)은 공정 변동에 의해 야기되는 부정합들이 제거되도록 PI 회로(900)의 나머지와 동일한 조건들 하에서 생성된다.

[0043] 도 11은 하나의 LSB가 100 fs에 대응하는 PI(900)의 시뮬레이션된 동작을 예시하는 플롯이다. 이 예에서, PI(900)는, 도 11에 예시된 바와 같이, 1.2 LSB에 대응하는 120 fs만의 최대 INL을 나타낸다. 이는 도 3에 예시된 기준의 디바이스에서의 6000 fs를 초과하는 최대 INL 애러와 비교된다.

[0044] 도 12는 도 3 내지 도 10에 관련하여 이상에서 설명된 바와 같은 고 선형성 위상 보간기의 동작을 예시하는 흐름도이다. 도 1 및 도 2에 관해 설명된 바와 같이, 고 선형성 위상 보간기가 고정된 기준 주파수로부터 정확한 분수형 주파수 클록 신호들을 생성하는데 사용될 수 있다.

[0045] 출력 신호와 입력 클록 신호 에지 사이의 원하는 위상 차이를 나타내는 위상 값 파라미터가 위상 보간기에 커플링된 제어 로직에 의해 생성될 수 있다(1202).

[0046] 제1 커패시터가 위상 값 파라미터에 비례하는 커패시터 상의 제1 전압을 생성하기 위해 위상 값 파라미터에 비례하는 제1 전류로 제1 기간 동안 충전될 수 있다(1204). 이상에서 더 상세히 설명된 바와 같이, DAC에 의해 제어되는 전류원이 제1 전류를 생성하는데 사용될 수 있다. 위상 값 파라미터는 DAC를 제어하는데 사용될 수 있다. 예를 들어, 위상 값은 12-비트 DAC에 제공되는 12-비트 디지털 값일 수 있다.

[0047] 제1 커패시터는 제1 전압에 의해 오프셋된 전압 램프를 형성하기 위해 일정한 값을 갖는 제2 전류로 제2 기간 동안 더 충전될 수 있다(1206). 이상에서 설명된 바와 같이, 제2 전류원은 제어를 위해 DAC를 사용하여 또한 구현될 수 있다.

[0048] 기준 전압이 제2 기간 동안 전압 램프와 비교될 수 있다(1208). 이상에서 설명된 바와 같이, 도 4의 비교기(110)와 같은 비교기가 이 비교를 위해 사용될 수 있다.

[0049] 출력 신호는 그러면 위상 값 파라미터에 의해 특정되는 위상량만큼 입력 클록으로부터 오프셋되는 출력 신호를 생성하기 위해 전압 램프가 기준 전압과 동일한 시간에 표명될 수 있다(1210).

[0050] 이상에서 더 상세히 설명된 바와 같이, 기준 전압이 다른 기간 동안 제2 커패시터를 충전하도록 구성되는 전류원에 의해 생성될 수 있다(1212). 제2 커패시터는 각각의 보간 사이클의 끝에 리셋될 수 있다. 이런 방식으로, 기준 전압은 공정 변동에 의해 야기되는 부정합들이 제거되도록 PI 회로의 나머지와 동일한 조건들 하에서 생성될 수 있다.

[0051] 다른 실시예들

[0052] 도 4를 다시 참조하면, 다른 예시적인 실시예에서, 전류원(401)은  $(\alpha)I_0$ 의 값을 가질 수 있고 전류원(402)은  $(1-\alpha)I_0$ 의 값을 가질 수 있다.

[0053] 다른 실시예에서, 전류원(401)은 파라미터( $\alpha$ )에 비례하는 전류 값을 가질 수 있고 전류원(402)은  $I_1$ 의 정전류 값을 가질 수 있다. 이 경우, 전류원(401)으로부터의 전류는 샘플 기간(502) 동안 고정된 기울기를 갖는 램프 전압이 전류원(402)에 의해 단독으로 생성되도록 그 기간(502) 동안 저항기(R1)를 향할 수 있다.

[0054] 다른 실시예에서, 전류원들의 다양한 조합들이 제1 기간 동안 요청된 위상 변이량에 비례하는 전압 기울기를 생성하도록 그리고 샘플링 기간 동안 고정된 기울기를 갖는 추가적인 전압 기울기를 생성하도록 구성될 수 있다.

[0055] 다양한 실시예들에서, 램프 커패시터는 개별 커패시터, MOS 디바이스, 다수의 디바이스들 등으로서 구현될 수 있다.

[0056] 다른 실시예에서, 위상 변이를 결정하기 위한 두 스텝 램프 신호가, 유도형 디바이스를 사용하여 두 스텝 램프를 갖는 전류를 생성하는 것과 같이, 다른 유형의 디바이스 특성을 사용하여 생성될 수 있다.

[0057] 분수형 주파수 클록 발생기 시스템이 본 명세서에서 설명되어 있지만, 다른 시스템들이 SerDes 인터페이스들을 위한 클록 복원, PLL들의 주파수 제어 등과 같은 기능들을 위해 본 명세서에서 개시된 고 선형성 위상 보간기를 구현할 수 있다.

[0058] 본 명세서에서, "커플"이란 용어와 그 파생어들은 간접, 직접, 광학적, 및/또는 무선 전기 접속을 의미한다. 따라서, 제1 디바이스가 제2 디바이스에 커플링되면, 그 접속은 직접 전기 접속을 통하거나, 다른 디바이스들 및 접속들을 경유하는 간접 전기 접속을 통하거나, 광학적 전기 접속을 통하거나, 그리고/또는 무선 전기 접속을 통해 될 수 있다.

[0059] 비록 방법 단계들이 도면들에서 도시되며 그리고/또는 본 명세서에서 순차적 방식으로 설명하지만, 도시되는 그리고/또는 설명되는 그 단계들 중 하나 이상은 생략, 반복, 동시에 수행, 그리고/또는 상이한 순서로 수행될 수 있다.

[0060] 변형예들이 설명된 실시예들에서 가능하고, 다른 실시예들이 청구항들의 범위 내에서 가능하다.

도면

도면 1a

도면 1b

## 도면2

### 도면3

### (종래기술)

도면4

도면5

도면6

도면7

## 도면8

DAC 특성

દોષ 9

도면10

## 도면11

## 도면12