(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3977087号

(P3977087)

(45) 発行日 平成19年9月19日(2007.9.19)

(24) 登録日 平成19年6月29日(2007.6.29)

(51) Int.C1.

F 1

|      |      |           |      |       |   |

|------|------|-----------|------|-------|---|

| HO4N | 1/41 | (2006.01) | HO4N | 1/41  | B |

| HO3M | 7/30 | (2006.01) | HO3M | 7/30  | A |

| HO3M | 7/40 | (2006.01) | HO3M | 7/40  |   |

| HO4N | 7/30 | (2006.01) | HO4N | 7/133 | Z |

請求項の数 10 (全 24 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2002-13524 (P2002-13524)    |

| (22) 出願日     | 平成14年1月22日 (2002.1.22)        |

| (65) 公開番号    | 特開2002-320091 (P2002-320091A) |

| (43) 公開日     | 平成14年10月31日 (2002.10.31)      |

| 審査請求日        | 平成17年1月24日 (2005.1.24)        |

| (31) 優先権主張番号 | 特願2001-36095 (P2001-36095)    |

| (32) 優先日     | 平成13年2月13日 (2001.2.13)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (72) 発明者  | 五十嵐 進<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

最終頁に続く

(54) 【発明の名称】画像符号化装置、方法及びプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

n 個の複数の直交変換係数を同数の量子化閾値と比較して、比較結果に基づき選択的に前記直交変換係数を量子化して符号化する画像符号化装置であって、

前記直交変換係数を、第1のスキャン順序に並べ替えて、n 個ずつ出力する第1のスキャン変換手段と、

前記第1のスキャン変換手段が出力する n 個ずつの前記直交変換係数を、n 個の量子化閾値と比較して、該比較結果に基づき選択的に前記直交変換係数を量子化して出力する量子化手段と、

前記量子化手段が出力する量子化された直交変換係数を、ジグザグスキャン順序に並べ替えて出力する第2のスキャン変換手段と、

前記第2のスキャン変換手段が出力する前記量子化された直交変換係数を符号化する符号化手段と、

を含み、

前記第1のスキャン順序は、前記量子化手段における前記比較結果が有意となる前記直交変換係数が前記 n 個ずつの出力単位に分散されるようなスキャン順序であることを特徴とする画像符号化装置。

## 【請求項 2】

前記第1のスキャン順序が、偶数番目のサンプルはジグザグスキャン順序の先頭から順方向に、奇数番目のサンプルはジグザグスキャン順序の末尾から逆方向順にそれぞれ配列

させた順序であることを特徴とする、請求項 1 に記載の画像符号化装置。

【請求項 3】

前記第 1 のスキャン順序が、奇数番目のサンプルはジグザグスキャン順序の先頭から順方向に、偶数番目のサンプルはジグザグスキャン順序の末尾から逆方向順にそれぞれ配列させた順序であることを特徴とする、請求項 1 記載の画像符号化装置。

【請求項 4】

前記第 1 のスキャン順序が、偶数番目のサンプルはラスタスキャン順序の先頭から順方向に、奇数番目のサンプルはラスタスキャン順序の末行から順方向順にそれぞれ配列させた順序であることを特徴とする、請求項 1 記載の画像符号化装置。

【請求項 5】

前記第 1 のスキャン順序が、奇数番目のサンプルはラスタスキャン順序の先頭から順方向に、偶数番目のサンプルはラスタスキャン順序の末行から順方向順にそれぞれ配列させた順序であることを特徴とする、請求項 1 記載の画像符号化装置。

【請求項 6】

前記第 1 のスキャン順序が、偶数番目のサンプルはラスタスキャン縦方向順序の先頭から順方向に、奇数番目のサンプルはラスタスキャン縦方向順序の末列から順方向順にそれぞれ配列させた順序であることを特徴とする、請求項 1 記載の画像符号化装置。

【請求項 7】

前記第 1 のスキャン順序が、奇数番目のサンプルはラスタスキャン縦方向順序の先頭から順方向に、偶数番目のサンプルはラスタスキャン縦方向順序の末列から順方向順にそれぞれ配列させた順序であることを特徴とする、請求項 1 記載の画像符号化装置。

【請求項 8】

前記第 1 のスキャン変換手段が、複数のスキャン順序を有し、前記直交変換手段の直交変換処理結果に応じて適応的に前記複数のスキャン順序よりただ一つを選択してスキャン変換を行なうことを特徴とする、請求項 1 記載の画像符号化装置。

【請求項 9】

$n$  個の複数の直交変換係数を同数の量子化閾値と比較して、比較結果に基づき選択的に前記直交変換係数を量子化して符号化する画像符号化方法であって、

前記直交変換係数を、第 1 のスキャン順序に並べ替えて、 $n$  個ずつ出力する第 1 のスキャン変換工程と、

前記第 1 のスキャン変換工程より出力される  $n$  個ずつの前記直交変換係数を、 $n$  個の量子化閾値と比較して、該比較結果に基づき選択的に前記直交変換係数を量子化して出力する量子化工程と、

前記量子化工程より出力される量子化された直交変換係数を、ジグザグスキャン順序に並べ替えて出力する第 2 のスキャン変換工程と、

前記第 2 のスキャン変換工程より出力される前記量子化された直交変換係数を符号化する符号化工程と、

を含み、

前記第 1 のスキャン順序は、前記量子化工程における前記比較結果が有意となる前記直交変換係数が前記  $n$  個ずつの出力単位に分散されるようなスキャン順序である

ことを特徴とする画像符号化方法。

【請求項 10】

$n$  個の複数の直交変換係数を同数の量子化閾値と比較して、比較結果に基づき選択的に前記直交変換係数を量子化して符号化する画像符号化方法をコンピュータに実行させるための画像符号化プログラムであって、前記画像符号化方法は、

前記直交変換係数を、第 1 のスキャン順序に並べ替えて、 $n$  個ずつ出力する第 1 のスキャン変換工程と、

前記第 1 のスキャン変換工程より出力される  $n$  個ずつの前記直交変換係数を、 $n$  個の量子化閾値と比較して、該比較結果に基づき選択的に前記直交変換係数を量子化して出力する量子化工程と、

10

20

30

40

50

前記量子化工程より出力される量子化された直交変換係数を、ジグザグスキャン順序に並べ替えて出力する第2のスキャン変換工程と、

前記第2のスキャン変換工程より出力される前記量子化された直交変換係数を符号化する符号化工程と、

を含み、

前記第1のスキャン順序は、前記量子化工程における前記比較結果が有意となる前記直交変換係数が前記n個ずつの出力単位に分散されるようなスキャン順序である

ことを特徴とする画像符号化プログラム。

【発明の詳細な説明】

【0001】

10

【発明の属する技術分野】

本発明は画像の符号化を行う装置、方法及びプログラムに関する。

【0002】

【従来の技術】

多値画像の圧縮技術として、従来より原画像を複数の画素からなるブロック単位に分割して直交変換を施し、指定された量子化閾値で量子化してハフマン符号化するものが知られている。かかる符号化処理はJPEG(Joint Photographic Experts Group)方式でも取りいれられており、これをハードウェア化して符号化、復号化する装置が従来より知られている。

【0003】

20

例えば、ハードウェア化された符号化装置では、従来より量子化処理を最小限の回路規模で良好な処理レートを得るために工夫がなされており、ジグザグスキャン順に変換された直交変換係数が複数個ずつ処理される。そこで、従来の符号化装置の構成を以下に説明する。

【0004】

従来の符号化装置は、直交変換器により、複数のブロックに分割された入力原画像を、該ブロック単位で直交変換を施し、直交変換係数を出力する。出力された係数は、ジグザグスキャン変換器によりジグザグスキャン順に並べ替えられ、2係数ずつ比較器へ出力され、これに対応する量子化閾値も2つずつ同様に比較器へ出力される。比較器では出力係数と対応する量子化閾値の比較を行い、直交変換係数が量子化閾値より小さいかどうかという比較結果情報をそれぞれ出力する。この比較結果情報は、該直交変換係数を対応する量子化閾値で量子化した結果が0になるかどうかという情報と等価である。

30

【0005】

制御装置では、比較器の出力結果に応じて、2つの直交変換係数の量子化結果の少なくともいずれか一方が0であれば、量子化結果の0にならない方(有意係数)を選択するように、選択器に制御信号を出力し(両方共0の場合はいずれを選択するような制御信号を出力しても動作には影響しない)、いずれも0でないならばジグザグスキャン順になるように一つずつ2サイクルに分けて交互に選択するように制御信号を出力する。また制御装置は比較器の出力結果に応じて、ハフマン符号化器にフォーマット信号を出力する。該フォーマット信号は、2つの直交変換係数のうちいずれか一方が0であれば"0と有意係数のペア"、両方共0であれば"0と0のペア"、両方共有意係数であれば"一つの有意係数のみ"を示す情報(両方共有意係数の場合は、係数を一つずつ2サイクルに分けて量子化処理することになるので、2サイクル連続で"一つの有意係数のみ"を示す情報を出力することになる)を、ならびに"0と有意係数のペア"であるならば該0と有意係数のペアのどちらがジグザグスキャン順で先であるのかを示す情報を含む。

40

【0006】

このように、直交変換係数が0であれば量子化処理することなく結果が得られる(即ち0)ので、2つの直交変換係数のうち少なくともいずれか一方が0であれば、該2つの直交変換係数を実質的に1サイクルで量子化処理するように制御する。しかし、比較の結果、二つの係数の両方が有意であれば、どちらの係数も0でないので量子化処理を必要とし、

50

そのために 2 サイクルの処理期間が必要となる。

【 0 0 0 7 】

また、ハードウェア化された復号化装置では、従来より逆量子化処理を最小限の回路規模で良好な処理レートを得るために工夫がなされており、例えば、量子化直交変換係数のうち有意係数のみについてのみ逆量子化演算及びメモリへの書き込みを行ない、メモリの初期化動作をする提案がなされている。以下に、従来の復号化装置の構成を説明する。

【 0 0 0 8 】

従来の復号化器は、ハフマン復号化器により、ハフマン符号化された符号データを復号し、量子化された直交変換係数とそれ以前に 0 がいくつ続いているかを示すゼロラン情報を出力する。出力された量子化直交変換係数は、逆量子化器へ入力され、量子化閾値テーブルが出力する該量子化直交変換係数に対応する量子化閾値を用いて逆量子化処理を施し、直交変換係数として選択器へ出力される。

10

【 0 0 0 9 】

アドレス生成器は出力されたゼロラン情報を、出力量子化直交変換係数が直交変換処理単位ブロック内での位置に対応するかを計算し、対応する位置に応じたブロックメモリの書き込みアドレス及び量子化閾値テーブルの読み出しアドレスをそれぞれ出力すると共に、単位ブロックにつき、量子化処理に先んじてブロックメモリを初期化する為の初期化対象アドレスをブロックメモリへ出力し、初期化動作中であることを示す信号を制御装置へ出力する。該初期化処理は、単位ブロックの処理前に予め 0 を書きこんでおき、実際の処理段でブロックメモリへ書込む直交変換係数を有意係数（0 でない係数）のみに限定し、無意係数（0 である係数）の書き込み処理を省くための前処理である。この場合、有意係数が書き込まれたアドレスのみ初期化すればよく、その為に有意係数の書き込みが発生したアドレスを記憶しておく必要があり、初期化の為の書き込みアドレスは該記憶しておいたアドレス情報をもとに生成する。

20

【 0 0 1 0 】

量子化閾値テーブルは、前記書き込みアドレス生成器の出力をもとに、処理対象となる量子化直交変換係数に対応する量子化閾値を読み出し、逆量子化器に出力する。制御装置は初期化動作中を示す信号をもとに、初期化データである 0 値及び初期化データを選択するか否かを表す順序選択信号を選択器に出力し、またブロックメモリの書き込み動作・読み出し動作を制御する制御信号及び読み出しアドレス生成器に出力する。該制御信号は、単位直交変換ブロック分の書き込み動作が終了したら読み出し動作を開始し、1 サイクルにつき 2 係数ずつ読み出していき、単位直交変換ブロック分データを読み出し終わった時点で読み出しを終了し、初期化処理の為の初期化データ書き込み処理を開始し、初期化処理が終了した後に次処理対象直交変換ブロックの書き込み動作を開始するように指示される。

30

【 0 0 1 1 】

読み出しアドレス生成器は、制御装置の出力する書き込み・読み出し制御をもとに、読み出し期間中はブロックメモリに書き込まれた単位直交変換処理ブロック分のデータをジグザグスキヤン順に順次読み出しを行なうよう、アドレスを生成してブロックメモリに出力する。

【 0 0 1 2 】

ブロックメモリは、直交変換処理単位ブロック毎に初期化、書き込み、ジグザグスキヤン順に読み出し、のサイクルで動作する。また、ブロックメモリは選択器の出力を書き込みアドレスに書き込み、読み出しは読み出しアドレスに応じて、制御装置の出力する書き込み・読み出し制御信号に従って行なう。読み出し値は、逆直交変換器へ出力する。

40

【 0 0 1 3 】

逆直交変換器は、ブロックメモリよりジグザグスキヤン順に出力される直交変換係数を順次逆直交変換し、単位ブロック毎に変換結果を出力する。

【 0 0 1 4 】

以上のような構成では、ブロックメモリに対する書き込み処理は単位ブロック内に存在する有意係数の数分だけクロックサイクルを要し、読み出しは 2 係数ずつの読み出しとしたので単位ブロック内のサンプル数を 64 とすると 32 クロックサイクルを要し、初期化は単位ブ

50

ロック内に存在する有意係数の数分だけクロックサイクルを要することになる。

【0015】

例えば、単位ブロック内のサンプル数を64とし、処理対象となる単位ブロック内に有意係数が20個存在していたとすると、該処理対象ブロックの処理に要する総クロックサイクル数は、書き込み処理=20サイクル、読み出し処理=32サイクル、初期化処理=20サイクルであるので、合計して72クロックサイクルということになる。

【0016】

さらに、ある単位直交変換ブロック ( $8 \times 8 = 64$  サンプルとする) を処理するのに要するクロックサイクル数の最小値は、該処理対象ブロック内の有意係数の数が0であった場合であり、その際のクロックサイクル数は、書き込み処理=0サイクル、読み出し処理=32サイクル、初期化処理=0サイクルであるので、合計して32サイクルということになる。これに対し、ある単位直交変換ブロックを処理するのに要するクロックサイクル数の最大値は、該処理対象ブロック内の有意係数の数が64であった場合であり、その際のクロックサイクル数は、書き込み処理=64サイクル、読み出し処理=32サイクル、初期化処理=64サイクルであるので、合計して160サイクルということになる。

10

【0017】

【発明が解決しようとする課題】

従来の符号化装置の構成では比較手段に入力される2個の直交変換係数のペアのうち、少なくともどちらか一方の量子化結果が0になることが処理速度の観点から望ましい。その為には、直交変換ブロック内での量子化直交変換係数の各要素を、有意係数がなるべく平均的に分散されて比較手段に入力されることが望ましいが、ジグザグスキャン順に入力させてしまうと有意係数が集中して配列される傾向にあるため、符号化処理速度があがらないという問題があった。

20

【0019】

【課題を解決するための手段】

本発明は前記の問題を鑑みて、符号化効率をあげるために、以下の手段を提供する。

【0020】

n個の複数の直交変換係数を同数の量子化閾値と比較して、比較結果に基づき選択的に前記直交変換係数を量子化して符号化する画像符号化装置であって、前記直交変換係数を、第1のスキャン順序に並べ替えて、n個ずつ出力する第1のスキャン変換手段と、前記第1のスキャン変換手段が出力するn個ずつの前記直交変換係数を、n個の量子化閾値と比較して、該比較結果に基づき選択的に前記直交変換係数を量子化して出力する量子化手段と、前記量子化手段が出力する量子化された直交変換係数を、ジグザグスキャン順序に並べ替えて出力する第2のスキャン変換手段と、前記第2のスキャン変換手段が出力する前記量子化された直交変換係数を符号化する符号化手段とを含み前記第1のスキャン順序は、前記量子化手段における前記比較結果が有意となる前記直交変換係数が前記n個ずつの出力単位に分散されるようなスキャン順序であることにより、有意係数がなるべく平均的に分散されて配列されるような順序にすることにより、全体の処理レートの向上を図る。

30

【0023】

40

【発明の実施の形態】

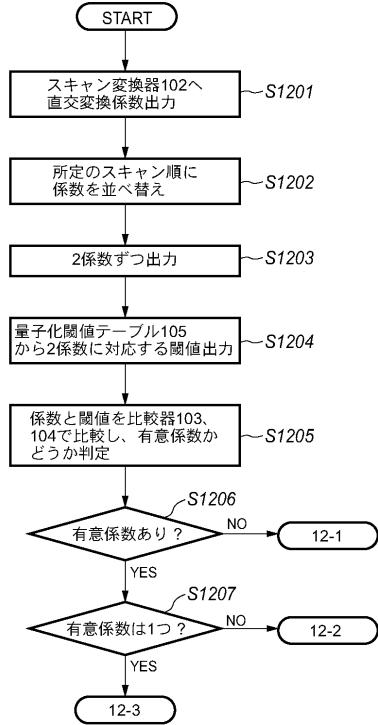

[第1の実施形態]

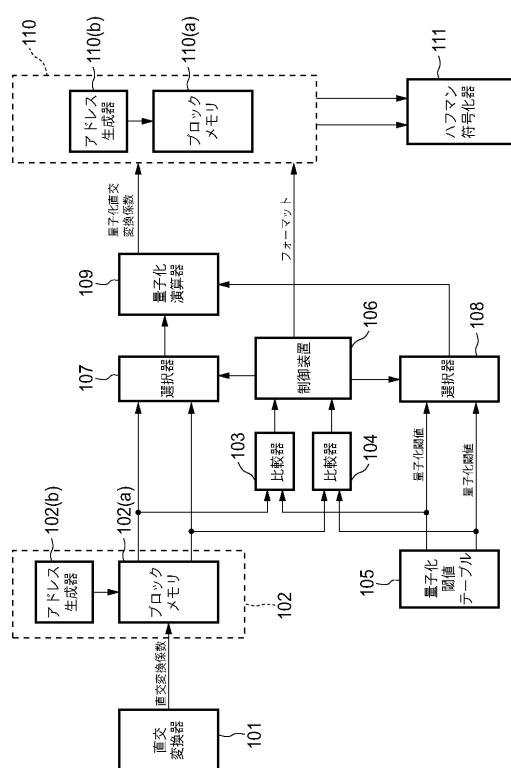

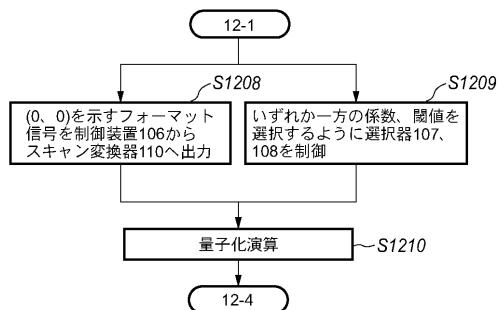

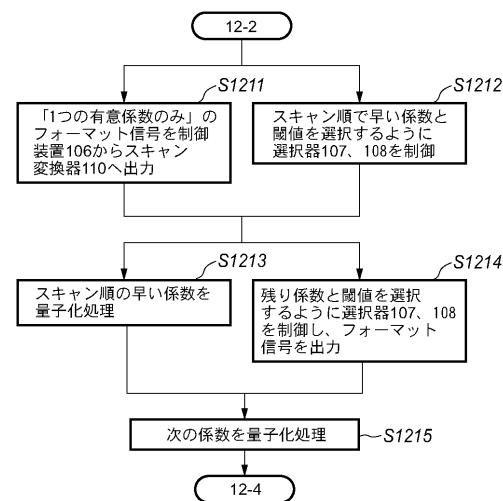

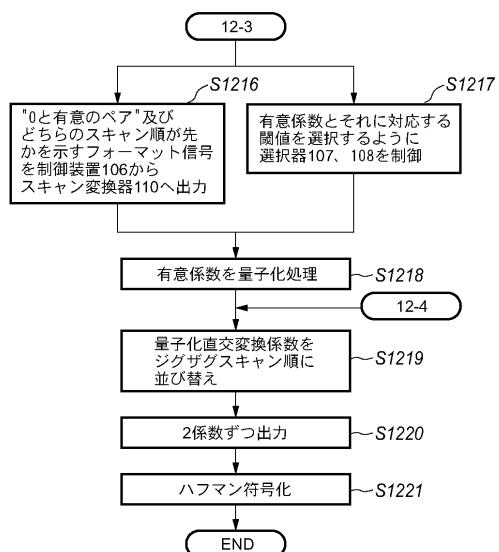

図1に、本発明の第1の実施形態の符号化装置の構成例を示す。本実施形態では2係数ずつ処理する構成となっている。また、処理の流れは図12aから図12dのフローチャートに示すようになる。

【0024】

101は直交変換器であり、符号化処理対象となる原画像を複数のブロック単位に分割したものを入力とし、該ブロック単位で直交変換を施し、直交変換係数を第1のスキャン変換器102へ順次出力する(S1201)。

【0025】

50

第1のスキャン変換器102は、直交変換器101より出力された直交変換係数を入力とし、予め定められたスキャン順序に並べ替え(S1202)、2係数ずつ出力する。また102は、例えば102(a)に示すロックメモリと102(b)に示すアドレス生成器より構成され、102(a)は101より出力された直交変換係数を、一旦1ブロック分蓄え、102(b)の指示するアドレスに従って書き込み及び読み出しを行なう。102(b)は102(a)から直交変換係数を読み出していったときに、予め定められたスキャン順で出力されるようアドレスを生成する。実際のスキャン順序は前記直交変換ブロック単位内でなるべく有意係数が分散されるように考慮されたものが処理速度の観点から望ましく、例えば図2bに示したスキャン順、図2cに示したスキャン順、または図2dに示したスキャン順などが有利である。

10

#### 【0026】

量子化閾値テーブル105は、予め所定のスキャン順序に対応するようにテーブル成分が並べ替えられており、102の出力する2つの直交変換係数にそれぞれ対応した量子化閾値を2つずつ出力する(S1204)。比較器103, 104は102及び105より出力された直交変換係数と対応する量子化閾値の2組のペアをそれぞれ入力とし、直交変換係数と量子化閾値を比較して直交変換係数が量子化閾値より小さいか否かという比較結果情報をそれぞれ出力する(S1205)。この比較結果情報は、該直交変換係数を対応する量子化閾値で量子化した結果が0になるかどうかという情報と等価である。

#### 【0027】

制御装置106は比較器103, 104の出力結果に応じて、102が出力する2つの直交変換係数の量子化結果の少なくともいずれか一方が0であれば(8-3)、量子化結果の0にならない方(有意係数)を選択するように、選択器107及び選択器108に制御信号を出力し(両方共0の場合はいずれを選択するような制御信号を出力しても動作には影響しない)、いずれも0でないならば第1のスキャン変換器102で変換されたスキャン順になるように一つずつ2サイクルに分けて交互に選択するように制御信号を出力する。また制御装置106は比較器103, 104の出力結果に応じて、第2のスキャン変換器110にフォーマット信号を出力する。該フォーマット信号は、102が出力する2つの直交変換係数のうちいずれか一方が0であれば"0と有意係数のペア"、両方共0であれば"0と0のペア"、両方共有有意係数であれば"一つの有意係数のみ"を示す情報(両方共有有意係数の場合は、係数を一つずつ2サイクルに分けて量子化処理することになるので、2サイクル連続で"一つの有意係数のみ"を示す情報を出力することになる)を、ならびに"0と有意係数のペア"であるならば該0と有意係数のペアのうちどちらが第1のスキャン変換器102で変換されたスキャン順で先であるのかを示す情報を含む。

20

#### 【0028】

このように、直交変換係数が0であれば量子化演算処理することなく結果が得られる(即ち0)ので、2つの直交変換係数のうち少なくともいずれか一方が0であれば、該2つの直交変換係数を実質的に1サイクルで量子化処理するように制御する。

30

#### 【0029】

選択器107は102の出力する2つの直交変換係数のうちいずれか一方を、106の出力する制御信号に従って選択し、量子化演算器109へ出力する。

40

#### 【0030】

選択器108は、105の出力する2つの量子化閾値のうちいずれか一方を、106の出力する制御信号に従って選択し、量子化演算器109へ出力する。また、選択器108の出力する量子化閾値は、常に選択器107の出力する直交変換係数に対応する量子化閾値となる。

#### 【0031】

量子化演算器109は、107の出力を108の出力で除算して得る量子化結果を、第2のスキャン変換器110へ出力する。

#### 【0032】

第2のスキャン変換器110は、106の出力するフォーマット信号に応じて、109の

50

出力をジグザグスキャン順に並べ替え (S 1 2 1 9)、2つずつハフマン符号化器 1 1 1 へ出力する (S 1 2 2 0)。また 1 1 0 は、例えば 1 1 0 (a) に示すブロックメモリと 1 1 0 (b) に示すアドレス生成器より構成され、1 1 0 (a) は 1 0 9 の出力を、一旦 1 ブロック分蓄え、1 1 0 (b) の指示するアドレスに従って書き込み及び読み出しを行なう。1 1 0 (b) は 1 1 0 (a) から直交変換係数を読み出していったときに、ジグザグスキャン順で出力されるようにアドレスを生成する。

#### 【0 0 3 3】

ハフマン符号化器 1 1 1 は、1 1 0 の出力を順次ハフマン符号化していく (S 1 2 2 1)。このように 1 0 2 より出力される 2 つの直交変換係数の量子化結果のうち、いずれか一方が 0 であれば該 2 つの係数を量子化するのに 1 サイクルの処理時間ですみ、いずれも 0 でないならばどちらも除算による量子化処理が必要となる為、該 2 つの係数を量子化するのに 2 サイクルの処理期間が必要となる。

10

#### 【0 0 3 4】

以下、例として 1 0 2 の出力する 2 つの直交変換係数を量子化閾値で量子化した結果を 1 0 2 の出力する順番に並べると、以下に示したようになる場合の処理を説明する。

#### 【0 0 3 5】

例：「0」は量子化結果が 0、「有」は量子化結果が 0 でない（つまり有意係数）ことを示す。

#### 【0 0 3 6】

量子化結果：(0、有)、(0、0)、(有、0)、(有、有)

20

まず最初のペア (0、有) は一方が 0 で他方が有意係数であるので、制御装置 1 0 6 は選択器 1 0 7, 1 0 8 に対し有意係数の方を選択するよう、制御信号を出力し (S 1 2 1 7)、また第 2 のスキャン変換器 1 1 0 には"0 と有意係数のペア"という情報、ならびにそのどちらが第 1 のスキャン変換器 1 0 2 で変換されたスキャン順で先であるのかを示す情報を同時に output する (S 1 2 1 6)。

#### 【0 0 3 7】

量子化演算器 1 0 9 は 1 0 7 より出力された有意係数を 1 0 8 の出力である量子化閾値で除算して得た量子化直交変換係数（有意係数）を第 2 のスキャン変換器 1 1 0 に出力する (S 1 2 1 8)。

#### 【0 0 3 8】

30

次のペア (0、0) は両方共 0 であるので、制御装置 1 0 6 は選択器 1 0 7, 1 0 8 に対しいずれか一方（どちらでもよい）を選択するよう、制御信号を出力し (S 1 2 0 9)、また第 2 のスキャン変換器 1 1 0 には"0 と 0 のペア"を示すフォーマット信号を同時に output する (S 1 2 0 8)。

#### 【0 0 3 9】

量子化演算器 1 0 9 は 1 0 7 より出力された係数を 1 0 8 より出力された量子化閾値で除算して得た量子化直交変換係数（この場合結果的には無意係数になる）を第 2 のスキャン変換器 1 1 0 に出力する (S 1 2 1 0)。

#### 【0 0 4 0】

40

その次のペア (有、0) は一方が有意係数で他方が 0 であるので、制御装置 1 0 6 は選択器 1 0 7, 1 0 8 に対し有意係数の方を選択するよう、制御信号を出力し (S 1 2 1 7)、また第 2 のスキャン変換器 1 1 0 には"0 と有意係数のペア"という情報ならびにそのどちらが第 1 のスキャン変換器 1 0 2 で変換されたスキャン順で先であるのかを示す情報を同時に output する (S 1 2 1 6)。

#### 【0 0 4 1】

量子化演算器 1 0 9 は 1 0 7 より出力された有意係数を 1 0 8 の出力である量子化閾値で除算して得た量子化直交変換係数（有意係数）を第 2 のスキャン変換器 1 1 0 に出力する (S 1 2 1 8)。

#### 【0 0 4 2】

その次のペア（有、有）は両方共 0 でないので、制御装置 1 0 6 は選択器 1 0 7, 1 0 8

50

に対します最初のサイクルでは第1のスキャン変換器102で変換されたスキャン順で早い方を選択するよう、制御信号を出力し(S1212)、また第2のスキャン変換器110には"一つの有意係数のみ"という情報を同時に出力する(S1211)。その次のサイクルでは第1のスキャン変換器102で変換されたスキャン順で後の方を選択するよう、制御信号を出力し、また第2のスキャン変換器110には"一つの有意係数のみ"という情報を同時に出力する(S1214)。

【0043】

量子化演算器109は、2サイクルに分けて107より出力された係数及び108より出力された量子化閾値を用いて、2サイクルに分けて量子化演算し、その結果を量子化直交変換係数として2サイクルに分けて第2のスキャン変換器110に出力する(S1213 10、S1215)。

【0044】

このように、以上示した例では8個の係数の量子化処理を合計5サイクルで行なうことになる。

【0045】

[第2の実施形態]

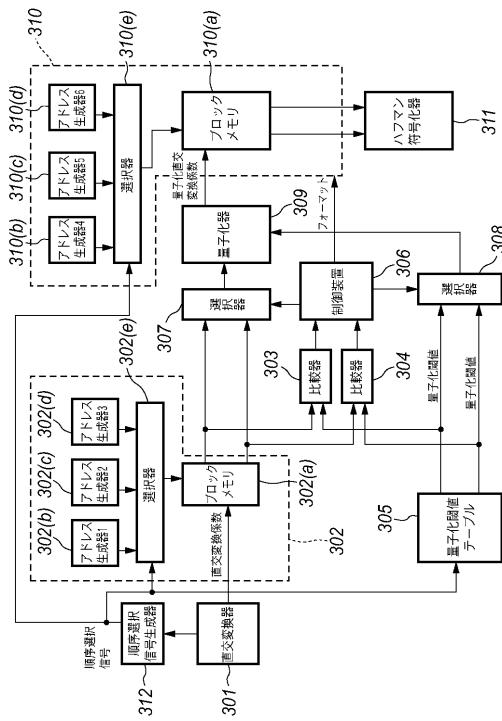

図3に、本発明の第2の実施形態の符号化装置の構成例を示す。

【0046】

301は直交変換器であり、符号化処理対象となる原画像を複数のブロック単位に分割したものを入力とし、該ブロック単位で直交変換を施し、直交変換係数を第1のスキャン変換器302へ順次出力するとともに、該処理対象ブロックの周波数分布情報を順序選択信号生成器312へ出力する。順序選択信号生成器312は、301の出力する周波数分布情報をもとに第1のスキャン変換器302の備える複数のスキャン順序うちただ一つを選択する順序選択信号を出力する。 20

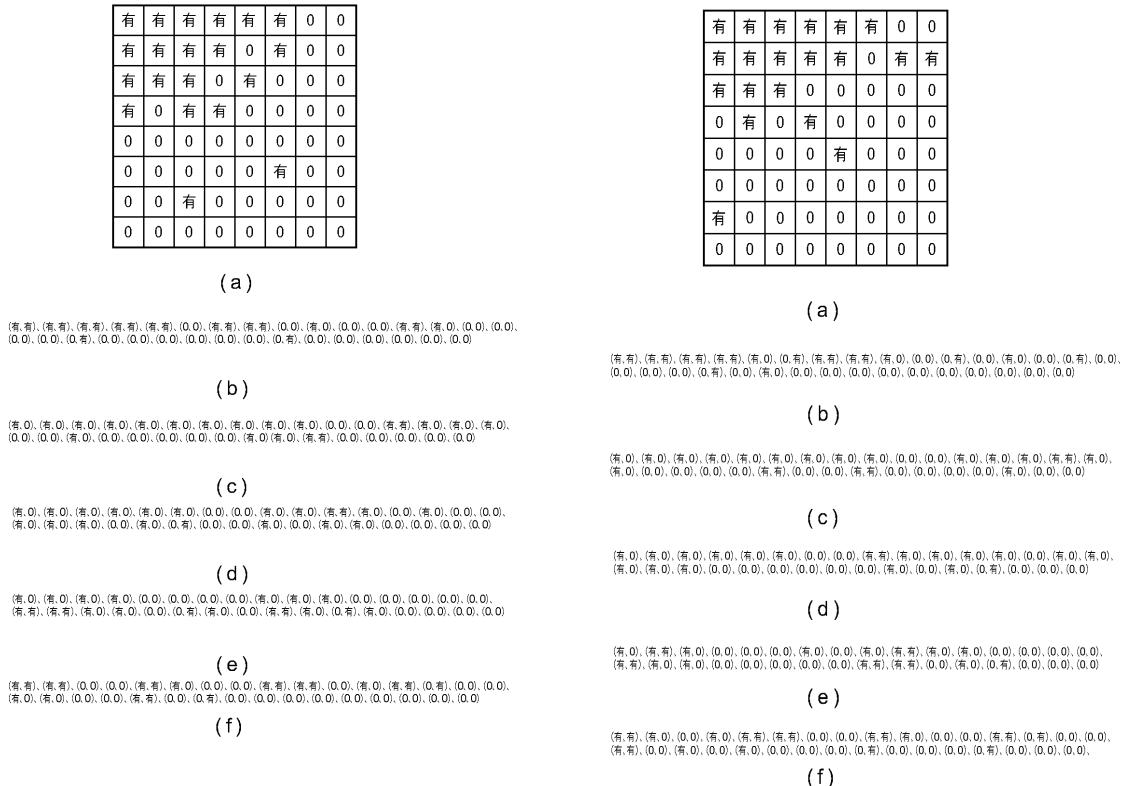

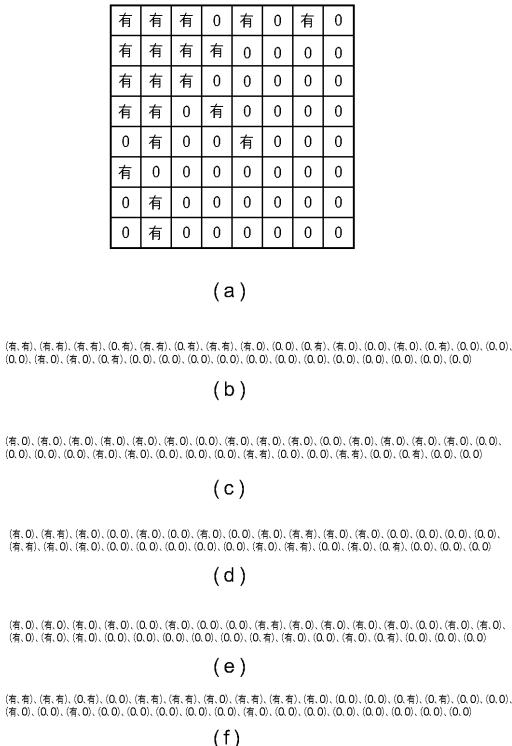

【0047】

例えば、図5(a)に示す量子化結果配列例のように、有意係数が上半分に偏っている場合、図2(a)から(d)に示すスキャン順序でスキャンすると、(有、有)の組み合わせの数は、それぞれ5、2、1、4となる。従って、第1のスキャン変換器302としては図2cに示すスキャン順序でスキャンすれば(有、有)の組み合わせの数が少なくなる。また、図6(a)に示す量子化結果配列例のように、有意係数が左半分に偏っている場合、図2(a)から(d)に示すスキャン順序でスキャンすると、(有、有)の組み合わせの数は、それぞれ5、2、4、1となる。従って、第1のスキャン変換器302としては図2dに示すスキャン順序でスキャンすれば(有、有)の組み合わせの数が少なくなる。このように、312は処理対象ブロックの周波数分布情報をもとに、処理速度的に有利となるスキャン順序を選択するよう、順序選択信号を生成していく。 30

【0048】

第1のスキャン変換器302は、直交変換器301より出力された直交変換係数を入力とし、予め備えた複数のスキャン順序のうち312より出力された順序選択信号に従って一つを選択し、該選択したスキャン順序に並べ替え、2係数ずつ出力する。また302は、302(a)に示すブロックメモリと、302(b)に示すアドレス生成器1、302(c)に示すアドレス生成器2、及び302(d)に示すアドレス生成器3と、312より出力された順序選択信号に従って302(b)、302(c)、302(d)の出力より一つを選択する選択器302(e)より構成される。302(a)は301より出力された直交変換係数を、一旦1ブロック分蓄え、302(e)の出力の指示するアドレスに従って書き込み及び読み出しが行なう。302(b)、302(c)、302(d)はそれぞれ302(a)から直交変換係数を読み出していくときに、例えば図2bに示したスキャン順、図2cに示したスキャン順、図2dに示したスキャン順のような予め定められたスキャン順で出力されるようにアドレスを生成する。 40

【0049】

量子化閾値テーブル305は、直交変換器312の出力する順序選択信号をもとに、30

2の出力する2つの直交変換係数にそれぞれ対応した量子化閾値を2つずつ出力する。

【0050】

比較器303, 304は302及び305より出力された直交変換係数と対応する量子化閾値の2組のペアをそれぞれ入力とし、直交変換係数と量子化閾値を比較して直交変換係数が量子化閾値より小さいか否かという比較結果情報をそれぞれ出力する。この比較結果情報は、該直交変換係数を対応する量子化閾値で量子化した結果が0になるかどうかという情報と等価である。

【0051】

制御装置306は比較器303, 304の出力結果に応じて、302が出力する2つの直交変換係数の量子化結果の少なくともいずれか一方が0であれば、量子化結果の0にならない方を選択するように、選択器307及び選択器308に制御信号を出力し(両方共0の場合はいずれを選択するような制御信号を出力しても動作には影響しない)、いずれも0でないならば第1のスキャン変換器302で選択されたスキャン順になるように2サイクルに分けて一つずつ交互に選択するように制御信号を出力する。また制御装置306は比較器303, 304の出力結果に応じて、第2のスキャン変換器310にフォーマット信号を出力する。該フォーマット信号は、302が出力する2つの直交変換係数のうちいずれか一方が0であれば"0と有意係数のペア"、両方共0であれば"0と0のペア"、両方共有意係数であれば"一つの有意係数のみ"を示す情報(両方共有意係数の場合は、係数を一つずつ2サイクルに分けて量子化処理することになるので、2サイクル連続で"一つの有意係数のみ"を示す情報を出力することになる)を、ならびに"0と有意係数のペア"であるならば該0と有意係数のペアのうちどちらが第1のスキャン変換器302で変換されたスキャン順で先であるのかを示す情報を含む。

【0052】

このように、直交変換係数が0であれば量子化演算処理することなく結果が得られる(即ち0)ので、2つの直交変換係数のうち少なくともいずれか一方が0であれば、該2つの直交変換係数を実質的に1サイクルで量子化処理するように制御する。

【0053】

選択器307は302の出力する2つの直交変換係数のうちいずれか一方を、306の出力する制御信号に従って選択し、量子化演算器309へ出力する。選択器308は、305の出力する2つの量子化閾値のうちいずれか一方を、306の出力する制御信号に従って選択し、量子化演算器309へ出力する。また、選択器308の出力する量子化閾値は、常に選択器307の出力する直交変換係数に対応する量子化閾値となる。

【0054】

量子化演算器309は、307の出力を308の出力で除算して得る量子化結果を、第2のスキャン変換器310へ出力する。

【0055】

第2のスキャン変換器310は、306の出力するフォーマット信号に応じて、直交変換器312の出力する順序選択信号をもとに、309の出力をジグザグスキャン順に並べ替え、2つずつハフマン符号化器311へ出力する。また310は、310(a)に示すプロックメモリと310(b)に示すアドレス生成器4、310(c)に示すアドレス生成器5、及び310(d)に示すアドレス生成器6と、301より出力された順序選択信号に従って310(b)、310(c)、310(d)の出力より一つを選択する選択器310(e)より構成される。310(a)は309の出力を、一旦1プロック分蓄え、310(e)が出力するアドレスに従って書き込み及び読み出しを行なう。310(b)、310(c)、310(d)はそれぞれ310(a)から量子化直交変換係数を読み出していったときに、ジグザグスキャン順で出力されるようにアドレスを生成する。

【0056】

ハフマン符号化器311は、310の出力を順次ハフマン符号化していく。

【0057】

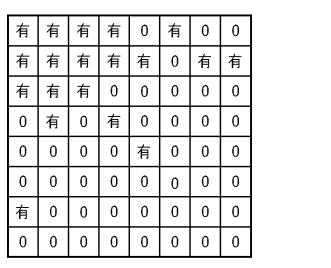

図4(a)に、8×8画素単位にプロック分割された画像に直交変換及び量子化を施した

10

20

30

40

50

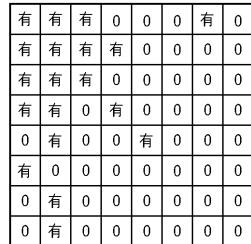

例を示す。図で「有」は有意係数、「0」は無意係数を表す。一般に多くの画像は直交変換を施した場合直流成分、低周波成分に電力が集中することが知られており、また量子化閾値は、人間の視覚特性が高周波成分に対し鈍感であることを考慮して、高周波成分に対応する量子化閾値に大きい値を割り当てることが多い。そのため、図4(a)に示すように、有意係数は直交変換ブロックの左上の方、つまりジグザグスキャン順で早い方に連続して集中する傾向にある。

【0058】

図4(a)の量子化結果配列例では、ジグザグスキャン順に2つずつ係数を取り出して並べると、図4(b)のようになる。この場合、(有、有)の組み合わせが7つあるので、64係数の量子化処理時間は $7 \times 2 + (32 - 7) = 39$ サイクルとなる。即ち、図4(a)に示した例では従来例の構成では39サイクルの量子化処理時間をする。

【0059】

これに対し、本発明の第1の実施形態の構成では量子化処理に要する処理時間は以下のようになる。

【0060】

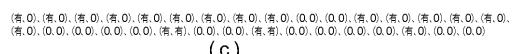

まず、図2bに示したスキャン順を選択して図4(a)に示す量子化結果配列例を該スキャン順に2つずつ並べると、図4(c)のようになる。この場合、(有、有)の組み合わせが2つあるので、64係数の量子化処理時間は $2 \times 2 + (32 - 2) = 34$ サイクルとなる。

【0061】

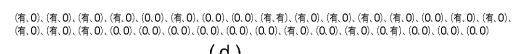

次に、図2cに示したスキャン順を選択して図4(a)に示す量子化結果配列例を該スキャン順に2つずつ並べると、図4(d)のようになる。この場合、(有、有)の組み合わせが1つあるので、64係数の量子化処理時間は $1 \times 2 + (32 - 1) = 33$ サイクルとなる。

【0062】

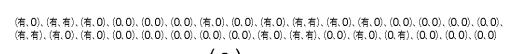

次に、図2dに示したスキャン順を選択して図4(a)に示す量子化結果配列例を該スキャン順に2つずつ並べると、図4(e)のようになる。この場合、(有、有)の組み合わせが2つあるので、64係数の量子化処理時間は $2 \times 2 + (32 - 2) = 34$ サイクルとなる。

【0063】

前記のように、従来のスキャン順に従った場合と、本発明におけるスキャン順に従った場合において、 $8 \times 8$ のブロックにサイクル数の差は、図2b及び図2dに示したスキャン順を選択した場合は5サイクル、図2cに示したスキャン順を選択した場合は6サイクルである。これを画面全体(画素数Na)に換算すると以下の式によりサイクル数の差(D)を求めることができる。

【0064】

総画素数が200万ならば、 $D = (Na / 64) \times 5$  [サイクル]について、図2bに示したスキャン順を選択すれば、

$$D = 200 \times 10^6 / 64 \times 5 = 15.6 \times 10^6 \text{ [サイクル]}$$

図2cに示したスキャン順を選択すれば、

$$D = 200 \times 10^6 / 64 \times 6 = 18.75 \times 10^6 \text{ [サイクル]} \text{ となる。}$$

【0065】

[第3の実施形態]

なお、上述した図2bから図2dに示した高周波成分と低周波成分とが入り組んだスキャン順を採用せず、図2eに示した様なラスタスキャン縦方向のスキャン順序、又はラスタスキャン順序を採用してもよい。以下、ラスタスキャン縦方向のスキャン順序を適用した場合を具体的に説明する。

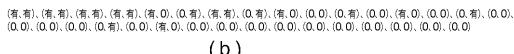

【0066】

図14(a)は、 $8 \times 8$ 画素単位にブロック分割された画像に直交変換及び量子化を施した例である。図4(a)と同様、図14(a)においても、「有」は有意係数、「0」は

10

20

30

40

50

無意係数を表す。

【0067】

図14(a)の例では、ジグザグスキャン順に2つずつ係数を取り出して並べると、図14bのようになる。この場合、(有、有)の組み合わせが9個あるので、64係数の量子化処理時間は $9 \times 2 + (32 - 9) = 41$ サイクルとなる。即ち、図14(a)に示した例(従来例の構成)では41サイクルの量子化処理時間をする。

【0068】

これに対し、図2eに示したスキャン順を採用した場合、量子化処理に要する処理時間は以下のようなになる。図2eに示したスキャン順を採用して図14(a)の例を該スキャン順に2つずつ並べると、図14cのようになる。この場合、(有、有)の組み合わせが6つあるので、64係数の量子化処理時間は $6 \times 2 + (32 - 6) = 38$ サイクルとなる。

10

【0069】

図15(a)に $8 \times 8$ 画素単位にブロック分割された画像に直交変換及び量子化を施した別の例である。図4(a)と同様、図15(a)においても、「有」は有意係数、「0」は無意係数を表す。

【0070】

図15(a)の例では、ジグザグスキャン順に2つずつ係数を取り出して並べると、図15bのようになる。この場合、(有、有)の組み合わせが8個あるので、64係数の量子化処理時間は $8 \times 2 + (32 - 8) = 40$ サイクルとなる。即ち、図15(a)に示した例(従来例の構成)では40サイクルの量子化処理時間をする。

20

【0071】

これに対し、図2eに示したスキャン順を採用した場合、量子化処理に要する処理時間は以下のようなになる。図2eに示したスキャン順を選択して図15(a)の例を該スキャン順に2つずつ並べると、図15cのようになる。この場合、(有、有)の組み合わせが5つあるので、64係数の量子化処理時間は $5 \times 2 + (32 - 5) = 37$ サイクルとなる。

【0072】

以上のように、図2eに示すスキャン順を採用しても、サイクル数を十分に低減する効果を得ることが可能である。

【0073】

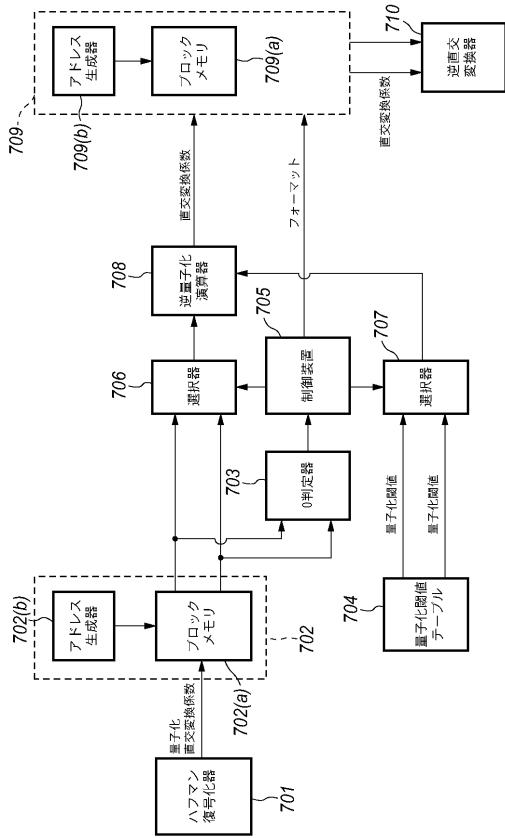

[第4の実施形態]

30

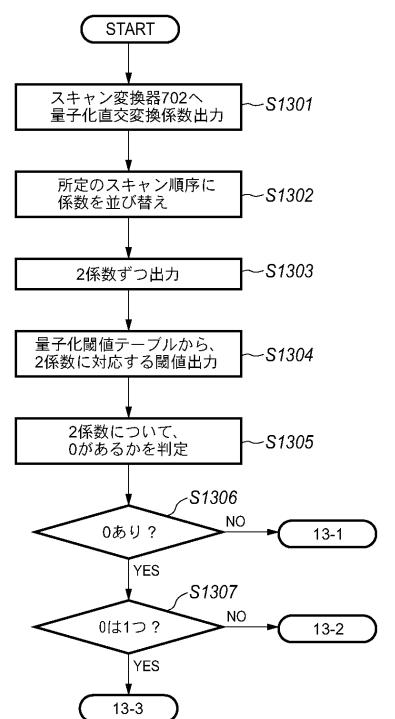

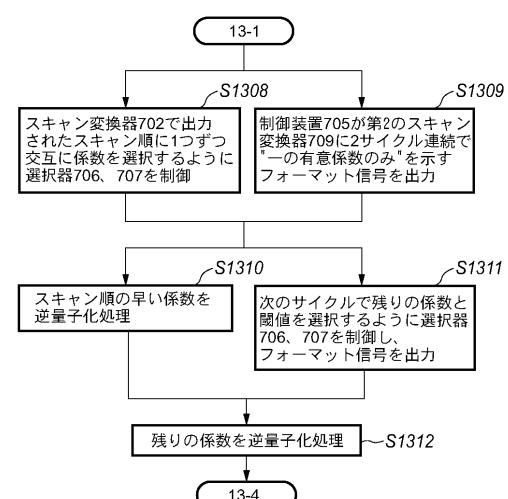

図7に本発明の第4の実施形態を示す。701はハフマン復号化器であり、ハフマン符号化された符号データを復号し、量子化された直交変換係数として第1のスキャン変換器702へ出力する(S1301)。

【0074】

第1のスキャン変換器702は、ハフマン復号器701より出力された量子化直交変換係数を入力とし、予め定められたスキャン順序に並べ替え(S1302)、2係数ずつ出力する(S1303)。また702は、例えば702(a)に示すブロックメモリと702(b)に示すアドレス生成器より構成され、702(a)は701より出力された量子化直交変換係数を、一旦1ブロック分蓄え、702(b)の指示するアドレスに従って書き込み及び読み出しを行なう。702(b)は702(a)から量子化直交変換係数を読み出していったときに、予め定められたスキャン順で出力されるようにアドレスを生成する。実際のスキャン順序は前記直交変換ブロック単位内でなるべく有意係数が分散されるように考慮されたものが処理速度の観点から望ましく、例えば図2bに記載のスキャン順、図2cに記載のスキャン順、または図2bに記載のスキャン順などが有利である。

40

【0075】

量子化閾値テーブル704は、702の出力する2つの量子化直交変換係数にそれぞれ対応した量子化閾値を2つずつ出力する(S1304)。

【0076】

0判定機703は702より出力された2つの量子化直交変換係数を入力とし、該入力された量子化直交変換係数がそれぞれ0であるか否か判定し、その判定結果を制御装置70

50

5に出力する( S 1 3 0 5 )。

【 0 0 7 7 】

制御装置 7 0 5 は 0 判定器 7 0 3 の出力結果に応じて、7 0 2 が出力する 2 つの量子化直交変換係数のうちすくなくともいずれか一方が 0 であれば、0 でない方(有意係数)を選択するように、選択器 7 0 6 及び選択器 7 0 7 に制御信号を出力し(両方共 0 の場合はいずれを選択するような制御信号を出力しても動作に影響しない)、いずれも 0 でないならば 2 サイクルに分けて第 1 のスキャン変換器 7 0 2 で出力されたスキャン順になるよう一つずつ交互に選択するように制御信号を出力する。また制御装置 7 0 5 は 0 判定器 7 0 3 の出力結果に応じて、第 2 のスキャン変換器 7 0 9 にフォーマット信号を出力する。該フォーマット信号は、7 0 2 が出力する 2 つの量子化直交変換係数のうちいずれか一方が 0 であれば"0 と有意係数のペア"、両方共 0 であれば"0 と 0 のペア"、両方共有意係数であれば"一つの有意係数のみ"を示す情報(両方共有意係数の場合は、係数を一つずつ 2 サイクルに分けて逆量子化処理することになるので、2 サイクル連続で"一つの有意係数のみ"を示す情報を出力することになる)を、ならびに"0 と有意係数のペア"であるならば該 0 と有意係数のペアのうちどちらが第 1 のスキャン変換器 7 0 2 で変換されたスキャン順であるのかを示す情報を含む。10

【 0 0 7 8 】

このように、量子化直交変換係数が 0 であれば逆量子化演算処理することなく結果が得られる(即ち 0)ので、2 つの量子化直交変換係数のうち少なくともいずれか一方が 0 であれば、該 2 つの量子化直交変換係数を実質的に 1 サイクルで逆量子化するように制御する。20

【 0 0 7 9 】

選択器 7 0 6 は 7 0 2 の出力する 2 つの量子化直交変換係数のうちいずれか一方を、7 0 5 の出力する制御信号に従って選択し、逆量子化演算器 7 0 8 へ出力する。選択器 7 0 7 は、7 0 4 の出力する 2 つの量子化閾値のうちいずれか一方を、7 0 5 の出力する制御信号に従って選択し、逆量子化演算器 7 0 8 へ出力する。また、選択器 7 0 7 の出力する量子化閾値は、常に選択器 7 0 6 の出力する量子化直交変換係数に対応する量子化閾値となる。

【 0 0 8 0 】

逆量子化演算器 7 0 8 は、7 0 6 の出力に 7 0 7 の出力を乗じて得る逆量子化結果を、第 2 のスキャン変換器 7 0 9 へ出力する。30

【 0 0 8 1 】

第 2 のスキャン変換器 7 0 9 は、制御装置 7 0 5 の出力するフォーマット信号に応じて、7 0 8 の出力を予め定められたスキャン順に並べ替え( S 1 3 1 9 )、2 つずつ逆直交変換器 7 1 0 へ出力する( S 1 3 2 0 )。また 7 0 9 は、例えば 7 0 9 ( a ) に示すプロックメモリと 7 0 9 ( b ) に示すアドレス生成器より構成され、7 0 9 ( a ) は 7 0 8 の出力を一旦プロック分蓄え、7 0 9 ( b ) の指示するアドレスに従って書き込み及び読み出しを行なう。7 0 9 ( b ) は 7 0 9 ( a ) から直交変換係数を読み出していったときに、予め定められたスキャン順で出力されるようにアドレスを生成する。第 2 のスキャン変換器 7 0 9 の施す実際のスキャン変換の順序は、逆直交変換器 7 1 0 の構成に応じて決定されるべきで、例えばラスタスキャン順、または縦方向のラスタスキャン順などが一般的であろう。40

【 0 0 8 2 】

逆直交変換器 7 1 0 は、7 0 9 の出力に対し、順次逆直交変換処理を施して出力していく( S 1 3 2 1 )。

【 0 0 8 3 】

以上のような構成では、前述したような 0 判定器を設け、量子化直交変換係数の逆量子化結果が 0 になるのかどうかを逆量しか処理する前に知り、少なくともどちらか一方が 0 であるならば乗算処理をする必要がない為、他方の係数とあわせて 2 つの係数を 1 サイクルでただ一つの逆量子化演算器で逆量子化処理できることになる。50

## 【0084】

例として、702の出力する2つの量子化直交変換係数が以下に示したようになる場合の処理を説明する。

## 【0085】

例：「0」は量子化直交変換係数が0、「有」は量子化直交変換係数が0でない（つまり有意係数）ことを示す。

## 【0086】

量子化直交変換係数：（0、有）、（0、0）、（有、0）、（有、有）

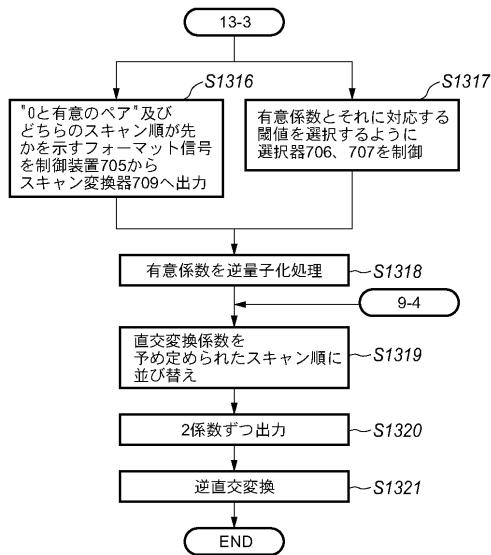

まず最初のペア（0、有）は一方が0で他方が有意係数であるので、制御装置705は選択器706, 707に対し有意係数の方を選択するよう、制御信号を出力し（S1317 10）、また第2のスキャン変換器709には"0と有意係数のペア"という情報ならびに、そのどちらが第1のスキャン変換器702で変換されたスキャン順で先であるかを示す情報を同時に出力する（S1316）。

## 【0087】

逆量子化演算器708は706より出力された有意係数に707の出力である量子化閾値を乗じて得る直交変換係数（有意係数）を第2のスキャン変換器709に出力する（S1318）。

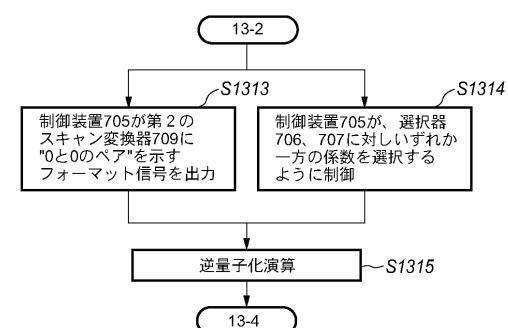

## 【0088】

次のペア（0、0）は両方共0であるので、制御装置705は選択器706, 707に対しいずれか一方（どちらでもよい）を選択するよう、制御信号を出力し（S1314）、また第2のスキャン変換器709には"0と0のペア"という情報を同時に出力する（S1313）。

## 【0089】

逆量子化演算器708は706より出力された係数に707の出力である量子化閾値を乗じて得る直交変換係数（この場合結果的には無意係数になる）を第2のスキャン変換器709に同時に出力する（S1315）。

## 【0090】

その次のペア（有、0）は一方が有意係数で他方が0であるので、制御装置705は選択器706, 707に対し有意係数の方を選択するよう、制御信号を出力し（S1317）、また第2のスキャン変換器709には"0と有意係数のペア"という情報ならびにそのどちらが第1のスキャン変換器702で変換されたスキャン順であるかを示す情報を同時に出力する（S1316）。

## 【0091】

逆量子化演算器708は706より出力された係数に707の出力である量子化閾値を乗じて得る直交変換係数（有意係数）を第2のスキャン変換器709に出力する（S1318）。

## 【0092】

その次のペア（有、有）は両方共0でないので、制御装置705は選択器706, 707に対しまず最初のサイクルでは702で変換されたスキャン順で早い方を選択するよう、制御信号を出力し（S1308）、また第2のスキャン変換器709には"一つの有意係数のみ"という情報を同時に出力する（S1309）。その次のサイクルでは702で変換されたスキャン順で後の方を選択するよう、制御信号を出力し、また第2のスキャン変換器709には"一つの有意係数のみ"という情報を同時に出力する（S1311）。

## 【0093】

逆量子化演算器708は2サイクルに分けて706より出力された係数及び707より出力された量子化閾値を用いて、2サイクルに分けて逆量子化演算し、その結果を直交変換係数として2サイクルに分けて第2のスキャン変換器709に出力する（S1310、S1312）。

## 【0094】

このように、以上示した例では8個の係数の逆量子化処理を合計5サイクルで行うことが 50

できる。

【0095】

[第5の実施形態]

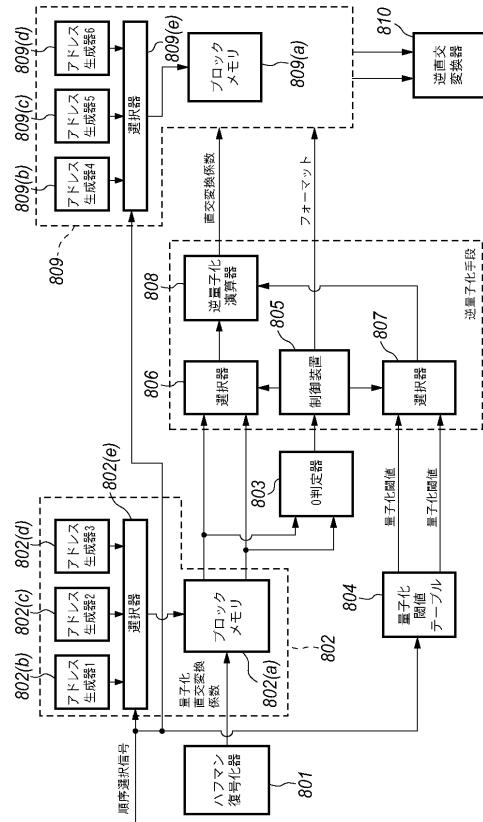

図8に本発明の第5の実施形態の復号化装置の構成例を示す。

【0096】

801はハフマン復号化器であり、ハフマン符号化された符号データを復号し、量子化された直交変換係数として第1のスキャン変換器802へ出力する。第1のスキャン変換器802は、ハフマン復号化器801より出力された量子化直交変換係数を入力とし、予め定められた複数のスキャン順序のうち予め定められた順序選択信号に従って一つを選択し、該選択したスキャン順序に並べ替え、2係数ずつ出力する。また802は、802(a)に示すロックメモリと、802(b)に示すアドレス生成器1、802(c)に示すアドレス生成器2、及び802(d)に示すアドレス生成器3と、順序選択信号に従って802(b)、802(c)、802(d)の出力より一つを選択する選択器802(e)より構成される。802(a)は801より出力された量子化直交変換係数を、一旦1ロック分蓄え、802(e)が出力するアドレスに従って書き込み及び読み出しを行なう。802(b)、802(c)、802(d)が備えるスキャン順序は、例えばそれぞれ図2bに記載のスキャン順、図2cに記載のスキャン順、図2dに記載のスキャン順、又は、図2eのスキャン順等が処理速度の観点から有利である。図2eは、ラスタスキャン縦方向のスキャン順序であるが、ラスタスキャン順序を採用してもよい。

【0097】

例えば、図10(a)に示す直交変換係数配列例のように、有意係数が上半分に偏っている場合、図2(a)から(e)に示すスキャン順序でスキャンすると、(有、有)の組み合わせの数は、それぞれ6、3、1、5、6となる。従って、図2cに示すスキャン順序で書き込み読み出しを行えば(有、有)の組み合わせの数が少なくなる。また、図11(a)に示す量子化結果配列例のように、有意係数が左半分に偏っている場合、図2(a)から(e)に示すスキャン順序でスキャンすると、(有、有)の組み合わせの数は、それぞれ5、2、4、1、6となる。従って、図2dに示すスキャン順序で書き込み読み出しを行えば(有、有)の組み合わせの数が少なくなる。このように、処理対象ブロックの有意係数分布情報をもとに処理速度的に有利となるスキャン順序が選択される。

【0098】

量子化閾値テーブル804は、順次選択信号をもとに、802の出力する2つの量子化直交変換数にそれぞれ対応した量子化閾値を2つずつ出力する。0判定器803は802より出力された2つの量子化直交変換係数を入力とし、該入力された量子化直交変換係数がそれぞれ0であるか否か判定し、その判定結果を制御装置805に出力する。

【0099】

制御装置805は0判定器803の出力結果に応じて、802が出力する2つの量子化直交変換係数のうち少なくともいずれか一方が0であれば、0でない方を選択するように、選択器806及び選択器807に制御信号を出力し(両方共0の場合はいずれを選択するような制御信号を出力しても影響しない)、いずれも0でないならば2サイクルに分けて第1のスキャン変換器802で変換されたスキャン順になるように一つずつ交互に選択するように制御信号を出力する。また制御装置805は0判定器803の出力結果に応じて、第2のスキャン変換器809にフォーマット信号を出力する。該フォーマット信号は、802が出力する2つの量子化直交変換係数のうちいずれか一方が0であれば"0と有意係数のペア"、両方共0であれば"0と0のペア"、両方共有意係数であれば"一つの有意係数のみ"を示す情報(両方共有意係数の場合は、係数を一つずつ2サイクルに分けて逆量子化処理することになるので、2サイクル連続で"一つの有意係数のみ"を示す情報を出力することになる)を、ならびに"0と有意係数のペア"であるならば該0と有意係数のペアのうちどちらが第1のスキャン変換器802で変換されたスキャン順で先であるのかを示す情報を含む。

【0100】

10

20

30

40

50

このように、量子化直交変換係数が 0 であれば逆量子化演算処理することなく結果が得られる（即ち 0）ので、2 つの量子化直交変換係数のうち少なくともいずれか一方が 0 であれば、該 2 つの量子化直交変換係数を実質的に 1 サイクルで逆量子化するように制御する。

【0101】

選択器 806 は 802 の出力する 2 つの量子化直交変換係数のうちいずれか一方を、805 の出力する制御信号に従って選択し、逆量子化演算器 808 へ出力する。選択器 807 は、804 の出力する 2 つの量子化閾値のうちいずれか一方を、805 の出力する制御信号に従って選択し、逆量子化演算器 808 へ出力する。また、選択器 807 の出力する量子化閾値は、常に選択器 806 の出力する量子化直交変換係数に対応する量子化閾値となる。

10

【0102】

逆量子化演算器 808 は、806 の出力に 807 の出力を乗じて得る逆量子化結果を、第 2 のスキャン変換器 809 に出力する。

【0103】

第 2 のスキャン変換器 809 は、順序選択信号をもとに 802 で選択されたスキャン順序に対応するスキャン順序を選択し、該選択されたスキャン順序に従って 808 の出力を並べ替え、2 つずつ逆直交変換器 810 へ出力する。また 1809 は、809 (a) に示すプロックメモリと 809 (b) に示すアドレス生成器 4、809 に示すアドレス生成器 5、及び 809 (d) に示すアドレス生成器 6 と、順序選択信号に従って 809 (b)、809 (d) の出力により一つを選択する選択器 809 (e) より構成される。809 (a) は 808 の出力を一旦 1 ブロック分蓄え、809 (e) の出力するアドレスに従って書き込み及び読み出しを行なう。逆直交変換器 810 は、809 の出力を順次逆直交変換処理していく。

20

【0104】

図 9 (a) に、 $8 \times 8$  画素単位にプロック分割された画像に直交変換及び量子化を施した例を示す。図で「有」は有意係数、「0」は無意係数を表す。

【0105】

一般に多くの画像は直交変換を施した場合直流成分、低周波成分に電力が集中することが知られており、また量子化閾値は、人間の視覚特性が高周波成分に対し鈍感であることを考慮して、高周波成分に対応する量子化閾値に大きい値を割り当てることが多い。その為図 9 (a) に示すように、有意係数は直交変換プロックの左上の方、つまりジグザグスキャン順で早い方に連続して集中する傾向にある。この特性を利用して、該有意係数が直交変換プロック内でなるべく均等に分散されるように考慮してスキャン順を定めることにより、量子化処理時間を最小限に押さえることができる。

30

【0106】

図 9 (a) に示された例において、本発明の第 4 の実施形態の構成では、処理に要するサイクルの数は以下のようになる。

【0107】

まず、図 2b に示したスキャン順を選択して図 9 (a) の例を該スキャン順に 2 つずつ並べると、図 9 (c) のようになる。この場合、(有、有)の組み合わせが 2 つあるので、64 係数の量子化処理時間は  $2 \times 2 + (32 - 2) = 34$  サイクルとなる。

40

【0108】

図 2c に示したスキャン順を選択して図 9 (a) の例を該スキャン順に 2 つずつ並べると、図 9 (d) のようになる。この場合、(有、有)の組み合わせが 1 つあるので、64 係数の量子化処理時間は  $1 \times 2 + (32 - 1) = 33$  サイクルとなる。

【0109】

次に、図 2d に示したスキャン順を選択して図 9 (a) の例を該スキャン順に 2 つずつ並べると、図 9 (e) のようになる。この場合、(有、有)の組み合わせが 3 つあるので、64 係数の量子化処理時間は  $3 \times 2 + (32 - 3) = 35$  サイクルとなる。

50

## 【0110】

次に、図2eに示したスキャン順を選択して図9(a)の例を該スキャン順に2つずつ並べると、図9(f)のようになる。この場合、(有、有)の組み合わせが7つあるので、64係数の量子化処理時間は $7 \times 2 + (32 - 7) = 39$ サイクルとなる。

## 【0111】

従って、ロックメモリ709(a)への書き込みサイクルは図2cの場合は33サイクルとなる。また、ロックメモリ709(a)からの読み出しサイクルは $8 \times 8 \div 2 = 32$ サイクルであり、初期化処理サイクルは必要ないので、全体としての処理サイクルは最小で $33 + 32 = 65$ サイクルとなる。

## 【0112】

一方、図9(a)に示された例において、従来例の構成では処理に要するサイクル数は以下のようになる。

## 【0113】

図9(a)に示された例では、有意係数の個数は20個であるので、該処理対象ブロックの処理に要する総クロックサイクル数は、書き込み処理=20サイクル、読み出し処理32サイクル、初期化処理=20サイクルであるので、合計して72サイクルとなる。

## 【0114】

従って、図9(a)に示された例においては、従来より約10%程度処理時間が短縮されたこととなる。又、従来の構成では、 $8 \times 8$ の単位ブロック当たりに要する処理サイクル数は32~160サイクルと非常に大きい開きがあり、そのため圧縮率の高い符号データと圧縮率の低い符号データとで復号化勝利に要する時間の差が大きくなってしまうという問題があったのに対し、本発明の構成を備えた本実施形態では、 $8 \times 8$ の単位ブロック当たりに要する処理サイクル数は64~96サイクルと開きが小さく、従って、圧縮率の高い符号データと圧縮率の低い符号データとで復号化処理に要する時間の差が小さいという効果がある。この事実は、復号化装置を組み込むシステムが復号化装置に要求する処理速度として、その復号化装置の持つ処理速度の最悪値に合わせなければならない場合などに効果的であり、また復号化装置を組み込むシステムが扱う画像符号データが、比較的圧縮率の低いものが多い場合などにも有効である。

## 【0115】

以上示したように、ロックメモリの初期化処理期間を省き、逆量子化器に投入する量子化直交変換係数の有意係数がなるべく均等に分散されるようにスキャン順を考慮することにより、画像の圧縮率に拘わらず高速に復号化処理を行うことができる。

## 【0116】

## [他の実施形態]

なお、本発明は、複数の機器（例えばホストコンピュータ、インタフェイス機器、リーダ、プリンタなど）から構成されるシステムに適用しても、一つの機器からなる装置（例えば、複写機、ファクシミリ装置など）に適用してもよい。

## 【0117】

また、本発明の目的は、前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記憶媒体（または記録媒体）を、システムあるいは装置に供給し、そのシステムあるいは装置のコンピュータ（またはCPUやMPU）が記憶媒体に格納されたプログラムコードを読み出し実行することによっても、達成されることは言うまでもない。この場合、記憶媒体から読み出されたプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコードを記憶した記憶媒体は本発明を構成することになる。また、コンピュータが読み出したプログラムコードを実行することにより、前述した実施形態の機能が実現されるだけでなく、そのプログラムコードの指示に基づき、コンピュータ上で稼働しているオペレーティングシステム(OS)などが実際の処理の一部または全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

## 【0118】

10

20

30

40

50

さらに、記憶媒体から読み出されたプログラムコードが、コンピュータに挿入された機能拡張カードやコンピュータに接続された機能拡張ユニットに備わるメモリに書込まれた後、そのプログラムコードの指示に基づき、その機能拡張カードや機能拡張ユニットに備わるCPUなどが実際の処理の一部または全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

【0119】

【発明の効果】

以上示したように、本発明により量子化又は逆量子化される係数のうち、有意のものがなるべく均等に分散されるように考慮したスキャン順序を採用することにより、ジグザクスキャン順で処理する場合よりも、処理サイクルを低減でき、全体として高速に符号化処理を行なうことが可能となる。

【0120】

また、予め複数のスキャン順序を用意し、これを順序選択信号によって切替えて使用することで、入力係数の分布に適応したスキャン順序を選択することが可能となり、処理サイクルをより効果的に低減できる。

【図面の簡単な説明】

【図1】本発明の第1の実施形態の構成図である。

【図2 a】ジグザグスキャン順序を示す図である。

【図2 b】本発明におけるスキャン順序の一つを示す図である。

【図2 c】本発明におけるスキャン順序の一つを示す図である。

【図2 d】本発明におけるスキャン順序の一つを示す図である。

【図2 e】本発明におけるスキャン順序の一つを示す図である。

【図3】本発明の第2の実施形態の構成を示す図である。

【図4】 $8 \times 8$  ブロックの量子化結果例、及び、それについて図2 (a) 乃至(d)に示すスキャン順序で2個ずつ配列した場合の組合せを示す図である。

【図5】 $8 \times 8$  ブロックの量子化結果例、及び、それについて図2 (a) 乃至(d)に示すスキャン順序で2個ずつ配列した場合の組合せを示す図である。

【図6】 $8 \times 8$  ブロックの量子化結果例、及び、それについて図2 (a) 乃至(d)に示すスキャン順序で2個ずつ配列した場合の組合せを示す図である。

【図7】本発明の第4の実施形態の構成を示す図である。

【図8】本発明の第5の実施形態の構成を示す図である。

【図9】 $8 \times 8$  ブロックの直交変換係数配列例、及び、それについて図2 (a) 乃至(d)に示すスキャン順序で2個ずつ配列した場合の組合せを示す図である。

【図10】 $8 \times 8$  ブロックの直交変換係数配列例、及び、それについて図2 (a) 乃至(d)に示すスキャン順序で2個ずつ配列した場合の組合せを示す図である。

【図11】 $8 \times 8$  ブロックの直交変換係数配列例、及び、それについて図2 (a) 乃至(d)に示すスキャン順序で2個ずつ配列した場合の組合せを示す図である。

【図12 a】本発明の第1の実施形態における、処理の流れを示したフローチャートである。

【図12 b】本発明の第1の実施形態における、処理の流れを示したフローチャートである。

【図12 c】本発明の第1の実施形態における、処理の流れを示したフローチャートである。

【図12 d】本発明の第1の実施形態における、処理の流れを示したフローチャートである。

【図13 a】本発明の第4の実施形態における、処理の流れを示したフローチャートである。

【図13 b】本発明の第4の実施形態における、処理の流れを示したフローチャートである。

【図13 c】本発明の第4の実施形態における、処理の流れを示したフローチャートである。

10

20

30

40

50

る。

【図13d】本発明の第4の実施形態における、処理の流れを示したフロー チャートである。

【図14】8×8 ブロックの量子化結果例、及び、それについて図2(a)又は(e)に示すスキャン順序で2個ずつ配列した場合の組合せを示す図である。

【図15】8×8 ブロックの量子化結果例、及び、それについて図2(a)又は(e)に示すスキャン順序で2個ずつ配列した場合の組合せを示す図である。

【図16】8×8 ブロックの量子化結果例、及び、それについて図2(a)又は(e)に示すスキャン順序で2個ずつ配列した場合の組合せを示す図である。

【図1】

【図2 a】

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 1  | 2  | 6  | 7  | 15 | 16 | 28 | 29 |

| 3  | 5  | 8  | 14 | 17 | 27 | 30 | 43 |

| 4  | 9  | 13 | 18 | 26 | 31 | 42 | 44 |

| 10 | 12 | 19 | 25 | 32 | 41 | 45 | 54 |

| 11 | 20 | 24 | 33 | 40 | 46 | 53 | 55 |

| 21 | 23 | 34 | 39 | 47 | 52 | 56 | 61 |

| 22 | 35 | 38 | 48 | 51 | 57 | 60 | 62 |

| 36 | 37 | 49 | 50 | 58 | 59 | 63 | 64 |

【図2 b】

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 1  | 3  | 11 | 13 | 29 | 31 | 55 | 57 |

| 5  | 9  | 15 | 27 | 33 | 53 | 59 | 44 |

| 7  | 17 | 25 | 35 | 51 | 61 | 46 | 42 |

| 19 | 23 | 37 | 49 | 63 | 48 | 40 | 22 |

| 21 | 39 | 47 | 64 | 50 | 38 | 24 | 20 |

| 41 | 45 | 62 | 52 | 36 | 26 | 18 | 8  |

| 43 | 60 | 54 | 34 | 28 | 16 | 10 | 6  |

| 58 | 56 | 32 | 30 | 14 | 12 | 4  | 2  |

【 図 2 c 】

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 1  | 3  | 5  | 7  | 9  | 11 | 13 | 15 |

| 17 | 19 | 21 | 23 | 25 | 27 | 29 | 31 |

| 33 | 35 | 37 | 39 | 41 | 43 | 45 | 47 |

| 49 | 51 | 53 | 55 | 57 | 59 | 61 | 63 |

| 50 | 52 | 54 | 56 | 58 | 60 | 62 | 64 |

| 34 | 36 | 38 | 40 | 42 | 44 | 46 | 48 |

| 18 | 20 | 22 | 24 | 26 | 28 | 30 | 32 |

| 2  | 4  | 6  | 8  | 10 | 12 | 14 | 16 |

【 図 2 e 】

|   |    |    |    |    |    |    |    |

|---|----|----|----|----|----|----|----|

| 1 | 9  | 17 | 25 | 33 | 41 | 49 | 57 |

| 2 | 10 | 18 | 26 | 34 | 42 | 50 | 58 |

| 3 | 11 | 19 | 27 | 35 | 43 | 51 | 59 |

| 4 | 12 | 20 | 28 | 36 | 44 | 52 | 60 |

| 5 | 13 | 21 | 29 | 37 | 45 | 53 | 61 |

| 6 | 14 | 22 | 30 | 38 | 46 | 54 | 62 |

| 7 | 15 | 23 | 31 | 39 | 47 | 55 | 63 |

| 8 | 16 | 24 | 32 | 40 | 48 | 56 | 64 |

【 図 2 d 】

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 1  | 17 | 33 | 49 | 50 | 34 | 18 | 2  |

| 3  | 19 | 35 | 51 | 52 | 36 | 20 | 4  |

| 5  | 21 | 37 | 53 | 54 | 38 | 22 | 6  |

| 7  | 23 | 39 | 55 | 56 | 40 | 24 | 8  |

| 9  | 25 | 41 | 57 | 58 | 42 | 26 | 10 |

| 11 | 27 | 43 | 59 | 60 | 44 | 28 | 12 |

| 13 | 29 | 45 | 61 | 62 | 46 | 30 | 14 |

| 15 | 31 | 47 | 63 | 64 | 48 | 32 | 16 |

【 図 3 】

〔 図 4 〕

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 有 | 有 | 有 | 有 | 0 | 有 | 0 | 0 |

| 有 | 有 | 有 | 有 | 0 | 有 | 0 | 0 |

| 有 | 有 | 有 | 0 | 有 | 0 | 0 | 0 |

| 有 | 0 | 有 | 有 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 有 | 0 | 0 |

| 0 | 0 | 有 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

(a)

(b)

(c)

( d )

【図5】

(a)

( b )

(c)

(d)

(e)

【 図 6 】

(a)

( b )

(c)

(d)

【 図 7 】

〔 四 8 〕

【図9】

【図11】

【図12a】

【図12b】

【図12c】

【図12d】

【図13a】

【図13b】

【図13c】

【図13d】

【 図 1 4 】

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 有 | 有 | 有 | 有 | 0 | 0 | 0 | 0 |

| 有 | 有 | 有 | 有 | 有 | 有 | 0 | 0 |

| 有 | 有 | 有 | 0 | 有 | 0 | 0 | 0 |

| 有 | 0 | 有 | 有 | 0 | 0 | 0 | 0 |

| 有 | 有 | 0 | 0 | 有 | 0 | 0 | 0 |

| 有 | 0 | 0 | 有 | 0 | 0 | 0 | 0 |

| 0 | 0 | 有 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

(a)

(c)

(c)

### 【図15】

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 有 | 有 | 有 | 0 | 有 | 0 | 0 | 0 |

| 有 | 有 | 有 | 有 | 0 | 有 | 0 | 0 |

| 有 | 有 | 有 | 0 | 有 | 0 | 0 | 0 |

| 有 | 有 | 0 | 有 | 0 | 0 | 0 | 0 |

| 有 | 0 | 有 | 有 | 有 | 0 | 0 | 0 |

| 0 | 有 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 有 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

(a)

(b)

(c)

【 図 1 6 】

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 有 | 有 | 有 | 有 | 0 | 有 | 0 | 0 |

| 有 | 有 | 有 | 0 | 有 | 0 | 0 | 0 |

| 有 | 有 | 有 | 有 | 0 | 有 | 0 | 0 |

| 0 | 0 | 有 | 0 | 有 | 0 | 0 | 0 |

| 有 | 有 | 有 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 有 | 0 | 0 |

| 有 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 有 | 0 | 0 | 0 | 0 |

(a)

( b )

(c)

---

フロントページの続き

(72)発明者 大塚 克己

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 千葉 幸郎

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 佐藤 誠

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 立野 徹也

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 堀井 啓明

(56)参考文献 特開平06-054196 (JP, A)

特開平08-195954 (JP, A)

特開平9-168151 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N1/41-1/419

H04N7/12-7/137