(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5404991号

(P5404991)

(45) 発行日 平成26年2月5日(2014.2.5)

(24) 登録日 平成25年11月8日(2013.11.8)

(51) Int.Cl.

HO2M 3/155 (2006.01)

F 1

HO2M 3/155

H

請求項の数 10 (全 19 頁)

(21) 出願番号 特願2006-30036 (P2006-30036)

(22) 出願日 平成18年2月7日 (2006.2.7)

(65) 公開番号 特開2007-215268 (P2007-215268A)

(43) 公開日 平成19年8月23日 (2007.8.23)

審査請求日 平成20年10月8日 (2008.10.8)

前置審査

(73) 特許権者 504378124

スパンション エルエルシー

アメリカ合衆国 カリフォルニア州 94

088-3453 サニーベイル テグウ

イン ドライブ 915

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100109346

弁理士 大貫 敏史

(72) 発明者 稲富 研一

愛知県春日井市高蔵寺町二丁目1844番

2 富士通ヴィエルエスアイ株式会社内

審査官 三島木 英宏

最終頁に続く

(54) 【発明の名称】 DC - DC コンバータの制御回路、DC - DC コンバータ、およびDC - DC コンバータの制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電源電圧が供給され、DC - DC コンバータの周期的なスイッチング制御のタイミングを制御する発振信号を出力する発振回路と、

起動指令に応じて漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて前記DC - DC コンバータの出力電圧を漸次増加するように制御するランプ制御部とを備え、

前記発振回路は、前記漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に応じて、前記発振信号の周波数を前記出力電圧が漸次増加する過程で漸次増加させることを特徴とするDC - DC コンバータの制御回路。

10

## 【請求項 2】

前記制御電圧値は第一容量の端子電圧値であり、前記第一容量が前記起動信号に応じて充電されることにより前記制御電圧値が漸次増加することを特徴とする請求項1に記載のDC - DC コンバータの制御回路。

## 【請求項 3】

前記発振回路は、

前記漸次増加する制御電圧値に応じて前記発振周波数を設定する周波数設定部を備えることを特徴とする請求項2に記載のDC - DC コンバータの制御回路。

## 【請求項 4】

前記周波数設定部は、

20

前記漸次増加する制御電圧値に応じた電圧を出力するバッファ部と、

前記バッファ部の出力電圧に応じたバイアス電流を設定する電流設定部と、

前記バイアス電流により充電され、所定電圧に到達することに応じて放電される第二容量とを備えることを特徴とする請求項3に記載のDC-D Cコンバータの制御回路。

【請求項5】

電源電圧が供給され、DC-D Cコンバータの周期的なスイッチング制御のタイミングを制御する発振信号を出力する発振回路と、

起動指令に応じて増加し停止指令に応じて減少する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて前記DC-D Cコンバータの出力電圧を増加または減少するように制御するランプ制御部とを備え、

前記発振回路は、前記増加または減少する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて、前記発振信号の周波数を前記出力電圧が増加または減少する過程で増加または減少させることを特徴とするDC-D Cコンバータの制御回路。

【請求項6】

電源電圧が供給され、周期的なスイッチング制御のタイミングを制御する発振信号を出力する発振回路と、

起動指令に応じて漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて出力電圧を漸次増加するように制御するランプ制御部とを備え、

前記発振回路は、前記漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に応じて、前記発振信号の周波数を前記出力電圧が漸次増加する過程で漸次増加させることを特徴とするDC-D Cコンバータ。

【請求項7】

前記制御電圧値は第一容量の端子電圧値であり、前記第一容量が前記起動信号に応じて充電されることにより前記制御電圧値が漸次増加することを特徴とする請求項6に記載のDC-D Cコンバータ。

【請求項8】

電源電圧が供給され、周期的なスイッチング制御のタイミングを制御する発振信号を出力する発振回路と、

起動指令に応じて増加し停止指令に応じて減少する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて出力電圧を増加または減少するように制御するランプ制御部とを備え、

前記発振回路は、前記増加または減少する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて、前記発振信号の周波数を前記出力電圧が増加または減少する過程で増加または減少させることを特徴とするDC-D Cコンバータ。

【請求項9】

DC-D Cコンバータの周期的なスイッチング制御のタイミングを制御する発振信号を出力するステップと、

起動指令に応じて漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて前記DC-D Cコンバータの出力電圧を漸次増加するように制御するステップとを備え、

前記発振信号を出力するステップは、前記漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に応じて、前記発振信号の周波数を前記出力電圧が漸次増加する過程で漸次増加させることを特徴とするDC-D Cコンバータの制御方法。

【請求項10】

DC-D Cコンバータの周期的なスイッチング制御のタイミングを制御する発振信号を出力するステップと、

起動指令に応じて増加し停止指令に応じて減少する制御電圧値に基づいて前記DC-D Cコンバータの出力電圧を増加または減少するように、前記電源電圧に基づく電圧値とは異なる制御するステップとを備え、

前記発振信号を出力するステップは、前記増加または減少する、前記電源電圧に基づく

10

20

30

40

50

電圧値とは異なる制御電圧値に基づいて、前記発振信号の周波数を前記出力電圧が増加または減少する過程で增加または減少させることを特徴とするDC - DCコンバータの制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、DC - DCコンバータの制御に関するものであり、特に、DC - DCコンバータにおける、電源投入時や電源切断時の出力電圧の制御に関するものである。

【背景技術】

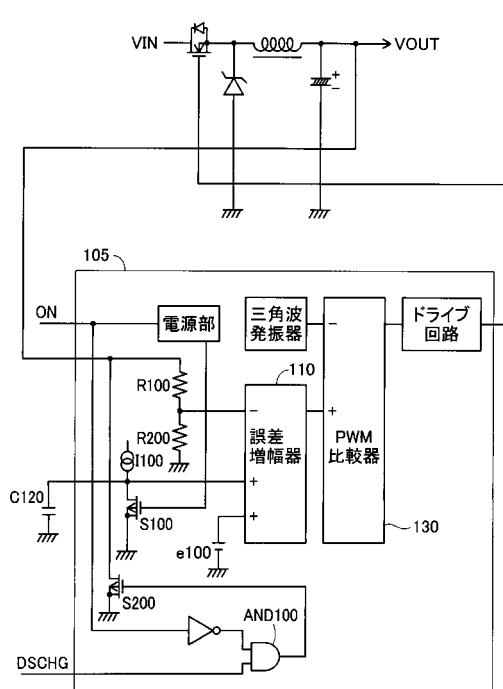

【0002】

特許文献1には、電源投入時 / 電源切断時の出力電圧立ち上がり / 立ち下がり特性が負荷に依存しないようにすることを目的とする直流 - 直流変換制御回路が開示されている。電圧制御型の直流 - 直流変換制御回路である。

【0003】

図7に示すように、DC - DC制御回路105において、定電流回路I100は、スイッチ回路S100がOFF時にソフトスタート用コンデンサC120を充電して、一定の時間でソフトスタート用コンデンサC120の電位を上昇させるための充電回路である。

【0004】

誤差增幅器110は、基準電圧e100とソフトスタート用コンデンサC120の電圧のうち低い方の電圧値を基準電圧値として、抵抗R100 / R200によって分圧された電圧との差異を増幅して、その出力をPWM比較器130へと出力する。

【0005】

定電流回路I100がソフトスタート用コンデンサC120を充電することに応じて、DC - DCコンバータの出力電圧を決める基準電圧値を徐々に上昇させ、一定時間後に正規の電圧値を出力するように制御するため、DC - DCコンバータの出力電圧は負荷に依存せず、ソフトスタート用コンデンサC120の容量で決まる時定数により制御される。

【0006】

アンド回路AND100は、負荷容量放電の有効 / 無効を制御するDSCHG信号がHigh(有効)であり、電源の切断時にON / OFFを制御するON信号がLowとなることにより、Highレベルとなる。

【0007】

負荷容量放電用スイッチ回路S200は、アンド回路AND100の出力がHighレベルを出力しているときON状態となり、DC - DCコンバータの出力とグランド間を短絡し、DC - DCコンバータの負荷に依存することなくDC - DCコンバータの出力負荷容量を強制的に放電する。

【0008】

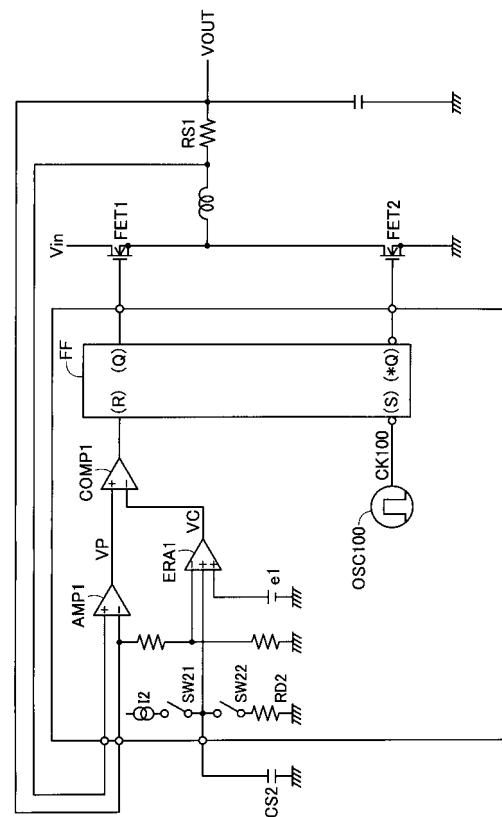

また、図8に電流制御型DC - DCコンバータを示す。

【0009】

電圧増幅器AMP1は、電流測定抵抗RS1に流れる電流により発生する電圧降下を増幅し、電流測定抵抗RS1に流れる電流に比例した電圧VPを出力する。

【0010】

誤差増幅器ERA1は、二つの非反転入力端子に印加される電圧のうち低い方の電圧と反転入力端子に印加される電圧の差を増幅して電圧VCを出力する。

【0011】

発振器OSC100は、一定の周波数でパルスを発生し、フリップフロップ回路FFを定期的にセットする。フリップフロップ回路FFがセットされると、メインスイッチングトランジスタであるMOSトランジスタFET1がオンされるとともに、同期整流スイッチであるMOSトランジスタFET2はオフされる。

【0012】

電圧比較器COMP1は、電圧増幅器AMP1の出力VPが誤差増幅器ERA1の出力

10

20

30

40

50

V Cよりも大きくなると、フリップフロップ回路 F F をリセットしてMOSトランジスタF E T 1をオフにする。

#### 【0013】

スイッチ回路 S W 2 1は、定電流回路 I 2とソフトスタート用コンデンサ C S 2とを接続する回路であり、スイッチ回路 S W 2 2は、放電抵抗 R D 2とソフトスタート用コンデンサ C S 2とを接続する回路である。

#### 【0014】

特許文献1に開示されている電圧制御型DC - DCコンバータの場合と同様に、誤差増幅器 E R A 1の非反転入力端子には、基準電圧 e 1とソフトスタート用コンデンサ C S 2とが接続されている。電源の投入に応じて、ソフトスタート用コンデンサ C S 2は定電流回路 I 2により充電されて徐々に電圧が上昇していく。ソフトスタート用コンデンサ C S 2の電圧が基準電圧 e 1より低電圧である間は、誤差増幅器 E R A 1は、出力電圧 V O U Tの分圧値を、ソフトスタート用コンデンサ C S 2の電圧に対して差分して増幅し電圧 V Cを出力する。10

#### 【0015】

【特許文献1】特開平9-154275号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0016】

上記の背景技術のDC - DCコンバータにおいては、電圧制御型、電流制御型に関わらず、電源投入に伴う起動時には、定電流回路により徐々に充電が行なわれるソフトスタート用コンデンサの端子電圧が基準電圧とされ、出力電圧 V O U Tが徐々に立ち上がる、いわゆるソフトスタート動作が行なわれる。電源投入に伴う起動時においては、ソフトスタート用コンデンサの端子電圧が誤差増幅器の基準電圧とされるところ、定常動作状態に至るまでの間は、基準電圧 e 1に比して低電圧で推移する。出力電圧 V O U Tへは限られた電力量を供給すれば足り、電力供給の不要な周期もある。20

#### 【0017】

しかしながら、電流制御型DC - DCコンバータにおいては、発振器O S C 1 0 0の周波数で決まる周期ごとにMOSトランジスタF E T 1がオンする。出力電圧 V O U Tへの電力供給が不要な周期であっても電力の供給が開始されてしまうこととなる。更に、一旦オンされたMOSトランジスタF E T 1がオフ制御されるまでには、DC - DCコンバータの制御を構成する回路の時間遅延が必要とされる。この間、MOSトランジスタF E T 1のオン状態が無条件に継続してしまう。30

#### 【0018】

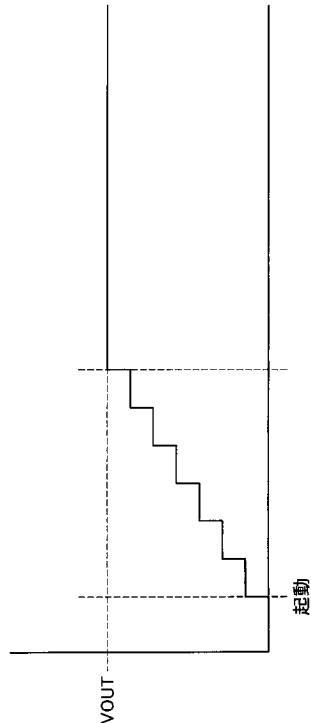

特にDC - DCコンバータの負荷が軽い場合、電流制御型DC - DCコンバータの出力電圧 V O U Tが、ソフトスタート用コンデンサ C S 2により設定された電圧値を越えて上昇する期間が発生してしまう場合がある。図9に一例を示す。MOSトランジスタF E T 1の導通制御において、発振器O S C 1 0 0による発振周期ごとにオン制御からオフ制御に至るまでの回路応答による時間遅れや、ソフトスタート用コンデンサ C S 2の端子電圧の上昇などが影響して、起動時の出力電圧 V O U Tは、滑らかなランプ波形を示さず階段状に上昇してしまう場合がある。定電流回路 I 2によるソフトスタート用コンデンサ C S 2の充電動作により期待される出力電圧 V O U Tの滑らかなランプ制御を実現できない場合も考えられ問題である。40

#### 【0019】

本発明は前記背景技術に鑑みなされたものであり、DC - DCコンバータの電源投入時または/および電源停止時、出力電圧を滑らかにランプ制御することが可能なDC - DCコンバータの制御回路、DC - DCコンバータ、およびDC - DCコンバータの制御方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0020】

10

20

30

40

50

前記目的を達成するために、本発明に係るDC - DCコンバータの制御回路は、電源電圧が供給され、DC - DCコンバータの周期的なスイッチング制御のタイミングを制御する発振信号を出力する発振回路と、起動指令に応じて漸次増加する、電源電圧に基づく電圧値とは異なる制御電圧値に基づいてDC - DCコンバータの出力電圧を漸次増加するように制御するランプ制御部とを備え、発振回路は、漸次増加する、電源電圧に基づく電圧値とは異なる制御電圧値に応じて、発振信号の周波数を出力電圧が漸次増加する過程で漸次増加させることを特徴とする。

#### 【0021】

また、本発明に係るDC - DCコンバータは、電源電圧が供給され、周期的なスイッチング制御のタイミングを制御する発振信号を出力する発振回路と、起動指令に応じて漸次増加する、電源電圧に基づく電圧値とは異なる制御電圧値に基づいて出力電圧を漸次増加するように制御するランプ制御部とを備え、発振回路は、漸次増加する、電源電圧に基づく電圧値とは異なる制御電圧値に応じて、発振信号の周波数を出力電圧が漸次増加する過程で漸次増加させることを特徴とする。

10

#### 【0022】

本発明のDC - DCコンバータの制御回路およびDC - DCコンバータでは、DC - DCコンバータは、発振回路により周期的なタイミングでスイッチング制御する発振信号を出力する。ランプ制御部は、起動指令に応じて漸次増加する、電源電圧に基づく電圧値とは異なる制御電圧値に基づいてDC - DCコンバータの出力電圧を漸次増加するように制御する。そして、発振回路は、漸次増加する、電源電圧に基づく電圧値とは異なる制御電圧値に応じて、発振信号の周波数を出力電圧が漸次増加する過程で漸次増加させる。

20

#### 【0023】

また、本発明に係るDC - DCコンバータの制御方法は、DC - DCコンバータの周期的なスイッチング制御のタイミングを制御する発振信号を出力するステップと、起動指令に応じて漸次増加する、電源電圧に基づく電圧値とは異なる制御電圧値に基づいてDC - DCコンバータの出力電圧を漸次増加するように制御するステップとを備え、発振信号を出力するステップは、漸次増加する、電源電圧に基づく電圧値とは異なる制御電圧値に応じて、発振信号の周波数を出力電圧が漸次増加する過程で漸次増加させる。

#### 【0024】

本発明のDC - DCコンバータの制御方法では、DC - DCコンバータは、周期的なスイッチング制御のタイミングを制御する発振信号が出力される。また、起動指令に応じて漸次増加する、電源電圧に基づく電圧値とは異なる制御電圧値に基づいてDC - DCコンバータの出力電圧を漸次増加するように制御する。そして、漸次増加する、電源電圧に基づく電圧値とは異なる制御電圧値に応じて、発振信号の周波数を出力電圧が漸次増加する過程で漸次増加させる。

30

#### 【0025】

これにより、起動指令により出力電圧が漸次上昇する過程、または/および停止指令により出力電圧が漸次下降する過程の制御電圧値に応じて、発振回路の発振周波数が制御される。

#### 【0026】

40

起動指令や停止指令に伴う出力電圧の遷移期間において、発振回路の毎周期ごとにスイッチング制御が行なわれても、出力電圧に対して過度な電力が供給されることなく、出力電圧を滑らかなランプ波形とすることができます。

#### 【発明の効果】

#### 【0027】

本発明によれば、DC - DCコンバータの電源投入時または/および電源停止時のDC - DCコンバータの出力電圧を、滑らかなランプ波形に制御するDC - DCコンバータの制御回路、および制御方法を提供することが可能となる。

#### 【発明を実施するための最良の形態】

#### 【0028】

50

以下、本発明の電流制御型DC-DCCコンバータの制御回路、電流制御型DC-DCCコンバータ、および制御方法について具体化した実施形態を図1乃至図6に基づき図面を参照しつつ詳細に説明する。

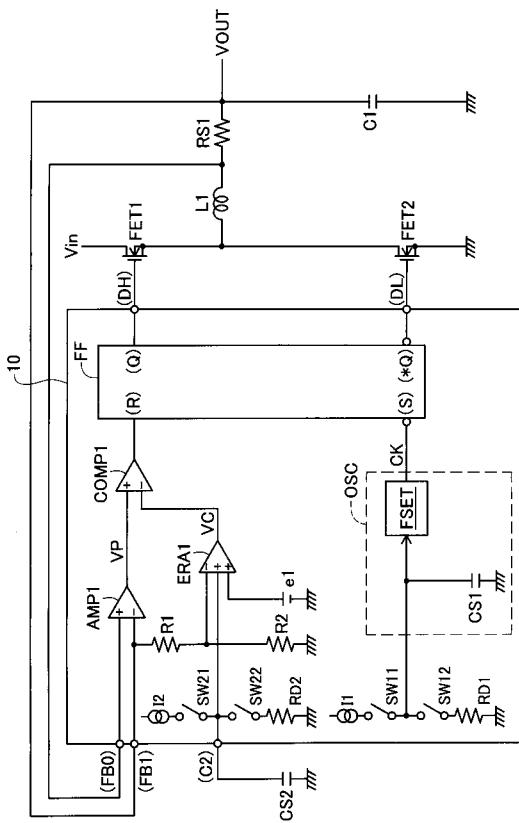

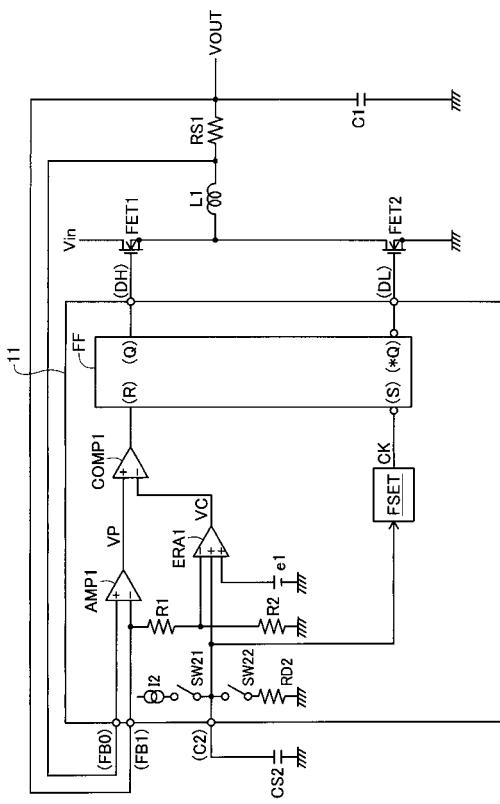

#### 【0029】

図1は、第1実施形態の電流制御型DC-DCCコンバータを示す回路図である。降圧型の構成である。また、同期整流方式の回路構成を有している。

#### 【0030】

主スイッチ素子であるMOSトランジスタFET1のドレイン端子は、入力電圧VINが入力され、ソース端子は、チョークコイルL1の入力端子および同期整流スイッチ素子であるMOSトランジスタFET2のドレイン端子に接続されている。MOSトランジスタFET2のソース端子は、接地電位に接続されている。また、MOSトランジスタFET1のゲート端子は、制御回路10の出力端子(DH)に接続され、MOSトランジスタFET2のゲート端子は、制御回路10の出力端子(DL)に接続されている。チョークコイルL1の出力端子は、電流測定抵抗RS1の入力端子および制御回路10の入力端子(FB0)に接続されている。電流測定抵抗RS1の出力端子は、平滑コンデンサC1に接続され、DC-DCCコンバータの出力端子VOUTとされる。平滑コンデンサC1の他端子は、接地電位に接続されている。また、出力端子VOUTは、制御回路10の入力端子(FB1)に接続されている。

10

#### 【0031】

制御回路10は、MOSトランジスタFET1、FET2をスイッチング制御して同期整流方式で動作する降圧型コンバータを、電流制御型で動作させる制御を行なう回路である。入力端子(FB1)に入力されるDC-DCCコンバータの出力電圧VOUTは、入力端子(FB1)と接地電位との間に直列接続される入力抵抗R1と接地抵抗R2により分圧され、誤差増幅器ERA1の反転入力端子に入力される。誤差増幅器ERA1の第1の非反転入力端子は、接地電位からの基準電圧e1が入力接続され、第2の非反転入力端子は、ソフトスタート端子(C2)を介してソフトスタート用容量素子CS2が接続されている。誤差増幅器ERA1の出力電圧VCは、電圧比較器COMP1の反転入力端子に入力される。

20

#### 【0032】

入力端子(FB1)および(FB0)は、電圧増幅器AMP1の反転入力端子および非反転入力端子に各々接続されている。電圧増幅器AMP1の出力電圧VPは、電圧比較器COMP1の非反転入力端子に入力される。電圧比較器COMP1の出力端子は、フリップフロップ回路FFのリセット端子(R)に接続されている。

30

#### 【0033】

フリップフロップ回路FFのセット端子(S)は、後述する発振回路OSCから出力される発振信号CKが入力される。フリップフロップ回路FFの非反転出力端子(Q)は、制御回路の出力端子(DH)に接続され、反転出力端子(\*Q)は、制御回路10の出力端子(DL)に接続されている。ここで、フリップフロップ回路FFのセット端子(S)は、ローレベルの信号入力によってトリガされ、リセット端子(R)は、ハイレベルの信号入力によってトリガされる。

40

#### 【0034】

スイッチ回路SW21は、定電流回路I2を、ソフトスタート端子(C2)を介してソフトスタート用容量素子CS2に接続する回路である。起動指令(不図示)に応じて導通され、少なくとも停止指令(不図示)が発せられる時点では非導通とされている。また、スイッチ回路SW22は、放電用抵抗素子RD2を、ソフトスタート端子(C2)を介してソフトスタート用容量素子CS2に接続する回路である。停止指令に応じて導通され、少なくとも起動指令が発せられる時点では非導通とされている。

#### 【0035】

発振回路OSCは、周波数設定部FSETと容量素子CS1とを備えて構成されている。容量素子CS1は、接地電位と周波数設定部FSETの制御入力端子との間に備えられ

50

ている。周波数設定部 F S E T は、制御入力端子に入力される容量素子 C S 1 の端子電圧に応じて発振周波数が設定され、発振信号 C K を出力する。

#### 【 0 0 3 6 】

容量素子 C S 1 は、ソフトスタート用容量素子 C S 2 に対する充放電回路と同様な回路構成により、充放電が行なわれる。すなわち、スイッチ回路 S W 1 1 は、定電流回路 I 1 を容量素子 C S 1 に接続する回路である。起動指令（不図示）に応じて導通され、少なくとも停止指令（不図示）が発せられる時点では非導通とされている。スイッチ回路 S W 1 1 の導通により、容量素子 C S 1 への電流経路（充電経路）が確立される。また、スイッチ回路 S W 1 2 は、放電用抵抗素子 R D 1 を容量素子 C S 1 に接続する回路である。停止指令に応じて導通され、少なくとも起動指令が発せられる時点では非導通とされている。スイッチ回路 S W 1 2 の導通により、容量素子 C S 1 からの電流経路（放電経路）が確立される。10

#### 【 0 0 3 7 】

ここで、容量素子 C S 1 は第 1 容量素子の一例である。また、定電流回路 I 1 は第 1 電流部および充電電流部の一例であり、抵抗素子は第 2 電流部および放電電流部の一例である。スイッチ回路 S W 1 1 は第 1 スイッチ回路の一例であり、スイッチ回路 S W 1 2 は第 2 スイッチ回路の一例である。

#### 【 0 0 3 8 】

発振回路 O S C は、所定の発振周波数で発振信号 C K を出力して、フリップフロップ回路 F F をセットする。フリップフロップ回路 F F のセットに応じて、非反転出力端子（ Q ）がハイレベルとなり反転出力端子（ \* Q ）はローレベルとなる。各々、出力端子（ D H ）、（ D L ）を介して、MOSトランジスタ F E T 1 を導通し、MOSトランジスタ F E T 2 を非導通とする。20

#### 【 0 0 3 9 】

誤差増幅器 E R A 1 は、二つの非反転入力端子に入力される電圧のうち低い電圧レベルを基準電圧として、反転入力端子に入力される、出力電圧 V O U T を入力抵抗 R 1 と接地抵抗 R 2 とで分圧した電圧との差を誤差増幅して電圧 V C を出力する。電圧増幅器 A M P 1 は、電流測定抵抗 R S 1 に流れる電流により発生する電圧降下を増幅した電圧 V P を出力する。電圧 V C 、 V P は、各々電圧比較器 C O M P 1 の反転入力端子、非反転入力端子に入力される。電圧比較器 C O M P 1 は、電圧 V P が電圧 V C に達することによりフリップフロップ回路 F F をリセットする。フリップフロップ回路 F F のリセットに応じて、非反転出力端子（ Q ）がローレベルとなり反転出力端子（ \* Q ）はハイレベルとなる。各々、出力端子（ D H ）、（ D L ）を介して、MOSトランジスタ F E T 1 を非導通とし、MOSトランジスタ F E T 2 を導通する。誤差増幅器 E R A 1 に入力される信号の誤差電圧に応じて電圧 V C の電圧レベルが決定される。このため、基準電圧に対して分圧電圧が低いレベルであるほどコイル電流のピーク電流値が大きく制御され、分圧電圧が基準電圧に近づくにつれて、ピーク電流値は小さなものとなる。30

#### 【 0 0 4 0 】

D C - D C コンバータが起動されると、スイッチ回路 S W 2 1 が導通して、ソフトスタート用容量素子 C S 2 は定電流回路 I 2 により充電開始される。ソフトスタート用容量素子 C S 2 の充電の初期段階では、ソフトスタート用容量素子 C S 2 の端子電圧は基準電圧 e 1 に比して低い電圧レベルにある。このため、誤差増幅器 E R A 1 は、分圧電圧をソフトスタート用容量素子 C S 2 の端子電圧に対して誤差増幅する。ソフトスタート用容量素子 C S 2 は定電流回路 I 2 により徐々に充電されるので、端子電圧は徐々に高い電圧レベルに上昇する。誤差増幅器 E R A 1 は、徐々に上昇する端子電圧に対して分圧電圧を誤差増幅する。ソフトスタート用容量素子 C S 2 の端子電圧に応じて出力電圧 V O U T が徐々に上昇する制御が行なわれる。ソフトスタート動作である。40

#### 【 0 0 4 1 】

ソフトスタート用容量素子 C S 2 の端子電圧が基準電圧 e 1 の電圧レベルを越えると、誤差増幅器 E R A 1 は、分圧電圧を基準電圧 e 1 に対して誤差増幅する。基準電圧 e 1 に50

応じて出力電圧 VOUT が制御される。

#### 【0042】

DC - DC コンバータの動作が停止されると、スイッチ回路 SW22 が導通して、ソフトスタート用容量素子 CS2 は放電用抵抗素子 RD2 を介して放電される。ソフトスタート用容量素子 CS2 の放電の初期段階では、ソフトスタート用容量素子 CS2 の端子電圧は基準電圧 e1 に比して高い電圧レベルにある。誤差増幅器 ERA1 は、分圧電圧を基準電圧 e1 に対して誤差増幅し、出力電圧 VOUT を基準電圧 e1 に応じて一定電圧レベルに維持する。ソフトスタート用容量素子 CS2 の放電が進むと端子電圧が基準電圧 e1 を下回って徐々に下降する。誤差増幅器 ERA1 は、分圧電圧を徐々に下降する端子電圧に対して誤差増幅する。ソフトスタート用容量素子 CS2 の端子電圧に応じて出力電圧 VOUT が徐々に下降する制御が行なわれる。10

#### 【0043】

MOS ドランジスタ FET1、FET2 は、フリップフロップ回路 FF のセットとリセットにより導通と非導通とが繰り返される。フリップフロップ回路 FF のセットは、発振信号 CK により行なわれるので、導通と非導通との周期は、発振回路 OSC から出力される発振信号 CK の発振周波数で決定される。後述するように、第 1 実施形態では、DC - DC コンバータの起動、停止に伴う出力電圧 VOUT の電圧レベルの遷移期間に、発振周波数を漸次増減する。

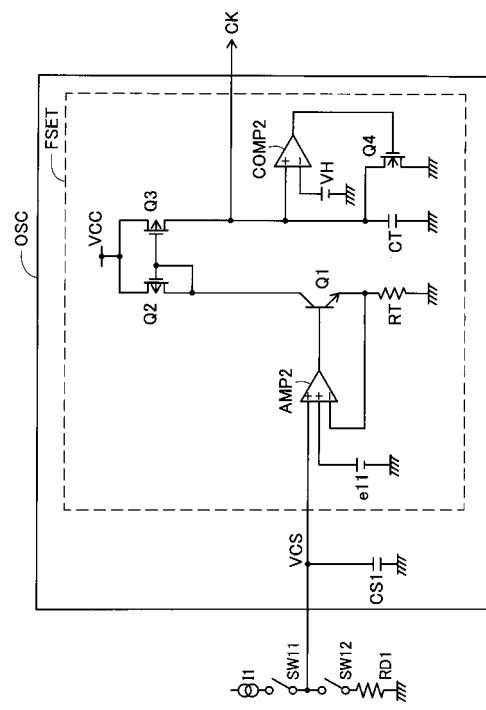

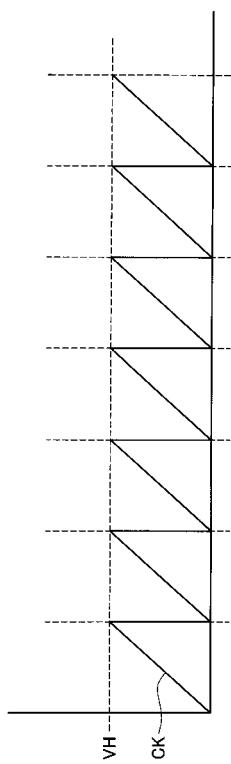

#### 【0044】

図 2 に発振回路 OSC の具体例を示す。発振信号 CK として鋸波を出力する。周波数設定部 FSET は以下の構成を有している。容量素子 CS1 の端子電圧 VCS が入力される第 1 の非反転入力端子と定常設定電圧 e11 が入力される第 2 の非反転入力端子とを備える電圧増幅器 AMP2 の出力端子が、トランジスタ Q1 のベース端子に接続されている。トランジスタ Q1 のエミッタ端子は、電流設定用抵抗素子 RT の一端に接続されると共に、電圧増幅器 AMP2 の反転入力端子に接続されている。電流設定用抵抗素子 RT の他端は接地電位に接続されている。20

#### 【0045】

電圧増幅器 AMP2 とトランジスタ Q1 がバッファ部の一例として構成されており、電流設定用抵抗素子 RT が電流設定部の一例である。バッファ部の出力であるトランジスタ Q1 のエミッタ端子が第 1 および第 2 の非反転入力端子のうち低い電圧レベルに制御され、電流設定部である電流設定用抵抗素子 RT に印加されることにより、所定のバイアス電流がトランジスタ Q1 に流れる。30

#### 【0046】

トランジスタ Q1 のコレクタ端子は、トランジスタ Q2 のドレイン端子およびゲート端子、更にトランジスタ Q3 のゲート端子に接続されている。トランジスタ Q2 および Q3 のソース端子には電源電圧 VCC が供給されている。トランジスタ Q2 および Q3 によりカレントミラー回路が構成されている。電流設定用抵抗素子 RT により設定されたバイアス電流は、カレントミラー回路によりトランジスタ Q3 から出力される。

#### 【0047】

トランジスタ Q3 のドレイン端子は、一端が接地電位に接続された周波数設定用容量素子 CT の他端に接続され出力端子 CK とされる。出力端子 CK は、電圧比較器 COMP2 の非反転入力端子に接続されている。電圧比較器 COMP2 の反転入力端子には発振信号 CK のピーク電圧 VH が入力されている。電圧比較器 COMP2 の出力端子は、トランジスタ Q4 のゲート端子に接続されている。トランジスタ Q4 は、出力端子と接地電位との間に接続されている。出力端子から発振信号 CK が出力される。40

#### 【0048】

電圧増幅器 AMP2 とトランジスタ Q1 を備えて例示されているバッファ部は、電圧増幅器 AMP2 の反転入力端子に入力される電圧を、二つの非反転入力端子に印加される電圧のうち低い方の電圧となるように制御を行なう。

#### 【0049】

10

20

30

40

50

すなわち、二つの非反転入力端子に印加される電圧のうち低い方の電圧を基準電圧として、電圧増幅器 A M P 2 は、基準電圧と電流設定用抵抗素子 R T に印加される電圧との差を増幅して、トランジスタ Q 1 のベースに出力する。電流設定用抵抗素子 R T の印加電圧は電流設定用抵抗素子 R T に流れるバイアス電流に依存するので、電流設定用抵抗素子 R T に流れる電流が少なく印加電圧が低いときには、電圧増幅器 A M P 2 の出力電圧は上昇しトランジスタ Q 1 のベース電流を増加させる。トランジスタ Q 1 のベース電流が増加するとトランジスタ Q 1 のエミッタ電流も増加して電流設定用抵抗素子 R T に流れる電流が増加する。逆に、電流設定用抵抗素子 R T に流れる電流が大きく印加電圧が高いときには、電圧増幅器 A M P 2 の出力電圧は減少しトランジスタ Q 1 のベース電流を減少させる。トランジスタ Q 1 のベース電流が減少するとトランジスタ Q 1 のエミッタ電流も減少して電流設定用抵抗素子 R T に流れる電流が減少する。これにより、電流設定用抵抗素子 R T に印加される電圧は、基準電圧に一致する。

10

#### 【 0 0 5 0 】

電流設定用抵抗素子 R T に印加される電圧に基づいてバイアス電流が決定される。バイアス電流は、トランジスタ Q 1 を介してトランジスタ Q 2 および Q 3 で構成されるカレントミラー回路に流れ、トランジスタ Q 3 から出力される。出力されたバイアス電流は周波数設定用容量素子 C T を充電することにより、出力端子の電圧レベルを時間と共に上昇させる。定常動作状態ではバイアス電流は所定電流値に維持されるので、発振信号 C K は所定の傾きで直線的に増加する波形となる。電圧比較器 C O M P 2 により、出力端子の電圧値がピーク電圧 V H に達することによりトランジスタ Q 4 が導通し、出力端子を接地電位に引き抜く。出力端子が接地電位まで引き抜かれると、電圧比較器 C O M P 2 の出力電圧が反転しトランジスタ Q 4 が非導通となるので、再度、バイアス電流による周波数設定用容量素子 C T の充電が開始される。これを繰り返すことにより発振信号 C K が出力される。出力端子から出力される発振信号 C K は、図 3 に示すように、鋸波状の波形となる。ここで、発振信号 C K の発振周波数は、周波数設定用容量素子 C T の容量値、および発振信号 C K のピーク電圧 V H が共に固定であるので、バイアス電流に比例する周波数となる。定常動作状態では、一定の発振周波数を持って発振する波形が得られる。

20

#### 【 0 0 5 1 】

D C - D C コンバータが起動されると、スイッチ回路 S W 1 1 が導通して容量素子 C S 1 は定電流回路 I 1 により充電が開始される。容量素子 C S 1 の充電の初期段階では、容量素子 C S 1 の端子電圧 V C S は、定常設定電圧 e 1 1 に比して低い電圧レベルにある。このため、バッファ部は、端子電圧 V C S を電流設定用抵抗素子 R T に印加する。

30

#### 【 0 0 5 2 】

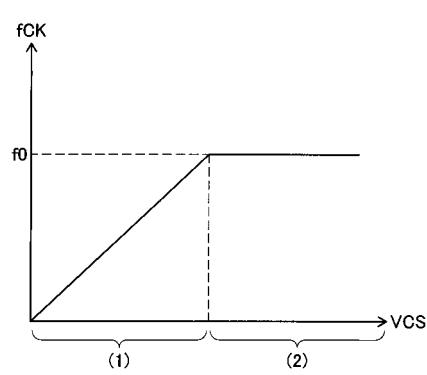

容量素子 C S 1 は定電流回路 I 1 により徐々に充電されるので、端子電圧 V C S は徐々に高い電圧レベルに上昇する。電圧増幅器 A M P 2 およびトランジスタ Q 1 により、徐々に上昇する端子電圧 V C S に応じて電流設定用抵抗素子 R T に略同一の電圧が印加される。起動に伴う容量素子 C S 1 への充電動作により、電流設定用抵抗素子 R T への印加電圧が漸次増大しバイアス電流が漸次増加する。したがって、発振信号 C K の発振周波数は、起動指令後の時間経過に伴い漸次増加する。図 4 に示す発振周波数特性において、( 1 ) の領域を発振周波数の増加方向に推移する。

40

#### 【 0 0 5 3 】

端子電圧 V C S が定常設定電圧 e 1 1 の電圧レベルを越えると、電流設定用抵抗素子 R T への印加電圧は定常設定電圧 e 1 1 に維持される。これにより、定常動作状態においては、バイアス電流は定常設定電圧 e 1 1 に応じた電流値となる。したがって、発振信号 C K の発振周波数は、固定される。図 4 に示す発振周波数特性において、( 2 ) の領域である周波数 f 0 となる。尚、周波数 f 0 による発振周期が、第 1 周期の一例である。

#### 【 0 0 5 4 】

D C - D C コンバータの動作が停止されると、スイッチ回路 S W 1 2 が導通して容量素子 C S 1 は放電用抵抗素子 R D 1 を介して放電が開始される。容量素子 C S 1 の放電の初期段階では、端子電圧 V C S は定常設定電圧 e 1 1 に比して高い電圧レベルにある。電流

50

設定用抵抗素子 R T に印加される電圧は定常設定電圧  $e_{11}$  に維持される。バイアス電流は定常動作状態と同じ固定された電流値である。したがって、発振信号 C K の発振周波数は、図 4 に示す発振周波数特性において、(2) の領域である周波数  $f_0$  となる。

#### 【0055】

容量素子 C S 1 の放電が進むと、端子電圧 V C S が定常設定電圧  $e_{11}$  を下回って徐々に下降する。徐々に下降する端子電圧 V C S に応じて電流設定用抵抗素子 R T に略同一の電圧が印加される。電流設定用抵抗素子 R T への印加電圧が漸次下降し、バイアス電流が漸次下降する。したがって、発振信号 C K の発振周波数は、停止指令後の時間経過に伴い漸次減少する。図 4 に示す発振周波数特性において、(1) の領域を発振周波数の減少方向に推移する。

10

#### 【0056】

第 1 実施形態の D C - D C コンバータの制御回路 10 においては、起動指令に伴い、発振回路 OSC から出力される発振信号 C K の発振周波数が漸次増加していく。同様に、停止指令に伴い、発振回路 OSC から出力される発振信号 C K の発振周波数が漸次減少していく。これにより、D C - D C コンバータにおいて電流制御型の制御が行なわれ、発振信号 C K の毎周期ごとにフロップフロップ回路 F F がセットされて M O S ランジスタ F E T 1 が導通状態とされる場合にも、D C - D C コンバータの起動 / 停止指令後の一定期間において、セット動作の時間間隔を長くすることができる。遷移期間中に必要以上にセット動作が繰り返されることが抑制され、不必要的電極供給が抑制されることにより、出力電圧 V O U T の滑らかな遷移を実現することができる。

20

#### 【0057】

第 1 実施形態では、発振信号 C K の発振周波数の設定用に専用の容量素子 C S 1 、および専用の充放電回路（定電流回路 I 1 、抵抗素子 R D 1 、スイッチ回路 S W 1 1 、 S W 1 2 ）を備えているので、出力電圧 V O U T の遷移状況に応じて最適な発振周波数の遷移に調整することができる。

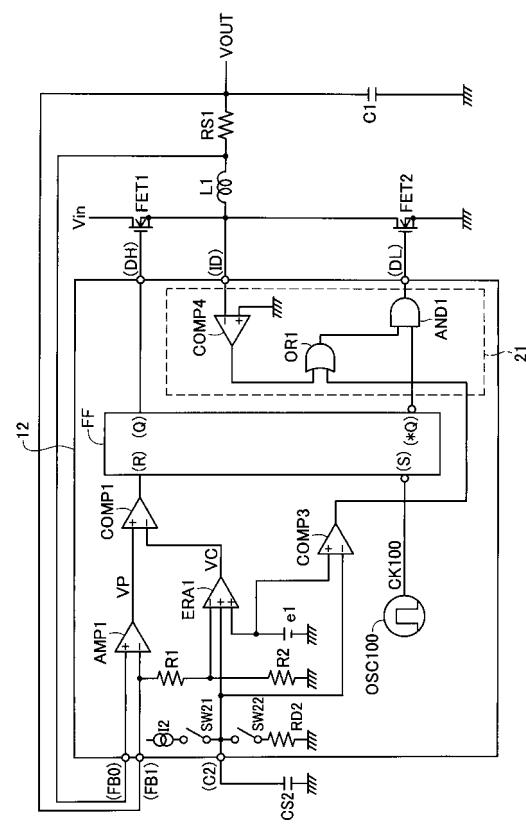

#### 【0058】

図 5 は第 1 実施形態の変形例である。第 1 実施形態（図 1 ）に備えられている専用の容量素子 C S 1 、および専用の充放電回路（定電流回路 I 1 、抵抗素子 R D 1 、スイッチ回路 S W 1 1 、 S W 1 2 ）に代えて、ソフトスタート用コンデンサ C S 2 の端子電圧を利用したものである。停止指令による出力電圧 V O U T の立ち上げ、停止指令による出力電圧 V O U T の立ち下げは、ソフトスタート用容量素子 C S 2 を漸次、充放電することにより得られる端子電圧で決定している。この端子電圧を利用すれば、発振信号 C K における、起動時の発振周波数の漸次増加、および停止時の発振周波数の漸次減少を実現することができる。

30

#### 【0059】

発振信号 C K の発振周波数の制御を、ソフトスタート用容量素子 C S 2 で代用することにより、回路構成を減らすことができ、低消費電流を図ることができる。

#### 【0060】

図 6 は、電流制御型 D C - D C コンバータにおいて同期整流方式で動作させる場合、D C - D C コンバータの起動時および停止時に、同期整流素子における電流の逆流を許可することで、出力電圧 V O U T の電圧遷移を制御する回路例である。起動時や停止時にも発振信号 C K の発振周波数を低減することなく、出力電圧 V O U T を滑らかにランプ制御する回路例である。

40

#### 【0061】

図 6 の回路例では、図 8 の背景技術の回路図に加えて、非反転入力端子に基準電圧  $e_1$  が入力され、反転入力端子にソフトスタート用容量素子 C S 2 の端子電圧が入力された電圧比較器 C O M P 3 と、同期整流制御回路 21 とを備えて構成されている。更に、M O S ランジスタ F E T 1 と F E T 2 との接続点が接続されている電流検出端子（ I D ）を備えている。

#### 【0062】

50

同期整流制御回路 21 は、反転入力端子に電流検出端子 (ID) が接続され、非反転入力端子に接地電位が接続された電圧比較器 COMP4 と、電圧比較器 COMP3 および COMP4 の出力信号が入力される論理和ゲート OR1 と、論理和ゲート OR1 の出力信号とフリップフロップ回路 FF の反転出力端子 (\*Q) からの出力信号とが入力される論理積ゲート AND1 とが備えられている。論理積ゲートの出力端子は出力端子 (DL) に接続されている。

#### 【0063】

同期整流素子であるMOSトランジスタFET2は、論理積ゲートAND1の出力信号がハイレベルであるとき導通する。これは、論理積ゲートAND1に入力されている2つの入力信号が共にハイレベルである場合である。電圧比較器COMP3またはCOMP4の出力信号のうち少なくともいずれか一方がハイレベルである状態で、フリップフロップ回路FFがリセット状態となり反転出力端子(\*Q)からハイレベルの信号が出力される場合である。10

#### 【0064】

ここで、電圧比較器COMP3の出力信号がハイレベルである場合とは、ソフトスタート用容量素子CS2の端子電圧が基準電圧e1に比して低い電圧レベルである場合である。DC-DCコンバータの起動時または停止時にソフトスタート用容量素子CS2が充放電されている遷移期間である。

#### 【0065】

また、電圧比較器COMP4の出力信号がハイレベルである場合とは、反転入力端子が負電圧である場合である。MOSトランジスタFET2が同期整流素子として導通している期間である。20

#### 【0066】

電流制御型DC-DCコンバータは、発振器OSC100からの発振信号CK100の毎周期ごとにMOSトランジスタFET1が強制的に導通され、入力電圧VINから出力電圧VOUTに対して無条件に電力が供給される。特に負荷が軽い場合に出力電圧VOUTが必要以上に上昇してしまうことがある。

#### 【0067】

そこで、入力電圧VINから出力電圧VOUTに必要以上に供給された電力を、入力電圧VINに回生させることで、DC-DCコンバータの起動時や停止時の出力電圧VOUTのランプ制御を滑らかにすることができます。30

#### 【0068】

電圧比較器COMP3は、ソフトスタート用容量素子CS2の端子電圧が基準電圧e1よりも低く、起動動作から定常動作状態への出力電圧VOUTの遷移期間、また、停止動作に伴う定常動作状態時から停止までの出力電圧VOUTの遷移期間において、同期整流素子であるMOSトランジスタFET2の電流の逆流するのを許可する。

#### 【0069】

フリップフロップ回路FFがセットされてからリセットされるまでの時間、チョークコイルL1にエネルギーが蓄積される。MOSトランジスタFET1が非導通とされると、チョークコイルL1に蓄積されたエネルギーはMOSトランジスタFET2を介して出力側に放出される。負荷に電力供給されると共に、平滑コンデンサC1に電荷が蓄積されて、出力電圧VOUTが上昇する。出力電圧VOUTに接続されている負荷が無負荷状態等の軽い場合、チョークコイルL1に蓄えられたエネルギーは、全て平滑コンデンサC1に蓄積されて出力電圧VOUTを上昇させるだけに使用される。チョークコイルL1から平滑コンデンサC1へのエネルギーの移動により、平滑コンデンサC1の電圧値(出力電圧VOUT)がピーク値に達するのは、チョークコイルL1のインダクタンス値と平滑コンデンサC1の容量値で決まる共振周波数の1/4の時間である。40

#### 【0070】

MOSトランジスタFET2の逆流が許可されている場合、共振周波数の1/4の時間が経過して平滑コンデンサC1の電圧がピーク値に達した後、MOSトランジスタFET50

2に、通常の同期整流方向とは逆方向の電流が流れ始め、平滑コンデンサC1のエネルギーはチョークコイルL1に戻り始める。この後、MOSトランジスタFET2が非導通となると、チョークコイルL1に蓄積されたエネルギーは、MOSトランジスタFET1のボディーダイオードを介して入力電圧VINに戻される。これにより、必要以上に供給されたエネルギーが入力電圧VINに回生させることができる。DC-DCコンバータの負荷が軽い状態でも、DC-DCコンバータの出力電圧VOUTが必要に上昇することなく、出力電圧VOUTを滑らかに遷移させる制御が可能となる。

#### 【0071】

以上詳細に説明したとおり、本実施形態に係る電流制御型DC-DCコンバータの制御回路10によれば、DC-DCコンバータの主スイッチ素子であるMOSトランジスタFET1は、フリップフロップ回路FFによりスイッチング制御される。フリップフロップ回路FFのセット端子(S)には発振回路OSCが接続され、発振信号CKの周期ごとにフリップフロップ回路FFがセットされてMOSトランジスタFET1が導通状態とされる。発振回路OSCから出力される発振信号CKは、DC-DCコンバータが停止状態と定常動作状態との間の遷移状態にある場合、発振周波数が、DC-DCコンバータの出力電圧VOUTの電圧値の増減に合わせて漸次増減する。

#### 【0072】

また、本実施形態に係る電流制御型DC-DCコンバータの制御方法によれば、DC-DCコンバータの主スイッチ素子であるMOSトランジスタFET1は、所定周期ごとに導通状態にセットされる。定常動作状態においては、所定周期は第1周期である周波数f0とされ、定常動作状態と停止状態との間の遷移状態においては、所定周期は、第1周期(周波数f0)を最短周期として、DC-DCコンバータの出力電圧VOUTの電圧値の増減に合わせて漸次減増する。

#### 【0073】

発振信号CKの毎周期ごとにMOSトランジスタFET1が導通状態にセットされる電流制御型の制御であっても、起動指令により出力電圧VOUTが漸次上昇する過程で発振信号CKの発振周波数が漸次上昇し、または/および停止指令により出力電圧VOUTが漸次下降する過程で発振信号CKの発振周波数が漸次下降するので、停止状態と定常動作状態との間の遷移状態にある場合に、MOSトランジスタFET1が導通状態にセットされる時間間隔を長くすることができる。出力電圧VOUTに対して過度な電力が供給されることなく、出力電圧VOUTを滑らかなランプ波形とすることができます。

#### 【0074】

尚、本発明は前記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内で種々の改良、変形が可能であることは言うまでもない。

例えば、本実施形態においては、容量素子CS1を備えて発振回路OSCが構成される場合について説明したが、制御端子を備えておき、容量素子を外付けとすることもできる。容量素子を外付けとすれば、発振信号CKにおける発振周波数の漸次な増減を自在に調整することができる。この場合、容量素子を外付けすることに代えて、外部の制御回路などから制御電圧を直接入力する構成とすることも可能である。

また、容量素子CS1を充放電する充電電流部として定電流回路I1を備え、放電電流部として放電用抵抗素子RD1を備える場合について説明したが、本発明はこれに限定されるものではない。定電流回路I1に代え、また定電流回路I1と共に、抵抗素子を備え、放電用抵抗素子RD1に代え、また放電用抵抗素子RD1と共に、停電流回路を備える構成とすることもできる。

#### 【0075】

ここで、本発明の技術思想により、背景技術における課題を解決するための手段を以下に列記する。

(付記1) DC-DCコンバータの周期的なスイッチング制御のタイミングを指令する発振回路を備え、

前記発振回路は、前記スイッチング制御が停止状態と定常動作状態との間の遷移状態で

10

20

30

40

50

あって、時間経過に伴い前記DC - DCコンバータの出力電圧値が上昇していく遷移状態にあっては発振周波数を漸次増大し、時間経過に伴い前記DC - DCコンバータの出力電圧値が下降していく遷移状態にあっては発振周波数を漸次減少することを特徴とする電流制御型DC - DCコンバータの制御回路。

(付記2) 前記DC - DCコンバータの主スイッチ素子をスイッチング制御するフリップフロップ回路を備え、

前記発振回路から出力される発振信号は、前記フリップフロップ回路のセット端子に入力されることを特徴とする付記1に記載の電流制御型DC - DCコンバータの制御回路。

(付記3) 起動指令に応じて端子電圧が漸次上昇し、停止指令に応じて端子電圧が漸次下降する電圧信号が入力される制御端子と、

前記制御端子の端子電圧に応じて、前記発振回路の発振周波数を設定する周波数設定部と

を備えることを特徴とする付記1に記載の電流制御型DC - DCコンバータの制御回路。

(付記4) 前記制御端子に対して電流出力を行なう第1電流部と、

前記起動指令に応じて、前記第1電流部を介して前記制御端子までの電流経路を確立する第1スイッチ回路と、

前記制御端子に対して電流引き込みを行なう第2電流部と、

前記停止指令に応じて、前記第2電流部を介して前記制御端子までの電流経路を確立する第2スイッチ回路と

を備えることを特徴とする付記3に記載の電流制御型DC - DCコンバータの制御回路。

(付記5) 前記第1電流部または／および前記第2電流部は、定電流源回路または／および抵抗素子を備えることを特徴とする付記4に記載の電流制御型DC - DCコンバータの制御回路。

(付記6) 前記周波数設定部は、

前記制御端子の端子電圧に応じた電圧を出力するバッファ部と、

前記バッファ部の出力電圧に応じたバイアス電流を設定する電流設定部と

を備えることを特徴とする付記3に記載の電流制御型DC - DCコンバータの制御回路。

(付記7) 前記バッファ部は、

前記制御端子の端子電圧が入力される第1の非反転入力端子と、

前記定常動作状態における発振周波数を設定する定常設定電圧が入力される第2の非反転入力端子と

を備え、

前記バッファ部は、前記第1および第2の非反転入力端子に入力される電圧のうち低い電圧値を出力することを特徴とする付記6に記載の電流制御型DC - DCコンバータの制御回路。

(付記8) 前記発振回路は、

起動指令に応じて漸次充電されて端子電圧が漸次上昇し、停止指令に応じて漸次放電されて前記端子電圧が漸次下降する第1容量素子と、

前記第1容量素子の端子電圧に応じて、発振周波数を設定する周波数設定部と

を備えることを特徴とする付記1に記載の電流制御型DC - DCコンバータの制御回路。

(付記9) 前記第1容量素子に対して充電を行なう充電電流部と、

前記起動指令に応じて、前記充電電流部を介して前記第1容量素子への充電経路を確立する第1スイッチ回路と、

前記第1容量素子に対して放電を行なう放電電流部と、

前記停止指令に応じて、前記放電電流部を介して前記第1容量素子からの放電経路を確立する第2スイッチ回路と

を備えることを特徴とする付記8に記載の電流制御型DC - DCコンバータの制御回路。

10

20

30

40

50

。

(付記 10) 前記充電電流部または / および前記放電電流部は、定電流源回路または / および抵抗素子を備えることを特徴とする付記 9 に記載の電流制御型 D C - D C コンバータの制御回路。

(付記 11) 前記周波数設定部は、

前記第 1 容量素子の端子電圧に応じた電圧を出力するバッファ部と、

前記バッファ部の出力電圧に応じたバイアス電流を設定する電流設定部と

を備えることを特徴とする付記 8 に記載の電流制御型 D C - D C コンバータの制御回路

。

(付記 12) 前記バッファ部は、

10

前記第 1 容量素子の端子電圧が入力される第 1 の非反転入力端子と、

前記定常動作状態における発振周波数を設定する定常設定電圧が入力される第 2 の非反転入力端子と

を備え、

前記バッファ部は、前記第 1 および第 2 の非反転入力端子に入力される電圧のうち低い電圧値を出力することを特徴とする付記 11 に記載の電流制御型 D C - D C コンバータの制御回路。

(付記 13)

20

周期的なスイッチング制御のタイミングを指令する発振回路を備え、

前記発振回路は、前記スイッチング制御が停止状態と定常動作状態との間の遷移状態であって、時間経過に伴い出力電圧値が上昇していく遷移状態にあっては発振周波数を漸次増大し、時間経過に伴い出力電圧値が下降していく遷移状態にあっては発振周波数を漸次減少することを特徴とする電流制御型 D C - D C コンバータ。

(付記 14) 主スイッチ素子と、

前記主スイッチング素子をスイッチング制御するフリップフロップ回路とを備え、

前記発振回路から出力される発振信号は、前記フリップフロップ回路のセット端子に入力されることを特徴とする付記 13 に記載の電流制御型 D C - D C コンバータ。

(付記 15) 前記発振回路は、

起動指令に応じて漸次充電されて端子電圧が漸次上昇し、停止指令に応じて漸次放電されて前記端子電圧が漸次下降する第 1 容量素子と、

30

前記第 1 容量素子の端子電圧に応じて、前記発振回路の発振周波数を設定する周波数設定部と

を備えることを特徴とする付記 13 に記載の電流制御型 D C - D C コンバータ。

(付記 16) 前記第 1 容量素子に対して充電を行なう充電電流部と、

前記起動指令に応じて、前記充電電流部を介して前記第 1 容量素子への充電経路を確立する第 1 スイッチ回路と、

前記第 1 容量素子に対して放電を行なう放電電流部と、

前記停止指令に応じて、前記放電電流部を介して前記第 1 容量素子からの放電経路を確立する第 2 スイッチ回路と

を備えることを特徴とする付記 13 に記載の電流制御型 D C - D C コンバータ。

40

(付記 17) 前記充電電流部または / および前記放電電流部は、定電流源回路または / および抵抗素子を備えることを特徴とする付記 16 に記載の電流制御型 D C - D C コンバータ。

(付記 18) 前記周波数設定部は、

前記第 1 容量素子の端子電圧に応じた電圧を出力するバッファ部と、

前記バッファ部の出力電圧に応じたバイアス電流を設定する電流設定部と

を備えることを特徴とする付記 15 に記載の電流制御型 D C - D C コンバータ。

(付記 19) 前記バッファ部は、

前記第 1 容量素子の端子電圧が入力される第 1 の非反転入力端子と、

前記定常動作状態における発振周波数を設定する定常設定電圧が入力される第 2 の非反

50

転入力端子と

を備え、

前記バッファ部は、前記第1および第2の非反転入力端子に入力される電圧のうち低い電圧値を出力することを特徴とする付記18に記載の電流制御型DC-DCコンバータ。

(付記20) 周期的なスイッチング制御が行なわれる電流制御型DC-DCコンバータの制御方法であって、

定常動作状態において、第1周期でスイッチング制御を行なうステップと、

前記スイッチング制御が停止状態と定常動作状態との間の遷移状態であって、時間経過に伴い出力電圧値が上昇していく遷移状態にあっては、前記第1周期を最短周期として、発振周期を漸次増大し、時間経過に伴い出力電圧値が下降していく遷移状態にあっては、前記第1周期を最短周期として、発振周期を漸次減少するステップと

を有することを特徴とする電流制御型DC-DCコンバータの制御方法。

【図面の簡単な説明】

【0076】

【図1】第1実施形態の回路図である。

【図2】発振回路の具体例である。

【図3】発振信号CKの波形図である。

【図4】発振回路の発振周波数特性を示す図である。

【図5】第1実施形態の変形例を示す回路図である。

【図6】出力電圧のランプ制御を行なう別案の回路図である。

【図7】背景技術の回路図(電圧制御型)である。

【図8】背景技術の回路図(電流制御型)である。

【図9】図8において起動時の出力波形のランプ波形を示す図である。

【符号の説明】

【0077】

10 制御回路

21 同期整流制御回路

(C2) ソフトスタート端子

(DH)、(DL) 出力端子

(FB0)、(FB1) 入力端子

(ID) 電流検出端子

AMP1、AMP2 電圧増幅器

C1 平滑コンデンサ

COMP1、COMP2、COMP3 電圧比較器

CS1 容量素子

CS2 ソフトスタート用容量素子

CT 周波数設定用容量素子

ERA1 誤差増幅器

FET1、FET2 MOSトランジスタ

FF フリップフロップ回路

FSET 周波数設定部

I1、I2 定電流回路

L1 チョークコイル

OSC 発振回路

RD1、RD2 放電用抵抗素子

RS1 電流測定抵抗

RT 電流設定用抵抗素子

SW11、SW12、SW21、SW22 スイッチ回路

VOUT 出力端子

e1 基準電圧

10

20

30

40

50

e 1 1 定常設定電圧

CK 発振信号

VCS 容量素子 C S 1 の端子電圧 V C S

VH ピーク電圧

VIN 入力電圧

【図 1】

第1実施形態の回路図

【図 2】

発振回路の具体例

【図3】

発振信号CKの波形

【図4】

発振回路の発振周波数特性

【図5】

第1実施形態の変形例

【図6】

出力電圧のランプ制御を行なう別案回路図

【図7】

背景技術の回路図(電圧制御型)

【図8】

背景技術の回路図(電流制御型)

【図9】

図8において起動時の出力電圧ランプ波形

---

フロントページの続き

(56)参考文献 特開昭62-268359(JP,A)

特開2005-045856(JP,A)

特開平11-356053(JP,A)

国際公開第2004/006630(WO,A1)

特開2003-274643(JP,A)

特開2002-171750(JP,A)

特開2002-354801(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155