(12)

## Patentschrift

(21) Deutsches Aktenzeichen: 11 2018 003 635.9

(86) PCT-Aktenzeichen: PCT/IB2018/057444

(87) PCT-Veröffentlichungs-Nr.: WO 2019/064193

(86) PCT-Anmelddatum: 26.09.2018

(87) PCT-Veröffentlichungstag: 04.04.2019

(43) Veröffentlichungstag der PCT Anmeldung

in deutscher Übersetzung: 16.04.2020

(45) Veröffentlichungstag

der Patenterteilung: 06.05.2021

(51) Int Cl.: **H01R 12/52 (2011.01)**

**H01L 23/64 (2006.01)**

**H01R 33/76 (2006.01)**

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

|                                                                                             |                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (30) Unionspriorität:<br><b>15/717,978</b> 28.09.2017 US                                    | (72) Erfinder:<br><b>Hejase, Jose Ale, Austin, TX, US; Becker, Wiren, Poughkeepsie, NY, US; Dreps, Daniel, Austin, Tex., US; Chun, Sungjun, Poughkeepsie, NY, US; Beaman, Brian, Research Triangle Park, NC, US</b> |

| (73) Patentinhaber:<br><b>International Business Machines Corporation, Armonk, N.Y., US</b> | (56) Ermittelter Stand der Technik:<br><b>US 2018 / 0 019 558 A1</b>                                                                                                                                                |

| (74) Vertreter:<br><b>Richardt Patentanwälte PartG mbB, 65185 Wiesbaden, DE</b>             |                                                                                                                                                                                                                     |

(54) Bezeichnung: **HYBRIDKONTAKTFLÄCHENGITTER-ARRAY-VERBINDER FÜR VERBESSERTE SIGNALINTEGRITÄT UND ENTSPRECHENDES FERTIGUNGSVERFAHREN**

(57) Hauptanspruch: Verfahren, wobei das Verfahren aufweist:

Bereitstellen eines Körpers (102) für einen Hybridkontakteflächengitter-Array-Verbinder, wobei der Körper (102) eine erste Mehrzahl von Löchern (104) und eine zweite Mehrzahl von Löchern (106, 402) enthält;

Abscheiden einer leitfähigen Schicht (208, 210) auf einer oberen Fläche des Körpers (102), einer unteren Fläche des Körpers (102) und auf Wandflächen der ersten Mehrzahl von Löchern (104), wobei die obere Fläche des Körpers (102) mit der unteren Fläche des Körpers (102) elektrisch übereinstimmt;

Entfernen der leitfähigen Schicht (208, 210) von Wandflächen eines ersten Teilsatzes (202) der ersten Mehrzahl von Löchern (104); und

Entfernen eines Abschnitts der leitfähigen Schicht (208, 210) auf der oberen Fläche des Körpers (102) und der unteren Fläche des Körpers (102) aus einem Bereich (206), der den ersten Teilsatz (202) der ersten Mehrzahl von Löchern (104) umgibt.

**Beschreibung****HINTERGRUND**

**[0001]** Die vorliegende Erfindung bezieht sich allgemein auf das Gebiet von Verbindern und im Besonderen auf Hybridkontakteflächengitter-Array(Land Grid Array)-Verbinder für verbesserte Signalintegritätseigenschaften.

**[0002]** Ein Hybridkontakteflächengitter-Array(HLGA)-Verbinder stellt eine Verbindung zwischen einem Chip-Trägergehäuse (z.B. einem Gehäuse einer Zentraleinheit (central processing unit) oder CPU) und einer Leiterplatte (printed circuit board, PCB) bereit. Das HLGA, das über Kugeln eines Kugelgitter-Arrays (ball grid array, BGA) auf die PCB gelötet wird, enthält Federkontakte, die mit den Chip-Trägerkontakteflächen zusammenpassen, die mit Nickel und Gold plattierte sind und die eine elektrische Verbindung zwischen dem Chip-Trägergehäuse und der PCB bereitstellen. Das Chip-Trägergehäuse wird in dem HLGA platziert und wird durch einen Federmechanismus festgehalten. Falls das Chip-Trägergehäuse nicht korrekt funktioniert, ermöglicht das HLGA einen einfachen Austausch des nicht funktionierenden Chip-Trägergehäuses vor Ort, ohne die gesamte PCB austauschen zu müssen.

**[0003]** Die US 2018 / 0 019 558 A1 offenbart Sockelkontaktetechniken und -konfigurationen mit einem Buchsensubstrat, das eine erste Seite und eine zweite Seite aufweist, die gegenüber der ersten Seite angeordnet ist, einer Öffnung, die durch das Buchsensubstrat gebildet ist, und einem elektrischen Kontakt, der in der Öffnung angeordnet ist und konfiguriert ist, um elektrische Signale zwischen der ersten Seite und der zweiten Seite des Buchsensubstrats zu leiten, wobei der elektrische Kontakt einen freitragenden Abschnitt aufweist, der sich über die erste Seite hinaus erstreckt, wobei die erste Seite und die Oberflächen des Buchsensubstrats in der Öffnung mit einem Metall plattierte sind.

**KURZDARSTELLUNG DER ERFINDUNG**

**[0004]** Ausführungsformen der vorliegenden Erfindung enthalten ein Verfahren zum Fertigen eines Hybridkontakteflächengitter-Array-Verbinder und der resultierenden Strukturen. Das Verfahren kann ein Bereitstellen eines Körpers enthalten, der eine erste Mehrzahl von Löchern und eine zweite Mehrzahl von Löchern enthält. Das Verfahren kann darüber hinaus ein Abscheiden einer leitfähigen Schicht auf der oberen und der unteren Fläche des Körpers und den Wandflächen der ersten Mehrzahl von Löchern enthalten, was dazu führt, dass die obere und die untere Fläche elektrisch übereinstimmen. Das Verfahren kann darüber hinaus ein Entfernen der leitfähigen Schicht von den Wandflächen eines ersten Teilsatzes

der ersten Mehrzahl von Löchern enthalten. Das Verfahren kann darüber hinaus ein Entfernen eines Abschnitts der leitfähigen Schicht von der oberen Fläche des Körpers und der unteren Fläche des Körpers aus einem Bereich enthalten, der den ersten Teilsatz der ersten Mehrzahl von Löchern umgibt.

**Figurenliste**

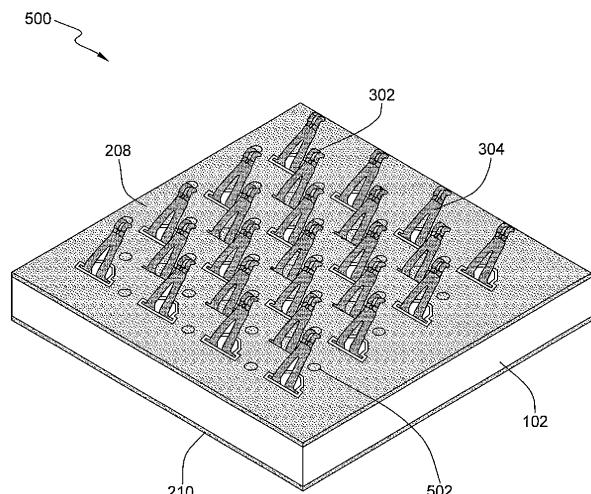

**Fig. 1** stellt einen beispielhaften Körper eines Hybridkontakteflächengitter-Array(HLGA)-Verbinder, der mit Löchern für plattierte Durchkontakte und mit Löchern für Federkontakte versehen ist, gemäß einer Ausführungsform der vorliegenden Erfindung dar;

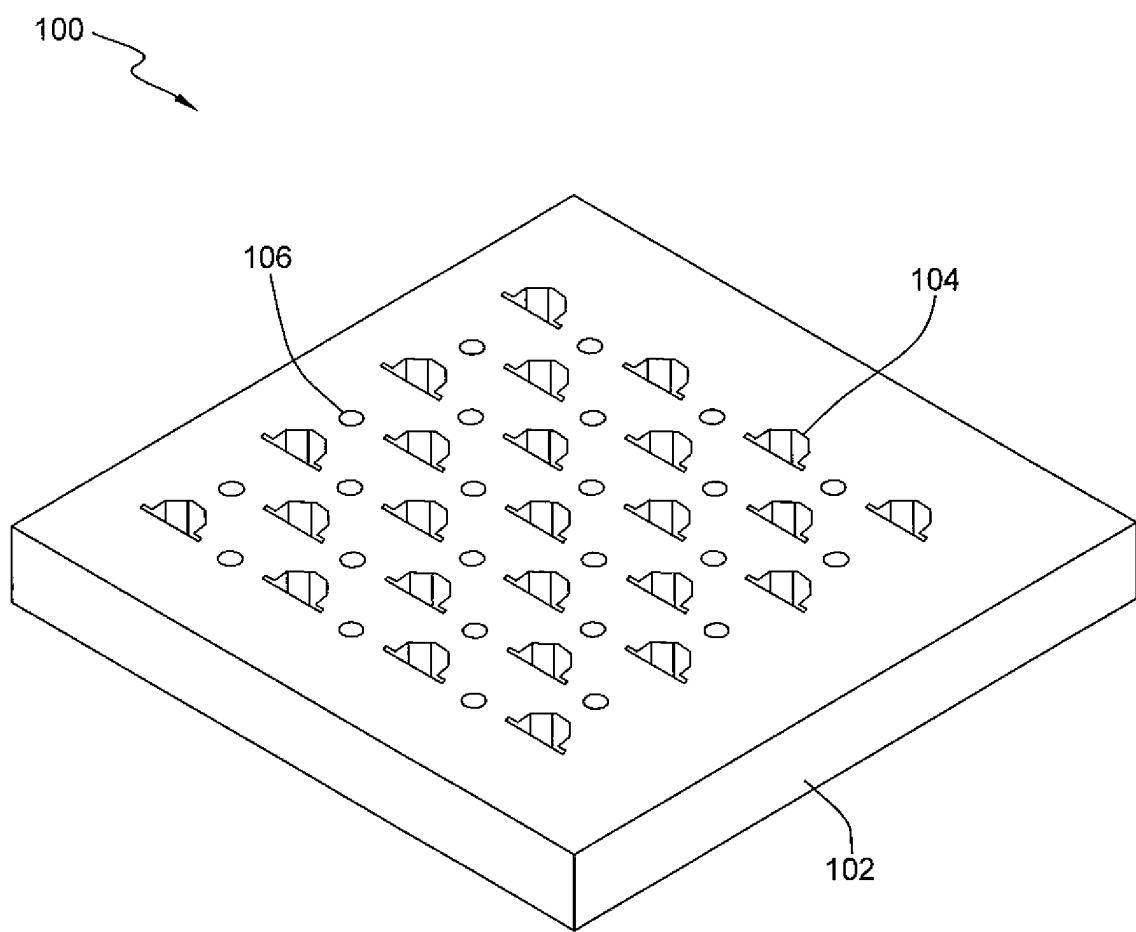

**Fig. 2** stellt den HLGA-Verbinderkörper von **Fig. 1** nach Fertigungsschritten zum Plattieren und Ätzen gemäß einer Ausführungsform der vorliegenden Erfindung dar;

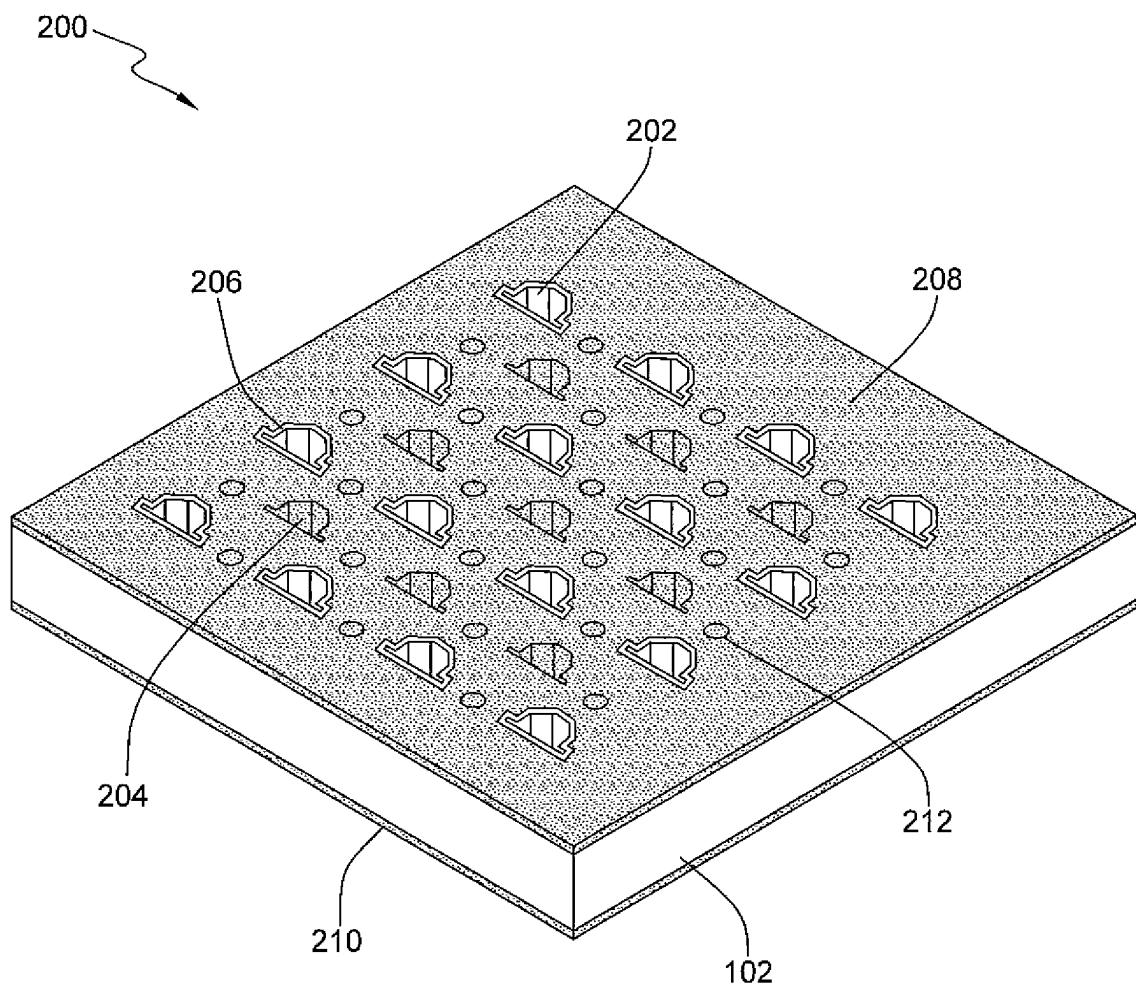

**Fig. 3** stellt den HLGA-Verbinderkörper von **Fig. 2** nach dem Einbau der Signalfederkontakte und von Massefederkontakte gemäß einer Ausführungsform der vorliegenden Erfindung dar;

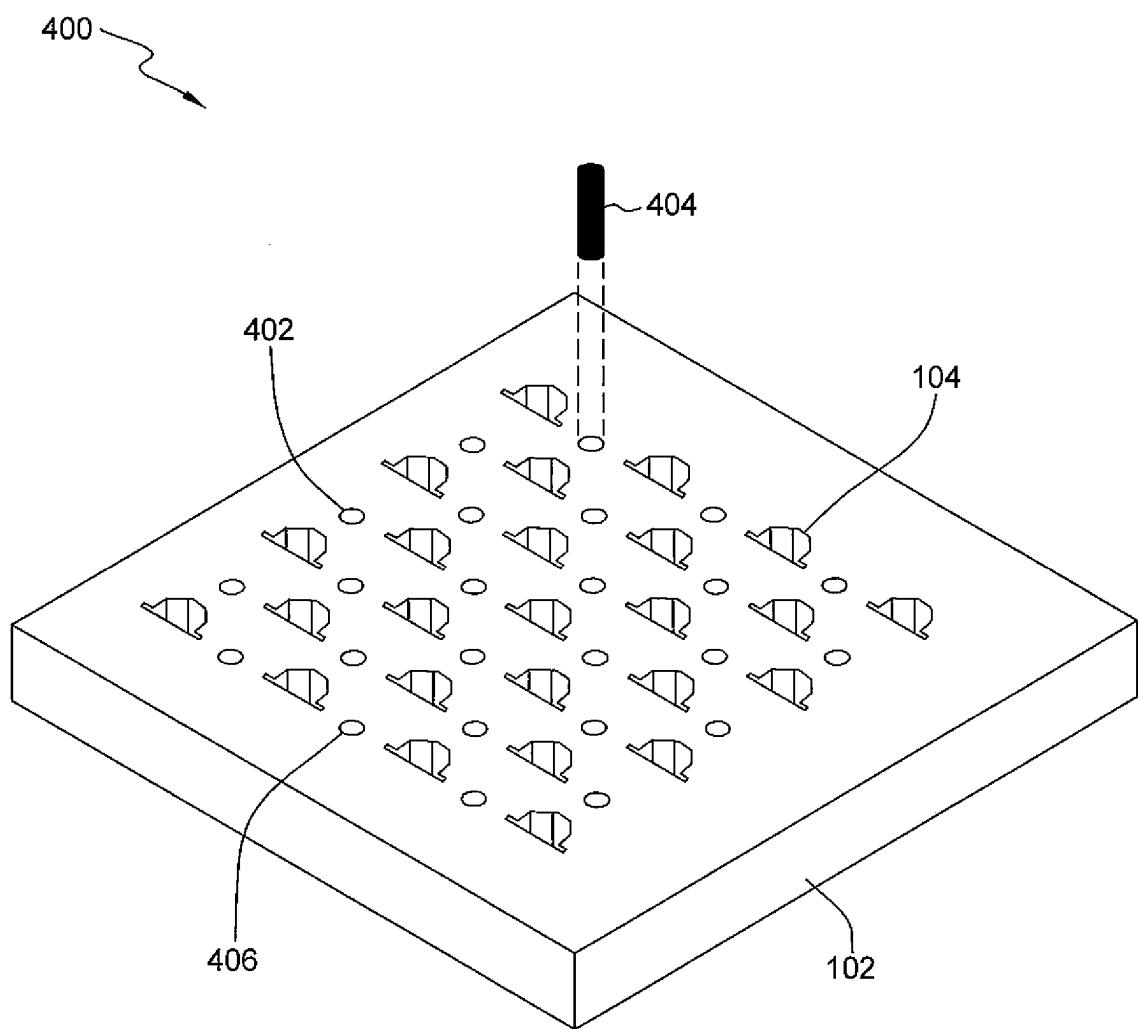

**Fig. 4** stellt einen beispielhaften HLGA-Verbinderkörper, der mit Löchern für leitfähige Stifte und mit Löchern für Federkontakte versehen ist, gemäß einer Ausführungsform der vorliegenden Erfindung dar; und

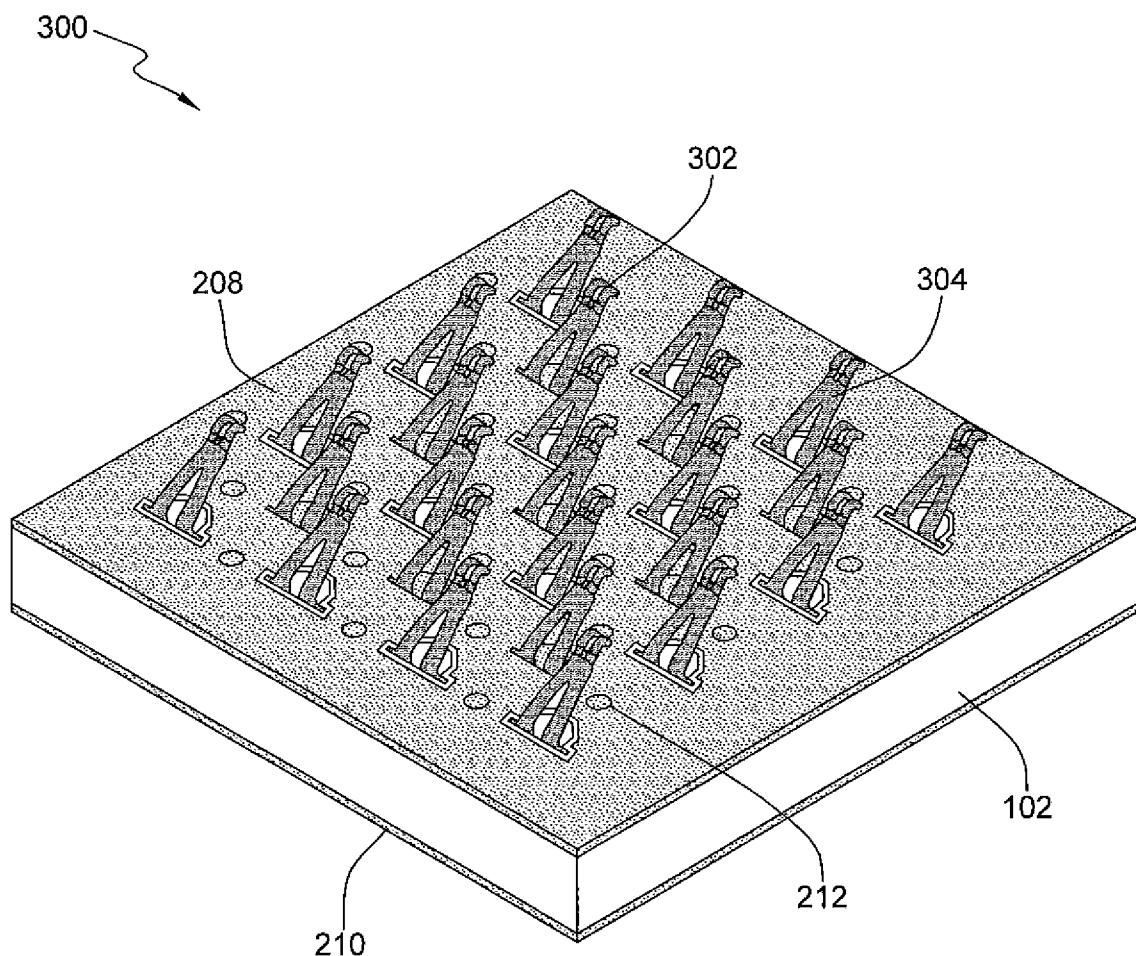

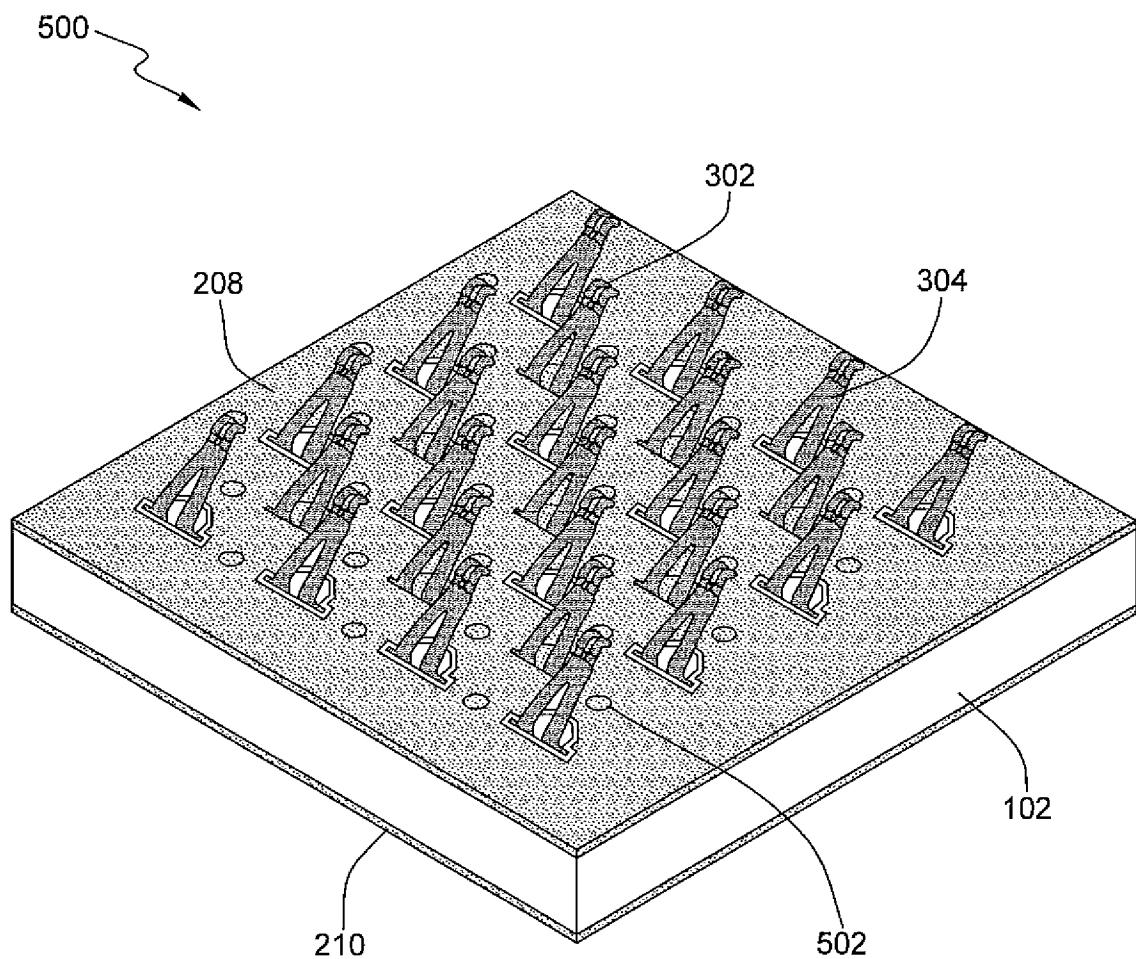

**Fig. 5** stellt den HLGA-Verbinderkörper von **Fig. 4** nach dem Einbau der plattierten leitfähigen Stifte, der Signalfederkontakte und der Massefederkontakte gemäß einer Ausführungsform der vorliegenden Erfindung dar.

**AUSFÜHRLICHE BESCHREIBUNG**

**[0005]** Ausführungsformen der vorliegenden Erfindung stellen einen Hybridkontakteflächengitter-Array (HLGA)-Verbinder für eine verbesserte Signalintegrität bereit. Bei der Verwendung wird ein HLGA-Verbinder auf Kontaktflächen auf einer Leiterplatte (PCB) gelötet. Die Verbindung wird zwischen Kugelgitter-Array(BGA)-Kugeln auf dem HLGA und Kupferkontakteflächen auf der PCB hergestellt. Ein Chip-Trägergehäuse (z.B. eine Zentraleinheit oder CPU) wird in das HLGA eingesetzt und durch eine Federklemmanordnung sicher festgehalten. Der HLGA-Verbinder enthält Metallfederkontakte, die in einem Kunststoffkörper montiert sind, die eine elektrische Verbindung zwischen der CPU und der PCB bereitstellen. Beispielsweise werden elektrische Signale von einer ersten CPU durch ein erstes HLGA in die PCB, durch ein zweites HLGA und zu einer zweiten CPU übertragen. Die elektrischen Signale können gedämpft werden, Rauschen und Übersprechen entwickeln und zu Impedanzfehlpassungen führen. Aktuelle HLGA-Verbinder können Datenübertra-

gungsgeschwindigkeiten von bis zu 25 Gbps (Gigabit/Sekunde) aufweisen. Aufgrund von Bedenken im Hinblick auf Impedanzfehlanpassung und Übersprechen ist es schwierig, höhere Datengeschwindigkeiten mit vorhandenen HLGA-Verbbindern zu erzielen.

**[0006]** Ausführungsformen der vorliegenden Erfindung erkennen an, dass ein Ansatz zum Konstruieren eines HLGA für eine bessere Signalintegrität vorhanden ist, das in der Lage ist, Datenübertragungsgeschwindigkeiten von mehr als 25 Gbps zu erzielen. Bei einer Ausführungsform werden plattierte Durchkontaktierungen oder leitfähige Stifte in einem halben Rasterabstand (mit Zwischenräumen) zwischen den Löchern in dem Körper des Verbinderkörpers aus Kunststoff (d.h., aus einem dielektrischen Material) platziert, die die Federkontakte aufnehmen. Die plattierten Durchkontaktierungen/leitfähigen Stifte werden mit den Massekontaktfedern elektrisch verbunden. Das Netz von geerdeten plattierten Durchkontaktierungen/leitfähigen Stiften erzeugt eine Kapazität in dem HLGA-Verbinder, die die induktive Fehlpassung in dem Verbinder insgesamt verringert. Darüber hinaus erzeugt ein kürzerer und dichterer Rückweg die richtige Umgebung, um elektrisches Übersprechen zu verringern und die Frequenz jeglicher Resonanzen eines Übersprechens in Verbinder zu erhöhen.

**[0007]** Wenn in der Beschreibung auf „eine Ausführungsform“, „eine beispielhafte Ausführungsform“ usw. Bezug genommen wird, weist dies darauf hin, dass die beschriebene Ausführungsform ein bestimmtes Merkmal, eine bestimmte Struktur oder Eigenschaft enthalten kann. Darüber hinaus beziehen sich solche Ausdrücke nicht unbedingt auf dieselbe Ausführungsform. Wenn ein bestimmtes Merkmal, eine bestimmte Struktur oder Eigenschaft in Verbindung mit einer Ausführungsform beschrieben wird, wird des Weiteren vorausgesetzt, dass ein Fachmann über die Kenntnisse verfügt, um ein solches Merkmal, eine solche Struktur oder Eigenschaft in Verbindung mit sonstigen Ausführungsformen nachzuvollziehen, unabhängig davon, ob sie ausdrücklich beschrieben werden.

**[0008]** Für Beschreibungszwecke sollen sich im Folgenden die Begriffe „obere(r,s)“, „rechte(r,s)“, „linke(r,s)“, „vertikale(r,s)“, „horizontale(r,s)“, „oben liegende(r,s)“, „unten liegende(r,s)“ und Ableitungen davon so auf die offenbarten Strukturen und Verfahren beziehen, wie sie in den Figuren der Zeichnungen ausgerichtet sind. Die Begriffe „darüber liegend“, „über“, „positioniert auf“ oder „positioniert über“ bedeuten, dass sich ein erstes Element wie zum Beispiel eine erste Struktur auf einem zweiten Element wie zum Beispiel einer zweiten Struktur befindet, wobei sich dazwischen liegende Elemente wie zum Beispiel eine Grenzflächenstruktur zwischen dem ersten Element und dem zweiten Element befinden können. Der Be-

griff „direkter Kontakt“ bedeutet, dass ein erstes Element wie zum Beispiel eine erste Struktur und ein zweites Element wie zum Beispiel eine zweite Struktur ohne jegliche dazwischenliegende leitende, isolierende oder Halbleiterschichten an der Grenzfläche der beiden Elemente verbunden sind.

**[0009]** Bestimmte Elemente, auf die im Singular Bezug genommen wird, können so, wie hierin auf sie Bezug genommen wird, auch als Plural betrachtet werden. In den folgenden Beispielen bezieht sich der Begriff „X“ sowohl auf ein einzelnes „X“ als auch auf zwei oder mehr „X“: „Loch“, „Signalkontakt-Freilegungsbereich“, „plattierte leitfähige Durchkontaktierung“, „Massefederkontakt“, „Signalfederkontakt“, „leitfähiger Stift“, eingesetzter „leitfähiger Stift“ und „plattierter leitfähiger Stift“.

**[0010]** Die vorliegende Erfindung wird im Folgenden unter Bezugnahme auf die Figuren ausführlich beschrieben.

**[0011]** **Fig. 1** ist ein beispielhafter HLGA-Verbinderkörper, der allgemein mit 100 gekennzeichnet wird, gemäß einer Ausführungsform der vorliegenden Erfindung. **Fig. 1** stellt lediglich eine Veranschaulichung einer Umsetzung bereit und impliziert keinerlei Einschränkungen in Bezug auf die verschiedenen Ausführungsformen, die umgesetzt werden können. Zahlreiche Modifizierungen an der dargestellten Ausführungsform können durch Fachleute vorgenommen werden, ohne vom Umfang der Erfindung abzuweichen, wie er in den Ansprüchen angegeben wird.

**[0012]** Bei einer Ausführungsform enthält der HLGA-Verbinder **100** einen Verbinderkörper **102**, Löcher für Federkontakte **104** und Löcher für plattierte Durchkontaktierungen **106**. Bei beispielhaften Ausführungsformen kann der HLGA-Verbinder **100** sonstige (in **Fig. 1** nicht dargestellte) Attribute wie zum Beispiel Kennzeichnungen, elektrische Schaltungen, elektrische Bauteile usw. enthalten. Bei einer Ausführungsform kann der HLGA-Verbinder **100** vierseitig (z.B. ein Quadrat oder ein Rechteck) sein, er ist jedoch nicht auf eine bestimmte Form beschränkt und wird lediglich durch die CPU/PCB-Kombination im Hinblick auf eine Form und eine Größe beschränkt.

**[0013]** Gemäß Ausführungsformen der vorliegenden Erfindung besteht der Verbinderkörper **102** bevorzugt aus einem festen dielektrischen Material. Zu beispielhaften dielektrischen Materialien zählen Kunststoff, Keramik, Glas, Glimmer und verschiedene Metalloxide, ohne darauf beschränkt zu sein. Dielektrische Materialien sind elektrisch isolierend und daher schlechte Leiter für elektrischen Strom. Dielektrische Materialien unterstützen darüber hinaus wirksam elektrostatische Felder. Bei einer Ausführungsform wird ein dielektrisches Material für den Verbinderkörper **102** verwendet, so dass eine gute Signal-

integrität für durch elektrische Kontakte wie zum Beispiel Metallfederkontakte (siehe z.B. **Fig. 3**, einen Massefederkontakt **302** und einen Signalfederkontakt **304**), die in dem Verbinderkörper **102** enthalten sind, geleitete elektrische Signale aufrechterhalten wird.

**[0014]** Bei einer Ausführungsform handelt es sich bei den Löchern für die Federkontakte **104** um Löcher in dem Verbinderkörper **102**, die auf der oberen Fläche des Verbinderkörpers **102** beginnen und auf der unteren Fläche des Verbinderkörpers **102** enden und vollständig durch den Verbinderkörper **102** hindurchführen. Bei der Ausführungsform befindet sich die untere Fläche des Verbinderkörpers **102** gegenüber der oberen Fläche des Verbinderkörpers **102**. Gemäß einer Ausführungsform können die Löcher für die Federkontakte **104** dazu verwendet werden, ein Platzieren der Metallfederkontakte in dem Verbinderkörper **102** zu ermöglichen. Bei einer Ausführungsform sind die Löcher für die Federkontakte **104** in einem sich wiederholenden Gittermuster innerhalb des Verbinderkörpers **102** positioniert. Gemäß einer Ausführungsform der vorliegenden Erfindung sind die Löcher für die Federkontakte **104** in einer Weise geformt, die die Federkontakte sicher in dem Verbinderkörper **102** hält, so dass die Federkontakte nicht gelockert werden, wenn der HLGA-Verbinder **100** verwendet wird. Bei einer Ausführungsform bleiben die Löcher für die Federkontakte **104** nach dem Platzieren der Metallfederkontakte leer. Bei einer weiteren Ausführungsform werden die Löcher für die Federkontakte **104**, die für einen Massefederkontakt **302** verwendet werden, vor jeglichem (im Folgenden erörterten) Plattieren eines leitfähigen Materials nach dem Platzieren sämtlicher der Massefederkontakte **302** mit einem dielektrischen Material gefüllt. Bei der Ausführungsform sorgt das zusätzliche dielektrische Material in den Löchern für die Federkontakte **104** für eine verbesserte elektrische Leistungsfähigkeit des HLGA-Verbinder.

**[0015]** Bei einer Ausführungsform handelt es sich bei den Löchern für die plattierte Durchkontaktierungen **106** um Löcher in dem Verbinderkörper **102**, die auf der oberen Fläche des Verbinderkörpers **102** beginnen und auf der unteren Fläche des Verbinderkörpers **102** enden und vollständig durch den Verbinderkörper **102** hindurchführen. Gemäß einer Ausführungsform können die Löcher für die plattierte Durchkontaktierungen **106** mit einem leitfähigen Material plattierte werden, das eine elektrische Verbindung zwischen einer leitfähigen Plattierung auf der oberen Fläche des Verbinderkörpers **102** und einer leitfähigen Plattierung auf der unteren Fläche des Verbinderkörpers **102** bereitstellt. Bei einer Ausführungsform sind die Löcher für die plattierte Durchkontaktierungen **106** an den Mittelpunkten (d.h., im halben Rasterabstand) zwischen den Löchern für die Federkontakte **104** in dem Verbinderkörper **102** po-

sitioniert. Bei einer Ausführungsform weisen die Löcher für die plattierte Durchkontaktierungen **106** eine wesentlich geringere Größe im Verhältnis zu den Löchern für die Federkontakte **104** auf.

**[0016]** **Fig. 2** stellt den HLGA-Verbinder von **Fig. 1** nach Fertigungsschritten zum Platten und Ätzen dar und wird gemäß einer Ausführungsform der vorliegenden Erfindung allgemein mit 200 gekennzeichnet. **Fig. 2** stellt lediglich eine Veranschaulichung einer Umsetzung bereit und impliziert keinerlei Einschränkungen in Bezug auf die verschiedenen Ausführungsformen, die umgesetzt werden können. Zahlreiche Modifizierungen an der dargestellten Ausführungsform können durch Fachleute vorgenommen werden, ohne vom Umfang der Erfindung abzuweichen, wie er in den Ansprüchen angegeben wird.

**[0017]** Bei einer Ausführungsform enthält der HLGA-Verbinder **200** das zuvor erörterte Merkmal, den Verbinderkörper **102**, und neue Merkmale, Löcher für Signalkontakte **202**, Löcher für Massekontakte **204**, einen Signalkontakt-Freilegungsbereich **206**, eine obere leitfähige Schicht **208**, eine untere leitfähige Schicht **210** und eine plattierte leitfähige Durchkontaktierung **212**.

**[0018]** Gemäß einer Ausführungsform der vorliegenden Erfindung handelt es sich bei den Löchern für die Signalkontakte **202** und den Löchern für die Massekontakte **204** um die Löcher für die Federkontakte **104**, die entweder als Signalverbindung oder als Masseverbindung zwischen dem Chip-Trägergehäuse (z.B. der Zentraleinheit oder CPU) und der Leiterplatte (PCB) bezeichnet werden sind. Bei einer Ausführungsform gelten die sonstigen Merkmale der Löcher für die Federkontakte **104**, die zuvor erörtert worden sind, für die Löcher für die Signalkontakte **202** und die Löcher für die Massekontakte **204**. Bei einer Ausführungsform wird das Loch für den Massekontakt **204** letztendlich mit einem leitfähigen Metall wie zum Beispiel Kupfer plattierte, und wenn der Federkontakt in dem Loch für den Massekontakt **204** platziert wird, ist ein elektrischer Kontakt zwischen dem Federkontakt und dem auf der Oberfläche plattierte Metall erforderlich. Bei dieser Ausführungsform ist das Loch für den Massekontakt **204** mit keinem anderen Material als mit Luft gefüllt. Bei der zuvor erörterten Ausführungsform mit einem dielektrischen Material, das nach der Platzierung der Federkontakte das Loch für den Massekontakt **204** füllt, stellt eine Oberflächenplattierung über dem dielektrischen Material in dem Loch für den Massekontakt **204** (z.B. eine Plattierung mit einem leitfähigen Metall wie zum Beispiel Kupfer) dadurch, dass sie mit den Massefederkontakten, der oberen leitfähigen Schicht **208** und der unteren leitfähigen Schicht **210** in physchem Kontakt steht, eine elektrische Verbindung zwischen den Massefederkontakten (wie zum Beispiel dem Massefederkontakt **302** in **Fig. 3**), der (im

Folgenden erörterten) oberen leitfähigen Schicht **208** und der (im Folgenden erörterten) unteren leitfähigen Schicht **210** bereit.

**[0019]** Bei einer Ausführungsform handelt es sich bei der oberen leitfähigen Schicht **208** und der unteren leitfähigen Schicht **210** um die obere Fläche bzw. die untere Fläche des Verbinderkörpers **102** im Anschluss an ein Aufbringen einer leitfähigen Schicht. Gemäß einer Ausführungsform der vorliegenden Erfindung handelt es sich bei der leitfähigen Schicht, die auf die obere leitfähige Schicht **208** und die untere leitfähige Schicht **210** aufgebracht wird, um Kupfer, das mit einem Plattierungsprozess aufgebracht wird. Bei der Ausführungsform steht die aufgebrachte leitfähige Schicht, die auf die obere Fläche des Verbinderkörpers **102** aufgebracht wird, in direktem Kontakt mit der oberen Fläche des Verbinderkörpers **102**. Bei der Ausführungsform steht darüber hinaus die aufgebrachte leitfähige Schicht, die auf die untere Fläche des Verbinderkörpers **102** aufgebracht wird, in direktem Kontakt mit der unteren Fläche des Verbinderkörpers **102**. Gemäß sonstigen Ausführungsformen handelt es sich bei der leitfähigen Schicht, die auf die obere leitfähige Schicht **208** und auf die untere leitfähige Schicht **210** aufgebracht wird, um ein beliebiges ausreichend leitfähiges Material nach dem Stand der Technik, das durch einen beliebigen Prozess nach dem Stand der Technik aufgebracht wird. Bei einer Ausführungsform ist die obere leitfähige Schicht **208** im Anschluss an das Aufbringen der leitfähigen Schicht vollständig mit dem leitfähigen Material bedeckt und stimmt mit diesem elektrisch überein. Darüber hinaus ist bei der Ausführungsform die untere leitfähige Schicht **210** im Anschluss an das Aufbringen der leitfähigen Schicht ebenfalls vollständig mit dem leitfähigen Material bedeckt und stimmt ebenfalls mit diesem elektrisch überein. Bei der Ausführungsform sind die Wandflächen für das Loch für den Signalkontakt **202**, die Wandflächen für das Loch für den Massekontakt **204** und die Wandflächen für die platierte leitfähige Durchkontaktierung **212** platziert und stimmen mit der oberen leitfähigen Schicht **208** und der unteren leitfähigen Schicht **210** elektrisch überein, bis ein (im Folgenden erörterter) Signalkontakt-Freilegungsbereich **206** erzeugt wird.

**[0020]** Gemäß einer Ausführungsform der vorliegenden Erfindung handelt es sich bei dem Signalkontakt-Freilegungsbereich **206** um einen Bereich um die Löcher für den Signalkontakt **202**, von dem die leitfähige Schicht entfernt worden ist. Bei einer Ausführungsform wird ein Abschnitt der oberen leitfähigen Schicht **208** von der oberen Fläche des Verbinderkörpers **102** um jedes der Löcher für die Signalkontakte **202** entfernt. Bei der Ausführungsform wird ein Abschnitt der unteren Schicht **210** ebenfalls von der unteren Fläche des Verbinderkörpers **102** um jedes der Löcher für die Signalkontakte **202** entfernt. Darüber hinaus wird bei der Ausführungsform die Plat-

tierung auf den Wandflächen des Lochs für den Signalkontakt **202** entfernt. Gemäß einer Ausführungsform der vorliegenden Erfindung wird ein subtraktiver Photolithographieprozess dazu verwendet, den Abschnitt der oberen leitfähigen Schicht **208** und den Abschnitt der unteren leitfähigen Schicht **210** zu entfernen. Beispielsweise wird im Hinblick auf die obere leitfähige Schicht **208** ein Photolack über der oberen leitfähigen Schicht **208** aufgebracht. Ein Belichtungsmuster wird in dem Photolack entwickelt, das jeden Signalkontakt-Freilegungsbereich **206** definiert. Der Verbinderkörper **102** wird erhitzt, um den verbleibenden Photolack zu stabilisieren. Anschließend wird ein Ätzprozess dazu verwendet, den Abschnitt der oberen leitfähigen Schicht **208** um jedes der Löcher für den Signalkontakt **202** zu entfernen, was zu der Ausbildung des Signalkontakt-Freilegungsbereichs **206** führt. Ein Photolack-Ablöseprozess entfernt den Überschuss des Photolacks von der oberen leitfähigen Schicht **208**. Anschließend wird der Verbinderkörper **102** durch einen Reinigungsprozess bearbeitet, um jegliche verbleibenden Bearbeitungsmaterialien zu entfernen. Bei einer Ausführungsform wird derselbe Prozess dazu verwendet, jeweils den Signalkontakt-Freilegungsbereich **206** in der unteren leitfähigen Schicht **210** zu definieren. Die Ergebnisse der obigen Photolithographieprozesse bestehen in einem Entfernen der Plattierung von den Wandflächen des Lochs für den Signalkontakt **202**, dem Erzeugen des Signalkontakt-Freilegungsbereichs **206** (zum elektrischen Isolieren des Signalfederkontakte **304** in Fig. 3) und einem Intaktlassen der Plattierung auf den Wandflächen des Lochs für den Massekontakt **204**. Gemäß sonstigen Ausführungsformen der vorliegenden Erfindung kann ein beliebiger Prozess nach dem Stand der Technik dazu verwendet werden, jeweils den Signalkontakt-Freilegungsbereich **206** in der oberen leitfähigen Schicht **208** sowie in der unteren leitfähigen Schicht **210** zu definieren.

**[0021]** Bei einer Ausführungsform handelt es sich bei der platierten leitfähigen Durchkontaktierung **212** um ein Loch für eine platierte Durchkontaktierung **106**, das mit einem leitfähigen Material platiert worden ist. Gemäß einer Ausführungsform der vorliegenden Erfindung handelt es sich bei dem leitfähigen Material, das auf die platierte leitfähige Durchkontaktierung **212** aufgebracht wird, um Kupfer, das mithilfe eines elektrolytischen Plattierungsprozesses aufgebracht wird. Gemäß sonstigen Ausführungsformen handelt es sich bei dem leitfähigen Material, das auf die platierte leitfähige Durchkontaktierung **212** aufgebracht wird, um ein beliebiges ausreichend leitfähiges Material nach dem Stand der Technik, das durch einen beliebigen Prozess nach dem Stand der Technik aufgebracht wird. Bei einer Ausführungsform wird die platierte leitfähige Durchkontaktierung **212** nach dem Aufbringen des leitfähigen Materials auf die Löcher für die platierten Durchkontaktierungen **106** mit

der oberen leitfähigen Schicht **208** sowie mit der unteren leitfähigen Schicht **210** elektrisch verbunden.

**[0022]** **Fig. 3** stellt den HLGA-Verbinder von **Fig. 2** nach dem Einbau von Metallfederkontakte dar und wird gemäß einer Ausführungsform der vorliegenden Erfindung allgemein mit 300 gekennzeichnet. **Fig. 3** stellt lediglich eine Veranschaulichung einer Umsetzung bereit und impliziert keinerlei Einschränkungen in Bezug auf die verschiedenen Ausführungsformen, die umgesetzt werden können. Zahlreiche Modifizierungen an der dargestellten Ausführungsform können durch Fachleute vorgenommen werden, ohne vom Umfang der Erfindung abzuweichen, wie er in den Ansprüchen angegeben wird.

**[0023]** Bei einer Ausführungsform enthält der HLGA-Verbinder **300** die zuvor erörterten Merkmale, den Verbinderkörper **102**, die obere leitfähige Schicht **208**, die untere leitfähige Schicht **210** und die plattierte leitfähige Durchkontaktierung **212**, und neue Merkmale, einen Massefederkontakt **302** und einen Signalfederkontakt **304**.

**[0024]** Bei einer Ausführungsform handelt es sich bei dem Massefederkontakt **302** um einen vorab ausgebildeten Metallfederkontakt, der in die Löcher für die Massekontakte **204** in dem Verbinderkörper **102** eingesetzt (d.h., geheftet) wird. Der Massefederkontakt **302** kommt mit den Massekontakteflächen des Kontaktflächengitter-Arrays (LGA) auf der CPU sowie mit dem Lot auf den Massekontakteflächen auf der PCB in Kontakt, wodurch eine Verbindung zwischen der CPU und der PCB bereitgestellt wird. Gemäß einer Ausführungsform der vorliegenden Erfindung wird der Massefederkontakt **302** aus Kupfer vorab ausgebildet. Gemäß sonstigen Ausführungsformen der vorliegenden Erfindung wird der Massefederkontakt **302** aus einem beliebigen sonstigen ausreichend leitfähigen Metall nach dem Stand der Technik vorab ausgebildet. Bei einer Ausführungsform wird der Massefederkontakt **302** in die Löcher für die Federkontakte **204** geheftet und wird mechanisch festgehalten. Bei einer Ausführungsform weist der Massefederkontakt **302** dadurch, dass der Massefederkontakt **302** mit der oberen leitfähigen Schicht **208**, der unteren leitfähigen Schicht **210** und der leitfähigen Plattierung im Inneren des Lochs für den Massekontakt **204** physisch in Kontakt steht, eine elektrische Verbindung mit der oberen leitfähigen Schicht **208**, der unteren leitfähigen Schicht **210** und der plattierte leitfähigen Durchkontaktierung **212** auf.

**[0025]** Bei einer Ausführungsform handelt es sich bei dem Signalfederkontakt **304** um einen vorab ausgebildeten Metallfederkontakt, der in die Löcher für die Signalkontakte **202** in dem Verbinderkörper **102** eingesetzt (d.h., geheftet) wird. Der Signalfederkontakt **304** kommt mit den Signalkontakteflächen des Kontaktflächengitter-Arrays (LGA) auf der CPU und

dem Lot auf den Signalkontakteflächen auf der PCB in Kontakt, wodurch eine Verbindung zwischen der CPU und der PCB bereitgestellt wird. Gemäß einer Ausführungsform der vorliegenden Erfindung wird der Signalfederkontakt **304** aus Kupfer vorab ausgebildet. Gemäß sonstigen Ausführungsformen der vorliegenden Erfindung wird der Signalfederkontakt **304** aus einem beliebigen sonstigen leitfähigen Metall nach dem Stand der Technik vorab ausgebildet. Bei einer Ausführungsform wird der Signalfederkontakt **304** in die Löcher für die Signalkontakte **202** geheftet und wird mechanisch festgehalten. Bei einer Ausführungsform ist der Signalfederkontakt **304** mit keiner der oberen leitfähigen Schicht **208**, der unteren leitfähigen Schicht **210** und der plattierte leitfähigen Durchkontaktierung **212** elektrisch verbunden.

**[0026]** **Fig. 4** ist ein beispielhafter HLGA-Verbinderkörper, der allgemein mit 400 gekennzeichnet wird, gemäß einer Ausführungsform der vorliegenden Erfindung. **Fig. 4** stellt lediglich eine Veranschaulichung einer Umsetzung bereit und impliziert keinerlei Einschränkungen in Bezug auf die verschiedenen Ausführungsformen, die umgesetzt werden können. Zahlreiche Modifizierungen an der dargestellten Ausführungsform können durch Fachleute vorgenommen werden, ohne vom Umfang der Erfindung abzuweichen, wie er in den Ansprüchen angegeben wird.

**[0027]** Bei einer Ausführungsform enthält der HLGA-Verbinder **400** die zuvor erörterten Merkmale, den Verbinderkörper **102** und die Löcher für die Federkontakte **104**, und neue Merkmale, Löcher für leitfähige Stifte **402** und einen leitfähigen Stift **404**.

**[0028]** Bei einer Ausführungsform ähneln die Löcher für die leitfähigen Stifte **402** im Wesentlichen den Löchern für die plattierte Durchkontaktierungen **106**. Gemäß einer Ausführungsform der vorliegenden Erfindung handelt es sich bei den Löchern für die leitfähigen Stifte **402** um die Löcher in dem Verbinderkörper **102**, die auf der oberen Fläche des Verbinderkörpers **102** beginnen und auf der unteren Fläche des Verbinderkörpers **102** enden und vollständig durch den Verbinderkörper **102** hindurchführen. Bei einer Ausführungsform sind die Löcher für die leitfähigen Stifte **402** an den Mittelpunkten zwischen den Löchern für die Federkontakte **104** in dem Verbinderkörper **102** positioniert. Bei einer Ausführungsform weisen die Löcher für die leitfähigen Stifte **402** eine wesentlich geringere Größe als die Löcher für die Federkontakte **104** auf.

**[0029]** Bei einer Ausführungsform handelt es sich bei dem leitfähigen Stift **404** um einen massiven Stift (z.B. einen Bolzen), der in die Löcher für die leitfähigen Stifte **402** geheftet wird und mechanisch festgehalten wird. Gemäß einer Ausführungsform ist der leitfähige Stift **404** aus Kupfer hergestellt. Gemäß einer weiteren Ausführungsform ist der leitfähige Stift

**404** aus einem beliebigen leitfähigen Metall nach dem Stand der Technik hergestellt.

**[0030]** Bei einer Ausführungsform handelt es sich bei einem eingesetzten leitfähigen Stift **406** um den leitfähigen Stift **404**, der in den Verbinderkörper **102** eingesetzt wird. Bei einer Ausführungsform befinden sich die Oberseite und die Unterseite des eingesetzten leitfähigen Stifts **406** auf derselben Ebene wie die obere Fläche bzw. die untere Fläche des Verbinderkörpers **102**. Bei einer weiteren Ausführungsform erstrecken sich die Oberseite und die Unterseite des eingesetzten leitfähigen Stifts **406** über die Ebene der oberen Fläche bzw. die Ebene der unteren Fläche des Verbinderkörpers **102** hinaus bis zu einer maximalen Höhe oberhalb der jeweiligen Ebene.

**[0031]** **Fig. 5** ist der HLGA-Verbinder von **Fig. 4** nach Fertigungsschritten zum Plattieren und Ätzen und wird gemäß einer Ausführungsform der vorliegenden Erfindung allgemein mit 500 gekennzeichnet. **Fig. 5** stellt lediglich eine Veranschaulichung einer Umsetzung bereit und impliziert keinerlei Einschränkungen in Bezug auf die verschiedenen Ausführungsformen, die umgesetzt werden können. Zahlreiche Modifizierungen an der dargestellten Ausführungsform können durch Fachleute vorgenommen werden, ohne vom Umfang der Erfindung abzuweichen, wie er in den Ansprüchen angegeben wird.

**[0032]** Bei einer Ausführungsform enthält der HLGA-Verbinder **500** die zuvor erörterten Merkmale, den Verbinderkörper **102**, die obere leitfähige Schicht **208**, die untere leitfähige Schicht **210**, den Massefederkontakt **302** und den Signalfederkontakt **304**, und ein neues Merkmal, einen platierten leitfähigen Stift **502**.

**[0033]** Bei einer Ausführungsform handelt es sich bei dem platierten leitfähigen Stift **502** um den eingesetzten leitfähigen Stift **406**, der dem zuvor beschriebenen Photolithographieprozess unterzogen worden ist, der in der oberen leitfähigen Schicht **208**, der unteren leitfähigen Schicht **210**, dem (in **Fig. 5** nicht dargestellten) Signalkontakt-Freilegungsbereich **206**, der Plattierung auf der Oberseite des eingesetzten leitfähigen Stiftes **406**, der Plattierung auf der Unterseite des eingesetzten leitfähigen Stiftes **406** und einer elektrischen Verbindung der Plattierung mit dem Massefederkontakt **302** resultiert. Gemäß einer Ausführungsform der vorliegenden Erfindung handelt es sich bei der Plattierung auf der Oberseite und der Unterseite des platierten leitfähigen Stifts **502** um eine Kupferplattierung. Gemäß sonstigen Ausführungsformen der vorliegenden Erfindung handelt es sich bei der Plattierung auf der Oberseite und der Unterseite des platierten leitfähigen Stifts **502** um eine beliebige leitfähige Plattierung nach dem Stand der Technik.

**[0034]** Die hierin verwendete Terminologie dient lediglich der Beschreibung bestimmter Ausführungsformen und soll die Erfindung nicht beschränken. So, wie sie hierin verwendet werden, sollen die Singularformen „ein“, „eine“ und „der“, „die“, „das“ auch die Pluralformen enthalten, sofern dies aus dem Kontext nicht eindeutig anders hervorgeht. Es versteht sich darüber hinaus, dass die Begriffe „aufweist“ und/oder „aufweisend“, wenn sie in dieser Beschreibung verwendet werden, das Vorhandensein von angegebenen Merkmalen, Ganzzahlen, Schritten, Vorgängen, Elementen und/oder Komponenten bezeichnen, jedoch nicht das Vorhandensein bzw. die Beifügung von einem/einer bzw. mehreren anderen Merkmalen, Ganzzahlen, Schritten, Vorgängen, Elementen, Komponenten und/oder Gruppen davon ausschließen.

**[0035]** Nachdem Ausführungsformen eines HLGA für eine verbesserte Signalintegrität und ein Prozess zum Fertigen eines HLGA für eine verbesserte Signalintegrität (die der Veranschaulichung dienen und nicht beschränkend sein sollen) beschrieben worden sind, wird darauf hingewiesen, dass durch Fachleute Modifizierungen und Variationen angesichts der obigen Lehren vorgenommen werden können. Es versteht sich daher, dass Änderungen an bestimmten offensichtlichen Ausführungsformen vorgenommen werden können, die in den Umfang der Erfindung fallen, wie er durch die beigefügten Ansprüche dargestellt wird.

#### Bezugszeichenliste

|                                |                                                                                                                    |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------|

| <b>100, 200, 300, 400, 500</b> | HLGA-Verbinder                                                                                                     |

| <b>102</b>                     | Körper (Verbinderkörper)                                                                                           |

| <b>104</b>                     | erste Mehrzahl von Löchern (Löcher für die Federkontakte)                                                          |

| <b>106</b>                     | zweite Mehrzahl von Löchern (Löcher für die platierten Durchkontaktierungen und Löcher für die leitfähigen Stifte) |

| <b>202</b>                     | erster Teilsatz (Löcher für die Signalkontakte)                                                                    |

| <b>204</b>                     | zweiter Teilsatz (Löcher für die Massekontakte)                                                                    |

| <b>206</b>                     | Bereich (Signalkontakt-Freilegungsbereich)                                                                         |

| <b>208</b>                     | obere leitfähige Schicht                                                                                           |

|     |                                          |

|-----|------------------------------------------|

| 210 | untere leitfähige Schicht                |

| 212 | plattierte leitfähige Durchkontaktierung |

| 302 | Federkontakt (Mas-<br>sefederkontakt)    |

| 304 | Federkontakt (Si-<br>gnalfederkontakt)   |

| 402 | Löcher für die leitfähigen Stifte        |

| 404 | leitfähiger Stift                        |

| 406 | eingesetzter leitfähiger Stift           |

| 502 | plattierter leitfähiger Stift            |

### Patentansprüche

1. Verfahren, wobei das Verfahren aufweist:

Bereitstellen eines Körpers (102) für einen Hybridkontakteflächengitter-Array-Verbinder, wobei der Körper (102) eine erste Mehrzahl von Löchern (104) und eine zweite Mehrzahl von Löchern (106, 402) enthält;

Abscheiden einer leitfähigen Schicht (208, 210) auf einer oberen Fläche des Körpers (102), einer unteren Fläche des Körpers (102) und auf Wandflächen der ersten Mehrzahl von Löchern (104), wobei die obere Fläche des Körpers (102) mit der unteren Fläche des Körpers (102) elektrisch übereinstimmt;

Entfernen der leitfähigen Schicht (208, 210) von Wandflächen eines ersten Teilsatzes (202) der ersten Mehrzahl von Löchern (104); und

Entfernen eines Abschnitts der leitfähigen Schicht (208, 210) auf der oberen Fläche des Körpers (102) und der unteren Fläche des Körpers (102) aus einem Bereich (206), der den ersten Teilsatz (202) der ersten Mehrzahl von Löchern (104) umgibt.

2. Verfahren nach Anspruch 1, das des Weiteren aufweist:

Heften einer Mehrzahl von Federkontakte (302, 304) in die erste Mehrzahl von Löchern (104), wobei: die Mehrzahl von Federkontakte (304), die in den ersten Teilsatz (202) der ersten Mehrzahl von Löchern (104) geheftet wird, voneinander elektrisch isoliert wird; und

die Mehrzahl von Federkontakte (302), die in einen zweiten Teilsatz (204) der ersten Mehrzahl von Löchern (104) geheftet wird, zumindest miteinander, mit der leitfähigen Schicht (208) auf der oberen Fläche des Körpers (102) und der leitfähigen Schicht (210) auf der unteren Fläche des Körpers (102) elektrisch übereinstimmt.

3. Verfahren nach Anspruch 1, wobei ein subtraktiver Photolithographieprozess dazu verwendet wird,

die leitfähige Schicht (208, 210) von den Wandflächen des ersten Teilsatzes (202) der ersten Mehrzahl von Löchern (104) und dem Bereich (206), der den ersten Teilsatz (202) der ersten Mehrzahl von Löchern (104) umgibt, zu entfernen.

4. Verfahren nach Anspruch 1, das des Weiteren aufweist:

Abscheiden eines Materials in einen zweiten Teilsatz (204) der ersten Mehrzahl von Löchern (104).

5. Verfahren nach Anspruch 4, wobei es sich bei dem Material um ein dielektrisches Material handelt.

6. Verfahren nach Anspruch 1, wobei der Schritt zum Abscheiden einer leitfähigen Schicht (208, 210) auf einer oberen Fläche des Körpers (102), einer unteren Fläche des Körpers (102) und auf Wandflächen der ersten Mehrzahl von Löchern (104) des Weiteren aufweist:

Abscheiden der leitfähigen Schicht (208, 210) auf Wandflächen der zweiten Mehrzahl von Löchern (106, 402).

7. Verfahren nach Anspruch 1, das des Weiteren aufweist:

Heften eines leitfähigen Stiftes (404) in jedes der zweiten Mehrzahl von Löchern (106, 402), wobei der leitfähige Stift (404) eine elektrische Verbindung zwischen der leitfähigen Schicht (208) auf der oberen Fläche des Körpers (102) und der leitfähigen Schicht (210) auf der unteren Fläche des Körpers (102) bereitstellt.

8. Hybridkontakteflächengitter-Array-Verbinder, der aufweist:

einen Körper (102), wobei der Körper (102) eine erste Mehrzahl von Löchern (104) und eine zweite Mehrzahl von Löchern (106, 402) enthält;

eine leitfähige Schicht (208, 210) auf einer oberen Fläche des Körpers (102), einer unteren Fläche des Körpers (102), auf Wandflächen eines ersten Teilsatzes (202) der ersten Mehrzahl von Löchern (104) und Wandflächen der zweiten Mehrzahl von Löchern (106, 402), so dass die obere Fläche des Körpers (102), die untere Fläche des Körpers (102), der erste Teilsatz (202) der ersten Mehrzahl von Löchern (104) und die zweite Mehrzahl von Löchern (106, 402) elektrisch übereinstimmen; und

Federkontakte (302, 304), die in die erste Mehrzahl von Löchern (104) geheftet sind.

9. Hybridkontakteflächengitter-Array-Verbinder nach Anspruch 8, wobei sich die zweite Mehrzahl von Löchern (106, 402) an Mittelpunkten zwischen der ersten Mehrzahl von Löchern (104) befindet.

10. Hybridkontakteflächengitter-Array-Verbinder nach Anspruch 8, wobei die zweite Mehrzahl von Lö-

chern (106, 402) im Verhältnis zu der ersten Mehrzahl von Löchern (104) kleiner ist.

11. Hybridkontakteflächengitter-Array-Verbinder nach Anspruch 8, wobei es sich bei dem Körper (102) um ein dielektrisches Material handelt.

12. Hybridkontakteflächengitter-Array-Verbinder nach Anspruch 8, wobei es sich bei der leitfähigen Schicht (208, 210) um Kupfer handelt.

13. Hybridkontakteflächengitter-Array-Verbinder nach Anspruch 8, wobei es sich bei den Federkontakte (302, 304) um Kupfer handelt.

14. Hybridkontakteflächengitter-Array-Verbinder, der aufweist:

einen Körper (102), wobei der Körper (102) eine erste Mehrzahl von Löchern (104) und eine zweite Mehrzahl von Löchern (106, 402) enthält;

leitfähige Stifte (404), die in jedes der zweiten Mehrzahl von Löchern (106, 402) geheftet sind;

eine leitfähige Schicht (208, 210) auf einer oberen Fläche des Körpers (102), einer unteren Fläche des Körpers (102), auf Wandflächen eines ersten Teilsatzes (202) der ersten Mehrzahl von Löchern (104) und den leitfähigen Stiften (404), so dass die obere Fläche des Körpers (102), die untere Fläche des Körpers (102), der erste Teilsatz (202) der ersten Mehrzahl von Löchern (104) und die leitfähigen Stifte (404) elektrisch übereinstimmen; und

Federkontakte (302, 304), die in die erste Mehrzahl von Löchern (104) geheftet sind.

15. Hybridkontakteflächengitter-Array-Verbinder nach Anspruch 14, wobei sich die zweite Mehrzahl von Löchern (106, 402) an Mittelpunkten zwischen der ersten Mehrzahl von Löchern (104) befindet.

16. Hybridkontakteflächengitter-Array-Verbinder nach Anspruch 14, wobei die zweite Mehrzahl von Löchern (106, 402) im Verhältnis zu der ersten Mehrzahl von Löchern (104) kleiner ist.

17. Hybridkontakteflächengitter-Array-Verbinder nach Anspruch 14, wobei es sich bei dem Körper (102) um ein dielektrisches Material handelt.

18. Hybridkontakteflächengitter-Array-Verbinder nach Anspruch 14, wobei es sich bei den leitfähigen Stiften (404) um Kupfer handelt.

19. Hybridkontakteflächengitter-Array-Verbinder nach Anspruch 14, wobei es sich bei den Federkontakte (302, 304) um Kupfer handelt.

Es folgen 5 Seiten Zeichnungen

Anhängende Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5