(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4825784号

(P4825784)

(45) 発行日 平成23年11月30日(2011.11.30)

(24) 登録日 平成23年9月16日(2011.9.16)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12

S

H01L 23/12

E

請求項の数 11 (全 10 頁)

(21) 出願番号 特願2007-322337 (P2007-322337)

(22) 出願日 平成19年12月13日 (2007.12.13)

(65) 公開番号 特開2009-147080 (P2009-147080A)

(43) 公開日 平成21年7月2日 (2009.7.2)

審査請求日 平成22年8月30日 (2010.8.30)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100077621

弁理士 綿貫 隆夫

(74) 代理人 100092819

弁理士 堀米 和春

(72) 発明者 小泉 直幸

長野県長野市小島田町80番地 新光電気

工業株式会社内

(72) 発明者 大井 淳

長野県長野市小島田町80番地 新光電気

工業株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置用パッケージおよびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

コア基板の表裏面に配線パターンが形成され、該表裏面の配線パターンがコア基板を貫通する貫通孔に形成された導通部を介して電気的に接続する半導体装置用パッケージにおいて、

前記コア基板は、前記導通部用の第1の貫通孔、第2の貫通孔および突起が一体的に形成されるとともに、表面に絶縁層が形成された2枚の金属板が、互いの金属板の前記突起が相手側金属板の前記第2の貫通孔に進入するようにして積層されるとともに、前記各突起の先端が相手側金属板の表面に露出して第1の端子部に形成され、さらに、各金属板の、相手側金属板の前記第1の端子部が露出する側の表面に、前記絶縁層から露出する第2の端子部が形成されていることを特徴とする半導体装置用パッケージ。

## 【請求項 2】

前記2枚の金属板のうちの一方が電源層、他方が接地層であることを特徴とする請求項1記載の半導体装置用パッケージ。

## 【請求項 3】

前記絶縁層が電着塗装によって形成されることを特徴とする請求項1または2記載の半導体装置用パッケージ。

## 【請求項 4】

前記コア基板の一方の表面の側の前記第1の端子部および第2の端子部が外部接続端子に形成されていることを特徴とする請求項1~3いずれか1項記載の半導体装置用パッケ

ージ。

**【請求項 5】**

前記外部接続端子にバンプが形成されていることを特徴とする請求項 4 記載の半導体装置用パッケージ。

**【請求項 6】**

前記配線パターンが多層に形成されていることを特徴とする請求項 1 ~ 5 いずれか 1 項記載の半導体装置用パッケージ。

**【請求項 7】**

コア基板の表裏面に配線パターンが形成され、該表裏面の配線パターンがコア基板を貫通する貫通孔に形成された導通部を介して電気的に接続する半導体装置用パッケージの製造方法において、

10

前記導通部用の第 1 の貫通孔、第 2 の貫通孔および突起が一体的に形成されるとともに、表面に絶縁層が形成された 2 枚の金属板を、互いの金属板の前記突起が相手側金属板の前記第 2 の貫通孔に進入するようにして積層して前記コア基板を形成する工程と、

前記各突起の先端を相手側金属板の表面に露出して第 1 の端子部に形成する工程と、

前記各金属板の、相手側金属板の前記第 1 の端子部が露出する側の表面に、前記絶縁層から露出する第 2 の端子部を形成する工程と、

20

前記第 1 の貫通孔に前記導通部を形成する工程と、

前記コア基板の表裏面に、前記導通部を介して電気的に接続する配線パターンを形成する工程を含むことを特徴とする半導体装置用パッケージの製造方法。

20

**【請求項 8】**

前記 2 枚の金属板の前記第 1 の貫通孔、第 2 の貫通孔および突起を、金属板をエッチング加工して形成することを特徴とする請求項 7 記載の半導体装置用パッケージの製造方法。

。

**【請求項 9】**

前記 2 枚の金属板の前記第 1 の貫通孔、第 2 の貫通孔および突起を、金属板をプレス加工することによって形成することを特徴とする請求項 7 記載の半導体装置用パッケージの製造方法。

**【請求項 10】**

前記突起を、金属板を切り起こし加工することによって形成することを特徴とする請求項 9 記載の半導体装置用パッケージの製造方法。

30

**【請求項 11】**

前記第 2 の端子部を、前記金属板に設けた凸部を研削加工することによって前記絶縁層を除去して形成することを特徴とする請求項 7 ~ 10 いずれか 1 項記載の半導体装置用パッケージの製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体装置用パッケージおよびその製造方法に関する。

**【背景技術】**

**【0002】**

いわゆるビルドアップ配線基板（半導体装置用パッケージ）は、両面銅貼りコア基板（ガラエポ樹脂基板）にドリルによってスルーホールを形成し、無電解銅めっき、電解銅めっきを施し、さらにエッチング加工を施すことにより、表裏面に、スルーホールめっき皮膜（導通部）によって電気的に接続する配線パターンを形成し、さらにビルドアップ法によって、多層の配線パターンを形成するようしている（特許文献 1）。

**【特許文献 1】特開平 11-68319 号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0003】**

10

20

30

40

50

しかしながら、従来の上記半導体装置用パッケージでは次のような課題がある。

すなわち、ガラス繊維にエポキシ樹脂を含浸したコア基板にスルーホールをあけるには、ドリルを用いて、しかも1つづつあける必要があるため、加工に長時間を要し、コスト高となるという課題がある。また、ドリルによる孔明けの場合には、スルーホールの孔径、ピッチを小さくできないので、配線密度を高められないという課題がある。

さらには、内層に電源層と接地層を設けることが多いが、これらを電解めっき膜で形成することとなるので、厚くすることが困難で、抵抗値が大きくなるという課題がある。

そこで、本発明は上記課題を解決すべくなされ、その目的とするところは、高密度配線が可能で、また抵抗値を低くすることができる半導体装置用パッケージおよびその製造方法を提供するにある。

10

#### 【課題を解決するための手段】

##### 【0004】

本発明に係る半導体装置用パッケージは、コア基板の表裏面に配線パターンが形成され、該表裏面の配線パターンがコア基板を貫通する貫通孔に形成された導通部を介して電気的に接続する半導体装置用パッケージにおいて、前記コア基板は、前記導通部用の第1の貫通孔、第2の貫通孔および突起が一体的に形成されるとともに、表面に絶縁層が形成された2枚の金属板が、互いの金属板の前記突起が相手側金属板の前記第2の貫通孔に進入するようにして積層されて形成されるとともに、前記各突起の先端が相手側金属板の表面に露出して第1の端子部に形成され、さらに、各金属板の、相手側金属板の前記第1の端子部が露出する側の表面に、前記絶縁層から露出する第2の端子部が形成されていることを特徴とする。

20

##### 【0005】

前記2枚の金属板のうちの一方が電源層、他方が接地層であることを特徴とする。

前記絶縁層が電着塗装によって形成されることを特徴とする。

前記コア基板の一方の表面の側の前記第1の端子部および第2の端子部が外部接続端子に形成されていることを特徴とする。

また、前記外部接続端子にバンプが形成されていることを特徴とする。

##### 【0006】

また本発明に係る半導体装置用パッケージの製造方法は、コア基板の表裏面に配線パターンが形成され、該表裏面の配線パターンがコア基板を貫通する貫通孔に形成された導通部を介して電気的に接続する半導体装置用パッケージの製造方法において、前記導通部用の第1の貫通孔、第2の貫通孔および突起が一体的に形成されるとともに、表面に絶縁層が形成された2枚の金属板を、互いの金属板の前記突起が相手側金属板の前記第2の貫通孔に進入するようにして積層して前記コア基板を形成する工程と、前記各突起の先端を相手側金属板の表面に露出して第1の端子部に形成する工程と、前記各金属板の、相手側金属板の前記第1の端子部が露出する側の表面に、前記絶縁層から露出する第2の端子部を形成する工程と、前記第1の貫通孔に前記導通部を形成する工程と、前記コア基板の表裏面に、前記導通部を介して電気的に接続する配線パターンを形成する工程を含むことを特徴とする。

30

##### 【0007】

前記2枚の金属板の前記第1の貫通孔、第2の貫通孔および突起を、金属板をエッチング加工して形成することを特徴とする。

前記2枚の金属板の前記第1の貫通孔、第2の貫通孔および突起を、金属板をプレス加工することによって形成することを特徴とする。

また、前記突起を、金属板を切り起こし加工することによって形成することを特徴とする。

また、前記第2の端子部を、前記金属板に設けた凸部を研削加工することによって前記絶縁層を除去して形成することを特徴とする。

#### 【発明の効果】

##### 【0008】

40

50

本発明によれば、金属板に、ドリルではなく、プレス加工やエッチング加工によって孔明け加工が行えるので、貫通孔を小径に、かつピッチを小さくでき、したがって、高密度配線が可能となる。また、所要厚さの金属板を用いることで、強度的に優れ、抵抗値を低くすることができる半導体装置用パッケージを提供できる。

【発明を実施するための最良の形態】

【0009】

以下本発明における最良の実施の形態を添付図面に基づいて詳細に説明する。

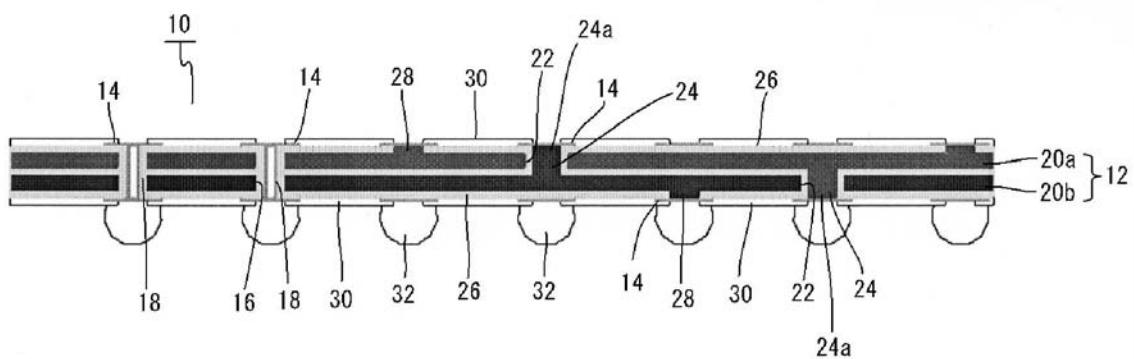

図1は、本実施の形態における半導体装置用パッケージ10の断面図である。

半導体装置用パッケージ10は、コア基板12の表裏面に配線パターン14が形成され、該表裏面の配線パターン14がコア基板12を貫通する貫通孔16に形成された導通部18を介して電気的に接続されて成る。 10

【0010】

コア基板12は、導通部18用の第1の貫通孔16、第2の貫通孔22および突起24が一体的に形成されるとともに、表面に絶縁層26が形成された2枚の金属板20a、20bが、互いの金属板20a、20bの突起24が相手側金属板の第2の貫通孔22に進入するようにして積層されて形成される。絶縁層26は、樹脂を電着塗装して形成されている。なお、電着塗装でなく、塗布など、他の手段によって絶縁層26を形成してもよい。絶縁層26の厚さは特に限定されるものではない。

【0011】

そして各突起24の先端の絶縁層26が除去されて、該先端が相手側金属板の表面に露出して第1の端子部24aに形成され、さらに、各金属板の、相手側金属板の第1の端子部24aが露出する側の表面の所要個所に、絶縁層26から露出する第2の端子部28が形成されている。 20

【0012】

導通部18、絶縁層26、第1の端子部24a、第2の端子部28上に、無電解銅めっき、次いで電解銅めっきを施して、銅めっき皮膜を形成し、この銅めっき皮膜をエッチング加工して、配線パターン14に形成する。

この配線パターン14上に絶縁層(本実施の形態ではソルダーレジスト層)30を形成し、この絶縁層30の一部を開口して配線パターン14を露出させてパッドに形成している。 30

【0013】

本実施の形態では、一層目の配線パターンそのものをパッドに形成したが、ビルドアップ法によりこれら配線パターンを多層に形成してもよいことはもちろんである。

そして下面側のパッドに外部接続用のバンプ32が形成されて半導体装置用パッケージ10に完成される。 40

【0014】

なお、バンプ32の代わりにピン(図示せず)を接合することによって、PGAタイプの半導体装置用パッケージとすることもできる。また、図2(j)において、バンプもピンも取り付けない、LGAタイプの半導体装置用パッケージとして用いることもできる。

上面側のパッド14に半導体チップ(図示せず)をフリップチップ接続し、半導体チップとパッケージ上面との間にアンダーフィル樹脂(図示せず)を充填して半導体装置とすることができる。

【0015】

前記2枚の金属板20a、20bのうちの一方を電源層、他方を接地層として用いることができる。

金属板20a、20bは、任意の厚さのものを選定できる。例えば金属板に200μm程度の厚さのものを用いれば、強度的に優れ、また抵抗値も減じることができ、好適である。

また、金属板を用いるので、各種の孔明け加工も、プレス加工やエッチング加工で、小径に、かつピッチも狭く容易に行えるので、高密度配線が可能となる。例えば、第1の貫 50

通孔 1 6 や第 2 の貫通孔 2 2 の孔径は 40  $\mu\text{m}$  程度までの小径に、また孔間のピッチも 40  $\mu\text{m}$  程度までに小さくできるので、高密度配線が可能となる。

金属板 2 0 a、2 0 b の材質は特に限定されないが、4 2 アロイ (FeNi 合金) や銅合金材を用いることができる。

#### 【0016】

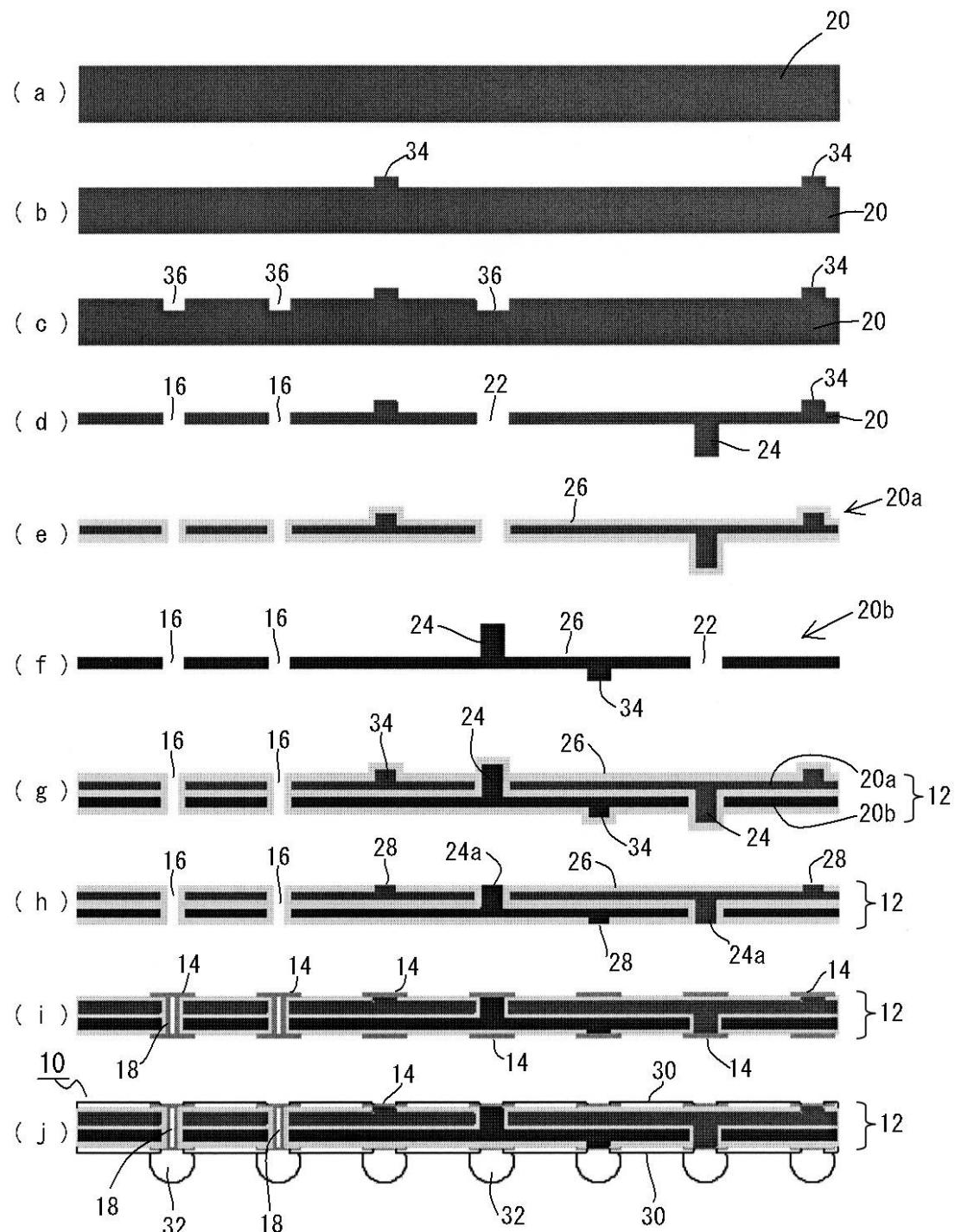

次に、製造方法の一例について説明する。

図 2 は、エッティング加工によってコア基板 1 2 を形成し、半導体装置用パッケージ 1 0 に組み立てる工程図である。

まず、金属板 2 0 (図 2 (a)) の片面をエッティング加工し、凸部 3 4 を形成する (図 2 (b))。

なお、エッティング加工はフォトリソグラフィーで行い、マスクとなるレジストパターンを形成したり、除去したりする工程が必要であるが、説明を省略する (以下の工程においても同じ)。

#### 【0017】

次に、金属板 2 0 の同じ片面側に、第 1 の貫通孔 1 6、第 2 の貫通孔 2 2 となる部位にエッティングにより穴 3 6 を形成する (図 2 (c))。

次に、裏面側をハーフエッティングして、穴 3 6 を貫通させて、第 1 の貫通孔 1 6、第 2 の貫通孔 2 2 を形成するとともに、突起 2 4 を形成する (図 2 (d))。

次に、電着塗装によって、絶縁層 2 6 を金属板 2 0 に形成する。絶縁層 2 6 は、第 1 の貫通孔 1 6 内、第 2 の貫通孔 2 2 内、凸部 3 4 上、突起 2 4 上にも形成される。

このようにして、金属板 2 0 a が形成される (図 2 (e))。

#### 【0018】

同様の工程により金属板をエッティング加工して、もう一方の金属板 2 0 b を形成する (図 2 (f))。この金属板 2 0 b にも、第 1 の貫通孔 1 6、第 2 の貫通孔 2 2、凸部 3 4、突起 2 4 が形成され、さらに表面に絶縁層 2 6 が形成される。

#### 【0019】

次に、図 2 (g) に示すように、2 枚の金属板 2 0 a、2 0 b を、互いの金属板の突起 2 4 が相手側金属板の第 2 の貫通孔 2 2 に進入するようにして積層してコア基板 1 2 を形成する。

2 枚の金属板 2 0 a、2 0 b は、別途接着剤により接着して一体化してもよいが、絶縁層 2 6 に粘着性のある樹脂を用い、この絶縁層 2 6 により接着し、キュアして一体化するようにしてもよい。

#### 【0020】

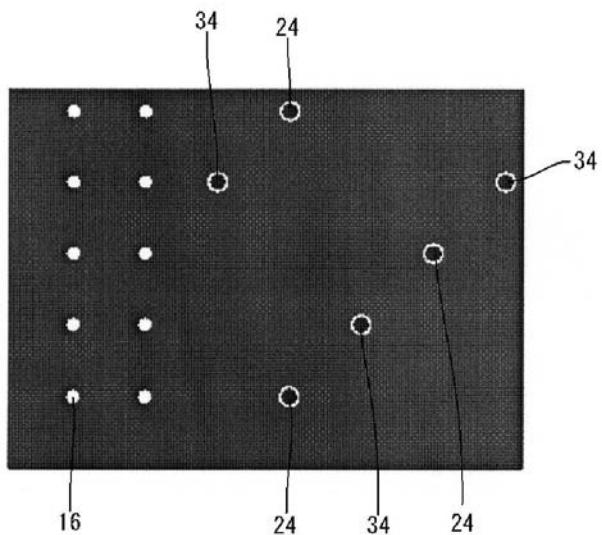

次に、各突起 2 4 の先端面上の絶縁層 2 6 を研削して除去し、先端を相手側金属板の表面に露出して第 1 の端子部 2 4 a に形成するとともに、各凸部 3 4 の先端面上の絶縁層 2 6 を研削して除去することにより、各金属板 2 2 a、2 2 b の、相手側金属板の第 1 の端子部 2 4 a が露出する側の表面に、絶縁層 2 6 から露出する第 2 の端子部 2 8 を形成する (図 2 (h))。なお、図 3 は、2 枚の金属板 2 0 a、2 0 b を積層した状態における、第 1 の貫通孔 1 6、突起 2 4、凸部 3 4 の位置を示す平面図である。なお、第 1 の貫通孔 1 6、突起 2 4、凸部 3 4 の配置はこれに限定されることはもちろんである。

#### 【0021】

次に、無電解銅めっき、次いで電解銅めっきを施して、第 1 の貫通孔 1 6 内に導通部 1 8 を形成するとともに、コア基板 1 2 の表裏面に銅めっき皮膜を形成し、この同めっき皮膜をエッティングして配線パターン (パッド) 1 4 を形成する (図 2 (i))。

#### 【0022】

次いで、配線パターン 1 4 を覆って絶縁層 (ソルダーレジスト層) 3 0 を形成するとともに、露光、現像して、パッド 1 4 を露出させる。

そして一方の面の側に、外部接続端子となるバンプ 3 2 を形成して半導体装置用パッケージ 1 0 に完成できる。

なお、上記では両側に 1 層ずつの配線パターン 1 4 を形成したが、ビルドアップ法によ

10

20

30

40

50

り適宜複数層の配線パターンに形成することができる。

【0023】

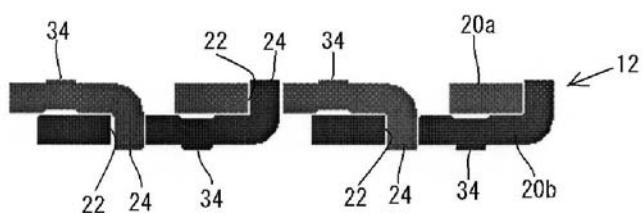

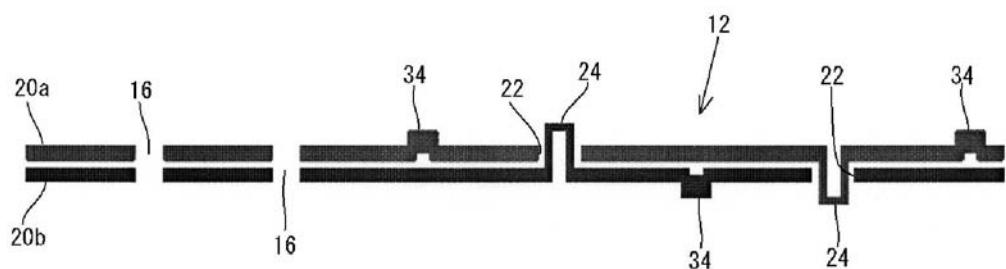

図4は、2枚の金属板20a、20bをプレス方式で形成する実施の形態の説明図であり、それぞれの金属板20a、20bをプレス加工によって形成した後、互いの金属板の突起24が相手側金属板の第2の貫通孔22に進入するようにして積層した状態を示す部分説明図である。

【0024】

本実施の形態では、各金属板に、第1の貫通孔16（図示せず）および第2の貫通孔22をポンチによって容易に形成できる。また、凸部34は、金属板を裏面側から突き上げることによって、反対側に盛り上げるようにして形成している。また本実施の形態では、突起34は、凸部34とは反対方向に、金属板を切り起こすことによって形成している。金属板を切り起こすことによって生じた孔は、金属板に被覆する絶縁層26（図示せず）によって埋めるようにするとよい。

【0025】

上記のようにして形成した金属板20a、20bを図4のように積層してコア基板12を形成した後は、図2（g）～図2（j）の工程と同様の工程により、半導体装置用パッケージ10に形成できる。

なお、本実施の形態においても、第1の貫通孔16、第2の貫通孔22、突起24、凸部34等の配置は任意である。

【0026】

図5は、プレス方式によるさらに他の実施の形態を示す説明図であり、それぞれの金属板20a、20bをプレス加工によって形成した後、互いの金属板の突起24が相手側金属板の第2の貫通孔22に進入するようにして積層した状態を示す説明図である。

本実施の形態では、突起24、凸部34の両方を、金属板を裏面側から突き上げる方式で形成している。なお、図5では絶縁層26を省略している。

【0027】

上記のようにして形成した金属板20a、20bを図5のように積層してコア基板12を形成した後、図2（g）～図2（j）の工程と同様の工程により、半導体装置用パッケージ10に形成できる。

なお、本実施の形態においても、第1の貫通孔16、第2の貫通孔22、突起24、凸部34等の配置は任意である。

なお、以上の各実施の形態において、凸部34を形成せず、この部位の第2の端子部28は、単に絶縁層26をエッティングして除去し、金属板を直接に露出させることによって形成してもよい（図示せず）。

【図面の簡単な説明】

【0028】

【図1】本実施の形態における半導体装置用パッケージの断面図である。

【図2】図1の半導体装置用パッケージをエッティング加工によって形成する場合の工程図である。

【図3】第1の貫通孔、突起、凸部等の配置の一例を示す平面図である。

【図4】2枚の金属板をプレス方式で形成し、積層してコア基板に形成した状態を示す部分説明図である。

【図5】2枚の金属板をプレス方式で形成し、積層してコア基板に形成した状態を示す他の実施の形態の説明図である。

【符号の説明】

【0029】

- 10 半導体装置用パッケージ

- 12 コア基板

- 14 配線パターン（パッド）

- 16 第1の貫通孔

10

20

30

40

50

- 1 8 導通部

2 0 a、2 0 b 金属板

2 2 第2の貫通孔

2 4 突起

2 4 a 第1の端子部

2 6 絶縁層

2 8 第2の端子部

3 0 絶縁層(ソルダーレジスト層)

3 2 パンプ

3 4 凸部

3 6 穴

10

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 立岩 昭彦

長野県長野市小島田町80番地 新光電気工業株式会社内

審査官 宮崎 園子

(56)参考文献 実開昭60-109362 (JP, U)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12