(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6574744号

(P6574744)

(45) 発行日 令和1年9月11日(2019.9.11)

(24) 登録日 令和1年8月23日(2019.8.23)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 652C |

| HO1L 29/12  | (2006.01) | HO1L 29/78 | 653C |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 652K |

| HO1L 29/739 | (2006.01) | HO1L 29/78 | 652J |

| HO1L 29/06  | (2006.01) | HO1L 29/78 | 652T |

請求項の数 4 (全 51 頁) 最終頁に続く

(21) 出願番号

特願2016-182065 (P2016-182065)

(22) 出願日

平成28年9月16日(2016.9.16)

(65) 公開番号

特開2018-46255 (P2018-46255A)

(43) 公開日

平成30年3月22日(2018.3.22)

審査請求日

平成30年9月6日(2018.9.6)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(73) 特許権者 317011920

東芝デバイス&amp;ストレージ株式会社

東京都港区芝浦一丁目1番1号

(74) 代理人 100108062

弁理士 日向寺 雅彦

(72) 発明者 北川 光彦

東京都港区芝浦一丁目1番1号 株式会社

東芝内

審査官 柴垣 宙央

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電形の第1半導体領域と、

前記第1半導体領域の上に設けられた第2導電形の第2半導体領域と、

前記第2半導体領域の上に選択的に設けられた第1導電形の第3半導体領域と、

前記第3半導体領域の上に設けられ、前記第2半導体領域および前記第3半導体領域と電気的に接続された第1電極と、

前記第1半導体領域の上に設けられ、第1方向において前記第2半導体領域と離間した第2導電形の第4半導体領域と、

前記第4半導体領域の上に選択的に設けられた第1導電形の第5半導体領域と、

前記第5半導体領域の上に設けられ、前記第1電極と離間し、前記第4半導体領域および前記第5半導体領域と電気的に接続された第2電極と、

前記第1半導体領域の上に設けられ、前記第1方向において第1ゲート絶縁層を介して前記第2半導体領域と対面する第1ゲート電極と、

前記第4半導体領域と前記第1ゲート電極との間に設けられ、第2ゲート絶縁層を介して前記第4半導体領域と対面する第2ゲート電極と、

前記第1半導体領域の下に設けられた第2導電形の第6半導体領域と、

前記第6半導体領域の下に選択的に設けられた第1導電形の第7半導体領域と、

前記第7半導体領域の下に設けられ、前記第6半導体領域および前記第7半導体領域と電気的に接続された第3電極と、

10

20

前記第1半導体領域の下に設けられ、前記第1方向において第3ゲート絶縁層を介して前記第6半導体領域と対面する第3ゲート電極と、

を備えた半導体装置。

**【請求項2】**

前記第1半導体領域の下に設けられ、前記第1方向において前記第6半導体領域と離間した第2導電形の第8半導体領域と、

前記第8半導体領域の下に選択的に設けられた第1導電形の第9半導体領域と、

前記第9半導体領域の下に設けられ、前記第3電極と離間し、前記第8半導体領域および前記第9半導体領域と電気的に接続された第4電極と、

前記第8半導体領域と前記第3ゲート電極との間に設けられ、第4ゲート絶縁層を介して前記第8半導体領域と対面する第4ゲート電極と、

をさらに備えた請求項1記載の半導体装置。

**【請求項3】**

前記第1半導体領域の上に設けられ、前記第1方向において、前記第2半導体領域と前記第4半導体領域との間に位置し、前記第1ゲート絶縁層および前記第2ゲート絶縁層を含む第1絶縁部と、

前記第1半導体領域の上に設けられ、前記第1方向において、前記第1絶縁部との間に前記第2半導体領域が位置する第2絶縁部と、

前記第1半導体領域の上に設けられ、前記第1方向において、前記第1絶縁部との間に前記第4半導体領域が位置する第3絶縁部と、

をさらに備え、

前記第1絶縁部の少なくとも一部と前記第2絶縁部の少なくとも一部との間の前記第1方向における距離は、1.0 μm以下であり、

前記第1絶縁部の少なくとも一部と前記第3絶縁部の少なくとも一部との間の前記第1方向における距離は、1.0 μm以下である請求項1または2に記載の半導体装置。

**【請求項4】**

前記第1絶縁部の前記第1方向における長さは、前記第1絶縁部の少なくとも一部と前記第2絶縁部の少なくとも一部との間の前記距離の2倍以上であり、前記第1絶縁部の少なくとも一部と前記第3絶縁部の少なくとも一部との間の前記距離の2倍以上である請求項3記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の実施形態は、半導体装置に関する。

**【背景技術】**

**【0002】**

近年、電力制御用の半導体装置として、MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor : 金属酸化物半導体電界効果トランジスタ) や、IGBT (insulated gate bipolar transistor : 絶縁ゲートバイポーラトランジスタ)、IGET (Injection Enhanced Gate Transistor : 注入促進型絶縁ゲートトランジスタ) 等が用いられている。MOSFETは、キャリアとして電子および正孔のどちらか一方を用いるユニポーラ型の半導体装置であるため、通電方向にビルトインポテンシャルが存在しない。このため、IGBTやIGETなどのバイポーラ型の半導体装置に比べて、低い印加電圧でも通電させることができるもの、その通電能力は、バイポーラ型の半導体装置に劣る。

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【特許文献1】特開2008-300474号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

10

20

30

40

50

## 【0004】

本発明が解決しようとする課題は、通電能力を向上できる半導体装置を提供することである。

## 【課題を解決するための手段】

## 【0005】

実施形態に係る半導体装置は、第1導電形の第1半導体領域と、第2導電形の第2半導体領域と、第1導電形の第3半導体領域と、第1電極と、第2導電形の第4半導体領域と、第1導電形の第5半導体領域と、第2電極と、第1ゲート電極と、第2ゲート電極と、第2導電形の第6半導体領域と、第1導電形の第7半導体領域と、第3電極と、第3ゲート電極と、を有する。前記第2半導体領域は、前記第1半導体領域の上に設けられている。

前記第3半導体領域は、前記第2半導体領域の上に選択的に設けられている。前記第1電極は、前記第3半導体領域の上に設けられ、前記第2半導体領域および前記第3半導体領域と電気的に接続されている。前記第4半導体領域は、前記第1半導体領域の上に設けられ、第1方向において前記第2半導体領域と離間している。前記第5半導体領域は、前記第4半導体領域の上に選択的に設けられている。前記第2電極は、前記第5半導体領域の上に設けられ、前記第1電極と離間し、前記第4半導体領域および前記第5半導体領域と電気的に接続されている。前記第1ゲート電極は、前記第1半導体領域の上に設けられ、前記第1方向において第1ゲート絶縁層を介して前記第2半導体領域と対面している。前記第2ゲート電極は、前記第4半導体領域と前記第1ゲート電極との間に設けられ、第2ゲート絶縁層を介して前記第4半導体領域と対面している。前記第6半導体領域は、前記第1半導体領域の下に設けられている。前記第7半導体領域は、前記第6半導体領域の下に選択的に設けられている。前記第3電極は、前記第7半導体領域の下に設けられ、前記第6半導体領域および前記第7半導体領域と電気的に接続されている。前記第3ゲート電極は、前記第1半導体領域の下に設けられ、前記第1方向において第3ゲート絶縁層を介して前記第6半導体領域と対面している。

## 【図面の簡単な説明】

## 【0006】

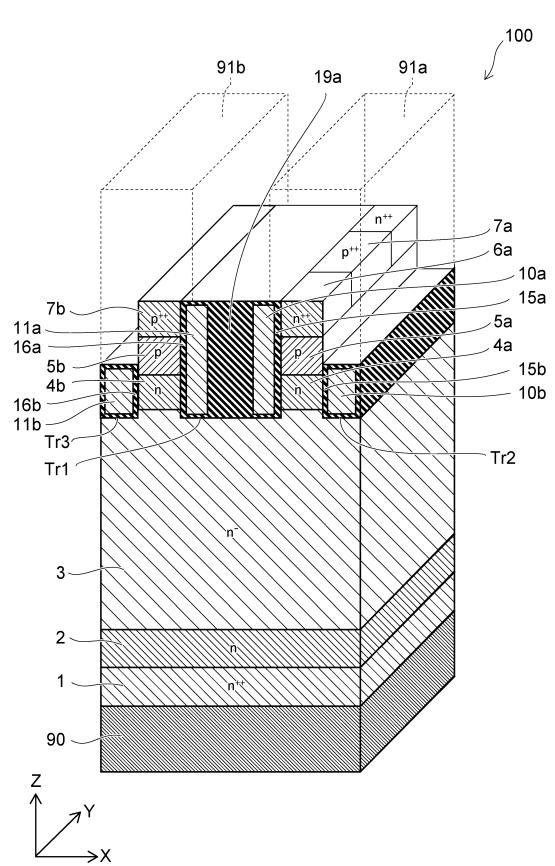

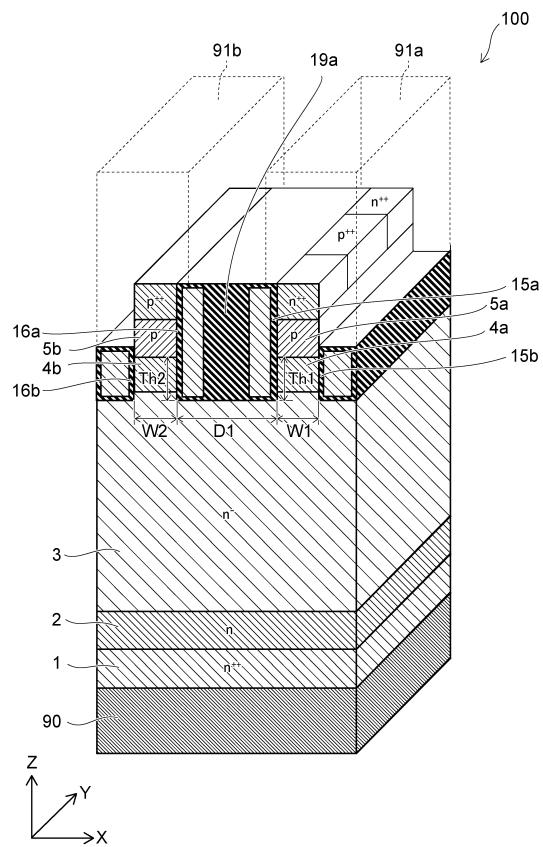

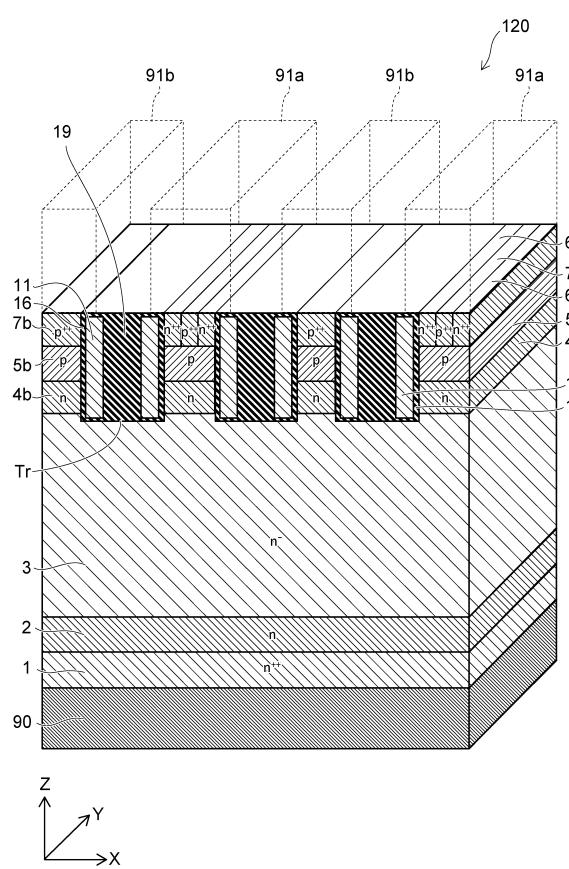

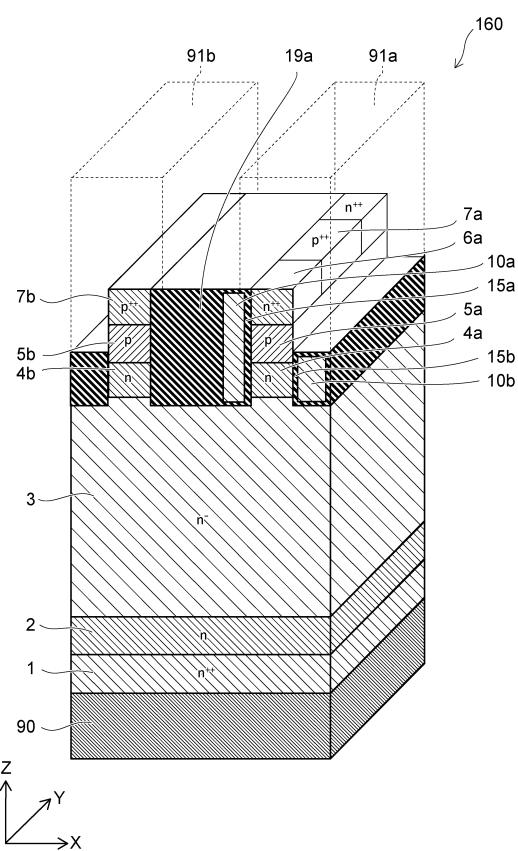

【図1】第1実施形態に係る半導体装置の一部を表す斜視断面図である。

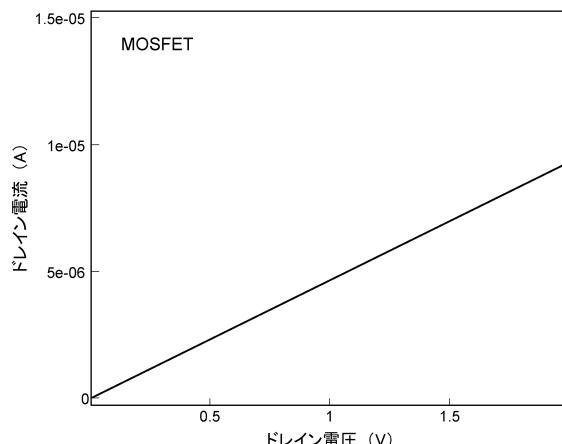

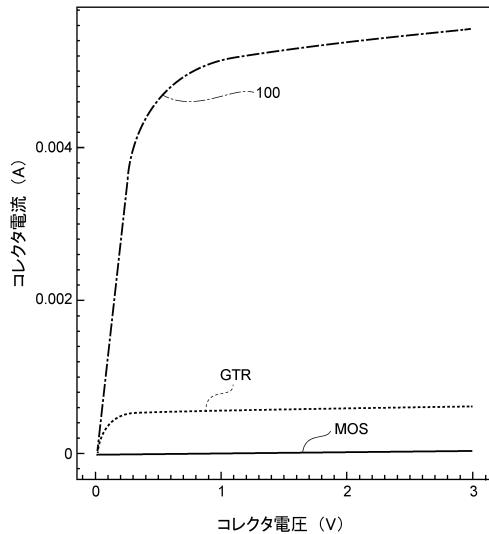

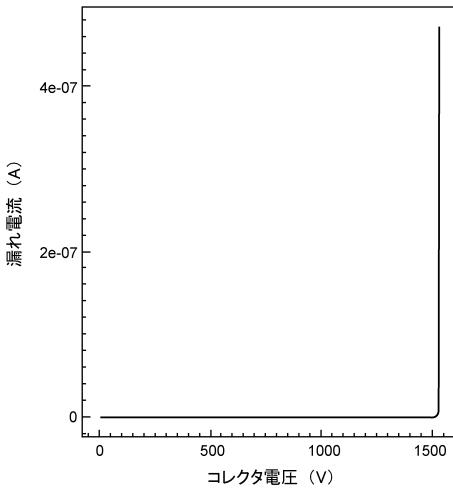

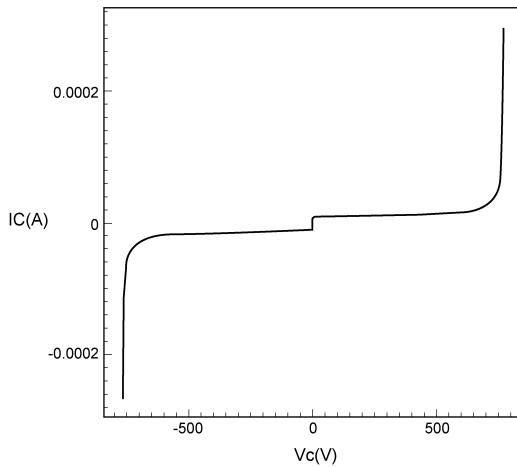

【図2】MOSFETの電流電圧特性を表すシミュレーション結果である。

【図3】IGBT(IGBT)の電流電圧特性を表すシミュレーション結果である。

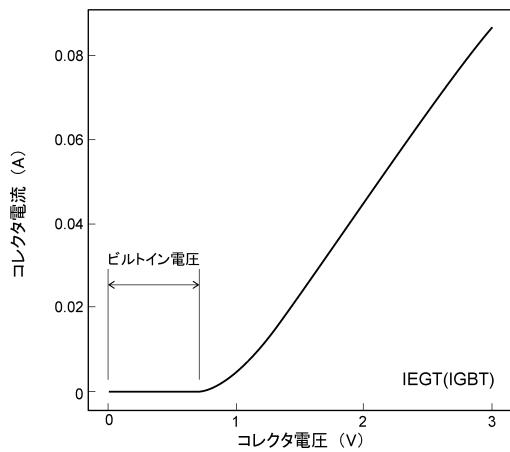

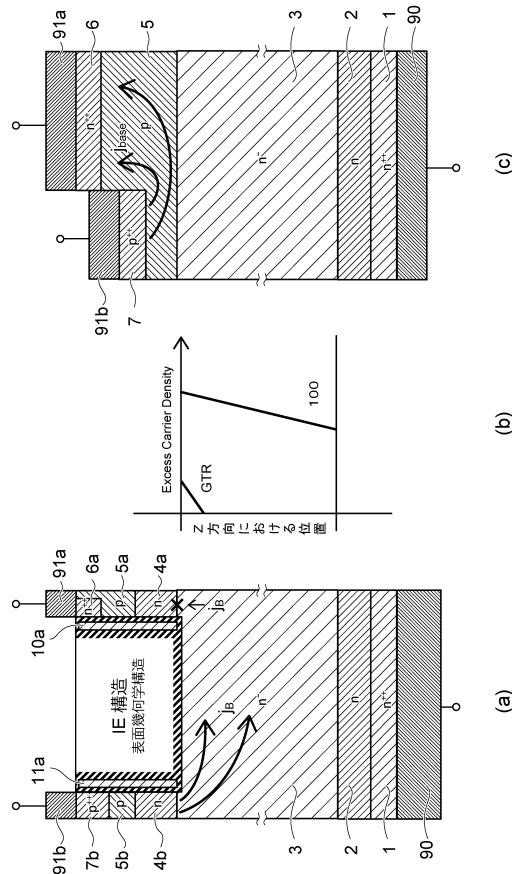

【図4】第1実施形態に係る半導体装置の動作原理を表す概念図である。

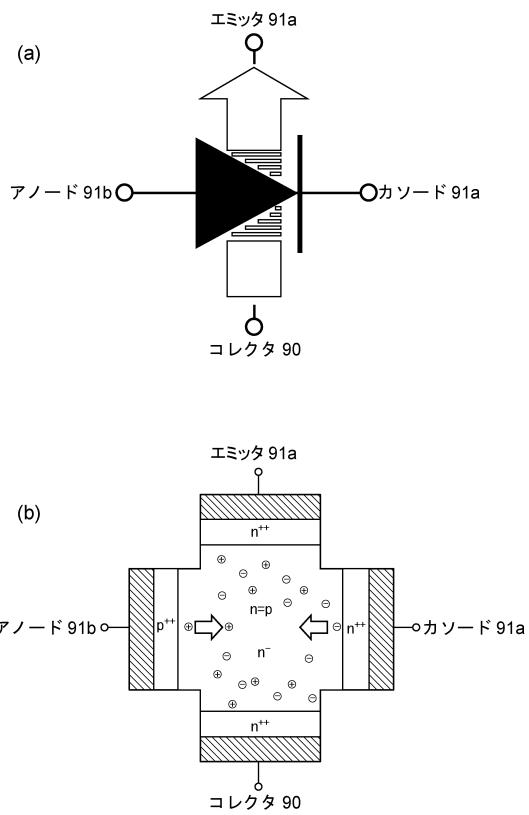

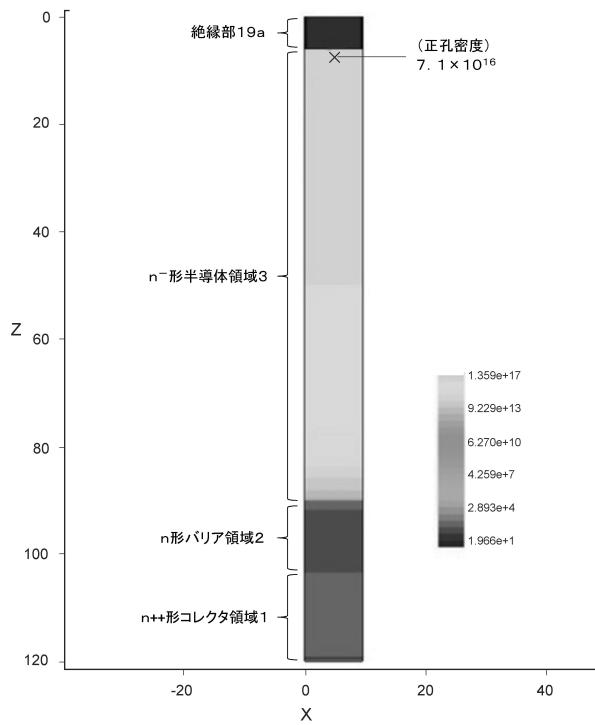

【図5】(a)第1実施形態に係る半導体装置の一部を表す断面図である。(b)第1実施形態に係る半導体装置と参考例に係る半導体装置における過剰キャリアの濃度を比較するグラフである。(c)参考例に係る半導体装置の一部を表す断面図である。

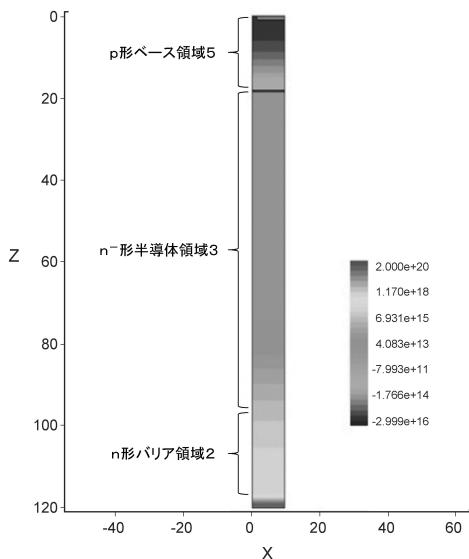

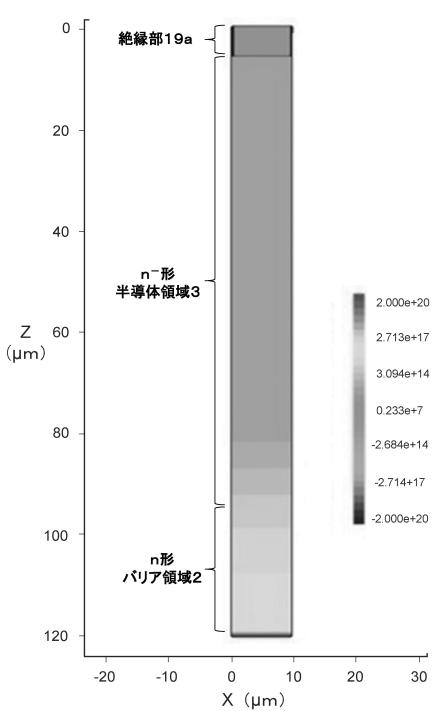

【図6】シミュレーションに用いた参考例に係る半導体装置の断面構造である。

【図7】参考例に係る半導体装置のオン状態における正孔の分布を表すシミュレーション結果である。

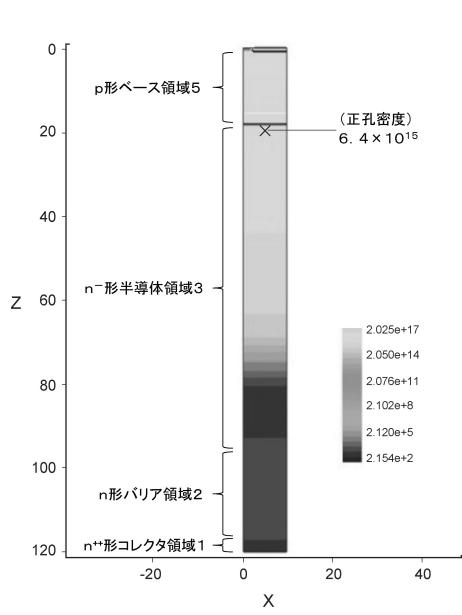

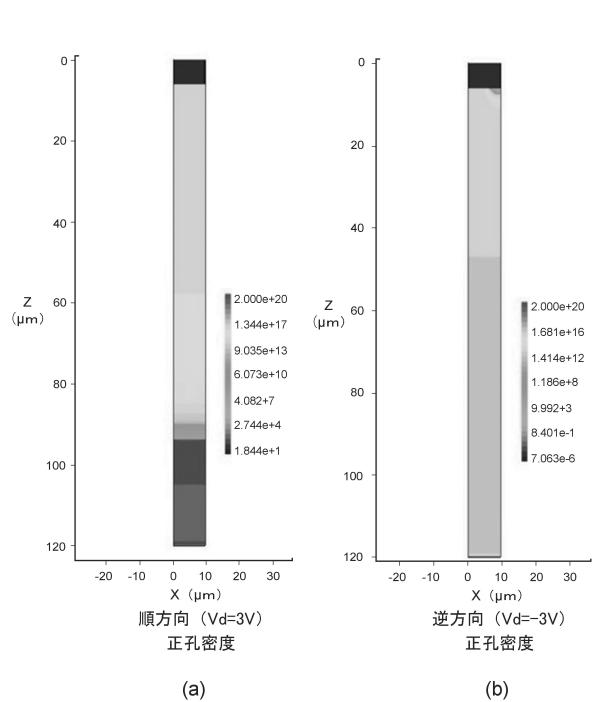

【図8】本実施形態に係る半導体装置のオン状態における正孔の分布を表すシミュレーション結果である。

【図9】第1実施形態に係る半導体装置と参考例に係る半導体装置の通電特性を表すシミュレーション結果である。

【図10】シミュレーションに用いた第1実施形態に係る半導体装置の断面構造である。

【図11】第1実施形態に係る半導体装置において順方向および逆方向へ通電させた場合のオン状態における正孔の濃度を表すシミュレーション結果である。

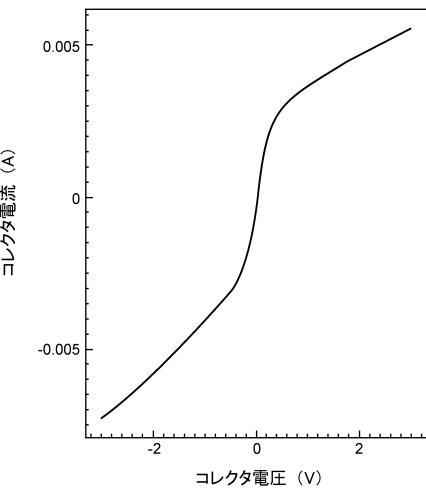

【図12】第1実施形態に係る半導体装置における双方向の通電特性を表すシミュレーション結果である。

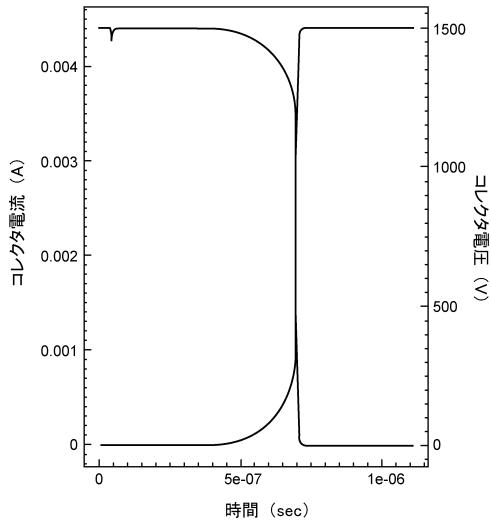

【図13】第1実施形態に係る半導体装置のターンオフ時のコレクタ電圧とコレクタ電流の変化を表すシミュレーション結果である。

【図14】第1実施形態に係る半導体装置の静耐圧波形を表すシミュレーション結果である。

10

20

30

40

50

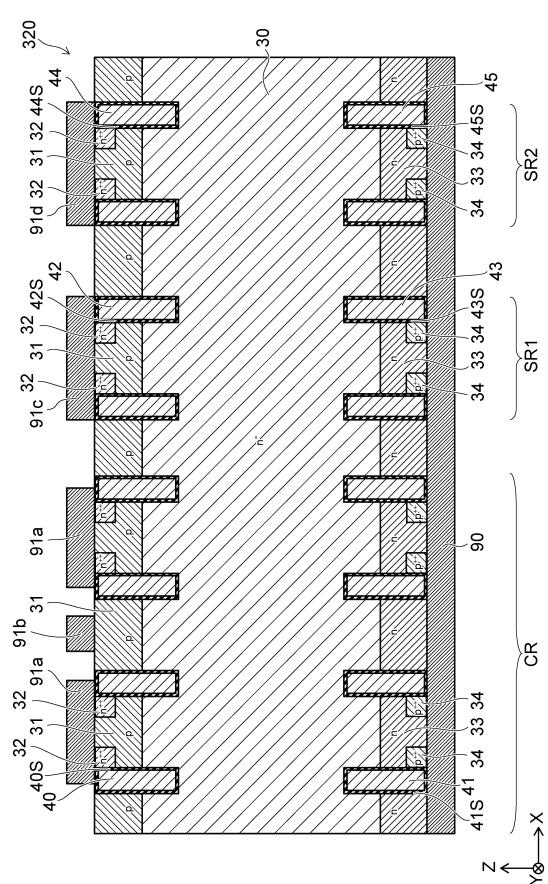

- 【図15】第1実施形態に係る半導体装置の一部を表す斜視断面図である。

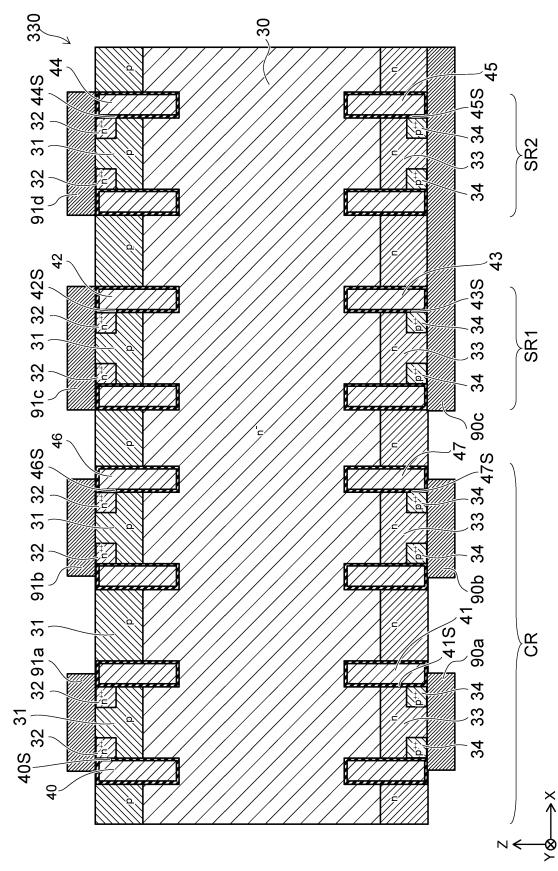

- 【図16】第1実施形態の第1変形例に係る半導体装置の一部を表す斜視断面図である。

- 【図17】第1実施形態の第2変形例に係る半導体装置の一部を表す斜視断面図である。

- 【図18】第1実施形態の第3変形例に係る半導体装置の一部を表す斜視断面図である。

- 【図19】第1実施形態の第4変形例に係る半導体装置の一部を表す斜視断面図である。

- 【図20】第1実施形態の第5変形例に係る半導体装置の一部を表す斜視断面図である。

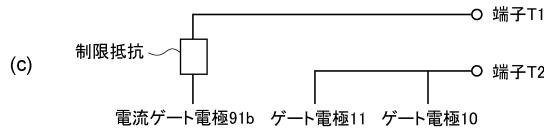

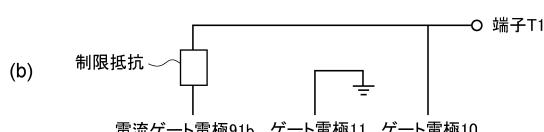

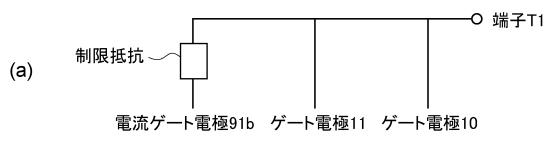

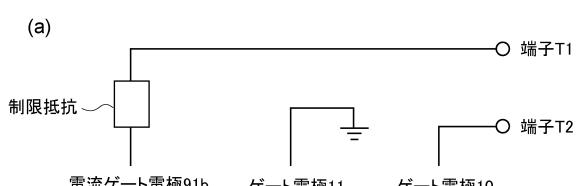

- 【図21】第1実施形態に係る半導体装置の制御回路の一部を表す回路図である。

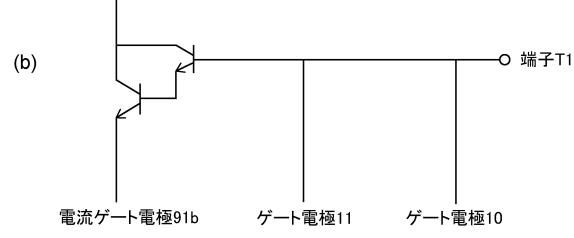

- 【図22】第1実施形態に係る半導体装置の制御回路の一部を表す回路図である。

- 【図23】第1実施形態の変形例に係る半導体装置の一部を表す斜視断面図である。

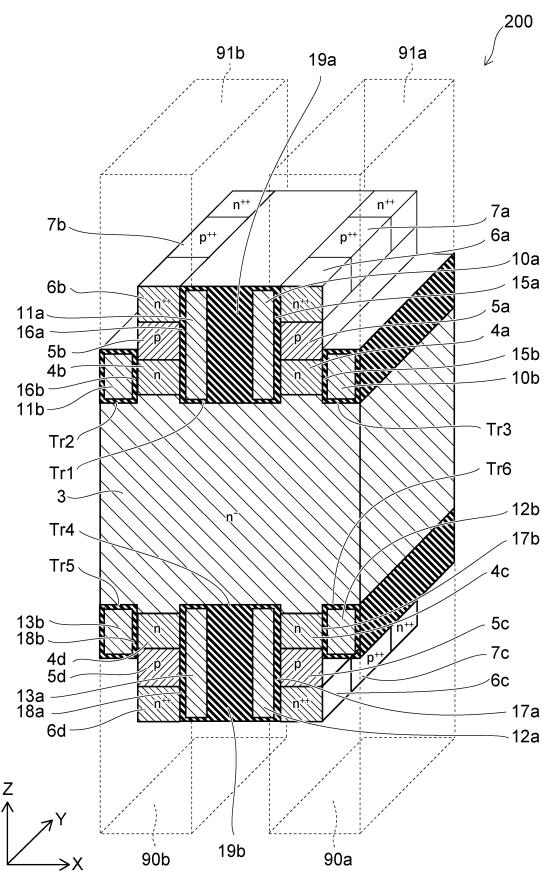

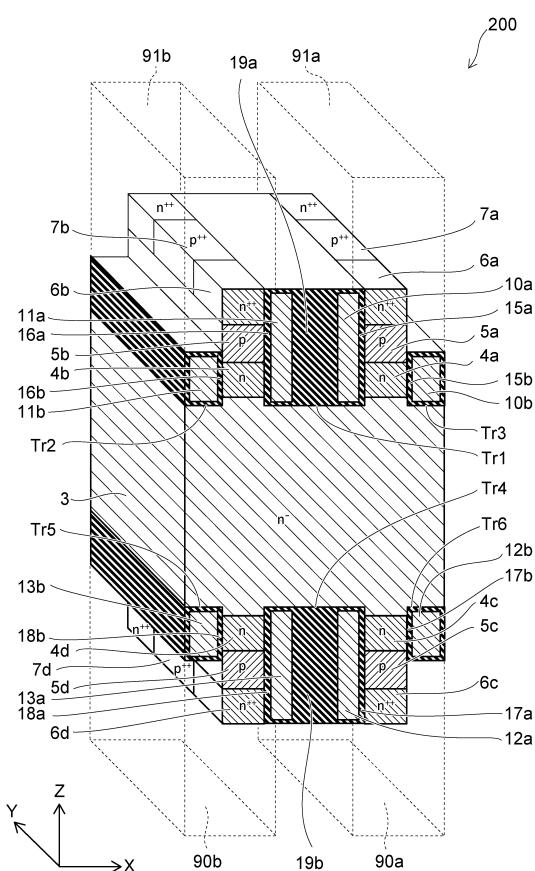

- 【図24】第2実施形態に係る半導体装置の一部を表す斜視断面図である。 10

- 【図25】第2実施形態に係る半導体装置の一部を表す斜視断面図である。

- 【図26】第2実施形態に係る半導体装置の駆動方法の一例を表すフロー・チャートである。

- 【図27】第2実施形態に係る半導体装置の駆動方法の一例を表すフロー・チャートである。

- 【図28】第2実施形態に係る半導体装置の電流電圧特性の一例を表すグラフである。

- 【図29】第2実施形態に係る半導体装置のターンオフ時の波形を表すシミュレーション結果である。

- 【図30】参考例に係る半導体装置の断面構造と耐圧を表す図である。 20

- 【図31】第2実施形態に係る半導体装置の断面構造と耐圧印加時の素子内部の電界を表す図である。

- 【図32】第2実施形態に係る半導体装置の順方向と逆方向の耐圧波形を表すシミュレーション結果である。

- 【図33】第2実施形態に係る半導体装置で実現可能な動作モードの例を表す図である。

- 【図34】第2実施形態に係る半導体装置の応用例を表す断面図である。

- 【図35】第2実施形態の変形例に係る半導体装置の一部を表す斜視断面図である。

- 【図36】第3実施形態に係る半導体装置の一部を表す断面図である。

- 【図37】第3実施形態の第1変形例に係る半導体装置の一部を表す断面図である。

- 【図38】第3実施形態の第2変形例に係る半導体装置の一部を表す断面図である。

- 【図39】第3実施形態の第3変形例に係る半導体装置の一部を表す断面図である。 30

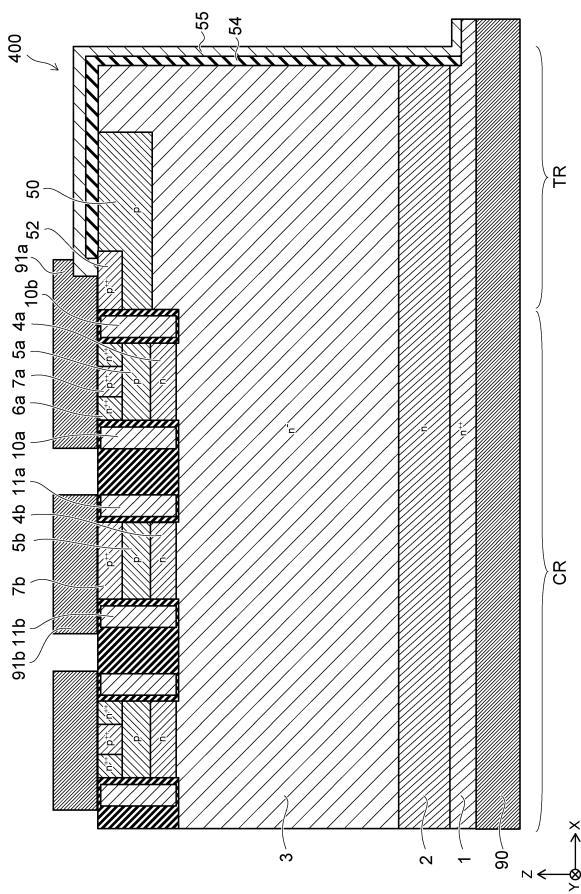

- 【図40】第4実施形態に係る半導体装置の一部を表す断面図である。

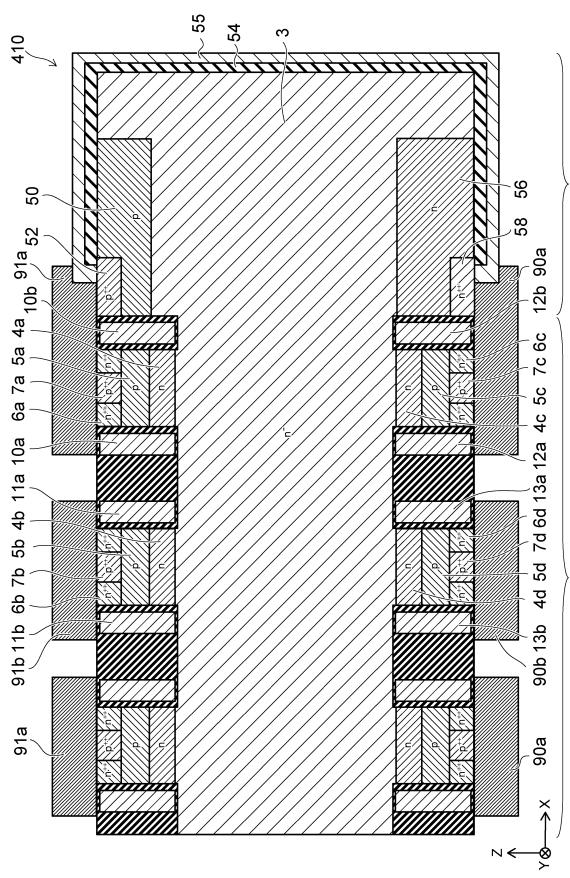

- 【図41】第4実施形態の第1変形例に係る半導体装置の一部を表す断面図である。

- 【図42】第4実施形態の第2変形例に係る半導体装置の一部を表す断面図である。

- 【図43】第4実施形態の第3変形例に係る半導体装置の一部を表す断面図である。

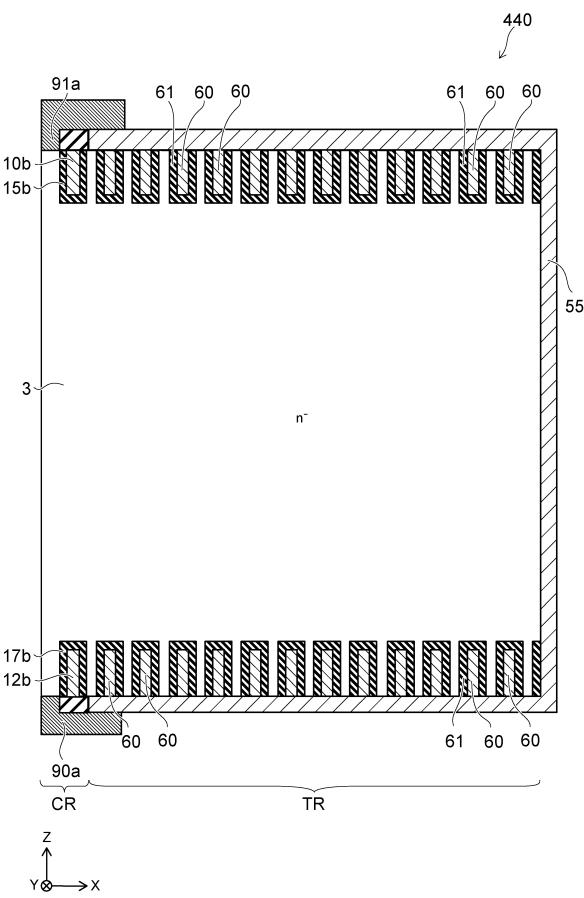

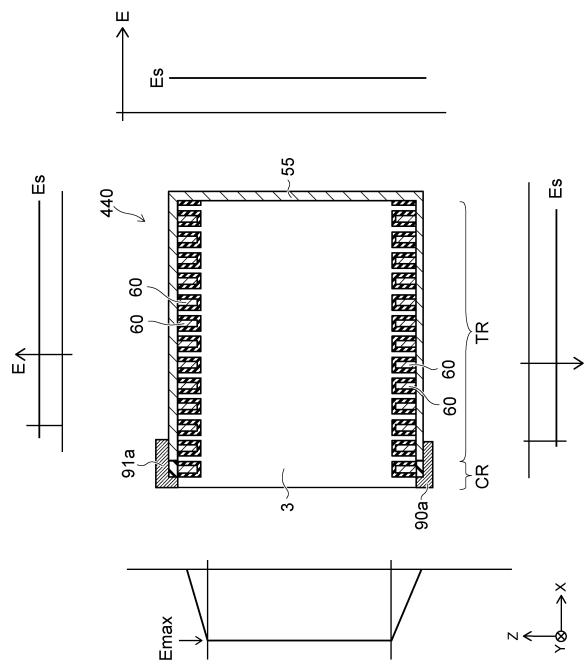

- 【図44】シミュレーションに用いた第4実施形態の第3変形例に係る半導体装置の一部を表す断面図である。

- 【図45】図44に表す構造における電位分布を表すシミュレーション結果である。

- 【図46】第4実施形態の第4変形例に係る半導体装置の一部を表す断面図である。

- 【図47】第4実施形態の第4変形例に係る半導体装置の一部を表す断面図および各部の電界を表すグラフである。 40

- 【図48】第4実施形態の第4変形例に係る半導体装置のシミュレーション結果である。

- 【図49】第4実施形態の第4変形例に係る半導体装置のシミュレーション結果である。

- 【図50】第4実施形態の第4変形例に係る半導体装置の耐圧波形を表すシミュレーション結果である。

- 【図51】第4実施形態の第5変形例に係る半導体装置の一部を表す断面図である。

- 【図52】第4実施形態の第5変形例に係る半導体装置のシミュレーション結果である。

- 【図53】第5実施形態に係る半導体装置を表す平面図である。

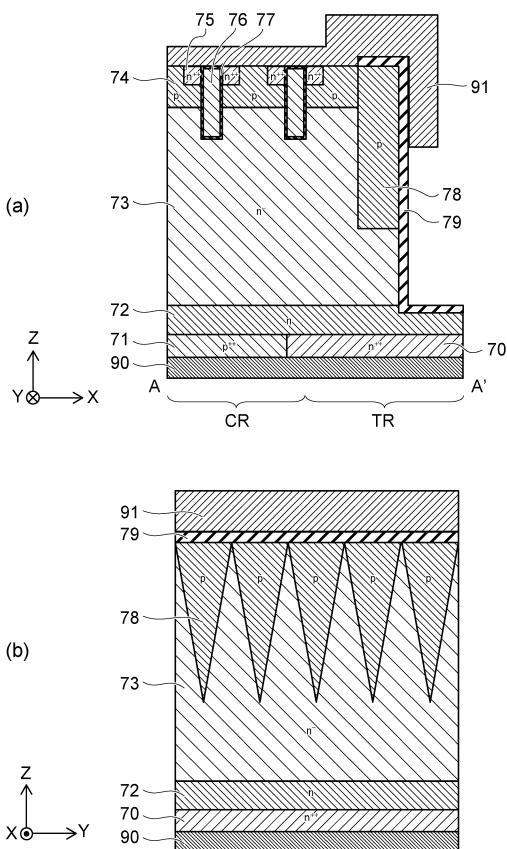

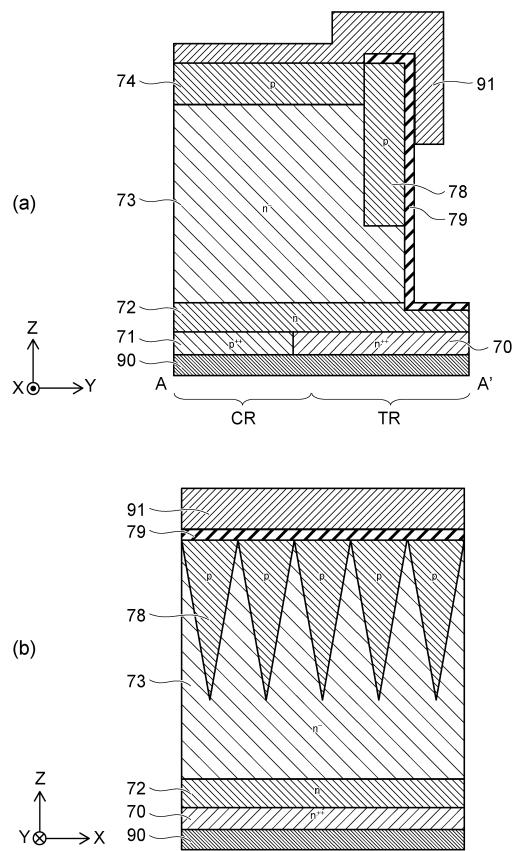

- 【図54】(a) 図53のA-A'断面図である。(b) 図53のB-B'断面図である。

- 【図55】(a) 図53のC-C'断面図である。(b) 図53のD-D'断面図である。 50

。

**【発明を実施するための形態】**

**【0007】**

以下に、本発明の各実施形態について図面を参照しつつ説明する。

なお、図面は模式的または概念的なものであり、各部分の厚みと幅との関係、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

また、本願明細書と各図において、既に説明したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

各実施形態の説明には、XYZ直交座標系を用いる。コレクタ電極90(90a)から

エミッタ電極91(91a)に向かう方向をZ方向とし、Z方向に対して垂直であり相互に直交する2方向をX方向(第1方向)およびY方向とする。

10

以下の説明において、 $n^{++}$ 、 $n^+$ 、 $n$ 、 $n^-$ 及び $p^{++}$ 、 $p^+$ 、 $p$ 、 $p^-$ の表記は、各導電形における不純物濃度の相対的な高低を表す。すなわち、「+」が付されている表記は、「+」および「-」のいずれも付されていない表記よりも不純物濃度が相対的に高く、「-」が付されている表記は、いずれも付されていない表記よりも不純物濃度が相対的に低いことを示す。また、「+」が複数付されている表記は、その数が多くなるほど、不純物濃度が高いことを示している。

以下で説明する各実施形態について、各半導体領域のp形とn形を反転させて実施することも可能である。

20

**【0008】**

(第1実施形態)

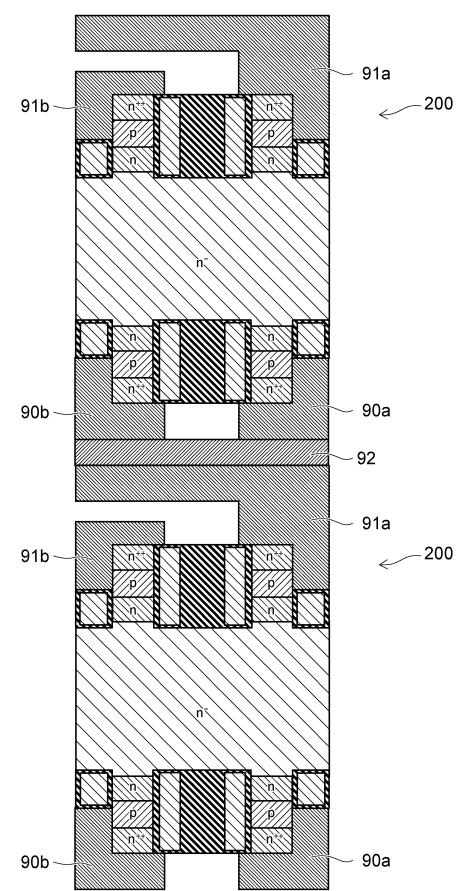

図1は、第1実施形態に係る半導体装置100の一部を表す斜視断面図である。

なお、図1では、エミッタ電極91aおよび電流ゲート電極91bが透過して表されている。

**【0009】**

図1に表すように、半導体装置100は、 $n^{++}$ 形コレクタ領域1と、n形バリア領域2と、 $n^-$ 形半導体領域3と、n形バリア領域4aおよび4bと、p形ベース領域5aと、p形アノード領域5bと、 $n^{++}$ 形コンタクト領域6aおよび6bと、 $p^{++}$ 形コンタクト領域7aおよび7bと、ゲート電極10a、10b、11a、および11bと、ゲート絶縁層15a、15b、16a、および16bと、コレクタ電極90と、エミッタ電極91aと、電流ゲート電極91bと、を有する。

30

**【0010】**

半導体装置100の裏面には、コレクタ電極90が設けられている。 $n^{++}$ 形コレクタ領域1は、コレクタ電極90の上に設けられ、コレクタ電極90と電気的に接続されている。

n形バリア領域2は、 $n^{++}$ 形コレクタ領域1の上に設けられている。

$n^-$ 形半導体領域3は、n形バリア領域2の上に設けられている。

**【0011】**

n形バリア領域4aは、 $n^-$ 形半導体領域3の一部の上に設けられている。

p形ベース領域5aは、n形バリア領域4aの上に設けられている。

$n^{++}$ 形コンタクト領域6aおよび $p^{++}$ 形コンタクト領域7aは、p形ベース領域5aの上に選択的に設けられている。

**【0012】**

エミッタ電極91aは、 $n^{++}$ 形コンタクト領域6aの上面および一側面と、 $p^{++}$ 形コンタクト領域7aの上面および一側面と、p形ベース領域5aの一側面と、に接しており、これらの半導体領域と電気的に接続されている。

**【0013】**

ゲート電極10aおよび10bは、それぞれ、ゲート絶縁層15aおよび15bを介して $n^-$ 形半導体領域3の上に設けられている。ゲート電極10bのZ方向における長さは

50

、ゲート電極 10 a の Z 方向における長さよりも短い。n 形バリア領域 4 a および p 形ベース領域 5 a は、X 方向において、ゲート電極 10 a と 10 b の間に位置し、ゲート絶縁層 15 a および 15 b を介してゲート電極 10 a および 10 b と対面している。

#### 【0014】

n 形バリア領域 4 b は、n<sup>-</sup>形半導体領域 3 の他の一部の上に設けられており、n 形バリア領域 4 a と X 方向において離間している。

p 形アノード領域 5 b は、n 形バリア領域 4 b の上に設けられている。

p<sup>++</sup> 形コンタクト領域 7 b は、p 形アノード領域 5 b の上に設けられている。

電流ゲート電極 91 b は、p<sup>++</sup> 形コンタクト領域 7 b の上面および一側面と、p 形アノード領域 5 b の一側面と、に接しており、これらの半導体領域と電気的に接続されている。10

#### 【0015】

ゲート電極 11 a および 11 b は、それぞれ、ゲート絶縁層 16 a および 16 b を介して n<sup>-</sup>形半導体領域 3 の上に設けられている。ゲート電極 11 b の Z 方向における長さは、ゲート電極 11 a の Z 方向における長さよりも短い。n 形バリア領域 4 b および p 形アノード領域 5 b は、X 方向において、ゲート電極 11 a と 11 b の間に位置し、ゲート絶縁層 16 a および 16 b を介してゲート電極 11 a および 11 b と対面している。

#### 【0016】

ゲート電極 10 a および 10 b とエミッタ電極 91 aとの間には、ゲート絶縁層 15 a および 15 b が設けられ、これらの電極は離間している。同様に、ゲート電極 11 a および 11 b と電流ゲート電極 91 b との間には、ゲート絶縁層 16 a および 16 b が設けられ、これらのは、離間している。20

#### 【0017】

ゲート電極 10 a は、X 方向において、n 形バリア領域 4 a および p 形ベース領域 5 a と、ゲート電極 11 a と、の間に位置している。ゲート電極 11 a は、X 方向において、n 形バリア領域 4 b および p 形アノード領域 5 b と、ゲート電極 10 a と、の間に位置している。ゲート電極 10 a と 11 a との間には、絶縁部 19 a が設けられ、ゲート電極 10 a と 11 a は、X 方向において離間している。

換言すると、n バリア領域 4 a および p 形ベース領域 5 a は、ゲート電極 10 a および 11 a、ゲート絶縁層 15 a および 16 a、絶縁部 19 a が内部に設けられたトレンチ Tr 1 と、ゲート電極 10 b および ゲート絶縁層 15 b が内部に設けられたトレンチ Tr 2 と、の間に設けられている。また、n バリア領域 4 b および p 形アノード領域 5 b は、トレンチ Tr 1 と、ゲート電極 11 b および ゲート絶縁層 16 b が内部に設けられたトレンチ Tr 3 と、の間に設けられている。30

#### 【0018】

n 形バリア領域 4 a および 4 b、p 形ベース領域 5 a および p 形アノード領域 5 b、p<sup>++</sup> 形コンタクト領域 7 b、ゲート電極 10 a ~ 11 b は、それぞれ、Y 方向に延びている。n<sup>++</sup> 形コンタクト領域 6 a と p<sup>++</sup> 形コンタクト領域 7 a とは、p 形ベース領域 5 a の上において、Y 方向に交互に設けられている。

半導体装置 100 では、例えば、図 1 に表す構造が X 方向において繰り返し設けられている。40

#### 【0019】

次に、各構成要素の材料の一例を説明する。

n<sup>++</sup> 形コレクタ領域 1 と、n 形バリア領域 2 と、n<sup>-</sup> 形半導体領域 3 と、n 形バリア領域 4 a および 4 b と、p 形ベース領域 5 a および 5 b と、n<sup>++</sup> 形コンタクト領域 6 a および 6 b と、p<sup>++</sup> 形コンタクト領域 7 a および 7 b と、は、半導体材料として、シリコンまたは炭化シリコンを含む。半導体材料としてシリコンが用いられる場合、n 形不純物として、ヒ素、リン、またはアンチモンを用いることができ、p 形不純物として、ボロンを用いることができる。

ゲート電極 10 a ~ 11 b は、ポリシリコンなどの導電材料を含む。

ゲート絶縁層 15a～16b および絶縁部 19a は、酸化シリコンなどの絶縁材料を含む。

コレクタ電極 90、エミッタ電極 91a および電流ゲート電極 91b は、アルミニウムなどの金属を含む。

#### 【0020】

次に、本実施形態に係る半導体装置 100 の動作および本実施形態によって解決される課題とその効果について説明する。

図 2 は、MOSFET の電流電圧特性を表すシミュレーション結果である。

図 3 は、IGBT (IGBT) の電流電圧特性を表すシミュレーション結果である。

高耐圧向けに設計された MOSFET では、通電時の高抵抗ベース層 ( $n^-$  形半導体領域 3 に相当) の抵抗をいかに小さくするかということが設計上重要になる。しかし、高抵抗ベース層の厚みや抵抗は、素子の電圧定格を決めた時点ではほぼ決まってしまう。キャリアが電子だけのユニポーラデバイス (MOSFET) は、電流密度が上がるにつれて空間電荷が増加する。その結果、図 2 に表される MOSFET の電流電圧特性のように、流れ 10 の電流に上限がある。

これに対して、キャリアが電子と正孔のバイポーラデバイスは、高抵抗ベース層中に生じる電子と正孔のプラズマ状態(伝導度変調)を利用して、空間電荷の制限が無く、MOSFET (ユニポーラデバイス) よりも桁違いに大きな電流を流すことが可能となる。このことから p-i-n ダイオードや、IGBT (IGBT)、サイリスタなどのバイポーラ動作の素子は、MOSFET (ユニポーラデバイス) に比べて格段に大きな電力を制御 20 することができる。

図 2 と図 3 は、同じ高抵抗ベース層(厚さ約 100 μm、n 形不純物濃度  $1.0 \times 10^{13}$  、1500V 設計)において、MOSFET と IGBT (IGBT) の電流電圧特性をシミュレーションした結果である。例えば、ドレイン電圧およびコレクタ電圧が 2.0 V のときのドレイン電流およびコレクタ電流を比較すると、IGBT は MOSFET に比べて約 1000 倍の電流を流す能力があることが分かる。

#### 【0021】

しかし、ダイオードや IGBT (IGBT)、サイリスタなどの素子は、図 3 に表されるように、その伝導度変調特性の代償として、コレクタ電圧がビルトインポテンシャル未満では電流が流れないという欠点も有している。なお、ビルトインポテンシャルは、シリコンの (Si) 場合は約 0.7V であり、ワイドバンドギャップ半導体では、それよりも大きな値となる。例えば、炭化シリコン (SiC) のビルトインポテンシャルは、3.5V 程度である。

このため、半導体材料のビルトインポテンシャル以下の電圧利用域では、p-i-n ダイオードや IGBT (IGBT)、サイリスタ素子の利点は生かせず、1/10～1/1000 程度の通電特性しか有さないユニポーラの MOSFET もしくは電流駆動のバイポーラトランジスタ (GTR など) に頼らざるを得ない。シリコンよりもはるかに大きなビルトインポテンシャルが発生する炭化ケイ素 (SiC) などのワイドバンドギャップの場合、この問題はさらに深刻であり、MOSFET と IGBT の並列接続でこの問題を解決する応用回路上の試みも報告されている。

#### 【0022】

ここで、図 4 を参照しつつ、本実施形態に係る半導体装置の動作原理を説明する。

図 4 は、第 1 実施形態に係る半導体装置の動作原理を表す概念図である。

ダイオードやサイリスタは、電流が流れる方向にビルトインポテンシャル電圧 (0.7V) が生じる。これは高抵抗ベース中に深いキャリアプラズマを蓄積・維持するためのポテンシャルであり、避けることができない。しかし、ダイオードやサイリスタの電流方向 (アノードカソード間方向) と直角方向 (コレクタエミッタ間方向) には、ビルトインポテンシャルは存在しない。もし、主電流に比べて十分少ないアノード・カソード電流によって非常に高い効率で、高抵抗ベース中にサイリスタ並みのキャリアプラズマを発生させると同時に、コレクタ・エミッタ間方向に主電流を流すことが出来れば、サイリスタのビル 40 50

トイン電圧の問題は解決できる。

#### 【0023】

次に、図1を参照しつつ、本実施形態に係る半導体装置の具体的な動作について説明する。ゲート電極10aおよび10bに閾値以上の正電圧が印加されると、ゲート絶縁層15aおよび15b近傍のp形ベース領域5aに、電子の反転層が形成される。この状態で、エミッタ電極91aに対してコレクタ電極90に正の電圧が印加されると、半導体装置100に含まれるMOSFETがオン状態となり、コレクタ電極90からエミッタ電極91aへ順方向の電流が流れる。この状態は通常のユニポーラMOSFETの動作である。<sup>10</sup>

n-形半導体領域3の伝導度変調は生じず、伝導度変調時のバイポーラデバイスのような大きな通電能力は得られない。

本実施形態に係る発明は、次の点で従来のユニポーラMOSFETと大きく異なる。それは、n-形半導体領域3へ少数キャリア(正孔)を注入する為の電流ゲート電極91bを有する点である。さらにその注入電流が、トレンチTr1～Tr3などの幾何学形状や、n形バリア領域4aおよび4bなどによって得られるIE(Injection Enhanced)効果により、非常に僅かな電流で大きな伝導度変調を生じさせるように設計されている点である。<sup>20</sup>

#### 【0024】

本実施形態に係る発明では、エミッタ電極91aに対して電流ゲート電極91bに、p形アノード領域5bとn形バリア領域4bとの間のビルトインポテンシャル以上の正電圧が印加されると、p形アノード領域5bとn<sup>++</sup>形コンタクト領域6aで形成されるp-i-nダイオードにバイポーラモードで順方向の電流が流れる。この時、p形アノード領域5bからn-形半導体領域3へ正孔が注入され、同時に、n<sup>++</sup>形コンタクト領域6aからp形ベース領域5aのn形MOSFETチャネルを通り、n-形半導体領域3へ電子が注入される。この時、p形アノード領域5bとn<sup>++</sup>形コンタクト領域6a間に形成されるp-i-nダイオードの高抵抗のi層に相当するトレンチTr1直下及びトレンチTr1～Tr3の間に、前記p-i-nダイオードの通電に伴う深い伝導度変調(過剰キャリアプラズマの蓄積)が生じる。このp-i-nダイオードの通電に伴う深い伝導度変調(過剰キャリアプラズマの蓄積)は、トレンチTr1～Tr3の形状に依存したIE効果で増幅される。つまり、p形アノード領域5bから注入された正孔がn<sup>++</sup>形コンタクト領域6aのトレンチ溝幾何学形状で堰き止められ、n<sup>++</sup>形コンタクト領域6aから注入された電子がp形アノード領域5bのトレンチ溝幾何学形状により堰き止められる。その結果、前記p-i-nダイオードの高抵抗i層に相当するトレンチTr1直下及びトレンチTr1～Tr3の間に、n-形半導体領域3の不純物濃度に比べて1桁から5桁大きな過剰キャリアプラズマの蓄積を生じさせることが可能となる。これにより、半導体装置100に含まれる高抵抗なn-形半導体領域3へのプラズマ蓄積により1桁から5桁低抵抗化している状態である。この時、エミッタ電極91aに対するコレクタ電極90の電位差はまだない、もしくはビルトイン電圧に比べて十分小さな変動である。<sup>30</sup>

#### 【0025】

さらにこの状態で、エミッタ電極91aに対してコレクタ電極90に正の電圧が印加されると、半導体装置100のエミッタ電極91aとコレクタ電極90の間に順方向電流が流れる。この時、半導体装置100のn-形半導体領域3は、コレクタ印加電圧が0Vからビルトイン電圧以下でも、深い伝導度変調状態を生じたバイポーラモードで動作する。<sup>40</sup>

また、ゲート電極11aおよび11bに負電圧が印加される場合には、p形アノード領域5bに正孔の蓄積層が形成されるとともに、ゲート絶縁層16aおよび16b近傍のn形バリア領域4bに正孔の反転層が形成され、n-形半導体領域3への正孔の注入がさらに促進される。

なお、ここでは、「深い伝導度変調状態」と「プラズマの蓄積」もしくは「過剰キャリアプラズマの蓄積」は同じ意味で使用している。

また、「ビルトインポテンシャル」は、「p形不純物拡散領域とn形不純物拡散領域のフェルミ順位の差」のこと、「pin(もしくはp-n)ダイオードの順方向の電流が流

10

20

30

40

50

れ始める電流の閾値電圧(順方向の電流-電圧波形において電流が立ち上がりはじめる点の電圧)」と同じ意味で使用している。

#### 【0026】

このように、本実施形態に係る半導体装置では、MOSFETによってエミッタ電極91aとコレクタ電極90との間の通電時に、電流ゲート電極91bからn<sup>-</sup>形半導体領域3へ正孔を注入して、電導度変調を生じさせることができる。すなわち、本実施形態に係る半導体装置では、ユニポーラデバイス同様にエミッタ電極91aとコレクタ電極90との間にビルトインポテンシャルが無いにも拘らず、バイポーラデバイス同様の、n<sup>-</sup>形半導体領域3での深い伝導度変調で、大きな通電能力と低いオン抵抗を有する。

また、ビルトインポテンシャルが無く、低いコレクタ電圧においても通電可能であるため、本実施形態に係る発明は、特にワイドバンドギャップ半導体が用いられた半導体装置に対して好適に用いられる。ワイドバンドギャップ半導体は、シリコンよりも大きなビルトインポтенシャルを有するため、バイポーラデバイスに用いられた際には、より大きなドレイン電圧が必要となるためである。このようなワイドバンドギャップ半導体としては、炭化シリコン以外にも、窒化ガリウム(GaN)、酸化ガリウム(Ga<sub>2</sub>O<sub>3</sub>)、ダイヤモンドなどが挙げられる。

#### 【0027】

さらに本実施形態に係る半導体装置は、エミッタ電極91a側のトレンチTr1～Tr3やn形バリア領域4aおよび4bによる、エミッタ電極91aと電流ゲート電極91bとの間で生じるIE効果により、GTR(ジャイアントトランジスタ：電力用バイポーラトランジスタ)に比べてより小さな駆動電流(数分の一から数百分の一)で効果的にn<sup>-</sup>形半導体領域3で深い伝導度変調を起こすことができる。つまり、本実施形態に係る半導体装置では、1.0×10<sup>14</sup>～1.0×10<sup>18</sup>cm<sup>-3</sup>程度の、GRTより沢山のキャリアプラズマを蓄積することができ、より大電流を制御することが可能である。

#### 【0028】

この点について、図5を用いて詳細に説明する。

図5(a)は、第1実施形態に係る半導体装置100の一部を表す断面図である。

図5(b)は、第1実施形態に係る半導体装置と参考例に係る半導体装置における過剰キャリアの濃度を比較するグラフである。

図5(c)は、参考例に係る半導体装置の一部を表す断面図である。

なお、図5(a)では、図1に表す半導体装置100と同様の機能を有する半導体装置が表されている。図5(b)では、図5(a)および(c)の各半導体装置において、Z方向の各位置における過剰キャリアの濃度が表されている。図5(c)では、参考例に係る半導体装置として、GTRの一部が表されている。

#### 【0029】

図5(c)に表す参考例に係る半導体装置では、コレクタ電極90、n<sup>++</sup>形コレクタ領域1、n形バリア領域2、n<sup>-</sup>形半導体領域3、p形ベース領域5、n<sup>++</sup>形コンタクト領域6、p<sup>++</sup>形コンタクト領域7、エミッタ電極91a、および電流ゲート電極91bが設けられている。図5(c)に表すように、GTRでは、p<sup>++</sup>形コンタクト領域7からp形ベース領域5へ注入された正孔は、p形ベース領域5からn<sup>++</sup>形半導体領域6へ流れてしまう。すなわち、p形ベース領域5から注入された過剰キャリアが、n<sup>-</sup>形半導体領域3に蓄積されず、電導度変調への寄与が小さい。

これに対して、図5(a)に表すように、本実施形態に係る半導体装置100では、エミッタ電極91a側のトレンチTr1～Tr3およびn形バリア領域4aおよび4bによるIE効果(エミッタ電極91a側での過剰キャリアの蓄積効果)により、p形アノード領域5bから注入された正孔が、エミッタ電極91aに流れることを抑制し、電流ゲート電極91bからエミッタ電極91aに流れる電流を抑制することができる。すなわち、本実施形態に係る半導体装置では、n<sup>-</sup>形半導体領域3に過剰キャリアを効率的に蓄積し、p形ベース領域5から注入された正孔の電導度変調への寄与を高めることができる。

このため、図5(b)に表すように、本実施形態に係る半導体装置100と参考例に係

10

20

30

40

50

る半導体装置では、過剰キャリアの濃度に大きな差が存在する。

#### 【0030】

本実施形態に係る半導体装置100と参考例に係る半導体装置における過剰キャリアの濃度の違いについて、図6～図8を参照して、より詳細に説明する。

図6は、シミュレーションに用いた参考例に係る半導体装置の断面構造である。

図7は、参考例に係る半導体装置のオン状態における正孔の分布を表すシミュレーション結果である。

図8は、本実施形態に係る半導体装置100のオン状態における正孔の分布を表すシミュレーション結果である。

#### 【0031】

図6には、図5(c)に表したGTRのn<sup>-</sup>形半導体領域3およびp形ベース領域5における不純物濃度が表されている。図6では、n<sup>-</sup>形半導体領域3およびp形ベース領域5のそれぞれにおいて、色が白いほど各導電形の不純物濃度が低く、黒いほど不純物濃度が高いことを表している。

また、図7および図8では、オン状態で、コレクタ電極側に3.0Vの電圧が印加された場合の正孔の分布が示されている。色が白いほど正孔の濃度が高く、黒いほど正孔の濃度が低いことを表している。なお、図8の本実施形態に係る半導体装置のシミュレーション結果では、絶縁部19a(トレンチTr1)下方における正孔の分布が表されている。

#### 【0032】

これらのシミュレーションでは、GTRと半導体装置100について、ともに1500Vの素子耐圧を得られる設計とした。具体的には、n<sup>-</sup>形半導体領域3の厚みを100μm、n<sup>-</sup>形半導体領域3の不純物濃度を $1 \times 10^{13} \text{ cm}^{-3}$ 、セルサイズを19.2μm、半導体装置100におけるトレンチTr1の深さを6μmとし、単位セル面積を同一とし、電流ゲインは同じ値に揃えた。

#### 【0033】

図7に示すように、GTRでは、pn接合面近傍における正孔の濃度は、 $6.4 \times 10^{15} \text{ cm}^{-3}$ であった。一方で、図8に示すように、本実施形態に係る半導体装置100では、絶縁部19a下部における正孔の濃度は、 $7.1 \times 10^{16} \text{ cm}^{-3}$ であり、GTRに比べて1桁以上大きな値が得られた。

#### 【0034】

図9は、第1実施形態に係る半導体装置と参考例に係る半導体装置の通電特性を表すシミュレーション結果である。

図9に表す結果から、GTRは、MOSFETに比べて大きな通電能力を備えるが、本実施形態に係る半導体装置100は、このGTRよりもさらに大きな通電能力を備えていることがわかる。

#### 【0035】

以上の通り、本実施形態によれば、MOSFETなどのユニポーラデバイスよりも桁違いに大きな通電能力を有し、コレクタ電圧がビルトイン電圧未満においても、バイポーラデバイス同様の、n<sup>-</sup>形半導体領域3での深い伝導度変調で大きな通電能力と低いオン抵抗を備えた半導体装置が得られる。

また、本実施形態によれば、GTRに比べて、低い駆動電流でより多くのキャリアプラズマを蓄積することができ、より大電流を制御することが可能な半導体装置が得られる。

#### 【0036】

以上では、コレクタ電極90からエミッタ電極91aへ、順方向に電流を流す場合について説明したが、本実施形態に係る半導体装置100は、以下で説明するように、エミッタ電極91aからコレクタ電極90へ、逆方向に電流を流すことも可能である。

コレクタ電極90に対してエミッタ電極91aに正の電圧が印加された状態で、ゲート電極10aおよび10bに閾値以上の正電圧が印加されると、n<sup>++</sup>形コンタクト領域6aとn形バリア領域4aとがp形ベース領域5aの反転層で接続される。これにより、エミッタ電極91aからコレクタ電極90へ逆方向の電流が流れる。

10

20

30

40

50

この場合（逆電圧）でも、エミッタ電極 91a に対して電流ゲート電極 91b に、p 形アノード領域 5b と n 形バリア領域 4b との間のビルトインポテンシャル以上の正電圧が印加されると、p 形アノード領域 5b と n<sup>++</sup> 形コンタクト領域 6a で形成される p-i-n ダイオードにバイポーラモードで順方向の電流が流れ、その結果、n<sup>-</sup> 形半導体領域 3 に深い伝導度変調が起こる。

つまり、エミッタ電極 91a に対してコレクタ電極 90 に負の電圧が印加された場合も、半導体装置 100 のエミッタ電極 91a とコレクタ電極 90 の間に流れる逆方向に電流は、コレクタ印加電圧が 0V からビルトイン電圧以下でも、半導体装置 100 の n<sup>-</sup> 形半導体領域 3 が深い伝導度変調を起こした状態下でのバイポーラモードの動作である。

#### 【0037】

10

ここで、図 10～図 12 を参照しつつ、本実施形態に係る半導体装置の順方向および逆方向への通電特性について、詳細に説明する。

図 10 は、シミュレーションに用いた第 1 実施形態に係る半導体装置 100 の断面構造である。

図 11 は、第 1 実施形態に係る半導体装置 100 において順方向および逆方向へ通電させた場合のオン状態における正孔の濃度を表すシミュレーション結果である。

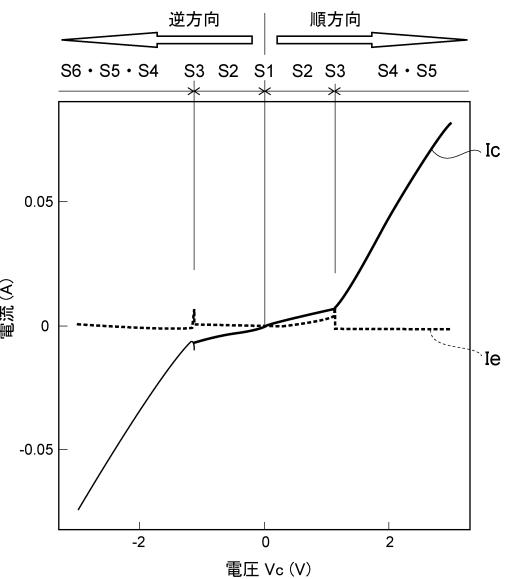

図 12 は、第 1 実施形態に係る半導体装置 100 における双方向の通電特性を表すシミュレーション結果である。

#### 【0038】

20

図 10 は、絶縁部 19a（トレンチ Tr1）下方における不純物濃度の分布が表されている。図 10 では、色が白いほど n 形不純物濃度が低く、黒いほど n 形不純物濃度が高いことを表している。

また、図 11 は、図 7 および図 8 と同様に、オン状態でコレクタ電極側に 3.0V の電圧が印加された場合の正孔の分布が示されており、色が白いほど正孔の濃度が高く、黒いほど正孔の濃度が低いことを表している。なお、図 11 (a) は、順方向への通電時の様子を表し、図 11 (b) は、逆方向への通電時の様子を表している。

#### 【0039】

図 11 に表す結果から、順方向および逆方向のどちらに電流を流した場合でも、絶縁部 19a 下方の領域において正孔が高い濃度で蓄積されていることがわかる。

また、図 12 に表す結果から、逆方向に通電させた場合でも、順方向への通電時と同様に、高い通電特性が得られていることがわかる。

30

さらに、図 12 に表されるように、コレクタ電圧がビルトイン電圧未満であってもサイリスタと同様の高い通電能力を有するため、順方向通電時および逆方向通電時のいずれにおいても、トライアックのようなスナップバックは生じない。

#### 【0040】

以上の通り、本実施形態に係る半導体装置は、順方向および逆方向のいずれの通電についても、高い通電能力を備える。

順方向または逆方向への通電時に、ゲート電極 10a および 10b に印加される電圧が閾値未満になると、p 形ベース領域 5a の反転層が消滅し、コレクタ電極 90 とエミッタ電極 91a との間の通電が無くなり、半導体装置 100 がオフ状態となる。

40

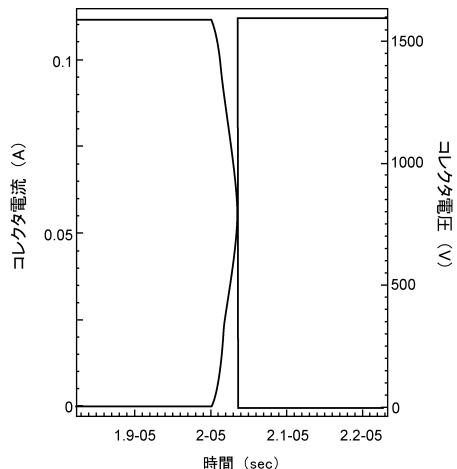

#### 【0041】

図 13 は、第 1 実施形態に係る半導体装置 100 のターンオフ時のコレクタ電圧とコレクタ電流の変化を表すシミュレーション結果である。

図 14 は、第 1 実施形態に係る半導体装置 100 の静耐圧波形を表すシミュレーション結果である。

なお、図 13 および図 14 は、素子耐圧が 1500V に設計された半導体装置 100 におけるターンオフ時の様子を表している。図 13 および図 14 に表されるように、本実施形態に係る半導体装置 100 において、ターンオフ時に設計値と同様の耐圧が得られていることがわかる。

また、ターンオフ時に、電流ゲート電極 91b の電位をエミッタ電極 91a の電位に対

50

して負にして電流を引きぬくことで、より確実に半導体装置 100 をオフ状態にすることができます。また、ゲート電極 10a および 10b と電流ゲート電極 91b のタイミングをずらすことによって、半導体装置のオン状態のときの抵抗とスイッチング特性とのトレードオフの改善が可能である。例えば、ゲート電極 10a および 10b への印加電圧を変化させる前に、電流ゲート電極 91b の電圧をマイナスにして、数  $\mu$  秒～数十  $\mu$  秒後に、ゲート電極 10a および 10b の電圧を低下させてもよい。この方法によれば、導体装置 100 の n- 形半導体領域 3 の蓄積キャリアが無くなつた後に、ゲート電極 10a および 10b を遮断することができ、ユニポーラの MOSFET モードのターンオフ(テイル電流を生じない)時のテイル電流を抑制することが可能である。

## 【0042】

10

以上で説明した本発明の動作原理によれば、エミッタ電極 91a と電流ゲート電極 91b 間の過剰キャリアの蓄積量(キャリア濃度のピーク値)が、n- 形半導体領域 3 中での過剰キャリアの量を決め、n- 形半導体領域 3 中での過剰キャリアの量が、導体装置 100 のエミッタ電極 91a とコレクタ電極 90 との間の抵抗を決める。

また、エミッタ電極 91a と電流ゲート電極 91b 間の過剰キャリアの蓄積量(キャリア濃度のピーク値)は、エミッタ電極 91a 側のトレンチ Tr1～Tr3 の形状による IE 効果によって決まる。この IE 効果は、トレンチ Tr1 の深さ(～数 10  $\mu$ m)、ゲート電極 10a と 10b・ゲート電極 11a と 11b の間隔(10 nm～数  $\mu$ m)、エミッタ電極 91a と電流ゲート電極 91b の間隔、および n 形バリア領域 4a および 4b における n 形不純物濃度などで決まる。IE 効果については、例えば、「M.Kitagawa et al, "A 4500 V Injection Enhanced Insulated Gate Bipolar Transistor (IEGT) Operating in a Mode Similar to a Thyristor", IEDM'93 .Technical Digest, pp679-682, 1993」、「M.Kitagawa et al, "Design Criterion and Operation Mechanism for 4.5kV Injection Enhanced Gate Transistor", Jpn. J. Appl. Phys. Vol.37 pp4294-4300, 1998」、「M.Kitagawa et al, "4.5kV Injection Enhanced Gate Transistor: Experimental Verification of the Electrical Characteristics", Jpn. J. Appl. Phys. Vol.36 pp3433-3437, 1997」、および「M.Kitagawa et al, "Study of 4.5 kV MOS-Power Device with Injection-Enhanced Trench Gate Structure", Jpn. J. Appl. Phys. Vol.36 pp1411-1413, 1997」などに記載されている。

## 【0043】

30

ここで、IE 効果を高めるための寸法関係について、図 15 を用いて説明する。

図 15 は、第 1 実施形態に係る半導体装置 100 の一部を表す断面図である。

図 15 に表すように、p 形ベース領域 5a の幅(X 方向における長さ)W1 および p 形アノード領域 5b の幅 W2 が狭く、p 形ベース領域 5a と p 形アノード領域 5b との間隔 D1 が広いほど、IE 効果は大きくなる。また、p 形ベース領域 5a の下面(pn 接合面)と絶縁部 19a の下端(トレンチ Tr1 の下端)との間の Z 方向における厚み Th1、p 形アノード領域 5b の下面(pn 接合面)と絶縁部 19a の下端(トレンチ Tr1 の下端)との間の Z 方向における厚み Th2 が大きく、n 形バリア領域 4a および 4b における n 形不純物濃度が高いほど、IE 効果は大きくなる。

## 【0044】

40

幅 W1 および W2 は、1.0  $\mu$ m 以下であることが望ましい。幅 W1 および幅 W2 を 1.0  $\mu$ m 以下にすることで、オン状態において n- 形半導体領域 3 に蓄積された正孔が、p 形ベース領域 5a および 5b へ流れ難くなり、n- 形半導体領域 3 における正孔の濃度を高めることができる。なお、図 1 に表す例では、p 形ベース領域 5a の幅は、n 形バリア領域 4a の幅、および X 方向におけるゲート絶縁層 15a と 15b との間の距離と等しい。p 形ベース領域 5b の幅は、n 形バリア領域 4b の幅、および X 方向におけるゲート絶縁層 16a と 16b との間の距離と等しい。

なお、図 15 に表す例では、幅 W1 は、ゲート絶縁層 10a と 10b との間の X 方向における距離と等しく、幅 W2 は、ゲート絶縁層 11a と 11b との間の X 方向における距離と等しい。距離 D1 は、ゲート絶縁層 10a、ゲート絶縁層 11a、および絶縁部 19

50

aを含む、トレンチTr1内に設けられた絶縁部のX方向における長さと等しい。

また、図15に表す例では、n形バリア領域4aとp形ベース領域5aとのX方向における長さが等しく、n形バリア領域4bとp形アノード領域5bとのX方向における長さが等しいが、これらの半導体領域における長さは互いに異なっていてもよい。すなわち、各ゲート電極および各ゲート絶縁層が設けられたトレンチの側壁がテーパ状に形成されていてもよい。この場合、ゲート絶縁層10aの少なくとも一部と、ゲート絶縁層10bの少なくとも一部と、の間のX方向における距離が、1.0μm以下であり、ゲート絶縁層11aの少なくとも一部と、ゲート絶縁層11bの少なくとも一部と、の間のX方向における距離が、1.0μm以下であればよい。

#### 【0045】

10

さらに、W1、W2、D1、Th1、およびTh2は、以下の式(1)～(4)の少なくともいずれかを満たすことが望ましい。

$$Th1 / W1 > 2 \quad \dots \quad (1)$$

$$Th2 / W2 > 2 \quad \dots \quad (2)$$

$$(Th1 \times D1) / W1 > 2 \mu m \quad \dots \quad (3)$$

$$(Th2 \times D1) / W2 > 2 \mu m \quad \dots \quad (4)$$

#### 【0046】

20

式(1)を満たすことで、エミッタ電極91aからn<sup>-</sup>形半導体領域3に注入された電子が、電流ゲート電極91bに流れにくくなり、n<sup>-</sup>形半導体領域3における電子の過剰キャリア濃度を高めることができる。

式(2)を満たすことで、電流ゲート電極91bからn<sup>-</sup>形半導体領域3に注入された正孔が、エミッタ電極91aに流れにくくなり、n<sup>-</sup>形半導体領域3における正孔の過剰キャリア濃度を高めることができる。

式(3)および(4)を満たすことで、n<sup>-</sup>形半導体領域3からエミッタ電極91aおよび電流ゲート電極91bへの正孔の流出を抑え、n<sup>-</sup>形半導体領域3における正孔の過剰キャリア濃度を高めることができる。

#### 【0047】

30

また、距離D1は、幅W1または幅W2の2倍以上であることが望ましい。より望ましくは、距離D1は、幅W1または幅W2の10倍以上である。このような構造によれば、半導体装置100の単位面積あたりのp形ベース領域5aおよび5bの面積を小さくし、n<sup>-</sup>形半導体領域3に蓄積された正孔がp形ベース領域5aおよび5bへより流れ難くなる。

#### 【0048】

さらに、n形バリア領域2におけるn形不純物濃度を高くすることで、IE効果で生じた過剰キャリアがn<sup>-</sup>形半導体領域3からコレクタ電極90に流れ難くなり、IE効果をさらに高めることができる。

#### 【0049】

40

これらの構造によってIE効果を高めることで、より一層、半導体装置の通電能力を高め、オン抵抗を低減することができる。

また、コレクタ電極90とエミッタ電極91aとの間に通電させる場合、エミッタ電極91aと電流ゲート電極91bとの間を流れる電流は小さいことが望ましい。エミッタ電極91aと電流ゲート電極91bとの間のIE効果(n<sup>-</sup>形半導体領域3に蓄積された正孔がエミッタ電極91aへ流れ難くなること等)で、電流ゲート電極91bから91aへ流れる電流が小さくても、電流流路をトレンチ形状で絞ることで、ゲート電流密度(つまりn<sup>-</sup>形半導体領域3のエミッタ側の過剰キャリアのピーク濃度)を上げることに成功し、その結果、素子のエミッタ91aとコレクタ90間のオン抵抗が下がり、半導体装置の消費電力を低減することが可能となるためである。

#### 【0050】

(第1変形例)

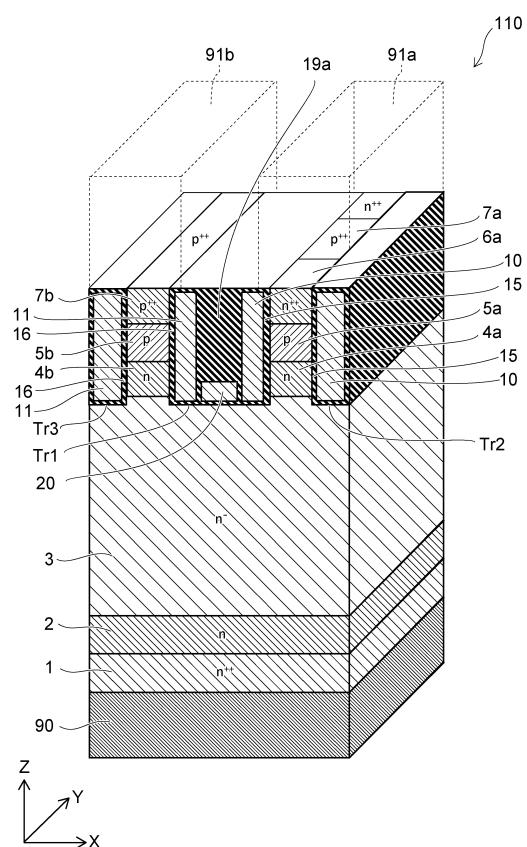

図16は、第1実施形態の第1変形例に係る半導体装置110の一部を表す斜視断面図

50

である。

半導体装置 110 は、電極 20 をさらに備える点と、ゲート電極 10a および 10b に代えてゲート電極 10 が設けられ、ゲート電極 11a および 11b に代えてゲート電極 11 が設けられている点で、半導体装置 100 と異なる。

#### 【0051】

半導体装置 110 では、n 形バリア領域 4a、p 形ベース領域 5a、n<sup>++</sup> 形コンタクト領域 6a、および p<sup>++</sup> 形コンタクト領域 7a が、X 方向において、ゲート絶縁層 15 を介してゲート電極 10 同士の間に位置している。

また、n 形バリア領域 4b、p 形アノード領域 5b、n<sup>++</sup> 形コンタクト領域 6b、および p<sup>++</sup> 形コンタクト領域 7b が、X 方向において、ゲート絶縁層 16 を介してゲート電極 11 同士の間に位置している。 10

#### 【0052】

電極 20 は、X 方向において、ゲート電極 10 と 11 との間に設けられ、これらのゲート電極と離間している。電極 20 は、絶縁部 19a の一部を介して、Z 方向において n<sup>-</sup> 形半導体領域 3 と対面している。また、電極 20 は、例えば、エミッタ電極 91a と電気的に接続されている。

#### 【0053】

ゲート電極 10 と 11 との間に、エミッタ電極 91a と電気的に接続された電極 20 が設けられていることで、半導体装置をターンオフした際に、電極 20 の下部（トレンチ Tr 1 の下端）からも n<sup>-</sup> 形半導体領域 3 へ向けて空乏層が広がる。これにより、半導体装置の耐圧を向上させることが可能となる。あるいは、半導体装置の耐圧が向上した分、n<sup>-</sup> 形半導体領域 3 における n 形不純物濃度を高め、半導体装置のオン抵抗を低減することが可能となる。 20

また、電極 20 をゲート電極として、ゲート電極 10 と 11 と独立に制御することで、素子のオン電圧や阻止状態の耐圧のみならず、素子のスイッチングスピードと通電能力などとのトレードオフの改善、バイポーラモードでのコレクタ電極 90、エミッタ電極 91a、および電流ゲート電極 91b から n<sup>-</sup> 形半導体領域 3 へのキャリア（正孔または電子）の実効的な注入効率、および n<sup>-</sup> 形半導体領域 3 から各電極へのキャリアの実効的排出効率をコントロールすることが可能である。 30

#### 【0054】

##### （第 2 变形例）

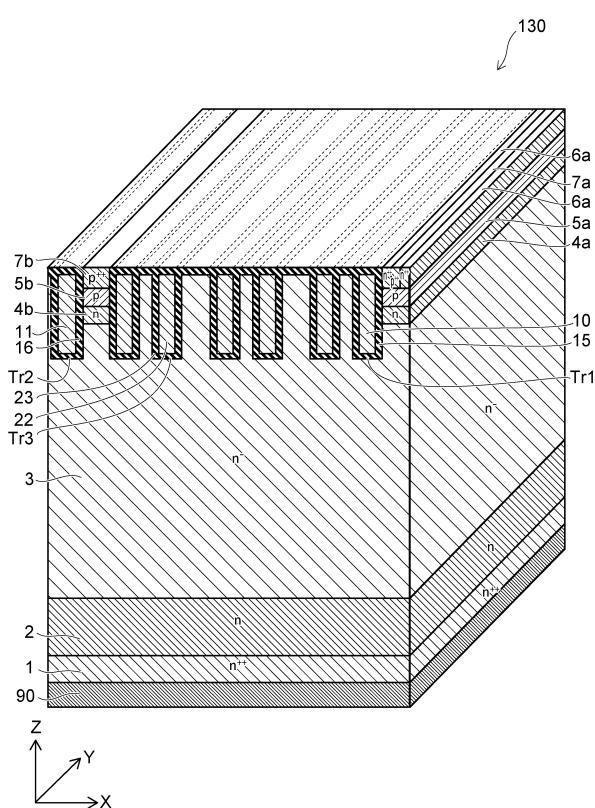

図 17 は、第 1 実施形態の第 2 变形例に係る半導体装置 120 の一部を表す斜視断面図である。

半導体装置 120 は、ゲート電極の構造および n<sup>++</sup> 形コンタクト領域 6a と p<sup>++</sup> 形コンタクト領域 7a の配置について、半導体装置 100 と差異を有する。

#### 【0055】

半導体装置 120 では、p 形ベース領域 5a の上において、複数の n<sup>++</sup> 形コンタクト領域 6a が設けられている。複数の n<sup>++</sup> 形コンタクト領域 6a は、それぞれ、X 方向において、ゲート絶縁層 15 を介してゲート電極 10 と対面している。p<sup>++</sup> 形コンタクト領域 7a は、X 方向において n<sup>++</sup> 形コンタクト領域 6a 同士の間に設けられている。また、n<sup>++</sup> 形コンタクト領域 6a と p<sup>++</sup> 形コンタクト領域 7a は、Y 方向に延びている。 40

#### 【0056】

p 形アノード領域 5b および p<sup>++</sup> 形コンタクト領域 7b は、X 方向において、ゲート絶縁層 16 を介してゲート電極 11 と対面している。ゲート電極 10 および 11 は、トレンチ Tr 内に設けられている。ゲート電極 10 と 11 との間には絶縁部 19 が設けられ、ゲート電極 10 と 11 は、X 方向において離間している。

#### 【0057】

このように、n<sup>++</sup> 形コンタクト領域 6a および p<sup>++</sup> 形コンタクト領域 7a の配置や、各ゲート電極の形状を変化させた場合であっても、上述したように半導体装置の I-E 効 50

果を高めることで、n<sup>-</sup>形半導体領域3で深い伝導度変調を生じさせ、大きな通電能力と低いオン抵抗を実現することが可能である。

#### 【0058】

##### (第3変形例)

図18は、第1実施形態の第3変形例に係る半導体装置130の一部を表す斜視断面図である。

なお、図18に表す半導体装置130の上面には、Z方向から見た場合の、ゲート電極10および11、電極22、トレンチTr1～Tr3の外縁が破線で表されている。また、図18では、エミッタ電極91aおよび電流ゲート電極91bが省略されている。

#### 【0059】

半導体装置130は、電極22および絶縁層23をさらに備える点で、半導体装置120と異なる。

電極22は、絶縁層23を介してn<sup>-</sup>形半導体領域3中に設けられている。また、電極22は、エミッタ電極91aと電気的に接続されている。

#### 【0060】

電極22は、p形ベース領域5aとp形アノード領域5bとの間ににおいて、X方向に複数設けられており、それぞれがY方向に延びている。また、n<sup>-</sup>形半導体領域3の電極22同士の間の領域は、絶縁層23によって覆われている。

#### 【0061】

エミッタ電極91aは、半導体装置120と同様に、n<sup>++</sup>形コンタクト領域6aおよびp<sup>++</sup>形コンタクト領域7aの上に設けられる。エミッタ電極91aは、さらに、電極22の上に設けられてもよい。電流ゲート電極91bも、半導体装置120と同様に、p<sup>++</sup>形コンタクト領域7bの上に設けられる。

#### 【0062】

複数の電極22を設け、p形ベース領域5aとp形アノード領域5bとの間の距離を長くする(単位面積あたりのp形ベース領域5aとp形アノード領域5bの面積を減少させる)ことで、オン状態において、n<sup>-</sup>形半導体領域3から過剰キャリアが排出され難くなる。このため、本変形例によれば、オン状態でのn<sup>-</sup>形半導体領域3における過剰キャリアの蓄積量を増大させ、さらなる半導体装置の通電能力の向上、オン抵抗の低減、および駆動電流の低減が可能となる。

#### 【0063】

##### (第4変形例)

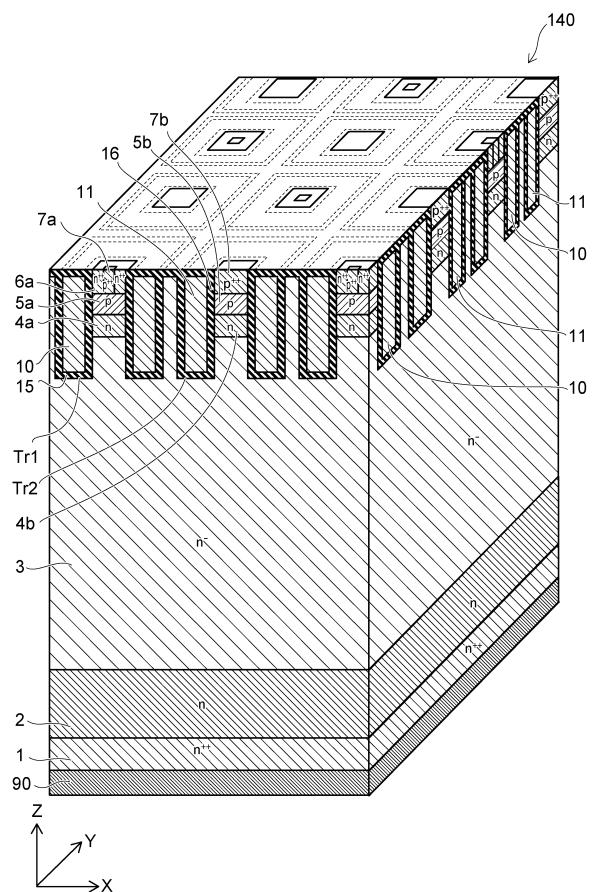

図19は、第1実施形態の第4変形例に係る半導体装置140の一部を表す斜視断面図である。

なお、図19に表す半導体装置140の上面には、Z方向から見た場合の、ゲート電極10および11、トレンチTr1およびTr2の外縁が破線で表されている。また、図19では、エミッタ電極91aおよび電流ゲート電極91bが省略されている。

#### 【0064】

半導体装置140では、ゲート電極10および11が、それぞれ、ゲート絶縁層15および16を介してn<sup>-</sup>形半導体領域3中に環状に設けられている。

n形バリア領域4a、p形ベース領域5a、n<sup>++</sup>形コンタクト領域6a、およびp<sup>++</sup>形コンタクト領域7aは、ゲート電極10の内側に設けられている。n<sup>++</sup>形コンタクト領域6aは、例えば、ゲート電極10の内側において環状に設けられ、p<sup>++</sup>形コンタクト領域7aは、このn<sup>++</sup>形コンタクト領域6aの内側に設けられている。

n形バリア領域4bおよびp形アノード領域5bは、ゲート電極11の内側に設けられている。p形アノード領域5bの上に、さらにp<sup>++</sup>形コンタクト領域7bが設けられてもよい。

#### 【0065】

n<sup>++</sup>形コンタクト領域6aおよびp<sup>++</sup>形コンタクト領域7aの上には、不図示のエミッタ電極91aが設けられ、これらの半導体領域と電気的に接続される。また、p形ア

10

20

30

40

50

ノード領域 5 b の上には、不図示の電流ゲート電極 9 1 b が設けられ、 p 形アノード領域 5 b と電気的に接続される。

#### 【 0 0 6 6 】

すなわち、本変形例に係る半導体装置では、 M O S F E T として機能する領域および n - 形半導体領域 3 へ正孔を注入するための領域が、 X 方向および Y 方向において、互いに離間して複数設けられている。本変形例においても、半導体装置 1 0 0 に比べて I E 効果をさらに大きくすることができ、さらなる半導体装置の通電能力の向上、オン抵抗の低減、および駆動電流の低減が可能となる。

#### 【 0 0 6 7 】

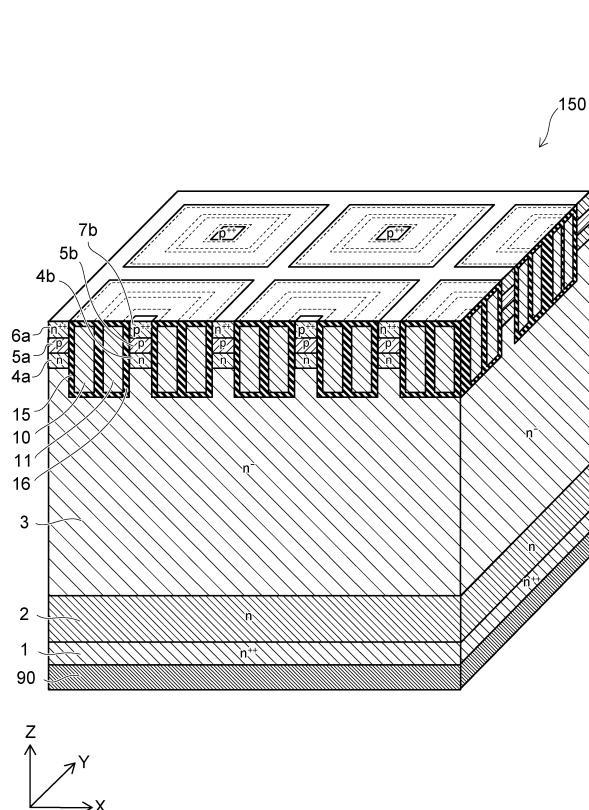

( 第 5 変形例 )

10

図 2 0 は、第 1 実施形態の第 5 変形例に係る半導体装置 1 5 0 の一部を表す斜視断面図である。

なお、図 2 0 に表す半導体装置 1 5 0 の上面には、 Z 方向から見た場合の、各ゲート電極の外縁が破線で表されている。また、図 2 0 では、エミッタ電極 9 1 a および電流ゲート電極 9 1 b が省略されている。

#### 【 0 0 6 8 】

半導体装置 1 5 0 では、ゲート電極 1 0 および 1 1 が環状に設けられている。ただし、ゲート電極 1 1 がゲート電極 1 0 の内側に設けられ、 n 形バリア領域 4 b および p 形アノード領域 5 b がゲート電極 1 1 の内側にゲート絶縁層 1 6 を介して設けられている点で、半導体装置 1 4 0 と異なる。電流ゲート電極 9 1 b は、 p 形アノード領域 5 b の上に設けられる。

20

#### 【 0 0 6 9 】

n 形バリア領域 4 a 、 p 形ベース領域 5 a 、および n + + 形コンタクト領域 6 a は、ゲート電極 1 0 同士の間に、ゲート絶縁層 1 5 を介して設けられている。 p 形ベース領域 5 a の上に、 p + + 形コンタクト領域 7 a がさらに設けられていてよい。エミッタ電極 9 1 a は、例えば、 n 形バリア領域 4 a 、 p 形ベース領域 5 a 、および n + + 形コンタクト領域 6 a に沿って、電流ゲート電極 9 1 b 同士の間に格子状に設けられる。

#### 【 0 0 7 0 】

すなわち、本変形例に係る半導体装置では、 n - 形半導体領域 3 へ正孔を注入するための領域が、 X 方向および Y 方向において、互いに離間して複数設けられ、これらの領域の間に M O S F E T として機能する領域が設けられている。本変形例においても、半導体装置 1 0 0 に比べて I E 効果をさらに大きくすることができ、さらなる半導体装置の通電能力の向上、オン抵抗の低減、および駆動電流の低減が可能となる。

30

#### 【 0 0 7 1 】

ここで、図 2 1 および図 2 2 を用いて、第 1 実施形態に係る半導体装置に接続される制御回路の例を説明する。

図 2 1 および図 2 2 は、第 1 実施形態に係る半導体装置の制御回路の一部を表す回路図である。

なお、図 2 1 および図 2 2 では、ゲート電極 1 0 a および 1 0 b が、まとめてゲート電極 1 0 と表記され。ゲート電極 1 1 a および 1 1 b が、まとめてゲート電極 1 1 と表記されている。また、エミッタ電極 9 1 a は、グランド電位に接続される。

40

#### 【 0 0 7 2 】

図 2 1 ( a ) に表す回路では、電流ゲート電極 9 1 b 、ゲート電極 1 0 および 1 1 が、共通の端子 T 1 に接続されている。また、電流ゲート電極 9 1 b と端子 T 1 との間には、端子 T 1 への印加電圧を調整して電流ゲート電極 9 1 b に印加するための制限抵抗が接続されている。半導体装置 1 0 0 をターンオンする際には、端子 T 1 に正電圧が印加される。端子 T 1 に正電圧が印加されると、ゲート電極 1 0 と向かい合う p 形ベース領域 5 a に反転層が形成される。また、電流ゲート電極 9 1 b にビルトインポテンシャル以上の正電圧が印加されることで、 n - 形半導体領域 3 に正孔が注入される。

#### 【 0 0 7 3 】

50

図21(a)に表す回路では、電流ゲート電極91b、ゲート電極10および11の電圧の制御を、1つの端子で行うことができ、半導体装置100の端子数の増加を抑えることができる。

#### 【0074】

図21(b)に表す回路は、ゲート電極11が、端子T1に接続されず、エミッタ電極91aと同じグランド電位に接続されている点で、図21(a)に表す回路と異なる。このため、図21(a)に表す回路に比べて、ゲート電極10が接続された配線における容量を低減し、ゲート電極10のスイッチング速度を向上させることができる。また、ゲート電極11に正電圧が印加されると、ゲート絶縁層16a近傍のp形ベース領域5bの正孔が排斥されるが、図21(b)に表す回路では、この現象が発生しない。このため、図21(a)に表す回路に比べて、n<sup>-</sup>形半導体領域3への正孔の注入を効率的に行うことができる。

10

#### 【0075】

図21(c)に表す回路では、電流ゲート電極91bが、制限抵抗を介して端子T1に接続され、ゲート電極10および11が、共通の端子T2に接続されている。このため、電流ゲート電極91bと、ゲート電極10および11と、にそれぞれ最適な電圧を印加できる。

#### 【0076】

図22(a)は、ゲート電極11が、端子T2に接続されず、グランド電位に接続されている点で、図21(c)に表す回路と異なる。図22(a)に表す回路によれば、図21(c)に表す回路と比較して、スイッチング速度を向上させ、n<sup>-</sup>形半導体領域3への正孔の注入を効率的に行うことができる。

20

#### 【0077】

図22(b)に表す回路では、制限抵抗に代えて、端子T1と電流ゲート電極91bとの間に、ダーリントン接続されたトランジスタが設けられている点で、図21(a)に表す回路と異なる。具体的には、ダーリントン接続のコレクタ側は、コレクタ電源Vに接続され、ベースに端子T1が接続され、エミッタ側に電流ゲート電極91bが接続されている。この回路によれば、小さなゲート電流によって、コレクタ電源Vから電流ゲート電極91bに大きな電流を流すことができる。すなわち、小さなゲート電流でも、n<sup>-</sup>形半導体領域3へ多くの正孔を注入することが可能となる。

30

#### 【0078】

上述した回路例以外にも、半導体装置に含まれるMOSFETをターンオンさせ、電流ゲート電極91bからn<sup>-</sup>形半導体領域3へ正孔を注入させることができれば、具体的な回路構成は、適宜変更可能である。

#### 【0079】

##### (変形例)

図23は、第1実施形態の変形例に係る半導体装置160の一部を表す斜視断面図である。

半導体装置160は、ゲート電極11aおよび11bを有していない点で、半導体装置100と異なる。

40

#### 【0080】

ゲート電極11aおよび11bが設けられていない場合でも、エミッタ電極91aに対して電流ゲート電極91bに、ビルトインポテンシャル以上の電圧が印加されることで、n<sup>-</sup>形半導体領域3に正孔を注入することができる。ただし、上述した通り、ゲート電極11aおよび11bに負電圧を印加することで、n<sup>-</sup>形半導体領域3への正孔の注入を促進し、より一層、半導体装置の通電能力を高め、オン抵抗を低減させることができる。

#### 【0081】

##### (第2実施形態)

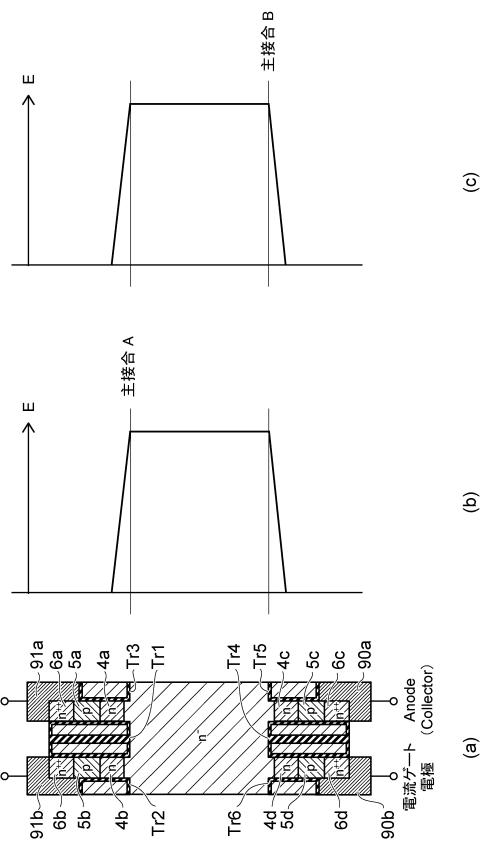

図24および図25を参照しつつ、第2実施形態に係る半導体装置の一例を説明する。

50

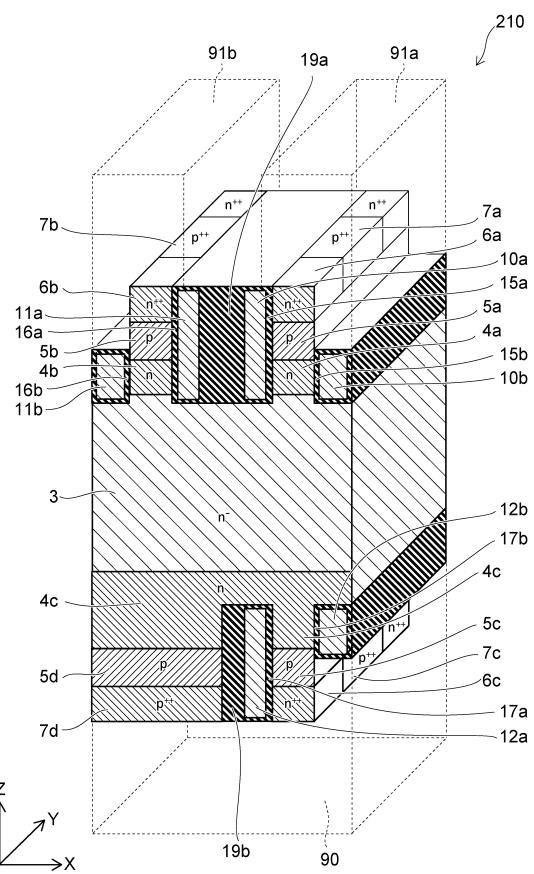

図24および図25は、第2実施形態に係る半導体装置200の一部を表す斜視断面図である。

なお、図24および図25では、エミッタ電極91aおよび電流ゲート電極91bが透過して表されている。また、図24と図25では、半導体装置200を異なる角度から見たときの様子が表されている。

#### 【0082】

図24に表すように、n形バリア領域4aの上には、半導体装置100と同様に、p形ベース領域5a、n<sup>++</sup>形コンタクト領域6a、p<sup>++</sup>形コンタクト領域7a、およびエミッタ電極91aが設けられている。

n形バリア領域4bの上には、p形ベース領域5bが設けられている。p形ベース領域5bの上には、n<sup>++</sup>形コンタクト領域6bおよびp<sup>++</sup>形コンタクト領域7bが選択的に設けられている。p形ベース領域5b、n<sup>++</sup>形コンタクト領域6b、およびp<sup>++</sup>形コンタクト領域7bは、電流ゲート電極91bと電気的に接続されている。

#### 【0083】

nバリア領域4aおよびp形ベース領域5aは、ゲート電極10aおよび11a、ゲート絶縁層15aおよび16a、絶縁部19aが内部に設けられたトレンチTr1と、ゲート電極10bおよびゲート絶縁層15bが内部に設けられたトレンチTr2との間に設けられている。また、nバリア領域4bおよびp形アノード領域5bは、トレンチTr1と、ゲート電極11bおよびゲート絶縁層16bが内部に設けられたトレンチTr3との間に設けられている。

#### 【0084】

n<sup>-</sup>形半導体領域3の一部の下には、n形バリア領域4cが設けられ、n形バリア領域4cの下には、p形ベース領域5cが設けられている。p形ベース領域5cの下には、n<sup>++</sup>形コンタクト領域6cおよびp<sup>++</sup>形コンタクト領域7cが設けられている。コレクタ電極90aは、n<sup>++</sup>形コンタクト領域6cの下面および一側面と、p<sup>++</sup>形コンタクト領域7cの下面および一側面と、p形ベース領域5cの一側面と、に接しており、これらの半導体領域と電気的に接続されている。

#### 【0085】

ゲート電極12aおよび12bは、それぞれ、ゲート絶縁層17aおよび17bを介してn<sup>-</sup>形半導体領域3の上に設けられている。ゲート電極12bのZ方向における長さは、ゲート電極12aのZ方向における長さよりも短い。n形バリア領域4cおよびp形ベース領域5cは、X方向において、ゲート電極12aと12bの間に位置し、ゲート絶縁層17aおよび17bを介してゲート電極12aおよび12bと対面している。

#### 【0086】

図25に表すように、n形バリア領域4dは、n<sup>-</sup>形半導体領域3の他の一部の下に設けられており、n形バリア領域4cとX方向において離間している。n形バリア領域4dの下側の構造は、例えば、n形バリア領域4cの下側の構造と、X方向において対称である。

#### 【0087】

すなわち、n形バリア領域4dの下にp形ベース領域5dが設けられ、p形ベース領域5dの下にn<sup>++</sup>形コンタクト領域6dおよびp<sup>++</sup>形コンタクト領域7dが設けられている。そして、コレクタ電極90bが、p形ベース領域5d、n<sup>++</sup>形コンタクト領域6d、およびp<sup>++</sup>形コンタクト領域7dと電気的に接続されている。また、n形バリア領域4dおよびp形ベース領域5dは、それぞれ、X方向において、ゲート絶縁層18aおよび18bを介してゲート電極13aおよび13bと対面している。

#### 【0088】

換言すると、n形バリア領域4cおよびp形ベース領域5cは、ゲート電極12aおよび13a、ゲート絶縁層17aおよび18a、絶縁部19bが内部に設けられたトレンチTr4と、ゲート電極12bおよびゲート絶縁層17bが内部に設けられたトレンチTr5との間に設けられている。また、n形バリア領域4dおよびp形ベース領域5dは、

10

20

30

40

50

トレンチTr4と、ゲート電極13bおよびゲート絶縁層18bが内部に設けられたトレンチTr6と、の間に設けられている。

#### 【0089】

ゲート電極12aおよび12bとコレクタ電極90aとの間には、ゲート絶縁層17aおよび17bが設けられ、これらの電極は離間している。同様に、ゲート電極13aおよび13bとコレクタ電極90bとの間には、ゲート絶縁層18aおよび18bが設けられ、これらの電極は離間している。ゲート電極12aと13aとの間には、絶縁部19bが設けられ、ゲート電極12aと13aは、X方向において離間している。

#### 【0090】

なお、図24および図25では、エミッタ電極91a側に設けられたトレンチTr1～Tr3やゲート電極10aおよび11aなどが、コレクタ電極90aおよび90b側に設けられたTr4～Tr6やゲート電極12aおよび13aなどと、Z方向において並んでいるが、これらの構成要件は、Z方向において並んでいなくてもよい。

また、図24および図25では、エミッタ電極91a側に設けられたトレンチTr1～Tr3やゲート電極10aおよび11aなどが、コレクタ電極90aおよび90b側に設けられたトレンチTr4～Tr6やゲート電極12aおよび13aなどと、同じ方向に延びているが、これらは互いに異なる方向に延びていてもよい。

トレンチTr4～Tr6のそれぞれのX方向における長さや、X方向における互いの距離の関係は、例えば、図15を参照しつつ説明したトレンチTr1～Tr3の関係と同じである。

#### 【0091】

次に、第2実施形態に係る半導体装置200の駆動方法の一例について説明する。

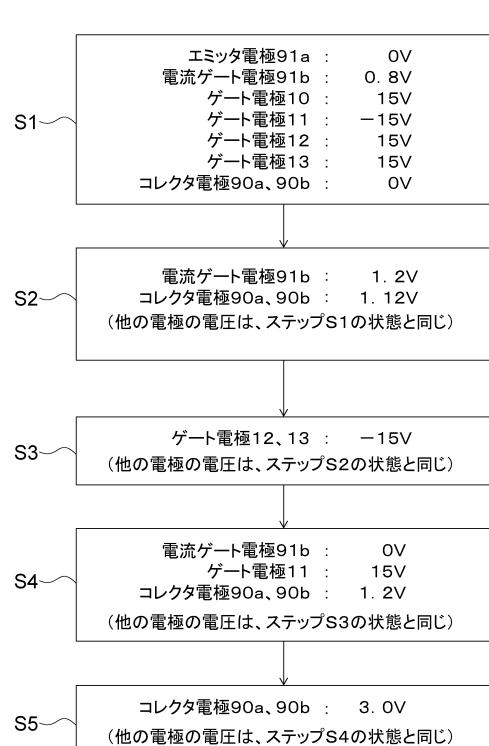

図26および図27は、第2実施形態に係る半導体装置200の駆動方法の一例を表すフローチャートである。

#### 【0092】

なお、図26および図27では、各半導体領域がシリコンから構成されている場合の駆動方法の一例が表されている。また、図26および図27では、ゲート電極10aおよび10bが、まとめてゲート電極10と表記されている。同様に、ゲート電極11a、11b、12a、12b、13a、および13bは、それぞれ、ゲート電極11、12、および13と表記されている。

#### 【0093】

まず、図26を用いて、コレクタ電極90aおよび90bからエミッタ電極91aへ電流を流す場合について説明する。

最初の状態では、エミッタ電極91aおよび電流ゲート電極91b、ゲート電極10～13、およびコレクタ電極90aおよび90bには、電圧が印加されていない。

#### 【0094】

この状態から、ステップS1に表す電圧を、各電極に印加する。エミッタ電極91aに対して、電流ゲート電極91bに、ビルトインポテンシャル(0.7V)以上の正電圧が印加されることで、p<sup>++</sup>形コンタクト領域7bからn<sup>-</sup>形半導体領域3に正孔が注入される。また、ゲート電極11に負電圧が印加されることで、p形ベース領域5bに正孔の蓄積層が形成され、n<sup>-</sup>形半導体領域3への正孔の注入が促進される。一方で、ゲート電極10、12、および13に正電圧が印加されることで、p形ベース領域5a、5c、および5dのそれぞれに反転層が形成される。

#### 【0095】

次に、ステップS2に表す電圧を、各電極に印加する。コレクタ電極90aおよび90bに正電圧が印加されることで、エミッタ電極91aから、コレクタ電極90aおよび90bに向けて、電子が流れる。また、コレクタ電極90aおよび90bへの正電圧の印加に合わせて、電流ゲート電極91bへの印加電圧を高める。これにより、コレクタ電極90aおよび90bと、電流ゲート電極91bと、の間の電位差の増加を抑え、コレクタ電極90aおよび90bと、電流ゲート電極91bと、の間で電流が流れ難くなる。

10

20

30

40

50

## 【0096】

次に、ステップS3に表す電圧を、各電極に印加する。ゲート電極12および13に負電圧が印加されることで、p形ベース領域5cおよび5dに正孔の蓄積層が形成され、コレクタ電極90aおよび90bからもn<sup>-</sup>形半導体領域3へ正孔が注入される。すなわち、ステップS2では、半導体装置200は、電子のみをキャリアとするユニポーラ型のMOSFETとして動作していたが、本ステップS3では、半導体装置200の動作が、電子および正孔をキャリアとするバイポーラ型のIGBT(IGBT)へ切り替わる。

## 【0097】

次に、ステップS4に表す電圧を、各電極に印加する。ゲート電極11に正電圧から負電圧が印加されることで、p形ベース領域5bに形成されていた正孔の蓄積層が消滅し、電子の反転層が形成される。また、電流ゲート電極91bの電圧が低下することで、p形ベース領域5bの反転層を通って、電流ゲート電極91bからコレクタ電極90aおよび90bに電子が流れ始める。すなわち、ステップS1～S3では、電流ゲート電極91bからn<sup>-</sup>形半導体領域3へ正孔を注入していたのに対して、ステップS4では、電流ゲート電極91bからn<sup>-</sup>形半導体領域3へ電子が注入される。

10

## 【0098】

次に、ステップS5に表すように、コレクタ電極90aおよび90bに印加する電圧を増大させる。これにより、半導体装置200に流れる電流値が上昇する。このとき、半導体装置200は、IGBTとして動作しているため、大きな通電能力を有する。従って、コレクタ電極90aおよび90bにおける電圧を上昇させることで、その電圧の上昇に応じた大きな電流を流すことが可能である。

20

## 【0099】

次に、図27を用いて、エミッタ電極91aからコレクタ電極90aおよび90bへ電流を流す場合について説明する。

## 【0100】

まず、図26のステップS1と同様の電圧を、各電極に印加する。これにより、n<sup>-</sup>形半導体領域3へ正孔が注入される。

## 【0101】

次に、ステップS2に表す電圧を、各電極に印加する。すなわち、コレクタ電極90aおよび90bに負電圧を印加する。また、電流ゲート電極91bと、コレクタ電極90aおよび90bとの間の電位差が大きくなりすぎないように、電流ゲート電極91bへの印加電圧を低下させる。コレクタ電極90aおよび90bに負電圧が印加されることで、p形ベース領域5a、5c、および5dの反転層を通って、エミッタ電極91aからコレクタ電極90aおよび90bへ電流が流れる。

30

## 【0102】

次に、ステップS3に表すように、ゲート電極10に負電圧を印加する。これにより、p形ベース領域5aに正孔の蓄積層が形成され、エミッタ電極91aからn<sup>-</sup>形半導体領域3へ正孔が注入される。このステップによって、半導体装置200の動作が、MOSFETからIGBTに切り替わる。

## 【0103】

40

次に、ステップS4に表す電圧を、各電極に印加する。ゲート電極11の印加電圧が負電圧から正電圧へ変化することで、p形ベース領域5bに形成されていた正孔の蓄積層が消滅し、電子の反転層が形成される。

## 【0104】

そして、ステップS4、S5、およびS6では、コレクタ電極90aおよび90bに印加される負電圧を大きくしていくことで、逆方向に流れる電流を大きくしている。また、電流ゲート電極91bと、コレクタ電極90aおよび90bとの間の電位差が大きくなりすぎないように、コレクタ電極90aおよび90bの電圧の変化に合わせて、適宜、電流ゲート電極91bに印加される負電圧を大きくしている。

## 【0105】

50

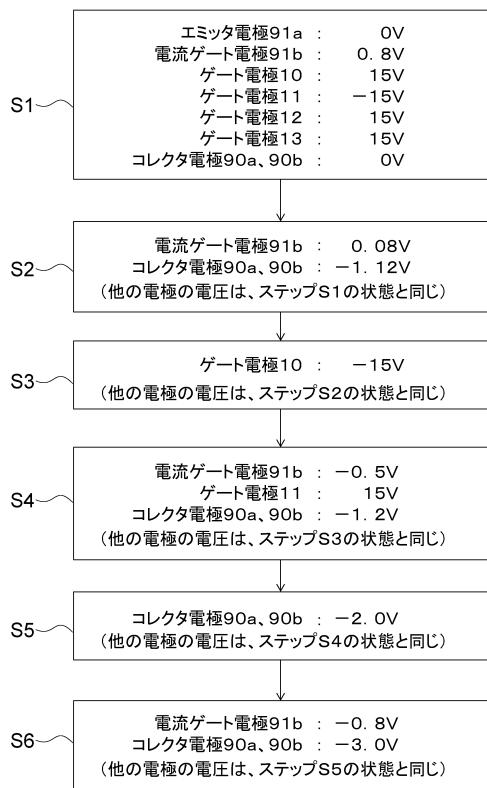

ここで、図28を用いて、上述した駆動方法を実行した際の半導体装置200の電流電圧特性を説明する。

図28は、第2実施形態に係る半導体装置200の電流電圧特性の一例を表すグラフである。

#### 【0106】

図28において、横軸は、コレクタ電極90aおよび90bへ印加された電圧Vcを表す。グラフ中の実線は、コレクタ電極90aおよび90bを流れる電流Icの、電圧Vcに対する変化を表し、破線は、電流ゲート電極91bを流れる電流Ieの、電圧Vcに対する変化を表している。また、グラフの上側には、図26および図27に表したステップのうち、各電圧Vcに対応するステップが記載されている。

10

#### 【0107】

順方向に電流を流す場合、ステップS2では、半導体装置200がMOSFETとして動作しているため、電圧Vcが上昇するにつれて、電流Icも線形に増大する。ステップS3で、半導体装置200の動作がMOSFETからIGTに切り替えられると、その後のステップS4およびS5では、ステップS2に比べて、電圧Vcに対して電流Icが大きく上昇している。

#### 【0108】

逆方向に電流を流す場合も同様に、ステップS2では、電圧Vcが上昇するにつれて電流Icも線形に増大する。ステップS4以降は、ステップS1に比べて、電圧Vcに対して電流Icが大きく上昇している。

20

#### 【0109】

このように本実施形態に係る半導体装置においては、図28に表す結果から、電流ゲート電極91bからn<sup>-</sup>形半導体領域3への少量の正孔注入によって、通電方向に拘らず、コレクタ電極が0Vから±3Vの範囲で、サイリスタのような深い伝導度変調での通電特性を得られていることがわかる。

#### 【0110】

なお、ここでは、ステップS2において電流ゲート電極91bからn<sup>-</sup>形半導体領域3へ正孔を注入する場合について説明したが、コレクタ電極90aおよび90bのいずれかからn<sup>-</sup>形半導体領域3へ正孔を注入するように、ゲート電極12または13を制御してもよい。この場合、コレクタ電極90aおよび90bのいずれかには、図26および図27に表した各ステップにおいて、電流ゲート電極91bと同じ電圧が印加される。

30

#### 【0111】

また、本実施形態に係る半導体装置は、順方向の通電時および逆方向の通電時のいずれにおいても、n<sup>-</sup>形半導体領域3へ正孔を注入し、n<sup>-</sup>形半導体領域3で深い伝導度変調を起こしつつ、動作をMOSFETからIGT(IGBT)へ移行させることができる。このため、双方向に通電可能でありながら、図28に表されるように、トライアックのようなスナップバックの発生は無い。

#### 【0112】

図29は、第2実施形態に係る半導体装置200のターンオフ時の波形を表すシミュレーション結果である。

40

図29では、T=0secでゲート電極12a、12b、13a、および13bをターンオフし、T=20μsecでゲート電極10a、10b、11a、および11bをターンオフした際の結果を表している。すなわち、コレクタ電極90側のゲート電極をターンオフすることで、コレクタ電極90からn<sup>-</sup>形半導体領域3への正孔の注入を停止させ、その後に、エミッタ電極91a側のゲート電極をターンオフすることで、これらの電極からの電子の注入を停止させた場合の結果を表している。

#### 【0113】

このように、エミッタ電極91a側とコレクタ電極90側とでゲート電極をターンオフするタイミングをずらすことで、n<sup>-</sup>形半導体領域3における過剰キャリアの蓄積量を低下させたうえで半導体装置をターンオフさせることが可能となり、ターンオフ時のスイッ

50

チング損失を低減することが可能となる。

【 0 1 1 4 】

あるいは、ターンオフ時には、コレクタ電圧がビルトインポテンシャル以上か未満かに拘らず、動作を IEGT (IGBT) から MOSFET へ移行させてターンオフすることで、テイル電流をさらに小さくすることができる。ただし、実際の高耐圧の半導体装置の場合、MOSFET の通電は、IEGT に比べて小さいため、MOSFET へ移行することで短絡モードとなり、かえって損失が増大する可能性もある。

【 0 1 1 5 】

次に、本実施形態に係る半導体装置の順方向および逆方向における耐圧について、図3-0および図3-1を参照しつつ、説明する。

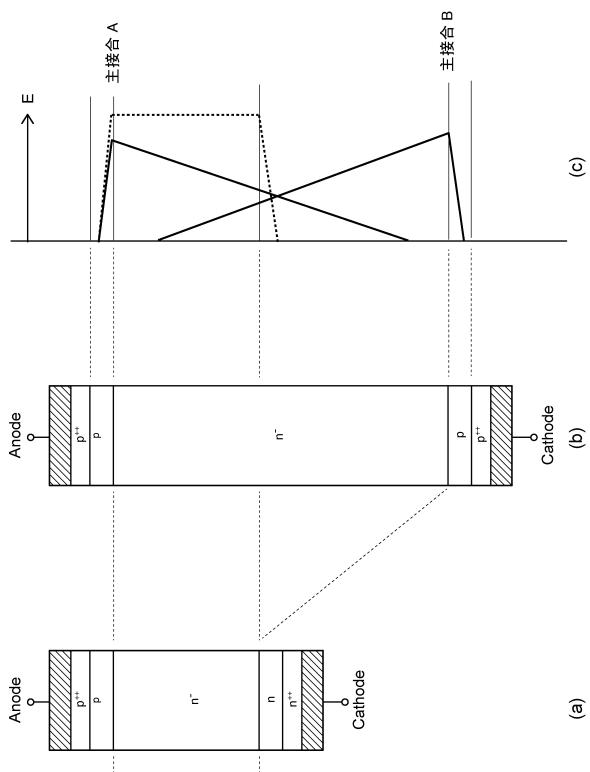

図30は、参考例に係る半導体装置の断面構造と耐圧を表す図である。

より具体的には、図30(a)には、パンチスルーパー型の半導体装置の断面構造が表され、図30(b)には、ノンパンチスルーパー型の半導体装置の断面構造が表されている。図30(c)では、図30(a)に表す半導体装置の順方向の耐圧時の各点の電界が破線で表され、図30(b)に表す半導体装置の順方向および逆方向の耐圧時の各点の電界が実線で表されている。

図31は、第2実施形態に係る半導体装置の断面構造と耐圧印加時の素子内部の電界を表す図である。

図31(a)では、半導体装置200の断面構造が模式的に表されている。図31(b)は、順方向の耐圧時の各点の電界を表し、図31(c)は、逆方向の耐圧時の各点の電界を表している。

( 0 1 1 6 )

【 0 1 1 7 】

図30(b)に表す半導体装置では、カソード電極からアノード電極へ向けて、順に、

$p^{++}$ 形コンタクト領域、 $p$ 形半導体領域、 $n^-$ 形半導体領域、 $p$ 形半導体領域、および

$p^{++}$ 形コンタクト領域が設けられている。

図 30 ( b ) に表す半導体装置において、アノード電極に対してカソード電極に正電圧が印加された場合、図 30 ( c ) に表すように、アノード電極側の p 形半導体領域と n 形半導体領域との間の主接合 A から n 形半導体領域へ空乏層が広がる。n 形半導体領域の厚みは、空乏層の広がりに対して十分に厚いため、空乏層の広がりは n 形半導体領域中で止まる。

一方で、カソード電極に対してアノード電極に正電圧が印加された場合は、図30(c)に表すように、カソード電極側のp形半導体領域とn<sup>-</sup>形半導体領域との間の主接合Bからn<sup>-</sup>形半導体領域へ空乏層が広がり、空乏層の広がりは、n<sup>-</sup>形半導体領域中で止まる。

このように、図 30 (b) に表す半導体装置は、順方向および逆方向のいずれにも耐圧を得ることが可能である。ただし、n<sup>-</sup>形半導体領域 3 を耐圧時の空乏層の伸びよりも厚いノンパンチスルーラー型の構造であるため、図 30 (a) に表す半導体装置に比べて、n<sup>-</sup>形半導体領域が厚く、半導体装置の低損失化が容易ではない。

【0118】

ここで、図31(a)に表すように、本実施形態に係る半導体装置では、カソード電極91に対してアノード電極90に正電圧が印加された場合、トレンチTr4～Tr6の底部からn<sup>-</sup>形半導体領域3へ空乏層が広がる。このとき、トレンチTr4～Tr6の底部から広がる空乏層は、カソード電極91側のトレンチTr1～Tr3の底部からn<sup>-</sup>形半導体領域3へ広がる空乏層によって止められる。

また、アノード電極90に対してカソード電極91に正電圧が印加された場合、トレンチTr1～Tr3の底部からn<sup>-</sup>形半導体領域3へ空乏層が広がる。このとき、トレンチTr1～Tr3の底部から広がる空乏層は、アノード電極90側のトレンチTr4～Tr6の底部からn<sup>-</sup>形半導体領域3へ広がる空乏層によって止められる。

すなわち、本実施形態に係る半導体装置では、トレンチTr1～Tr6が、主接合AまたはBとしての機能と、空乏層のストッパーとしてのn形フィールドストップ領域として機能と、を印加電圧の方向に応じて変化させている。10

#### 【0119】

この結果、本実施形態に係る半導体装置では、図31(b)および図31(c)に表すように、順方向の耐圧時および逆方向の耐圧時のいずれにおいても、空乏層がn<sup>-</sup>形半導体領域3の全面に広がるパンチスルーパー型を実現することができる。すなわち、本実施形態によれば、双方向の通電が可能でありながら、いずれの方向にもパンチスルーパー型の耐圧を実現することができ、半導体装置を低損失化することが可能となる。

#### 【0120】

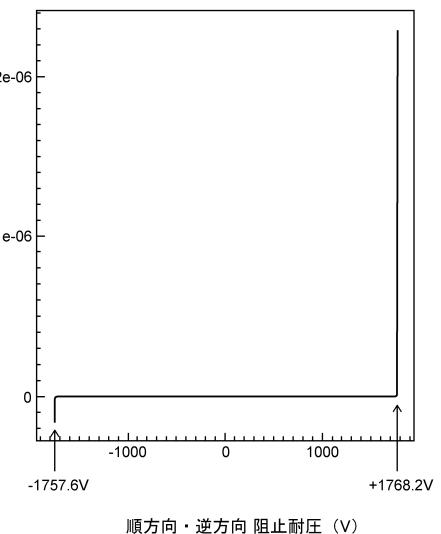

図32は、第2実施形態に係る半導体装置200の順方向と逆方向の耐圧波形を表すシミュレーション結果である。20

ここでは、n<sup>-</sup>形半導体領域3におけるn形不純物濃度を $1.0 \times 10^{13} \text{ cm}^{-3}$ 、n<sup>-</sup>形半導体領域3の厚みを $108 \mu\text{m}$ としてシミュレーションを行った。図32から、順方向および逆方向のいずれの耐圧時にも、約1750Vの耐圧が得られていることがわかる。

#### 【0121】

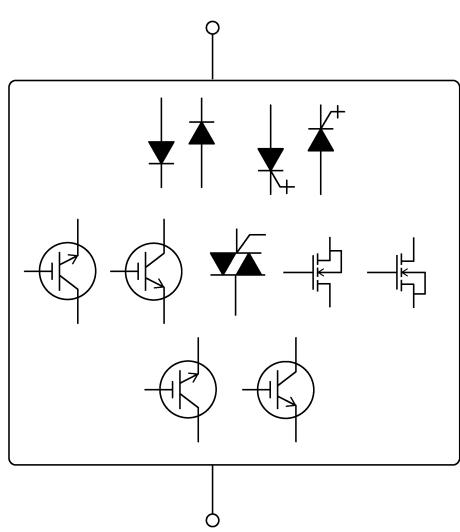

図33は、第2実施形態に係る半導体装置200で実現可能な動作モードの例を表す図である。

図33に表すように、本実施形態に係る半導体装置200によれば、ゲート電極10～13の電圧を制御することで、半導体装置200の動作を、ダイオードや、MOSFET、IGBT、トライアックなどに適宜切り替えることが可能である。30

このように、本実施形態に係る半導体装置は、各ゲート電極の制御のみで、従来のほとんどすべてのパワーデバイスの理想的な特性を再現可能である。応用回路によっては大幅な部品点数の削減も期待できる。また、本実施形態に係る半導体装置によれば、従来素子の性能を飛躍的に高める可能性もある。

#### 【0122】

以上の通り、本実施形態に係る半導体装置では、「ビルトインポテンシャル以下の深い伝導度変調の利用」「ビルトインポテンシャルの無いサイリスタ(IGBT、IGBT)」「MOSFETとIGBTの融合」「サイリスタのような深いバイポーラモードでの完全双方向通電特性」「パンチスルーパー型設計で順逆阻止耐圧保証」などを同時に複数実現することができる。これは、従来のGTRの理想的な特徴である、電流ゲート、バイポーラ動作、かつビルトイン電圧なしと、従来のサイリスタ(IGBT, IGBTなども含む)の特徴である大きな通電能力と、の両方の長所を同時に兼ね備えながら、従来の不純物拡散層を用いた半導体装置には実現不可能だった、電力を効率良く制御するために理想的な特長を、従来の限界を超えて実現した電力用半導体装置である。40

#### 【0123】

図34は、第2実施形態に係る半導体装置の応用例を表す断面図である。

図34に表す例では、半導体装置200のコレクタ電極90aおよび90bが、別の半導体装置200のエミッタ電極91aと、金属層92を介して直列に接続されている。

上述した通り、本実施形態に係る半導体装置200は、通電方向にビルトインポテンシ50

ヤルが存在しない。このため、複数の半導体装置 200 を直列に接続した場合であっても、ビルトインポテンシャルの重畠も発生しない。従って、本実施形態に係る半導体装置は、複数の半導体装置を直列に接続する場合に、特に有利である。

#### 【0124】

(変形例)

図35は、第2実施形態の変形例に係る半導体装置210の一部を表す斜視断面図である。

半導体装置210は、ゲート電極13aおよび13b、n<sup>++</sup>形コンタクト領域6dが設けられておらず、n<sup>++</sup>形コンタクト領域6cと、p<sup>++</sup>形コンタクト領域7cおよび7dが、共通のコレクタ電極90と接続されている点で、半導体装置200と異なる。

10 また、半導体装置210では、n<sup>-</sup>形半導体領域3の下に共通のn形バリア領域4cが設けられている。p形ベース領域5cおよび5dは、n形バリア領域4cの下に設けられ、p形ベース領域5cは、ゲート電極12aと12bとの間に位置している。p<sup>++</sup>形コンタクト領域7dは、p形ベース領域5dの下に設けられている。

#### 【0125】

半導体装置210では、ゲート電極13aおよび13bが設けられていないため、MOSFET動作の際にコレクタ電極側からの正孔注入は行えないが、図26および図27に表す通電動作は、同様に実行可能である。すなわち、ゲート電極13以外の電圧を、図26に表すように印加していくことで、コレクタ電極90からエミッタ電極91aへ順方向に電流を流すことが可能である。また、ゲート電極13以外の電圧を、図27に表すように印加していくことで、エミッタ電極91からコレクタ電極90へ逆方向に電流を流すことが可能である。

20

#### 【0126】

(第3実施形態)

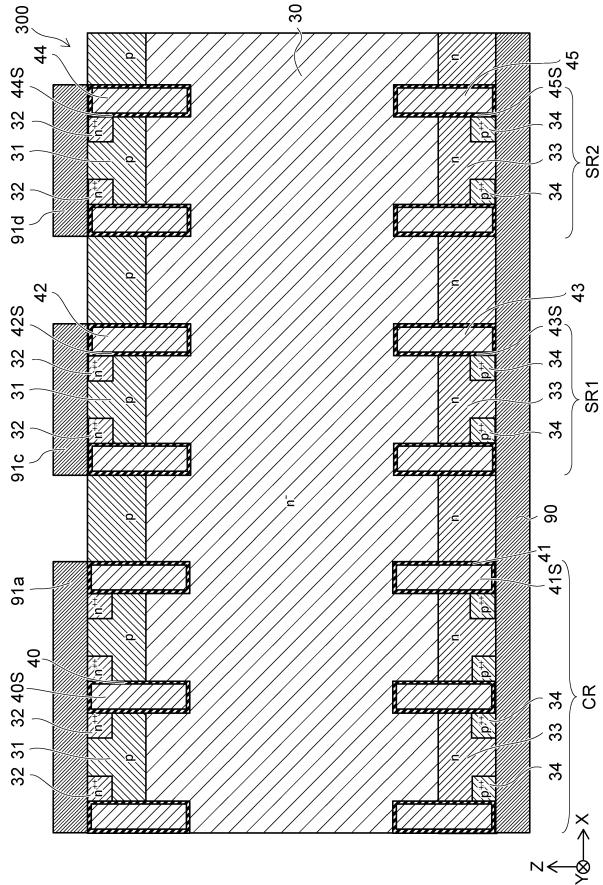

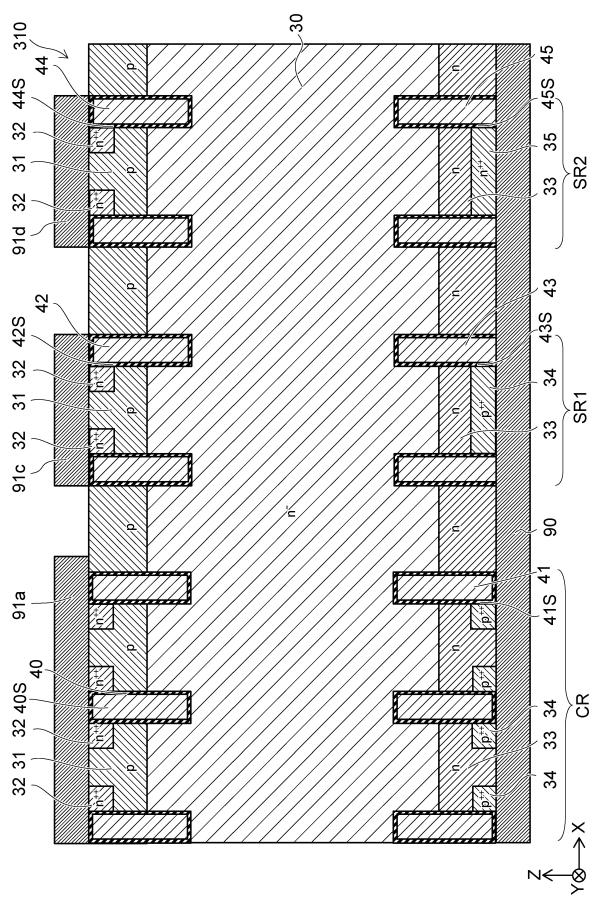

図36は、第3実施形態に係る半導体装置300の一部を表す断面図である。

図36に表すように、半導体装置300は、n<sup>-</sup>形半導体領域30と、p形ベース領域31と、n<sup>++</sup>形コンタクト領域32と、n形バリア領域33と、p<sup>++</sup>形コンタクト領域34と、ゲート電極40～45と、ゲート絶縁層40S～45Sと、コレクタ電極90と、エミッタ電極91a、91c、および91dと、を有する。

#### 【0127】

半導体装置300は、図36に表すように、素子領域CR、センス領域SR1、およびセンス領域SR2を有する。素子領域CRは、コレクタ電極90とエミッタ電極91aとの間で通電が行われる領域である。センス領域SR1およびセンス領域SR2は、それぞれ、エミッタ電極91cおよび91dと、コレクタ電極90との間で通電が行われる領域である。

30

#### 【0128】

p形ベース領域31は、n<sup>-</sup>形半導体領域30の上に設けられている。

n<sup>++</sup>形コンタクト領域32は、p形ベース領域31の上に選択的に設けられている。

n形バリア領域33は、n<sup>-</sup>形半導体領域30の下に設けられている。

p<sup>++</sup>形コンタクト領域34は、n形バリア領域33の下に選択的に設けられている。

40

p形ベース領域31、n<sup>++</sup>形コンタクト領域32、n形バリア領域33、およびp<sup>++</sup>形コンタクト領域34は、それぞれ、X方向において複数設けられ、Y方向に延びている。

#### 【0129】

ゲート電極40は、素子領域CRにおいて、ゲート絶縁層40Sを介してn<sup>-</sup>形半導体領域30中およびp形ベース領域31中に設けられている。ゲート電極42は、センス領域SR1において、ゲート絶縁層42Sを介してn<sup>-</sup>形半導体領域30中およびp形ベース領域31中に設けられている。ゲート電極44は、センス領域SR2において、ゲート絶縁層44Sを介してn<sup>-</sup>形半導体領域30中およびp形ベース領域31中に設けられている。

50

ゲート電極 4 0、4 2、および 4 4 は、それぞれ、X 方向において、ゲート絶縁層 4 0 S、4 2 S、および 4 4 S を介して p 形ベース領域 3 1 および n<sup>++</sup> 形コンタクト領域 3 2 と対面している。

#### 【 0 1 3 0 】

エミッタ電極 9 1 a は、素子領域 C R において、p 形ベース領域 3 1 および n<sup>++</sup> 形コンタクト領域 3 2 の上に設けられ、これらの半導体領域と電気的に接続されている。エミッタ電極 9 1 c は、センス領域 S R 1 において、p 形ベース領域 3 1 および n<sup>++</sup> 形コンタクト領域 3 2 の上に設けられ、これらの半導体領域と電気的に接続されている。エミッタ電極 9 1 d は、センス領域 S R 2 において、p 形ベース領域 3 1 および n<sup>++</sup> 形コンタクト領域 3 2 の上に設けられ、これらの半導体領域と電気的に接続されている。 10

#### 【 0 1 3 1 】

エミッタ電極 9 1 c および 9 1 d には、エミッタ電極 9 1 a と同様の電圧が印加される。また、エミッタ電極 9 1 c および 9 1 d は、それぞれの電極に流れる電流をモニタできるように、不図示の検出器が接続されている。

#### 【 0 1 3 2 】

ゲート電極 4 1 は、素子領域 C R において、ゲート絶縁層 4 1 S を介して n<sup>-</sup> 形半導体領域 3 0 中および n 形バリア領域 3 3 中に設けられている。ゲート電極 4 3 は、センス領域 S R 1 において、ゲート絶縁層 4 3 S を介して n<sup>-</sup> 形半導体領域 3 0 中および n 形バリア領域 3 3 中に設けられている。ゲート電極 4 5 は、センス領域 S R 2 において、ゲート絶縁層 4 5 S を介して n<sup>-</sup> 形半導体領域 3 0 中および n 形バリア領域 3 3 中に設けられている。 20

ゲート電極 4 1、4 3、および 4 5 は、それぞれ、X 方向において、ゲート絶縁層 4 1 S、4 3 S、および 4 5 S を介して n 形バリア領域 3 3 および p<sup>++</sup> 形コンタクト領域 3 4 と対面している。

#### 【 0 1 3 3 】

コレクタ電極 9 0 は、素子領域 C R、センス領域 S R 1、およびセンス領域 S R 2 において、各領域の n 形バリア領域 3 3 および p<sup>++</sup> 形コンタクト領域 3 4 と電気的に接続されている。

ゲート電極 4 0 ~ 4 5 は、それぞれ、X 方向において複数設けられ、Y 方向に延びている。 30

#### 【 0 1 3 4 】

ここで、半導体装置 3 0 0 の動作について説明する。

エミッタ電極 9 1 a に対してコレクタ電極 9 0 に正の電圧が印加された状態で、ゲート電極 4 0 に閾値以上の正電圧が印加されると、ゲート絶縁層 4 0 S 近傍の p 形ベース領域 3 1 に電子の反転層が形成される。このとき、ゲート電極 4 1 に閾値以上の正電圧を印加してもよい。この場合、ゲート絶縁層 4 1 S 近傍の n 形バリア領域 3 3 に電子の蓄積層が形成される。

これにより、半導体装置 3 0 0 は、電子のみをキャリアとする M O S F E T として動作し、コレクタ電極 9 0 からエミッタ電極 9 1 a へ電流が流れる。 40

#### 【 0 1 3 5 】

続けて、コレクタ電極 9 0 への印加電圧を上昇させ、エミッタ電極 9 1 a に対するコレクタ電極 9 0 への印加電圧がビルトインポテンシャルよりも高くなると、ゲート電極 4 1 に閾値以上の負電圧を印加し、ゲート絶縁層 4 1 S 近傍の n 形バリア領域 3 3 に正孔の反転層を形成する。これにより、エミッタ電極 9 1 a から n<sup>-</sup> 形半導体領域 3 0 へ電子が注入され、コレクタ電極 9 0 から n<sup>-</sup> 形半導体領域 3 0 へ正孔が注入される。すなわち、半導体装置 3 0 0 の動作が、M O S F E T から、電子および正孔をキャリアとする I G B T へ移行する。

#### 【 0 1 3 6 】

一方で、コレクタ電極 9 0 とエミッタ電極 9 1 a との間の電位差に拘らず、ゲート電極 4 2 には、閾値以上の正電圧が印加され、ゲート電極 4 3 には、閾値以上の負電圧が印加 50

される。また、ゲート電極 4 4 および 4 5 には、閾値以上の正電圧が印加される。すなわち、素子領域 C R における動作に拘らず、センス領域 S R 1 は I G B T として動作し、センス領域 S R 2 は M O S F E T として動作するように、各ゲート電極に電圧が印加される。

#### 【 0 1 3 7 】

センス領域 S R 2 は、M O S F E T として動作するため、コレクタ電極 9 0 とエミッタ電極 9 1 d との間にビルトインポテンシャルが存在しない。一方で、センス領域 S R 1 は、I G B T として動作するため、コレクタ電極 9 0 とエミッタ電極 9 1 c との間の電位差が、ビルトインポтенシャル以上にならなければ動作しない。

このため、例えば、センス領域 S R 2 で電流が検出された状態で、コレクタ電極 9 0 とエミッタ電極 9 1 a との間の電位差を上昇させていく、センス領域 S R 1 で電流が検出されたときに、素子領域 C R の動作を M O S F E T から I G B T に切り替えることができる。このように、2つのセンス領域を流れる電流を検出して、その検出結果に基づいて M O S F E T と I G B T の切り替えを行うことで、より正確なタイミングで M O S F E T と I G B T の切り替えを行うことができる。従って、例えば、電位差がビルトインポテンシャル未満のときにゲート電極 4 1 の電圧を切り替えてしまい、コレクタ電極 9 0 とエミッタ電極 9 1 a との間で通電が行われなくなるといったことを抑制できる。

#### 【 0 1 3 8 】

なお、図 3 6 に表した素子領域 C R は、一例である。本実施形態に係る半導体装置 3 0 0 の素子領域 C R は、適宜変更することが可能である。以下で、本実施形態に係る半導体装置の各変形例について説明する。

#### 【 0 1 3 9 】

##### ( 第 1 変形例 )

図 3 7 は、第 3 実施形態の第 1 変形例に係る半導体装置 3 1 0 の一部を表す断面図である。

半導体装置 3 1 0 は、センス領域 S R 1 および S R 2 の構造が半導体装置 3 0 0 と異なる。

#### 【 0 1 4 0 】

センス領域 S R 1 において、n<sup>-</sup> 形半導体領域 3 0 の下には、n 形バリア領域 3 3 および電極 4 3 が設けられている。電極 4 3 は、X 方向において、絶縁層 4 3 S を介して n 形バリア領域 3 3 と対面している。電極 4 3 同士の間であって、n 形バリア領域 3 3 の下には、全面に p<sup>++</sup> 形コンタクト領域 3 4 が設けられている。

#### 【 0 1 4 1 】

センス領域 S R 2 において、n<sup>-</sup> 形半導体領域 3 0 の下には、n 形バリア領域 3 3 および電極 4 5 が設けられている。電極 4 5 は、X 方向において、絶縁層 4 5 S を介して n 形バリア領域 3 3 と対面している。電極 4 5 同士の間であって、n 形バリア領域 3 3 の下には、全面に n<sup>++</sup> 形コンタクト領域 3 5 が設けられている。

電極 4 3 および 4 5 は、例えば、コレクタ電極 9 0 と電気的に接続されている。

#### 【 0 1 4 2 】

半導体装置 3 1 0 では、センス領域 S R 1 のコレクタ電極 9 0 側において、電極 4 3 同士の間の全面に p<sup>++</sup> 形コンタクト領域 3 4 が設けられている。このため、電極 4 3 の電圧に拘らず、コレクタ電極 9 0 とエミッタ電極 9 1 c との間の電圧がビルトインポテンシャル以上になると、p<sup>++</sup> 形コンタクト領域 3 4 を通して正孔が注入される。

また、センス領域 S R 2 のコレクタ電極 9 0 側において、電極 4 5 同士の間の全面に n<sup>++</sup> 形コンタクト領域 3 5 が設けられている。このため、電極 4 5 の電圧に拘らず、エミッタ電極 9 1 d から n<sup>-</sup> 形半導体領域 3 0 へ注入された電子は、n<sup>++</sup> 形コンタクト領域 3 5 を通してコレクタ電極 9 0 へ流れる。

#### 【 0 1 4 3 】

このように、ゲート電極 4 3 および 4 5 をコレクタ電極 9 0 に接続した場合であっても、半導体装置 3 1 0 の構造によれば、センス領域 S R 1 における I G B T 動作による電流

10

20

30

40

50

を検出し、センス領域 S R 2においてM O S F E T動作による電流を検出することが可能である。すなわち、半導体装置 3 0 0 では、M O S F E T動作時とI G B T動作時で、ゲート電極 4 1 と 4 3との間およびゲート電極 4 1 と 4 5との間に、異なった電圧が印加されていた。しかし、本変形例によれば、そのような制御が不要となり、半導体装置 3 1 0 の制御を容易にすることができます。

#### (第 2 变形例)

図 3 8 は、第 3 実施形態の第 2 变形例に係る半導体装置 3 2 0 の一部を表す断面図である。

半導体装置 3 2 0 は、素子領域 C R の構造が半導体装置 3 0 0 と異なる。

素子領域 C R において、p 形ベース領域 3 1 の一部の上には、電流ゲート電極 9 1 b が設けられ、p 形ベース領域 3 1 の当該一部は、電流ゲート電極 9 1 b と電気的に接続されている。エミッタ電極 9 1 a と電流ゲート電極 9 1 b は、離間して設けられている。

#### 【 0 1 4 4 】

電流ゲート電極 9 1 b には、第 1 実施形態および第 2 実施形態と同様に、エミッタ電極 9 1 a に対して、ビルトインポテンシャル以上の電圧が印加される。

すなわち、ゲート電極 4 0 および 4 1 に正電圧が印加され、素子領域 C R がM O S F E Tとして動作する際、エミッタ電極 9 1 a に対して電流ゲート電極 9 1 b にビルトインポテンシャル以上の正電圧が印加され、電流ゲート電極 9 1 b から n - 形半導体領域 3 0 へ正孔が注入される。

#### 【 0 1 4 5 】

すなわち、半導体装置 3 2 0 における素子領域 C R では、第 2 実施形態に係る半導体装置 2 0 0 と同様に、M O S F E T として動作させる際に n - 形半導体領域 3 0 に正孔を注入し、n - 形半導体領域 3 0 で電導度変調を生じさせることで、通電能力を高め、オン抵抗を低減することが可能である。

#### 【 0 1 4 6 】

#### (第 3 变形例)

図 3 9 は、第 3 実施形態の第 3 变形例に係る半導体装置 3 3 0 の一部を表す断面図である。

半導体装置 3 3 0 は、素子領域 C R の構造が半導体装置 3 0 0 と異なる。

#### 【 0 1 4 7 】

素子領域 C R において、p 形ベース領域 3 1 の一部および n + + 形コンタクト領域 3 2 の一部には、エミッタ電極 9 1 a が電気的に接続され、p 形ベース領域 3 1 の他の一部および n + + 形コンタクト領域 3 2 の他の一部には、電流ゲート電極 9 1 b が電気的に接続されている。エミッタ電極 9 1 a および電流ゲート電極 9 1 b は、互いに離間して設けられている。半導体装置の動作時には、電流ゲート電極 9 1 b に、エミッタ電極 9 1 a に対してビルトインポテンシャル以上の電圧が印加される。

#### 【 0 1 4 8 】

また、素子領域 C R において、n 形バリア領域 3 3 の一部および p + + 形コンタクト領域 3 4 の一部には、コレクタ電極 9 0 a が電気的に接続され、n 形バリア領域 3 3 の他の一部および p + + 形コンタクト領域 3 4 の他の一部には、コレクタ電極 9 0 b が電気的に接続されている。コレクタ電極 9 0 a および 9 0 b は、互いに離間して設けられている。半導体装置の動作時には、コレクタ電極 9 0 b に、コレクタ電極 9 0 a に対してビルトインポテンシャル以上の電圧が印加される。

#### 【 0 1 4 9 】

センス領域 S R 1 および S R 2 では、n 形バリア領域 3 3 および p + + 形コンタクト領域 3 4 は、コレクタ電極 9 0 c と電気的に接続されている。コレクタ電極 9 0 c は、コレクタ電極 9 0 a と電気的に接続されている。

#### 【 0 1 5 0 】

ゲート電極 4 0 および 4 1 に正電圧が印加されると、素子領域 C R がM O S F E Tとして動作する。このとき、コレクタ電極 9 0 b および電流ゲート電極 9 1 b から n - 形半導

10

20

30

40

50

体領域 30 へ正孔が注入される。本変形例によれば、半導体装置 320 に比べて、n<sup>-</sup> 形半導体領域 30 により多くの正孔を注入し、n<sup>-</sup> 形半導体領域 30 に蓄積される正孔の濃度を高め、素子領域 CR における通電能力をさらに高めることができる。

#### 【0151】

##### (第4実施形態)

図40は、第4実施形態に係る半導体装置400の一部を表す断面図である。

半導体装置400は、素子領域CRと、素子領域CRを囲む終端領域TRと、を有する。

図40に表すように、素子領域CRには、例えば、第1実施形態に係る半導体装置100と同様の機能を有する構造が設けられている。

10

#### 【0152】

終端領域TRでは、n<sup>-</sup>形半導体領域3の上に、p形半導体領域50が設けられている。p形半導体領域50の上には、p<sup>++</sup>形半導体領域52が選択的に設けられている。エミッタ電極91aは、p<sup>++</sup>形半導体領域52と電気的に接続されている。

#### 【0153】

n形バリア領域2の周り、n<sup>-</sup>形半導体領域3の周り、およびp形半導体領域50の上には、絶縁層54が設けられている。絶縁層54の上には、半絶縁層55が設けられている。半絶縁層55の一端は、p<sup>++</sup>形半導体領域52に接続され、他端は、n<sup>++</sup>形コレクタ領域1に接続されている。すなわち、半絶縁層55の一端は、エミッタ電極91aと同電位に接続され、他端は、コレクタ電極90と同電位に接続される。

20

なお、図40に表す例に限らず、本実施形態に係る半導体装置400では、絶縁層54が設けられずに半絶縁層55が、p形半導体領域50、n<sup>-</sup>形半導体領域3、n形バリア領域2、およびn<sup>++</sup>形コレクタ領域1の各半導体領域に直接接してもよい。この場合、絶縁層54を半絶縁層55の上に設けても良い。

#### 【0154】

半絶縁層55の電気抵抗は、n<sup>-</sup>形半導体領域3などの半導体領域の電気抵抗よりも高く、絶縁層54の電気抵抗よりも低い。絶縁層54は、絶縁材料として、例えば、酸化シリコンまたは窒化シリコンなどを含む。半絶縁層55は、半絶縁材料として、SIN (Semi-Insulating Silicon Nitride : 窒化アモルファスシリコン) またはSIPOS (Semi-Insulating Polycrystalline Silicon : 半絶縁性多結晶シリコン) を含む。

30

#### 【0155】

コレクタ電極90とエミッタ電極91aとの間に電位差がある場合、n<sup>++</sup>形コレクタ領域1とp<sup>++</sup>形半導体領域52との間で半絶縁層55を通して微小な電流が流れる。半導体装置400の耐圧時に、n<sup>++</sup>形コレクタ領域1とp<sup>++</sup>形半導体領域52との間の電位差が、半絶縁層55において徐々に降下していくことで、半導体装置400の外周に生じる電界強度の偏りを緩和し、半導体装置400の耐圧を高めることができる。

#### 【0156】

また、半絶縁層55がn<sup>-</sup>形半導体領域3の周りにZ方向に沿って設けられ、n<sup>++</sup>形コレクタ領域1とp<sup>++</sup>形半導体領域52との間の半絶縁層55に沿った距離を長くすることで、半絶縁層55における電圧降下をより緩やかにし、半導体装置400の耐圧をさらに高めることができる。

40

#### 【0157】

##### (第1変形例)

図41は、第4実施形態の第1変形例に係る半導体装置410の一部を表す断面図である。

半導体装置410では、素子領域CRに、第2実施形態に係る半導体装置200と同様の機能を有する構造が設けられている。

#### 【0158】

終端領域TRの素子領域CR側では、n<sup>-</sup>形半導体領域3の上に、p形半導体領域50が設けられ、n<sup>-</sup>形半導体領域3の下に、n形半導体領域56が設けられている。

50

p形半導体領域50の上には、p<sup>++</sup>形半導体領域52が設けられ、p<sup>++</sup>形半導体領域52は、エミッタ電極91aと電気的に接続されている。

n形半導体領域56の下には、n<sup>++</sup>形半導体領域58が設けられ、n<sup>++</sup>形半導体領域58は、コレクタ電極90aと電気的に接続されている。

#### 【0159】

絶縁層54は、p形半導体領域50の上面、n<sup>-</sup>形半導体領域3の側面、およびn形半導体領域56の下面に設けられている。半絶縁層55は、絶縁層54の上に設けられている。半絶縁層55の一端は、p<sup>++</sup>形半導体領域52に接続され、他端は、n<sup>++</sup>形半導体領域58に接続されている。

#### 【0160】

本変形例では、終端領域TRにおいて、半絶縁層55が、半導体装置410の上面から下面に亘って連続的に設けられている。このため、n<sup>++</sup>形半導体領域58とp<sup>++</sup>形半導体領域52との間の半絶縁層55に沿った距離を長くすることができ、終端領域TRにおいて、半導体装置410の上面、側面、および下面の各部における電圧降下をさらに小さくすることができる。このため、半導体装置400に比べて、終端領域TRにおける電界集中をさらに緩和し、半導体装置の耐圧をさらに高めることができる。

#### 【0161】

##### (第2変形例)

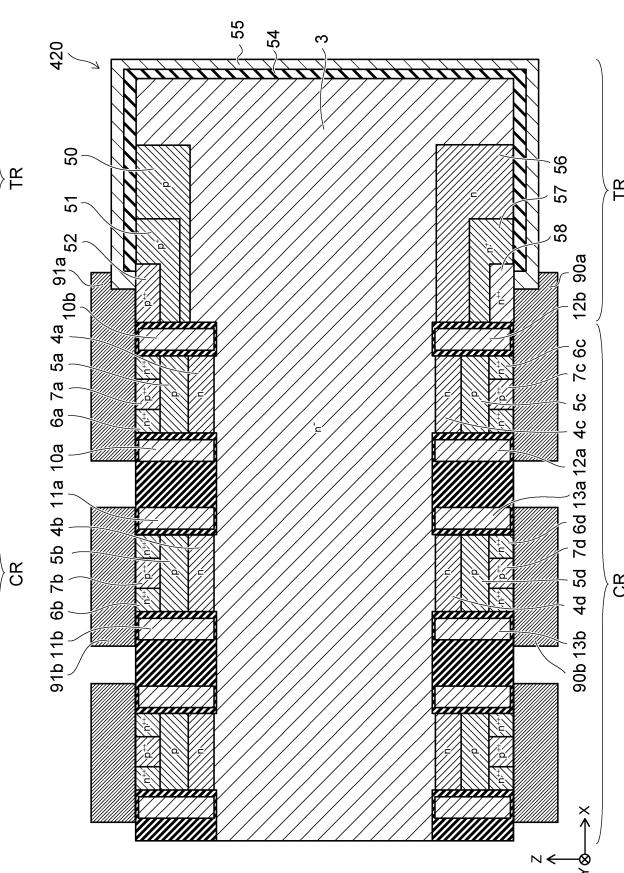

図42は、第4実施形態の第2変形例に係る半導体装置420の一部を表す断面図である。

半導体装置420は、p<sup>+</sup>形半導体領域51およびn<sup>+</sup>形半導体領域57がさらに設けられている点で、半導体装置410と異なる。

#### 【0162】

p<sup>+</sup>形半導体領域51は、p形半導体領域50の上に選択的に設けられている。p<sup>++</sup>形半導体領域52は、p<sup>+</sup>形半導体領域51の上に選択的に設けられている。

また、n<sup>+</sup>形半導体領域57は、n形半導体領域56の上に選択的に設けられている。n<sup>++</sup>形半導体領域58は、n<sup>+</sup>形半導体領域57の上に選択的に設けられている。

#### 【0163】

本変形例においても、半導体装置410と同様に、終端領域TRにおける電界集中を緩和し、半導体装置の耐圧を向上させることができる。

#### 【0164】

##### (第3変形例)

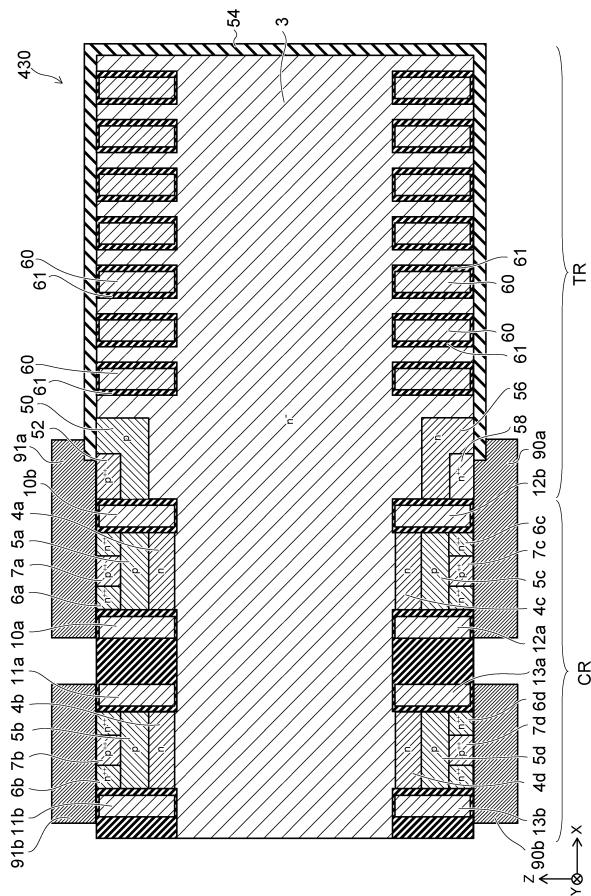

図43は、第4実施形態の第3変形例に係る半導体装置430の一部を表す断面図である。

半導体装置430では、終端領域TRにおいて、半絶縁層55に代えて、導電部60および絶縁層61が設けられている。導電部60は、絶縁層61を介してn<sup>-</sup>形半導体領域3中に設けられている。導電部60は、半導体装置430の上面側と下面側の両方に設けられている。また、半導体装置の中央から外周に向かう方向において、複数の導電部60が、互いに離間して設けられている。それぞれの導電部60は、半導体装置430の外周に沿って環状に設けられている。

#### 【0165】

または、平面視(Z方向から見た場合)において、ドット状あるいは矩形状の導電部60を複数設け、これらの導電部60を、半導体装置430の外周に沿って環状に配列させてもよい。この場合、導電部60同士の間隔は、半導体装置430をターンオフした際の空乏層の広がりに合わせて設定される。

#### 【0166】

導電部60は、コレクタ電極90aやエミッタ電極91aなどとは電気的に分離されており、導電部60の電位は、フローティングである。導電部60は、それぞれが電気的に互いに分離されて設けられていてもよいし、隣り合う複数の導電部60が電気的に接続されていてもよい。

10

20

30

40

50

例えば、エミッタ電極 91a に対してコレクタ電極 90a に正電圧が印加され、半導体装置 430 がオフ状態のとき、上面側（コレクタ電極 90a 側）では、半導体装置の中央側から外周に向かって、各導電部 60 の電位が徐々に降下していき、下面側（エミッタ電極 91a 側）では、外周から中央側に向かって、各導電部 60 の電位が徐々に降下していく。そして、n- 形半導体領域 3 における等電位線は、各導電部 60 の電位に応じて、広がっていく。このため、終端領域 TR における電界集中を緩和し、半導体装置の耐圧を向上させることが可能である。

#### 【0167】

また、導電部 60 が、半導体装置 430 の上面側と下面側の両方に設けられていることで、導電部 60 同士の間の電圧降下を小さくし、終端領域 TR における電界集中をさらに緩和させ、半導体装置の耐圧を向上させることができる。あるいは、半導体装置の耐圧が向上した分、終端領域 TR の厚み（半導体装置の中心から外周に向かう方向の寸法）を薄くし、半導体装置を小型化することが可能となる。10

#### 【0168】

また、半導体装置 430 では、素子領域 CR において、半導体装置 200 と同様の機能を有する構造が設けられている。第 2 実施形態で説明したように、半導体装置 200 は、耐圧の保持方向に拘らず、Z 方向において空乏層が n- 形半導体領域 3 の全面に広がるパンチスルーパー型の構造を有する。

本変形例に係る半導体装置 430 では、終端領域 TR における耐圧を保持するための p-n 接合が設けられておらず、終端領域 TR における耐圧は、導電部 60 によって得ている。20 そして、この導電部 60 は、n- 形半導体領域 3 を中心として Z 方向に対称に設けられている。

終端領域 TR に p-n 接合を設け、これにより耐圧を得る場合、Z 方向における構造が非対称となるため、パンチスルーパー型の構造においては、順方向および逆方向のいずれか一方において耐圧を得ることができるが、他方においては耐圧を得ることができない。しかし、本変形例のように、導電部 60 を n- 形半導体領域 3 を中心として Z 方向に対称に設けることで、耐圧の保持方向に拘らず、終端領域 TR において高い耐圧を得ることができる。従って、本変形例に係る半導体装置の終端領域 TR の構造は、図 43 に表すように、パンチスルーパー型の双方向通電可能な構造が素子領域 CR に設けられている場合に、特に有効である。30

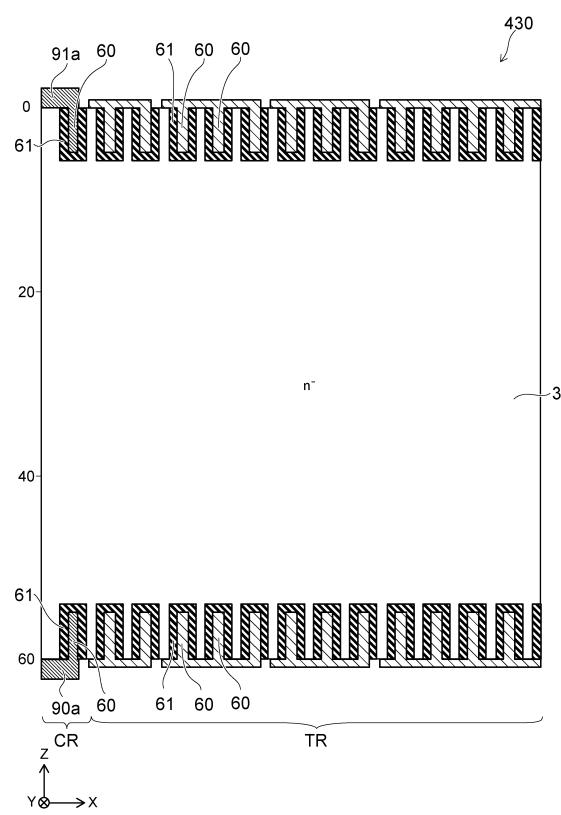

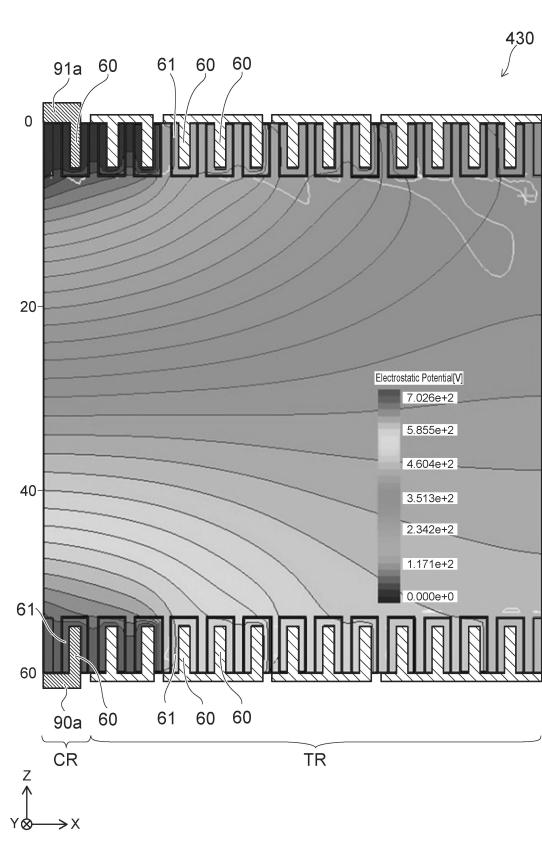

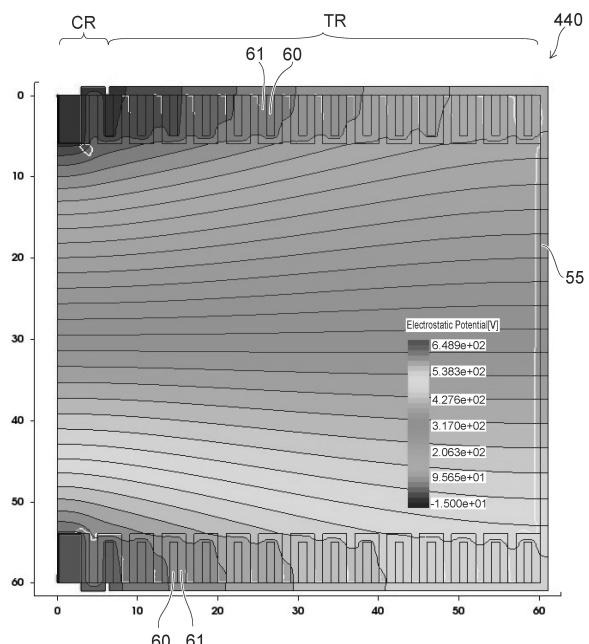

#### 【0169】

本変形例に係る半導体装置 430 のシミュレーション結果について、図 44 および図 45 を参照しつつ説明する。

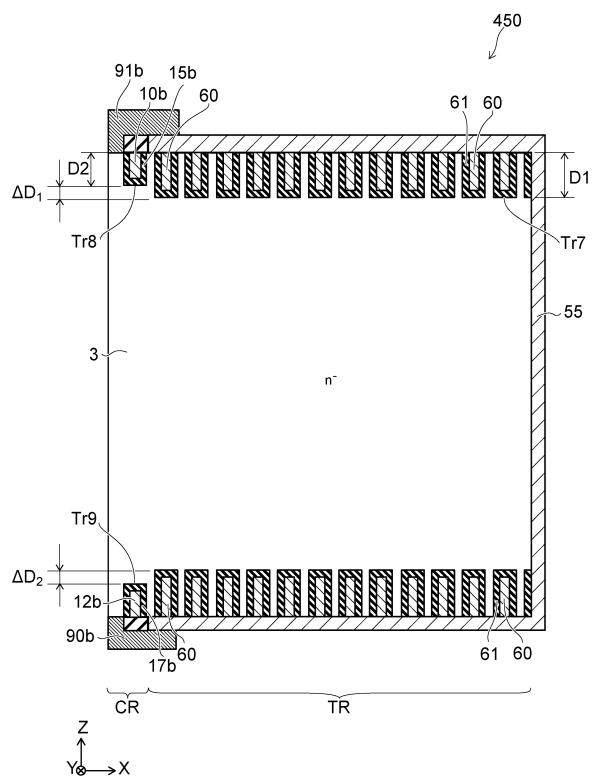

図 44 は、シミュレーションに用いた第 4 実施形態の第 3 変形例に係る半導体装置 430 の一部を表す断面図である。

図 45 は、図 44 に表す構造における電位分布を表すシミュレーション結果である。

なお、図 45 では、半導体装置 430 の Z 方向における中心から上方では、色が黒いほど電位が低いことを表し、中心から下方では、色が黒いほど電位が高いことを表している。

#### 【0170】

図 44 に表すように、シミュレーションに用いた半導体装置 430 では、隣り合う複数の導電部 60 同士が電気的に接続されている。また、最も素子領域 CR 側に設けられた導電部 60 が、エミッタ電極 91a およびコレクタ電極 90a と接続されている。

#### 【0171】

このような構造についてシミュレーションを行った結果、図 45 に表すように、半導体装置 430 の上面、側面、および下面に等電位線が広がっており、半導体装置 430 の上面、側面、および下面で耐圧が保持されていることがわかる。また、このように、上面、側面、および下面で耐圧が保持されることで、上面側および下面側の一方の終端領域だけで等電位線を分布させて耐圧を確保する場合に比べて、終端領域の厚み（半導体装置の中心から外周に向かう方向の寸法）を薄くし、半導体装置を小型化することが可能となる。4050

また、図45に表す結果から、Z方向において略対称に電位が分布していることもわかる。従って、本変形例によれば、コレクタ電極90とエミッタ電極91aとの間の耐圧の方向に拘らず、半導体装置430の上面、側面、および下面で耐圧を保持することが可能である。

#### 【0172】

##### (第4変形例)

図46は、第4実施形態の第4変形例に係る半導体装置440の一部を表す断面図である。

なお、図46では、素子領域CRに設けられたn<sup>-</sup>形半導体領域3以外の各半導体領域が省略されている。

10

#### 【0173】

半導体装置440は、終端領域TRを覆う半絶縁層55が設けられている点で、半導体装置430と異なる。

半絶縁層55は、終端領域TRの上面、側面、および下面に設けられ、各導電部60と接続されている。また、半絶縁層55の一端は、エミッタ電極91aと接続され、他端はコレクタ電極90と接続されている。

半絶縁層55は、抵抗性のフィールドプレートとして、終端領域TRにおける導電部60の電位を、終端領域TRの厚み方向において均一に分布させ、耐圧印加時に、終端領域TRの上面および下面における電界集中を抑制する働きがある。

#### 【0174】

20

本変形例による効果について、図47を参照しつつ、説明する。

図47は、第4実施形態の第4変形例に係る半導体装置440の一部を表す断面図および各部の電界を表すグラフである。

図47において、断面図の上方には、半導体装置430の上面側（エミッタ電極91a側）における電界強度が表され、下方には、半導体装置430の下面側（コレクタ電極90側）における電界強度が表されている。また、断面図の右側方には、半導体装置430の端面における電界強度が表され、左側方には、半導体装置430の素子領域CRにおける電界強度が表されている。

#### 【0175】

半導体装置440は、Z方向において対称な構造を有し、かつn<sup>-</sup>形半導体領域3の全面に亘って空乏層が広がるパンチスルーパー型の構造を有している。このため、図47の左側方のグラフに示されるように、素子領域CRにおける電界強度は、Z方向においてEmax×でほぼ一定となっている。

30

#### 【0176】

終端領域TRでは、半絶縁層55が設けられていることで、半導体装置400と同様に、コレクタ電極90からエミッタ電極91aに向けて半絶縁層55中を電流が流れる。このとき、導電部60の電位が半絶縁層55の各部の電位と等しくなることで、終端領域TRにおけるn<sup>-</sup>形半導体領域3中の電位をより均等に分布させることができる。このため、図47の上方、右側方、および下方のグラフに示されるように、終端領域TRにおける電界強度は、それぞれの面に沿って、Esでほぼ一定となる。なお、Esは、Emaxよりも小さな値である。

40

また、半導体装置440は、Z方向において対称な構造を有するため、このような終端領域TRにおける均一な電位の分布は、半導体装置440の耐圧の方向に拘らず得られる。

#### 【0177】

このように、本変形例によれば、耐圧の方向に拘らず、終端領域TRにおける電界集中をより一層緩和し、半導体装置の耐圧を高めることができる。あるいは、終端領域TRにおける電界集中が緩和された分、終端領域TRの厚みを小さくし、半導体装置を小型化することが可能である。

#### 【0178】

50

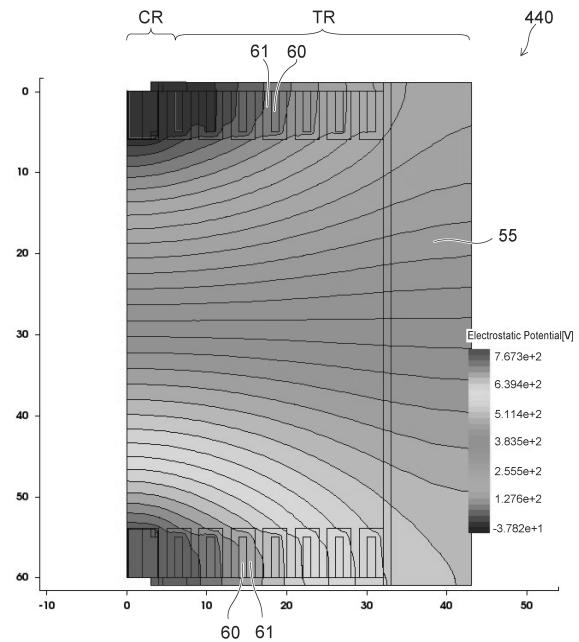

図48および図49は、第4実施形態の第4変形例に係る半導体装置440のシミュレーション結果である。

図48および図49では、それぞれ、半導体装置440の終端領域TRにおける電位分布が示されている。図48および図49では、図45と同様に、半導体装置440のZ方向における中心から上方では、色が黒いほど電位が低いことを表し、中心から下方では、色が黒いほど電位が高いことを表している。

また、図48と図49では、半導体装置440の側面に設けられた半絶縁層55の厚みが異なる。すなわち、図48に表す半導体装置では、終端領域TRの上面、側面、および下面に設けられた半絶縁層55の厚みが一定である。これに対して、図49に表す半導体装置では、終端領域TRの側面に設けられた半絶縁層55の厚みが、上面および下面に設けられた半絶縁層55の厚みよりも厚い。

10

#### 【0179】

図48に表すように、半絶縁層55の厚みが一定である場合、終端領域TRの上面、側面、および下面において、均等に電圧が降下していく。これに対して、図49に表すように、側面の半絶縁層55が厚い場合、側面上の半絶縁層55の電気抵抗が他の部分よりも低くなる。この結果、側面における電圧降下が小さくなり、電界強度が低下する。このため、図49に表す構成によれば、半導体装置の側面がダイシングなどの加工によって粗く形成されている場合でも、側面における電界強度を低下させ、側面を流れるリーク電流を低減させることが可能となる。

#### 【0180】

図50は、第4実施形態の第4変形例に係る半導体装置440の耐圧波形を表すシミュレーション結果である。

20

図50では、n<sup>-</sup>形半導体領域3におけるn形不純物濃度を $1.0 \times 10^{13} \text{ cm}^{-3}$ 、n<sup>-</sup>形半導体領域3のZ方向における厚みを $48 \mu\text{m}$ として700Vの耐圧を保証するよう半導体装置を設計した場合の、計算結果の一例が表されている。

図50に表す結果から、耐圧の保持方向に拘らず、700V以上の耐圧が得られていることが分かる。

#### 【0181】

##### (第5変形例)

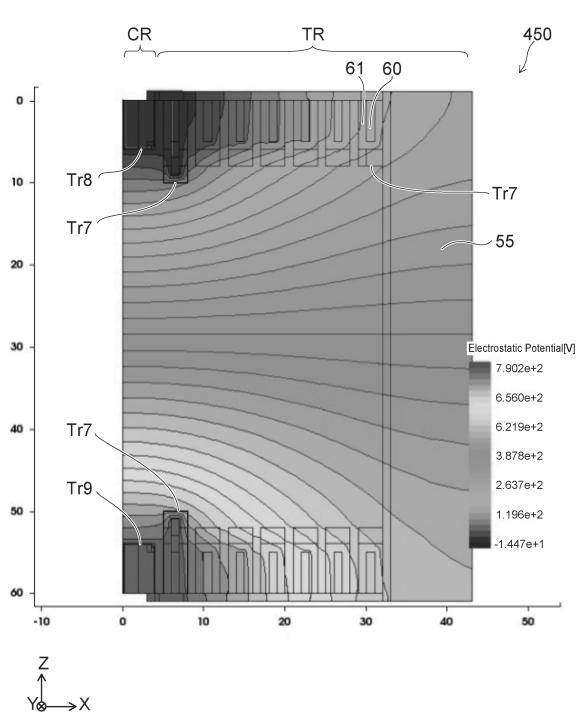

図51は、第4実施形態の第5変形例に係る半導体装置450の一部を表す断面図である。

30

なお、図51では、素子領域CRに設けられたn<sup>-</sup>形半導体領域3以外の各半導体領域が省略されている。

#### 【0182】

半導体装置450は、導電部60が設けられたトレンチTr7の深さ(Z方向における寸法)D1が、ゲート電極10bが設けられたトレンチTr8の深さD2、およびゲート電極12bが設けられたトレンチTr9の深さD3よりも深い点で、半導体装置440と異なる。

より具体的には、トレンチTr7の深さD1は、素子領域CRの最も終端領域TR側に形成されたトレンチTr8およびTr9の各々の深さD2およびD3よりも深い。

40

#### 【0183】

また、これらのトレンチの深さの関係は、例えば、導電部60、ゲート電極10b、およびゲート電極12bのそれぞれのZ方向における寸法の関係に同様に表れる。すなわち、半導体装置450では、導電部60のZ方向における長さは、ゲート電極10bのZ方向における長さおよびゲート電極12bのZ方向における長さよりも長い。

#### 【0184】

トレンチTr7が、トレンチTr8およびTr9よりも深く設けられていることで、素子領域CR外周(素子領域CRと終端領域TRの境界領域)における電界集中を緩和し、半導体装置の耐圧をさらに高めることができる。

#### 【0185】

10

20

30

40

50

なお、全てのトレンチTr7が、トレンチTr8およびTr9よりも深く形成されている必要はない。例えば、終端領域TRに形成された複数のトレンチTr7のうち、最も素子領域CR側に位置するトレンチTr7のみが、トレンチTr8およびTr9よりも深く形成されていてもよい。また、トレンチTr7同士の深さが互いに異なっていてもよい。

#### 【0186】

また、深さD1とD2の差D<sub>1</sub>は、トレンチTr8の幅(X方向における寸法)の1/5倍以上であることが望ましい。同様に、深さD1とD3の差D<sub>2</sub>は、トレンチTr9の幅の1/5倍以上であることが望ましい。

このような構造によれば、半導体装置の耐圧をより一層高めることが可能である。

#### 【0187】

図52は、第4実施形態の第5変形例に係る半導体装置450のシミュレーション結果である。

図52に表すシミュレーションに用いた半導体装置では、終端領域TRに設けられた全てのトレンチTr7が、トレンチTr8およびTr9より深く形成されている。また、終端領域TRの最も素子領域CR側に位置するトレンチTr7が、他のトレンチTr7よりもさらに深く形成されている。

#### 【0188】

図52に表すシミュレーション結果から、終端領域TRの最も素子領域CR側に位置するトレンチTr7によって等電位線がn<sup>-</sup>形半導体領域3のZ方向中心側に持ち上げられている様子がわかる。この結果からも、本変形例によれば、素子領域CR外周における電界集中を緩和し、半導体装置の耐圧を向上できることがわかる。

#### 【0189】

なお、上述した各例では、素子領域CRに、第1実施形態または第2実施形態に係る半導体装置が設けられている場合について説明したが、本実施形態に係る半導体装置は、これに限られない。例えば、素子領域CRには、ダイオードやMOSFET、IGBTなどの単一の機能を有する素子が設けられてもよい。その場合でも、上述した各構成を終端領域TRに設けることで、半導体装置の外周における電界分布の偏りを緩和し、半導体装置の耐圧を高めることができる。

#### 【0190】

##### (第5実施形態)

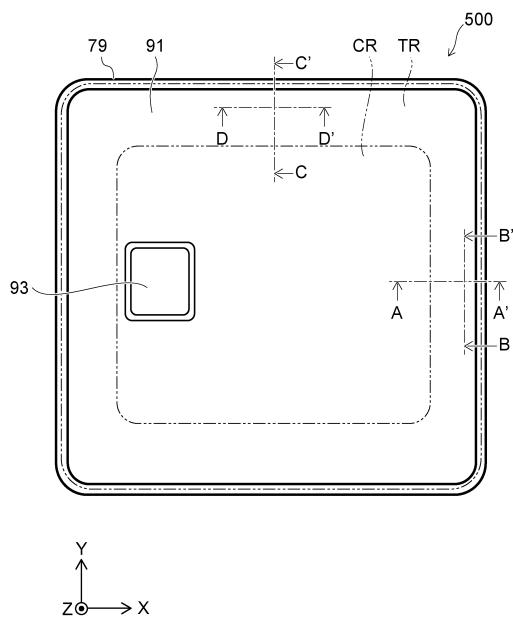

図53は、第5実施形態に係る半導体装置500を表す平面図である。

図54(a)は、図53のA-A'断面図であり、図54(b)は、図53のB-B'断面図である。

図55(a)は、図53のC-C'断面図であり、図55(b)は、図53のD-D'断面図である。

#### 【0191】

半導体装置500は、例えば、IGBTである。

図53～図55に表すように、半導体装置500は、n<sup>++</sup>形コンタクト領域70、p<sup>++</sup>形コレクタ領域71、n形バッファ領域72、n<sup>-</sup>形半導体領域73、p形ベース領域74、n<sup>++</sup>形エミッタ領域75、ゲート電極76、ゲート絶縁層77、p形半導体領域78、絶縁層79、コレクタ電極90、エミッタ電極91、およびゲートパッド93を有する。

#### 【0192】

図53に表すように、素子領域CRは、終端領域TRに囲まれている。

エミッタ電極91とゲートパッド93は、半導体装置500の上面に、互いに離間して設けられている。

#### 【0193】

図54および図55に表すように、コレクタ電極90は、半導体装置500の下面に設けられている。

n<sup>++</sup>形コンタクト領域70は、終端領域TRにおいて、コレクタ電極90の上に設け

10

20

30

40

50

られている。

p<sup>++</sup>形コレクタ領域71は、素子領域CRにおいて、コレクタ電極90の上に設けられている。

n<sup>++</sup>形コンタクト領域70およびp<sup>++</sup>形コレクタ領域71は、コレクタ電極90と電気的に接続されている。

n形バッファ領域72は、n<sup>++</sup>形コンタクト領域70およびp<sup>++</sup>形コレクタ領域71の上に設けられている。

#### 【0194】

n<sup>-</sup>形半導体領域73は、n形バッファ領域72の上に設けられている。

p形ベース領域74は、n<sup>-</sup>形半導体領域73の上に設けられている。

n<sup>++</sup>形エミッタ領域75は、p形ベース領域74の上に選択的に設けられている。

ゲート電極76は、n<sup>-</sup>形半導体領域73およびp形ベース領域74中にゲート絶縁層77を介して設けられている。p形ベース領域74およびn<sup>++</sup>形エミッタ領域75は、X方向において、ゲート絶縁層77を介してゲート電極76と対面している。

#### 【0195】

p形ベース領域74、n<sup>++</sup>形エミッタ領域75、およびゲート電極76は、X方向において複数設けられ、それぞれがY方向に延びている。

#### 【0196】

p形半導体領域78は、終端領域TRにおいて、n<sup>-</sup>形半導体領域73上に設けられ、

p形ベース領域74、n<sup>++</sup>形エミッタ領域75、およびゲート電極76を囲んでいる。

p形半導体領域78は、p形ベース領域74よりも深くまで設けられている。

絶縁層79は、n形バッファ領域72の外周上、n<sup>-</sup>形半導体領域73とp形半導体領域78の周り、およびp形半導体領域78の上に設けられている。

#### 【0197】

エミッタ電極91は、p形ベース領域74およびn<sup>++</sup>形エミッタ領域75の上に設けられ、これらの半導体領域と電気的に接続されている。ゲート電極76とエミッタ電極91との間にはゲート絶縁層77が設けられ、これらの電極は、電気的に分離されている。

また、エミッタ電極91の一部は、終端領域TRにも位置し、絶縁層79を介してp形半導体領域78の周りに設けられている。

#### 【0198】

図54(b)および図55(b)に表すように、n<sup>-</sup>形半導体領域73の一部とp形半導体領域78は、半導体装置500の外周において、周方向に沿って交互に設けられている。また、p形半導体領域78は、下方に向かうほど、素子領域CRから終端領域TRに向かう方向における長さが減少している。

このため、Z方向の各位置においてp形半導体領域78に含まれるp形不純物量は、上方に向かうほど増加し、下方に向かうほど減少している。また、p形半導体領域78同士の間に位置するn<sup>-</sup>形半導体領域73のn形不純物量は、Z方向の各位置において、上方に向かうほど減少し、下方に向かうほど増加している。

#### 【0199】

半導体装置500がターンオフされ、エミッタ電極91に対してコレクタ電極90に正電圧が印加されている場合、n<sup>-</sup>形半導体領域73とp形ベース領域74とのpn接合面およびn<sup>-</sup>形半導体領域73とp形半導体領域78とのpn接合面から空乏層が広がる。このとき、n<sup>-</sup>形半導体領域73とp形半導体領域78とのpn接合面からは横方向にも空乏層が広がる。

#### 【0200】

上述したように、p形半導体領域78に含まれるp形不純物量は、下方に向かうほど減少し、p形半導体領域78同士の間のn<sup>-</sup>形半導体領域73のn形不純物量は、下方に向かうほど減少している。

このため、n<sup>-</sup>形半導体領域73とp形半導体領域78との間の各点における電位は、上方から下方に向かって徐々に低下していく。すなわち、従来では、終端領域TRの面積

10

20

30

40

50

を大きくし、終端領域TRにおける電界集中を面内方向で緩和していたのに対して、本実施形態に係る半導体装置によれば、p形半導体領域78によって、終端領域TRにおける電界集中を上下方向で緩和させることができる。

従って、本実施形態によれば、半導体装置の終端領域の面積を小さくし、半導体装置を小型化することが可能となる。

#### 【0201】

なお、上述した各例では、第5実施形態に係る半導体装置がIGBTである場合について説明したが、第5実施形態に係る半導体装置は、素子領域CRにおいて、ダイオードやMOSFETなどであってもよい。これらの半導体装置においても、終端領域TRにp形半導体領域78が設けられていることで、半導体装置の外周における電界集中を上下方向において緩和し、半導体装置を小型化することができる。10

#### 【0202】

以上で説明した各実施形態における、各半導体領域の間の不純物濃度の相対的な高低については、例えば、SCM(走査型静電容量顕微鏡)を用いて確認することができる。なお、各半導体領域におけるキャリア濃度は、各半導体領域において活性化している不純物濃度と等しいものとみなすことができる。従って、各半導体領域の間のキャリア濃度の相対的な高低についても、SCMを用いて確認することができる。

また、各半導体領域における不純物濃度については、例えば、SIMS(二次イオン質量分析法)により測定することができる。

#### 【0203】

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。実施形態に含まれる、例えば、n<sup>++</sup>形コレクタ領域1、n形バリア領域2、n<sup>-</sup>形半導体領域3、n形バリア領域4、p形ベース領域5、n<sup>++</sup>形コンタクト領域6、p<sup>++</sup>形コンタクト領域7、ゲート電極10～13および40～45、ゲート絶縁層15～18および40S～45S、n<sup>-</sup>形半導体領域30、p形ベース領域31、n<sup>++</sup>形コンタクト領域32、n形バリア領域33、p<sup>++</sup>形コンタクト領域34、n<sup>++</sup>形コンタクト領域35、p形半導体領域50、p<sup>++</sup>形半導体領域51、p<sup>++</sup>形半導体領域52、絶縁層54、半絶縁層55、n形半導体領域56、n<sup>+</sup>形半導体領域57、n<sup>++</sup>形半導体領域58、導電部60、絶縁層61、n<sup>++</sup>形コンタクト領域70、p<sup>++</sup>形コレクタ領域71、n形バッファ領域72、n<sup>-</sup>形半導体領域73、p形ベース領域74、n<sup>++</sup>形エミッタ領域75、ゲート電極76、ゲート絶縁層77、p形半導体領域78、絶縁層79、コレクタ電極90、エミッタ電極91、金属層92、ゲートパッド93などの各要素の具体的な構成に関しては、当業者が公知の技術から適宜選択することができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。2030

#### 【符号の説明】

#### 【0204】

100、110、200、210、300～330、400～430、500 半導体装置、1 n<sup>++</sup>形ドレイン領域、2 n形バリア領域、3 n<sup>-</sup>形半導体領域、4 n形バリア領域、5 p形ベース領域、6 n<sup>++</sup>形コンタクト領域、7 p<sup>++</sup>形コンタクト領域、10～13 ゲート電極、30 n<sup>-</sup>形半導体領域、31 p形ベース領域、32 n<sup>++</sup>形コンタクト領域、33 n形バリア領域、34 p<sup>++</sup>形コンタクト領域、35 n<sup>++</sup>形コンタクト領域、40～45 ゲート電極、50 p形半導体領域、52 p<sup>++</sup>形半導体領域、55 半絶縁層、56 n形半導体領域、58 n<sup>++</sup>形半導体領域、60 導電部、70 n<sup>++</sup>形コンタクト領域、71 p<sup>++</sup>形コレクタ領域、72 n形バッファ領域、73 n<sup>-</sup>形半導体領域、74 p形ベース領域、75 n<sup>++</sup>形エミッタ領域、76 ゲート電極、77 ゲー4050

ト絶縁層、 7 8 p 形半導体領域、 7 9 絶縁層、 9 0 コレクタ電極、 9 1 エミ

ッタ電極、 9 2 金属層、 9 3 ゲートパッド

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【 図 3 6 】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図50】

【図51】

【図52】

【図53】

【図54】

【図55】

## フロントページの続き

(51)Int.Cl.

F I

|               |               |                  |               |              |                |

|---------------|---------------|------------------|---------------|--------------|----------------|

| <i>H 01 L</i> | <i>29/41</i>  | <i>(2006.01)</i> | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 2 F</i> |

| <i>H 01 L</i> | <i>29/423</i> | <i>(2006.01)</i> | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 2 L</i> |

| <i>H 01 L</i> | <i>29/49</i>  | <i>(2006.01)</i> | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 2 S</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 2 M</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 6 A</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 8 Z</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 5 C</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 5 A</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 7 F</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 2 N</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/06</i> | <i>3 0 1 M</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/06</i> | <i>3 0 1 S</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/06</i> | <i>3 0 1 V</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/78</i> | <i>6 5 2 P</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/06</i> | <i>3 0 1 F</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/06</i> | <i>3 0 1 G</i> |

|               |               |                  | <i>H 01 L</i> | <i>29/44</i> | <i>L</i>       |

|               |               |                  | <i>H 01 L</i> | <i>29/58</i> | <i>G</i>       |

|               |               |                  | <i>H 01 L</i> | <i>29/44</i> | <i>Y</i>       |

(56)参考文献 特開2001-320049(JP,A)

特開2010-225816(JP,A)

特開2005-340626(JP,A)

特開平10-256550(JP,A)

特開2015-176927(JP,A)

(58)調査した分野(Int.Cl., DB名)

|               |                    |

|---------------|--------------------|

| <i>H 01 L</i> | <i>2 9 / 7 8</i>   |

| <i>H 01 L</i> | <i>2 1 / 3 3 6</i> |

| <i>H 01 L</i> | <i>2 9 / 0 6</i>   |

| <i>H 01 L</i> | <i>2 9 / 1 2</i>   |

| <i>H 01 L</i> | <i>2 9 / 4 1</i>   |

| <i>H 01 L</i> | <i>2 9 / 4 2 3</i> |

| <i>H 01 L</i> | <i>2 9 / 4 9</i>   |

| <i>H 01 L</i> | <i>2 9 / 7 3 9</i> |