(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7356982号

(P7356982)

(45)発行日 令和5年10月5日(2023.10.5)

(24)登録日 令和5年9月27日(2023.9.27)

(51)国際特許分類

|        |                  |        |        |         |

|--------|------------------|--------|--------|---------|

| H 01 L | 21/336 (2006.01) | H 01 L | 29/78  | 3 0 1 G |

| H 01 L | 29/78 (2006.01)  | H 01 L | 29/78  | 3 0 1 X |

| H 01 L | 21/8234(2006.01) | H 01 L | 27/088 | E       |

| H 01 L | 27/088(2006.01)  | H 01 L | 27/092 | G       |

| H 01 L | 21/8238(2006.01) | H 01 L | 29/50  | M       |

請求項の数 9 (全34頁) 最終頁に続く

(21)出願番号 特願2020-534980(P2020-534980)

(86)(22)出願日 平成30年12月31日(2018.12.31)

(65)公表番号 特表2021-509536(P2021-509536)

A)

(43)公表日 令和3年3月25日(2021.3.25)

(86)国際出願番号 PCT/IB2018/060735

(87)国際公開番号 WO2019/135154

(87)国際公開日 令和1年7月11日(2019.7.11)

審査請求日 令和3年5月25日(2021.5.25)

(31)優先権主張番号 15/862,930

(32)優先日 平成30年1月5日(2018.1.5)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 390009531

インターナショナル・ビジネス・マシンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク州 アーモンク ニューオーチャードロード

New Orchard Road, Armonk, New York 10504, United States of America

(74)代理人 100112690

弁理士 太佐 種一

最終頁に続く

(54)【発明の名称】 縦型輸送電界効果トランジスタのための半導体構造を形成する方法、半導体構造、および集積回路

## (57)【特許請求の範囲】

## 【請求項1】

半導体構造を形成する方法であつて、

基板の上面に配置された複数のフィンを形成することと、

置換金属ゲート(RMG)・プロセスを使用して前記複数のフィンから1つまたは複数の縦型輸送電界効果トランジスタ(VTET)を形成することとを含み、

前記VTETのうちの所与の1つの少なくとも1つのフィンを囲むゲートが、ゲート・コンタクト金属層に配置されたゲート自己整合コンタクト(SAC)・キャッピング層を含み、前記ゲート・コンタクト金属層が、前記少なくとも1つのフィンの端部に隣接して配置される方法。

## 【請求項2】

前記1つまたは複数のVTETを形成することが、

前記複数のフィンを囲む前記基板の前記上面に配置された下部ソース/ドレイン領域を形成することと、

前記下部ソース/ドレイン領域に配置された下部スペーサを形成することとを含む、請求項1に記載の方法。

## 【請求項3】

前記1つまたは複数のVTETを形成することが、

前記下部スペーサおよび前記複数のフィンの側壁に配置された酸化物層を形成することと、

前記酸化物層に配置されたダミー・ゲートを形成することと、

前記複数のフィンの上面より下方で前記ダミー・ゲートに凹部形成することと、

前記酸化物層の露出部分を除去することと、

前記ダミー・ゲートおよび前記複数のフィンに配置された上部スペーサを形成することとをさらに含む、請求項 2 に記載の方法。

【請求項 4】

前記 1 つまたは複数の VTFET を形成することが、

前記複数のフィンの上部に上部接合部を形成することと、

前記上部スペーサに配置された酸化物層を形成することと、

前記酸化物層に配置されたライナを形成することと、

前記ライナに配置された層間誘電体層を形成することとをさらに含む、請求項 3 に記載の方法。

【請求項 5】

前記 1 つまたは複数の VTFET を形成することが、

前記複数のフィンの各々の前記上部接合部の上面を露出させるように前記層間誘電体層に上部ソース / ドレイン開口部を形成することと、

前記上部接合部に配置された上部ソース / ドレイン領域を形成することと、

前記上部ソース / ドレイン領域に配置された上部ソース / ドレイン・コンタクト金属層を形成することと、

前記層間誘電体層の上面より下方で前記上部ソース / ドレイン・コンタクト金属層に凹部形成することと、

前記凹部形成された上部ソース / ドレイン・コンタクト金属層に配置された上部ソース / ドレイン SAC キャッピング層を形成することとを含む、請求項 4 に記載の方法。

【請求項 6】

前記 1 つまたは複数の VTFET を形成することが、

前記ダミー・ゲートに配置された前記上部スペーサの一部を露出させるように前記層間誘電体層にゲート開口部を形成することと、

前記層間誘電体層の前記ゲート開口部の側壁にライナを堆積させることと、

前記ダミー・ゲートの一部を露出させるように前記上部スペーサの前記露出部分をエッチングすることと、

前記ダミー・ゲートを除去することと、

前記 1 つまたは複数のフィンを囲むゲート誘電体を形成し、かつ前記ゲート誘電体を囲む金属ゲート導体を形成するように前記置換金属ゲート・プロセスを行うことと、

前記層間誘電体層の前記ゲート開口部の残りの部分に前記ゲート・コンタクト金属層を充填することと、

前記層間誘電体層の前記上面より下方で前記ゲート・コンタクト金属層に凹部形成することと、

前記凹部形成されたゲート・コンタクト金属層に配置された前記ゲート SAC キャッピング層を形成することとをさらに含む、請求項 5 に記載の方法。

【請求項 7】

前記 1 つまたは複数の VTFET を形成することが、

前記下部ソース / ドレイン領域の上面の一部を露出させるように前記層間誘電体層に下部ソース / ドレイン開口部を形成することと、

前記下部ソース / ドレイン領域の前記上面の前記露出部分に配置された前記下部ソース / ドレイン開口部に下部ソース / ドレイン・コンタクト金属層を充填することと、

前記層間誘電体層の前記上面より下方で前記下部ソース / ドレイン・コンタクト金属層に凹部形成することと、

前記凹部形成された下部ソース / ドレイン・コンタクト金属層に配置された下部ソース / ドレイン SAC キャッピング層を形成することとをさらに含む、請求項 6 に記載の方法。

【請求項 8】

10

20

30

40

50

前記 1 つまたは複数の V T F E T を形成することが、

前記層間誘電体層、前記上部ソース / ドレイン S A C キャッピング層、前記ゲート S A C キャッピング層、および前記下部ソース / ドレイン S A C キャッピング層に配置された追加のライナを形成すること、

前記追加のライナに配置された追加の層間誘電体を形成することと、

前記上部ソース / ドレイン・コンタクト金属層、前記ゲート・コンタクト金属層、および前記下部ソース / ドレイン・コンタクト金属層の上面の一部を露出させるように、前記追加のライナ、前記追加の層間誘電体、前記上部ソース / ドレイン S A C キャッピング層、前記ゲート S A C キャッピング層、および前記下部ソース / ドレイン S A C キャッピング層にビアを形成することと、

前記ビアに上部ソース / ドレイン・コンタクト、ゲート・コンタクト、および下部ソース / ドレイン・コンタクトを形成することとをさらに含む、請求項 7 に記載の方法。

#### 【請求項 9】

前記 1 つまたは複数の V T F E T を形成することが、

少なくとも 1 つのシャロー・トレンチ絶縁領域を、前記複数のフィンの第 1 のサブセットと前記複数のフィンの少なくとも第 2 のサブセットとの間で前記基板および前記下部ソース / ドレイン領域に形成することをさらに含み、

前記ダミー・ゲートに凹部形成することが、

前記複数のフィンの前記第 1 のサブセットを囲む前記ダミー・ゲートの第 1 の部分に第 1 の深さまで凹部形成することと、

前記複数のフィンの前記第 2 のサブセットを囲む前記ダミー・ゲートの第 2 の部分に前記第 1 の深さより大きい第 2 の深さまで凹部形成することとを含み、

前記複数のフィンの前記第 1 のサブセットが、第 1 のチャネル長さを有する V T F E T を形成し、

前記複数のフィンの前記第 2 のサブセットが、前記第 1 のチャネル長さより短い第 2 のチャネル長さを有する V T F E T を形成する、請求項 3 に記載の方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

本発明は、半導体構造を形成するための技法に関する。より詳細には、本発明は、縦型輸送電界効果トランジスタ ( V T F E T ) のための置換金属ゲート ( R M G ) ・プロセスの技法に関する。

##### 【背景技術】

##### 【0 0 0 2】

半導体および集積回路チップは、特にそのコストおよびサイズが減少し続けるにつれて、多くの製品において広く使用されるようになっている。構造的特徴のサイズを減少させること、または所与のチップ・サイズに合わせたより多くの構造的特徴を提供すること、あるいはその両方が引き続き求められている。一般的に、小型化により、低電力レベルかつ低コストで性能を高めることができる。現在の技術は、論理ゲート、電界効果トランジスタ ( F E T ) 、およびキャパシタなどのあるマイクロデバイスの原子レベルのスケーリングであるか、またはこれに近づいている。

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0 0 0 3】

本発明は、縦型輸送電界効果トランジスタのための置換金属ゲート・プロセスによる、半導体構造を形成する方法、半導体構造、および集積回路を提供する。

##### 【課題を解決するための手段】

##### 【0 0 0 4】

本発明の一実施形態において、半導体構造を形成する方法が、基板の上面に配置された複数のフィンを形成することと、 R M G プロセスを使用して複数のフィンから 1 つまたは

10

20

30

40

50

複数の VTFET を形成することを含む。VTFET のうちの所与の 1 つの少なくとも 1 つのフィンを囲むゲートが、ゲート・コンタクト金属層に配置されたゲート自己整合コンタクト (SAC) ・キャッピング層を含み、ゲート・コンタクト金属層が、少なくとも 1 つのフィンの端部に隣接して配置される。

【0005】

本発明の別の実施形態において、半導体構造が、基板と、基板の上面に配置された複数のフィンとを含み、複数のフィンが、RMG プロセスを使用して形成された 1 つまたは複数の VTFET のチャネルを含む。VTFET のうちの所与の 1 つが、複数のフィンのうちの少なくとも 1 つを囲むゲートを含み、所与の VTFET のゲートが、ゲート・コンタクト金属層に配置されたゲート SAC キャッピング層を含み、ゲート・コンタクト金属層が、少なくとも 1 つのフィンの端部に隣接して配置される。

10

【0006】

本発明の別の実施形態において、集積回路が、基板と基板の上面に配置された複数のフィンとを含む 1 つまたは複数の VTFET を含み、複数のフィンが、RMG プロセスを使用して形成された 1 つまたは複数の VTFET のチャネルを含む。VTFET のうちの所与の 1 つが、複数のフィンのうちの少なくとも 1 つを囲むゲートを含み、所与の VTFET のゲートが、ゲート・コンタクト金属層に配置されたゲート SAC キャッピング層を含み、ゲート・コンタクト金属層が、少なくとも 1 つのフィンの端部に隣接して配置される。

20

【図面の簡単な説明】

【0007】

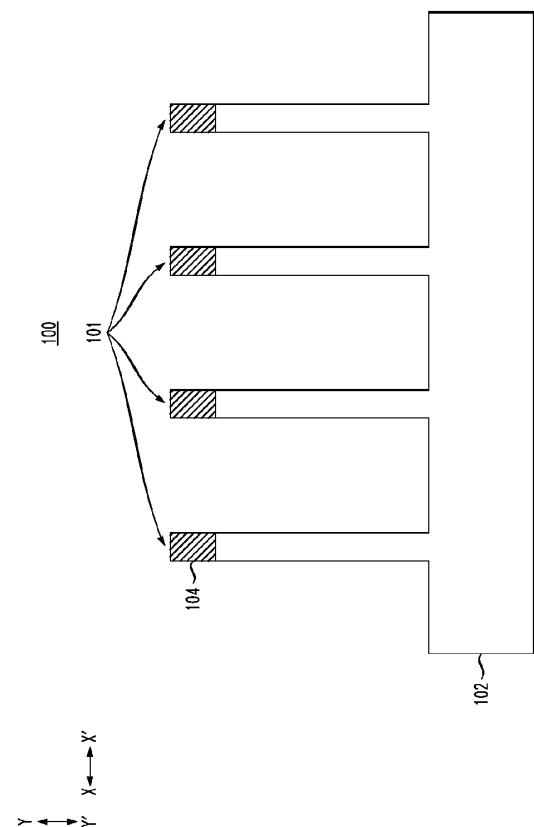

【図 1】本発明の一実施形態による、基板に配置された複数のフィンを含む半導体構造の側断面図である。

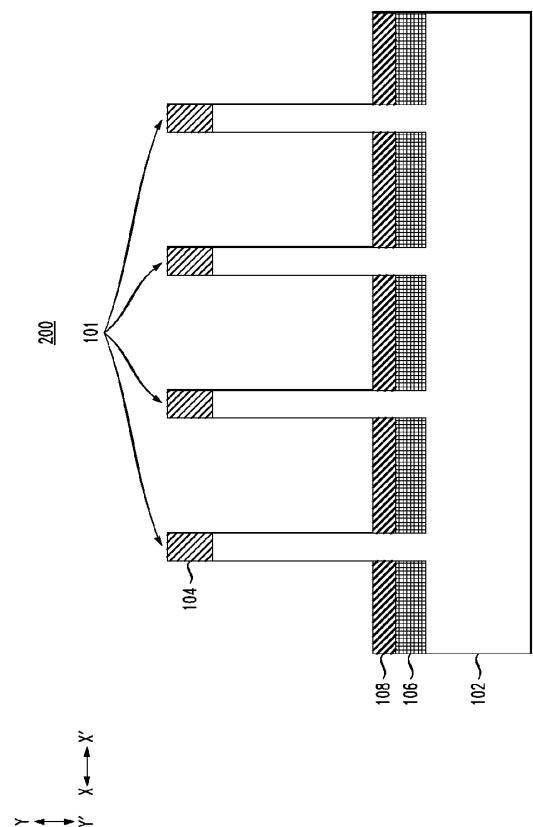

【図 2】本発明の一実施形態による、下部ソース / ドレイン領域および下部スペーサの形成後の、図 1 の半導体構造の側断面図である。

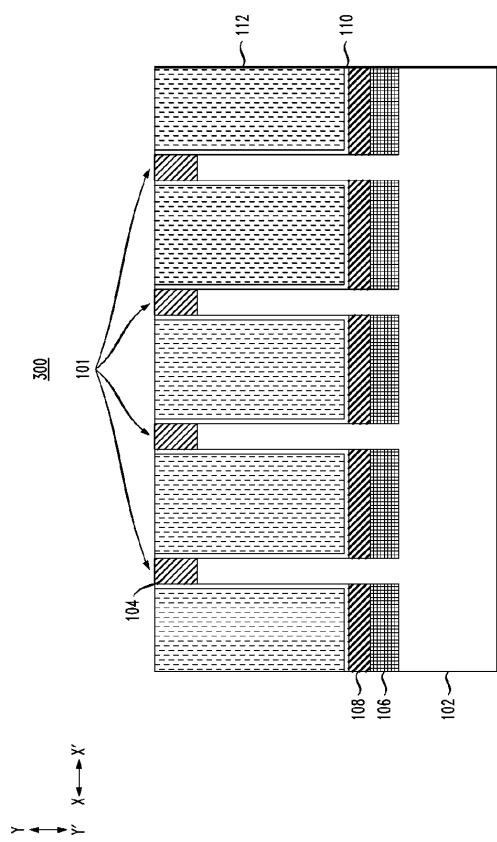

【図 3】本発明の一実施形態による、ダミー・ゲートの形成後の、図 2 の半導体構造の側断面図である。

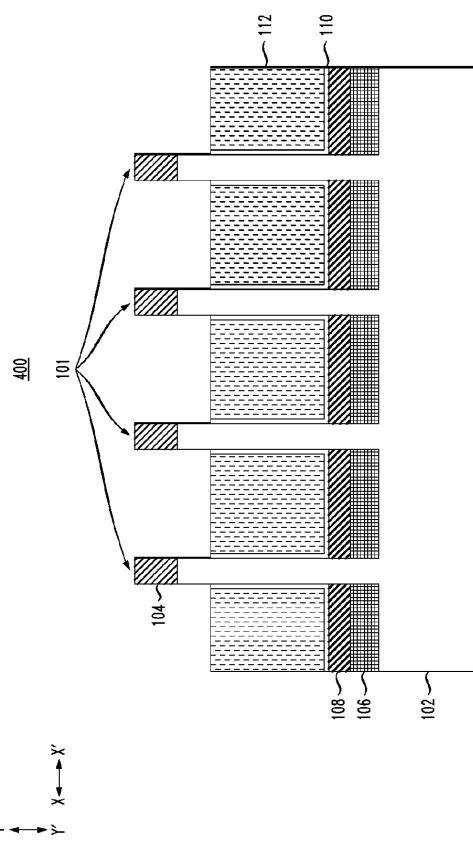

【図 4】本発明の一実施形態による、ダミー・ゲートの凹部形成後の、図 3 の半導体構造の側断面図である。

【図 5】本発明の一実施形態による、上部スペーサの形成後の、図 4 の半導体構造の側断面図である。

30

【図 6】本発明の一実施形態による、上部接合部の形成および活性化後の、図 5 の半導体構造の側断面図である。

【図 7】本発明の一実施形態による、絶縁層の充填後の、図 6 の半導体構造の側断面図である。

【図 8】本発明の一実施形態による、追加のスペーサおよび層間誘電体の形成後の、図 7 の半導体構造の側断面図である。

【図 9】本発明の一実施形態による、上部ソース / ドレイン・コンタクトの形成のために接合部の上部を露出させるように開口した後の、図 8 の半導体構造の側断面図である。

【図 10】本発明の一実施形態による、上部ソース / ドレインの形成後の、図 9 の半導体構造の側断面図である。

【図 11】本発明の一実施形態による、上部ソース / ドレイン領域上に金属層を充填した後の、図 10 の半導体構造の側断面図である。

【図 12】本発明の一実施形態による、金属層の凹部形成および上部ソース / ドレイン自己整合コンタクト・キャッピング層の形成後の、図 11 の半導体構造の側断面図である。

【図 13】本発明の一実施形態による、上部ソース / ドレイン自己整合コンタクト・キャッピング層の形成後の、図 11 の半導体構造の別の側断面図である。

【図 14】本発明の一実施形態による、ダミー・ゲートを開口するようにマスキングした後の、図 12 および図 13 の半導体構造の側断面図である。

【図 15】本発明の一実施形態による、ゲート開口部の側壁にライナを形成した後の、図 14 の半導体構造の側断面図である。

40

50

【図16】本発明の一実施形態による、ダミー・ゲートの除去後の、図15の半導体構造の側断面図である。

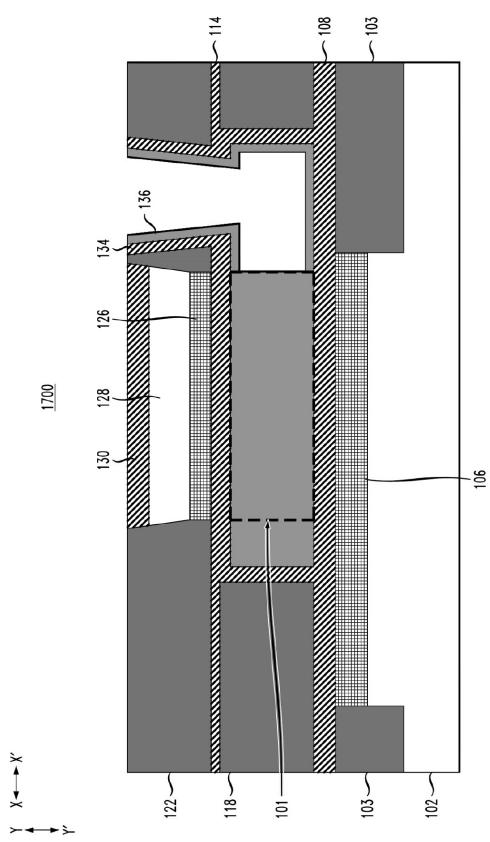

【図17】本発明の一実施形態による、置換金属ゲート・プロセス後の、図16の半導体構造の側断面図である。

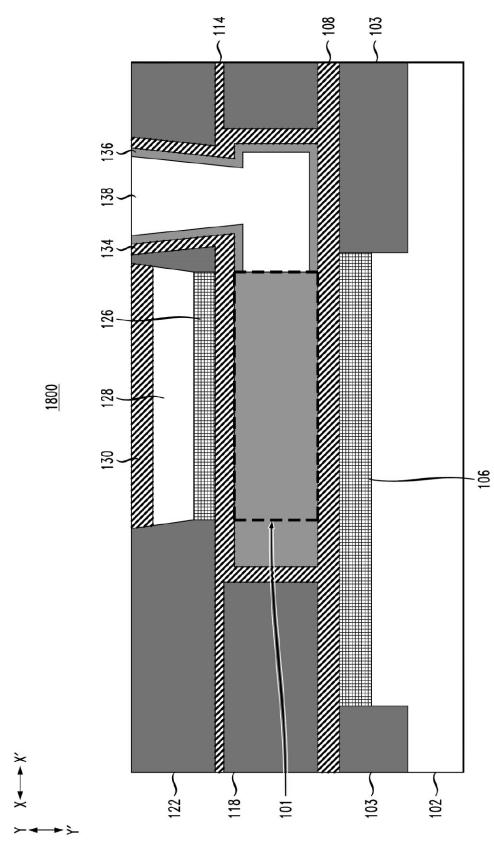

【図18】本発明の一実施形態による、ゲート開口部に金属を充填した後の、図17の半導体構造の側断面図である。

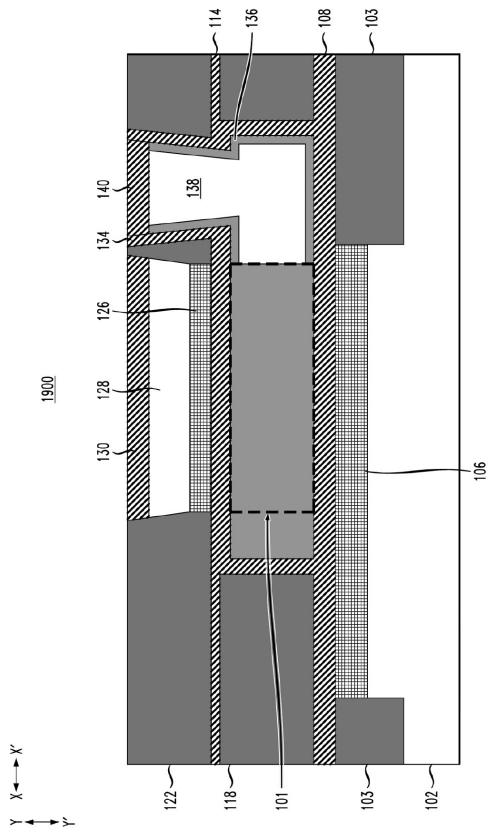

【図19】本発明の一実施形態による、ゲート開口部における金属の凹部形成およびゲート自己整合コンタクト・キャッピング層の形成後の、図18の半導体構造の側断面図である。

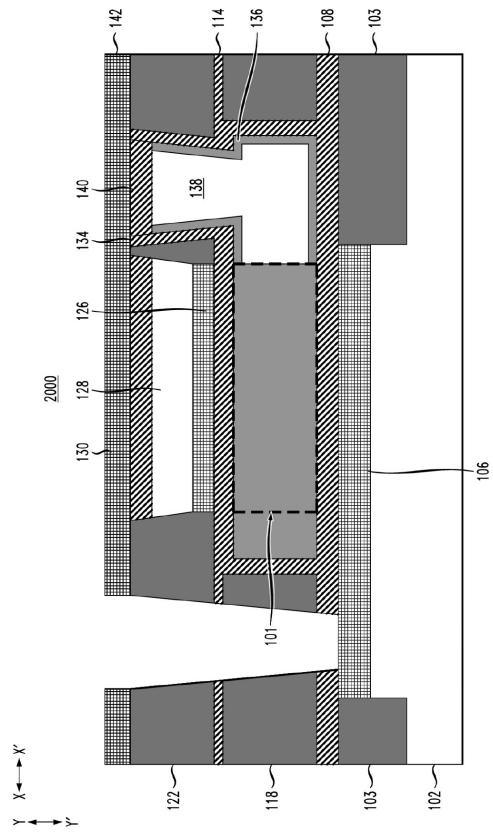

【図20】本発明の一実施形態による、下部ソース／ドレイン領域を開口するようにマスキングした後の、図19の半導体構造の側断面図である。 10

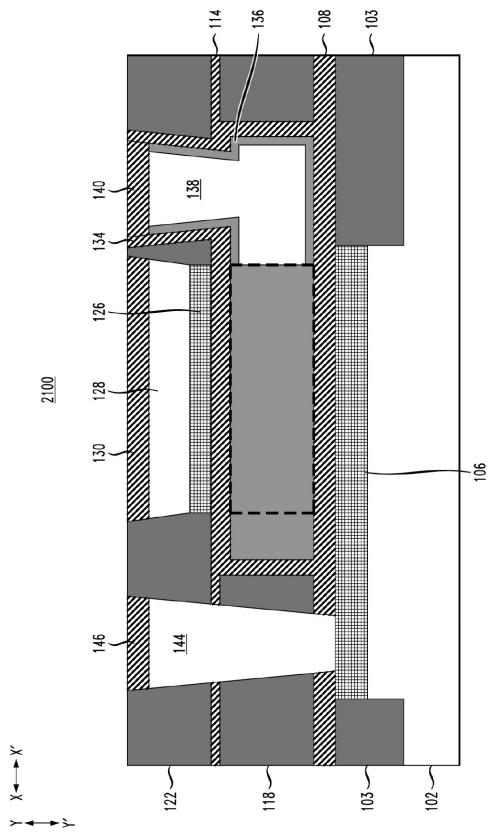

【図21】本発明の一実施形態による、下部ソース／ドレイン領域の開口部に金属を充填し、下部ソース／ドレイン自己整合コンタクト・キャッピング層を形成した後の、図20の半導体構造の側断面図である。

【図22】本発明の一実施形態による、ライナおよび層間誘電体の形成後の、図21の半導体構造の側断面図である。

【図23】本発明の一実施形態による、コンタクトにアクセスするためのピアを形成した後の、図22の半導体構造の側断面図である。

【図24】本発明の一実施形態による、図23の半導体構造の上面図である。

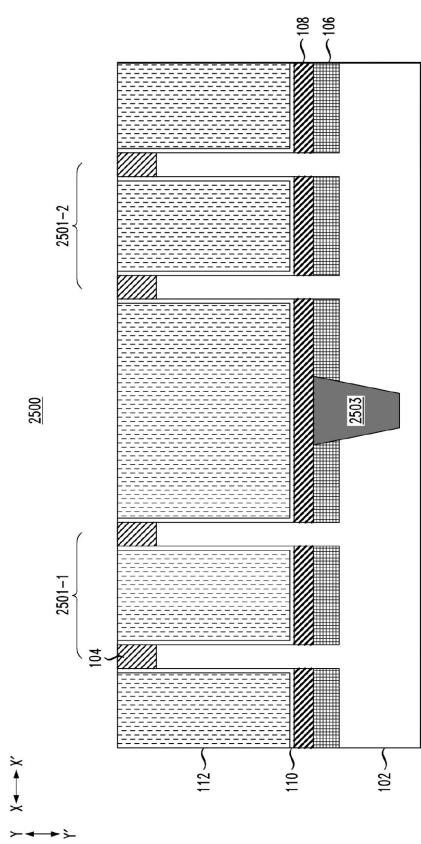

【図25】本発明の一実施形態による、長チャネル領域および短チャネル領域にフィンを含む半導体構造の側断面図である。 20

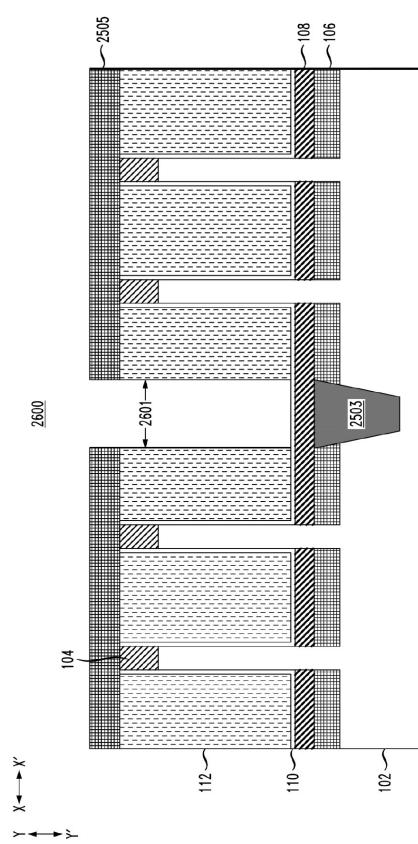

【図26】本発明の一実施形態による、ダミー・ゲートのパターニング後の、図25の半導体構造の側断面図である。

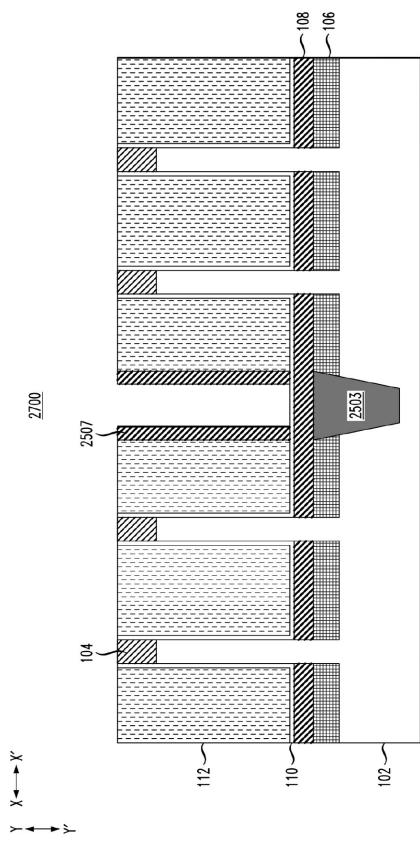

【図27】本発明の一実施形態による、ライナの形成後の、図26の半導体構造の側断面図である。

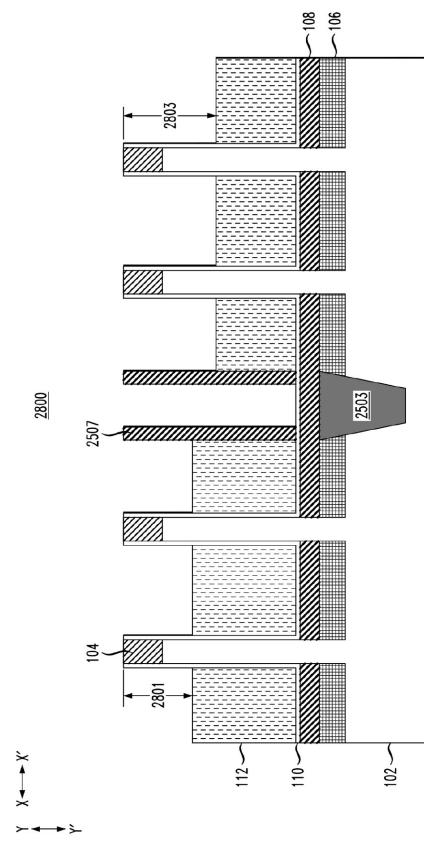

【図28】本発明の一実施形態による、ダミー・ゲートの凹部形成後の、図27の半導体構造の側断面図である。

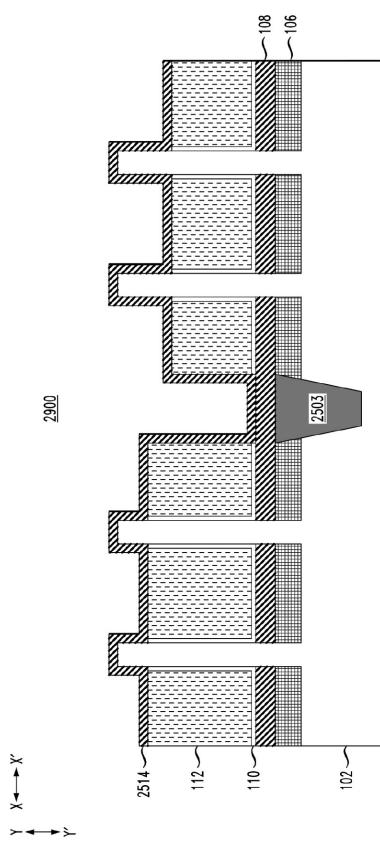

【図29】本発明の一実施形態による、上部スペーサの形成後の、図28の半導体構造の側断面図である。

【図30】本発明の一実施形態による、上部接合部の形成後の、図29の半導体構造の側断面図である。 30

【図31】本発明の一実施形態による、絶縁層の充填ならびに追加のスペーサおよび層間誘電体の形成後の、図30の半導体構造の側断面図である。

【図32】本発明の一実施形態による、上部ソース／ドレイン・コンタクトの形成のために接合部の上部を露出させるように開口した後の、図31の半導体構造の側断面図である。

【図33】本発明の一実施形態による、上部ソース／ドレイン領域の形成および金属層の充填後の、図32の半導体構造の側断面図である。

【図34】本発明の一実施形態による、金属層の凹部形成および上部ソース／ドレイン領域自己整合コンタクト・キャッピング層の形成後の、図33の半導体構造の側断面図である。

【図35】本発明の一実施形態による、共有ダミー・ゲートを含む半導体構造の側断面図である。 40

【図36】本発明の一実施形態による、共有ダミー・ゲートの開口後の、図35の半導体構造の側断面図である。

【図37】本発明の一実施形態による、ライナの形成後の、図36の半導体構造の側断面図である。

【図38】本発明の一実施形態による、共有ダミー・ゲートの除去後の、図37の半導体構造の側断面図である。

【図39】本発明の一実施形態による、p型電界効果トランジスタの仕事関数金属の形成後の、図38の半導体構造の側断面図である。 50

【図40】本発明の一実施形態による、p型仕事関数金属のパターニング後の、図39の半導体構造の側断面図である。

【図41】本発明の一実施形態による、n型電界効果トランジスタの仕事関数金属の形成後の、図40の半導体構造の側断面図である。

【図42】本発明の一実施形態による、金属の充填後の、図41の半導体構造の側断面図である。

【図43】本発明の一実施形態による、金属の凹部形成およびゲート自己整合コンタクト・キャッピング層の形成後の、図42の半導体構造の側断面図である。

【図44】本発明の一実施形態による、コンタクトにアクセスするためのビアの形成後の、図43の半導体構造の側断面図である。

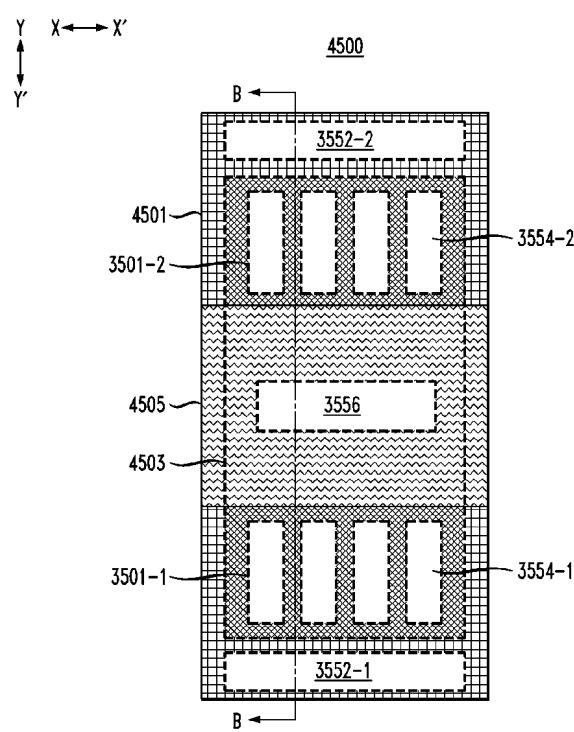

【図45】発明の一実施形態による、図44の半導体構造の上面図である。

【発明を実施するための形態】

【0008】

本明細書で、本発明の例示的な実施形態について、縦型輸送電界効果トランジスタのための置換金属ゲート・プロセスの例示的な方法、ならびにそのような方法を使用して形成された例示的な装置、システム、およびデバイスの文脈で説明する。しかしながら、本発明の実施形態は例示的な方法、装置、システム、およびデバイスに限定されるものではなく、他の適切な方法、装置、システム、およびデバイスにより広く適用可能であることを理解されたい。

【0009】

電界効果トランジスタ(FET)は、ソース、ゲート、およびドレインを有し、ソースおよびドレイン間に延びるチャネルに沿ったキャリア(電子または正孔)の流れに応じた動作を有するトランジスタである。ソースおよびドレイン間のチャネルを流れる電流は、ゲート下の横電界によって制御され得る。

【0010】

FETは、スイッチング、增幅、フィルタリング、および他のタスクに広く使用されている。FETは、金属酸化膜(MOS)半導体FET(MOSFET)を含む。n型トランジスタ(NFET)およびp型トランジスタ(PFET)の両方を使用して論理回路および他の回路を作製する、相補型MOS(CMOS)デバイスが広く使用されている。FETのソースおよびドレイン領域は、通常、ゲートがチャネル上方に形成されている状態で、チャネルの両側における半導体本体の目標領域にドーパントを添加することによって形成される。ゲートは、チャネル上のゲート誘電体とゲート誘電体上のゲート導体とを含む。ゲート誘電体は絶縁体材料であり、ゲート導体に電圧が加えられたときに大きい漏れ電流がチャネルに流入することを防ぐとともに、加えられたゲート電圧がチャネルに横電界を生じさせることができるようにする。

【0011】

集積回路デバイスの高い密度および高い性能の需要が増すにつれて、ゲート長さの縮小およびデバイスの他のサイズ減少またはスケーリングを含む、新しい構造的特徴および設計的特徴の開発が必要になる。しかしながら、継続されているスケーリングは、従来の作製技法の限界に達している。

【0012】

縦型FETプロセス・フローは、処理時にhigh-k金属ゲート(HKMG)モジュールが先に形成されるため、上部ソース/ドレインのエピタキシャル成長およびドーパント活性化アニール・プロセスなどの下流処理ステップのためのサーマル・バジェットに厳しい制約を有する。チャネル長さ(Lgate)が金属ゲートの凹部形成処理に大きく依存するため、Lgateのチップ変動が大きくなる。上部ソース/ドレイン・モジュールの高温プロセス(例えば、550°C超)により、閾値電圧(Vt)変化、反転厚さ(Tinv)の増加、およびチャネル内への酸素および金属の拡散による漏れ電流メトリック(Toxgl)の低下が生じる。したがって、縦型輸送FET(VTFET)のための置換金属ゲート(RMG)・プロセス・フローが必要である。

10

20

30

40

50

## 【0013】

本発明の実施形態は、RMGプロセスを使用してVTFETデバイスを形成し、ゲート・スタックについてのサーマル・バジェットの制約を取り除くための技法を提供する。本明細書に開示のRMGプロセスは、正確なLgateの定義および自己整合上部接合部を提供する。RMGプロセスを使用してVTFETを形成する技法を提供することに加えて、実施形態により、複数のチャネル長さを有するVTFETの形成、ゲートおよびソース/ドレイン領域間の短絡を避けるための自己整合ゲート・キャップの形成、および無視できるほど小さいn/p境界ずれを有するCMOSパターニングも可能になる。

## 【0014】

以下で、図1～図45に関して、RMGプロセスを使用して、複数のチャネル長さを有するVTFETおよびCMOS VTFETデバイスを含むVTFETを形成するための例示的なプロセスについて説明する。

10

## 【0015】

図1は、複数のフィン101が形成された基板102を含む、半導体構造の側断面図100である。図示したように、各フィン101の上部がハード・マスク104で覆われている。フィン101は、側壁画像転写(SIT)、またはリソグラフィおよび反応性イオン・エッチング(RIE)などを含むエッチングなどの他の適切な技法を使用して形成することができる。各フィン101は、5～10ナノメートル(nm)の幅または水平方向厚さ(方向X-X')を有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の幅を使用してもよい。各フィン101は、30nm～150nmの高さまたは垂直方向厚さ(方向Y-Y')を有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の高さを使用してもよい。隣接するフィン101同士の間隔は、20nm～100nmであってよいが、特定の適用の要求に応じて、他の間隔を有してもよい。

20

## 【0016】

本発明の一部の実施形態において、基板102はシリコン(Si)から形成された半導体基板を含むが、他の適切な材料を使用してもよい。例えば、基板102は任意の適切な基板構造、例えば、バルク半導体を含むことができる。基板102はシリコン含有材料を含むことができる。基板102に適したSi含有材料の例として、Si、シリコンゲルマニウム(SiGe)、シリコンゲルマニウム炭化物(SiGeC)、炭化ケイ素(SiC)、およびそれらの多層が挙げられるが、これらに限定されない。シリコンは、ウエハの作製において主に使用される半導体材料であるが、ゲルマニウム(Ge)、ヒ化ガリウム(GaAs)、窒化ガリウム(GaN)、SiGe、テルル化カドミウム(CdTe)、セレン化亜鉛(ZnSe)など(ただし、これらに限定されない)の代替の半導体材料を追加の層として使用してもよい。フィン101は、上記のように基板102をパターニングすることによって形成されるため、基板102と同一の材料から形成することができる。

30

## 【0017】

基板102は、いくつかのフィン101またはフィン101の上に形成される他の特徴に基づいて、要求に応じて選択された幅または水平方向厚さ(X-X')を有することができる。基板102は、20nm～500nmの高さまたは垂直方向厚さ(方向Y-Y')を有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の高さを使用してもよい。

40

## 【0018】

最初にハード・マスク104を基板全体の上面に形成することができ、次にSITまたは他の適切な技法を使用してパターニングを行い、フィン101が、パターンニングされたハード・マスク104により露出された基板のエッチング部分によって形成される。ハード・マスク104を窒化ケイ素(SiN)から形成することができるが、酸化ケイ素(SiOx)、二酸化ケイ素(SiO<sub>2</sub>)、および酸窒化ケイ素(SiON)などの他の適切な材料を使用してもよい。ハード・マスク104は、20nm～100nmの高さまたは垂直方向厚さ(方向Y-Y')を有することができるが、特定の適用の要求に応じて、こ

50

の範囲より大きいまたは小さい他の高さを使用してもよい。

【0019】

図2は、フィン101を囲む基板102の上面に下部ソース／ドレイン領域106を形成し、フィン101を囲む下部ソース／ドレイン領域106上に下部スペーサ108を形成した後の、図1の半導体構造の側断面図200である。

【0020】

下部ソース／ドレイン領域106は、イオン注入、気相ドーピング、プラズマ・ドーピング、プラズマ浸漬イオン注入、クラスタ・ドーピング、インフュージョン・ドーピング、液相ドーピング、固相ドーピングなどを使用して、適切にドープすることができる。n型ドーパントは、リン(P)、ヒ素(As)、およびアンチモン(Sb)の群から選択することができ、p型ドーパントは、ホウ素(B)、フッ化ホウ素(BF<sub>2</sub>)、ガリウム(Ga)、インジウム(In)、およびタリウム(Tl)の群から選択することができる。下部ソース／ドレイン領域106は、エピタキシャル成長プロセスによって形成することができる。一部の実施形態において、エピタキシ・プロセスは、現場ドーピング(エピタキシ中にドーパントがエピタキシ材料に取り込まれる)を含む。エピタキシャル材料は、気体前駆体または液体前駆体から成長させることができる。エピタキシャル材料は、気相エピタキシ(VPE)、分子線エピタキシ(MBE)、液相エピタキシ(LPE)、急速熱化学気相成長(RTCVD)、有機金属化学気相成長(MOCVD)、超高真空化学気相成長(UHVCVD)、低圧化学気相成長(LPCVD)、制限反応処理(CVD(LRPCVD))、または他の適切なプロセスを使用して成長させることができる。エピタキシャルシリコン、シリコンゲルマニウム(SiGe)、ゲルマニウム(Ge)、または炭素ドープシリコン(Si:C)、あるいはそれらの組合せは、トランジスタの型に応じてn型ドーパント(例えば、リンもしくはヒ素)またはp型ドーパント(例えば、ホウ素もしくはガリウム)などのドーパントを添加することによって、堆積中にドープ(現場ドープ)することができる。ソース／ドレイン中のドーパント濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$ ～ $3 \times 10^{21} \text{ cm}^{-3}$ 、または好ましくは $2 \times 10^{20} \text{ cm}^{-3}$ ～ $3 \times 10^{21} \text{ cm}^{-3}$ であってよい。

【0021】

下部ソース／ドレイン領域106は、 $10 \text{ nm}$ ～ $50 \text{ nm}$ の高さまたは垂直方向厚さ(方向Y-Y')を有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の高さを使用してもよい。

【0022】

下部スペーサ108は、非コンフォーマル堆積およびエッチバック処理(例えば、物理気相成長(PVD)、高密度プラズマ(HDP)堆積など)を使用して下部ソース／ドレイン領域106上に形成される。下部スペーサ108は、SiO<sub>2</sub>、SiN、炭化ケイ素酸化物(SiCO)、炭化ケイ素ホウ素窒化物(SiBCN)などから形成することができるが、他の適切な材料を使用してもよい。下部スペーサ108は、 $3 \text{ nm}$ ～ $10 \text{ nm}$ の高さまたは垂直方向厚さ(方向Y-Y')を有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の高さを使用してもよい。

【0023】

図3は、ダミー・ゲートの形成後の、図2の半導体構造の側断面図300である。ダミー・ゲートの形成は、下部スペーサ108の上面ならびにフィン101およびハード・マスク104の側壁に酸化物110を形成することを含む。酸化物110は、原子層堆積(ALD)または化学気相成長(CVD)などのコンフォーマル堆積プロセスによって形成することができる。酸化物110はSiO<sub>2</sub>、SiONなどから形成することができるが、他の適切な材料を使用してもよい。酸化物110は $2 \text{ nm}$ ～ $6 \text{ nm}$ の均一な厚さを有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の厚さを使用してもよい。

【0024】

ダミー・ゲート112は、CVDまたはALDなどの処理を使用して酸化物110上に

10

20

30

40

50

形成される。ダミー・ゲート 112 は、アモルファスシリコン (a-Si)、アモルファスシリコンゲルマニウム (a-SiGe)、SiO<sub>2</sub>、酸化チタン (TiO<sub>2</sub>)、または別の適切な材料から形成することができる。

#### 【0025】

図4は、ダミー・ゲート 112 に凹部形成し、フィン 101 およびフィン 101 に配置されたハード・マスク 104 の側壁における酸化物 110 の露出部分を除去した後の、図3の半導体構造の側断面図 400 である。ダミー・ゲート 112 および酸化物 110 には、ウェット・エッティング、RIEなどの処理を使用して凹部形成することができる。ダミー・ゲート 112 および酸化物 110 には、5 nm ~ 20 nm の深さ (方向 Y-Y') に凹部形成することができるが、ハード・マスク 104 下方のフィン 101 の側壁の少なくとも一部が露出していれば、他の深さを使用してもよい。

10

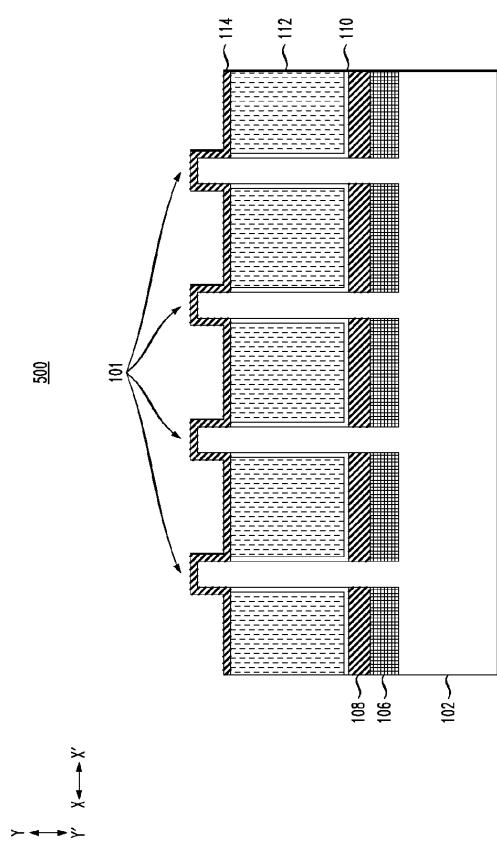

#### 【0026】

図5は、ハード・マスク 104 の除去および上部スペーサ 114 の形成後の、図4の半導体構造の側断面図 500 である。ハード・マスク 104 は、ドライ・エッティング処理またはウェット・エッティング処理を選択的に使用して除去することができる。上部スペーサ 114 は、ALD 処理または CVD 処理などのコンフォーマル堆積を使用して形成することができる。上部スペーサ 114 は、SiN、SiO<sub>2</sub> または SiON、SiOC、SiBCN などの別の適切な材料から形成することができる。上部スペーサ 114 は、3 nm ~ 10 nm の均一な厚さを有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の厚さを使用してもよい。

20

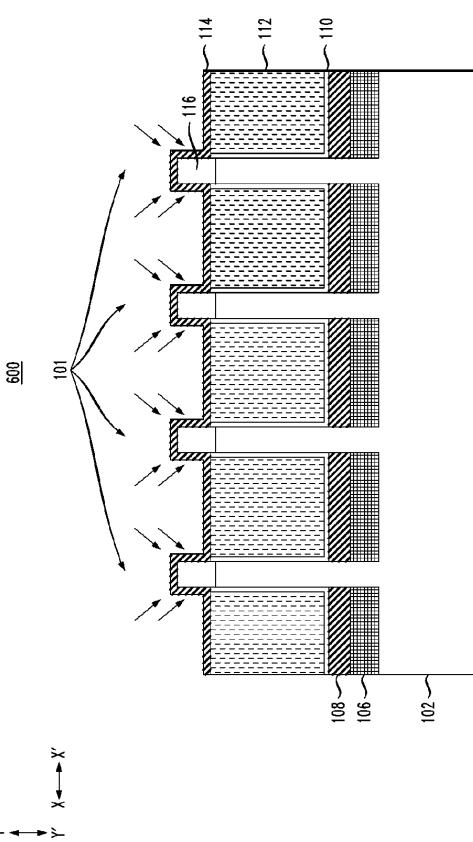

#### 【0027】

図6は、上部接合部 116 の形成および活性化後の、図5の半導体構造の側断面図 600 である。イオン注入、プラズマ・ドーピング、または別の適切なプロセスを使用して、フィン 101 の上部に上部接合部 116 (例えば、高濃度ドープ領域) を形成する。上部接合部 116 は、リン (P)、ヒ素 (As)、およびアンチモン (Sb) の群から選択された n 型ドーパントと、ホウ素 (B)、フッ化ホウ素 (BF<sub>2</sub>)、ガリウム (Ga)、インジウム (In)、およびタリウム (Tl) の群から選択された p 型ドーパントとを含むドーパントを使用することができる。上部接合部 116 の高さは、上部スペーサ 114 の下面より下方のフィンの領域に延びる。上部接合部 116 は、5 nm ~ 20 nm の高さまたは垂直方向厚さ (方向 Y-Y') を有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の高さを使用してもよい。

30

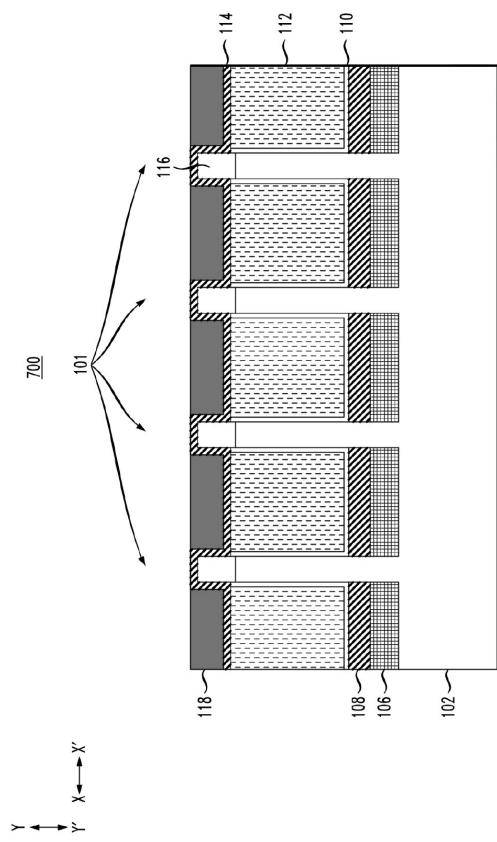

#### 【0028】

図7は、絶縁層または層間誘電体 (ILD) 層 118 の充填後の、図6の半導体構造の側断面図 700 である。絶縁層 118 は、SiO<sub>2</sub>、または SiOC、SiON などの別の適切な材料から形成することができる。絶縁層 118 は、絶縁材料を充填した後に、化学機械研磨または平坦化 (CMP) を使用して上部スペーサ 114 の上面まで平坦化することによって形成することができる。

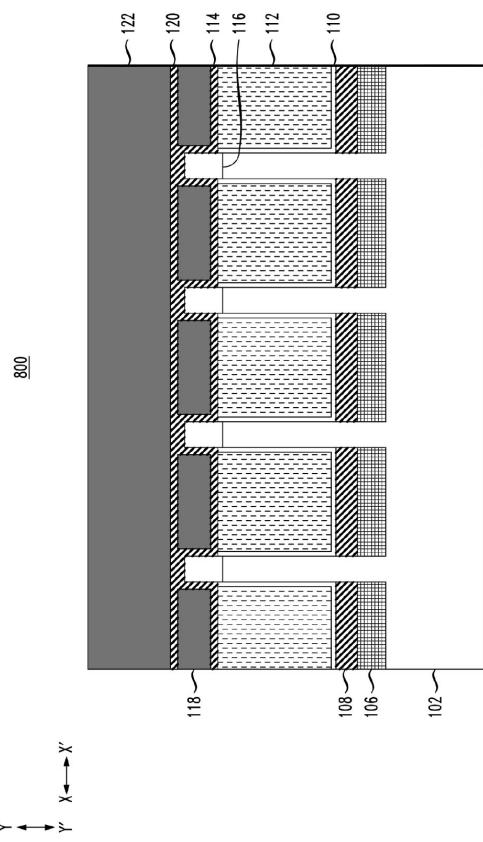

#### 【0029】

図8は、スペーサ 120 および ILD 層 122 の形成後の、図7の半導体構造の側断面図 800 である。スペーサ 120 は SiN から形成することができるが、SiO<sub>2</sub>、SiON、SiBCN、SiCO などの他の適切な材料を使用してもよい。スペーサ 120 は、5 nm ~ 15 nm の高さまたは垂直方向厚さ (方向 Y-Y') を有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の高さを使用してもよい。スペーサ 120 は、ALD または CVD などのコンフォーマル堆積処理を使用して形成することができる。

40

#### 【0030】

ILD 122 は SiO<sub>2</sub> から形成することができるが、SiON、SiCO などの他の適切な材料を使用してもよい。ILD 122 は、CVD 処理または ALD 処理を使用して形成することができる。ILD 122 は、30 nm ~ 150 nm の高さまたは垂直方向厚さ (方向 Y-Y') を有することができるが、特定の適用の要求に応じて、この範囲より大

50

きいまたは小さい他の高さを使用してもよい。

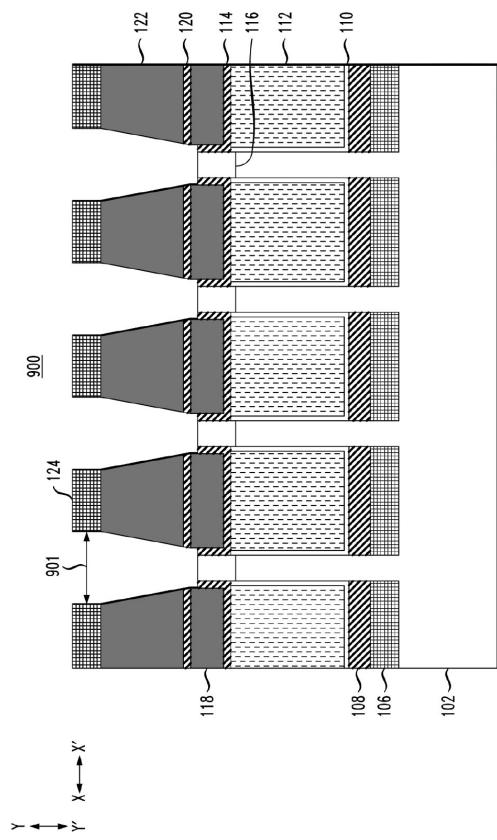

【0031】

図9は、上部ソース／ドレイン・コンタクトの形成のために接合部116の上部を露出させるように開口した後の、図8の半導体構造の側断面図900である。マスク層124が、リソグラフィおよびエッチングまたは他の適切な技法を使用して、ILD122の上面にパターニングされる。マスク層124は、有機材料、 $\text{SiO}_2$ 、酸化チタン( $\text{TiO}_x$ )の適切な組合せから形成することができるが、他の適切な材料を使用してもよい。マスク層124は、30nm～150nmの高さまたは垂直方向厚さ(方向Y-Y')を有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の高さを使用してもよい。

10

【0032】

マスク層124は、フィン101の上部より上方に開口部を設けるようにパターニングされる。フィン101上方の開口部の上部は、フィン101よりも幅広で、例えば20nm～80nmの幅901を有する。この幅は、フィン101の上面からの距離が短くなるにつれて、フィン101の幅に略一致する幅まで減少する。ILD122の開口部は、方向性RIEまたは他の適切な処理によって形成することができる。

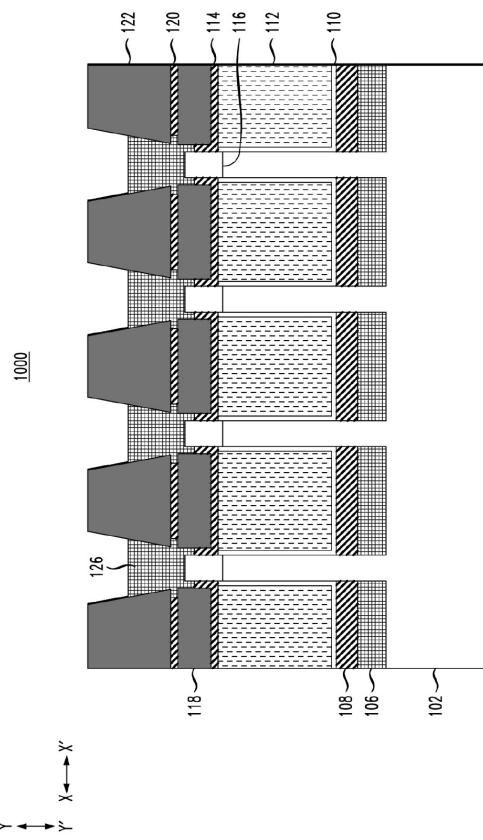

【0033】

図10は、上部ソース／ドレインの形成後の、図9の半導体構造の側断面図1000である。マスク層124は、プラズマ灰化／除去などの処理を使用して除去される。エピタキシャル成長を助けるために、場合により、スペーサ114、120の材料の横方向エッチングを行ってもよい。任意選択の横方向エッチング後、上部ソース／ドレイン領域126を、接合部116(および、スペーサ114、120の任意選択の横方向エッチングによって露出した領域)上でエピタキシャル成長させる。上部ソース／ドレイン領域126は、10nm～50nmの高さまたは垂直方向厚さ(方向Y-Y')を有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の高さを使用してもよい。上部ソース／ドレイン領域126は、下部ソース／ドレイン領域106と同様の材料から形成することができる。

20

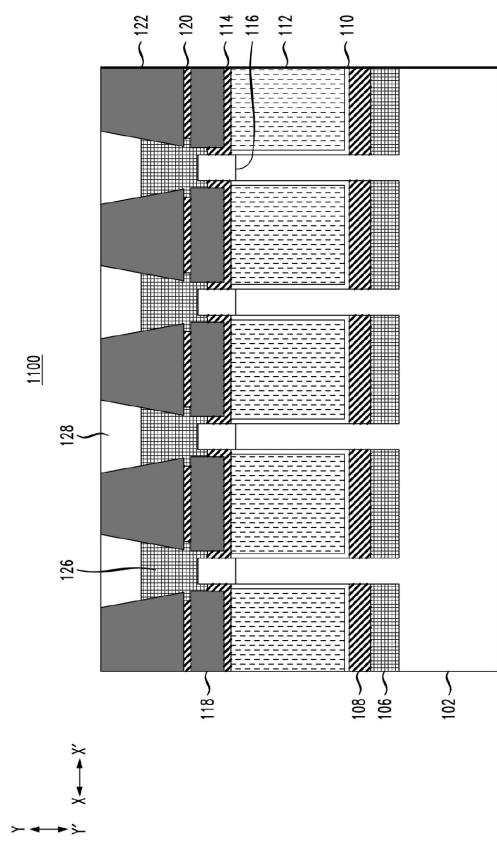

【0034】

図11は、金属を充填して、上部ソース／ドレイン領域126上に金属層128を形成した後の、図10の半導体構造の側断面図1100である。上部ソース／ドレイン・コンタクト金属層とも呼ばれる金属層128は、タングステン(W)から形成することができるが、チタン(Ti)、コバルト(Co)などの他の適切な材料を使用してもよい。金属層128は、金属材料を充填した後に、CMPまたは別の適切な技法を使用して、金属層128の上面がILD122の上面と略同一平面になるように平坦化することによって形成することができる。

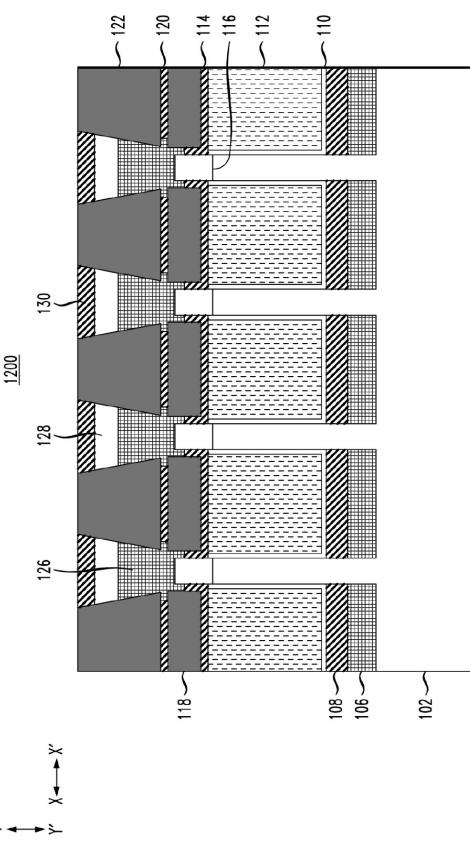

30

【0035】

図12は、金属層128に凹部形成し、上部ソース／ドレインSACキャッピング層とも呼ばれる自己整合コンタクト(SAC)・キャッピング層130を金属層128の上面に形成した後の、図11の半導体構造の側断面図1200である。金属層128には、ウエット・エッチング・プロセスまたはドライ・エッチング・プロセスを使用して凹部形成することができる。SACキャッピング層130は、ALD処理またはCVD処理を使用して形成することができる。金属層128には、5nm～20nmの深さまで凹部形成することができるが、特定の適用の要求に応じて、この範囲外の他の深さを使用してもよい。SACキャッピング層130は、SACキャッピング層130の上面がILD122の上面に一致するように、金属層128に凹部形成する深さに一致する高さまたは厚さ(方向Y-Y')を有することができる。

40

【0036】

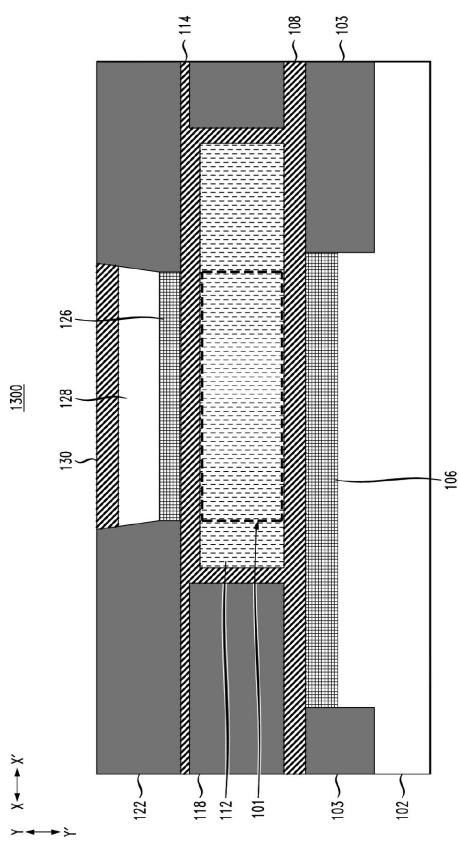

図13は、SACキャッピング層130の形成後の、図11の半導体構造の別の側断面図1300である。図12の側断面図1200(および図1～図11の側断面図)はフィン101に垂直に取っているが、側断面図1300はフィン101に平行に取っている。

50

フィン 101 のうちの 1 つが側断面図 1300 に破線の輪郭で示され、この図でフィン 101 がダミー・ゲート 112 の「後方」にあることを示している。側断面図 1300 は、シャロー・トレーニング (STI) 領域 103 が図示したように形成されている様子をさらに示す。STI 領域 103 は、絶縁層 118 および ILD 122 と同様の材料から形成することができる。

#### 【0037】

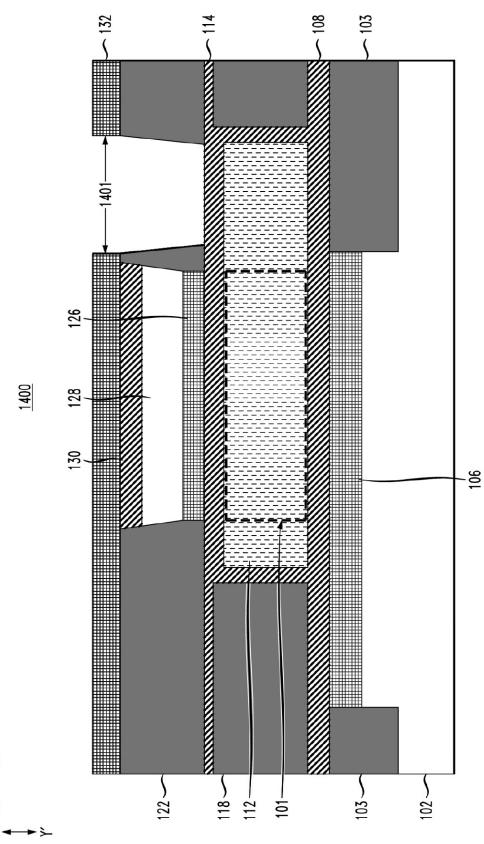

図 14 は、ダミー・ゲート 112 を開口するようにマスキングした後の、図 12 および図 13 の半導体構造の側断面図 1400 である。側断面図 1400 は、側断面図 1300 と同様に、フィン 101 に平行に取っている。マスク層 132 が、ILD 122 および SAC キャッピング層 130 の上面にパターニングされる。マスク層 132 は、マスク層 124 と同様の材料および同様のサイズを使用して形成することができる。SAC キャッピング層 130 により、上部ソース / ドレイン領域 126 およびゲート間の短絡が確実になくなる。上部ソース / ドレイン領域 126 上の SAC キャッピング層 130 は、エピタキシャル層が閉じ込められることによって同化しないため、マスク層 132 は、図示したように、ダミー・ゲート 112 を開口するようにパターニングすることができる。ダミー・ゲート 112 を露出させるための開口部は、75 nm、より一般的には 30 nm ~ 100 nm の幅 1401 を有することができるが、特定の適用の要求に応じて、この範囲外の他の幅を使用してもよい。

#### 【0038】

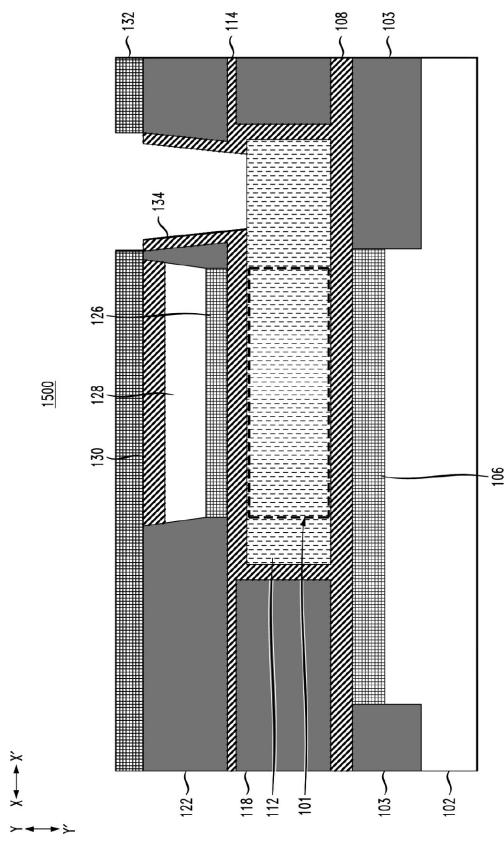

図 15 は、ゲート開口部の側壁にライナ 134 を堆積させ、ゲート開口部においてダミー・ゲート 112 の上面を露出させるように方向性エッチングした後の、図 14 の半導体構造の側断面図 1500 である。ライナ 134 は、下部スペーサ 108 および上部スペーサ 114 と同様の材料（例えば、SiN）から形成することができるが、他の適切な材料を使用してもよい。ライナ 134 は、3 nm ~ 10 nm の厚さを有することができるが、特定の適用の要求に応じて、この範囲外の他の厚さを使用してもよい。ダミー・ゲート 112 の上面を露出させる方向性エッチングは、方向性 RIE であってよい。

#### 【0039】

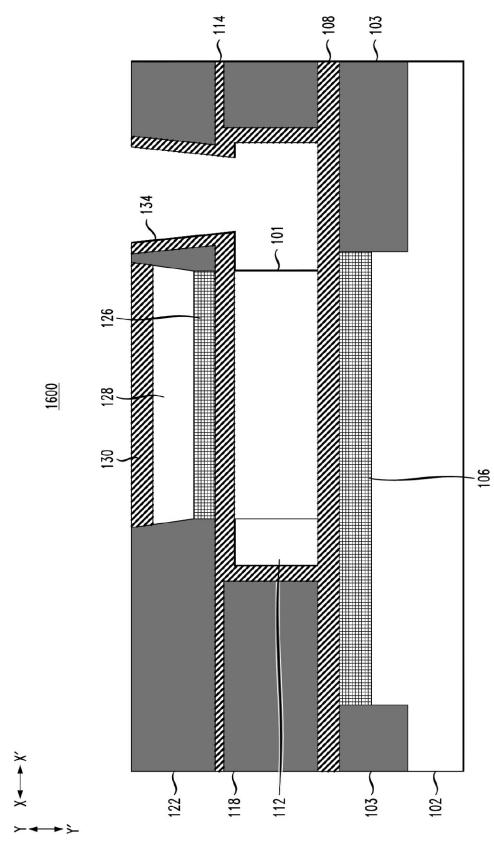

図 16 は、ダミー・ゲート 112 の除去後の、図 15 の半導体構造の側断面図 1600 である。マスク層 132 は、ダミー・ゲート 112 の除去より前に除去される。ダミー・ゲート 112 は、気相エッチング、ウェット・エッチング、または他の適切な処理を使用して酸化物層 110 上のダミー・ゲート 112 を選択的に除去することによって除去することができる。酸化物層 110 は、ダミー・ゲート 112 の除去中にフィン 101 を保護する。フィン 101 を覆う酸化物層 110 は、さらに詳細に後述する置換金属ゲート (RMG) ・プロセスにより前に希釈 HF エッチングなどを使用して除去される。ダミー・ゲート 112 とフィン 101 を覆う酸化物層 110 とを除去した後、ダミー・ゲート 112 後方のフィン 101 が図示したように見られる。

#### 【0040】

図 17 は、RMG プロセス後の、図 16 の半導体構造の側断面図 1700 である。RMG プロセスでは、フィン 101 を囲むゲート誘電体（図示せず）が形成された後に、ゲート導体 136 が形成される。

#### 【0041】

ゲート誘電体は、 $h_i g h-k$  誘電材料から形成することができるが、他の適切な材料を使用してもよい。 $h_i g h-k$  材料の例としては、酸化ハフニウム ( $HfO_2$ )、ハフニウムシリコン酸化物 ( $Hf-Si-O$ )、ハフニウムシリコン酸窒化物 ( $HfSiON$ )、酸化ランタン ( $La_2O_3$ )、ランタンアルミニウム酸化物 ( $LaAlO_3$ )、酸化ジルコニウム ( $ZrO_2$ )、ジルコニウムシリコン酸化物、ジルコニウムシリコン酸窒化物、酸化タンタル ( $Ta_2O_5$ )、酸化チタン ( $TiO_2$ )、バリウムストロンチウムチタン酸化物、バリウムチタン酸化物、ストロンチウムチタン酸化物、酸化イットリウム ( $Y_2O_3$ )、酸化アルミニウム ( $Al_2O_3$ )、鉛スカンジウムタンタル酸化物、および鉛亜鉛ニオブ酸塩などの金属酸化物を含むが、これらに限定されない。 $h_i g h-k$  材料は、ラ

10

20

30

40

50

ンタン (L a) 、アルミニウム (A l) 、およびマグネシウム (M g) などのドーパントをさらに含むことができる。ゲート誘電体は、2 nm ~ 5 nm の均一な厚さを有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の厚さを使用してもよい。

#### 【0042】

ゲート導体 136 は、金属（例えば、タングステン (W) 、チタン (T i) 、タンタル (T a) 、ルテニウム (R u) 、ジルコニウム (Z r) 、コバルト (C o) 、銅 (C u) 、アルミニウム (A l) 、鉛 (P b) 、白金 (P t) 、スズ (S n) 、銀 (A g) 、金 (A u) など）、導電性金属化合物材料（例えば、窒化タンタル (T a N) 、窒化チタン (T i N) 、炭化タンタル (T a C x) 、炭化チタン (T i C) 、チタンアルミニウム炭化物、ケイ化タングステン (W S i 2) 、窒化タングステン (W N) 、酸化ルテニウム (R u O 2) 、ケイ化コバルト、ケイ化ニッケルなど）、またはこれらおよび他の適切な材料の任意の適切な組合せを含む、任意の適切な導電性材料から形成することができるが、これらに限定されない。導電性材料は、堆積中または堆積後に取り込まれるドーパントをさらに含むことができる。一部の実施形態において、ゲート導体は、縦型トランジスタの閾値電圧を所望の値に設定するための仕事関数金属 (W F M) 層を含む。W F M は、窒化チタン (T i N) 、チタンアルミニウム窒化物 (T i A l N) 、窒化ハフニウム (H f N) 、ハフニウムシリコン窒化物 (H f S i N) 、窒化タンタル (T a N) 、タンタルシリコン窒化物 (T a S i N) 、窒化タングステン (W N) 、窒化モリブデン (M o N) 、窒化ニオブ (N b N) を含むがこれらに限定されない窒化物、炭化チタン (T i C) 、チタンアルミニウム炭化物 (T i A l C) 、炭化タンタル (T a C) 、炭化ハフニウム (H f C) を含むがこれらに限定されない炭化物、およびこれらの組合せであってよい。

10

20

30

#### 【0043】

ゲート導体 136 は、図示したように、フィン 101 の周囲の領域に充填され、スペーサの側壁およびゲート開口部を囲む側壁に 3 nm ~ 10 nm の厚さを有するが、特定の適用の要求に応じて、この範囲外の他の厚さを使用してもよい。

#### 【0044】

前述したように、ゲート誘電体およびゲート導体 136 は、R M G プロセスを使用して形成される。ゲート誘電体膜およびゲート導体 136 は、C V D、プラズマ化学気相成長 (P E C V D) 、A L D、蒸着、P V D、化学溶液堆積、または他の同様のプロセスなどの適切な堆積プロセスによって形成することができる。ゲート誘電体およびゲート導体 136 の厚さは、堆積プロセスならびに使用するゲート誘電体材料の組成および数に応じて変化し得る。

40

#### 【0045】

図 18 は、ゲート・コンタクト金属層とも呼ばれる金属層 138 を、図示したようにゲート開口部に充填した後の、図 17 の半導体構造の側断面図 1800 である。金属層 138 は、C M P または他の適切な処理を使用して、I L D 122 の上面と略同一平面の表面を有するように平坦化することができる。金属層 138 は、金属層 128 と同様の材料から形成することができる。

#### 【0046】

図 19 は、金属層 138 の凹部形成、およびゲート S A C キャッピング層とも呼ばれる S A C キャッピング層 140 の形成後の、図 18 の半導体構造の側断面図 1900 である。S A C キャッピング層 140 は、S A C キャッピング層 130 と同様の材料から同様の厚さで形成することができる。金属層 138 には、金属層 128 の凹部形成に使用したものと同様の処理を使用して凹部形成することができる。

50

#### 【0047】

図 20 は、マスク層 142 をパターニングし、下部ソース / ドレイン領域 106 の開口部を形成した後の、図 19 の半導体構造の側断面図 2000 である。マスク層 142 は、マスク層 124 に関して前述したものと同様の材料および同様のサイズを使用して形成することができる。下部ソース / ドレイン領域 106 の開口部は、方向性 R I E または他の

50

適切な処理によって形成することができる。

【0048】

図21は、下部ソース／ドレイン・コンタクト金属層とも呼ばれる金属層144を下部ソース／ドレイン領域106の開口部に充填した後の、図20の半導体構造の側断面図2100である。図21は、金属層144の凹部形成、および下部ソース／ドレイン・キャッピング層とも呼ばれるSACキャッピング層146の形成も示す。金属層144は、金属層128、138と同様の材料から同様の処理によって形成することができる。SACキャッピング層146は、SACキャッピング層130、140の形成に関して説明したものと同様の材料から同様の大きさで、同様の処理を使用して形成することができる。

【0049】

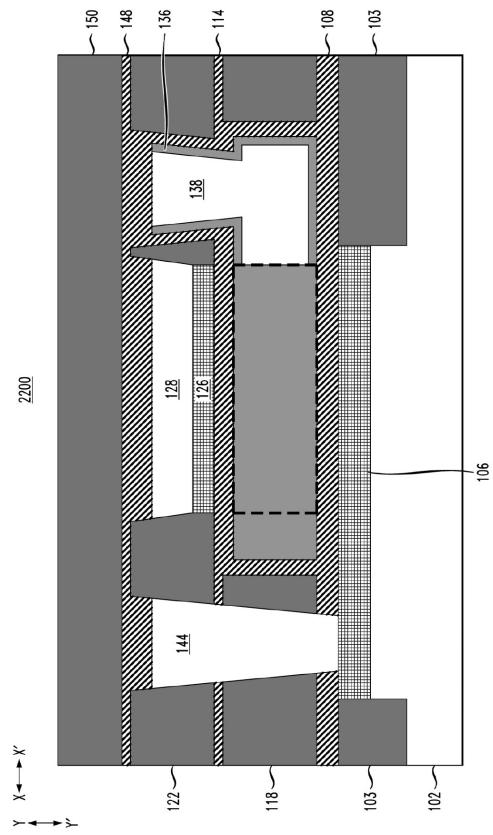

図22は、ライナ148およびILD150の形成後の、図21の半導体構造の側断面図2200である。ライナ148は、上部スペーサ114およびSACキャッピング層130、140、146と同様の材料から形成することができる。ライナ148は、5nm～20nmの高さまたは垂直方向厚さ（方向Y-Y'）を有することができるが、特定の適用の要求に応じて、この範囲外の他の厚さを使用してもよい。ILD150は、ILD122と同様の材料から形成することができる。ILD150は、30nm～150nmの高さまたは垂直方向厚さ（方向Y-Y'）を有するが、特定の適用の要求に応じて、この範囲外の他の厚さを使用してもよい。

【0050】

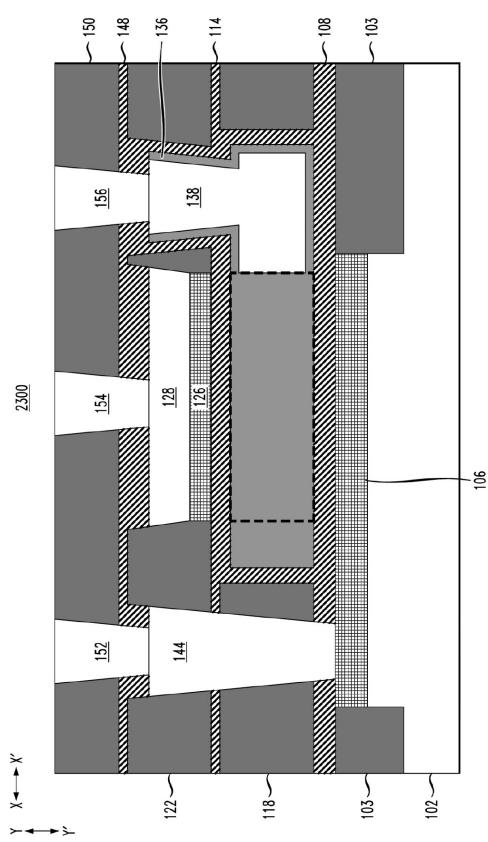

図23は、下部ソース／ドレイン領域106、上部ソース／ドレイン領域126、およびゲート導体136のそれぞれのコンタクトに（金属層128、138、144のそれを介して）アクセスするためのビア152、154、156を形成した後の、図22の半導体構造の側断面図2300である。ビア152、154、156は、CVDまたはALDなどのコンフォーマル堆積処理を使用して形成することができる、各々、上面に20nm～100nmの幅または水平方向厚さ（方向X-X'）を有することができるが、特定の適用の要求に応じて、この範囲外の他の幅を使用してもよい。ビア152、154、156が異なる幅を有してもよいことも理解されたい。

【0051】

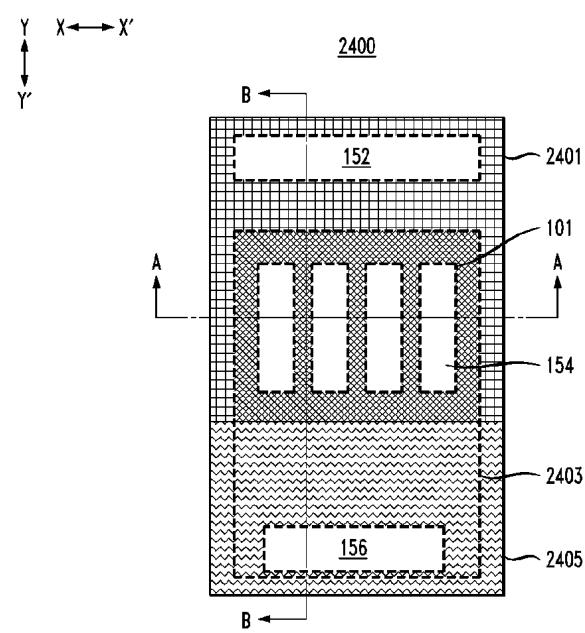

図24は、図23の半導体構造の上面図2400である。上面図2400は、フィン101に対するビア152、154、156の位置を示すように提示されており、したがって、図示を明瞭にするために、下にある層の様々な詳細が省略されていることに留意されたい。下部ソース／ドレイン・コンタクトのビア152は、30nm、またはより一般的には20nm～100nmの厚さ（方向Y-Y'）を有することができるが、特定の適用の要求に応じて、他の適切な厚さを使用してもよい。各フィン101は、45nm、またはより一般的には10nm～200nmの長さ（方向Y-Y'）を有することができるが、特定の適用の要求に応じて、他の適切な長さを使用してもよい。上部ソース／ドレイン・コンタクトのビア154は、図示したように、フィン101の長さに一致する長さを有することができるが、これは必要条件ではない。ゲート・コンタクトのビア156は、20nm、またはより一般的には15nm～100nmの厚さ（方向Y-Y'）を有することができるが、特定の適用の要求に応じて、他の適切な厚さを使用してもよい。

【0052】

上面図2400は、半導体構造のマスク領域2401、2403、2405を示す。マスク領域2401は、下部ソース／ドレイン106が形成される場所を示す。マスク領域2403は、ゲートが形成される場所を示す。マスク領域2405は、ダミー・ゲート112を露出させるための開口部が形成される場所を示す。

【0053】

縦型トランジスタのRMG方式では、ゲート・コンタクトの開口部156を通して、ダミー・ゲートを除去し、ゲート誘電体およびゲート導体を堆積させることが必要である。リソグラフィおよびエッチングのプロセスの変動により、ゲートおよびソース／ドレイン領域間の短絡の危険が大きくなるため、ゲート・コンタクトの開口部を上部ソース／ドレ

10

20

30

40

50

イン領域から離して配置すべきである。フィン 101 とゲート・コンタクトの開口部 156 との距離は、一般的に 20 nm ~ 100 nm であるため、ダミー・ゲートを除去し、ゲート誘電体およびゲート導体を堆積させることができない。しかしながら、例示的な実施形態において、上部ソース/ドレイン領域および下部ソース/ドレイン領域の開口部の上部に SAC キャッピング層が形成されることによって、寸法の制約ならびにゲートおよび上部ソース/ドレイン間の短絡のない RMG プロセスが可能になり、有利である。

#### 【0054】

前述したように、図 1 ~ 図 12 の側断面図は、例えば、図 24 の上面図 2400 の A-A 線に沿って、フィン 101 の長さに垂直に取っている。図 13 ~ 図 23 の側断面図は、例えば、図 24 の上面図 2400 の B-B 線に沿って、フィン 101 の長さに平行に取っている。

10

#### 【0055】

一部の実施形態において、RMG プロセスを使用して、共通の基板に形成された VTFET について複数の異なるチャネル長さを形成することができる。図 25 ~ 図 34 は、複数の異なるチャネル長さを形成するためのそのような処理の例を示す。

#### 【0056】

図 25 は、図 3 に示す半導体構造と同様の半導体構造の側断面図 2500 であり、同様の符号を付した要素は同様の材料から同様のサイズで、同様の処理によって形成される。しかしながら、図 25 に示す半導体構造では、フィンが異なる領域 2501-1、2501-2 に配置され、STI 領域 2503 (STI 領域 103 と同様の材料から形成される) が異なる領域 2501-1、2501-2 のフィン間に形成されている。STI 領域 2503 は、下部ソース/ドレイン領域 106 の形成後に形成することができる。図 25 ~ 図 34 に関して後述するプロセスの例において、領域 2501-1 のフィンを使用して「長」チャネル・デバイスを形成し、領域 2501-2 のフィンを使用して「短」チャネル・デバイスを形成する。

20

#### 【0057】

図 26 は、上面にマスク層 2505 をパターニングし、マスク層 2505 により露出されたダミー・ゲート 112 の部分をパターニングまたは除去するようにエッティングした後の、図 25 の半導体構造の側断面図 2600 である。マスク層 2505 は、マスク層 124 に関して前述したものと同様の材料から同様のサイズで形成することができる。開口部 2601 は、20 nm ~ 150 nm の幅を有することができるが、ダミー・ゲート 112 の材料の十分な部分が領域 2501-1、2501-2 の開口部 2601 に最も近いフィンを囲んだままであれば、この範囲より大きいまたは小さい他の適切な幅を使用してもよい。マスク層 2505 により露出されたダミー・ゲート 112 は、方向性 RIE または他の適切な処理を使用して除去することができる。

30

#### 【0058】

図 27 は、ライナ 2507 の形成後の、図 26 の半導体構造の側断面図 2700 である。ライナ 2507 は、下部スペーサ 108 と同様の材料 (例えば、SiN) から形成することができる。ライナ 2507 は、5 nm ~ 20 nm の幅または厚さ (方向 X-X') を有することができるが、特定の適用の要求に応じて、この範囲より大きいまたは小さい他の適切な幅を使用してもよい。ライナ 2508 は、任意の適切な堆積およびその後の RIE によって形成することができる。

40

#### 【0059】

図 28 は、ダミー・ゲート 112 の凹部形成後の、図 27 の半導体構造の側断面図 2800 である。ダミー・ゲート 112 の凹部形成は、図 4 に関して前述したものと同様の処理を使用することができるが、図 28 の例では、長チャネル領域 (例えば 2501-1) のダミー・ゲート 112 に第 1 の深さ 2801 で凹部形成され、他方で短チャネル領域 (例えば 2501-2) のダミー・ゲート 112 に第 2 の深さ 2803 で凹部形成され、第 2 の深さ 2803 が第 1 の深さ 2801 より大きい。一部の実施形態において、第 1 の深さ 2801 は 15 nm ~ 100 nm であってよく、他方で第 2 の深さ 2803 は 25 nm

50

~110nmであるが、要求に応じて、この範囲外の他の深さを使用して異なるチャネル長さを形成してもよい。図25～図34は2つの異なるチャネル長さが形成される例を示すが、実施形態はこれに限定されないことを理解されたい。それどころか、図25～図34に関して説明するものと同様の技法を使用して、要求に応じて任意の数の異なるチャネル長さを形成することができる。

#### 【0060】

ダミー・ゲート112に異なる深さ2801、2803まで凹部形成することは、最初に長チャネル領域および短チャネル領域の両方のダミー・ゲート112に深さ2801まで凹部形成し、次に長チャネル領域のダミー・ゲート112をマスキングまたは保護し、その後、短チャネル領域のダミー・ゲート112にさらに凹部形成することを含むことができる。あるいは、短チャネル領域のダミー・ゲート112を保護しながら長チャネル領域のダミー・ゲート112に凹部形成し、その後、長チャネル領域のダミー・ゲート112を保護しながら短チャネル領域のダミー・ゲート112に凹部形成してもよい（または、この逆も可能である）。

10

#### 【0061】

図29は、上部スペーサ2514の形成後の、図28の半導体構造の側断面図2900であり、上部スペーサ2514は、上部スペーサ114と同様の材料、同様の大きさを使用して、同様の処理によって形成することができる。上部スペーサ2514の形成前に、各フィン上のハード・マスク104が除去され、酸化物110は、上面が周囲のダミー・ゲート112と略同一平面になるように凹部形成される。上部スペーサ2514の形成前にライナ2507も除去される。

20

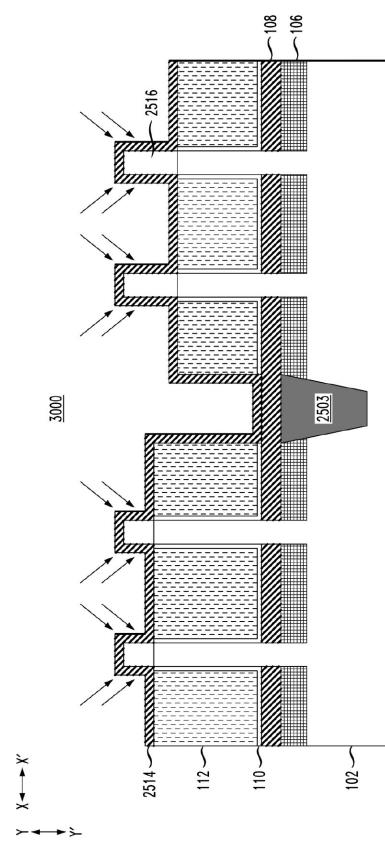

#### 【0062】

図30は、上部接合部2516の形成後の、図29の半導体構造の側断面図3000である。上部接合部2516の形成は、上部接合部116の形成に関して前述したものと同様の処理を使用することができる。図30に示すように、短チャネル領域の上部接合部2516は、長チャネル領域の上部接合部2516に対して「より長い」、またはより大きい垂直方向厚さを有する。長チャネル領域および短チャネル領域の両方の上部接合部2516は、周囲のダミー・ゲート112の表面より下方に2nm～10nmの深さまで延びるが、特定の適用の要求に応じて、この範囲外の他の適切な深さを使用してもよい。しかしながら、トランジスタ性能が非ドープ領域により低下するおそれがない限り、上部接合部2516はゲート導体と重なるべきである。

30

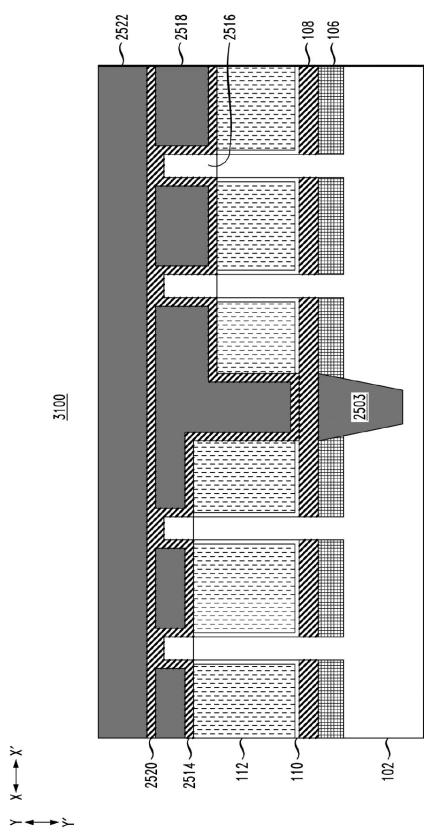

#### 【0063】

図31は、絶縁層2518、スペーサ2520、およびILD2522の形成後の、図30の半導体構造の側断面図3100である。絶縁層2518、スペーサ2520、およびILD2522は、絶縁層118、スペーサ120、およびILD122のそれぞれに関して前述したものと同様の材料から同様の大きさで、同様の処理を使用して形成することができる。

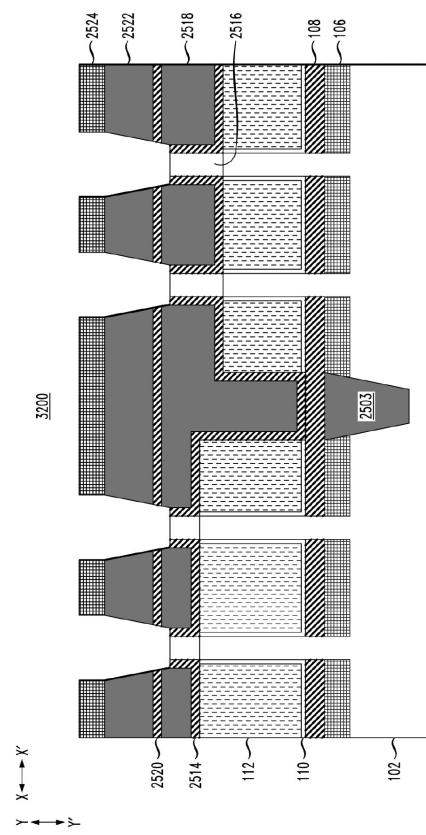

#### 【0064】

図32は、パターニングされたマスク層2524を使用して上部接合部2516を露出させるように開口した後の、図31の半導体構造の側断面図3200である。マスク層2524は、マスク層124に関して前述したものと同様の方法でパターニングすることができる。上部接合部2516を露出させるための開口部は、図9に関して前述したものと同様の処理を使用して形成することができる。

40

#### 【0065】

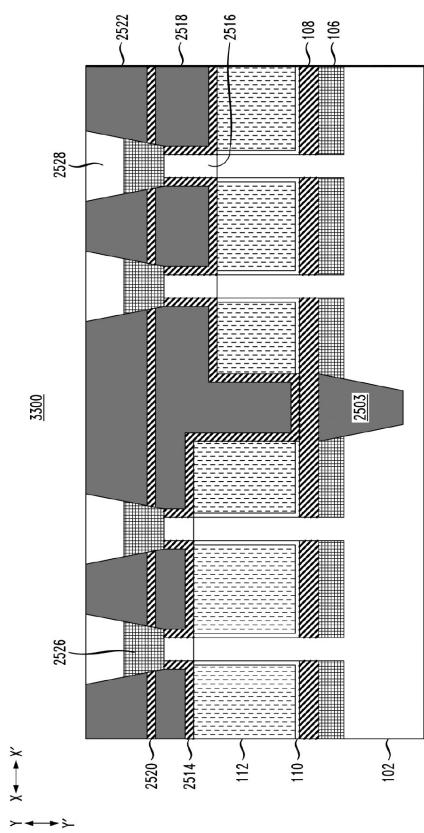

図33は、上部ソース／ドレイン領域2526の形成および上部ソース／ドレイン領域2526上への金属層2528の形成後の、図32の半導体構造の側断面図3300である。上部ソース／ドレイン領域2526は、上部ソース／ドレイン領域126に関して前述したものと同様の材料から同様の大きさで、同様の処理を使用して形成することができる。しかしながら、図33は、図10の任意選択の横方向エッチングを行わない一実施形態を示す。しかしながら、他の実施形態においては、図10に関して前述した任意選択の

50

横方向エッティングを使用して上部ソース／ドレイン領域 2526 を形成してもよい。金属層 2528 は、金属層 128 に関して前述したものと同様の材料から同様の大きさで、同様の処理を使用して形成することができる。

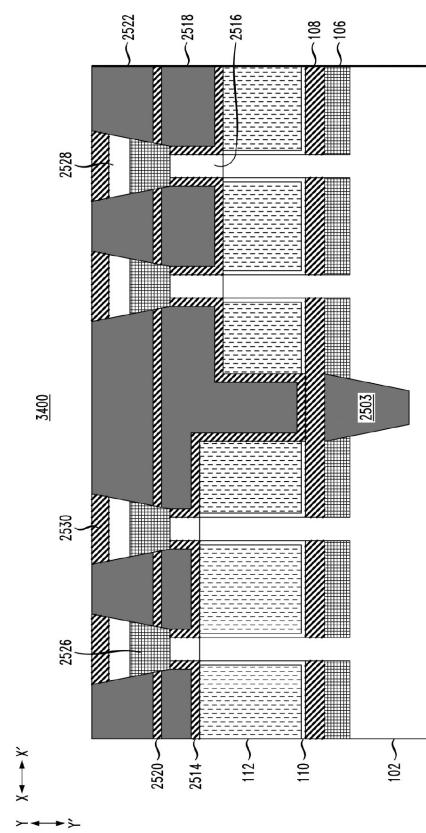

#### 【0066】

図 34 は、金属層 2528 の凹部形成、および本明細書で上部ソース／ドレイン SAC キャッピング層とも呼ばれる SAC キャッピング層 2530 の形成後の、図 33 の半導体構造の側断面図 3400 である。金属層 2528 の凹部形成および SAC キャッピング層 2530 の形成は、図 12 に関して前述したものと同様の処理を使用することができる。SAC キャッピング層 2530 は、SAC キャッピング層 130 と同様の材料から同様の大きさで形成することができる。

10

#### 【0067】

図 25～図 34 は、図 1～図 12 と同様に、フィンに垂直に（例えば、図 24 の上面図 2400 の A-A 線に沿って）取った断面図である。図 34 の半導体構造は、図 13～図 23 に関して前述したものと同様の RMG についてのさらなる処理を受けることができる。

#### 【0068】

本明細書に記載の RMG 技法を、CMOS デバイスの形成または CMOS のパターニングに使用することもできる。以下で、図 35～図 45 に関して、CMOS のパターニングのための RMG プロセスについて説明する。

#### 【0069】

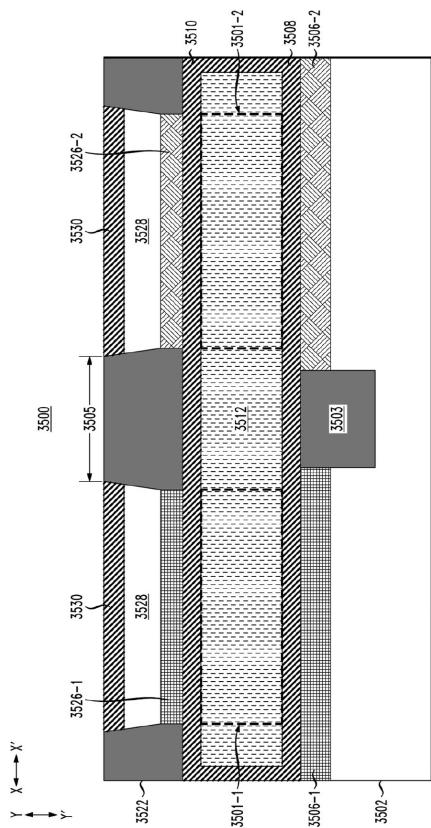

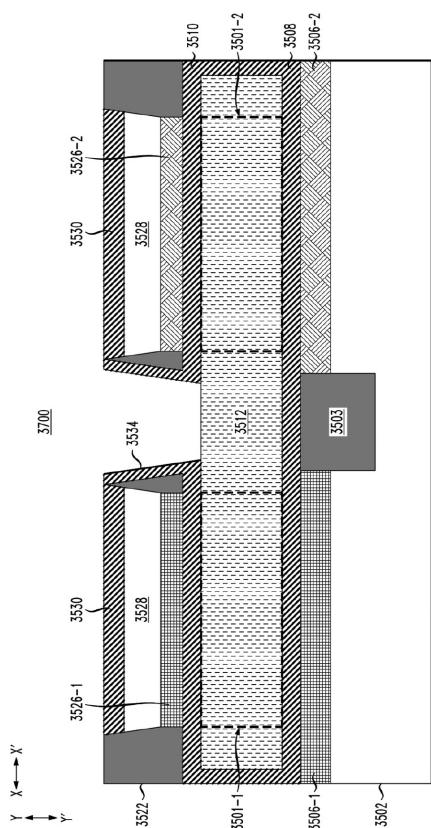

図 35 は、共有ダミー・ゲート 3512 を含む半導体構造の側断面図 3500 である。図 35 の半導体構造は、基板 3502、STI 領域 3503、下部ソース／ドレイン領域 3506-1、3506-2（まとめて下部ソース／ドレイン領域 3506）、下部スペーサ 3508、上部スペーサ 3510、ILD 3522、上部ソース／ドレイン領域 3526-1、3526-2（まとめて上部ソース／ドレイン領域 3526）、金属層 3528、および SAC キャッピング層 3530 を含み、これらは、基板 102、STI 領域 103、下部ソース／ドレイン領域 106、下部スペーサ 108、上部スペーサ 114、ILD 122、上部ソース／ドレイン領域 126、金属層 128、および SAC キャッピング層 130 のそれぞれに関して前述したものと同様の材料から同様の大きさで、同様の処理を使用して形成することができる。しかしながら、図 35 は、N F E T を形成する第 1 のフィン 3501-1 と P F E T を形成する第 2 のフィン 3502-2 を含む CMOS 配置を示す。フィン 3501-1、3501-2（まとめてフィン 3501）は、側断面図 3500 において共有ダミー・ゲート 3512 の「後方」にあるため、破線の輪郭で示されている。

20

#### 【0070】

N F E T の下部ソース／ドレイン領域 3506-1 および上部ソース／ドレイン領域 3526-1 は n 型ドーパントでドープすることができ、下部ソース／ドレイン領域 3506-2 および上部ソース／ドレイン領域 3526-2 は p 型ドーパントでドープすることができる。フィン 3501-1、3501-2 間の距離 3505 は、75 nm、またはより一般的には 30 nm～100 nm であってよいが、後述する処理を使用する共有ゲート・コンタクトの形成のための十分な空間があれば、要求に応じてこの範囲外の他の距離を使用してもよい。

30

#### 【0071】

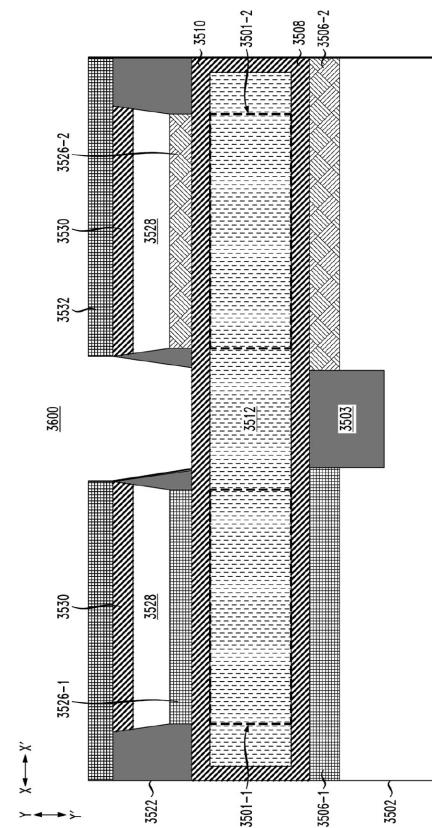

図 36 は、パターニングされたマスク層 3532 を使用して共有ダミー・ゲート 3512 を開口した後の、図 35 の半導体構造の側断面図 3600 である。共有ダミー・ゲート 3512 の開口部は、図 14 に関して前述したものと同様の処理を使用して形成することができる。マスク層 3532 は、マスク層 132 と同様の材料を使用して同様のサイズで形成することができる。

40

#### 【0072】

図 37 は、図 15 に関して前述したものと同様の処理を使用してライナ 3534 を形成した後の、図 36 の半導体構造の側断面図 3700 である。ライナ 3534 は、ライナ 1

50

34と同様の材料を使用して同様のサイズで形成することができる。

【0073】

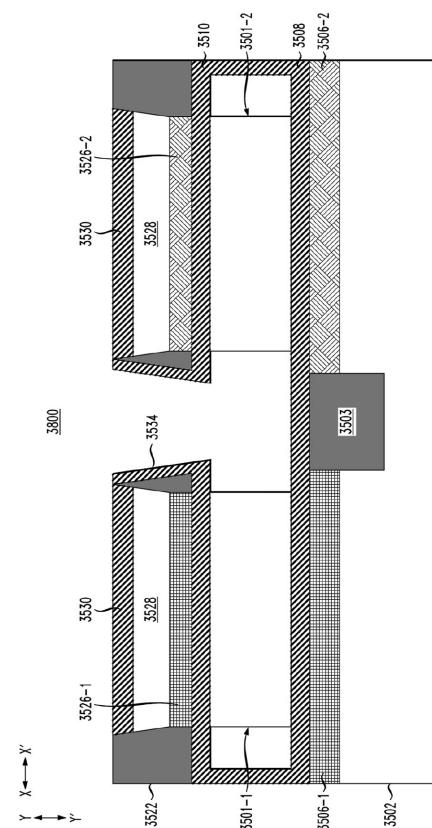

図38は、共有ダミー・ゲート3512の除去後の、図37の半導体構造の側断面図3800である。共有ダミー・ゲート3512は、ダミー・ゲート112の除去に関して前述したものと同様の処理を使用して除去することができる。

【0074】

図39は、ゲート誘電体(図示せず)およびPFEWT WFM3536-2(より一般的には、PFEETゲート導体3536-2)の堆積後の、図38の半導体構造の側断面図3900である。最初に、図示したように、NFETデバイスのフィン3501-1を囲むPFEET WFM3536-2が形成されるが、これは後述する後の処理中に除去される。PFEET WFM3536-2は、窒化チタン(TiN)、チタンアルミニウム窒化物(TiAlN)、窒化タンタル(TaN)、タンタルシリコン窒化物(TaSiN)などの窒化物、または炭化チタン(TiC)、チタンアルミニウム炭化物(TiAlC)、炭化タンタル(TaC)を含むがこれらに限定されない炭化物から形成することができるが、他の適切な材料を使用してもよい。PFEET WFM3536-2は、ALDまたはCVDなどのコンフォーマル堆積処理を使用して形成することができる。

10

【0075】

図40は、PFEET WFM3536-2のパターニング後の、図39の半導体構造の側断面図4000である。PFEET WFM3536-2は、PFEET領域(例えば、フィン3501-2を囲むPFEET WFM3536-2)をブロックすることによりパターニングされるが、NFET領域のPFEET WFM3536-2(例えば、フィン3501-1を囲むPFEET WFM3536-2の部分)が、ウェット化学エッチング(例えば、SC1)または他の適切な処理を使用して除去される。PFEET WFM3536-2は、有機ポリマー層(OPL)3537を使用してPFEET領域でブロックすることができる。PFEET WFM3536-2がNFET領域で除去されると、フィン3501-1を囲むゲート誘電体3534が見える(ゲート誘電体3534はフィン3501-2を同様に囲むが、側断面図4000では見えない)。PFEET WFM3536-2をNFET領域から除去する間にPFEET領域がOPL3537によりブロックされるが、図示したように、PFEET領域のPFEET WFM3536-2から一部の横方向アンダカット4001が取り除かれる。しかしながら、横方向アンダカット4001は小さく、そしてそのことはゲート金属のパターニング中の非常に小さいn p境界ずれに対応し、有利である。

20

30

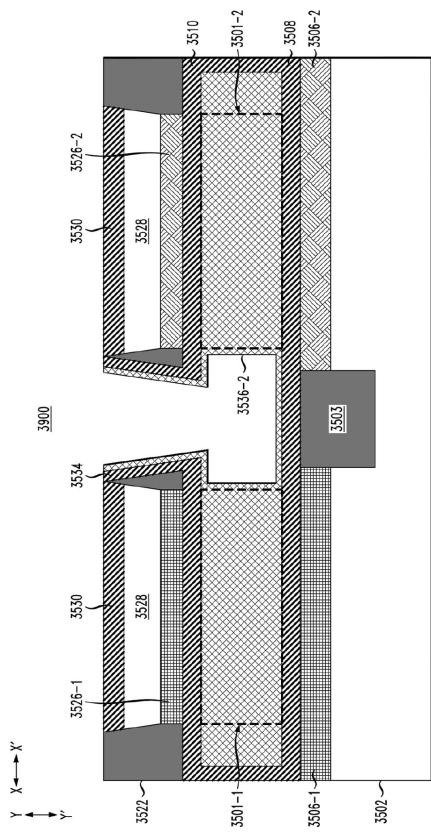

【0076】

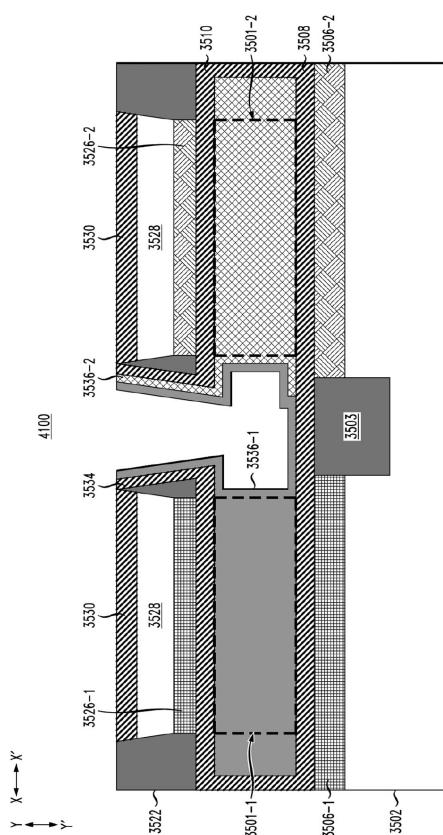

図41は、NFET WFM3536-1(より一般的には、NFETゲート導体3536-1)の形成後の、図40の半導体構造の側断面図4100である。NFET WFM3536-1は、ALDまたはCVDなどのコンフォーマル堆積処理を使用して形成することができる。NFET WFM3536-1は、窒化チタン(TiN)、チタンアルミニウム窒化物(TiAlN)、窒化タンタル(TaN)、タンタルシリコン窒化物(TaSiN)などの窒化物、炭化チタン(TiC)、チタンアルミニウム炭化物(TiAlC)、炭化タンタル(TaC)を含むがこれらに限定されない炭化物、およびこれらの組合せから形成することができるが、他の適切な材料を使用してもよい。図39~図41は、PFEET WFM3536-2の形成およびその後のNFET WFM3536-1の形成を示すが、他の実施形態において、NFET WFM3536-1は、同様の処理を使用するPFEET WFM3536-2の形成前に形成してもよい(例えば、最初にNFET WFM3536-1を形成し、次にNFET WFM3536-1をPFEET領域から除去しながらNFET領域をブロックしてもよい)ことを理解されたい。

40

【0077】

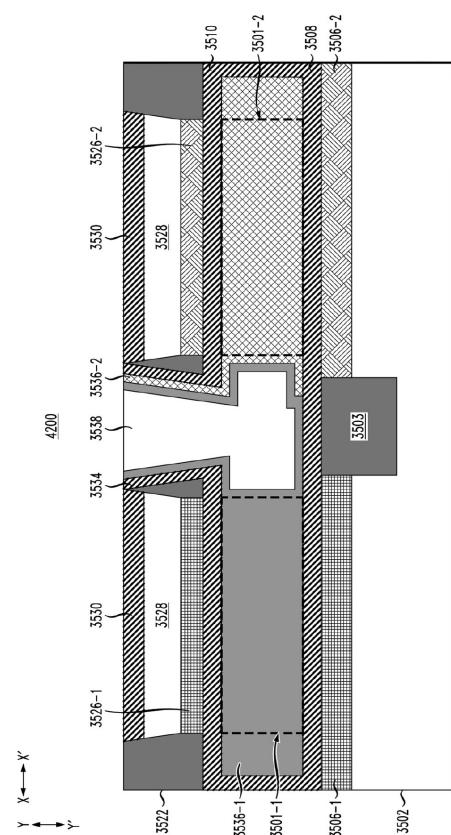

図42は、金属層138と同様の材料を使用して同様の処理によって形成することのできる金属層3538を充填した後の、図41の半導体構造の側断面図4200である。

【0078】

50

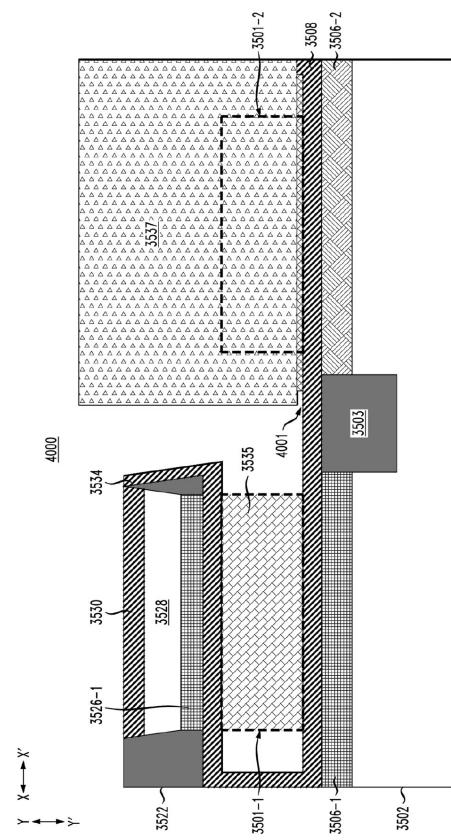

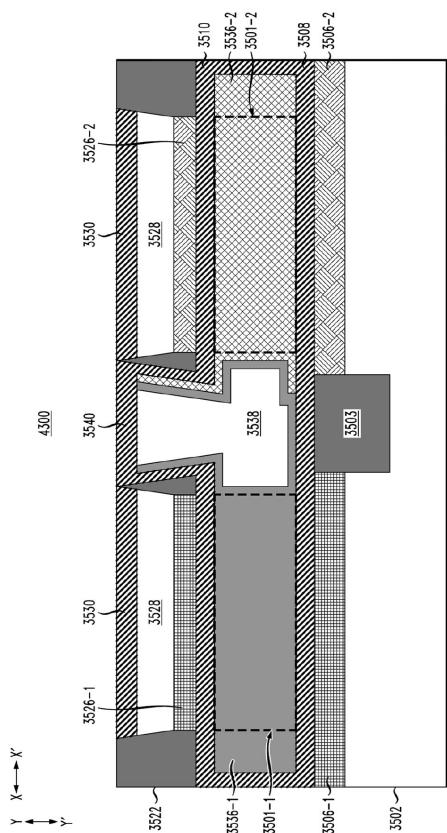

図43は、金属層3538の凹部形成（ならびにN F E T W F M 3536-1およびP F E T W F M 3536-2の凹部形成）、ならびにゲートS A Cキャッピング層または共有ゲートS A Cキャッピング層とも呼ばれるS A Cキャッピング層3540の形成後の、図42の半導体構造の側断面図4300である。金属層3538の凹部形成（ならびにN F E T W F M 3536-1およびP F E T W F M 3536-2の凹部形成）、ならびにS A Cキャッピング層3540の形成は、金属層138の凹部形成およびS A Cキャッピング層140の形成に関して前述したものと同様の処理を使用することができる。S A Cキャッピング層3540は、S A Cキャッピング層140と同様の材料および同様のサイズを使用して形成することができる。

## 【0079】

10

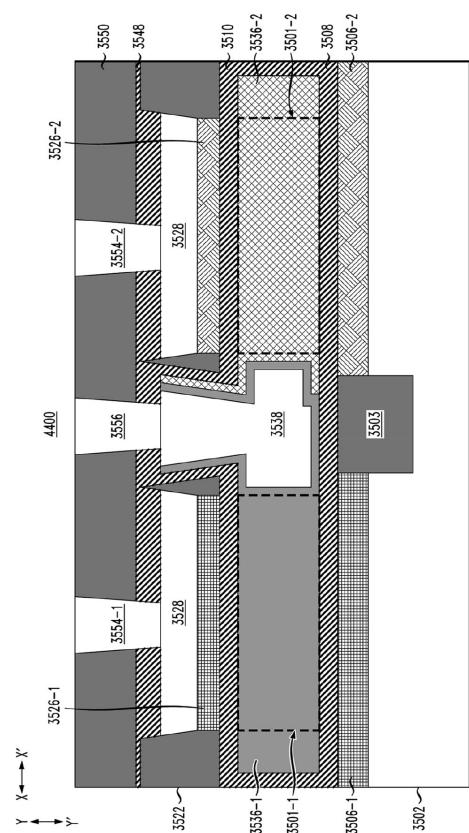

図44は、上部ソース／ドレイン領域3526-1、3526-2のそれぞれのコンタクトにアクセスするためのビア3554-1、3554-2の形成、および共有ゲートのコンタクトにアクセスするためのビア3556の形成後の、図43の半導体構造の側断面図4400である。ビア3554-1、3554-2（まとめてビア3554）およびビア3556は、ビア154、156の形成に関して前述したものと同様の材料から同様のサイズで、同様の処理を使用して形成することができる。図44には示さないが、下部ソース／ドレイン領域3506-1、3506-2のビア3552-1、3552-2も形成される（図45に示すように、ビア152の形成に関して説明したものと同様の処理によって形成される）。

## 【0080】

20

図45は、図44の半導体構造の上面図4500である。上面図4500は、フィン3501-1、3501-2に対するビア3552-1、3552-2、3554-1、3554-2、3556の位置を示すように提示されており、したがって、図示を明瞭にするために、下にある層の様々な詳細が省略されていることに留意されたい。下部ソース／ドレイン・コンタクトのビア3552-1、3552-2は、下部ソース／ドレイン・コンタクトのビア152と同様のサイズを有することができる。各フィン3501は、フィン101と同様の長さ（方向Y-Y'）を有することができる。上部ソース／ドレイン・コンタクトのビア3554-1、3554-2は、図示したようにフィン3501の長さに一致する長さを有することができるが、これは必要条件ではない。ゲート・コンタクトのビア3556は、ゲート・コンタクトのビア156と同様の厚さを有することができる。

30

## 【0081】

上面図4500は、マスク領域2401、2403、2405と同様のマスク領域4501、4503、4505を示す。図35～図44の側断面図は、対のフィン3501-1、3501-2に平行に、例えば、図45の上面図4500のB-B線に沿って取っている。

## 【0082】

本発明の一部の実施形態において、半導体構造を形成する方法は、基板の上面に配置された複数のフィンを形成することと、R M Gプロセスを使用して複数のフィンから1つまたは複数のV T F E Tを形成することとを含む。V T F E Tのうちの所与の1つの少なくとも1つのフィンを囲むゲートが、ゲート・コンタクト金属層に配置されたゲートS A Cキャッピング層を含み、ゲート・コンタクト金属層が、少なくとも1つのフィンの端部に隣接して配置される。

40

## 【0083】

1つまたは複数のV T F E Tを形成することが、複数のフィンを囲む基板の上面に配置された下部ソース／ドレイン領域を形成することと、下部ソース／ドレイン領域に配置された下部スペーサを形成することとを含むことができる。

## 【0084】

1つまたは複数のV T F E Tを形成することが、下部スペーサおよび複数のフィンの側壁に配置された酸化物層を形成することと、酸化物層に配置されたダミー・ゲートを形成することと、複数のフィンの上面より下方でダミー・ゲートに凹部形成することと、酸化

50

物層の露出部分を除去することと、ダミー・ゲートおよび複数のフィンに配置された上部スペーサを形成することとをさらに含むことができる。

【 0 0 8 5 】

1つまたは複数のV T F E Tを形成することが、複数のフィンの上部に上部接合部を形成することと、上部スペーサに配置された酸化物層を形成することと、酸化物層に配置されたライナを形成することと、ライナに配置された層間誘電体層を形成することとをさらに含むことができる。

【 0 0 8 6 】

1つまたは複数のV T F E Tを形成することが、複数のフィンの各々の上部接合部の上面を露出させるように層間誘電体層に上部ソース／ドレイン開口部を形成することと、上部接合部に配置された上部ソース／ドレイン領域を形成することと、上部ソース／ドレイン領域に配置された上部ソース／ドレイン・コンタクト金属層を形成することと、層間誘電体の上面より下方で上部ソース／ドレイン・コンタクト金属層に凹部形成することと、凹部形成された上部ソース／ドレイン・コンタクト金属層に配置された上部ソース／ドレインS A Cキャッピング層を形成することとをさらに含むことができる。

10

【 0 0 8 7 】

1つまたは複数のV T F E Tを形成することが、ダミー・ゲートに配置された上部スペーサの一部を露出させるように層間誘電体層にゲート開口部を形成することと、層間誘電体層の開口部の側壁にライナを堆積させることと、ダミー・ゲートの一部を露出させるように上部スペーサの露出部分をエッチングすることと、ダミー・ゲートを除去することと、1つまたは複数のフィンを囲むゲート誘電体を形成し、かつゲート誘電体を囲む金属ゲート導体を形成するように置換金属ゲート・プロセスを行うことと、層間誘電体層のゲート開口部の残りの部分にゲート・コンタクト金属層を充填することと、層間誘電体層の上面より下方でゲート・コンタクト金属層に凹部形成することと、凹部形成されたゲート・コンタクト金属層に配置されたゲートS A Cキャッピング層を形成することとをさらに含むことができる。

20

【 0 0 8 8 】

1つまたは複数のV T F E Tを形成することが、下部ソース／ドレイン領域の上面の一部を露出させるように層間誘電体層に下部ソース／ドレイン開口部を形成することと、下部ソース／ドレイン領域の上面の露出部分に配置された下部ソース／ドレイン開口部に下部ソース／ドレイン・コンタクト金属層を充填することと、層間誘電体層の上面より下方で下部ソース／ドレイン・コンタクト金属層に凹部形成することと、凹部形成された下部ソース／ドレイン・コンタクト層に配置された下部ソース／ドレインS A Cキャッピング層を形成することとをさらに含むことができる。

30

【 0 0 8 9 】

1つまたは複数のV T F E Tを形成することが、層間誘電体、上部ソース／ドレインS A Cキャッピング層、ゲートS A Cキャッピング層、および下部ソース／ドレインS A Cキャッピング層に配置された追加のライナを形成することと、追加のライナに配置された追加の層間誘電体を形成することと、上部ソース／ドレイン・コンタクト金属層、ゲート・コンタクト金属層、および下部ソース／ドレイン・コンタクト金属層の上面の一部を露出させるように、追加のライナ、追加の層間誘電体、上部ソース／ドレインS A Cキャッピング層、ゲートS A Cキャッピング層、および下部ソース／ドレインS A Cキャッピング層にピアを形成することと、ピアに上部ソース／ドレイン・コンタクト、ゲート・コンタクト、および下部ソース／ドレイン・コンタクトを形成することとをさらに含むことができる。

40

【 0 0 9 0 】

1つまたは複数のV T F E Tを形成することが、少なくとも1つのシャロー・トレチ絶縁領域を、複数のフィンの第1のサブセットと複数のフィンの少なくとも第2のサブセットとの間で基板および下部ソース／ドレイン領域に形成することとをさらに含むことができ、ダミー・ゲートに凹部形成することが、複数のフィンの第1のサブセットを囲むダミ

50

ー・ゲートの第1の部分に第1の深さまで凹部形成することと、複数のフィンの第2のサブセットを囲むダミー・ゲートの第2の部分に第1の深さより大きい第2の深さまで凹部形成することとを含む。複数のフィンの第1のサブセットが、第1のチャネル長さを有するV T F E Tを形成し、複数のフィンの第2のサブセットが、第1のチャネル長さより短い第2のチャネル長さを有するV T F E Tを形成する。

【0091】

ダミー・ゲートの第1の部分に凹部形成することと、ダミー・ゲートの第2の部分に凹部形成することが、少なくとも1つのシャロー・トレンチ絶縁領域に配置されたダミー・ゲートの上面を露出させるようにダミー・ゲート上のマスク層をパターニングすることと、少なくとも1つのシャロー・トレンチ絶縁領域に配置された下部スペーサーの一部を露出させるようにダミー・ゲートの露出部分を除去することと、ダミー・ゲートの露出した側壁にライナを形成することとを含むことができる。

10

【0092】

ダミー・ゲートが、複数のフィンの対を囲む共有ダミー・ゲートを含むことができ、複数のフィンの各対が、所与のCMOSデバイスのP F E Tおよび所与のCMOSデバイスのN F E Tの一方のチャネルを形成する第1のフィンと、所与のCMOSデバイスのP F E TおよびN F E Tの他方のチャネルを形成する第2のフィンとを含むことができる。

【0093】

1つまたは複数のV T F E Tを形成することが、共有ダミー・ゲートに配置された上部スペーサーに配置された層間誘電体層にゲート開口部をパターニングすることと、上部スペーサーの上面の一部を露出させるように層間誘電体層の一部を除去することと、ゲート開口部の層間誘電体層の露出した側壁にライナを形成することと、共有ダミー・ゲートを除去することとをさらに含むことができる。

20

【0094】

1つまたは複数のV T F E Tを形成することが、第1のフィンおよび第2のフィンを囲むゲート誘電体を形成することと、ゲート誘電体、基板の上面、および層間誘電体層の露出した側壁に配置されたライナを囲む第1のゲート導体層を形成することと、ゲート開口部の第1の部分および第1のフィンを囲む第1のゲート導体層を有機ポリマー層でプロックすることと、有機ポリマー層により露出された第2のフィンを囲む第1のゲート導体層を除去することと、有機ポリマー層を除去することと、第2のフィンを囲むゲート誘電体を囲む第2のゲート導体層を形成することとをさらに含むことができる。

30

【0095】

本方法は、第1のゲート導体層および第2のゲート導体層に接触するゲート開口部にゲート・コンタクト金属層を充填することと、層間誘電体の上面より下方でゲート・コンタクト金属層に凹部形成することと、凹部形成されたゲート・コンタクト金属層に配置されたゲートS A Cキャッピング層を形成することとをさらに含むことができる。

【0096】

本発明の一部の実施形態において、半導体構造は、基板と、基板の上面に配置された複数のフィンとを含み、複数のフィンが、R M Gプロセスを使用して形成された1つまたは複数のV T F E Tのチャネルを含む。V T F E Tのうちの所与の1つが、複数のフィンのうちの少なくとも1つを囲むゲートを含み、所与のV T F E Tのゲートが、ゲート・コンタクト金属層に配置されたゲートS A Cキャッピング層を含み、ゲート・コンタクト金属層が、少なくとも1つのフィンの端部に隣接して配置される。

40

【0097】

本半導体構造は、複数のフィンを囲む基板の上面に配置された下部ソース／ドレイン領域と、下部ソース／ドレイン領域に配置された下部スペーサーと、複数のフィンを囲むゲートと、ゲートに配置された上部スペーサーと、複数のフィンの各々に配置された上部スペーサーの一部に配置された上部ソース／ドレイン領域と、上部ソース／ドレイン領域に配置された上部ソース／ドレイン・コンタクト金属層と、上部ソース／ドレイン金属コンタクト層に配置された上部ソース／ドレインS A Cキャッピング層と、下部ソース／ドレイン領

50

域の一部に配置された下部ソース／ドレイン・コンタクト金属層と、下部ソース／ドレイン金属コンタクト層に配置された下部ソース／ドレインSACキャッピング層とをさらに含むことができる。

【0098】

一部の実施形態において、複数のフィンのうちの少なくとも2つが異なる高さを有する。

【0099】

一部の実施形態において、所与のVTFETのゲートが、複数のフィンの対を囲む共有ゲートを含み、複数のフィンの各対が、所与のCMOSデバイスのPFEトおよび所与のCMOSデバイスのNFEトの一方のチャネルを形成する第1のフィンと、所与のCMOSデバイスのPFEトおよびNFEトの他方のチャネルを形成する第2のフィンとを含む。

10

【0100】

本発明の一部の実施形態において、共有ゲートが、第1のフィンを囲む第1のゲート導体と、第2のフィンを囲む第2のゲート導体とを含み、ゲート・コンタクト金属層が第1のゲート導体および第2のゲート導体に接触する。

【0101】

本発明の一部の実施形態において、集積回路が、基板と基板の上面に配置された複数のフィンとを含む1つまたは複数のVTFETを含み、複数のフィンが、RMGプロセスを使用して形成された1つまたは複数のVTFETのチャネルを含む。VTFETのうちの所与の1つが、複数のフィンのうちの少なくとも1つを囲むゲートを含み、所与のVTFETのゲートが、ゲート・コンタクト金属層に配置されたゲートSACキャッピング層を含み、ゲート・コンタクト金属層が、少なくとも1つのフィンの端部に隣接して配置される。

20

【0102】

上記の説明で示した様々な材料、処理方法（例えば、エッチングのタイプ、堆積のタイプなど）、および寸法は、単に例示のために提示されたものであることを理解されたい。要求に応じて、様々な他の適切な材料、処理方法、および寸法を使用してもよい。

【0103】

上記の技法による半導体デバイスおよび半導体デバイスを形成するための方法を、様々な適用、ハードウェア、または電子システム、あるいはそれらの組合せで採用することができる。本発明の実施形態を実施するための適切なハードウェアおよびシステムとしては、センサおよび感知デバイス、パーソナル・コンピュータ、通信ネットワーク、電子商取引システム、携帯型通信デバイス（例えば、携帯電話およびスマート・フォン）、ソリッドステート媒体記憶デバイス、機能回路などが挙げられ得るが、これらに限定されない。半導体デバイスを組み込んだシステムおよびハードウェアが、本発明の実施形態によって考えられる。本明細書の教示を前提として、当業者は、本発明の実施形態の他の実施および適用を考えることができるだろう。

30

【0104】

前述した様々な構造を集積回路で実施することができる。これによって得られる集積回路チップは、作製者により、生ウエハの形で（すなわち、複数のパッケージされていないチップを有する單一ウエハとして）、ベア・ダイとして、またはパッケージされた形で流通させることができる。パッケージされた形の場合、チップは、單一チップ・パッケージ（マザーボードまたは他の高レベル・キャリアに付加されるリードを含むプラスチック・キャリアなど）、またはマルチチップ・パッケージ（片面もしくは両面相互接続または埋設相互接続を有するセラミック・キャリアなど）に装着される。いずれにしても、チップはその後、他のチップ、ディスクリート回路素子、または（a）マザーボードなどの中間製品もしくは（b）最終製品の一部としての他の信号処理デバイス、あるいはそれらの組合せに集積される。最終製品は、玩具および他の低性能の適用からディスプレイ、キーボード、または他の入力デバイス、および中央処理装置を有する高機能のコンピュータ製品まで、集積回路チップを含む任意の製品であってよい。

40

【0105】

50

例示の目的で本発明の様々な実施形態について説明したが、これらの説明は、網羅的なもの、または開示された実施形態に限定されるものではない。本発明の範囲から逸脱することなく、多くの修正および変更が当業者に明らかであろう。本明細書で使用した用語は、本発明の実施形態の原理、実際の適用、もしくは市場で見られる技術への技術的改良を最もよく説明するため、または本明細書に開示された本発明の実施形態を他の当業者が理解できるようにするために選択されたものである。

【図面】

【図 1】

【図 2】

10

20

30

40

50

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

10

20

30

40

50

【図 1 1】

【図 1 2】

10

20

【図 1 3】

【図 1 4】

30

40

50

【図 1 5】

【図 1 6】

10

【図 1 7】

【図 1 8】

20

30

40

50

【図 19】

【図 20】

10

【図 21】

【図 22】

20

30

40

50

【図23】

【図24】

10

20

【図25】

【図26】

30

40

50

【図27】

【図28】

10

20

【図29】

【図30】

30

40

50

【図3 1】

【図3 2】

10

20

30

40

【図3 3】

【図3 4】

50

【図35】

【図36】

10

【図37】

【図38】

20

30

40

50

【図39】

【図40】

10

【図41】

【図42】

20

30

40

50

【図 4 3】

【図 4 4】

10

20

30

40

【図 4 5】

50

## フロントページの続き

## (51)国際特許分類

|                         | F I          |   |  |

|-------------------------|--------------|---|--|

| H 01 L 27/092 (2006.01) | H 01 L 29/44 | S |  |

| H 01 L 29/417 (2006.01) | H 01 L 29/58 | G |  |

| H 01 L 29/41 (2006.01)  |              |   |  |

| H 01 L 29/423 (2006.01) |              |   |  |

| H 01 L 29/49 (2006.01)  |              |   |  |

## (72)発明者 リー、チューユン

アメリカ合衆国 12203 ニューヨーク州 オールバニ フラー・ロード 257

## (72)発明者 ヤン、チュン、ワイン

アメリカ合衆国 12203 ニューヨーク州 オールバニ フラー・ロード 257

## (72)発明者 バオ、ルーチャン

アメリカ合衆国 12203 ニューヨーク州 オールバニ フラー・ロード 257

## (72)発明者 ジャガンナタン、ヘマンス

アメリカ合衆国 12203 ニューヨーク州 オールバニ フラー・ロード 257

審査官 岩本 勉

## (56)参考文献

米国特許第 09773913 (U.S., B1)

米国特許第 09773708 (U.S., B1)

米国特許出願公開第 2017/0278951 (U.S., A1)

米国特許出願公開第 2017/0278943 (U.S., A1)

特開 2017-208567 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

H 01 L 29 / 78

H 01 L 21 / 336

H 01 L 21 / 8234

H 01 L 21 / 8238

H 01 L 29 / 417

H 01 L 29 / 41

H 01 L 29 / 423