(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7106265号**

**(P7106265)**

(45)発行日 令和4年7月26日(2022.7.26)

(24)登録日 令和4年7月15日(2022.7.15)

(51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| G 0 9 G | 3/3275(2016.01) | F I | G 0 9 G | 3/3275       |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 G | 3/20 6 3 1 H |

| G 0 9 G | 3/3233(2016.01) |     | G 0 9 G | 3/20 6 4 1 P |

| H 0 1 L | 27/32 (2006.01) |     | G 0 9 G | 3/20 6 1 2 U |

| H 0 1 L | 51/50 (2006.01) |     | G 0 9 G | 3/3233       |

請求項の数 18 (全15頁) 最終頁に続く

(21)出願番号 特願2017-223186(P2017-223186)

(22)出願日 平成29年11月20日(2017.11.20)

(65)公開番号 特開2019-95527(P2019-95527A)

(43)公開日 令和1年6月20日(2019.6.20)

審査請求日 令和2年11月13日(2020.11.13)

(73)特許権者 502161508

シナプティクス インコーポレイテッド

アメリカ合衆国， 9 5 1 3 1 カリフォ

ルニア州， サンノゼ， マッケイ ドラ

イブ 1 1 0 9

(74)代理人 100205350

弁理士 狩野 芳正

(74)代理人 100117617

弁理士 中尾 圭策

(74)代理人 100182187

弁理士 高岡 正之

(72)発明者 降旗 弘史

東京都中野区中野4丁目10番2号 シ

ナプティクス・ジャパン合同会社内

(72)発明者 斎藤 進

最終頁に続く

(54)【発明の名称】 表示ドライバ、表示装置及び画像補正方法

**(57)【特許請求の範囲】****【請求項1】**

表示パネルに表示される第一のラインを表示するための第一の電流と前記第一のラインの後に表示される第二のラインを表示するための第二の電流との間の差に基づいて前記第一のラインの第一の画像データを補正する補正回路を備え、前記第一の電流と前記第二の電流の間の差に基づいて前記第一のラインの前記第一の画像データを補正することは、前記第二のラインの第二の画像データの平均画像レベルと、前記第一のラインを含み、前記第二のラインが表示される前に表示される複数のラインの画像データの平均画像レベルの平均値との差に基づいて前記第一のラインの前記第一の画像データを補正することを含む

表示ドライバ。

**【請求項2】**

前記補正回路は、前記第二の画像データの前記平均画像レベルと前記複数のラインの前記画像データの前記平均画像レベルの平均値との間の差に応じた補正量を記憶するように構成されたルックアップテーブルを備え、

前記第二のラインの前記第二の画像データの前記平均画像レベルと前記複数のラインの画像データの平均画像レベルの平均値との間の差に基づいて前記第一の画像データを補正することは、前記補正量に基づいて前記第一の画像データを補正することを含む

請求項1に記載の表示ドライバ。

**【請求項3】**

前記第二のラインの前記第二の画像データの前記平均画像レベルと前記複数のラインの前記画像データの前記平均画像レベルの前記平均値との間の差を算出するように構成された補間回路を更に備え、

前記ルックアップテーブルは、更に、記憶された前記補正量と計算された前記差に基づき算出後補正量を算出するように構成された

請求項 2 に記載の表示ドライバ。

**【請求項 4】**

ライン毎に画像データの平均画像レベルを算出するように構成された平均画像レベル演算回路と、

前記ライン毎の前記画像データの算出された前記平均画像レベルを記憶するように構成されたレジスタと、

を更に備える

請求項 1 に記載の表示ドライバ。

**【請求項 5】**

表示パネルに表示される第一のラインを表示するための第一の電流と前記第一のラインの後に表示される第二のラインを表示するための第二の電流との間の差に基づいて前記第一のラインの第一の画像データを補正する補間回路と、

前記表示パネルの複数のデータ線を駆動するように構成されたマルチプレクサと、

を備え、

前記補間回路は、前記データ線を駆動する順番と補正量とを対応づけたルックアップテーブルを含み、前記マルチプレクサを用いて前記データ線を駆動する順番に応じた補正量を前記ルックアップテーブルに基づいて算出し、前記算出された補正量で前記第一のラインの前記第一の画像データを補正するように構成された

表示ドライバ。

**【請求項 6】**

表示パネルに表示される第一のラインを表示するための第一の電流と前記第一のラインの後に表示される第二のラインを表示するための第二の電流との間の差に基づいて前記第一のラインの第一の画像データを補正する補間回路と、

ライン毎に画像データの平均画像レベルを算出するように構成された平均画像レベル演算回路と、

前記ライン毎の前記画像データの算出された前記平均画像レベルを記憶するように構成されたレジスタと、

を備え、

前記平均画像レベル演算回路が、入力画像データの第一の組の複数ラインが前記表示パネルに表示される前記第一のラインに変換されるとき、前記第一の組の複数ラインの前記入力画像データの平均画像レベルを算出するように構成され、

前記第一の電流と前記第二の電流との間の差に基づいて前記第一の画像データを補正することは、前記第一の組の複数ラインの前記入力画像データの平均画像レベルに基づき、前記第一のラインの前記第一の画像データを補正することを含む

表示ドライバ。

**【請求項 7】**

前記第一のラインの前記第一の画像データを補正することは、前記入力画像データの前記算出された平均画像レベルと前記第二のラインの第二の画像データの平均画像レベルとの間の差に基づいて前記第一のラインの前記第一の画像データを補正することを含む

請求項 6 に記載の表示ドライバ。

**【請求項 8】**

前記平均画像レベル演算回路は、前記入力画像データの第二の組の複数ラインが前記第二のラインに変換されるとき、前記第二の組の複数ラインの前記入力画像データの平均画像レベルを算出するように構成され、

前記第二の組の複数ラインは、前記第一の組の複数ラインから 1 ラインだけずれており、

10

20

30

40

50

前記第一のラインの前記第一の画像データを補正することは、前記第一の組及び前記第二の組の複数ラインの平均画像レベルに基づいて前記第一のラインの前記第一の画像データを補正することを含む

請求項 6 に記載の表示ドライバ。

【請求項 9】

前記第一のラインの前記第一の画像データを補正することは、前記第二の組の複数ラインの前記入力画像データの算出された前記平均画像レベルと、前記第一の組の複数ライン及び第三の組の複数ラインの前記入力画像データの算出された平均画像レベルの平均値とに基づいて、前記第一のラインの前記第一の画像データを補正することを含み、

前記第一の組の複数ラインが、前記第三の組の複数ラインから 1 ラインだけずれている

請求項 8 に記載の表示ドライバ。

10

【請求項 10】

更に、前記第一の組の複数ラインの少なくとも一のラインを記憶するように構成されたラインメモリを備える

請求項 6 に記載の表示ドライバ。

【請求項 11】

表示パネルと、

前記表示パネルに画像データを表示するように構成された表示ドライバと、

を備え、

前記表示ドライバは、前記表示パネルに表示される第一のラインを表示するための第一の電流と前記第一のラインの後に表示される第二のラインを表示するための第二の電流との間の差に基づいて前記第一のラインの第一の画像データを補正する補正回路を備え、

前記第一の電流と前記第二の電流の間の差に基づいて前記第一の画像データを補正することは、前記第二のラインの第二の画像データの平均画像レベルと、前記第一のラインを含み、前記第二のラインが表示される前に表示される複数のラインの画像データの平均画像レベルの平均値との差に基づいて前記第一のラインの前記第一の画像データを補正することを含む

20

表示装置。

【請求項 12】

表示パネルと、

30

前記表示パネルに画像データを表示するように構成された表示ドライバと、

を備え、

前記表示ドライバは、前記表示パネルに表示される第一のラインを表示するための第一の電流と前記第一のラインの後に表示される第二のラインを表示するための第二の電流との間の差に基づいて前記第一のラインの第一の画像データを補正する補正回路と、

前記表示パネルの複数のデータ線に接続されたマルチプレクサと、

を備え、

前記補正回路は、前記データ線を駆動する順番と補正量とを対応づけたルックアップテーブルを含み、前記ルックアップテーブルに基づき、前記マルチプレクサを用いて前記データ線を駆動する順番に応じた補正量を算出し、前記算出された補正量で前記第一のラインの前記第一の画像データを補正するように構成された

40

表示装置。

【請求項 13】

表示パネルと、

前記表示パネルに画像データを表示するように構成された表示ドライバと、

を備え、

前記表示ドライバは、前記表示パネルに表示される第一のラインを表示するための第一の電流と前記第一のラインの後に表示される、前記第一のラインを含む第二のラインを表示するための第二の電流との間の差に基づいて前記第一のラインの第一の画像データを補正する補正回路を備え、

50

前記補正回路が、更に、入力画像データの第一の組の複数ラインが前記表示パネルに表示される前記第一のラインに変換されるとき、前記第一の組の複数ラインの前記入力画像データの平均画像レベルを算出するように構成され、

前記第一の電流と前記第二の電流と間の差に基づいて前記第一の画像データを補正することは、前記第一の組の複数ラインの前記入力画像データの平均画像レベルに基づき、前記第一のラインの前記第一の画像データを補正することを含む

表示装置。

**【請求項 14】**

前記補正回路は、更に、前記入力画像データの第二の組の複数ラインが前記第二のラインに変換されるとき、前記第二の組の複数ラインの前記入力画像データの平均画像レベルを算出するように構成され、

前記第一のラインの前記第一の画像データを補正することは、前記第一の組及び前記第二の組の複数ラインの平均画像レベルに基づいて前記第一のラインの前記第一の画像データを補正することを含む

請求項 13 に記載の表示装置。

**【請求項 15】**

表示パネルに表示される第一のラインの第一の画像データを表示するための第一の電流と前記第一のラインの後に表示される第二のラインを表示するための第二の電流との間の差に基づいて前記第一のラインの第一の画像データを補正することを含み、

前記第一の画像データを補正することは、前記第二のラインの第二の画像データの平均画像レベルと、前記第一のラインを含み、前記第二のラインが表示される前に表示される複数のラインの画像データの平均画像レベルの平均値との間の差に基づいて前記第一のラインの前記第一の画像データを補正することを含む

画像補正方法。

**【請求項 16】**

表示パネルに表示される第一のラインの第一の画像データを表示するための第一の電流と前記第一のラインの後に表示される第二のラインを表示するための第二の電流との間の差に基づいて前記第一のラインの前記第一の画像データを補正することを含み、

前記第一のラインの前記第一の画像データを補正することは、

複数のデータ線を駆動する順番と補正量とを対応づけたルックアップテーブルに基づいて前記複数のデータ線を駆動する順番に応じた補正量を算出することと、

前記算出された補正量で前記第一のラインの前記第一の画像データを補正することと、

を含む

画像補正方法。

**【請求項 17】**

表示パネルに表示される第一のラインの第一の画像データを表示するための第一の電流と前記第一のラインの後に表示される第二のラインを表示するための第二の電流との間の差に基づいて前記第一のラインの前記第一の画像データを補正することと、

入力画像データの第一の組の複数ラインの前記表示パネルに表示されるべき前記第一のラインへの変換に基づいて、前記第一の組の複数ラインの前記入力画像データの平均画像レベルを算出することと、

を含み、

前記第一のラインの前記第一の画像データを補正することは、前記第一の組の複数ラインの前記入力画像データの前記平均画像レベルに基づいて前記第一のラインの前記第一の画像データを補正することを含む

画像補正方法。

**【請求項 18】**

前記入力画像データの第二の組の複数ラインの前記第二のラインへの変換に基づいて、前記第二の組の複数ラインの前記入力画像データの平均画像レベルを算出することを更に含み、

10

20

30

40

50

前記第二の組の複数ラインは、前記第一の組の複数ラインから1ラインだけずれており、前記第一のラインの前記第一の画像データを補正することは、前記第一の組及び前記第二の組の複数ラインの平均画像レベルに基づいて前記第一のラインの前記第一の画像データを補正することを含む

請求項17に記載の画像補正方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示ドライバ、表示装置及び画像補正方法に関する。

【背景技術】

【0002】

液晶表示パネルやOrganic Light Emitting Diode(OLED)表示パネル等の表示パネルは、例えば、ノートブックコンピュータやデスクトップコンピュータ、スマートフォンといった電子機器に用いられている。例えば、表示パネルに表示される表示データの階調値が大きく変動し、供給される電圧のゆらぎによって表示データにおける可視欠陥が生じる場合がある。

【先行技術文献】

【特許文献】

【0003】

【文献】特開2006-003880号公報

特開2006-163074号公報

特表2007-523377号公報

【概要】

【0004】

一の観点では、表示ドライバは、表示パネル上に表示される第一のラインの画像データを格納するラインメモリと、前記第一のラインの画像データを表示するときに前記表示パネルに流れる電流から、前記第一のラインの次に表示される第二のラインの画像データを表示するときに前記表示パネルに流れる電流への変化量に基づき、前記表示パネルに出力される前記第一のラインの画像データを補正する補正回路と、を備える。

【図面の簡単な説明】

【0005】

【図1A】一実施形態における表示装置の構成の一例を示すブロック図である。

【図1B】一実施形態における画素回路の構成の一例を示すブロック図である。

【図2】一実施形態における表示パネルに表示されるラインの一例を示す図である。

【図3】一実施形態における画像データの補正処理の概要の一例を説明するための図である。

【図4】一実施形態における補正回路の構成の一例を示すブロック図である。

【図5】一実施形態におけるAPLリングレジスタの構成の一例を示す図である。

【図6】一実施形態における画像データ補正LUTの構成の一例を示す図である。

【図7】一実施形態におけるMUX補正LUTの構成の一例を示す図である。

【図8】一実施形態におけるMUXの構成の一例を示す図である。

【図9】一実施形態における画像データの補正処理フローの一例を示す図である。

【図10】一実施形態の変形例における表示装置の構成の一例を示すブロック図である。

【図11】一実施形態の変形例におけるSPRモードにおけるAPL算出方法の一例を示す図である。

【詳細な説明】

【0006】

以下、実施形態について、図面を参照して詳細に説明する。なお、ここに開示された技術がこれら実施形態の詳細説明がなくとも当業者により実施され得ることは明らかである。また、以下において、説明を不要に複雑にすることを避けるため、周知の特徴を詳細には

10

20

30

40

50

説明していない。

**【 0 0 0 7 】**

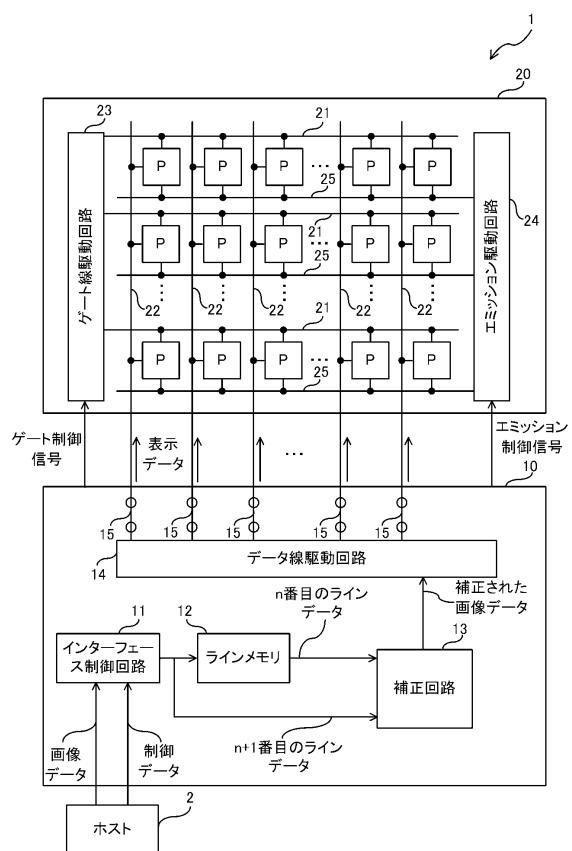

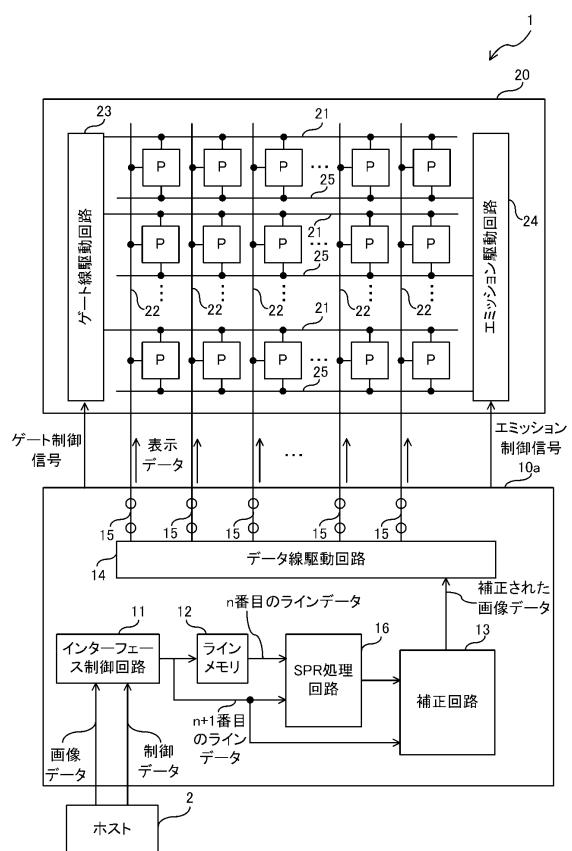

図 1 A は、一実施形態における表示装置 1 の構成を示すブロック図である。表示装置 1 は、表示パネル 2 0 及び表示ドライバ 1 0 を備える。

**【 0 0 0 8 】**

表示装置 1 0 は、ユーザに表示パネル 2 0 に表示される情報を提供する表示機能を有する。表示装置 1 0 は、表示パネルを備える電子機器の一例である。電子機器は、例えば、スマートフォン、ラップトップコンピュータ、ネットブックコンピュータ、タブレット、ウェブブラウザ、電子ブックリーダー、パーソナルデジタルアシスタント (PDA) といった携帯電子機器に限らない。例えば、電子機器は、表示パネルを備えるデスクトップコンピュータ又は表示パネルが用いられる自動車に搭載される表示機器等、あらゆるサイズ及び形状の機器であってもよい。また、タッチセンサを備え、指やスタイルス等の入力物体のタッチ検出が可能とされていてもよい。

10

**【 0 0 0 9 】**

表示パネル 2 0 は、例えば、Organic Light Emitting Diode (OLED) 表示パネルや液晶表示パネルである。表示パネル 2 0 は、ゲート線 2 1、データ線 2 2、ゲート線駆動回路 2 3、エミッション駆動回路 2 4、エミッション線 2 5 及び画素回路 P を備える。

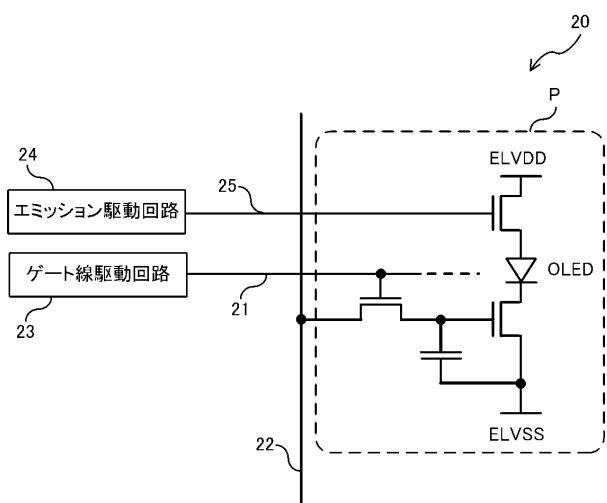

**【 0 0 1 0 】**

それぞれの画素回路 P は、図 1 B に示すように、ゲート線 2 1 とデータ線 2 2 とが交差する位置に設けられており、赤、緑、青のいずれかの色を表示する。各画素回路 P は、エミッション線 2 5 に接続されている。赤を表示する画素回路 P は、R サブピクセルとして用いられる。同様に、緑を表示する画素回路 P は G サブピクセルとして用いられ、青を表示する画素回路 P は B サブピクセルとして用いられる。

20

**【 0 0 1 1 】**

表示パネル 2 0 が OLED 表示パネルである場合、赤、緑、青を表示する画素回路 P はそれぞれ赤色、緑色、青色の光を発光する発光素子である OLED を備える。OLED は、エミッション駆動回路 2 4 からのエミッション信号に基づき、高電圧 E L V D D と低電圧 E L V S S との電位差が生じ、E L V D D から OLED に電流が流れることで OLED が点灯する。

30

**【 0 0 1 2 】**

図 1 A に戻り、ゲート線駆動回路 2 3 は、表示ドライバ 1 0 から受け取ったゲート制御信号に応じてゲート線 2 1 を駆動する。

**【 0 0 1 3 】**

エミッション駆動回路 2 4 は、表示ドライバ 1 0 から受け取ったエミッション制御信号に応じてエミッション線 2 5 を駆動する。

**【 0 0 1 4 】**

表示ドライバ 1 0 は、ホスト 2 から受け取った画像データ及び制御データに応じて表示パネル 2 0 を駆動して表示パネル 2 0 に画像を表示する。画像データは、表示すべき画像（元画像）の各画素の各サブピクセルの階調値を記述している。制御データは、表示ドライバ 1 0 を制御するためのコマンド及びパラメータを含んでいる。

40

**【 0 0 1 5 】**

ホスト 2 は、例えば、アプリケーションプロセッサ、Central Processing Unit (CPU)、Digital Signal Processor (DSP) である。

**【 0 0 1 6 】**

表示ドライバ 1 0 は、インターフェース制御回路 1 1、ラインメモリ 1 2、補正回路 1 3、データ線駆動回路 1 4 及びマルチプレクサ (MUX) 1 5 を備える。

**【 0 0 1 7 】**

インターフェース制御回路 1 1 は、ホスト 2 から受け付けた画像データを補正回路 1 3 に

50

転送する。インターフェース制御回路 11 は、制御データに含まれるコマンドに応答して表示ドライバ 10 の各回路を制御する。

#### 【 0 0 1 8 】

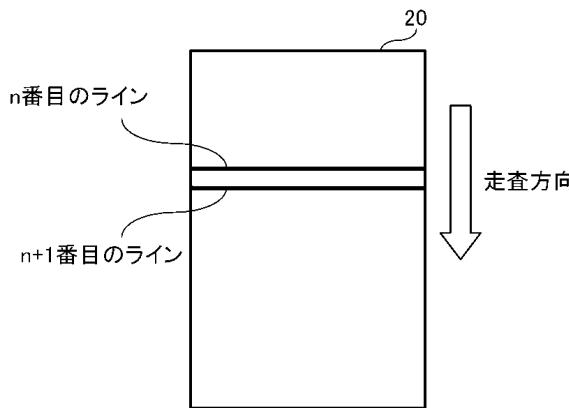

一実施形態では、インターフェース制御回路 11 は、こらから表示パネル 20 上に表示される n 番目のラインの画像データをラインメモリ 12 に出力し、n 番目のラインの次に表示される n + 1 番目のラインの画像データを補正回路 13 に出力する。実施形態において、n 番目のラインの画像データを n 番目のラインデータともいう。図 2 に示すように、例えば、表示パネル 20 に表示される n 番目のラインの次に、ゲート線 21 に対する走査方向において、n + 1 番目のラインが表示される。

#### 【 0 0 1 9 】

ラインメモリ 12 は、インターフェース制御回路 11 に入力された画像データを格納するメモリであり、例えば、Static Random Access Memory (SRAM) で構成される。ラインメモリ 12 は、例えば、表示ドライバ 10 が駆動する表示パネル 20 の 1 ラインの画像データを記憶する。

#### 【 0 0 2 0 】

補正回路 13 は、インターフェース制御回路 11 から受け付けた画像データに対して所望の画像データ処理を行う。

#### 【 0 0 2 1 】

補正回路 13 は、ラインデータをそれぞれ表示するときの表示パネル 20 に流れる電流の変化に基づき、表示パネル 20 を駆動する画像データを補正する。例えば、補正回路 13 は、ラインメモリ 12 から読み出される n 番目のラインデータと n + 1 番目のラインデータとに基づき、n 番目のラインデータに対する補正量を算出し、n 番目のラインデータを補正する。補正回路 13 は、補正された画像データを、データ線駆動回路 14 に出力し、表示パネル 20 に表示させる。補正回路 13 の動作の詳細については後述する。

#### 【 0 0 2 2 】

データ線駆動回路 14 は、補正された画像データの階調値に対応するソース電圧で各データ線 22 を駆動する。MUX 15 は、データ線 22 毎に設けられ、MUX 15 が駆動するとき、データ線 22 にソース電圧が供給される。複数の MUX 15 は、順次駆動される。

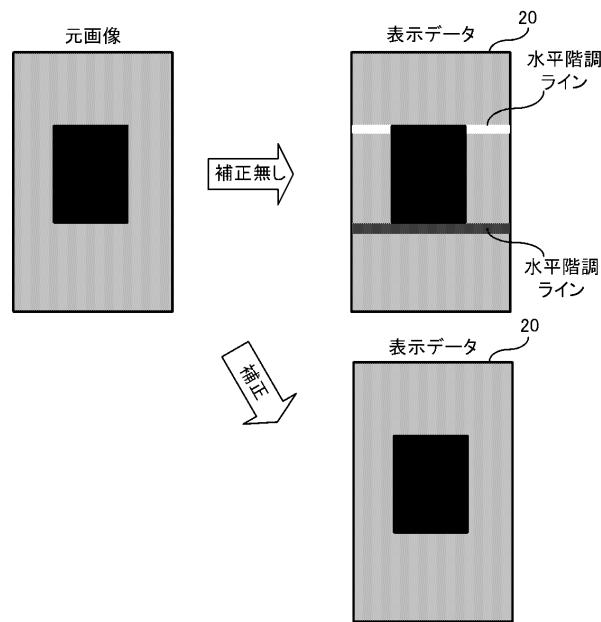

#### 【 0 0 2 3 】

例えば、元画像においてグレーから黒のように階調値が大きく変化するラインが含まれる場合、表示パネル 20 に流れる電流の変化が大きくなり、ELVDD の電源のゆらぎが発生し得る。一実施形態によれば、図 3 に示すような ELVDD の電源のゆらぎによって生じ得る水平階調ライン（疑似ライン）を発生させることなく、表示データを表示できる。水平階調ラインの発生に影響を与える ELVDD の電源のゆらぎを推定するため、一実施形態による画像補正処理によれば、これから表示する n 番目のラインデータを表示するときに表示パネル 20 に流れる電流から n + 1 番目のラインデータを表示するときに流れる電流への変化量に基づき、表示パネル 20 に出力される n 番目のラインデータを補正する。例えば、表示パネル 20 に流れる電流の変化量は、n 番目のラインデータの輝度の平均値である平均画像レベル (Average Picture Level (APL)) と次に表示する n + 1 番目のラインデータの APL を比較することで、APL の変化量を算出する。なお、ELVDD の電源のゆらぎは、複数のラインデータに影響を与えるため、例えば、n + 1 番目のラインデータの APL と比較する APL は、n + 1 番目のラインデータより前の所定数のラインデータの APL の平均値であってもよい。これにより、表示パネル 20 に流れる電流の変化に起因する電源のゆらぎによる複数ラインへの影響を補正できる。

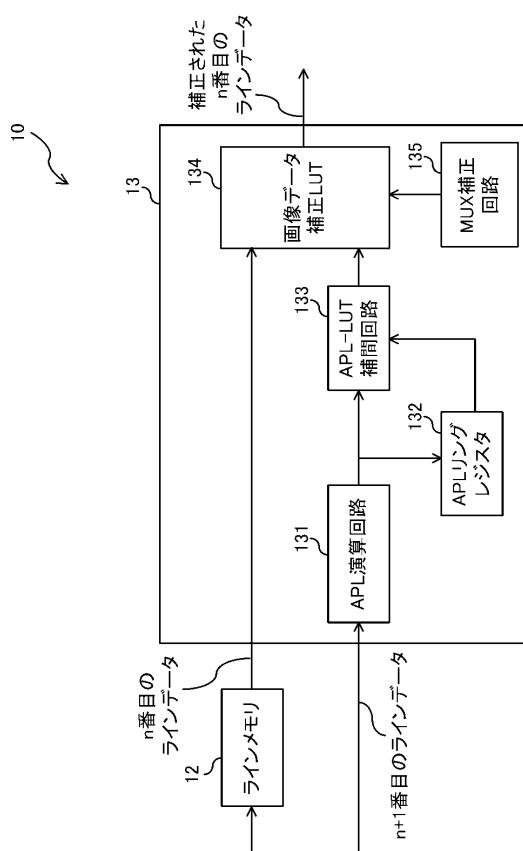

#### 【 0 0 2 4 】

図 4 は、一実施形態における補正回路 13 の構成を示すブロック図である。補正回路 13 は、APL 演算回路 131、APL リングレジスタ 132、APL - Look up Table (LUT) 補間回路 133、画像データ補正 LUT 134 及び MUX 補正回路 135 を備える。なお、APL 演算回路 131、APL リングレジスタ 132、APLUT 補

10

20

30

40

50

間回路 133、画像データ補正 LUT 134 及び MUX 補正回路 135 の全て又はいずれかは、補正回路 13 に含まれていなくてもよく、表示ドライバ 10 に含まれていればよい。

#### 【0025】

APL 演算回路 131 は、入力されるラインデータの APL をサブピクセル R、G、B 每に算出し、合算する。APL は、輝度の平均値を示す。実施形態では、次に表示される  $n + 1$  番目のラインデータの APL が算出される。APL 演算回路 131 は、算出した APL を APL リングレジスタ 132 及び APL-LUT 補間回路 133 に出力する。

#### 【0026】

APL リングレジスタ 132 は、 $n$  番目以前の複数のラインデータの APL を記憶している。APL リングレジスタ 132 は、 $n + 1$  番目のラインデータの APL が入力されると、最も古いラインデータの APL を削除し、 $n + 1$  番目のラインデータ APL を記憶する。

#### 【0027】

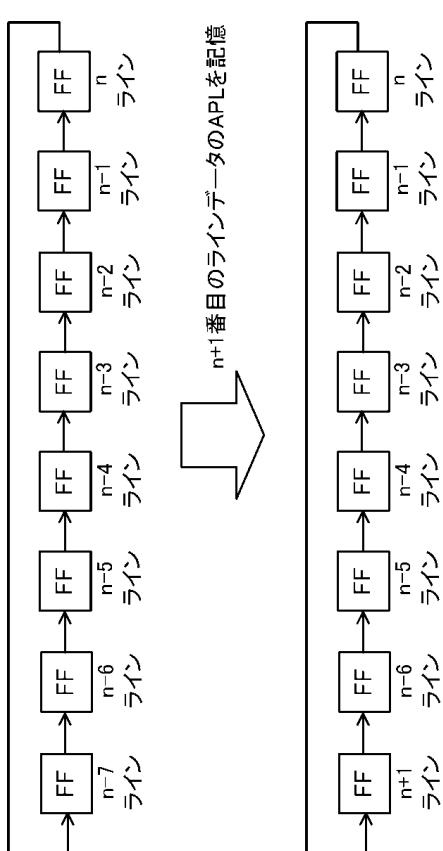

図 5 は、APL リングレジスタ 132 の構成の一例を示す図である。図 5 の上図に示すように、 $n + 1$  番目のラインデータの APL が APL リングレジスタ 132 に入力される前、APL リングレジスタ 132 は、例えば、 $n - 7 \sim n$  番目のラインデータのそれぞれの APL を、フリップフロップ (FF) を用いて記憶している。

#### 【0028】

次に、図 5 の下図に示すように、 $n + 1$  番目のラインデータの APL が APL リングレジスタ 132 に入力されると、APL リングレジスタ 132 は、最も古い  $n - 7$  番目のラインデータの APL に代えて、 $n + 1$  番目のラインデータの APL を記憶する。このように、図 5 では、APL リングレジスタ 132 は、合計 8 個のラインデータの APL を記憶する例を示したが、APL リングレジスタ 132 に記憶されるラインデータの APL の数は、一以上の任意の数であればよい。

#### 【0029】

画像データ補正 LUT 134 は、 $n + 1$  番目のラインデータより前の所定数のラインデータの APL の平均値から、これから表示される  $n$  番目のラインデータの次に表示される  $n + 1$  番目のラインデータの APL への変化量に応じた、ラインデータの補正量を記憶する。

#### 【0030】

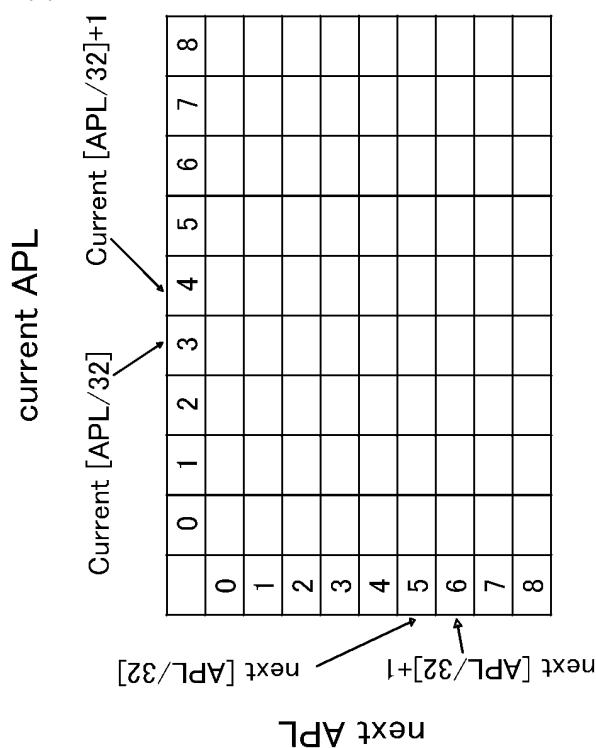

画像データ補正 LUT 134 は、図 6 に示すように、水平方向の current APL は、 $n$  番目のラインデータ及びそれ以前に表示されたラインデータの APL の平均値を示す。図 6 の垂直方向の next APL は、 $n + 1$  番目のラインデータの APL を示す。画像データ補正 LUT 134 には、current APL と next APL とに対応する補正量が示されている。

#### 【0031】

図 4 に戻り、APL-LUT 補間回路 133 は、 $n$  番目のラインデータの次に表示される  $n + 1$  番目のラインデータの APL と、 $n + 1$  番目のラインデータより前に表示された所定数のラインデータの APL の平均値との差を算出する。

#### 【0032】

例えば、5 ラインのラインデータにおいて、1 から 5 番目のラインデータ #0 ~ 4 の APL がそれぞれ、100、100、100、0、0 であり、ELVDD の電源のゆらぎが影響を与える得るライン数を 2 ラインとした場合、APL-LUT 補間回路 133 は次の動作を行う。この場合、電源のゆらぎが影響を与える得るライン数は 2 ラインであるため、2 つのラインデータの APL の平均値が算出される。

#### 【0033】

まず、 $n = 2$  の場合、つまり 2 番目のラインデータ #1 をこれから表示する場合、APL-LUT 補間回路 133 は、1、2 番目のラインデータ #0、1 の APL の平均値 ( $100 + 100 / 2 = 100$ ) と、3 番目のラインデータ #2 の APL 100 との差を算出する。この場合、差は 0 であるため、補正量は 0 となる。

#### 【0034】

$n = 3$  の場合、つまり 3 番目のラインデータ #2 をこれから表示する場合、APL-LUT

10

20

30

40

50

T補間回路133は、2、3番目のラインデータ#1、2のA P Lの平均値( $100 + 100 / 2 = 100$ )と、4番目のラインデータ#3のA P L0との差を算出する。この場合、差は100であり、図6に示す画像データ補正LUT134におけるLUT[current 100][next 0]で参照されるデータが補正量となる。

#### 【0035】

$n = 4$ の場合、つまり4番目のラインデータ#3をこれから表示する場合、A P L - L U T補間回路133は、3、4番目のラインデータ#2、3のA P Lの平均値( $100 + 0 / 2 = 50$ )と、5番目のラインデータ#4のA P L0との差を算出する。この場合、差は50であり、図6に示す画像データ補正LUT134におけるLUT[current 50][next 0]で参照されるデータが補正量となる。このように、実施形態では、1ライン毎に順次補正量が計算される。10

#### 【0036】

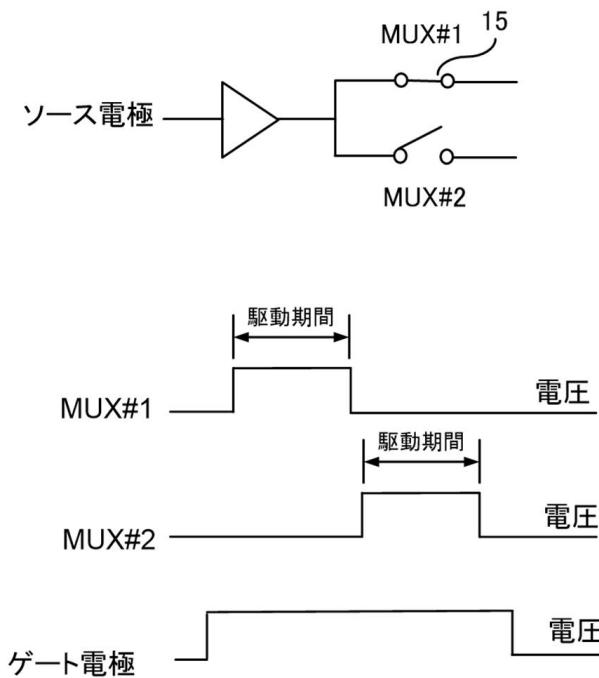

MUX補正回路135は、MUX15が駆動する順序に応じた補正量を算出し、A P L - L U T補間回路133に出力する。MUX補正回路135は、図7に示すMUX15の駆動順序と補正量とを対応づけたLUTを含んでもよい。

#### 【0037】

図8に示すように、例えば、MUX15がMUX#1及びMUX#2を含む場合、MUX#1がソース線22に電圧を送り、続いてMUX#2がデータ線22に電圧を送る。例えば、MUX#1による電圧の送信が始まる前に他のエミッションやO L E Dを駆動するトランジスタのV T キャンセルのような処理が実行されるため、MUX#1の駆動時間が十分でない場合もある。したがって、一実施形態では、MUX15が駆動する順序に応じて、画像データが補正されることにより、MUXの駆動順序に依存したE L V D D 摆れの補正を実現することが可能となる。MUX補正回路135に対して複数のMUX15が駆動する順序が入力されたとき、MUX補正回路135は、図7に示すLUTに基づき、MUX15の駆動順序に応じた補正量を算出する。MUX15の駆動順序に応じた補正量は、A P L - L U T補間回路133において算出された補正量に対して重みづけする係数として示されてもよい。20

#### 【0038】

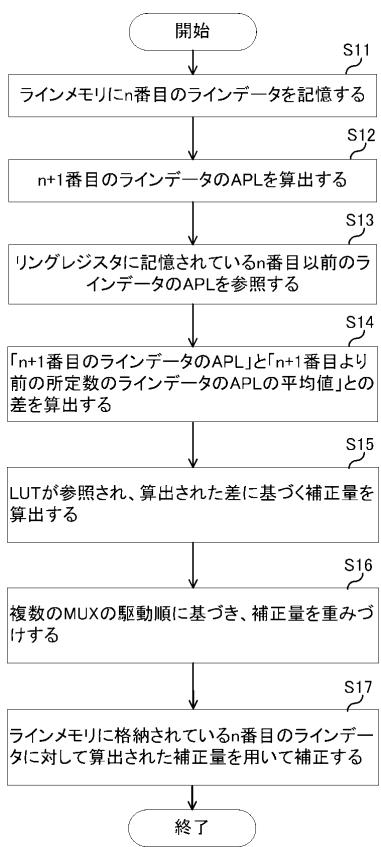

一実施形態における表示ドライバ10による画像データの補正処理は、図9のフローのように実行される。30

#### 【0039】

まず、ラインメモリ12にn番目のラインデータが記憶される(ステップS11)。

#### 【0040】

次に、A P L演算回路131は、次に表示されるn+1番目のラインデータのA P Lを算出する(ステップS12)。

#### 【0041】

A P L - L U T補間回路133は、A P Lリングレジスタ132に記憶されているn番目以前のラインデータのA P Lを参照し(ステップS13)、n+1番目のラインデータのA P Lとn+1番目より前の所定数のラインデータのA P Lの平均値との差を算出する(ステップS14)。40

#### 【0042】

画像データ補正LUT134において、算出された差に対応する補正量が算出される(ステップS15)。

#### 【0043】

さらに、MUX補正回路135は、複数のMUX15が駆動する順番に基づき、画像データ補正LUT134において算出された補正量を重みづけする(ステップS16)。ラインメモリ12に格納されているn番目のラインデータが、算出された補正量を用いて補正され、出力される(ステップS17)。

#### 【0044】

次に、一実施形態の変形例によれば、パネル構造に依存した画像データの補正処理が行わ50

れる。例えば、OLEDパネルでは、入力された画像データのピクセルを、サブピクセルレンダリング(SPR)処理により、擬似ピクセルにマッピングし、出力された画像を表示することがある。SPR処理において、ピクセルデータを画像の構造にマッピングするとき、複数ライン(例えば2ライン)で表示データの1ラインを表すことがある。

#### 【0045】

図10は、一実施形態の変形例における表示装置1aの構成を示すブロック図である。図10に示す表示装置1aは、図1Aに示した表示装置1と異なり、表示ドライバ10aがSPR処理回路16を備える。表示装置1aの構成では、SPR処理回路16と補正回路13とで一つのラインメモリ12を共用する。SPR処理回路16は、入力画像データの複数の入力ラインを、一つのラインに変換する。なお、一実施形態の変形例における表示装置1aにおいて、上述した表示装置1と同様な構成には同じ符号を付しており、詳細な説明は省略する。

10

#### 【0046】

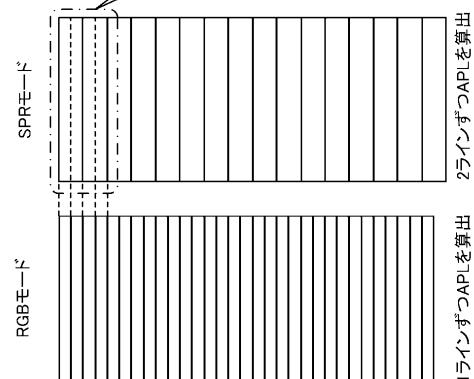

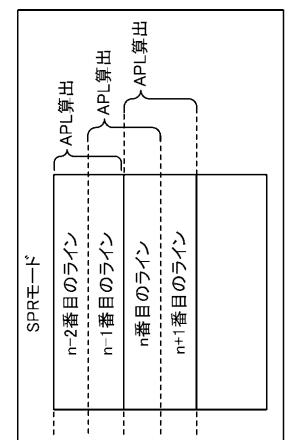

以下、SPR処理により、入力画像のサブピクセル2ラインを表示データの1ラインとして表す例を説明する。一実施形態の変形例では、次に表示されるラインデータより前に表示された所定数のラインデータのAPLの平均値を算出するとき、入力画像の2ライン単位かつ1ラインずつシフトさせてAPLを算出する。

#### 【0047】

図11は、一実施形態の変形例におけるAPLの算出方法の一例を示す図である。図11に示すように、RGBモードでは、1ラインずつAPLが算出される。一方、一実施形態の変形例におけるSPRモードでは、SPR処理により変換される前の入力画像の入力ラインである2ラインずつAPLが算出される。さらに、例えば、入力画像のn番目とn+1番目とのラインの画像データから変換された1ラインのラインデータが次に表示され、電源のゆらぎが表示データの2ラインに影響されるとき、次に表示されるラインデータより前のラインデータのAPLの平均値は、n番目とn-1番目とのラインデータのAPL及びn-1番目とn-2番目とのラインデータのAPLの平均値である。図11の例では、n-1番目のラインが2つのAPLを算出するときに重複して用いられ、APLは1ラインずつずらして算出される。このように、APL-LUT補間回路133は、次に表示されるラインに変換された入力画像データの複数の入力ラインから1ラインずつ走査方向の逆方向にずらした所定数の複数の入力ラインに基づき、次に表示されるラインより前に表示された画像データのAPLを算出する。

20

30

#### 【0048】

一実施形態では、上記変形例の2ラインずつAPLを算出する方法と1ラインずつAPLを算出する方法とを一つの表示ドライバにおいて切り替えて用いられてもよい。

#### 【0049】

以上、限られた数の実施形態についてのみ説明したが、本開示の利益を有する当業者は、本開示の範囲から逸脱することなく様々な他の実施形態及び変形例が考案され得ることを理解する。実施形態同士又はその変形例が組み合わせされてもよい。したがって、本明細書及び図面は、例示的開示に過ぎない。

#### 【符号の説明】

40

#### 【0050】

- 1、1a 表示装置(表示モジュール)

- 10、10a 表示ドライバ

- 11 インターフェース制御回路

- 12 ラインメモリ

- 13 補正回路

- 131 APL演算回路

- 132 APLリングレジスタ

- 133 APL-LUT補間回路

- 134 画像データ補正LUT

50

- 1 3 5 MUX 補正回路

1 4 データ線駆動回路

1 5 MUX

1 6 S P R 処理回路

2 0 表示パネル

2 1 ゲート線

2 2 データ線

2 3 ゲート線駆動回路

2 4 エミッショントransistor 駆動回路

2 5 エミッショントransistor 線

P 画素回路

【図面】

【図 1 A】

【図 1 B】

10

20

30

40

50

【図2】

【図3】

10

20

【図4】

【図5】

30

40

50

【図 6】

【図 7】

| MUX駆動順序 | 補正量    |

|---------|--------|

| 1       | MUX補正1 |

| 2       | MUX補正2 |

| :       | :      |

10

【図 8】

【図 9】

20

30

40

50

【図10】

【図11】

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

| F       | I     |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 1 1 D |

| G 0 9 G | 3/20  | 6 1 1 J |

| G 0 9 G | 3/20  | 6 4 2 A |

| H 0 1 L | 27/32 |         |

| H 0 5 B | 33/14 | A       |

東京都中野区中野4丁目10番2号 シナプティクス・ジャパン合同会社内

(72)発明者 能勢 崇

東京都中野区中野4丁目10番2号 シナプティクス・ジャパン合同会社内

審査官 西島 篤宏

(56)参考文献 特開2004-301964(JP,A)

特開平08-248920(JP,A)

特開2013-250505(JP,A)

特開2009-216801(JP,A)

特開2008-225036(JP,A)

(58)調査した分野 (Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

H 0 1 L 2 7 / 3 2

H 0 1 L 5 1 / 5 0