(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6505226号

(P6505226)

(45) 発行日 平成31年4月24日(2019.4.24)

(24) 登録日 平成31年4月5日(2019.4.5)

(51) Int.Cl.

H01L 33/08 (2010.01)

H01L 33/50 (2010.01)

F 1

H01L 33/08

H01L 33/50

請求項の数 19 (全 23 頁)

(21) 出願番号 特願2017-526124 (P2017-526124)

(86) (22) 出願日 平成27年11月18日 (2015.11.18)

(65) 公表番号 特表2017-538290 (P2017-538290A)

(43) 公表日 平成29年12月21日 (2017.12.21)

(86) 國際出願番号 PCT/GB2015/053496

(87) 國際公開番号 WO2016/079505

(87) 國際公開日 平成28年5月26日 (2016.5.26)

審査請求日 平成30年6月8日 (2018.6.8)

(31) 優先権主張番号 1420452.3

(32) 優先日 平成26年11月18日 (2014.11.18)

(33) 優先権主張国 英国(GB)

早期審査対象出願

(73) 特許権者 515046968

フェイスブック・テクノロジーズ・リミテッド・ライアビリティ・カンパニー

FACEBOOK TECHNOLOGY ES, LLC

アメリカ合衆国 カリフォルニア州94025, メンロ パーク, ウィロー ロード

1601

(74) 代理人 100105957

弁理士 恩田 誠

(74) 代理人 100068755

弁理士 恩田 博宣

(72) 発明者 ボナー、ジェームズ ロナルド

イギリス国 PA8 7BS アースキン

サンディーランズ アベニュー 48

最終頁に続く

(54) 【発明の名称】集積型カラーLEDマイクロディスプレイ

## (57) 【特許請求の範囲】

## 【請求項1】

集積型発光ダイオード(LED)マイクロディスプレイを製造する方法であって、光の波長を変化させることが可能な色変換器を提供するステップであって、

前記色変換器は、

導波路を形成するための未改質屈折率層間の改質屈折率層を含む基板と、

前記基板の前記改質屈折率層上に形成された色変換層と、

前記基板上に形成された透明層と、

前記色変換層と前記透明層との間に形成されたマスクとを含む、前記提供するステップと。

前記色変換器に接続され、電気接続を形成し、かつ前記色変換器に光をポンピングすることが可能なマイクロLEDアレイを提供するステップと、

電子駆動層の形態で前記マイクロLEDアレイ用のバックプレーン制御器を提供するステップとを含み、

前記色変換器の前記色変換層は、前記マイクロLEDアレイからのポンピングされた光よりも長い波長の光を生成し、生成された光を前記未改質屈折率層間の前記改質屈折率層によって形成された前記導波路を介して伝送する、方法。

## 【請求項2】

前記マイクロLEDアレイは、青色光または紫外(UV)光を前記色変換器にポンピングし、前記色変換器は、前記青色光またはUV光の一部を緑色光および赤色光に変換する、

10

20

請求項 1 に記載の方法。

**【請求項 3】**

前記色変換器が、前記色変換層および前記透明層とは反対側の前記基板の面上の不透明／反射構造を含む、請求項 1 に記載の方法。

**【請求項 4】**

前記色変換器が、前記色変換層と前記改質屈折率層との間のロングパスフィルタを含み、前記ロングパスフィルタは、前記色変換層によって変換された光を前記色変換層を通過させ、変換されていない光を再循環する、請求項 1 に記載の方法。

**【請求項 5】**

前記色変換層は、前記マイクロ L E D アレイの第 1 の部分のマイクロ L E D に結合された蛍光体または量子ドットまたは有機物質を含み、前記透明層は、前記マイクロ L E D の第 2 の部分のマイクロ L E D に結合された拡散層である、請求項 1 に記載の方法。 10

**【請求項 6】**

前記マスクは、不透明性または反射性であり、前記マスクは、前記未改質屈折率層間にさらに配置されている、請求項 1 に記載の方法。

**【請求項 7】**

集積型発光ダイオード (L E D) マイクロディスプレイであって、

光の波長を変化させることが可能な色変換器であって、前記色変換器は、

導波路を形成するための未改質屈折率層間の改質屈折率層を含む基板と、

前記基板の前記改質屈折率層上に形成された色変換層と、 20

前記基板上に形成された透明層と、

前記色変換層と前記透明層との間に形成されたマスクとを含む、前記色変換器と、

前記色変換器に接続され、電気的接続を形成し、前記色変換器に光をポンピングすることが可能なマイクロ L E D アレイと、

電子駆動層の形態の前記マイクロ L E D アレイ用のバックプレーン制御器と

を備え、

前記色変換器の前記色変換層は、前記マイクロ L E D アレイからのポンピングされた光よりも長い波長の光を生成し、生成された光を前記未改質屈折率層間の前記改質屈折率層によって形成された前記導波路を介して伝送する、集積型 L E D マイクロディスプレイ。 30

**【請求項 8】**

前記色変換層は、蛍光体、量子ドット、または有機物質のうちの少なくとも 1 つからなる、請求項 7 に記載の集積型 L E D マイクロディスプレイ。

**【請求項 9】**

前記基板は、ガラス、サファイア、シリコン、GaN、または炭化ケイ素で作製されている、請求項 7 に記載の集積型 L E D マイクロディスプレイ。

**【請求項 10】**

前記透明層は、青色光を出射させるか、拡散または散乱機能を代替的に提供する、請求項 7 に記載の集積型 L E D マイクロディスプレイ。

**【請求項 11】**

前記マスクが不透明／黒色または反射性である、請求項 7 に記載の集積型 L E D マイクロディスプレイ。 40

**【請求項 12】**

前記マイクロ L E D アレイが、レンズを含む光学的特徴部を含む、請求項 7 に記載の集積型 L E D マイクロディスプレイ。

**【請求項 13】**

前記光学的特徴部が凸形状であり、放射を最大にし、かつスペクトルクロストークを最小にする、請求項 12 に記載の集積型 L E D マイクロディスプレイ。

**【請求項 14】**

前記マイクロ L E D アレイは、n および p コンタクトを形成するように堆積されたボンディングパッドを含み、前記電子駆動層は、前記マイクロ L E D アレイの前記ボンディング 50

パッドに取り付けられるポンディングパッドを有する、請求項7に記載の集積型L E Dマイクロディスプレイ。

**【請求項15】**

前記マイクロL E Dアレイは、青色光または紫外(U V)光を前記色変換器にポンピングし、前記色変換器は、前記青色光またはU V光の一部を緑色光および赤色光に変換する、請求項7に記載の集積型L E Dマイクロディスプレイ。

**【請求項16】**

前記色変換器が、前記色変換層および前記透明層とは反対側の前記基板の面上の不透明/反射構造を含む、請求項7に記載の集積型L E Dマイクロディスプレイ。

**【請求項17】**

異なる色のサブ画素を有する複数の画素を有する発光ダイオード(L E D)マイクロディスプレイを提供する方法であって、

色変換器に光学的に結合されたマイクロL E Dアレイからの光を放射するステップであって、前記色変換器は、

導波路を形成するための未改質屈折率層間の改質屈折率層を含む基板と、

前記基板の前記改質屈折率層上に形成された色変換層と、

前記基板上に形成された透明層と、

前記色変換層と前記透明層との間に形成されたマスクとを含む、前記放射するステップと、

前記色変換器の前記色変換層によって、前記マイクロL E Dアレイの第1のマイクロL E Dからの光を、前記マイクロL E Dアレイから放射された光とは異なる波長を有する第2の光に変換するステップと、

前記色変換器の前記色変換層からの前記第2の光を、前記未改質屈折率層間の前記改質屈折率層によって形成された前記導波路を介して伝送するステップと、

前記色変換器の前記透明層によって、前記マイクロL E DアレイのマイクロL E Dからの光を伝達するステップとを含み、前記光および前記第2の光は、画素の異なる色のサブ画素を提供する、方法。

**【請求項18】**

前記色変換器は、前記ポンピングされた光を前記色変換層に伝送し、より長い波長の光を反射するための前記色変換層上のショートパスフィルタをさらに含む、請求項1に記載の方法。

**【請求項19】**

前記色変換器は、前記ポンピングされた光を前記色変換層に伝送し、より長い波長の光を反射するための前記色変換層上のショートパスフィルタをさらに含む、請求項7に記載の集積型L E Dマイクロディスプレイ。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、低消費電力の高輝度ディスプレイに関する。より詳細には、本発明は、集積型カラーL E Dマイクロディスプレイ、及び集積型カラーL E Dマイクロディスプレイを製造する方法に関する。

**【背景技術】**

**【0002】**

多くのカラーマイクロディスプレイが存在するが、従来技術のカラーマイクロディスプレイの多くには、多数の欠点がある。

O L E D、液晶、M E M Sなどの技術を使用したマイクロディスプレイの開発を報告する広範な文献がある。後者の2つは、完全に最高輝度の光源の外部に配置されたパターンジェネレータに基づいており、その結果、マイクロディスプレイを形成するために余分な部品が必要となる。さらなる基本的な欠点は、全ての画素が画像を表示するために使用されなくても、全ての画素が光でアドレスされなければならないので、電力損失が生じること

10

20

30

40

50

とである。このようなディスプレイのコントラスト比も損なわれる。

#### 【0003】

OLED技術は放射技術であり、簡単に言えば、蛍光発光層を取り囲むアノードおよびカソードに基づいている。これらの技術は、しばしば、小さな画素形成のためにカラーフィルタを有する白色光を使用する。その結果、RGBディスプレイにおける色域を達成するために、白色画素のスペクトル範囲の約60~70%が損失であるか、または不要になる。さらに、白色OLEDはモノクロOLEDよりも効率が悪いため、実際には放射光のわずか10~20%しか使用することができない。これは、全体的なOLED構造の効率性または光がどのようにして取り出されるかについての効率性が考慮されていない。

#### 【0004】

さらに、OLED構造は、より複雑であり、また、電子輸送層、正孔ブロッキング層および電子ブロッキング層のすべてが、厚さおよび屈折率が慎重に制御される。これは、電気的にドープされた電子輸送層および正孔輸送層が電荷注入を高め、かつ低い動作電圧を可能にするので、ディスプレイ性能を改善するために重要である。電荷ブロック層は、電荷キャリアを発光層内に閉じ込めるのを支援する。さらに、他の問題は、青色OLEDの波長領域における効率が低く、寿命が限られており、低輝度レベルと結合されていることが、ディスプレイの性能が根本的に制限されていることを意味する。

#### 【0005】

個々のLEDの表面実装ボンディングを提供する技術は存在する。典型的には、ピック・アンド・プレイス技術は大規模LEDにしか使用できない。したがって、ディスプレイの1インチあたりの画素数が制限される。また、画素あたり2つの電気コンタクトが必要である。前者の点については、マイクロLEDをピック・アンド・プレイスする技術が開発されている。しかしながら、電気コンタクトを提供するためには、小さな画素ピッチに対して後処理が必要とされるという課題がある。

#### 【0006】

このようなシステムの短所は、次のように要約することができる。

- ・製造 - フリップチップボンディング当たりの時間、各画素に関する同時nおよびp接続、および10μm未満の寸法で画素を配置する特性。

#### 【0007】

・半導体処理技術を用いたピック・アンド・プレイスマイクロLEDの後処理。第2のグローバルコンタクトを形成するためにLEDアレイの全域にコンフォーマルなコンタクト層を設けること。または、パターン形成されたコンタクト層が形成される平坦化構造を提供するために平坦化技術を組み合わせること。これを可能にするために光脱出用の透明コンタクト層またはコンタクト層の後工程のバターニングを提供する必要がある。制御パックプレーンへの電気的接続を提供する必要がある。

#### 【0008】

- ・性能 - 特に、駆動電流および温度に対する色の変化が小さい緑色LEDデバイスの選択。視覚応答のピーク付近の波長の小さな変化（すなわち、緑色）に対する眼の感受性のため、各緑色LEDの発光波長を狭い分布にする必要性。

#### 【0009】

本発明の少なくとも1つの態様の目的は、前述の問題の少なくとも1つまたは複数を回避または緩和することである。

本発明の少なくとも1つの態様の更なる目的は、低消費電力の高輝度ディスプレイ及びディスプレイを製造する方法を提供することである。

#### 【発明の概要】

#### 【0010】

本発明の第1の態様によれば、集積型LEDマイクロディスプレイを製造する方法であつて、

光の波長を変化させることができ可能な色変換器を提供するステップと、

色変換器に接続され、電気接続を形成し、かつ色変換器に光をポンピングする（pum

10

20

30

40

50

*p i n g*) ことが可能なマイクロLEDのアレイを提供するステップと、電子駆動層の形態でバックプレーン制御部を提供するステップとを含み、

マイクロLEDのアレイは、色変換器からの放射光よりも短い波長でポンピングされた光を生成し、それにより、より長い波長の光が生成される、集積型LEDマイクロディスプレイを製造する方法が提供される。

#### 【0011】

製造プロセスは、以下に記載される多数の異なる段階を含む。様々な実施形態において、図面を参照して説明することも明らかである。しかしながら、特定の実施形態は、これらの特定の詳細のうちの1つまたは複数を用いることなく、または他の既知の方法および構成と組み合わせて実施することができる。10

#### 【0012】

第1に、効率的な光生成のために最適化されたpおよびnドープGaN領域および層を含むGaN層が提供され、GaN層の上にオーミック電流拡散層および二酸化シリコン層が設けられている。GaN層の下方には、他の層よりもかなり厚い基板層が設けられている。オーミック電流拡散層は、20nmの厚さを有する。二酸化ケイ素の層は、約200nmの厚さを有する。基板層は、約200μmの厚さを有する。基板層は、サファイア、シリコン、GaNまたは炭化ケイ素のような任意の適切な材料とすることができます。オーミック電流拡散層の材料の例は、Ni/AuまたはNi/PtまたはAu/PtまたはPt/Ni/AuNi/AgまたはPdまたはITOまたはNi/ITOであり得る。20

#### 【0013】

プロセスは、画素または画素のアレイを形成するためのp-GaNの選択的な非活性化から開始することができる。これは次のように記載される。

- ・第1の拡散層（例えば、Ni/Au）がGaN-p層の上に堆積される。

#### 【0014】

・次に、パターン化されたマスク特徴部（例えば、フォトレジスト）が拡散層上に堆積される。

・構造がArなどのプラズマに露出されて拡散を除去した後、Cl<sub>2</sub>によりn-GaNに対して約1μmまでエッチングする（このプロセスは、プロセスの後の段階であり得る）30

・次に、パターン化されたマスク特徴部（例えばフォトレジスト）が画素形成のために堆積される。

#### 【0015】

・次に、層状構造をエッチング（プラズマまたはドライ）例えばArに晒して、マスクによって保護されていない領域から第1の拡散層を除去する。

- ・次に、構造をCHF<sub>3</sub>などのプラズマに晒す。

#### 【0016】

- ・次に、パターン化された特徴部の除去を実行する。

・次に、プラズマに晒された領域に高抵抗層を形成するための構造のアニーリングを行い、マスクによって保護された層において導電性（例えば、オーミックコンタクト）を維持して、画素または画素のアレイを形成する。40

#### 【0017】

代替的に、プロセスは、p-GaNの物理的エッチングを使用して画素または画素のアレイ形成とともに開始することができる。これは次のように記載される。

- ・第1の拡散層（例えば、Ni/Au）がGaN-p層の上に堆積される。

#### 【0018】

・次に、パターン化されたマスク特徴部（例えば、フォトレジスト）が拡散層上に堆積される。

・構造は、Cl<sub>2</sub>のようなプラズマに晒され、n-GaNに対して約1μmまでエッチングして画素を残す。50

## 【0019】

- ・次に、パターン化された特徴部の除去を実行する。

- ・その後、構造をアニーリングして画素または画素のアレイにおいて導電性を有するもの（例えば、オーミックコンタクト）を形成する。

## 【0020】

次に、画素の上の二酸化シリコンの層が除去され、次いで、二酸化シリコンの完全な層の形態で再堆積される。二酸化シリコンの完全な層は、約 200 nm の厚さを有し、かつ P E C V D などの任意の適切な技術を使用して堆積され得る。

## 【0021】

次に、画素の上の二酸化シリコンの完全な層の領域をエッチング除去して、オーミック電流拡散層への窓と、共通コンタクトが形成される窓とを形成する。この実施形態では、これは共通の n コンタクト領域である。不活性化プロセスに関して、パッシベーションを提供するために側壁に二酸化ケイ素を形成する必要がある。物理的にエッチングされた画素または画素アレイに対して、n - コンタクト領域が局所的にエッチングされるとき、側壁の表面不活性化が必要とされる。さらに、エッチングの領域に n コンタクト金属層が堆積される。n コンタクト金属は、Ti / Au であってもよく、約 50 / 250 nm の厚さを有してもよい。n コンタクト金属層は、グローバルコンタクトを形成し、かつ電気的機能および / または製造プロセスにおける更なるエッチングステップ（エッチングストップ）を制御するためのガイドとしての機能を有し得る。

## 【0022】

次に、ボンディングパッドが堆積されて n および p コンタクトが形成される。ボンディングパッドは、約 2 μm の高さおよび約 8 μm × 8 μm の断面を有し得る。同じ高さの p および n ボンディングパッドを有することが意図される。さらに、ボンディングパッドは、金属がどこにでも堆積されるようにマスキング層上に形成することができる。これにより、デバイスの化学研磨のための手段が提供されて、金属および誘電体平面を有する平坦な頂部層が提供される。このような頂部構造は、同じ高さで均一なボンディング手段（p および n ボンディングパッドスタック）を提供する。その結果、フリップチップ・バンプ・ボンディングおよびファン・デル・ワールス力に基づく直接ボンディングを含む（これに限定されない）ボンディング技術の範囲をバックプレーン制御部（CMOS、TFT または NMOS 層）に対する GaN に対して利用することができる。後者は、低温でかつ非常に小さいボンディング力でのボンディングが可能であるため、特に興味深い。LED アレイのサイズが増大するにつれて、必要とされる総ボンディング力は重要な特性となり、かつアレイサイズの物理的制限をもたらす可能性がある。また、低温ボンディングのために、アクティブマトリクス OLED (AMOLED) 制御バックプレーンと性質が類似している TFT バックプレーン構造を用いることができる。これにより、コストと複雑さが低減され、より大きな物理的寸法を有するディスプレイへのルートが提供される。

## 【0023】

シリコン製の一時的なウェハが GaN ウェハにボンディングされ得る。一時的なウェハは、約 500 μm の厚さを有し、かつ GaN 層よりもかなり厚い。

次に、基板層は、レーザーリフトオフのような任意の適切な技術によって除去され得る。基板層がシリコンである場合には、化学機械的研磨およびエッチングまたはこれらの技術の組み合わせが可能である。これは、全体的な設計に使用することができる、シリコン基板内にミクロフィーチャを形成する付加的な可能性を有する。

## 【0024】

次に、バッファまたは n - GaN 層をエッチングして光学的特徴部が好ましい実施形態ではマイクロレンズの形態で形成され得る。光学的特徴部は、放射を最大にし、かつ画素間の光学的クロストークを最小にするために凸形状であってもよい。光学的特徴部は、約 8 μm の幅を有し得る。

## 【0025】

代替例において、エッチングプロセスは、画素に近接して粗面化領域を形成してもよい

10

20

30

40

50

。深さ  $1 \mu\text{m}$  の粗面化された領域を用いて、光取り出しを改善することができる。

更なる代替例では、GaNピラーが形成され得るマトリクスエッチングプロセスが行われ得る。GaNピラーは、約  $2 \mu\text{m}$  の高さを有し得る。GaNピラーはまた、LED画素出力間の光学的分離を最大にして光学的クロストークを低減するために、先端が切り取られている形状が好ましい。

#### 【0026】

n側エッチングプロセスは、ウェハの他方側のnコンタクト金属層に対するエッチングにより適切なエッチングストップを提供することによって、正確に制御され得る。終点検出のようなリアルタイムプラズマモニタリング技術を用いることにより、エッチング深さをGaN量子ウェルの位置に関して正確に制御することができる。

10

#### 【0027】

更なる代替例では、nコンタクト層は、レンズの厚さを制御するためのエッチングストップとして使用することができる。終点検出は、レンズエッチング中にnコンタクト金属層まで同時に開口し、かつレンズ厚さの制御を提供するために使用されてもよい。

#### 【0028】

次に、導電性金属グリッドおよび/または不透明層を堆積する堆積ステップが行われ得る。導電性金属グリッドおよび/または不透明層は、nコンタクト抵抗を減少させるとともに、遮蔽効果を有する。金属グリッドおよび/または不透明層は、約  $200 \text{ nm}$  の厚さを有し、任意の適切な技術を用いて堆積されてもよい。

#### 【0029】

代替例において、ITO導電層を金属の代わりに堆積して、透明導電層を形成してもよい。適切なITOの厚さの選択は、光の透過率を増加させるための反射防止コーティングをもたらし得る。

20

#### 【0030】

更なる代替例では、GaNピラーが形成される場合、クロストークを最小にするために側壁を被覆するようにn金属の層でコーティングしてもよい。n金属の層は、約  $200 \text{ nm}$  の厚さを有し得る。

#### 【0031】

$\text{SiO}_2$ の層または任意の他の適切なタイプの単層または多層コーティングを、GaNレンズおよびn金属層の表面上に堆積させてもよい。これは、フレネル反射を減少させるので、GaN表面の保護および反射防止機能の両方を提供する。コーティングは、約  $80 \text{ nm}$  の厚さを有し得る。

30

#### 【0032】

更なる代替例では、光学的特徴部の湾曲した領域または粗面化された領域のみを誘電体コーティングで覆ってもよい。誘電体コーティングは、二酸化ケイ素から作製されてもよく、約  $80 \text{ nm}$  の厚さを有し得る。

#### 【0033】

更なる代替例では、コーティングを堆積してもよい。これは、多層誘電体コーティングであり得る。ショートパス波長フィルタ機能を提供する機能を有する1つのコーティングまたは追加のコーティングまたは層が単に設けられてもよい。ショートパスフィルタは、青色光がGaNを射出するが、より長い波長（すなわち、色変換層によって生成された赤色光または緑色光）を反射するように設計され得る。

40

#### 【0034】

プロセスはまた、色変換効率を向上させるとともに、コントラストの表示を改善するために、いくつかの実施形態において、サブ画素に隣接する高反射率層を有することができる色変換器の使用を必要とする。色変換器は、色変換層と、基板と、透明層と、マスクとを含む。色変換層は、蛍光体、量子ドット、有機物質、またはそれらの組み合わせとしてもよい。色変換層は、約  $1 \sim 20 \mu\text{m}$ 、好ましくは約  $1 \sim 10 \mu\text{m}$  の厚さを有し得る。基板は、ガラス、サファイア、シリコンまたは任意の他の適切な材料から作製され得る。青色光が色変換器を光学的にポンピングするために使用される場合、ディスプレイの青色サ

50

ブ画素の入射光を変換する必要はない。その結果、青色セルに何ら材料を設けないようにするか、シリコーンから作製され、かつ青色光を出射することができる透明層を設けるか、または赤色および緑色蛍光体と同様のビームプロファイルを提供する拡散または散乱機能を提供するようにしてもよい。マスクは、(一般にLCDディスプレイで使用される)不透明/ブラックマトリクス樹脂または反射性のものであってもよく、Au、AlまたはAgから作製され得る。

#### 【0035】

代替的な色変換器では、エッチングされたシリコン基板が設けられてもよい。色変換器は、色変換層、透明層およびエッチングされたシリコン領域を含み得る。

代替的な色変換器では、青色光を入射させるが、緑色および赤色などのより長い変換光を反射するショートパスフィルタが設けられ得る。

#### 【0036】

更なる代替例では、導波路のように動作するものとして記載することができる色変換器が設けられ得る。前述のように、色変換層、透明層、およびマスクが設けられる。加えて、不透明/反射フィーチャ、光導波機能を提供する改質屈折率透明層、および未改質屈折率層が設けられる。

#### 【0037】

更なる代替例では、ロングパスフィルタとして記載することができる色変換器が設けられる。色変換器は、色変換層の下方に位置するロングパスフィルタを有する。ロングパスフィルタは、変換された光を出射することができるが、青色の変換されていない光を再循環する。

#### 【0038】

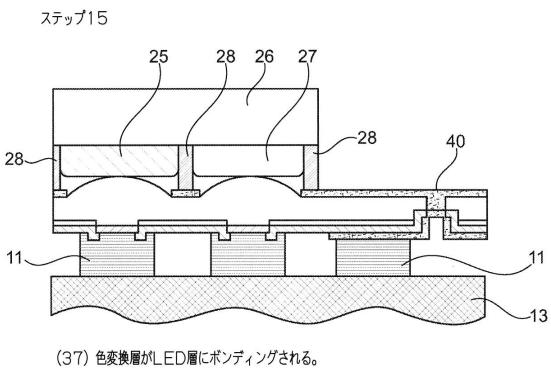

プロセスの次のステップでは、色変換器がLED層に搬送され、かつLED層と整列される。

次に、色変換器がデバイスの他の部分に取り付けられる。好ましい実施形態では、色変換器は青色光でポンピングされ、蛍光体層である赤色/緑色変換層が設けられている。代替的に、層は、量子ドットまたは透明/拡散層(青色)またはそれらの混合体であってもよい。ガラス基板から垂直下方に延在する不透明/黒色マスクまたは反射マスクが設けられ得る。反射マスクは、光を再循環させ、クロストークを最小にし、ディスプレイのコントラストを向上させる性能を有していることが好ましい。したがって、反射マスクは、フィルタが透過層の前に配置される場合、青色光を透過し、赤色光及び緑色光を反射する性能を有する。代替例において、フィルタが透過層の後に配置される場合、青色光は再循環され、赤色および緑色は透過される。

#### 【0039】

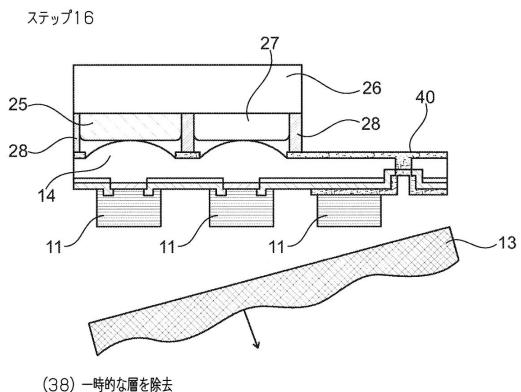

プロセスの次の段階で、一時的な層が除去され得る。

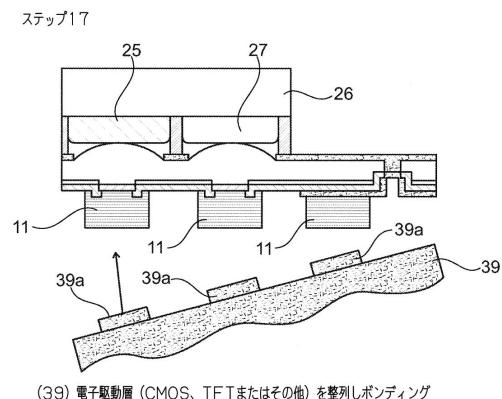

次に、LED上の金属ボンディングパッドに電子駆動層が搬送され、整列されて取り付けられる。ボンディング層スタックは、錫またはインジウムなどの低温はんだ材料、またはそれらの合金を含み得る。GaN p層の平坦性は、ファン・デル・ワールス力、水素結合および強力な共有結合を含む低温直接ボンディングを使用する可能性を提供する。電子駆動層は、CMOS、TFTまたはNMOSのNMOS層であってもよい。特に、直接ボンディング技術を使用する性能は、マトリクス有機発光ダイオード(AMOLED)マイクロディスプレイに用いられる薄膜トランジスタ技術を適合させる性能を許容する。

#### 【0040】

集積型カラーLEDマイクロディスプレイは、画素レイアウトの実施例を有する。一実施形態では、3つのサブ画素が $20 \times 20$ ミクロンのセル内に配置され、ボンディングパッドは画素から離れて配置される。

#### 【0041】

別の実施形態では、画素レイアウトの実施例は、各画素に含まれる4つのサブ画素を含み、ボンディングパッドが画素上に配置され得る。

集積型カラーLEDマイクロディスプレイは、赤色変換セル、緑色変換層、及び色変換

10

20

30

40

50

セルを有していない青色画素（透明／拡散層を含む）を含み得る。

**【0042】**

代替例の集積型カラーL E Dマイクロディスプレイでは、不透明／反射マトリクスが設けられ得る。

代替例の集積型カラーL E Dマイクロディスプレイでは、赤色変換セル、緑色変換セルおよび色変換セルを有していない青色画素のマトリクスが設けられてもよい。

**【0043】**

更なる代替例の集積型カラーL E Dマイクロディスプレイでは、赤色変換セル、緑色変換セル、色変換セルを有していない青色画素のマトリクス、および不透明／反射マトリクスが設けられてもよい。

10

**【0044】**

本発明の第2の態様によれば、集積型カラーL E Dマイクロディスプレイであって、光の波長を変化させることが可能な色変換器と、

色変換器に接続され、電気的接続を形成し、色変換器に光をポンピングすることが可能なL E Dと、

電子駆動層の形態のバックプレーン制御部と

を備え

L E Dは、色変換器からの放射光よりも短い波長で光をポンピングし、それにより、より長い波長の光が生成される、集積型L E Dマイクロディスプレイが設けられる。

**【0045】**

20

概して、本発明は、低消費電力の高輝度ディスプレイを提供する集積型カラーL E Dマイクロディスプレイを提供することにある。

集積型カラーL E Dマイクロディスプレイは、第1の態様で定義したように形成することができる。

**【0046】**

色変換器は、色変換層、基板、透明層およびマスクを含み得る。色変換層は、蛍光体、量子ドット、有機物質、またはそれらの組み合わせから作製され得る。色変換層は、約5～20μm、好ましくは約10～12μmの厚さを有し得る。基板は、ガラス、サファイア、シリコンまたは任意の他の適切な材料から作製され得る。透明層は、青色光を射出することができ、代替的には、拡散または散乱機能を提供し得る。マスクは、不透明／黒色または反射性であってもよい。

30

**【0047】**

L E Dは、レンズの形態である光学的特徴部を備えてもよい。光学的特徴部は凸形状であり、発光を最大にし、スペクトルクロストークを最小にする。

L E Dはまた、不透明／黒色マスクまたは反射性のマスクであって、Alまたは樹脂／ポリマーなどの金属から作製され得るマスクを含み得る。

**【0048】**

L E Dは、nおよびpコンタクトを形成するように堆積されたボンディングパッドを含み得る。ボンディングパッドは、約2μmの高さおよび約8μm×8μmの断面を有し得る。

40

**【0049】**

バックプレーン制御部は、ボンディングパッドを有する電子駆動層を含み得る。電子駆動層は、CMOS、TFTまたはNMOSのNMOS層であってもよい。

バックプレーン制御部のボンディングパッドは、L E Dのボンディングパッドに取り付けられる。

**【図面の簡単な説明】**

**【0050】**

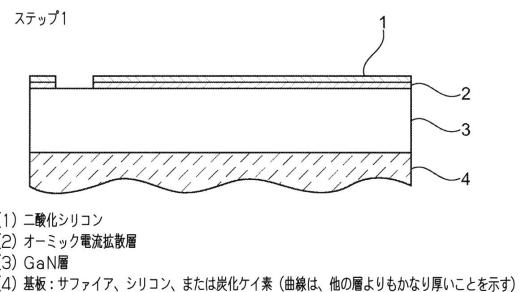

【図1】本発明の一実施形態による、上にオーミック電流拡散層および二酸化シリコン層があり、下にサファイア基板層があるGaN層を示す図。

【図2】本発明の一実施形態によるGaN層が二酸化シリコン層とオーミック電流拡散層

50

とからなるエッティングされた画素を有する代替の処理方法を示す図。

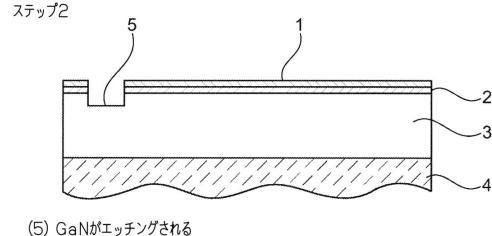

【図3】本発明の一実施形態による、図1に示すデバイスに対して実行されるエッティングプロセスを示す図。

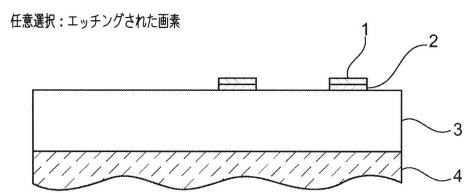

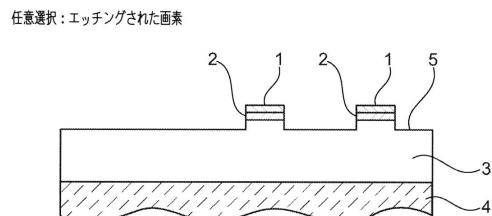

【図4】本発明の一実施形態による、画素の周りのGaN層がエッティングされて、エッティングされた領域を形成する図2に示すデバイスの代替のデバイスを示す図。

【図5】本発明の一実施形態による、画素を形成するためにオーミック電流拡散層および二酸化シリコン層がエッティングされるエッティングプロセスを示す図。

【図6】本発明の一実施形態による、導電領域および絶縁領域を生成するために使用されるプラズマ処理を示す図。

【図7】本発明の一実施形態による、画素上の二酸化シリコン層が除去され、次いで完全な層の形態で再堆積された二酸化シリコンの層を示す図。 10

【図8】本発明の一実施形態によるコンタクト窓を形成するために画素上の領域がエッティング除去された二酸化シリコンの完全な層を示す図。

【図9】本発明の一実施形態によるnおよびpコンタクトを形成するために堆積されたボンディングパッドを示す図。

【図10】本発明の一実施形態による除去される基板層を示す図。

【図11】本発明の一実施形態による光学的特徴部を形成するためにエッティングされるGaN層を示す図。

【図12】本発明の一実施形態による粗面化された領域を形成するための代替例のエッティング方法を示す図。 20

【図13】本発明の一実施形態による、マトリクスエッティングプロセスによりGaNピラーが形成される更なる代替例のエッティング方法を示す図。

【図14】本発明の一実施形態による、nコンタクト金属層に対するエッチを形成するためにGaN層が貫通してエッティングされる更なる代替例のエッティング方法を示す図。

【図15】本発明の一実施形態による、nコンタクト層がレンズの厚さを制御するためのエッティングストップとして使用される更なる代替例を示す図。

【図16】本発明の一実施形態による、導電性金属グリッドおよび/または不透明層が堆積される堆積ステップを示す図。

【図17】本発明の一実施形態による、透明導電層を形成するために、金属の代わりにITO導電層が堆積される代替例の堆積ステップを示す図。 30

【図18】本発明の一実施形態によるGaNピラーがn金属の層でコーティングされている更なる代替例を示す図。

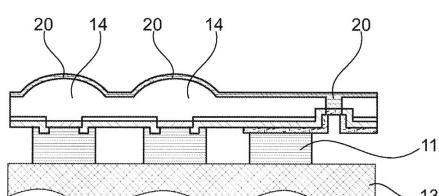

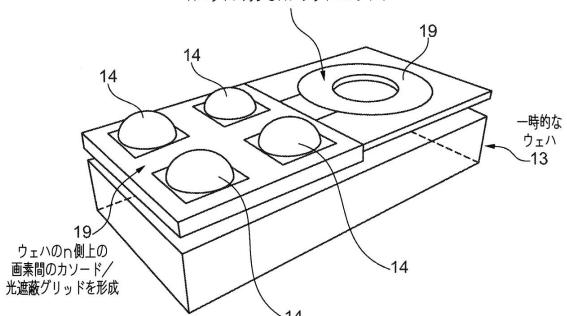

【図19】本発明の一実施形態による、図16に示すデバイスの上方斜視図。

【図20】本発明の一実施形態による、GaNレンズの表面およびn金属層の上にSiO<sub>2</sub>の層または任意の他の適切なタイプの単層または多層コーティングが堆積されるプロセスを示す図。

【図21】本発明の一実施形態による、光学的特徴部の湾曲した領域のみが誘電体コーティングで覆われている更なる代替例を示す図。

【図22】本発明の一実施形態による、ショートパス波長フィルタ機能を提供する機能を有するようにコーティングが堆積された更なる代替例を示す図。 40

【図23】本発明の一実施形態による色変換器を示す図。

【図24】本発明の一実施形態によるエッティングされたシリコン基板がある代替例の色変換器を示す図。

【図25】本発明の一実施形態によるショートパスフィルタである別の代替例の色変換器を示す図。

【図26】本発明の一実施形態による導波路のように動作するものとして記載された別の代替例の色変換器を示す図。

【図27】本発明の一実施形態によるロングパスフィルタとして記載された別の代替例の色変換器を示す図。

【図28】本発明の一実施形態による、LED層の上に搬送されて、LED層と整列され 50

る色変換器を示す図。

【図29】L E D層の他の部分の上に整列される色変換層を示す更なる図。

【図30】本発明の一実施形態による、デバイスの他の部分に取り付けられた色変換器を示す図。

【図31】本発明の一実施形態による、除去される一時的な層を示す図。

【図32】本発明の一実施形態による、金属ポンディングパッド上に搬送され、金属ポンディングパッドに整列される電子駆動層を示す図。

【図33】本発明の一実施形態によるポンディングパッドに取り付けられた金属ポンディングパッドを示す図。

【図34】本発明の一実施形態による画素レイアウトの実施例の平面図。 10

【図35】本発明の一実施形態による画素レイアウトの実施例の平面図。

【図36】本発明の一実施形態による画素レイアウトの更なる実施例の平面図。

【図37】本発明の一実施形態による画素レイアウトの更なる実施例の平面図。

【図38】本発明の一実施形態による、赤色変換セル、緑色変換層、及び色変換セルを有していない青色画素を示す図。

【図39】本発明の一実施形態による不透明／反射マトリクスが設けられた色変換セルを示す図。

【図40】本発明の一実施形態による赤色変換セル、緑色変換セル、および色変換セルを有していない青色画素のマトリクスを示す図。

【図41】本発明の一実施形態による、赤色変換セル、緑色変換セル、色変換セルを有していない青色画素のマトリクス、および不透明／反射マトリクスを示す図。 20

#### 【発明を実施するための形態】

##### 【0051】

本発明の実施形態を、添付の図面を参照して、例示的なものとして以下に説明する。

一般に、本発明は、低消費電力の高輝度ディスプレイを提供することにある。

図1～図41は、本発明によるマイクロディスプレイを製造する方法を示す。これについて説明する。

##### 【0052】

図1は、発光GaN層3を示し、発光GaN層3の上にはオーミック電流拡散層2と二酸化シリコン層1とが設けられている。GaN層3の下には、他の層よりもかなり厚い基板層4が設けられている。オーミック電流拡散層2は、約20nmの厚さを有する。二酸化シリコン層1は約200nmの厚さを有する。基板層4は、約200μmの厚さを有する。基板層4は、サファイア、シリコン、GaNおよび炭化ケイ素のような任意の適切な材料とすることができます。オーミック電流拡散層2の材料の例は、Ni/AuまたはNi/PtまたはAu/PtまたはPt/Ni/AuNi/AgまたはPdまたはITOまたはNi/ITOである。 30

##### 【0053】

図2は、GaN層3が、二酸化シリコン層1およびオーミック電流拡散層2を含むエッチングされた画素を有する代替のプロセス方法を示す。これは、LED画素を形成するための標準技術である。図2では、典型的には、最終画素寸法と同じサイズになる拡散層2が画定される。 40

##### 【0054】

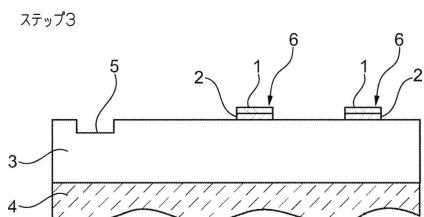

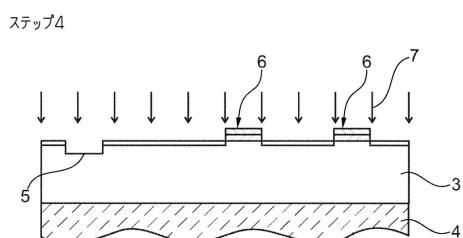

図3では、GaN変形プロセスである図1に示されたデバイスに対するエッチングプロセスが実行される。エッチングにより、GaN層3がエッチングされたエッチング領域5が生成される。エッチングプロセスは、任意の適切なエッチングプロセスを使用して実行され、好ましくは、CF<sub>3</sub>を使用するプラズマエッチングによって実行されるが、ウェットエッチングなどの他の技術を使用することができます。n材料へのエッチングは、CIを用いたプラズマエッチングを用いて行うことができる。

##### 【0055】

図4では、図2に示すデバイスの代替デバイスが、画素の周りのGaN層3においてエ

50

ツチングされて、エッチングされた領域 5 が形成される。

図 5 に示すように、画素形成を可能にするためにマスクが次に適用される。オーミック電流拡散層 2 および二酸化シリコン層 1 がエッチング除去されて画素 6 が形成される更なるエッチングプロセスがある。エッチングプロセスは、 $\text{CHF}_3$  等の任意の適切なプラズマエッチングプロセスを用いて実行される。画素 6 は、マトリクス状に形成することができる。これにより、 $0.5 \mu\text{m}$  から  $100 \mu\text{m}$  の寸法を有する画素が残る。典型的な寸法は、約  $3 \mu\text{m}$  である。

#### 【 0 0 5 6 】

図 6 に示すプロセスステップでは、導電領域および絶縁領域を生成するために使用されるプラズマ処理 7 がある。保護されていない GaN は、例えば  $\text{CHF}_3$  等のプラズマの GaN 改質プロセスに晒される。その後、パターン化された特徴部の除去に続いて、構造のアニーリングを行って、プラズマに晒された領域に高抵抗層が形成され、一方、マスクによって保護された層において導電性（例えば、オーミックコンタクト）が維持されて、画素または画素のアレイが形成される。

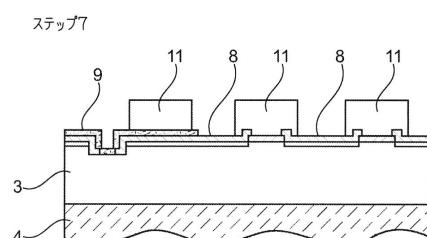

#### 【 0 0 5 7 】

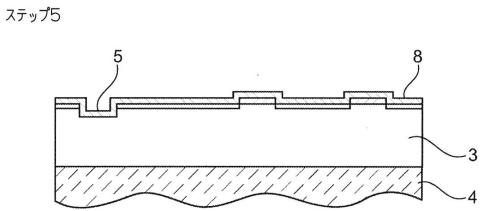

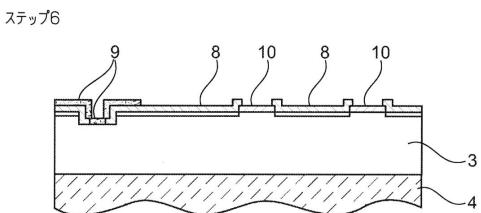

図 7 において、マスク層が形成される。画素 6 の上部の二酸化シリコン層 1 が除去され、フォトレジストのみまたは誘電体（例えば、上部にフォトレジストを有して  $\text{SiO}_2$  がパターニングされた  $\text{SiO}_2$ ）の完全な層 8 の形態で再堆積される。

#### 【 0 0 5 8 】

図 8 において、n コンタクト領域および拡散材料の上のマスクが開口される。次いで、導電性コンタクトが例えば、Ti : Au または他の組み合わせで堆積される。n コンタクト領域におけるエッチング側壁は、p - n 接合の両端の短絡を防止するために側壁上に電気絶縁層を有していることは明らかである。画素 6 の上の二酸化シリコンの完全な層 8 の領域がエッチング除去されて、コンタクトを形成するために下方にあるオーミック電流拡散層 2 へのコンタクト窓 10 が形成される。さらに、n コンタクト金属層 9 がエッチングの領域 5 に堆積される。n コンタクト金属層 9 はグローバルコンタクトを形成し、かつ電気的機能および / または製造プロセスにおけるさらなるエッチングステップを制御するためのガイドとしての機能を有する。

#### 【 0 0 5 9 】

図 9 において、ボンディングパッド 11 が堆積されて n コンタクトおよび p コンタクトを形成する。これは、同じマスキング層または代替的に新たなマスクを使用することができる。p ボンディングパッドおよび n ボンディングパッドは、同じ高さを有するという利点を有し、したがって、LED アレイに対するボンディングの成功確率が改善される。n パッドのエッチング深さは、後のプロセス（すなわち、GaN 側からエッチングし、レーザーリフトオフ後に露出された状態）のための正確なエッチングトップと、ウェハの裏面上の分散した電気コンタクトに対する接続を提供する手段との両方として使用することができる。さらに、ボンディングパッド金属を形成するためのマスク層は、トポロジー（topology）のない層を提供することができ、そのようなプロセスとして、CMP（化学機械的研磨（ダマシン））等を使用して、マスク層の上部に対して金属を平坦化することができる。この研磨プロセスにより、平坦なボンディング面の特性を有することができる。その結果、フリップ・チップ・バンプ・ボンディング（熱音波または熱圧縮）、または直接ボンディングまたはバックプレーン（例えば CMOS、TFT または NMOS 層）に対する機械的および電気的結合を形成する他の技術を含むが、これに限定されない一連のボンディング・プロセスを使用することが可能である。

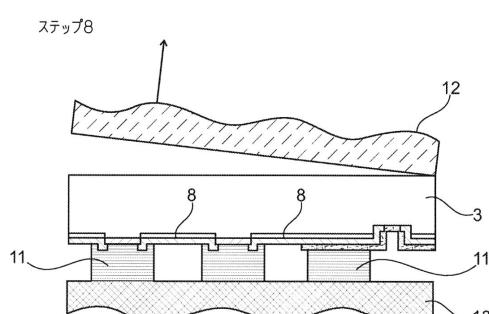

#### 【 0 0 6 0 】

図 10 に示すように、基板層 4 は、レーザーリフトオフなどの任意の適切な技術によって除去される。次いで、基板層 4 は、シリコーン化学機械的研磨およびシリコーンに対するエッチングを受ける。基板（サファイアなど）上の GaN は、基板層に接触している GaN 表面が一時的なウェハに結合される。GaN 層を基板から分離するために、業界標準技術を使用することができる。この特定の例では、レーザーリフトオフが使用される。代

10

20

30

40

50

替的に、シリコンまたはGaNを除去するためにCMPを使用することができる。これは、基板内に特徴部をエッティングすることができるよう、基板のエッティングと組み合わせられる。後に(図13)示すように、Siからピラーを残して、サブ画素間の分離を提供することができる。一時的なウェハ13の厚さは、GaN層3よりもかなり厚い。

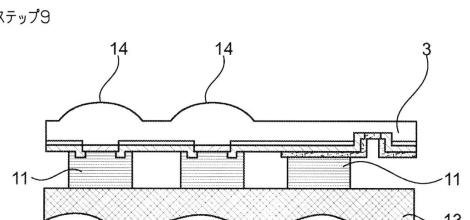

#### 【0061】

図11では、GaN層が裏面上に露出されるので、この構造内に一連の特徴部を形成することができる。これは、より多くの光を取り出す手段および/またはサブ画素間の光学的クロストークを減少させる特徴部を提供する手段を提供することができる。GaN層3は、エッティングされて、レンズの形態の光学的特徴部14が形成される。光学的特徴部14は、凸形状であり、かつ放射を最大にし、スペクトルクロストークを最小にする。反射防止膜として機能するようにSiO<sub>2</sub>等の特徴部上に層を堆積することも可能である。この特定の特徴部では、光取り出しを増加させ、サブ画素間の光学的クロストークを低減するために、レンズが形成される(高さはエッティングストップを用いて正確に決定され得る)。

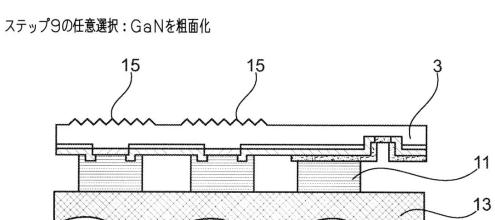

#### 【0062】

図12に示すように、代替例では、エッティングを用いて粗面化領域15を形成することができる。粗面化領域15は、光取り出しを改善するために用いることができる。この場合、散乱面がエッティングによって形成される。図11と同様に、1つまたは複数の層を堆積させて、フレネル反射を低減することができる。

#### 【0063】

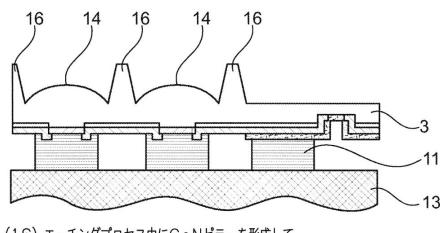

図13は、マトリクスエッティングプロセスにおいて、GaNピラー16が形成される更なる代替例を示す。図10で説明したように、ピラー16は光取り出し特徴部(この例ではレンズ)の間に形成することができる。これは、標準的な技術を用いて光取り出し機能と同時にGaN内に形成することができる。代替的に、ピラー16は、元の基板(図10に記載)に形成するか、または色変換基板(図23に記載)に形成することができる。ピラー16は、技術に関係なく理想的には滑らかな表面と高反射性の構造を有する。

#### 【0064】

図14に示すプロセスは、GaN層3が貫通してエッティングされて、エッティングされた領域5のnコンタクト金属層9に対するエッティングされた領域17を形成する更なるエッティングプロセスを含む。この特定の例では、光取り出し特徴部(レンズ)およびn開口を同時に形成することができる。エッティングは、任意の適切なエッティング技術によって行われる。

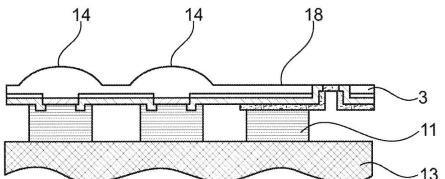

#### 【0065】

図15は、nコンタクト層9がレンズの厚さを制御するためのエッティングストップとして使用される代替例を示す。レンズエッチ18の間に終点検出を使用して、nコンタクト金属層9にまで貫通する開口の形成と、レンズ厚さの制御を提供すること同時に行う。図9に記載されているように、図14のプロセスの好ましい実施形態は、レンズのエッティング深さ、したがってQW層への近接度を正確に制御するように、nコンタクトをエッティングストップとして使用できることである。

#### 【0066】

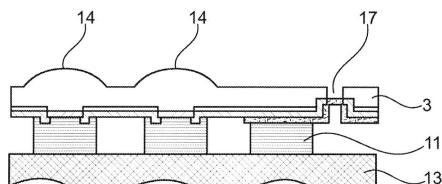

図16は、導電性金属グリッドおよび/または不透明層19を堆積する堆積ステップがあることを示す。これは、図9で説明したもの、および露出したGaN面上に分散され電気コンタクトを形成するために記載された技能と同様である。この場合、これは、ボンディングパッドと導電性GaN面との間に電気的ブリッジを形成する。この場合、不透明導体が使用される。結果として、これは光取り出し特徴部上に堆積されない。導電性金属グリッドおよび/または不透明層40は、バイアスを低減し、かつ遮蔽効果を有する。

#### 【0067】

図17は、金属の代わりにITO導電層20を堆積させて透明導電層20を形成する代替例を示す。適切なITO厚さの選択は、反射防止コーティングを形成することができる。図16と同様に、分散したnコンタクトを形成することができる。しかしながら、この

10

20

30

40

50

場合、透明なITO層を表面全体に均一に堆積させることができる（光取り出し特徴を覆わないようにパターン化することもできる）。これは、フレネル反射を低減するような厚さを有するように設計することもできる。

#### 【0068】

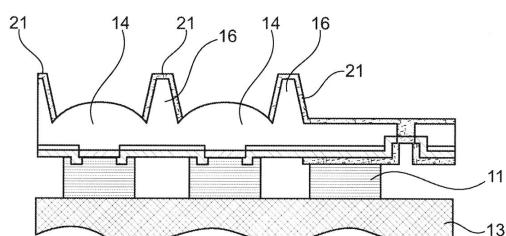

図18は、GaNピラー16がn金属の層21でコーティングされ、クロストークを最小に抑えるために側壁を被覆するさらなる代替例である。これは、図10と図17との組み合わせであり、金属をパターン化して分散された電気コンタクトを提供し、かつ反射性ピラーを提供することができる。

#### 【0069】

図19は、光取り出し特徴部、エッチングストップ、分散したnコンタクト、およびシリコン等の一時的なキャリアウェハにすべて結合されたものを形成する原理を説明するための図である。これは完成したGaNチップを集約し、その後、バックプレーン制御基板および色変換基板に統合することができる。

#### 【0070】

図20では、SiO<sub>2</sub>または任意の他の適切なタイプの単層または多層コーティング22が、GaNレンズ14およびn金属層19の表面上に堆積される。これは、保護および反射防止機能の両方を提供する。

#### 【0071】

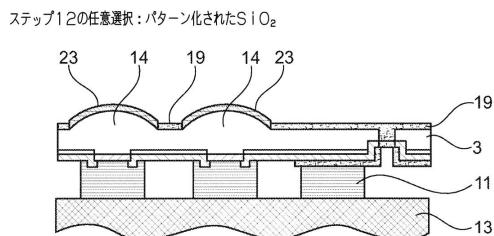

図21において、光学的特徴部14の湾曲した領域（または粗面化された領域15）のみが誘電体コーティング23で覆われているさらなる代替例がある。パターニングは、光取り出し領域の上に堆積するためにのみ使用される。

#### 【0072】

図22において、コーティング24a、24bが堆積されるさらなる代替例がある。よって、ここでは、多層誘電体コーティングが設けられる。ショートパス波長フィルタ機能を提供する機能を有する1つのコーティングまたは追加のコーティングまたは層が単に設けられてもよい。コーティング24a、24bは、光学的特徴部14のみを被覆するようにパターン化されるか、または表面を完全に覆ってもよい。ショートパスフィルタは、青色光がGaNを出射できるが、より長い波長（すなわち、色変換層によって生成された赤色光または緑色光）を反射するように設計され得る。図20および図21と同様に、本技術の大きな利点の1つは、多くの異なる層を光取り出し領域上に堆積できることである。この特定の構成では、ショートパスフィルタが使用される。これにより、ポンピング波長領域（例えば、青）の光を効率よく透過させることができる。ショートパスフィルタは、GaN表面に戻ってくる変換された光がエンドユーザの方向に出射する確率が高くなるように、より長い波長、すなわち緑色および赤色を反射する。

#### 【0073】

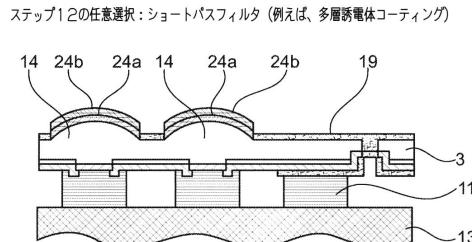

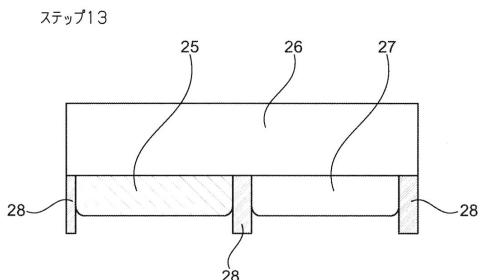

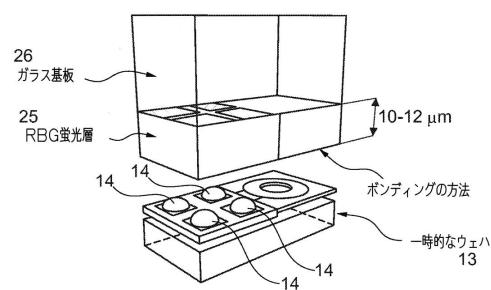

図23において、GaN層が準備され、次の段階で色変換器領域を形成することを示している。色変換器をGaN表面上に配置することができるが、別の基板を使用して柔軟性を向上させることが好ましい方法である。この場合、色変換器は、蛍光体、量子ドット、有機物質またはそれらの組み合わせであってもよい。色変換器基板は、ガラス、サファイア、シリコーン等のような材料の範囲とすることができる。この場合、各色変換器はサブ画素を提供し、かつ光学的にポンピングされる（好ましくは青またはUV光）。青色ポンピング波長が使用される場合、青色サブ画素は色変換物質を有さないが、同様の発光特性（例えば、ビームの発散）を有するように色変換器を模倣するための材料を有する。各LEDポンピングがUVの場合、赤、緑、青の色変換器が設けられる。コントラストを改善し、隣接する画素への光漏れを防止するために、サブ画素間にもマトリクスが形成される。これは、ブラックマトリクスまたは反射構造であってもよい。典型的には、マトリクスは色変換基板上に形成される。色変換器は、色変換層25、基板26、透明層27およびマスク28を含む。基板26は、ガラス、サファイア、シリコンまたは任意の他の適切な材料から作製され得る。

#### 【0074】

10

20

30

40

50

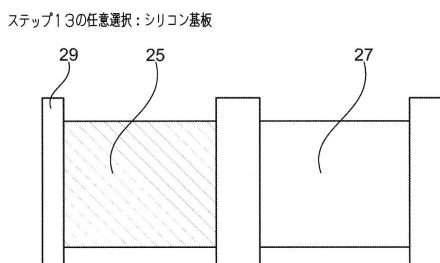

図24は、色変換領域用のマトリクスを形成するための任意選択を示す。シリコン基板上のGaNのルートが使用される場合、シリコン基板を容易に研磨し、かつエッチングすることが可能である（サファイアまたはSiC等の他の基板の場合、これははるかに困難なプロセスである）。その結果、湿式エッチングまたは乾式エッチング性能を用いてシリコン中にマトリクスをエッチングすることが可能である。どちらのエッチング技術を用いても、高いアスペクト比（即ち、構造の高さ対幅）を有するマトリクスを形成することができる。シリコンは、可視波長領域の光を吸収し、かつコントラストを高める。シリコンマトリクスを金属化して反射を提供し、かつ光変換／出力を向上させることも可能である。色変換器は、色変換層25、透明層27およびエッチングされたシリコン領域29を含む。

10

#### 【0075】

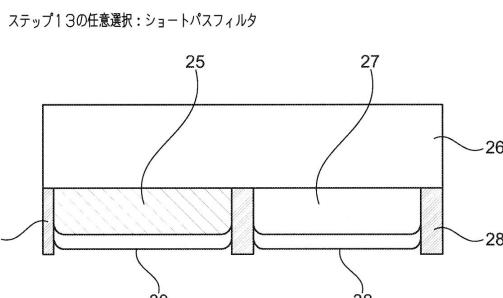

図25は、更なる代替例の色変換器である。性能を向上させるために、色変換器の層上にフィルタを含むようにすることができ、ショートパスフィルタは、青色光を透過し、かつより長い波長（即ち、緑色および赤色）を反射する。説明を簡単にするために、多層コーティングを全てのセル上に形成することができる。その結果、本質的に等方性である変換された光は、反射され、意図された方向に出射する。青色発光画素の場合、フィルタを有することが適切である場合とそうでない場合とがある。UV光でポンピングする場合、フィルタは、すべてのセルに配置され、かつUVポンピングを透過するが、長波長を反射する特性を有する。

#### 【0076】

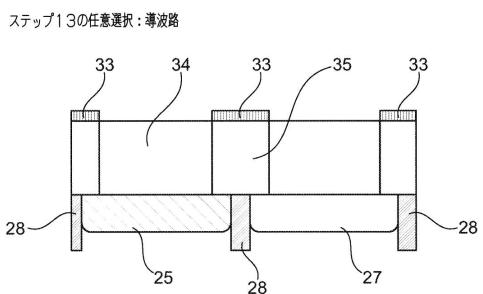

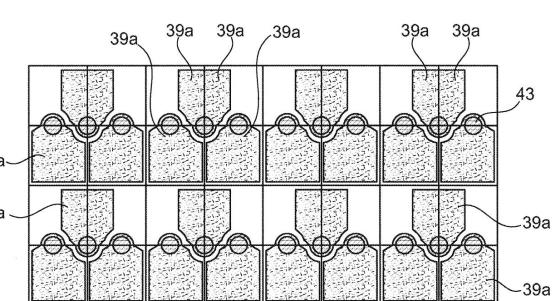

図26は、導波路のように動作するものとして説明される更なる代替例の色変換器である。前述したように、色変換層25、透明層27、およびマスク28が設けられている。さらに、不透明／反射特徴部33、光導波機能を提供する改質屈折率透明層34、および未改質屈折率層35が設けられている。（色変換器およびマトリクスが形成されている）色変換器の透明基板に関して、透明層27を改質することができる。これにより、基板平面に垂直な導波路を形成することができる。結果として、より高い屈折率の層は、光導波を強化し、かつ光をより低い発散で出射することを可能にする。基板の屈折率は、導波路を形成するためにレーザ誘起効果によって一例として改質することができ、またはより高い屈折率の材料を用いたエッチングおよび充填によって形成することができる。0.5～2mmの標準厚さの透明層34を使用することが可能である。さらに、20μmまでの厚さの基板層34を使用することが可能である。

20

#### 【0077】

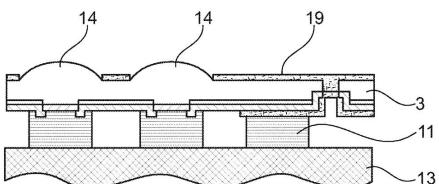

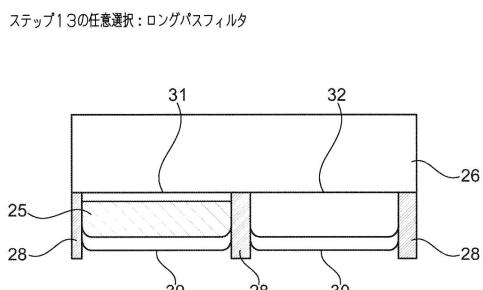

図27は、ロングパスフィルタとして記載された更なる代替例の色変換器である。色変換器の透明基板の更なる任意選択／実施形態は、色変換器が基板上に堆積される前にロングパスフィルタを堆積することである。これは、この配置において、変換されない青色光が色変換領域に反射されることを除き、図24と同様に動作する。色変換器は、青のサブ画素を覆わないようにパターン化される。色変換器は、色変換層25の下方に位置するロングパスフィルタ31を有する。ロングパスフィルタ31は、変換された光が出射するのを許容するが、青の変換されていない光を再循環させる。また、図27は、青色光の透過を可能にするために、ロングパスフィルタ32が青色画素の上に堆積されないことを示している。

30

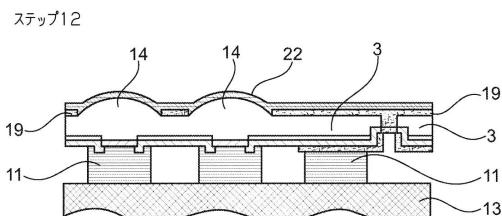

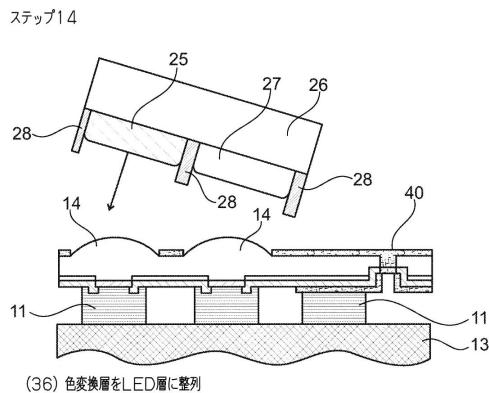

#### 【0078】

図28に示す次のステップにおいて、色変換器がLED層に搬送されてLED層に整列される。この図では、色変換層はLED基板に位置合わせされている。これは、2つの構造のボンディングのための準備であり、かつGaNサブ画素LEDが個々の色変換領域に整列するよう完了される。

40

#### 【0079】

図29において、色変換層がLED層の他の部分の上方に整列されている様子が更に示されている。図29は、図28の概略図である。図29は、色変換層用の透明基板と、薄いGaN LED層を支持するために使用される一時的なウェハとを強調する。

50

## 【0080】

図30において、色変換器がデバイスの他の部分に取り付けられている。したがって、適切な位置合わせが完了すると、2つの層を接触させて共にボンディングする。一例として、これはエポキシタイプのボンディング・プロセスであってもよい。この層のボンディングを実施して、2つの基板の間に局所的な気密シールを提供することも可能であり、これにより、色変換層に対する保護が強化される。好ましい実施形態では、色変換器は青色光でポンピングされ、蛍光体層である赤色／緑色変換層が設けられている。代替的に、層は、量子ドットまたは透明／拡散層（青色）またはそれらの混合である。図30は、不透明／黒色マスクまたは反射マスク28が、ガラス基板から垂直方向に延在することを示している。反射マスク28は、光を再循環させ、クロストークを最小に抑え、表示コントラストを向上させる性能を有していることが好ましい。したがって、反射マスク28は、フィルタが層の前に配置されたときに、青色光を透過し、赤色光および緑色光を反射する性能を有する。代替的に、フィルタが層の後に配置される場合、青色光は再循環され、赤色および緑色が透過される。

## 【0081】

図31において、一時的な層13は、組み合わされた層から除去される。これは、加熱、溶媒および／または他の標準的な技術によって達成することができる。

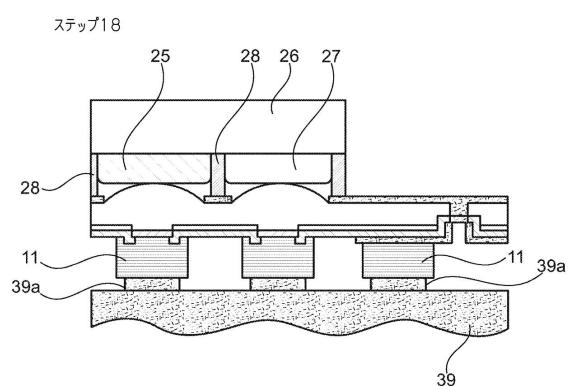

図32において、電子駆動層39が金属ボンディングパッド11に搬送され、金属ボンディングパッド11と整列される。電子駆動層39は、CMOS、TFTまたはNMOS層である。図では、分かりやすくするためにトポロジーを有するボンディングスタックを示す。好ましい実施形態では、GaN改質LEDは、平坦化された表面と共に使用することができる（図9の説明は、平坦で滑らかな表面を提供する方法である）。トポロジーがまったくないか、僅かであっても、異なる範囲の制御バックプレーンをCMOS、NMOS、TFTなどを含むがこれに限定されないGaN表面にボンディングすることができる。

## 【0082】

図33では、金属ボンディングパッド39aがボンディングパッド11に取り付けられている。これは、表示性能を提供するために必要な多くの特徴部を強調する完成したマイクロディスプレイ構造である。

## 【0083】

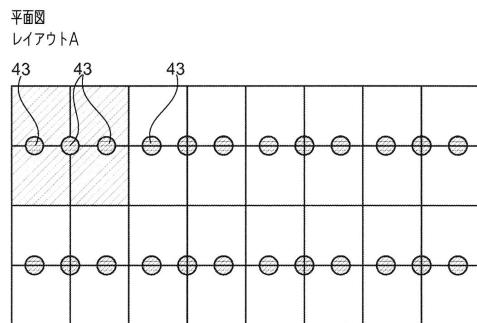

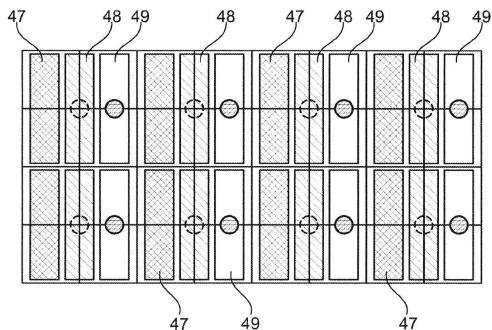

図34は、レイアウトAにおける画素レイアウトの実施例の平面図である。示される実施形態では、3つのサブ画素43は、 $20 \times 20$ ミクロンのセル内に配置される。これは、GaN誘導サブ画素の可能なレイアウトを強調している。この特定の構成では、3つのLED43が、一例として、 $20 \mu\text{m} \times 20 \mu\text{m}$ の画素領域内に配置される。

## 【0084】

図35において、ボンディングパッド39aは、画素43から離れて配置されているように示されている。各LEDサブ画素に関連するボンディングパッドは、一般に、より大きい。これにより、結合力が分散され、物理的損傷の可能性が低減される。さらに、ボンディングパッドの寸法を大きくすることによって抵抗を低減することができる。サブ画素のGaN mod定義のような技術を用いることにより、GaN表面上のトポロジーを低減し、明確な分離層を有するLEDサブ画素を提供することができるので、性能が向上する。

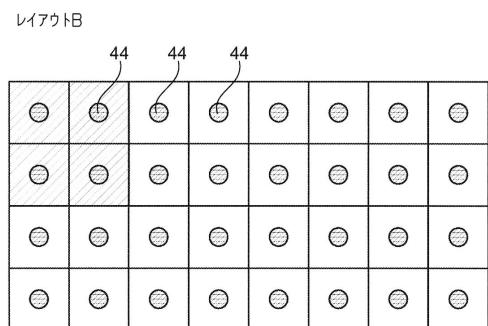

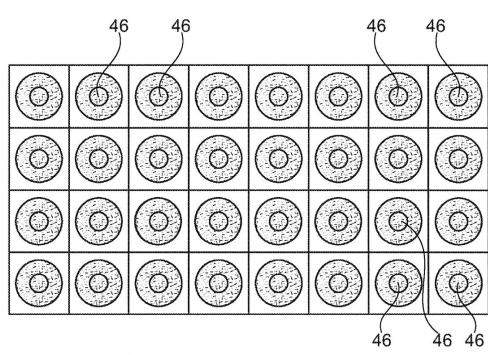

## 【0085】

図36は、レイアウトBにおける画素レイアウトの実施例の平面図である。示された実施形態では、各画素に含まれる4つのサブ画素44がある。これは、図34と同様であるが、この例では、 $20 \mu\text{m} \times 20 \mu\text{m}$ の画素領域内に4つのGaN誘導サブ画素44が画定されている。

## 【0086】

図37では、ボンディングパッド46を画素44の上方に配置することができる。これは、図36に示す各サブ画素の上方に大きなボンディングパッドを有する図35と同様で

ある。

**【0087】**

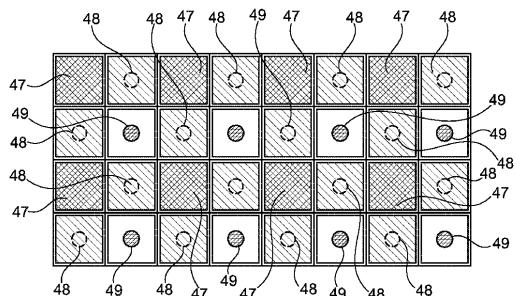

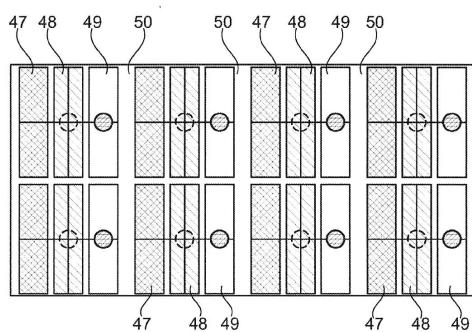

図38において、赤色変換セル47、緑色変換層48、および色変換セル49を有していない青色画素（透明／拡散層を含む）が設けられている。これは、図34のサブ画素レイアウトに関連する色変換層のレイアウトを表す。

**【0088】**

図39において、不透明／反射マトリクス50が示されている。これは、各サブ画素を分離するマトリクスも示す図38と同様である。

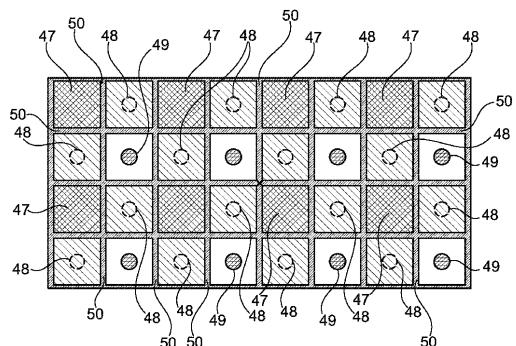

図40において、赤色変換セル47、緑色変換セル48、および色変換セル49を有していない青色画素のマトリクスが設けられている。これは、図36のサブ画素レイアウトに関連する色変換層のレイアウトを示す。

10

**【0089】**

図41において、赤色変換セル47、緑色変換セル48、色変換セル49を有していない青色画素のマトリクス、および不透明／反射マトリクス50が設けられている。これは図40と同様であり、かつ各サブ画素を分離するマトリクスを示す。

**【0090】**

以上、本発明の特定の実施形態を説明したが、記載された実施形態からの発展は、依然として本発明の範囲内に入ることが理解されるであろう。例えば、任意の適切なタイプの色変換器および任意の適切なタイプのLEDを使用することができる。

**【図1】**

**【図3】**

**【図2】**

**【図4】**

【図5】

(6) ニ酸化シリコンおよびオミック層をエッティングして画素を形成

【図7】

(8) ニ酸化シリコンの層を除去および堆積

【図6】

(7) プラズマ処理を行って導電領域および絶縁領域を形成

【図8】

(9) 金属層を堆積 (nコンタクト)

(10) ニ酸化シリコンをエッティングして画素に対するコンタクトを形成

【図9】

(11) ボンディングパッドを堆積 (nおよびpコンタクト)

【図10】

(12) LED基板を除去 (シリコーンに対するレーザリフトオフ、シリコーンに対する化学機械的ポリッシングおよびエッティング)

(13) 一時的なウェハをボンディング (曲線は、GaN層よりもかなり厚いことを示す)

【図11】

(14) GaNをエッティングして光学的特徴 (レンズ) を形成

【図12】

(15) GaNの表面を粗面化して光取り出しを改善

【図13】

ステップ9の任意選択：GaN層におけるマトリクス形成

(16) エッチングプロセス中にGaNピラーを形成して

LED画素間の光学的分離を提供し、光学的クロストークを低減

【図15】

ステップ10の任意選択：レンズ厚さを制御するためのnコンタクトのエッティングストップの使用

(18) レンズのエッティング中に使用される終点検出により

nコンタクトまで貫通するビアの開放と同時にレンズ厚さの制御を提供

【図14】

ステップ10

(17) nコンタクト上のエッティングストップまでGaNを貫通するビアをエッティング

【図16】

ステップ11

(19) 导電性金属グリッドおよび／または不透明層を堆積

【図17】

ステップ11の任意選択：ITO導電層

(20) ITOを金属の代わりに堆積して透明導電膜を形成。

適切なITOの厚さの選択により反射防止機能が生じる

【図19】

ウェハを貫通するビアおよび

Auエッティングストップ層上の

コンタクトを用いるウェハの側上の

nパッドに対するnグリッドコンタクト

ウェハのn側上の

画素間のカソード/

光遮蔽グリッドを形成

【図18】

ステップ11の任意選択：画素分離マトリクスを形成するためのn金属の使用

(21) 実施される場合に、堆積されたn金属がクロストーク低減マトリクスの側壁も被覆

【図20】

(22)  $\text{SiO}_2$ または他の単層または多層コーティングをGaNレンズおよび

n金属の表面上に堆積。これにより、保護および反射防止の両方の目的が提供される。

【図21】

(23) GaNレンズ(または粗面化表面)のみが被覆されるように

誘電体コーティングをパターン化

【図22】

ステップ12の任意選択：ショートパスフィルタ（例えば、多層誘電体コーティング）

(24) 異なるまたは追加のコーティングまたは層を塗布または堆積して

ショートパスフィルタ機能を提供。

これは、レンズのみを被覆するようにパターン化されるか、全面を被覆し得る。

ショートパスフィルタは、青色光をGaNから出射するのを許容するが、

より長い波長（即ち、色変換層によって生成された赤色光または緑色光）を反射する。

【図23】

ステップ13

(25) 色変換層（例えば、蛍光体、量子ドット、有機物質、またはそれらの組み合わせ）

(26) 基板（ガラス、サファイア、シリコンまたはその他）

(27) 青色光の出射を許容する透明層（拡散機能または散乱機能も提供）

(28) 不透明／黒色マスクまたは反射性のマスク

【図24】

(29) エッチングされたシリコン基板

【図26】

ステップ13の任意選択：導波路

(33) 不透明／反射特微部

(34) 光学的導波路機能を提供するための改良屈折率透明層

(35) 未改質屈折率

【図25】

ステップ13の任意選択：ショートパスフィルタ

(30) 青色光が入射するのを許容するが、緑色または赤色等のより長い変換された光を

反射するショートパスフィルタ層

【図27】

ステップ13の任意選択：ロングパスフィルタ

(31) 色変換層の下に位置するロングパスフィルタ

(変換された光の出射を許容するが、青色の変換されていない光を再循環)

(32) 青色光の透過を許容するためにロングパスフィルタは青色画素上には堆積されない。

【図28】

【図29】

【図30】

【図31】

【図32】

【図34】

(43) いくつかの画素レイアウトの実施例が使用され得る。

この場合、3つのサブ画素が各 $20\times20$ ミクロンの画素セル内に配置される。

【図33】

【図35】

(45) ボンディングパッドが画素から離れて配置され得る。

【図36】

(44) この代替的なレイアウトにおいて、4つのサブ画素が各画素に含まれる。

【 37 】

(46) ボンディングパッドが画素の上に配置され得る。

〔 40 〕

Fig. 40

【図4-1】

Fig. 41

【図38】

(47) 赤色変換セル

(48) 緑色変換セル

(49) 色変換セルを有していない青色画素（透明／拡散層を含み得る）

【図39】

(50) 不透明／反射マトリクス

---

フロントページの続き

(72)発明者 バレンタイン、ガレス ジョン

イギリス国 YO24 2TN ヨーク チャロナーズ ロード 44

(72)発明者 ゴートン、スティーブン ウォーレン

イギリス国 EH10 6EQ エдинバラ コレニー ドライブ 5

審査官 島田 英昭

(56)参考文献 再公表特許第2014/006987 (JP, A1)

特開2011-216668 (JP, A)

特開2014-160835 (JP, A)

米国特許出願公開第2012/0223875 (US, A1)

国際公開第2014/099499 (WO, A1)

特開2010-087224 (JP, A)

特開2010-040976 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L33/00-33/64

H05B33/00-33/28