(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4234397号

(P4234397)

(45) 発行日 平成21年3月4日(2009.3.4)

(24) 登録日 平成20年12月19日(2008.12.19)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12

B

H01L 23/12

Q

請求項の数 4 (全 24 頁)

(21) 出願番号 特願2002-329187 (P2002-329187)

(22) 出願日 平成14年11月13日 (2002.11.13)

(65) 公開番号 特開2003-179179 (P2003-179179A)

(43) 公開日 平成15年6月27日 (2003.6.27)

審査請求日 平成17年9月21日 (2005.9.21)

(31) 優先権主張番号 10/007982

(32) 優先日 平成13年11月13日 (2001.11.13)

(33) 優先権主張国 米国(US)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100077517

弁理士 石田 敬

(74) 代理人 100092624

弁理士 鶴田 準一

(74) 代理人 100100871

弁理士 土屋 繁

(74) 代理人 100082898

弁理士 西山 雅也

(74) 代理人 100081330

弁理士 樋口 外治

最終頁に続く

(54) 【発明の名称】チップモジュールエレメントおよび該チップモジュールエレメントを製造する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

キャパシタのアレイを形成し、

該キャパシタのアレイ中の前記キャパシタを電気的にテストし、欠陥のあるキャパシタを示すデータと容認できるキャパシタを示すデータとを備えるテストデータを生成し、

該テストデータを情報記憶媒体に保存し、

前記キャパシタのアレイの上に、容認できるキャパシタに電気的に結合された複数の導電性エレメントを含む相互接続構造を形成し、該相互接続構造の形成は、

前記キャパシタのアレイの上に接着性結合シートをラミネートし、

前記容認できるキャパシタに隣接する前記結合シートに複数の開孔を形成すると共に、前記欠陥のあるキャパシタに隣接する前記結合シートには開孔を形成しないようにし、

該開孔内部に導電性材料をデポジットすることを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

## 【請求項 2】

請求項 1 に記載の方法において、前記相互接続構造の形成は、スパッタリング、非電解メッキまたは電解メッキの少なくとも 1 つを使用して複数の導電性ポストを形成することを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

## 【請求項 3】

キャパシタのアレイと、

該キャパシタのアレイに結合した平面状相互接続構造と、

10

20

前記平面状相互接続構造に結合した多層回路構造であって、該平面状相互接続構造は前記キャパシタと該多層回路構造とを電気的に導通させる複数の導電性エレメントを備えているものと、

前記多層回路構造に結合した複数の導電性ピンと、を備え、

前記キャパシタのアレイは、前記ピンから前記多層回路構造を通り、導電性エレメントを通って前記キャパシタに至る電流を提供することによって充電され得るようになっており、

接着性結合シートが、前記キャパシタのアレイの上にラミネートされ、

前記欠陥のあるキャパシタに隣接する前記結合シートには開孔が形成されることなく、前記容認できるキャパシタに隣接する前記結合シートに複数の開孔が形成され、そして、

導電性材料が、前記開孔内部にデポジットされている、ことを特徴とするチップモジュールエレメント。

#### 【請求項 4】

請求項3に記載のチップモジュールエレメントにおいて、前記導電性エレメントは、導電性ポストとZ接続からなるグループの中から選択される、ことを特徴とするチップモジュールエレメント。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、埋め込キャパシタに関する。さらに、詳記すると、本発明は、マルチチップモジュールにキャパシタを埋め込むための構造および方法を提供するものである。

##### 【0002】

##### 【従来の技術】

バイパスキャパシタは、半導体チップの近傍でマルチチップモジュール (MCM : Multi-Chip Module) に電荷の溜めを供給することによってパワーシステムを信号誘発変動から保護している。現在、高性能メインフレームコンピュータは、半導体チップの近傍でMCMに数百の表面実装型LICA (Low Inductance Capacitor Array : 低インピーダンスキャパシタのアレイ) を利用している。このLICAは、MCMで価値のある表面エリアを消費し、現在のコストが1個当たり約3~10米国ドルとなっている。

##### 【0003】

MCMの周波数が増すにつれて、LICAの寄生直列インダクタンスが増大し、バイパスキャパシタとしてのLICAの有益性は減少する。直列インダクタンスが増大すると、所与の距離を越えて半導体チップに電荷を迅速に供給するキャパシタの能力は減退する。しかも、半導体チップの中心にあるスイッチングドライバからLICAキャパシタまでの距離は、これらのキャパシタが高周波における初期スイッチングノイズを減衰させるのをライト時間が阻止するほど十分に離れている。周波数が~1GHzに増加するのに従って、寄生インダクタンスのインピーダンスは、LICAのコンポーネントパフォーマンスを支配するポイントへと増大する。従って、LICAは、約1GHzの周波数を超えると、限られた有益性を有することになる。

##### 【0004】

LICとチップとの間の距離およびインダクタンスが薄膜MCMの厚さおよびインダクタンスよりも大きいことを認めた上で、GHzレベルの周波数におけるバイパスキャパシタの問題を解決しようとするならば、薄膜キャパシタを薄膜MCM内部に埋め込むことが一つの解決策である。このような解決策であれば、MCM側のさらなるアクティブコンポーネントのために高周波(>1GHz)の性能を提供し、より多くの適用分野を開拓することができる。

##### 【0005】

##### 【発明が解決しようとする課題】

ビルドアッププロセス (buildup process) を使ってMCMを作るとき、埋め込まれた薄膜キャパシタの層に何らかの欠陥が生じる可能性がある。このような欠陥は、MCMを使

10

20

30

40

50

用不能にする接地短絡への要因になりかねない。このような事態を回避するためには、全てのキャパシタをその接続に先立ち、後のビルトアップ層になる部分に至るまでテストすることが可能であろう。これは、ビルトアップ構造において、良好なキャパシタと欠陥のあるキャパシタとの考え得る全ての組み合わせに分割されたマスクが使用できないと、極めて困難である。キャパシタの数が多い場合、このようなマルチマスクを使用するアプローチの仕方は非常に現実的ではない。従って、必要なのは、上記した課題を克服する構造および方法であり、これが本発明の対象である。

### 【0006】

#### 【課題を解決するための手段】

本発明の第1の形態によれば、キャパシタのアレイを形成し、該キャパシタのアレイ中の前記キャパシタを電気的にテストし、欠陥のあるキャパシタを示すデータと容認できるキャパシタを示すデータとを備えるテストデータを生成し、該テストデータを情報記憶媒体に保存し、前記キャパシタのアレイの上に、容認できるキャパシタに電気的に結合された複数の導電性エレメントを含む相互接続構造を形成し、該相互接続構造の形成は、前記キャパシタのアレイの上に接着性結合シートをラミネートし、前記容認できるキャパシタに隣接する前記結合シートに複数の開孔を形成すると共に、前記欠陥のあるキャパシタに隣接する前記結合シートには開孔を形成しないようにし、該開孔内部に導電性材料をデポジットすることを備える、ことを特徴とするチップモジュールエレメントを製造する方法が提供される。

また、本発明の第2の形態によれば、キャパシタのアレイと、該キャパシタのアレイに結合した平面状相互接続構造と、前記平面状相互接続構造に結合した多層回路構造であつて、該平面状相互接続構造は前記キャパシタと該多層回路構造とを電気的に導通させる複数の導電性エレメントを備えているものと、前記多層回路構造に結合した複数の導電性ピンと、を備え、前記キャパシタのアレイは、前記ピンから前記多層回路構造を通り、導電性エレメントを通じて前記キャパシタに至る電流を提供することによって充電され得るようになっており、接着性結合シートが、前記キャパシタのアレイの上にラミネートされ、前記欠陥のあるキャパシタに隣接する前記結合シートには開孔が形成されることなく、前記容認できるキャパシタに隣接する前記結合シートに複数の開孔が形成され、そして、導電性材料が、前記開孔内部にデポジットされている、ことを特徴とするチップモジュールエレメントが提供される。

本発明の実施例は、キャパシタのアレイを形成し、キャパシタのアレイを電気的にテストし、どのキャパシタが欠陥を有するか或いはどのキャパシタが容認できるか特定し、欠陥のあるキャパシタのデータを情報記憶媒体に保存することを備えるチップモジュールエレメント製造の方法を提供する。この方法は、さらに、キャパシタのアレイの表面に相互接続構造を形成することを備える。ここで、相互接続構造は、複数の導電性エレメント（例えば、導電性ポストおよびZ接続）を含み、導電性エレメントは容認できるキャパシタに電気的に結合されている。相互接続構造を形成することは、スパッタリング、無電解メッキ、電解メッキのうち少なくとも1つの方法を使用して複数の導電性エレメントを形成することを備える。或いは代わりに、相互接続構造の形成は、キャパシタのアレイの表面に接着結合シートをラミネートさせ、容認できるキャパシタに隣接する結合シートに複数の開孔を形成し、開孔内部に導電性材料をデポジットすることを備えてもよい。キャパシタのアレイの形成は、シリコン基板上にキャパシタのアレイを形成することを備えてよい。

### 【0007】

本発明の実施例は、さらに、キャパシタのアレイ、このキャパシタのアレイに結合した平面状相互接続構造、および、この平面状相互接続構造の結合した多層回路構造を有するチップモジュールエレメントを提供する。相互接続構造は、キャパシタと多層回路構造を電気的に通じさせる複数の導電性エレメント（例えば、Z接続や導電性ポスト）を備える。多層回路構造には複数の導電性ピンが結合される。キャパシタのアレイは、前記ピンから多層回路構造を通過し、導電性エレメントを通過してキャパシタに至る電流を供給するこ

10

20

30

40

50

とによって充電され得る。

【0008】

【発明の実施の形態】

これらの提供物は、下記の説明が進むにつれて当業者に明らかになるであろう様々な副次的提供物および特徴と共に、本発明に係る方法およびチップモジュールエレメントによって獲得される。以下、その好ましい実施例を、単なる例としての添付図面を参照して詳細に説明される。

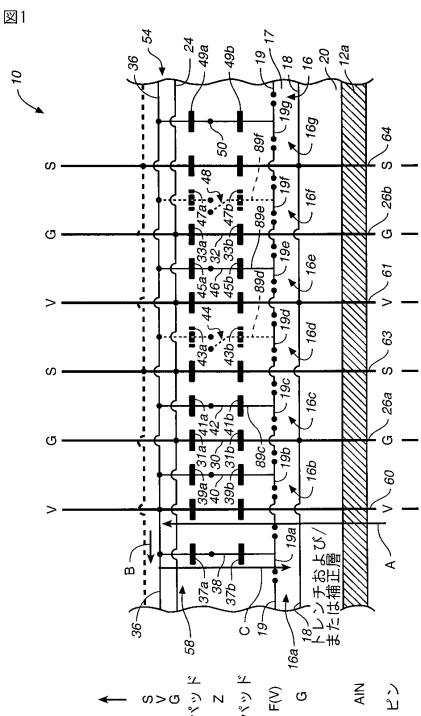

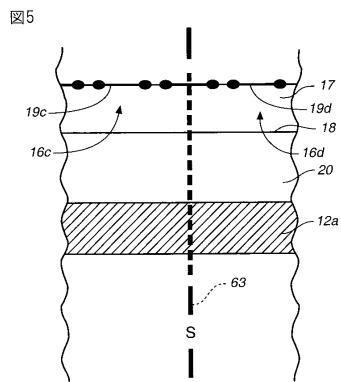

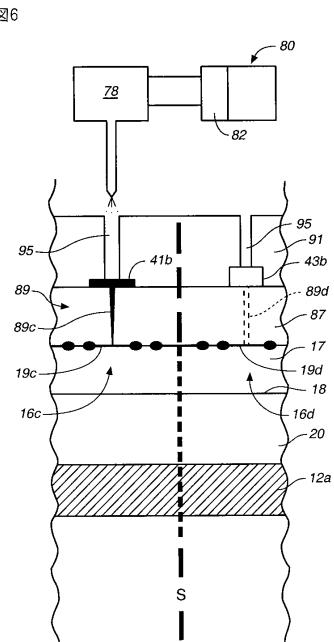

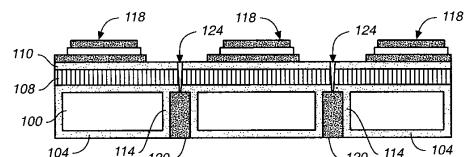

【0009】

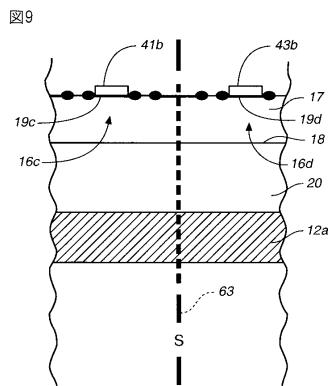

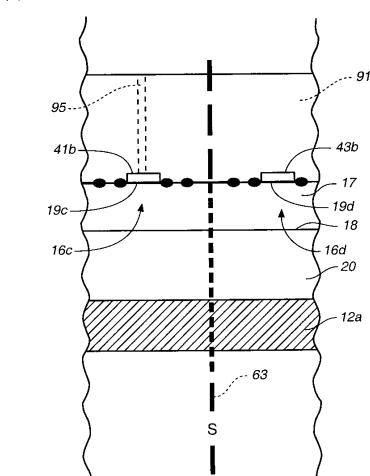

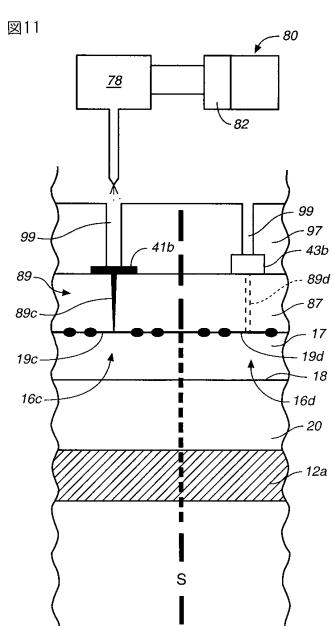

図1～図8について詳細に説明すると、ここに示してあるのは、複数の誘電層を支持する基板12a（例えば、AlN（窒化アルミニウム）基板またはセラミック基板）を有する基板アセンブリ（全体的に10として描かれている）である。その全てが、以下に規定される。基板アセンブリ10は、キャパシタ16a、16b、16c、16d、16e、16f、16gからなるキャパシタのアレイ（全体的に16として描かれている）を含み、キャパシタのアレイ16の各キャパシタは、全てのキャパシタのための底部電極としての接地層18、電極層セグメント（以下、19a、19b等で表される）、および、これらの間の誘電層を含む。基板アセンブリ10は、また、多層回路構造54、相互接続構造58、並びに、電圧ピン60、61、接地ピン26a-26bおよび信号ピン63、64を含む。各キャパシタ（例えば、キャパシタ16a、16b等）は、何らかの適切な誘電体を含み、表面誘電層20全体にわたって平面状であっても非平面状であってもよい。一例に過ぎないが、図1～図5に示す通り、キャパシタのアレイ16は、当業者によく知られている何らかの適切な手段によって形成することのできる共通の誘電層17を含む。

10

20

【0010】

接地層18は、好ましくは連続的で、接地ピン26a-26bに電気的に結合する。接地層18は、また、それぞれ接地パッド31a-31bと接地パッド33a-33bを含む導電性線路30、32を介して接地層24に電気的に結合する。キャパシタのアレイ16、すなわち、キャパシタ16a、16b、16c、16d、16e、16f、16gは、セグメント形電極層（全体的に19として描かれる）を含み、このセグメント形電極層の方は、一対のパッドとZ接続の複数の組み合わせからなる相互接続構造58を通して電極層36に結合する。詳述すると、下記のパッドとZ接続の組み合わせは、それぞれキャパシタ16a、16b、16c、16d、16e、16f、16gと関連する電極層セグメント19a、19b、19c、19d、19e、19fに結合する。その組み合わせとは、パッド37a、37bとZ接続38、パッド39a、39bとZ接続40、パッド41a、41bとZ接続42、パッド43a、43bとZ接続44、パッド45a、45bとZ接続46、パッド47a、47bとZ接続48、そして、パッド49a、49bとZ接続50である。ここでは、以下に述べるようなテストから、キャパシタ16d、16fに欠陥のあることが判明したと仮定する。そこで、導電性コラム（以下、89dおよび89fで表される）を点線で表し、これで、Z接続44、48が実際には形成されなかつたが形成されたものとし、キャパシタ16d、16fが無欠陥または無傷で容認できることが判明したものとする。

30

【0011】

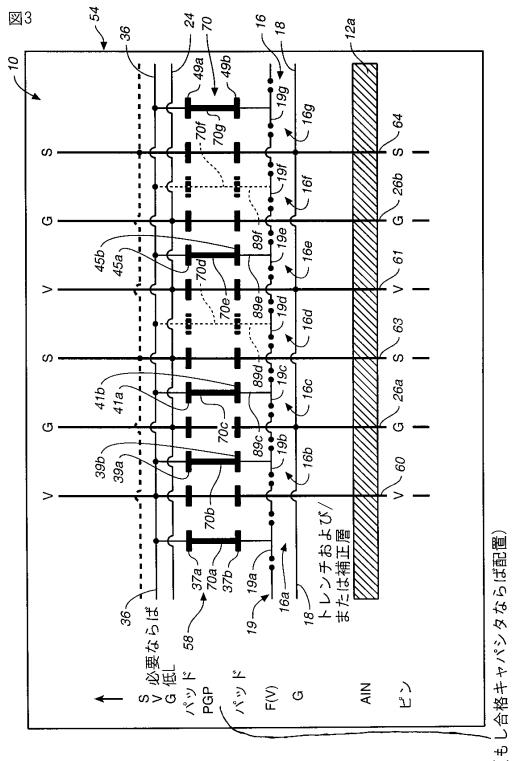

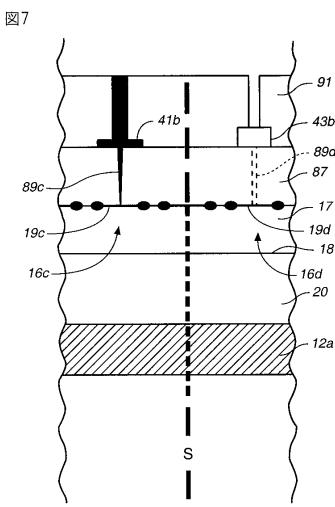

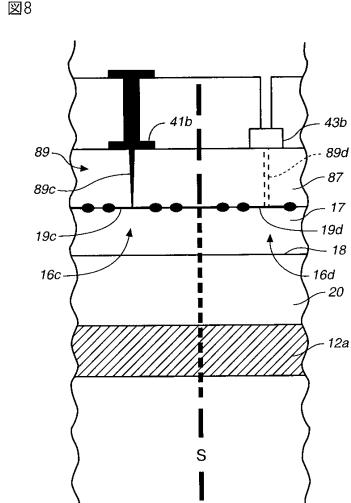

先に示した通のように、電極層19は、分割されたキャパシタ電極（すなわち、電極層セグメント19a、19b、19c、19d、19e、19f）にセグメント化されており、容認できるキャパシタのどれかと関連するピンのどれかに関して電圧または電荷がフローティングしている。セグメント形電極層19は、好ましくは、図1に示す通り、誘電層17の上に配置する。パッド（すなわち、パッド37b、39b、41b、43b、45b、47b、49b、図1参照）を、図9に最も良く示す通り、分割された電極層セグメント全ての上に直接載せてもよい。或いは代わりに、誘電層87をセグメント形電極層19および露出した誘電層17の上に配置し、次に、開口（図示されていない）を誘電層87に開け（例えば、レーザー78／コンピュータ80を使って）、続いて、図6、図7および図8に示す通り、電解メッキによって導電性コラム89、例えば、導電性コラム89c

40

50

を形成してもよい。導電性コラム 8 9 d を点線で表し、これで、導電性コラム 8 9 d が実際には形成されなかつたが、形成されたものとし、キャパシタ 1 6 d が無欠陥または無傷で容認できることが判明したことを示す。その後、パッド 4 1 b 等を、導電性コラム 8 9 ( 例えは、図 8 に示す通りの導電性コラム 8 9 c ) と接触するように誘電層 8 7 の上に配置する。

【 0 0 1 2 】

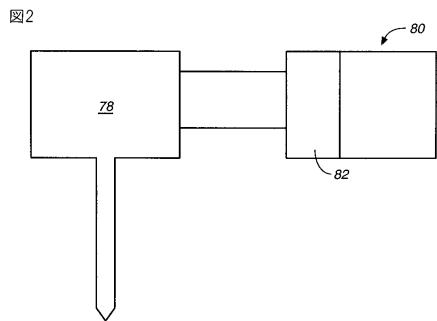

キャパシタが容認できるかどうかテストするのに、パッド 3 7 b 、 3 9 b 、 4 1 b 等を使用してもよい。詳記するならば、キャパシタ ( すなわち、 1 6 a 、 1 6 b 、 1 6 c 、 1 6 d 、 1 6 e 、 1 6 f 、 1 6 g ) のどれが短絡しているか特定するために、パッド ( すなわち、パッド 3 9 b 、 4 1 b 、 4 3 b 等 ) の各々を基板接地層 ( 例えは、図 1 の接地層 1 8 ) に関してテストしてもよい。そして、そのテストデータ ( “ 合格 ” キャパシタ対 “ 不合格 ” キャパシタのデータ ) をコンピュータ 8 0 、詳記するならば、コンピュータ 8 0 のメモリバンク 8 2 に蓄積し、保存する ( 図 2 参照 ) 。或いは代わりに、キャパシタの各々を、電極層セグメント 1 9 a 、 1 9 b 、 1 9 c 、 1 9 d 等を介して、パッドを介さずにテストしてもよい。

【 0 0 1 3 】

集積回路チップのゲートがスイッチングに電荷を必要とすることは知られている。マルチチップモジュールでは、ゲートおよびチップの近傍に位置するキャパシタが、電荷の溜めとして働く。先に示した通り、キャパシタは、チップに近接する膜 ( 例えは、誘電層 1 7 ) を含む。これもまた先に示した通り、キャパシタのアレイ 1 6 を製造するプロセスでは、1 つ以上のキャパシタに欠陥の生じることがあり得る。欠陥のあるキャパシタの短絡が、形成されたモジュールに欠陥を生じさせることもあり得る。

【 0 0 1 4 】

本発明の実施例では、欠陥のあるキャパシタをチップから電気的に絶縁する。例えは、好みの実施例では、キャパシタのアレイ 1 6 を、指示された手順に従って形成する。次に、このアレイ 1 6 を電気的にテストし、欠陥のあるキャパシタの場所のデータをコンピュータ 8 0 のメモリバンク 8 2 に保存する。次に、関連する電極層セグメント 1 9 a 、 1 9 b 、 1 9 c 等を含むキャパシタのアレイ 1 6 全体の上に結合シート ( 例えは、誘電層 8 7 ) を載置する。これにより、レーザー 7 8 または他のフライス削り手段が、保存された欠陥キャパシタの場所データを使って、合格キャパシタに見合う場所で結合シートに開孔 ( 図示されていない ) を開ける。これで、開孔を充填して導電性コラム、例えは、導電性コラム 8 9 c を生成できることになる。欠陥のあるキャパシタより上の領域は開放されない。つまり、キャパシタ 1 6 d が欠陥ありと仮定されたので、開孔 8 9 d は形成されなかつたということになる。

【 0 0 1 5 】

キャパシタのテストで欠陥ありとされたキャパシタの絶縁は、製造されたアセンブリにおいて行ってもよい。典型的に、キャパシタのテストは、先に示した通り、誘電層 8 7 およびパッド ( 例えは、パッド 4 1 b ) を配置する前にも行われる。テスト手順の一例として、キャパシタにバイアス電圧をかけ、漏れ電流を測定することによって欠陥キャパシタをふるい分けることができる。そこで、漏れ電流の大きいキャパシタは、欠陥ありと判別されることになる。この情報は、次に、合格キャパシタにだけ電圧ビア ( 例えは、導電性コラム 8 9 c ) が開けられるようにレーザーでドリリングするときに使用してもよい。合格キャパシタに開口を形成するのに使用されるレーザー 7 8 は、コンピュータ 8 0 によって操作される。欠陥キャパシタに関する情報は、レーザー 7 8 の動作を制御するコンピュータ 8 0 のメモリバンク 8 2 に保存される。レーザー 7 8 が欠陥キャパシタ ( 例えは、キャパシタ 1 6 d ) の上方にあるとき、レーザー 7 8 がアクティブ化するのを阻止し、続いて、レーザーでドリリングを行うためにレーザー 7 8 を合格キャパシタの上方に移動させる。このようにして、コンピュータ 8 0 は、レーザードリリングのためにレーザー 7 8 を欠陥のない合格キャパシタの上方にだけ移動させていく。

【 0 0 1 6 】

10

20

30

40

50

さらに、先に示した通り、開口 9 5 がレーザー 7 8 等の手段によって形成される。図 1 に示す本発明の実施例では、はんだを開口 9 5 の中にデポジットする。多層回路構造 5 4 ( 例えば、S 層、V 層または G 層とパッドを有する ) を別個に形成し、結合シート ( 例えば、誘電層 8 7 ) にラミネート化させることができる。欠陥キャパシタは、上方に Z 接続を持たず、絶縁される。別個に形成された回路構造 5 4 を、そこで結合シートにラミネート化させる。合格キャパシタを荷電するための導電通路は、間接的である。電流が矢印 A、B および C の方向に流れるにつれて、合格キャパシタが荷電される。図 1 に示す通り、電流は、V ピン 6 0 を通って V 平面または多層回路構造 5 4 の電極層 3 6 まで流れ、パッド 3 7 a、3 7 b を通ってキャパシタ 1 6 a へと流れしていくのである。

## 【 0 0 1 7 】

10

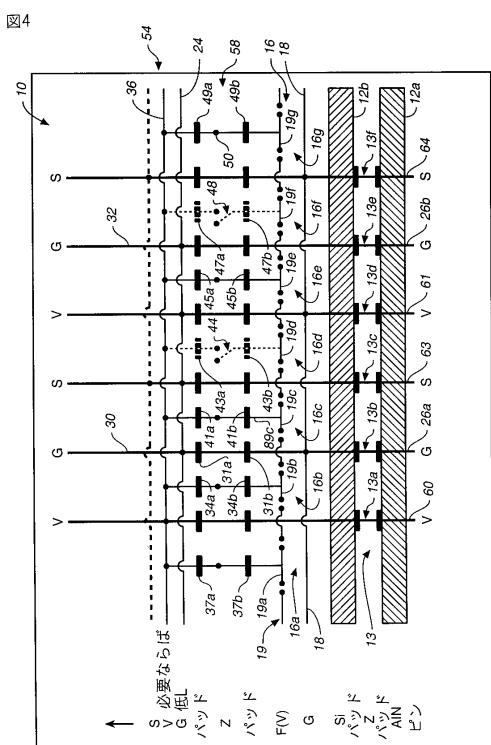

図 4 に示す本発明の実施例では、基板 1 2 b ( 例えば、シリコン基板 ) を Z 接続アセンブリ 1 3 の中に通して基板 1 2 a に結合させる。ここで、Z 接続アセンブリ 1 3 は、Z 接続 1 3 a、1 3 b、1 3 c、1 3 d、1 3 e、1 3 f を含む。基板 1 2 b は、相互接続構造 5 8 およびピン 6 0、2 6 a、6 3、4 1、2 6 b、6 4 によってキャパシタのアレイ 1 6 を支持する。従って、図 3 に示す本発明の実施例によれば、電気的通路が基板 1 2 b を通して形成され、結合シートの代わりに除去可能なマスク ( 例えば、SiN 等のハードマスクまたはフォトレジスト ) が使用される。図 1 1 に示す通り、適切なマスク材料の層 9 7 を層 8 7 の頂部または層 1 7 の頂部の上に配置する。そこで、レーザー 7 8 は開孔 9 9 を、開孔 9 9 が合格キャパシタ ( 例えば、キャパシタ 1 6 a、1 6 b、1 6 c、1 6 d、1 6 e、1 6 g ) と整合するように形成する。開孔 9 9 が形成された後、導電性ポストのアレイ 7 0 ( すなわち、導電性ポスト 7 0 a、7 0 b、7 0 c、7 0 d、7 0 e ) を合格キャパシタの上に、例えば、電解メッキによって形成する。直立する導電性ポストのアレイ 7 0 からマスクの層 9 7 を剥がす。これにより、標準のビルトアッププロセスを使って多層回路構造 5 4 ( 例えば、S 層、V 層または G 層とパッドを有する ) を導電性ポストのアレイ 7 0 の上に形成することができる。

## 【 0 0 1 8 】

20

図 1 2 ~ 図 2 1 について説明すると、そこに描かれているのは、高密度のスルーホールを有する多機能のマルチチップモジュール基板を作るための構造および方法である。将来の MCM 基板は、入出力キャパシティを増大させるべく、より高い動作周波数、高い CPU カウント、そして、より細かいピンピッチを有するのが望ましい。ペロフスカイト型キャパシタ ( perovskite capacitor ) を埋め込んだマイクロ加工シリコン ( micromachined Si ) 基板を使用することによって、これら 3 つの目標全てを達成することが可能となり得る。埋め込みペロフスカイト型キャパシタ材料、例えば、PZT、BST 等は、イネーブル速度 > GHz とモジュール面上のフリーアップエリアの両方に十分なバイパスキャパシタンスを提供できる。この材料を使用しなければ、フリーアップエリアは、今や追加 CPU に使用できる LICA 等、数百のばらばらなパッシブコンポーネントによって占領されることになる。マイクロ加工シリコンは、ペロフスカイト型キャパシタの高い歩留まりのための平面性と、スルーピアのピッチを約 1 mm より小さい値に縮小する可能性の両方を提供する。基板において最高のスルーホール密度を達成するためには、シリコンのディープリアクティブイオンエッティング ( DRIE : Deep Reactive Ion Etching ) を使って、約 1 0 0  $\mu$ m 程度または約 2 mm 前後の直径、4 5 0  $\mu$ m 程度の低い値のピッチを有する Si のスルーホールビアにほぼ 90 度の壁を形成する。スルーホールは、この構造のユーティリティを確保すべく互いに電気的に絶縁しなければならない。両方のキャパシタを組入れ、スルーピアを電気的に絶縁するためのプロセスおよび構造を図 1 2 ~ 図 2 1 に示す。詳述すると、図 1 2 ~ 図 2 1 は、高密度の導通スルーホールを有する多機能のマルチチップモジュール基板を作るための構造および方法を示す。強誘電性ペロフスカイトまたは寄生電気的ペロフスカイト ( 例えば、PZT または BST ) の薄膜等、キャパシタンス密度の高い材料を使って最良の歩留まりを得るために、シリコンウエハの平面状であることが高い歩留まりにとって極めて望ましい。

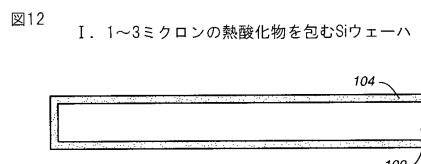

## 【 0 0 1 9 】

30

40

50

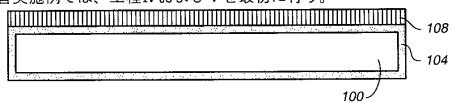

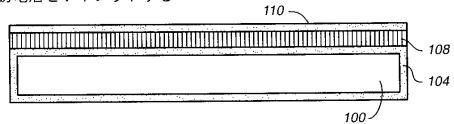

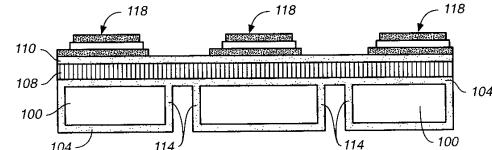

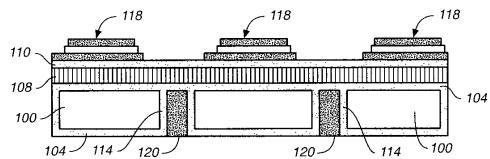

より詳細に図12～図21について説明すると、そこに見られるのは、厚さが約200μmから約3000μmまでの範囲のシリコン(Si)ウエハ100である。Siウエハ100は、二酸化ケイ素(SiO<sub>2</sub>)（すなわち、熱酸化物）を包む、厚さが約1μmから約3μmまでの範囲の層104に包まれている。SiO<sub>2</sub>包囲層104は、酸化環境の中でSiウエハ100から熱によって成長したものである。SiO<sub>2</sub>層104は、DRIEのためのエッティング止めとして機能させてもよい。SiO<sub>2</sub>包囲層104を定着させた後、Siウエハ100に構造的な支持を与え、ピア（下に、“116”で表される）が形成された後に平面性を確保するために、適切な誘電層108（例えば、Si<sub>3</sub>N<sub>4</sub>、酸窒化物、TEOS、LTO等）を図12の酸化構造の上にデポジットする。

## 【0020】

10

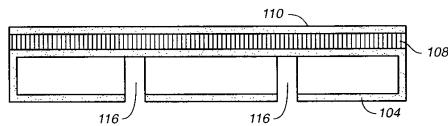

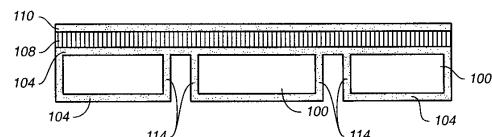

さらに、電極の接着状態または応力状態（例えば、引張応力または圧縮応力の度合い）を確保する目的で任意の誘電層110を誘電層108の上にデポジットさせてもよい。応力状態は、信頼性および歩留まり（例えば、クラッキング）およびキャパシタ歩留まり／性能に影響を及ぼし得る。ウエハ100の背側をプラズマ、レーザーまたは化学的方法によってドリリングし、それで、SiO<sub>2</sub>酸化物層104または誘電層108または110の上で止まるピア116を形成する（図15参照）。この工程は、場合によっては、当業者によく知られている予備ドリルマスキングプロセスとその後のマスク除去プロセスを必要とする。

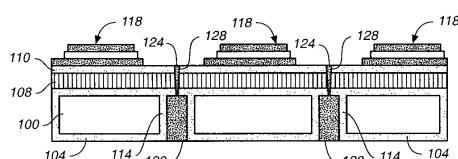

## 【0021】

20

ピア116を互いに電気的に絶縁するために、その内部でSiO<sub>2</sub>熱酸化物層114を成長させる。SiO<sub>2</sub>酸化物層114は、厚さが例えば約0.25μmから約3.00μmまでの範囲内など、適切ないかなる厚さであってもよい。或いは代わりに、ピア116の表面のCVDパッシベーションなど、他の処理を施してもよい。本発明の別の実施例では、このとき、ピア116を導通媒体120で満たすことができる。

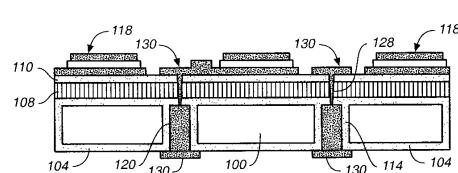

## 【0022】

キャパシタ118は、上側に任意の複数組のプロセスによって製造される。このとき、ピア116を導通媒体120で満たしてもよい（まだ行われていなかった場合）。接着を促進する層（例えば、TiN等）が最初に要求されることもあり得る。

## 【0023】

30

図18のウエハアセンブリの上側は、導通媒体120の上で止まるピア124を生成するために、プラズマ、レーザーまたは化学的方法によってドリリングする。このピア124は、直径がスルーピア114より小さいものとする。このステップは、場合によっては、当業者によく知られている予備ドリルマスキングプロセスとその後のマスク除去プロセスを必要とする。ピア124に、金属または導通充填材からなるプレート128でライニングまたはメッキを施す。この工程は、場合によっては、（a）背側の導体シードのデポジションとその後のエッティングおよび／または（b）正面側のマスキングとその後のマスク除去を必要とする。

## 【0024】

本発明のある実施例では、130として連続的に大きく描かれたパッド、相互接続構造、経路等をマスクし、メッキする追加的プロセスを行ってもよい（まだ行われていない場合）。ピン止め、その後の層ビルトアップ、Z接続、表面マウント等の追加的プロセスをここで行ってもよい。

40

## 【0025】

図22～図34について説明すると、そこに描かれているのは、並列処理膜を使って埋め込みコンポーネントを持つ多層電気基板を作るための構造および方法である。コンポーネントには、ICエレクトロニクスコンポーネントSi、GaAs、Si/Ge等、並びに、十分に小さい市販のパッシブコンポーネント（passive component）が含まれる。この構造は、高周波モジュール用途におけるバイパス使用のために多量のマイクロファラードのキャパシタンスを有する。価値あるコンポーネントを基板に埋め込むことは、周波数と密度の要求が市場を駆り立てるにつれて、ますます重要になってこよう。最新技術水準の要

50

求を満たすためには、分離したコンポーネントをコスト効率の高い仕方で埋め込むことが必要になるケースもあり得る。

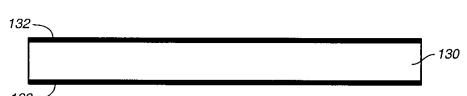

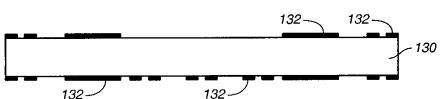

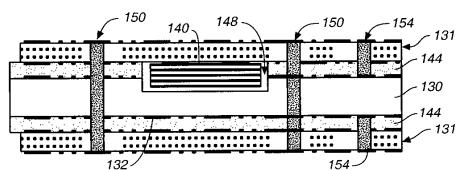

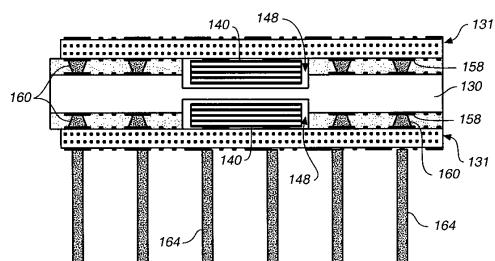

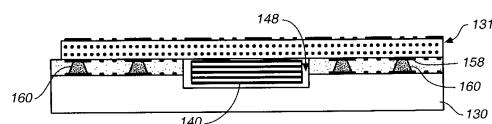

【0026】

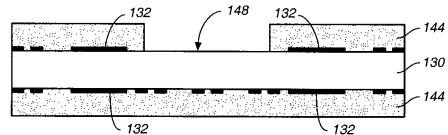

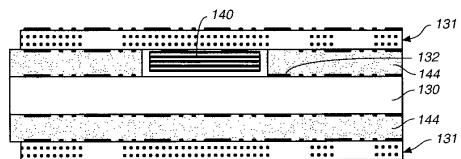

図22に見られるのは、単層または多層のコア基板130である。本発明の実施例は、銅被覆132を施したコア基板130と、施していないコア基板130とを含む。本発明の実施例はまた、内側Cu層を持つコア基板130も含む。本発明のさらなる実施例は、樹脂被覆銅(RRC)を利用する。先在する導通スルーピアを使用する実施例も、本発明の主旨および範囲から逸脱することなく実現できる。

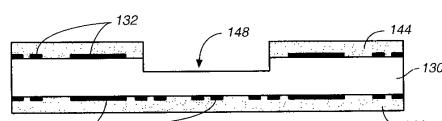

【0027】

コア基板130がCu被覆132-132で形成された後、Cu被覆132-132は、

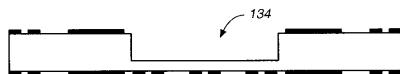

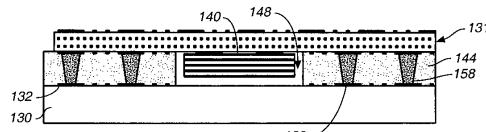

図23の構造を生成するためにパターン化し、エッチングしてもよい。本発明の実施例は、減法的パターン化、加法的パターン化および半加法的パターン化の全てを含む。本発明のある実施例では、Cu被覆132を完全にエッチングし、コンポーネント(下に“140”で表される)を埋め込むべき場所を空ける。他の実施例では、コア基板130の両側にコンポーネントを埋め込む。図24に最も良く示す通りの追加的実施例では、予備形成される(例えば、フライス、カッタまたはドリルを使って)キャビティ134を、その後にコンポーネントが埋め込まれる場所に形成してもよい。内側Cu層を持つコア基板130の場合は、Cu層をレーザー止めとして使ってコアキャビティ134をレーザーで開けてよい。

【0028】

131として大きく描かれた埋め込むべきコンポーネント140(図25参照)は、すでに作られた、好ましくは並列に作られた、同じく131として大きく描かれた分離した誘電膜(可能であれば、多層)または可撓膜の上に組み立てられる。ある実施例では、高温はんだ(例えば、Au-20Sn、Au-12Ge、Au-3.5SiまたはPb-5Sn)または導電性接着剤を使って、その後の処理およびコア基板130の使用における信頼性を確保する。他の実施例では、場合によっては、誘電膜131の上側となる下側にパッド層が存在しない。本発明の追加的実施例では、コア基板130の下側となるべく露出誘電膜131の表面にピン、スタッド瘤またははんだ瘤を取り付けてよい。

【0029】

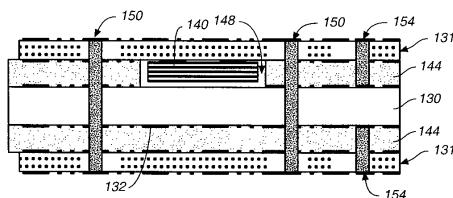

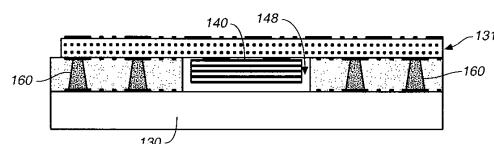

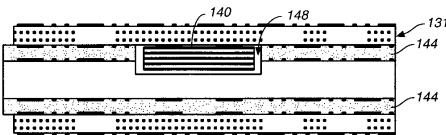

コア基板130(キャビティ134を一切持たない、すなわち、キャビティなしのコア基板130)にコンポーネント140(1つ以上の誘電膜を含む)を取り付ける様々な実施例を描いた図26~図30について説明すると、図23のパターン化銅被覆コア基板130の上に誘電層144-144を置くか、流すか、展延させるか、吹付けるか、または、ラミネート化させる。或いは、プリカットされた“プリブレグ”(または、類似材料)のアライメントが必要となることもあり得る。誘電層144の1つに、コンポーネント140を受容するための誘電性キャビティ148を形成する。注目すべきは、補助の下込め材、“グロップトップ”、または、他の接着/密封材を任意に、後続の処理に先立ってコンポーネント140全体に施してもよいことである。誘電膜131は、取り付けられたコンポーネント140を含めて、図27に最も良く示す通り、コンポーネント140がキャビティ148の中に留まるように図26の層状構造にラミネート化してもよい。誘電膜131-131は、応力釣合いのために両側でラミネート化してもよい。

【0030】

引き続き、スルーピア・アセンブリ150をドリル、デスマニア、eレス、Cuシード/ブレート、eプレートCuによって形成し、次に、スルーピアを充填してから、パネル化する。誘電膜131の露出側にパッド層が存在しない実施例では、パターン化および/またはパッド層作成を行ってよい。他の実施例では、スルーピア・アセンブリ150にCuキャップをかぶせてもよい。追加的実施例では、二通りのドリリング工程を使用してよく、コア基板130を貫通しない程度のブラインドピア・アセンブリ154(図28参照)を形成してもよい。

【0031】

10

20

30

40

50

図29で見られるのは、ラミネート化の間に、技術的に知られたはんだ付けまたは導電性ペースト充填によって接着性誘電膜131に作られるZ接続158である。図30では、金属ポスト160（例えば、Cu）をコア基板130（または、コア基板130の上に留まるスペーサ）の上に立てる。この場合は、Z接続が、ラミネート化の間に、技術的に知られた薄肉はんだ、拡散結合過渡液または導電性ペースト充填によって接着性誘電膜に作られる。

#### 【0032】

次に、キャビティのあるコア基板の様々な実施例を描いた図31～図35について説明すると、パターン化銅被覆コア基板130の上に誘電層144-144を置くか、流すか、展延させるか、吹付けるか、または、ラミネート化させる。或いは、プリカットされた“プリプレグ”（または、類似材料）のアライメントが必要となることもあり得る。補助の下込め材、“グロップトップ”、または、他の接着／密封材料を任意に、後続の処理に先立ってコンポーネント140全体に施してもよい。引き続き、図32に最も良く示す通り、誘電膜131-131は、取り付けられたコンポーネント140を含めて、コンポーネント140がキャビティ148の中に留まるように図31の構造にラミネート化してもよい。

10

#### 【0033】

誘電膜131-131は、図32に最も良く示す通り、応力釣合いのために両側でラミネート化してもよい。引き続き、スルービア・アセンブリ150をドリル、デスマニア（desmear）、eレス（e-less）、Cuシード／プレート（Cu seed/plate）、eプレートCu（e-plate Cu）によって形成し、次に、スルービアを充填してから、パネル化する。誘電膜131の露出側にパッド層が存在しない実施例では、パターン化および／またはパッド層作成を行ってもよい。他の実施例では、ビアにCuキャップをかぶせてよい。追加的実施例では、二通りのドリリング工程を使用してよく、コア基板130を貫通しない程度のブラインドビア・アセンブリ154を形成してもよい。

20

#### 【0034】

図34について説明すると、そこに見られるのは、ラミネート化の間に、技術的に知られたはんだ付けまたは導電性ペースト充填によって接着性誘電膜131に形成されたZ接続158である。ピン164を使用する両側処理（Double sided processing）を図34に示す。金属ポスト（例えば、Cu）160をコア基板130（または、コア上に留まるスペーサ）の上に立てる。この場合は、Z接続158を、ラミネート化の間に、技術的に知られた薄肉はんだ（thin solder）、拡散結合過渡液（diffusion bonding transient liquid）または導電性ペースト充填（conductive paste methodology）によって接着性誘電膜131に形成する。今や、埋め込みラミネートボードが、技術的によく知られている手段によって最終組み立てか誘電ビルトアップかどちらかのために使用可能（例えば、最終的なIC取り付けの組み立てのために使用可）である。或いは代わりに、積層ビアビルトアップ構造（stacked via build-up structure）またはもっと標準的な千鳥状ビア構造（staggered via structure）のためのポストメッキが、今や技術的に知られている通りに進行してもよい。

30

#### 【0035】

先に示した通り、埋め込みペロフスカイト型キャパシタ材料、例えば、PZT、BST等は、イネーブル速度 > GHz とモジュール面上のフリーアップエリア（free up real estate）の両方に十分なバイパスキャパシタンスを提供できる。この材料を使用しなければ、フリーアップエリアは、LICA等、数百のばらばらなパッシブコンポーネントによって占領されることになる。また、この材料は、周囲に沿って施されるLICAと対照的にチップの直ぐ近くに配置することができる。注意すべきは、ペロフスカイトがその処理温度（例えば、温度 > 600 ）の高さのために、ある種の基板材料（すなわち、有機ラミネート）の上で直接加工できることである。

40

#### 【0036】

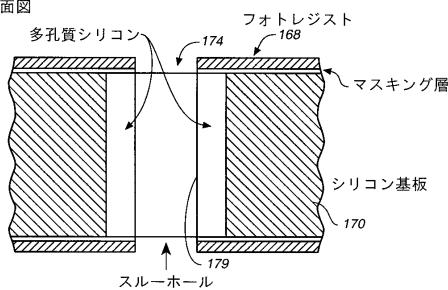

図36～図41について説明すると、そこに見られるのは、シリコン基板170に形成さ

50

れたインピーダンス調整可能なスルーピア構造 168 であり、また、スルーピア構造 168 を製造する方法の図解である。

【0037】

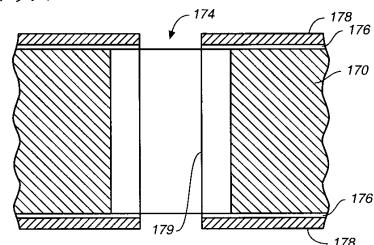

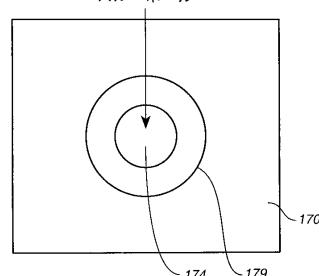

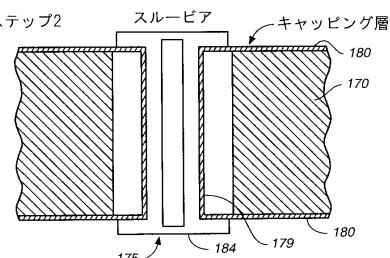

シリコン基板を集積回路 (IC) パッケージに組入れるために、これまで数通りのアプローチが開発されてきた。一例として、シリコンは、埋め込みパッシブコンポーネントを包含し、IC と PCB の間の CTE 整合を可能にし、極めて高い経路密度を許容する等々の多機能インタポーザ (multifunctional interposer) として使用できる。基板 170 等のシリコン基板をインタポーザとして使用するには、シリコン基板 170 に、IC と PCB の間の接続を形成する垂直スルーピア (例えば、図 39 のビア 175) を提供しなければならない。シリコン基板 170 において、スルーピアを適宜活用できるようにするために 10 は幾つかの要件を満たさなければならない。信号反射等を最小限に抑えるために、ビアを導電性シリコン基板 170 から絶縁しなければならず、配線のインピーダンスを他の IC 線および PCB 線のインピーダンスに整合しなければならない。ここで図 39 について説明すると、シリコン基板 170 は、多孔質シリコン領域 179 で包囲されたスルーピア 175 を含んでおり、このスルーピアは、ビア 175 をシリコン基板 170 から絶縁し、また、要件を満たすべくビア特性インピーダンスを調整するのに使用することができる。

【0038】

集積パッシブ、高密度相互接続、ディジタル機能から隔離された RF 機能、および、パッケージ内の光学系のためにマイクロ加工シリコンを使用するケースは、広く世界的に増えつつある。図 39 ~ 図 40 に描かれるように、新規のアプローチでは、50 ~ 70 の範囲でコントロールされた一定の信号線路インピーダンスをマイクロ加工シリコンパッケージ内部に供給することができる。このようなパッケージ内部の信号インピーダンス整合は、将来の高周波パッケージの用途において不可避のものとなるであろう。シリコン基板 170 に形成されたビア 175 の構造を図 36 ~ 図 39 に示す。シリコン基板 170 は、マスク層 176 とフォトレジスト 178 で被覆する。フォトレジスト 178 をパターン化し、マスク層 176 においてスルーホール 174 を形成すべくエッチングする。これで、スルーホール 174 は、マスク層 176 を通してシリコン基板 170 に形成される。電気化学的な陽極処理技術を使って、多孔質シリコン領域 179 をスルーホール 174 の周囲に迅速に形成する。多孔質シリコン領域 179 の安定化を行う。マスク層 176 とフォトレジスト 178 を除去した後、スルーホール 174 をキャッピング層 180 で覆い、続いて 20 、ビア 175 を金属メッキ 184 によって形成する。

【0039】

多孔質シリコン (PS : porous silicon) は、その幾つかの材料特性により、マイクロエレクトロニクスパッケージに使用するのが実際上有利とされる。シリコン構造の結晶性が高い上、材料密度が相対的に高い (レギュラーシリコンの 20 ~ 80 %) にも拘わらず、多孔質シリコンは絶縁材となっている。抵抗率が  $10 \text{ m} \cdot \text{cm}$  と低い高導電性シリコン基板に形成されたとしても、多孔質シリコンは、最大限  $10^{12} \cdot \text{cm}$  の抵抗率を持つことができる。その多孔質の性質のために、多孔質シリコンは誘電率が 2 と極めて低い。しかしながら、標準的な有孔率 (30 ~ 60 %) の材料であっても、誘電率は = 3 ~ 6 の範囲内である。

【0040】

フッ化水素酸の濃縮水溶液または濃縮エタノール溶液の中で、シリコン基板 170 を陽極エッチングすることによって多孔質シリコンを形成する。基板のドーピング条件またはエッチング条件に応じて、異なる種類の多孔質シリコンを作ることができる。エッチング速度は  $10 \mu\text{m} / \text{min}$  程度高くてよく、従って、相対的に短い時間でシリコンに大きい多孔質領域を形成することができる。

【0041】

多孔質シリコンがスルーホール 174 を包む絶縁構造を形成するのに数通りのプロセスフローを使用してもよい。一例に過ぎないが、シリコン基板 170 を、金属でも誘電体でもよい薄いマスク層 176 で覆う。唯一の要件は、マスク 176 がフッ化水素酸濃縮液に溶

10

20

30

40

50

けてはならないことである。基板 170 は、次に、フォトリソグラフィによってパターン化されたフォトレジスト 178 で被覆する。マスク層 176 は、フォトレジスト 178 を通してパターン化される。スルーホール 174 を、例えば、D R E I (deep reactive ion etching) を使ってシリコンにエッチングする。フッ化水素酸溶液中での陽極処理により、多孔質シリコン領域 179 がスルーホール 174 の周囲に迅速に形成される。ウェハの残りはフォトレジスト 178 で覆われるので、多孔質シリコンはスルーホール 174 の内側にしか形成されない。多孔質シリコンの表面を、250 ~ 300 の酸素雰囲気中の熱焼鈍によって安定させる（予備酸化）。形成された多孔質シリコン 179 を覆うため、この上にキャッピング層 180、例えば、CVD 酸化シリコン層をデポジットする。これにより、予備酸化された多孔質シリコンは、大気汚染および水の吸い上げから保護される。10

#### 【 0042 】

ここで注目すべきは、多孔質シリコン層 179 の特性を制御すべく調整できる可変パラメータが幾つか存在することである。先ず第 1 に、多孔質シリコン層 179 は様々な厚さに形成することができ、以下に示す通り、これがビアンピーダンスに影響する。加えて、多孔質シリコンの有孔率 (porosity) は、ビア開口を包む多孔質シリコン層 179 の誘電率を変えるべく調整することができる。また、必要であれば、多孔質シリコンを完全に酸化する、すなわち、多孔質シリコン酸化物に変換することができる。これにより、絶縁特性は改善され、誘電率は下げられる。とはいっても、完全酸化は、約 1000 とかなり高い処理温度を必要とするので、あらゆるプロセスにとって受け入れ可能ということにはならないであろう。20

#### 【 0043 】

多孔質シリコンで絶縁されたスルーホールの中にスルービアを形成する 1 つの例を図 39 に示す。多孔質シリコン 179 で満たされたスルーホール 174 をキャッピング層 180 で覆う。スルービア 175 をメッキスルーホール (P T H : plated through-hole) の形で形成するために、加法的電解メッキプロセスまたは減法的電解メッキプロセスを適用することができる。ホール 174 の縦横比に応じて、先端技術を使って、スルーホール 174 を金属で完全に満たすことができる。メッキスルーホールの場合、ビアは、標準プロセス材料の 1 つ、例えば、導電性エポキシで満たすことができる。満たされたビアの最終的構造を図 39 に示す。30

#### 【 0044 】

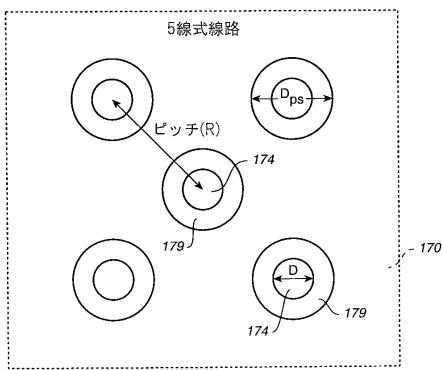

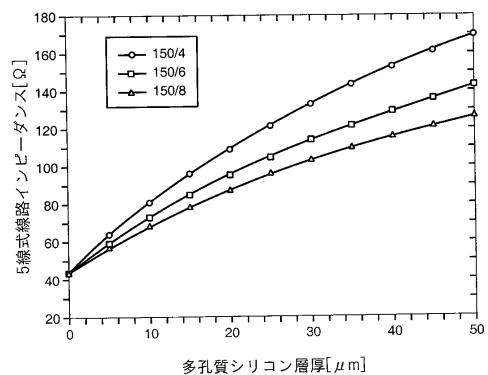

示された構造が配線インピーダンスの調整に使用できることを実証するために、数通りの多孔質シリコン誘電率について 5 線式線路インピーダンスを多孔質シリコン層の厚さの関数として計算した。前述したように、誘電率は、多孔質シリコン層の有孔率を変えることによって変更できる。計算によって得られた 5 線式線路構造の概略を図 40 に示す。計算は、ピッチ (R) を 150  $\mu\text{m}$  と仮定して行ったが、これは、フィクスチャ (fixture) で使用されている半導体ロードマップ (semiconductor road map) によって予測された数字である。ビアの直径 (D) は、一例として 30  $\mu\text{m}$  に等しいとした。多孔質シリコンリングの厚さの範囲は 0 ~ 15  $\mu\text{m}$  であった。図 41 に計算の結果を示す。多孔質シリコンリングを持たない本実施例の構成において特性インピーダンスを計算したところ、42 となつた。得られた計算結果は、多孔質シリコン絶縁を使用すると、配線インピーダンスが 40 から 130 超までの範囲内で変更できることを実証している。標準仕様は、通常、配線の特性インピーダンスが 50 ~ 70 の範囲内にあって、これが本実施例の多孔質シリコン絶縁をもって容易に達成できることを要求する。2 つのパラメータ、すなわち、多孔質シリコンの層厚と有孔率は可変であるから、極めて精密なインピーダンス調整が可能となる。40

#### 【 0045 】

このようにして、図 36 ~ 図 41 に示す本発明の実施により、電気的に絶縁されたスルービアをシリコン基板に形成できるようにするプロセスが提供される。円筒形の多孔質シリコン構造は、調整可能な特性、すなわち、誘電率と壁厚を有するので、このようにして形50

成されたスルービアのインピーダンスは、仕様要件に合致するように調整することができる。特性インピーダンスの整合により、I C パッケージの電気的特性は著しく改善される。これが、伝送線における反射を減少させ、さらに、損失の少ない電気的相互接続を可能にする。ビア絶縁のために多孔質シリコンを使用することは、他にも有機ポリマー材料を超える多くの利点を有する。そのうちの幾つかを挙げると、C T E のシリコン基板との適合性がより優れている、機械的安定性がより高い、高温処理に耐えられる（例えば、非酸化多孔質シリコンの場合は 700 以下、酸化多孔質シリコンの場合は 1000 超）等々である。

#### 【 0046 】

以上、本発明をその特定の実施例に従って説明したが、先の開示では、様々な改良、変更および代替の例が意図されており、幾つかの例において本発明の幾つかの特徴が他の特徴を同様に使用することなく、また、述べた通りの本発明の範囲および主旨から逸脱することなく使用されることは理解されよう。従って、本発明の主たる範囲および主旨から逸脱することなく、特定の状態または特定の材料を本発明の特徴的な思想および主旨に適合させるべく多くの改良を加えてよい。本発明は、本発明の実施のために考慮された最良の態様として開示された特定の実施例に限られるものでなく、付記請求項の範囲に属する全ての実施態様および等価の態様を含むものである。

10

#### 【 0047 】

（付記 1 ） キャパシタのアレイを形成し、

該キャパシタのアレイ中の前記キャパシタを電気的にテストし、欠陥のあるキャパシタを示すデータと容認できるキャパシタを示すデータとを備えるテストデータを生成し、

該テストデータを情報記憶媒体に保存し、

前記キャパシタのアレイの上に、容認できるキャパシタに電気的に結合された複数の導電性エレメントを含む相互接続構造を形成する、ことを特徴とするチップモジュールエレメントを製造する方法。

20

（付記 2 ） 付記 1 に記載の方法において、前記相互接続構造の形成は、スパッタリング、非電解メッキまたは電解メッキの少なくとも 1 つを使用して複数の導電性ポストを形成することを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

（付記 3 ） 付記 1 に記載の方法において、前記相互接続構造の形成は、

30

前記キャパシタのアレイの上に接着性結合シートをラミネートし、

前記容認できるキャパシタに隣接する前記結合シートに複数の開孔を形成し、

該開孔内部に導電性材料をデポジットすることを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

（付記 4 ） 付記 1 に記載の方法において、前記キャパシタのアレイの形成は、シリコン基板上にキャパシタのアレイを形成することを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

#### 【 0048 】

（付記 5 ） 付記 1 に記載の方法において、前記導電性エレメントは、導電性ポストと接続からなるグループの中から選択される、ことを特徴とするチップモジュールエレメントを製造する方法。

40

#### 【 0049 】

（付記 6 ） キャパシタのアレイと、

該キャパシタのアレイに結合した平面状相互接続構造と、

前記平面状相互接続構造に結合した多層回路構造であって、該平面状相互接続構造は前記キャパシタと該多層回路構造とを電気的に導通させる複数の導電性エレメントを備えているものと、

前記多層回路構造に結合した複数の導電性ピンと、を備え、

前記キャパシタのアレイは、前記ピンから前記多層回路構造を通り、導電性エレメントを通って前記キャパシタに至る電流を提供することによって充電され得るようになっている、ことを特徴とするチップモジュールエレメント。

50

(付記 7) 付記 6 に記載のチップモジュールエレメントにおいて、前記導電性エレメントは、導電性ポストと Z 接続からなるグループの中から選択される、ことを特徴とするチップモジュールエレメント。

(付記 8) 付記 1 に記載の方法において、前記キャパシタのアレイは、共通の接地層、および、キャパシタ誘電層の上の電極セグメントを含む、ことを特徴とするチップモジュールエレメントを製造する方法。

【0050】

(付記 9) 付記 8 に記載の方法において、さらに、前記電極セグメントの上にそれぞれ複数のパッドをデポジットすることを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

10

【0051】

(付記 10) 付記 8 に記載の方法において、さらに、前記キャパシタのアレイの上に第 1 誘電層をデポジットし、該第 1 誘電層に複数の開孔を形成し、その後、該開孔の中に導電性充填材をデポジットして複数の導電性コラムを形成することを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

【0052】

(付記 11) 付記 10 に記載の方法において、さらに、前記第 1 誘電層の上に複数のパッドを前記導電性ポストと接触するようにデポジットすることを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

20

【0053】

(付記 12) 付記 11 に記載の方法において、さらに、前記第 1 誘電層の上および前記パッドの上に第 2 誘電層をデポジットし、該第 2 誘電層に開口を形成して前記パッドを露出し、そして、前記開口を導電性材料で満たすことを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

【0054】

(付記 13) 付記 12 に記載の方法において、前記満たされた開口は、複数の導電性ポストを規定する、ことを特徴とするチップモジュールエレメントを製造する方法。

【0055】

(付記 14) 付記 12 に記載の方法において、前記満たされた開口は、複数の Z 接続を規定する、ことを特徴とするチップモジュールエレメントを製造する方法。

30

【0056】

(付記 15) 付記 9 に記載の方法において、さらに、前記パッドおよび電極セグメントの上に第 1 誘電層をデポジットすることを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

【0057】

(付記 16) 付記 15 に記載の方法において、さらに、前記第 1 誘電層に複数の開孔を形成して前記パッドを露出し、そして、前記開孔を導電性材料で満たすことを備える、ことを特徴とするチップモジュールエレメントを製造する方法。

【0058】

【発明の効果】

40

以上、詳述したように、本発明によれば、チップモジュールエレメントにおけるキャパシタに欠陥が生じても接地短絡によるチップモジュールエレメントの使用不能を回避することができる。

【図面の簡単な説明】

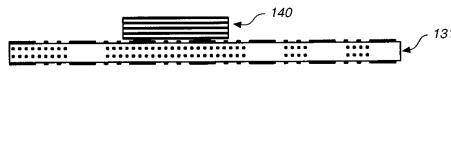

【図 1】キャパシタのアレイ、相互接続構造および多層回路構造を支持する基板を有する基板アセンブリの側部断面図である。

【図 2】コンピュータによって操作されるレーザーの概略図である。

【図 3】図 1 の基板アセンブリの他の実施例の側部断面図である。

【図 4】図 1 の基板アセンブリのさらなる実施例の側部断面図である。

【図 5】基板によって支持された誘電層と、接地層、該接地層によって支持されたキャパ

50

シタ誘電層および該キャパシタ誘電層の頂部に配置されたセグメント形電極層とを有するキャパシタとを開示する縦断面の部分拡大図である。

【図6】セグメント形電極層を含むキャパシタ誘電層の上の第2誘電層をデポジットした後、該第2誘電層の上にパッドをデポジットし、導電性材料で満たされた開口を通してパッドの1つを電極セグメント層の1つに電気的に結合し、そして、第2誘電層の上に第3誘電層をデポジットし、コンピュータ操作式レーザーを使ってパッドを露出することによって第3誘電層に開口を形成した後の、図5のアセンブリの縦断面の部分拡大図である。

【図7】第3誘電層に形成された開口を導電性材料で満たし、導電性ポストを生成した後の、図6のアセンブリの縦断面の部分拡大図である。

【図8】第3誘電層の上にパッドをデポジットし、導電性ポストと接触させた後の、図7のアセンブリの縦断面の部分拡大図である。

【図9】電極セグメント層の上にパッドを直接配置した後の、図5のアセンブリの縦断面の部分拡大図である。

【図10】マスク、誘電層または結合シートの1つをパッドおよび電極セグメント層の上に配置した後の、図9のアセンブリの縦断面の部分拡大図であり、ここで、点線は、マスク、誘電層または結合シートの1つから下へ、無欠陥のキャパシタに電気的に結合したパッドに向けてコンピュータ操作式レーザーによって形成される開口を表している。

【図11】関連するセグメント形電極層を含むキャパシタの上の第2誘電層をデポジットした後、該第2誘電層の上にパッドをデポジットし、導電性材料で満たされた開口を通してパッドの1つを、存続するキャパシタに関連する電極セグメント層の1つに電気的に結合させた後、そして、第2誘電層の上にマスク層をデポジットし、コンピュータ操作式レーザーを使ってパッドを露出することによってマスク層に開口を形成した後の、図5のアセンブリの縦断面の部分拡大図である。

【図12】熱酸化物（例えば、ケイ素酸化物）の中に包まれたシリコン基板の側部断面図である。

【図13】熱酸化物表面に第1誘電膜をデポジットした後の、図12の基板アセンブリの側部断面図である。

【図14】第1誘電膜の上に第2誘電膜をデポジットした後の、図13の基板アセンブリの側面図である。

【図15】熱酸化物層をトップとして使って基板の底側または背側を通るビアホールを形成した後の、図14の基板アセンブリの側面図である。

【図16】図15の形成されたビアホールの内壁に熱酸化物層を形成した後の、図15の基板アセンブリの側面図である。

【図17】第2誘電膜の上にキャパシタアセンブリを配置した後の、図16の基板アセンブリの側面図である。

【図18】ビアホールを導電性材料で満たした後の、図17の基板アセンブリの側面図である。

【図19】導電性材料に向けて小さいビアホールを形成した後の、図18の基板アセンブリの側面図である。

【図20】小さいビアホールを小さい導電性充填粒で満たした後の、図19の基板アセンブリの側面図である。

【図21】パッドを小さい導電性充填粒と接触させた後の、図20の基板アセンブリの側面図である。

【図22】対抗される金属（例えば、銅）被覆を施したコア基板を有する基板アセンブリの側面図である。

【図23】金属被覆をパターン化した後の、図22の基板アセンブリの側面図である。

【図24】基板にキャビティを形成した後の、図23の基板アセンブリの側面図である。

【図25】図24に示したキャビティの中に留まるコンポーネントを含む誘電アセンブリの側面図である。

【図26】対抗されるパターン化金属被覆の上に一対の誘電膜を配置した後の、図24の

10

20

30

40

50

基板アセンブリの側面図である。

【図27】誘電膜の一方の上に図25の誘電アセンブリを配置した後の、図26の基板アセンブリの側面図である。

【図28】図27の基板アセンブリの中にビアアセンブリを形成した後の、図27の基板アセンブリの側面図である。

【図29】基板、基板上に配置されたパターン化金属層、キャビティを有し、パターン化金属層の上に配置され、そこを通って延びる成形金属ポストを含む誘電層、および、関連するコンポーネントがキャビティの中に留まるように誘電層の上に配置された誘電膜を有する基板アセンブリの側面図である。

【図30】図29の基板アセンブリの他の実施例の側面図である。

10

【図31】図26の基板アセンブリ、ただし、基板の中まで延びるキャビティを有する基板アセンブリの側面図である。

【図32】関連するコンポーネントが基板内部のキャビティ部分を含むキャビティの中まで延びるように図25の誘電アセンブリを誘電膜の一方の上に配置した後の、図31の基板アセンブリの側面図である。

【図33】ビアアセンブリを内部に形成した後の、図32の基板アセンブリの側面図である。

【図34】両側が同様に処理してあり、基板が一対の誘電膜と関連するコンポーネントを収容する一対のキャビティを有し、示す通りのピンを備えた図29の基板アセンブリの側面図である。

20

【図35】図30の基板アセンブリに類似した、内部にコンポーネントが留まるキャビティを含む基板アセンブリの側面図である。

【図36】壁が多孔質シリコンでできたスルーホールを有するシリコン基板の縦断面図である。

【図37】スルーホールおよび多孔質シリコン壁を描くシリコン基板の平面図である。

【図38】図36のシリコン基板の他の縦断面図である。

【図39】スルービアを生成するためにスルーホールを導電性充填材で満たした後の、図39のシリコン基板の縦断面図である。

【図40】線路インピーダンス整合レンジの評価に使用される5線式線路構成を有する基板の平面図である。

30

【図41】多孔質シリコン層の厚さ(μm)と5線式線路インピーダンス( )との関係のグラフを示す図である。

#### 【符号の説明】

10...基板アセンブリ

12a...基板

16...キャパシタのアレイ

16a~16g...キャパシタ

17, 87...誘電層

18...接地層

19...セグメント形電極層

40

19a~19f...電極層セグメント

20...表面誘電層

26a-26b...接地ピン

30, 32...導電性線路

31a-31b; 33a-33b...接地パッド

36...電極層

37a, 37b; 39a, 39b; 41a, 41b; 43a, 43b; 45a, 38, 40, 42, 44, 46, 48, 50...Z接続

45b; 47a, 47b; 49a, 49b...パッド

54...多層回路構造

50

- 5 8 ... 相互接続構造

6 0 , 6 1 ... 電圧ピン

6 3 , 6 4 ... 信号ピン

7 8 ... レーザー

8 0 ... コンピュータ

8 2 ... メモリバンク

8 9 ; 8 9 c , 8 9 d , 8 9 f ... 導電性コラム

1 0 0 ... シリコンウエハ

1 0 4 ... SiO<sub>2</sub>包囲層

1 0 8 , 1 1 0 ... 誘電層 10

1 1 4 ... SiO<sub>2</sub>熱酸化物層 (スルービア)

1 1 6 , 1 2 4 , 1 7 5 ... ビア

1 2 0 ... 導通媒体

1 2 8 ... プレート

1 3 0 ... コア基板

1 3 1 ... 接着性誘電膜

1 5 4 ... ブラインドビア・アセンブリ

1 5 8 ... Z接続

1 6 0 ... 金属ポスト

1 6 4 ... ピン 20

1 6 8 ... スルービア構造

1 7 0 ... シリコン基板

1 7 4 ... スルーホール

1 7 6 ... マスク層

1 7 8 ... フォトレジスト

1 7 9 ... 多孔質シリコン領域 (多孔質シリコン層)

1 8 0 ... キャッピング層

1 8 4 ... 金属メッキ

【 四 1 】

【 図 2 】

【 义 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

図13 II. ウェーハ上に追加の誘電膜(1~50ミクロン)をデポジットする。

代替実施例では、工程IVおよびVを最初に行う。

【図14】

図14 III. 接着状態または応力状態を確保する目的で任意のさらなる誘電層をデポジットする

【図15】

図15 IV. 熱酸化物を止めとして使って背側をプラズマ、レーザーまたは化学的方法によってドリリングし、それでビアを形成する（場合によっては、予備ドリルマスキングとその後のマスク除去のプロセスを必要とする）

【図16】

図16 V. 止められたビアホールを絶縁するために0.25~3ミクロンの熱酸化物を成長させる

【図17】

図17 VI. キャバシタ作成プロセスを実行する

【図20】

図20 IX. ビア124に導通充填材からなるプレートでメッキを施す（場合によっては、

a)背側の導体シードのデポジションとその後の

b)正面側のマスキングとその後のマスク除去

を必要とする）

【図21】

図21 X. プロセスによっては、パッド、相互接続構造、経路等をマスクし、メッキする追加的プロセスを行ってもよい（工程IXに組み込まれていなかった場合）

【図18】

図18 VII. ビアホールを導電性媒体で満たす。接着を促進する層、例えば、TiN層が最初要求されることもあり得る（注：この充填をキャバシタ作成に先立って行なうことが可能であってもよい）。

【図19】

図19 VIII. プラズマ、レーザーまたは化学的方法によるドリリングによって導通充填材まで届く小さなビア124を形成する（場合によっては、予備ドリルマスキングとその後のマスク除去のプロセスを必要とする）

【図22】

図22 I. 単層または多層のコア基板。実施例は、銅被覆を施したコア基板と、施していないコア基板とを含む。実施例は、また、内側Cu層を持つコア基板も含む。さらなる実施例は、樹脂被覆銅(RRC)を利用する。ある実施例では、コアが導通スルービアを有する。

【図23】

図23

必要であれば、Cuをパターン化する。

a)ある実施例では、Cuを完全に蝕刻し、コンポーネントを埋め込むべき場所を空ける。ある実施例では、コンポーネントを両側に埋め込む。

【図24】

図24

b)ある実施例では、コアの、コンポーネントが埋め込まれる場所にキャビティを形成する。ある実施例では、コンポーネントを両側に埋め込む。

【図25】

図25

埋め込むべきコンポーネントを、先に処理された分離した誘電膜(可能であれば、多層)または可撓膜の上に組み立てる。ある実施例では、高温はんだ(例えば、Au-20Sn、Au-12Ge、Au-3.5SiまたはPb-5Sn)をこの工程で使って、その後の処理およびコア基板の使用における信頼性を確保する。ある実施例では、誘電膜の下側(場合によっては、上側になる)にパッド層が存在しない。ある実施例では、(例えば、基板の下側となるべく)露出する膜表面にピン、スタッド瘤またははんだ瘤を取り付けてもよい。

【図28】

図28

IVa-3)スルーピアをドリル、デスマニア、eレス、Cuシード/ブレート、eブレートCuによって形成し、次に、スルーピアを充填してから、バネル化する。誘電膜の露出側にパッド層が存在しない実施例では、パターン化および/またはパッド層作成を行ってよい。ある実施例では、ビアにCuキャップをかぶせてよい。ある実施例では、二通りのドリリング工程を使用してもよいが、いかなるビアもコアを貫通してはならない(ブライドビア)。

【図29】

図29

IVb-1)ラミネート化の間に、技術的に知られたはんだ付けまたは導電性ペースト充填によってZ接続を接着性誘電膜に作る。片側処理のみ図示する。

【図26】

図26

IV. コアへの取り付けが可能な多数の手段(および、その組合せ)が、ここでキャビティなしのコアをもって可能となる。

IVa-1)誘電層を置くか、流すか、または、ラミネート化させる。必要であれば、ブリカットされた“ブリブレグ”(または、類似材料)のアライメントを行う。補助の下込め材、“グロップトップ”、または、他の接着/密封材を任意に、後続の処理に先立ってコンポーネント全体に施してもよい。

【図27】

図27

IVa-2)分離した誘電膜をラミネート化させる。誘電膜は、応力釣合いのために両側でラミネート化してもよい。

【図30】

図30

IVc-1)金属ポスト(例えば、Cu)をコア(または、コア上に留まるスベーサ)の上に立てる。この場合は、Z接続を、ラミネート化の間に、技術的に知られた薄肉はんだ、拡散結合過渡液または導電性ペースト充填によって作る。片側処理のみ図示する。

【図31】

図31

V. コアへの取り付けが可能な多数の手段(および、その組合せ)が、ここでキャビティを設けたコアをもって可能となる。

Va-1)誘電層を置くか、流すか、または、ラミネート化させる。必要であれば、ブリカットされた“ブリブレグ”(または、類似材料)のアライメントを行う。補助の下込め材、“グロップトップ”、または、他の接着/密封材を任意に、後続の処理に先立ってコンポーネント全体に施してもよい。

【図32】

図32

Va-2)分離した誘電膜をラミネート化させる。誘電膜は、応力釣合いのために両側でラミネート化してもよい。

【図33】

図33

Va-3)スルーピアをドリル、デスマニア、eレス、Cuシード/プレート、eプレートCuによって形成し、次に、スルーピアを充填してから、バネル化する。誘電膜の露出側にパッド層が存在しない実施例では、バーチャル化および/またはパッド層作成を行ってもよい。ある実施例では、ピアにCuキャップをかぶせてもよい。ある実施例では、二通りのドリリング工程を使用してもよいが、いかなるピアもコアを貫通してはならない(ブラインドピア)。

【図34】

図34

Vb-1)ラミネート化の間に、技術的に知られたはんだ付けまたは導電性ペースト充填によってZ接続を接着性誘電膜に作る。ピン使用の両側処理を図示する。

【図35】

図35

Vc-1)金属ポスト(例えば、Cu)をコア(または、コア上に留まるスペーサ)の上に立てる。この場合は、Z接続を、ラミネート化の間に、技術的に知られた薄内はんだ、拡散結合過渡液または導電性ペースト充填によって作る。片側処理のみ図示する。

【図36】

図36

III. 図解

断面図

【図38】

図38

半径方向多孔質シリコン絶縁を持つスルーホールの構造

ステップ1

【図37】

図37

平面図

スルーホール

【図39】

図39

配線インピーダンス整合を可能にする多孔質シリコン絶縁を持つスルーホールの構造

ステップ2

【図40】

図40

線路インピーダンス整合レンジの推定に使用される5線式線路構成

【図41】

図41

多孔質シリコン層厚の関数として計算された5線式線路インピーダンス。計算は、ピットを $150\mu\text{m}$ と仮定し、3通りの多孔質シリコン誘電率 $\epsilon=4$ 、6および8について行った。

---

フロントページの続き

(72)発明者 マーク トーマス マコーマック

アメリカ合衆国, カリフォルニア 94550, リバーモア, ホワイト オーク プレイス 23

56

(72)発明者 マイケル ジー. ピーターズ

アメリカ合衆国, カリフォルニア 95051, サンタ クララ, ジアニーニ ドライブ 485

審査官 藤原 敬士

(56)参考文献 特開平07-030258 (JP, A)

特開2000-003980 (JP, A)

特開平04-184962 (JP, A)

特開平01-042849 (JP, A)

特開2001-196497 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12