**Patent Number:**

# United States Patent [19]

[11] E

# DeLisle et al.

# [54] HARDWARE BASED INTERFACE FOR MODE SWITCHING TO ACCESS MEMORY ABOVE ONE MEGABYTE

- [75] Inventors: David J. DeLisle, Spring; Saifuddin Fakhruddin, Tomball; Lloyd Gauthier, Austin, all of Tex.; Robert A. Kohtz, Cedar Rapids, Iowa

- [73] Assignee: Zenith Data Systems Corporation, Sacramento, Calif.

- [21] Appl. No.: 317,757

- [22] Filed: Oct. 4, 1994

# **Related U.S. Patent Documents**

Reissue of:

| [64] | Patent No .: | 5,283,889     |

|------|--------------|---------------|

|      | Issued:      | Feb. 1, 1994  |

|      | Appl. No.:   | 31,029        |

|      | Filed:       | Mar. 11, 1993 |

| 110  |              |               |

- U.S. Applications:

- [63] Continuation of Ser. No. 735,619, Jul. 25, 1991, abandoned, which is a continuation-in-part of Ser. No. 459,055, Dec. 29, 1989, abandoned.

### [56] References Cited

#### **U.S. PATENT DOCUMENTS**

4,453,211 6/1984 Askinazi et al. ..... 364/200

# [45] Reissued Date of Patent: Mar. 18, 1997

Re. 35,480

| 4,503,491 | 3/1985  | Lushtak et al 364/200 |

|-----------|---------|-----------------------|

| 4,727,480 | 2/1988  | Albright et al        |

| 4,779,187 | 10/1988 |                       |

| ,,        |         |                       |

| 4,787,032 | 11/1988 | Culley 364/200        |

| 4,899,306 | 2/1990  | Greer                 |

| 4,926,322 | 5/1990  | Stimac et al 364/200  |

| 4,942,606 | 7/1990  | Kaiser et al 380/4    |

| 4,943,910 | 7/1990  | Nakamura 364/200      |

| 4,959,860 | 9/1990  | Watters et al 380/4   |

| 4,984,213 | 1/1991  | Abdoo et al           |

| 4,985,871 | 1/1991  | Catlin 365/230.06     |

| 5,001,704 | 3/1991  | Narup et al 370/85.13 |

| 5,018,062 | 5/1991  | Culler et al 395/493  |

| 5,021,983 | 6/1991  | Nguyen et al          |

| 5,083,259 | 1/1992  | Maresh et al 395/325  |

| 5,283,889 | 2/1994  | DeLisle et al 395/500 |

| 5,381,530 | 1/1995  | Thayer et al 395/275  |

Primary Examiner-Mehmet B. Geckil

Attorney, Agent, or Firm-Fitch, Even, Tabin & Flannery

## [57] ABSTRACT

A relatively fast system control processor, such as an Intel 8051, is substituted for an Intel 8042 microprocessor in a PC/AT type compatible personal computer. In one embodiment of the invention, a System Control Processor Interface (SCPI) is provided between the central processing unit (CPU) and the system control processor (SCP) to maintain compatibility with the PC/AT bus. The combination of the faster SCP and the SCPI interface improves the overall system performance. Control circuitry is also provided for setting the A20 signal relatively quickly to allow memory access above one megabyte. In an alternate embodiment of the invention, a Mouse Keyboard Interface (MKI) is provided. The MKI provides even quicker switching of the Gate A20 signal by eliminating the need to interrupt the SCP. The MKI also provides support for a type PS/2 mouse.

## 6 Claims, 34 Drawing Sheets

Sheet 7 of 34

Re. 35,480

FIG. 12A

FIG. 12C

**U.S.** Patent

Re. 35,480

FIG.14B

FIG.15B

FIG.19

25

30

50

65

# HARDWARE BASED INTERFACE FOR MODE SWITCHING TO ACCESS MEMORY **ABOVE ONE MEGABYTE**

Matter enclosed in heavy brackets [] appears in the 5 original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue.

This application is a reissue application of Ser. No. 08/031,029, filed Mar. 11, 1993, issued on Feb. 1, 1994 as 10 U.S. Pat. No. 5,283,889, which is a continuation application of Ser. No. 07/735,619, filed Jul. 25, 1991, now abandoned which is a [continuation] continuation-in -part application of U.S. patent application Ser. No. 07/459,055 filed Dec. 29, 1989, now abandoned entitled FAST SWITCHING 15 MEMORY MODE SYSTEM.

This application is also related to an application for a PROCESS FOR IMPLEMENTING KEYNET IN PER-SONAL COMPUTERS, Ser. No. 07/459,042, filed on Dec. 29, 1989 now abandoned in favor of continuation applica- 20 responsibility for switching the A20 signal from the SCP. tion Ser. No. 08/019,997 filed on Feb. 17, 1993.

#### BACKGROUND OF THE INVENTION

1. Field of the Invention

This invention relates to a system control processor interface for an IBM PC/AT type compatible personal computer which emulates an Intel type 8042 system control processor and a control circuit for minimizing the time required to access memory above one megabyte.

2. Description of the Prior Art

Newer PC/AT compatible personal computers utilizing either of Intel's microprocessors 80286, 80386 or 80486 as a central processing [units] unit (CPU) are designed to be software compatible with a PC/XT type compatible personal <sup>35</sup> computer. The PC/XT machines utilize an Intel type 8088 microprocessor as a CPU which has only 20 address lines, A0-A19. Consequently, such microprocessors can only access memory up to one megabyte.

40 Intel 80286, 80386 or 80486 microprocessors have 24 address lines, A0-A23, which allow them to access memory up to sixteen megabytes. In order to be compatible with a type PC/XT software and also access memory above one megabyte, these microprocessors have two operating modes; 45 a real mode and a protected mode.

In the real mode, the object code of these microprocessors is compatible with a PC/XT machine based software. In the protected mode, all addresses are relative and the microprocessor can access memory above the one megabyte boundary. Consequently, while in the protected mode, their object code is no longer compatible with a PC/XT machine.

Switching between modes is controlled by an A20 signal from a keyboard controller also known as a system control processor (SCP). However, since [todays] today's comput-55 ers run much faster than their predecessors, there can be a problem with some programs that set the A20 signal. More specifically, known programs can write a command and data to set the A20 signal. After a predetermined time-out, the system continues executing under the assumption the A20 signal is correctly set. Because newer computers run much faster than some programs allow, the time-out can expire before the A20 signal is actually set. This will cause the computer to run code out of the wrong memory space resulting in a hung system.

Another problem in many known PC/AT compatible personal computers is that the switching of the A20 signal is

generally controlled by the SCP, generally an Intel-type 8042 microprocessor. The type 8042 microprocessor is slow relative to other microprocessors, such as an Intel 8051 microprocessor. For example, an Intel 8042 microprocessor has a 2.5 microsecond instruction time as opposed to a 1 microsecond instruction time for an Intel 8051. However, in order to be compatible with a PC/AT-bus, any substitution of the SCP requires emulation of an Intel 8042.

#### SUMMARY OF THE INVENTION

It is an object of the present invention to provide a personal computer which solves the problems associated with the prior art.

It is another object of the present invention to provide means for switching the A20 signal relatively faster than prior art machines.

It is yet another object of the invention to remove the sole

It is a further object of the present invention to provide a circuit which switches the A20 signal relatively quickly to allow for access to memory space above one megabyte.

It is yet a further object of the present invention to provide [a SCP] an SCP that is relatively faster than [a Intel-8042] an Intel 8042 microprocessor.

It is yet another object of the present invention to provide an interface which emulates an [Intel-8042] Intel 8042 microprocessor.

#### DESCRIPTION OF THE [DRAWING] DRAWINGS

These and other objects and advantages of the present invention will become readily apparent upon consideration of the following detailed description of the attached [drawing] drawings wherein:

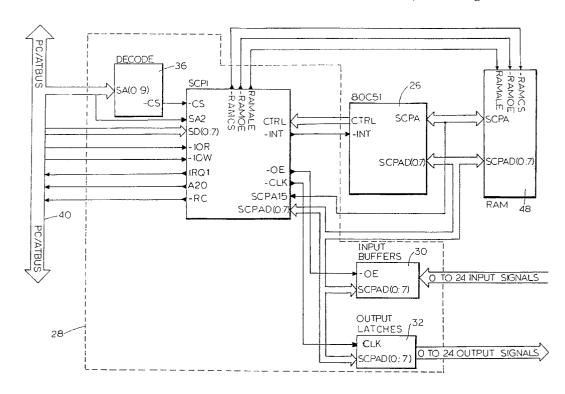

FIG. 1 is a simplified block diagram of a portion of a prior art type PC/AT compatible personal computer illustrating an Intel 8042 microprocessor as an SCP;

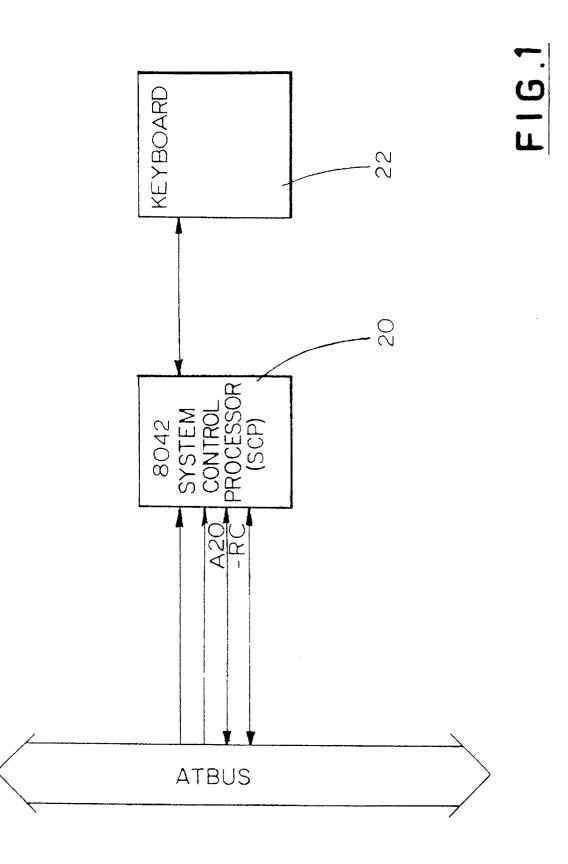

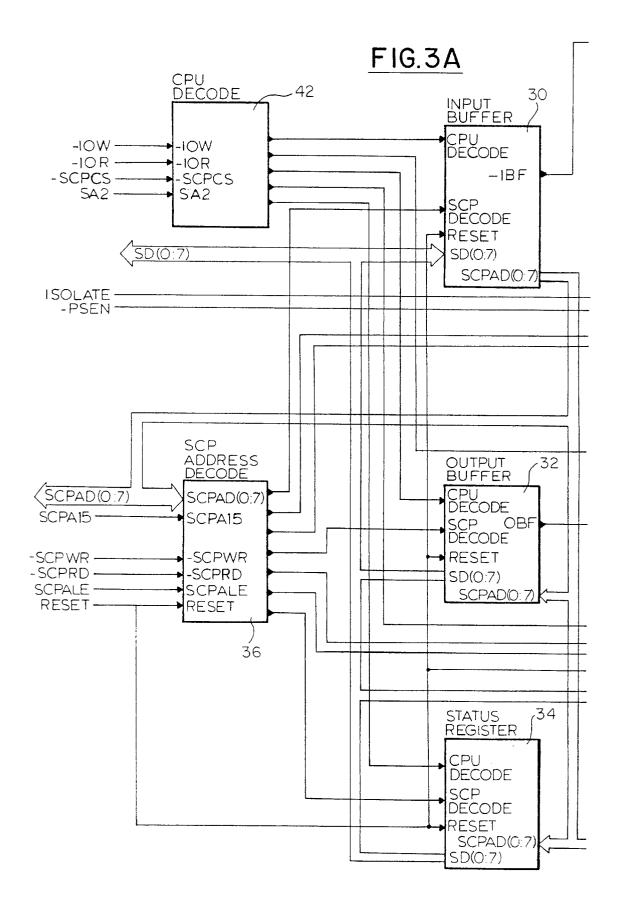

FIG. 2 is a block diagram of the system in accordance with the present invention which utilizes a system control processor interface (SCPI) for emulating an Intel 8042 bus;

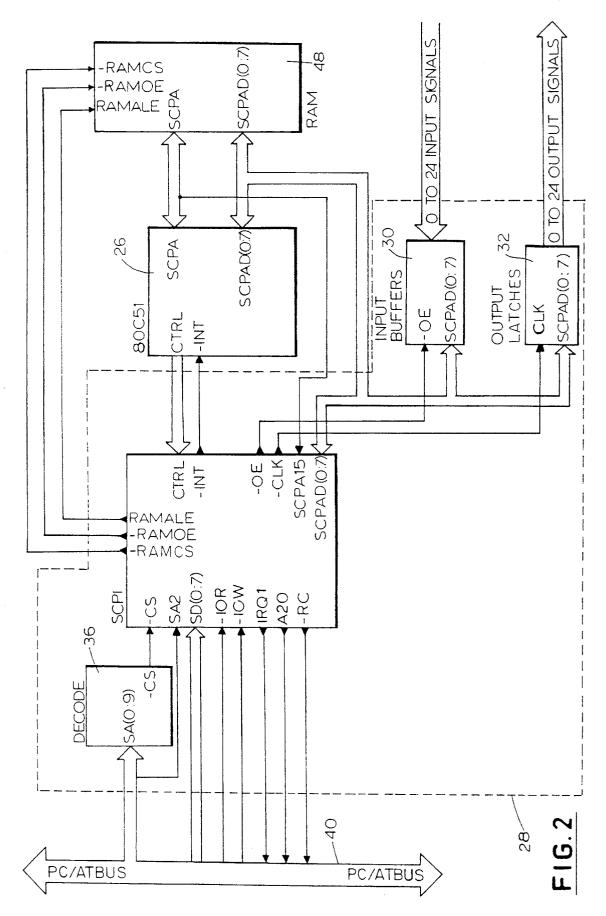

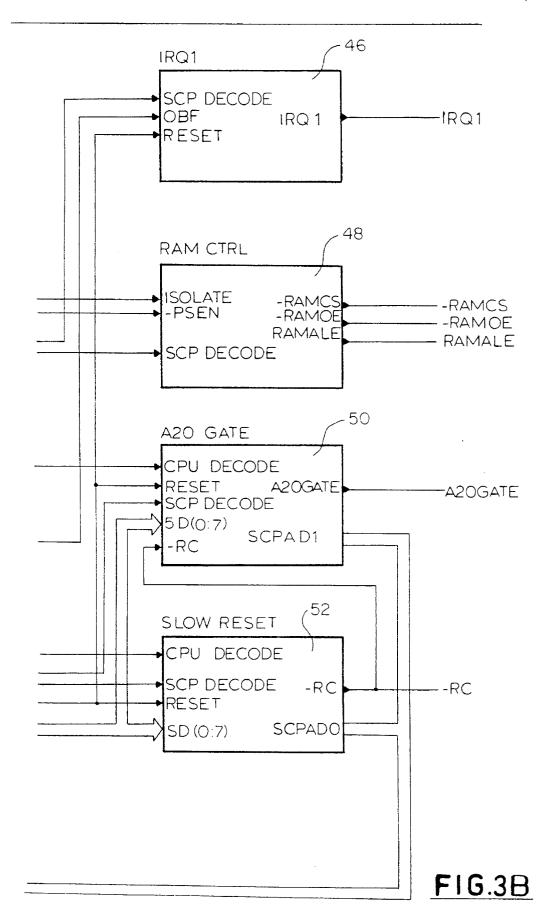

FIGS. 3A and 3B represent a block diagram of the SCPI in accordance with the present invention;

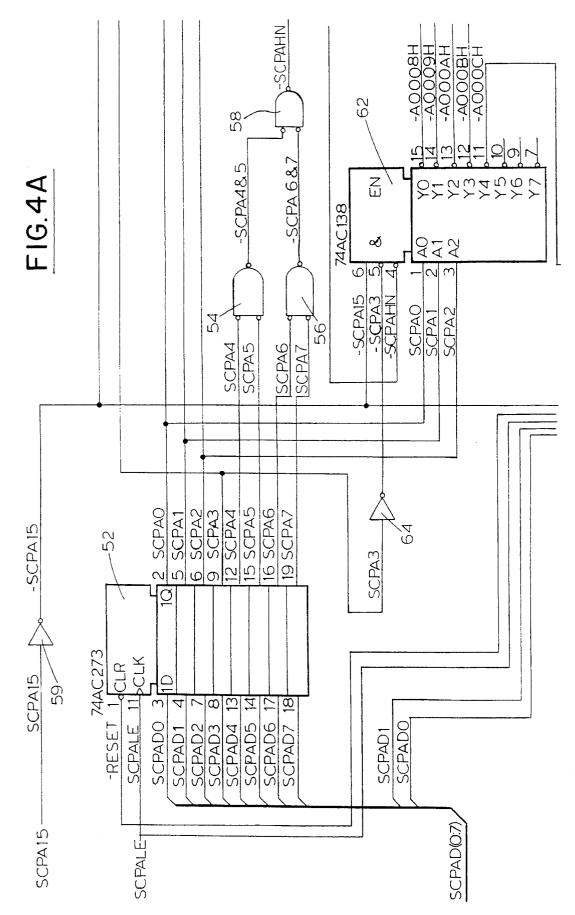

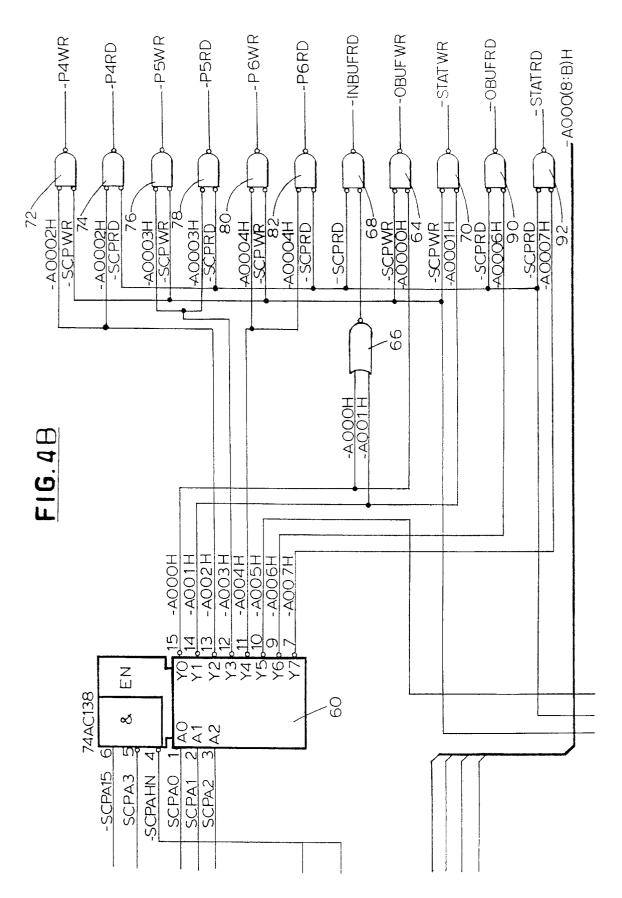

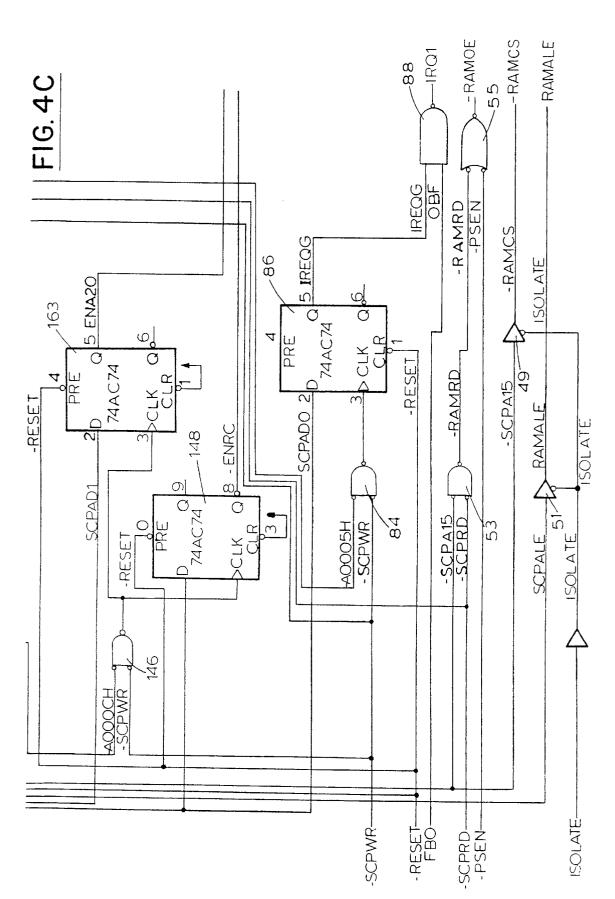

FIGS. 4A, 4B and 4C represent a schematic diagram of the address decoding circuitry in the SCPI in accordance with the present invention;

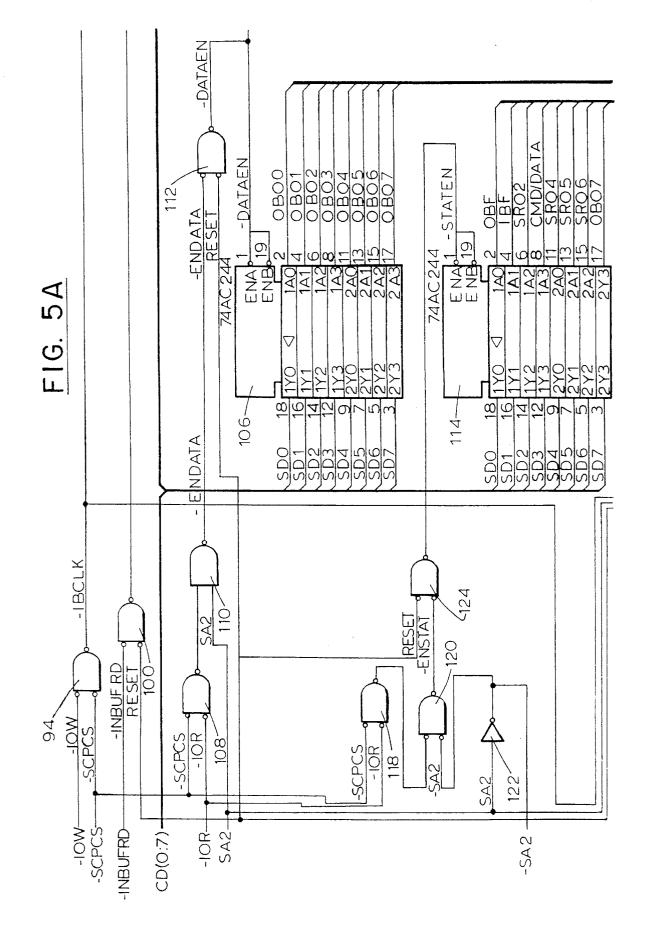

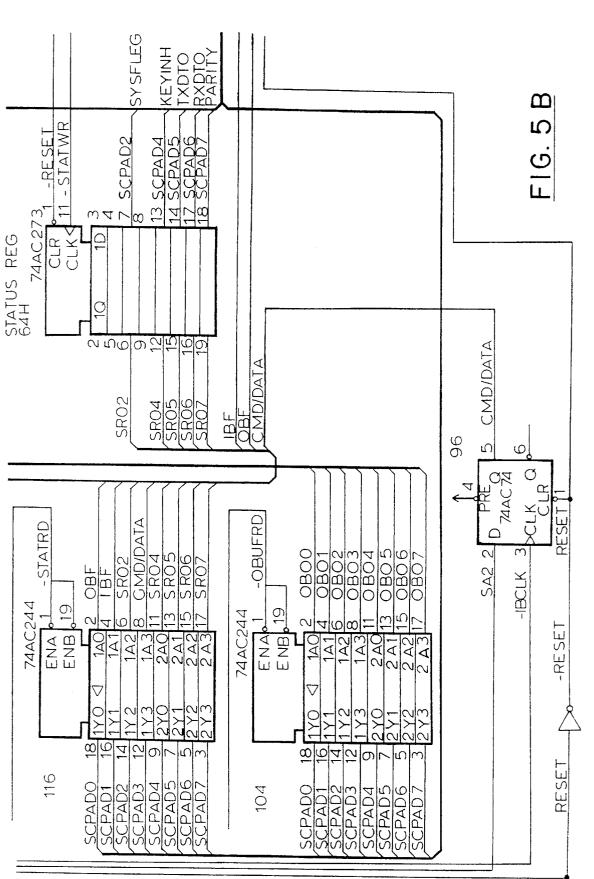

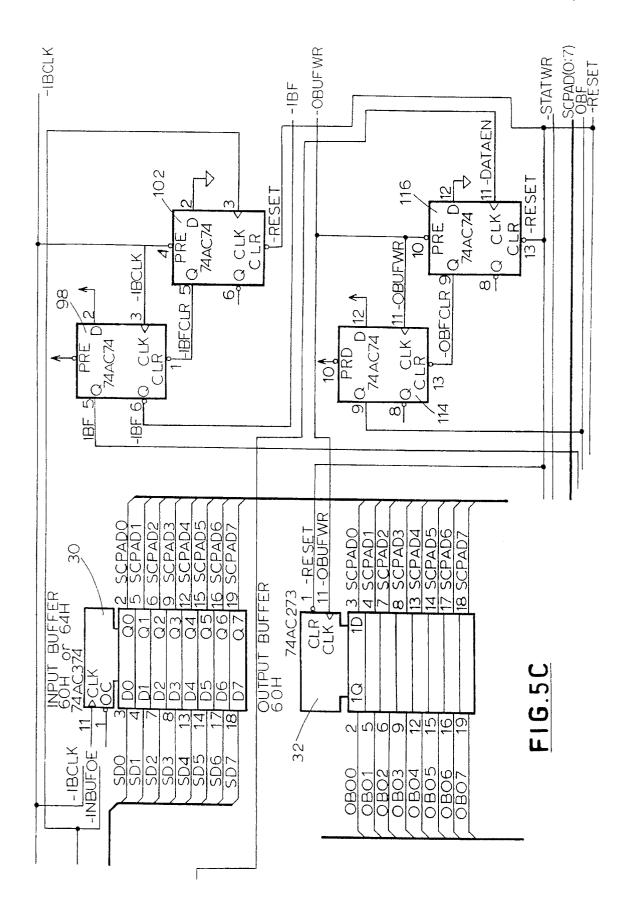

FIGS. 5A, 5B and 5C represent a schematic diagram of SCP/CPU interface logic circuitry in accordance with the present invention;

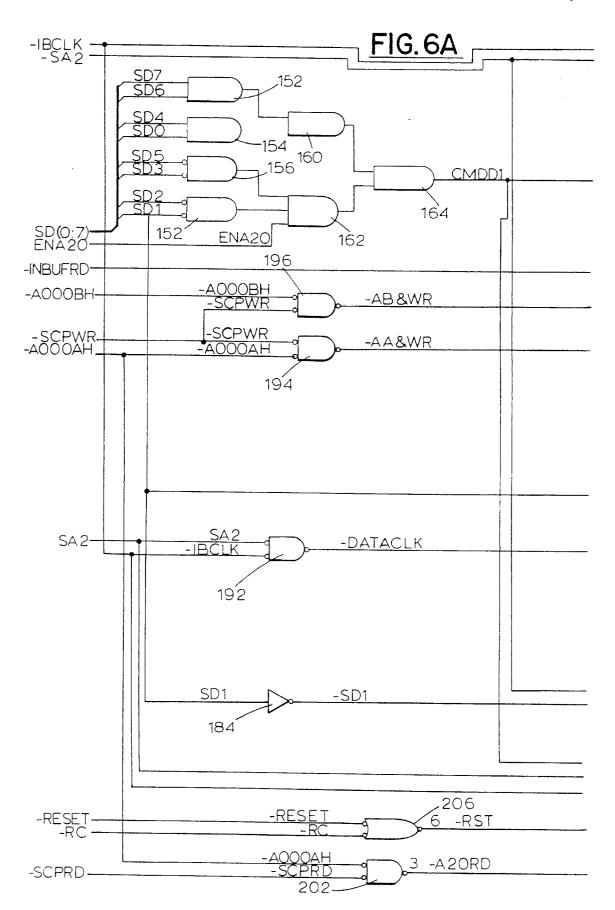

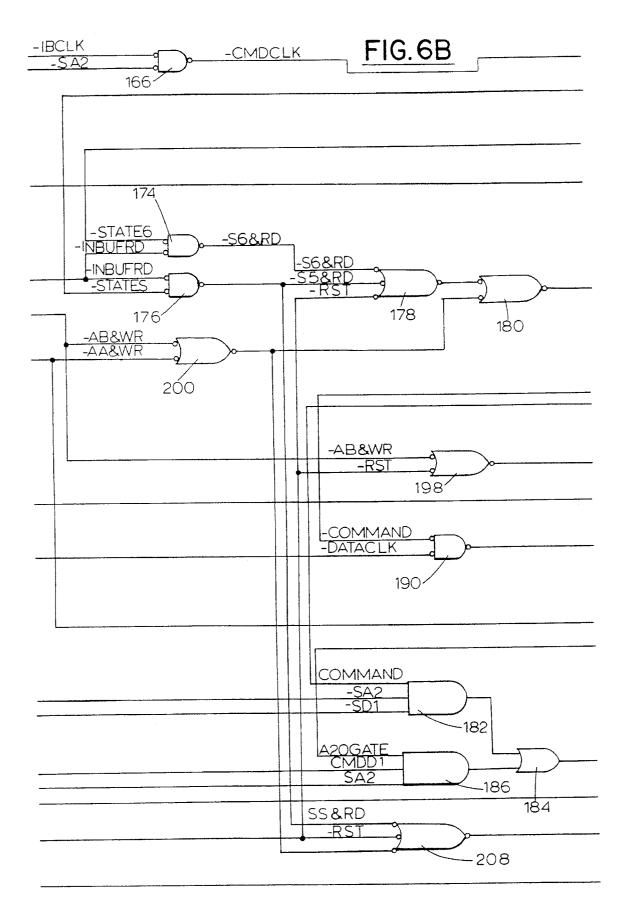

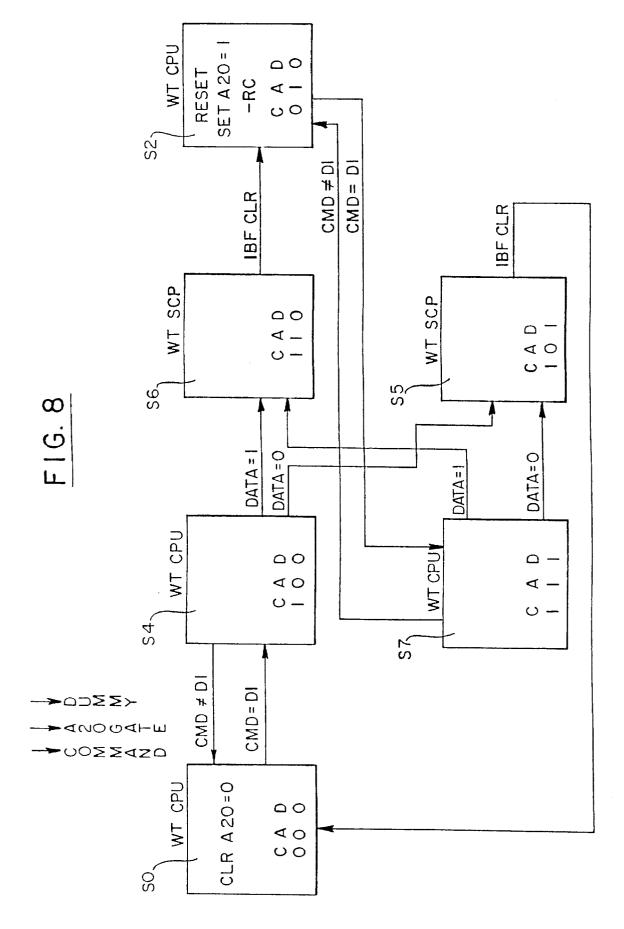

FIGS. 6A, 6B and 6C represent a schematic diagram of the control logic for the A20 signal control in accordances with the present invention;

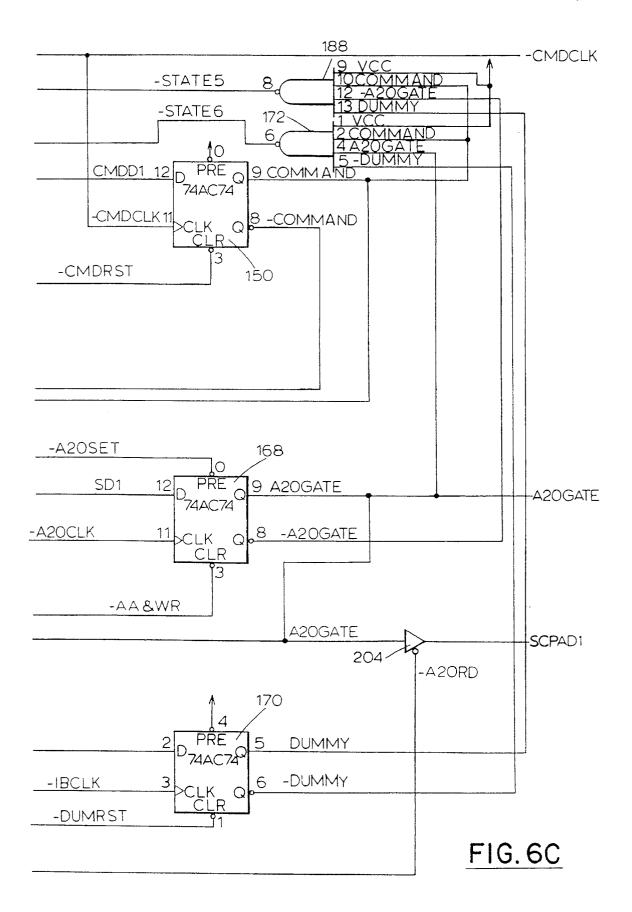

FIG. 7 is a schematic diagram of slow reset control logic in accordance with the present invention;

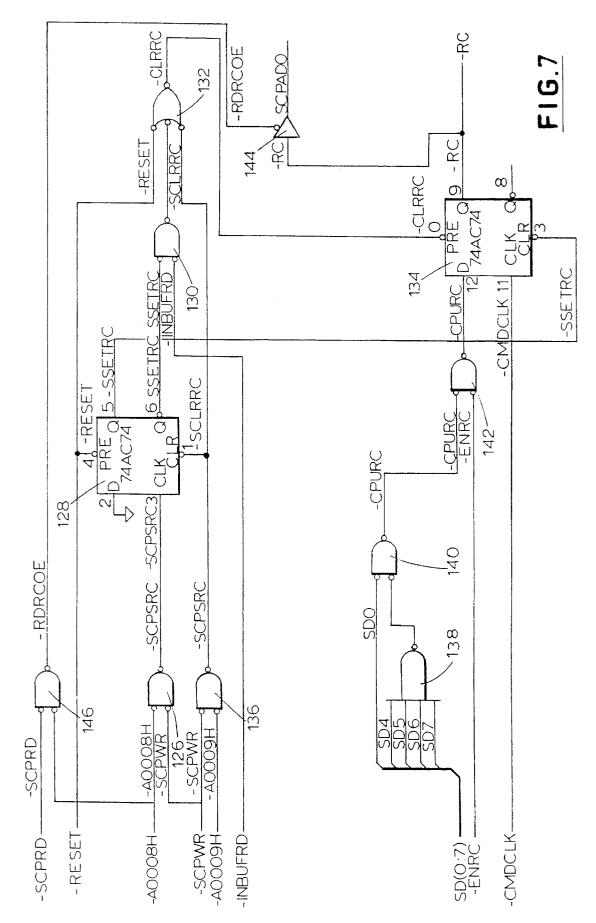

FIG. 8 is a state diagram of the A20 signal control logic in accordance with the present invention;

FIG. 9 is a pin-out diagram for the SCPI in accordance with the present invention;

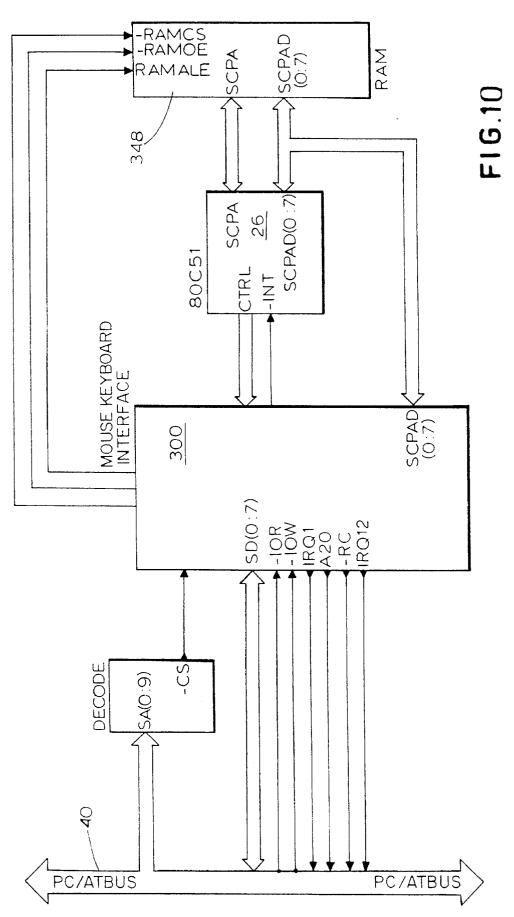

FIG. 10 is a block diagram of a system in accordance with an alternate embodiment of the present invention which utilizes a mouse keyboard interface (MKI) for emulating an Intel 8042 bus;

25

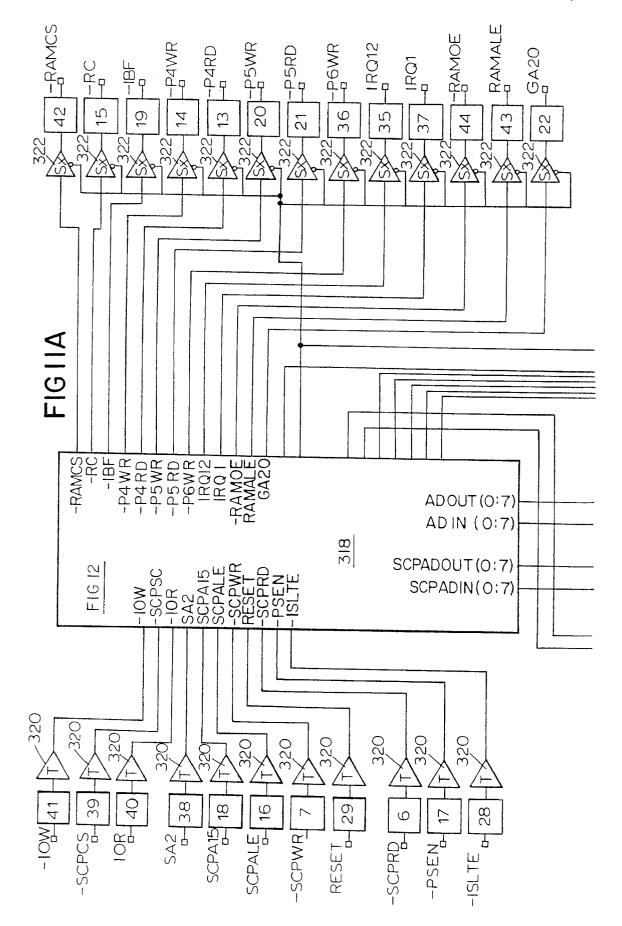

FIGS. 11A and 11B represent a top level diagram of a mouse keyboard interface (MKI) illustrated in FIG. 10;

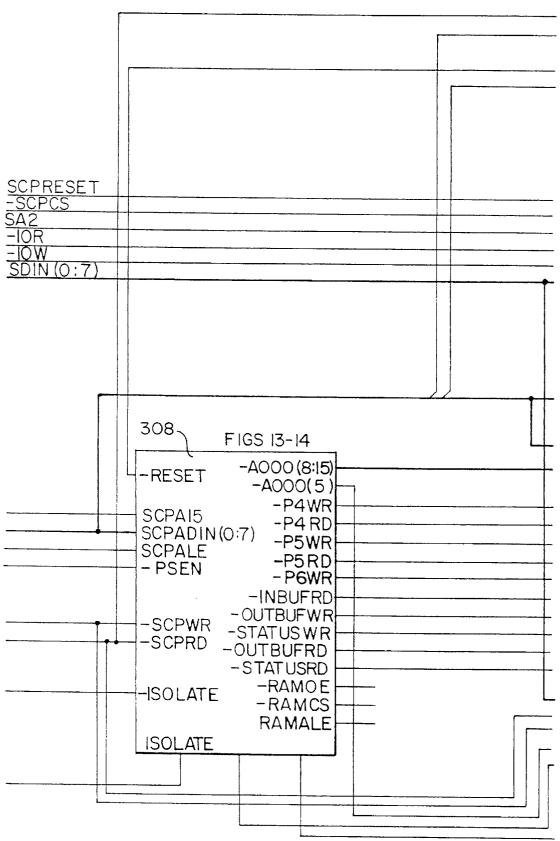

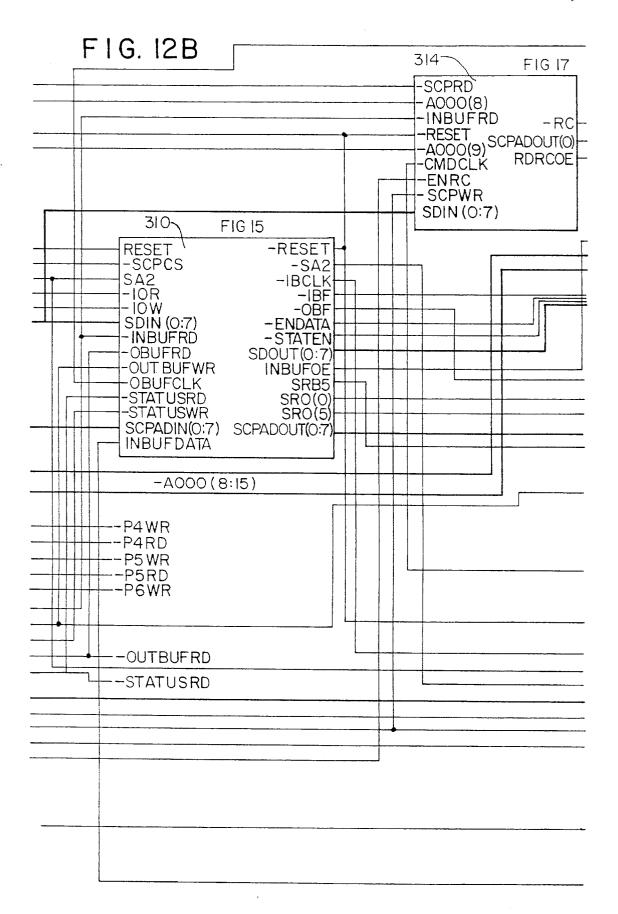

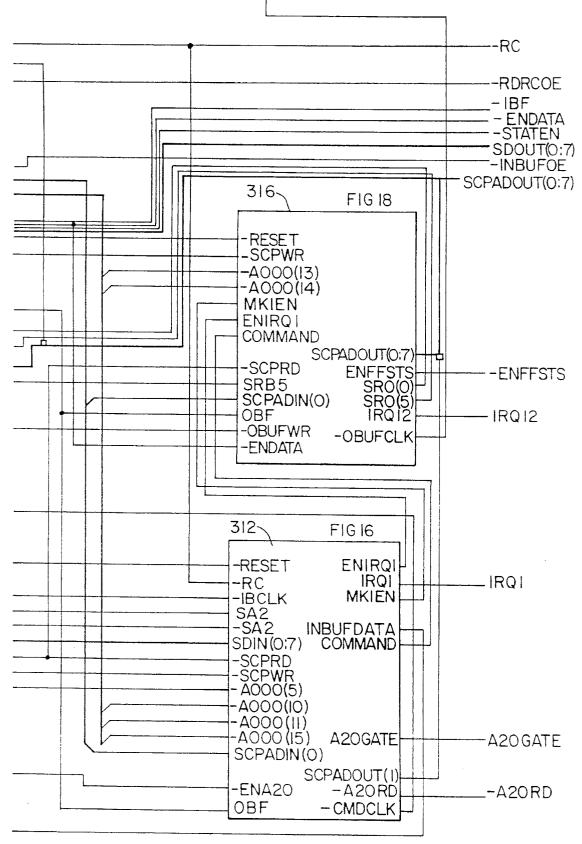

FIGS. 12A, 12B and 12C represent a block diagram of the MKI illustrated in FIGS. 11A and 11B;

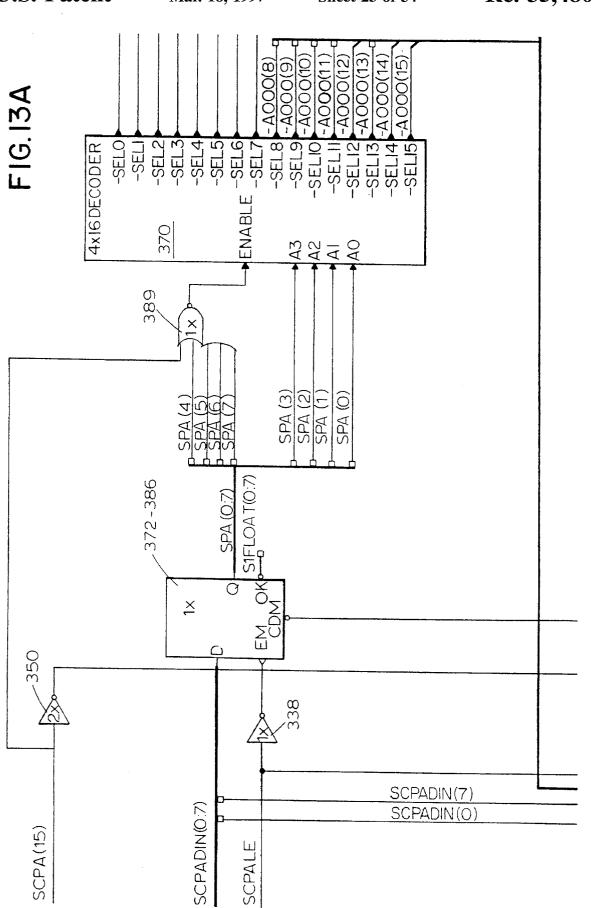

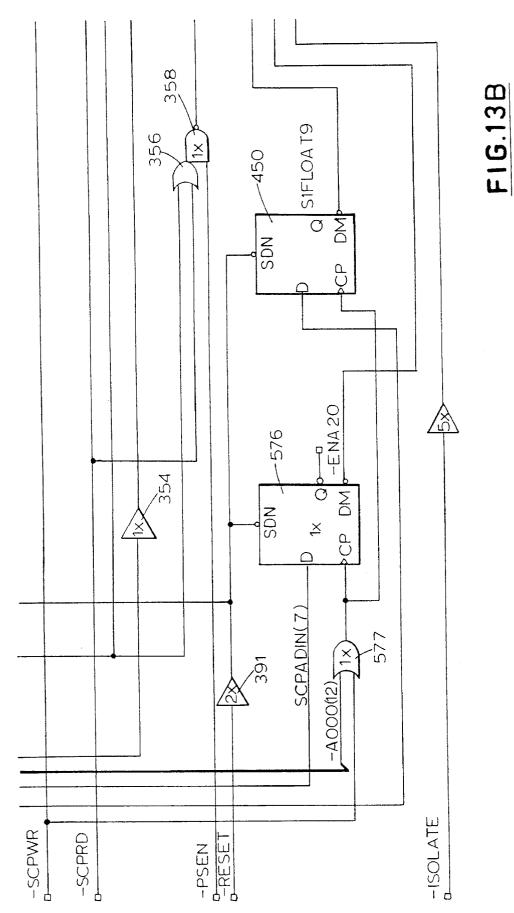

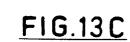

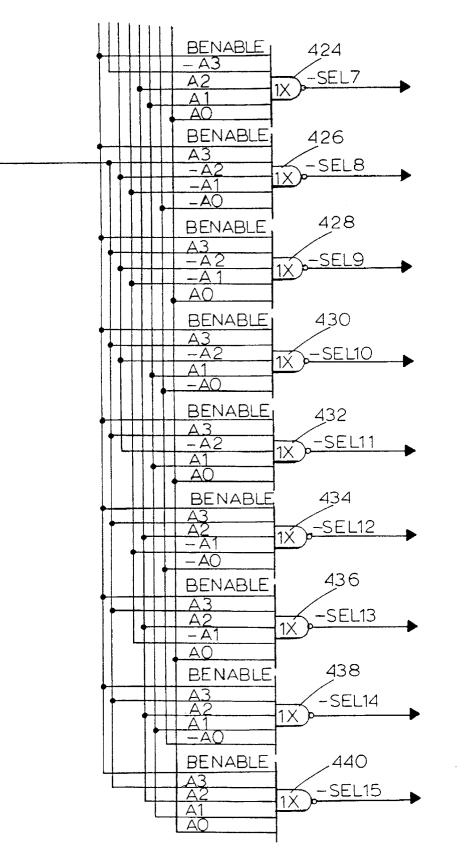

FIGS. **13**A, **13**B and **13**C represent a schematic diagram of the address decode and RAM control logic in accordance with the present invention;

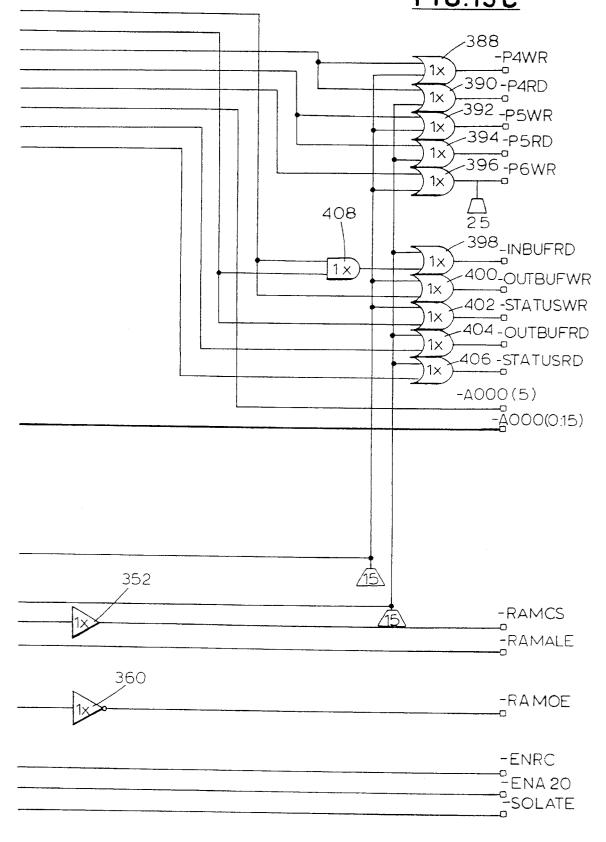

FIGS. 14A and 14B represent a schematic diagram of an address decode circuit in accordance with the present invention;

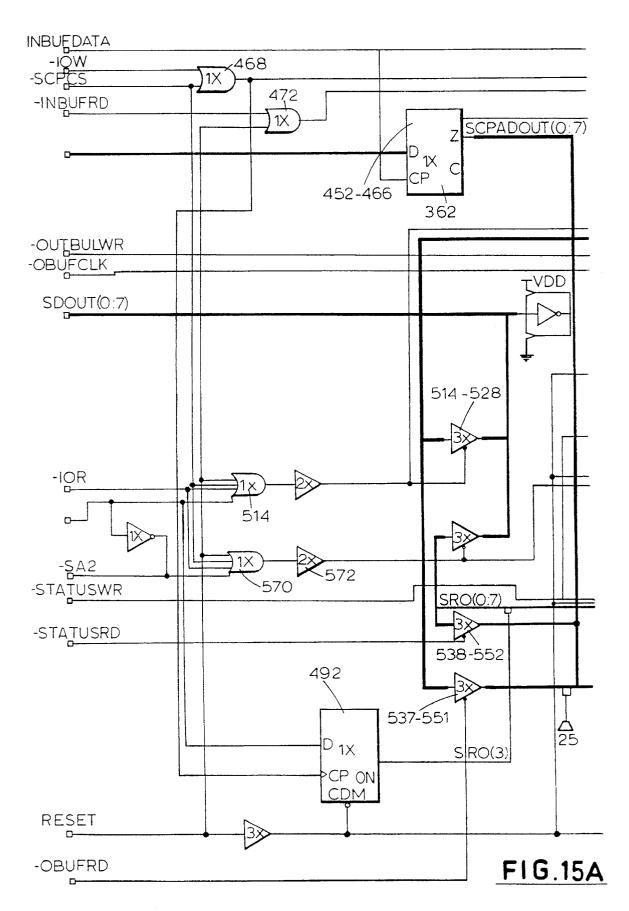

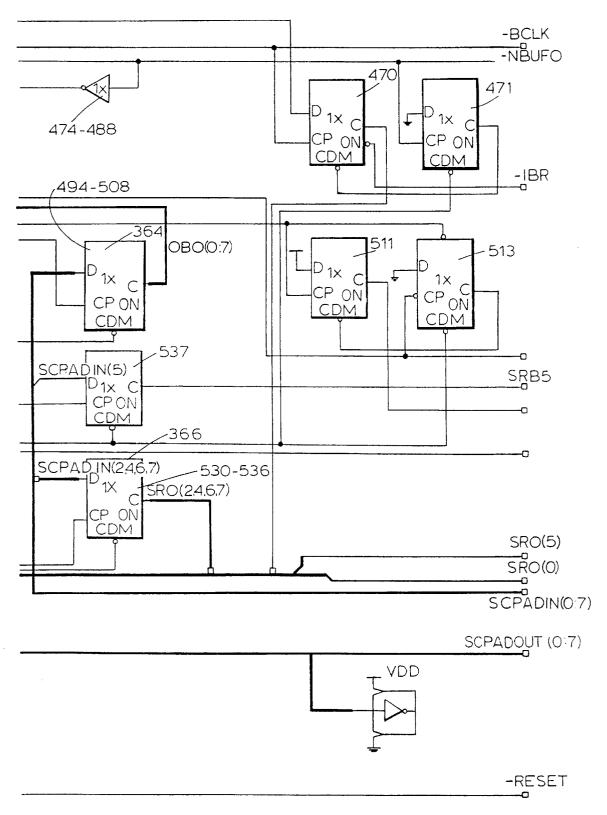

FIGS. **15**A and **15**B represent a schematic diagram of the CPU interface logic in accordance with the present invention;

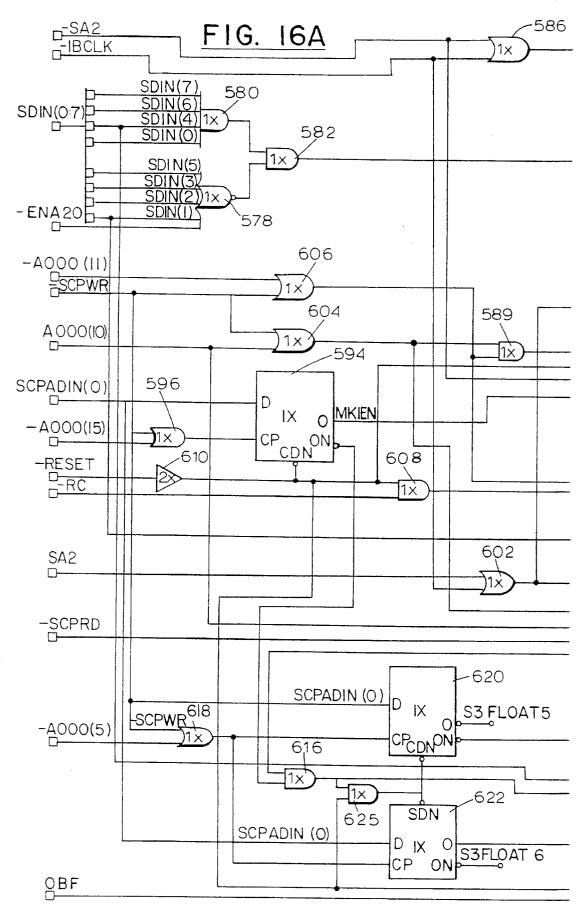

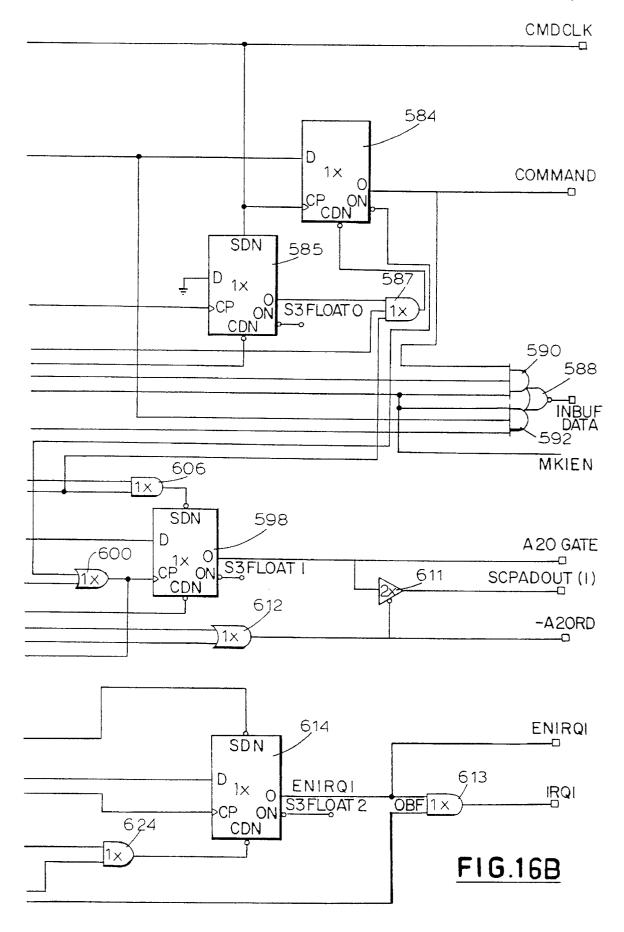

FIGS. **16**A and **16**B represent a schematic diagram of the 15 Gate A20 control logic in accordance with the present invention;

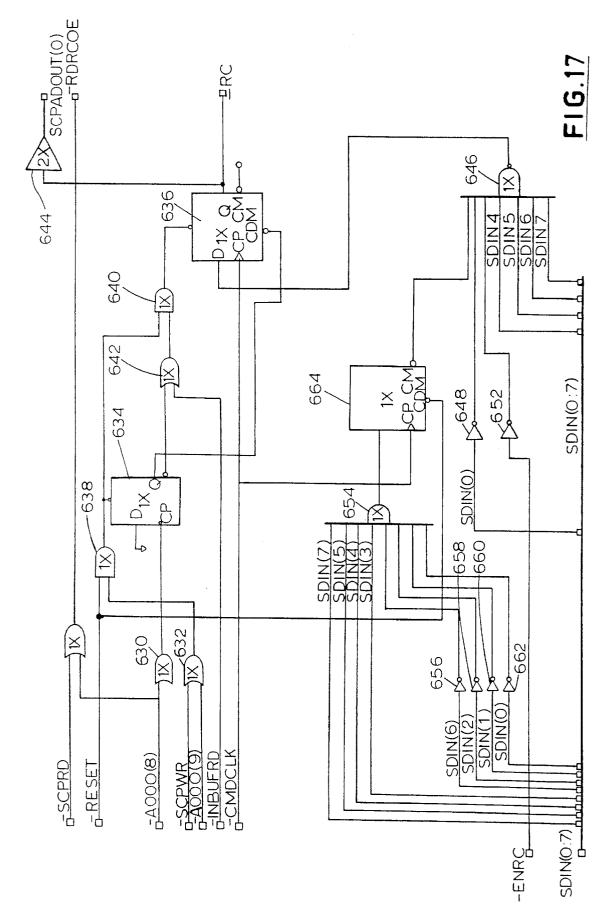

FIG. 17 is a schematic diagram of the slow reset logic in accordance with the present invention;

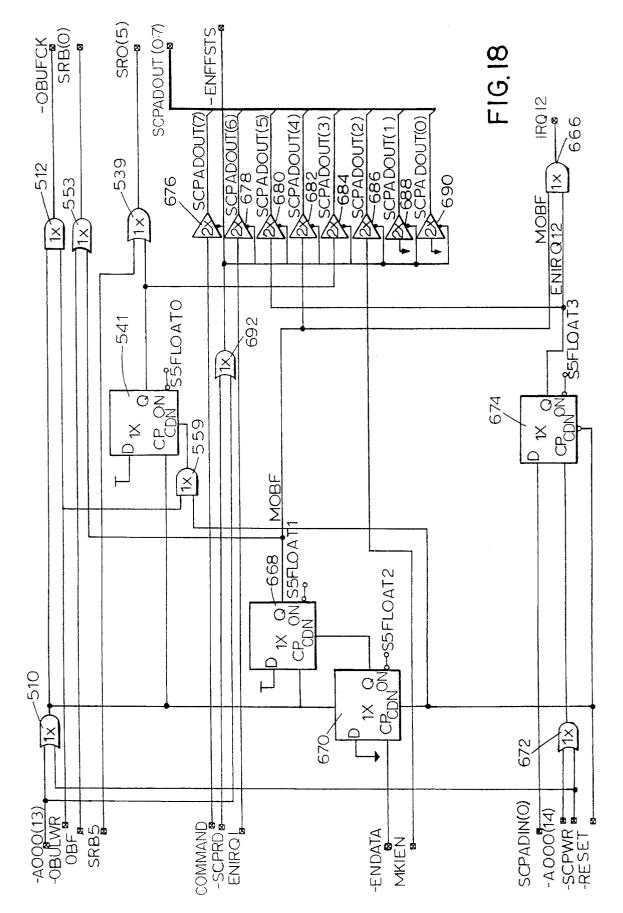

FIG. **18** is a schematic diagram of the IRQ**12** mouse <sup>20</sup> interrupt logic in accordance with the present invention; and

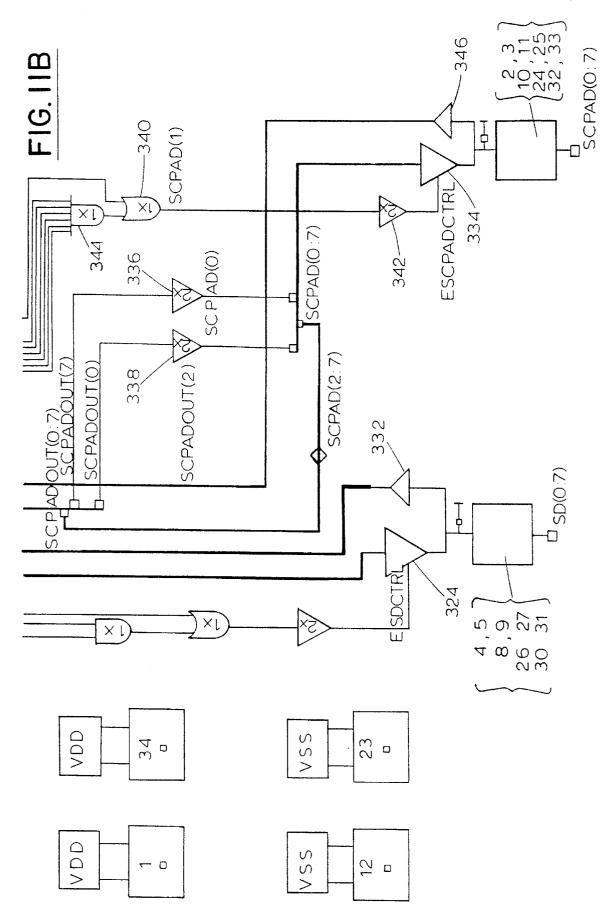

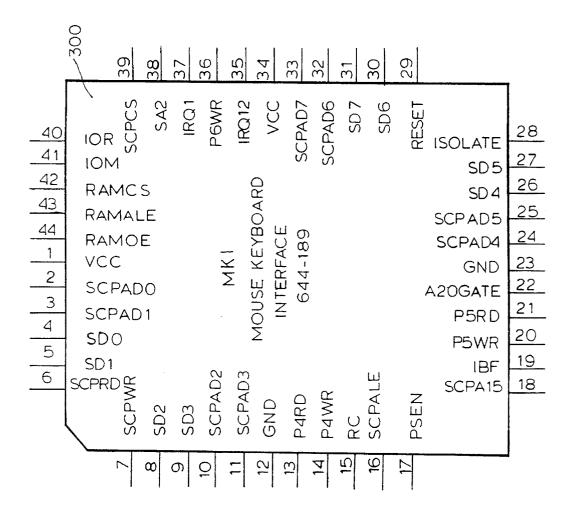

FIG. 19 is a pin diagram for the MKI in accordance with the present invention.

## DETAILED DESCRIPTION

Two embodiments of the invention are disclosed. The first embodiment relates to a System Control Processor Interface (SCPI) illustrated in FIGS. **2–9**. The second embodiment relates to a Mouse Keyboard Interface (MKI) illustrated in FIGS. **10–19**. Both embodiments emulate an Intel 8042 bus as well as provide relatively faster control of the Gate A20 signal. As will be discussed below, the MKI provides relatively faster control of the gate A20 signal than the SCPI by eliminating the need for service from the SCP in order to set the gate A 20 signal. Additionally, the MKI provides hardware support for a type PS/2 mouse.

Referring to the drawing and in particular to FIG. **1**, a portion of a known PC/AT compatible personal computer is illustrated. An SCP **20** acts as an interface between a CPU (not shown) and various peripherals, such as a keyboard **22**. In such an application, the SCP **20** monitors the keyboard **22** and communicates with the CPU.

In known newer type PC/AT machines, an Intel 8042 is 45 used as the SCP **20** while either an Intel 80286, 80386 or an 80486 is used as a CPU. An Intel 8042 is relatively slow and can decrease the overall system performance. However, in order to remain IBM PC/AT-compatible, any change in the SCP requires emulation of the Intel 8042.

#### SCPI

The SCPI allows the SCP 20 (FIG. 1) to be replaced with a relatively faster SCP 26, such as an Intel 8051 or any microprocessor that emulates an Intel 8042. The SCPI, generally identified with the reference numeral 28, is connected between a PC/AT system bus 40 and the SCP 26. The SCP 26 and the SCPI 28 emulate the Intel 8042 to maintain system compatibility. 60

An internal block diagram of the SCPI **28** is provided in FIG. **3**. As will be discussed in detail below, the SCPI **28** allows communication between the SCP **26** and the CPU, as well as communication between the CPU and the SCP **26** by way of three registers (FIG. 3); an input buffer **30**, an output 65 buffer **32** and a status register **34**. The SCPI **28** further includes SCP **26** address decoding logic **36**, CPU decoding

logic 42, slow reset logic 44, external random access memory (RAM) control logic 48, interrupt logic 46 and A20 signal logic 50.

Another important aspect of the SCPI relates to control of the A20 signal which allows memory access above the one megabyte boundary. This signal is set virtually immediately after the command/data sequence and data are received. In known systems, a command to control A20 signal is written by the CPU to an input buffer. In order to allow time for the SCP to read the data and set the Gate A20, a delay is incorporated to allow the SCP to read the data and set the A20 signal. Since some of the new microprocessors run much faster than the application software program allows, a time-out can occur long before the A20 signal is set, resulting in the computer running code out of the wrong memory space. The system in accordance with the present invention solves this problem.

## SCPI PIN DESCRIPTION

The SCPI 28 is a 44 pin integrated circuit as illustrated in FIG. 10, which may be formed as a gate array, such as by VLSI Technologies, Inc. Pin descriptions are provided in TABLE I.

#### TABLE I

|                      |                                    |      | SCPI PIN DESC         | CRIPTION                                                                                 |  |

|----------------------|------------------------------------|------|-----------------------|------------------------------------------------------------------------------------------|--|

| 0                    | PIN NO.                            | TYPE | NAME                  | PIN DESCRIPTION                                                                          |  |

| CPU Interface        |                                    |      | face                  |                                                                                          |  |

|                      | 29                                 | I    | RESET                 | Hardware Reset of<br>SCPI                                                                |  |

|                      | 31                                 | Ι    | –IOW                  | CPU I/O Write Strobe                                                                     |  |

| 5                    | 40                                 | I    | –IOR                  | CPU I/O Read Strobe                                                                      |  |

|                      | 39                                 | I    | -SCPCS                | Decode of SA 9:0<br>Provide an active<br>signal when an access<br>to 062H-06EH (even)    |  |

| 0                    | 38                                 | I    | SA2                   | happens<br>System Address Bus<br>Bit 2                                                   |  |

|                      | 4, 5, 8<br>9, 26, 27<br>30, 31     | В    | SDO:7                 | System Data Bus Bits<br>07                                                               |  |

|                      | 37                                 | 0    | IRQ1                  | Keyboard Interrupt                                                                       |  |

| 5                    | 22                                 | 0    | A20GATE               | Enable access to the memory above 1                                                      |  |

|                      | 15                                 | 0    | -SLOWRST<br>SCP Inter | megabyte<br>System Processor reset<br>face                                               |  |

|                      |                                    |      |                       |                                                                                          |  |

| 0                    | 18                                 | I    | SCPA15                | A15 from the SCP<br>Processor                                                            |  |

|                      | 2, 3, 10,<br>11, 24, 25,<br>32, 33 | В    | SCPADO:7              | Multiplexed address<br>data bus from SCP                                                 |  |

|                      | 16                                 | I    | SCPALE                | Address Latch Enable<br>for SCPADO:7                                                     |  |

| 5                    | 6                                  | I    | -SCPRD                | Memory Read Strobe                                                                       |  |

|                      | 7                                  | I    | -SCPWR                | Memory Write Strobe                                                                      |  |

|                      | 17                                 | I    | -PSEN                 | Program Store Enable<br>Read strobe to<br>external Program<br>Memory                     |  |

| 0                    | 19                                 | 0    | –IBF                  | Input Buffer Full<br>Interrupt to SCP when<br>the CPU has written<br>to the Input Buffer |  |

| External RAM Control |                                    |      |                       |                                                                                          |  |

|                      | 42                                 | 0    | -RAMCS                | RAM Chip Select                                                                          |  |

| 5                    | 44                                 | 0    | -RAMOE                | RAM Output Enable                                                                        |  |

|                      | 43                                 | Ő    | RAMALE                | RAM Address Latch                                                                        |  |

|                      |                                    |      |                       |                                                                                          |  |

## TABLE I-continued

|                 |      | SCPI PIN DE        | SCRIPTION                                                                                                                            |    |

|-----------------|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| PIN NO.         | TYPE | NAME               | PIN DESCRIPTION                                                                                                                      | 5  |

|                 |      | External Po        | Enable<br>ort Control                                                                                                                |    |

| 14              | 0    | –P4WR              | Port 4 Write. Used<br>to clock [SCPADO:7]<br>SPCAD 0:7 into 8<br>external Flip-<br>Flops. Provides 8<br>extra outputs for the<br>SCP | 10 |

| 13              | 0    | –P4RD              | Port 4 Read. Output<br>enable a buffer to<br>[SCPAD 0:7] SCPADO:7<br>to provide 8 inputs                                             | 15 |

| 20              | 0    | –P5WR              | Port 5 write. Used to<br>clock [SCPADO:7] SPCAD<br>0:7 into 8 external<br>Flip-Flops. Provides 8<br>extra outputs for the<br>SCP     | 20 |

| 21              | 0    | –P5RD              | Port 5 Read. Output<br>enable a buffer to<br>[SCPADO:7] SCPAD 0:7<br>to provide 8 inputs                                             | 25 |

| 36              | 0    | –P6WR              | Port 6 Write. Used<br>to clock SCPAD 0:7<br>into 8 external Flip-<br>Flops. Provides 8<br>extra outputs for the                      | 2. |

| 35              | 0    | -P6RD<br>Power and | SCP<br>Port 6 Read. Output<br>enable a buffer to<br>SCPAD 0:7 to provide<br>8 inputs<br>Ground                                       | 30 |

| 28              | I    | –ISOLATE           | In the event the SCP<br>is operating while<br>the rest of the unit<br>is not powered, this<br>signal will isolate<br>the rest of the | 35 |

| 1, 34<br>12, 23 |      | VCC<br>GND         | signals<br>Power Supply<br>Ground                                                                                                    | 4( |

The required output current driving capability of the pins is listed in TABLE II.

TABLE II

| CURRENT DRIVING ABILITY OF OUTPUTS<br>The output pins of the SCPI should have the<br>following current driving abilities: |                                                                                                                                                                                       |  |

|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                           |                                                                                                                                                                                       |  |

|                                                                                                                           | SD 0:7<br>IRO1                                                                                                                                                                        |  |

|                                                                                                                           | -SLOWRST                                                                                                                                                                              |  |

|                                                                                                                           | A20GATE                                                                                                                                                                               |  |

| 2 mA                                                                                                                      | IBF                                                                                                                                                                                   |  |

| 2 mA                                                                                                                      | -RAMCS                                                                                                                                                                                |  |

| 2 mA                                                                                                                      | -RAMOE                                                                                                                                                                                |  |

| 8 mA                                                                                                                      | RAMALE                                                                                                                                                                                |  |

| 8 mA                                                                                                                      | –P4WR                                                                                                                                                                                 |  |

| 8 mA                                                                                                                      | –P5WR                                                                                                                                                                                 |  |

| 8 mA                                                                                                                      | -P5RD                                                                                                                                                                                 |  |

| 8 mA                                                                                                                      | P6WR                                                                                                                                                                                  |  |

| 8 mA                                                                                                                      | -P6RD                                                                                                                                                                                 |  |

|                                                                                                                           | SCPI should have the<br>driving abilities:<br>12 mA<br>16 mA<br>4 mA<br>4 mA<br>12 mA<br>2 mA<br>2 mA<br>2 mA<br>2 mA<br>2 mA<br>8 mA<br>8 mA<br>8 mA<br>8 mA<br>8 mA<br>8 mA<br>8 mA |  |

# SCP INTERFACE

It is to be understood that as used herein, an "H" at the end of a number indicates that the number is a hexadecimal number. It is also to be understood that a minus sign (-) in front of a signal name, such as -IOW, indicates the logical complement of the signal and is identical to the format  $\overline{IOW}$ .

The SCP **26** can address the SCPI **28** as well as external RAM that is local only to the SCP **26**. A signal SCPA**15** determines if it is a RAM access or a SCPI access. If external RAM **48** is not used, the signal SCPA**15** can be tied low, thus allowing all external memory accesses to be to the SCPI **28**.

The RAM control circuitry **48** is illustrated in detail in FIG. **4**. Thirty-two kilobytes of external RAM **48** can be addressed by the SCP **26** at addresses 8000H to FFFFH for program storage. More particularly, the SCPI **28** generates a RAM chip select signal (-RAMCS), a RAM output enable signal (-RAMOE) and a RAM address latch enable signal (RAMALE) for external RAM control.

The RAM chip select signal (-RAMCS) is available at the output of a tristate device **49**. The signal (-SCPA**15**) is applied to the input of the tristate device **49** indicating a RAM access. The tristate device **49** is controlled by an ISOLATE signal (discussed below) which enables the tristate device **49** except under certain conditions, such as when the SCP **26** is operating with no power available to the other components.

The RAM address latch enable signal (RAMALE) is available from another tristate device **51**, also controlled by the ISOLATE signal. The input to the tristate device **51** is a signal (SCPALE), an address latch enable for the SCP external address data bus (SCPAD0-SCPAD7).

The RAM output enable signal (-RAMOE) is generated by a NAND gate **53** and a NOR gate **55**. The output of the NOR gate **55** represents the signal (-PSEN), program memory enable, is applied to an inverting input of the NOR gate **55**. A RAM read signal (-RAMRD) is applied to another inverting input of the NOR gate **55**. The signal (-RAMRD) is available at the output of a NAND gate **53**. The NAND gate **53** receives two inputs. One input is a SCP read signal (-SCPRD). The other signal is (-SCPA15) which represents a RAM access.

The SCP interface to the SCPI is accomplished through a memory mapping scheme, identified by the logic block **36** and illustrated in detail in FIG. **4**. The scheme utilizes Intel **8051** external memory address data lines (SCPAD**0**-SC-PAD**7**), connected as inputs to an eight bit register **52**, which may be a Motorola type 74AC373. During a memory access, a lower address byte is latched into the register **52** using an SCP latch enable signal (SCPALE), applied to the clock input (CLK) of the register **52**,

The addresses from the SCP external address data lines (SPCAD0-SCPAD1) are available at the output of the register **52** forming an eight bit internal address bus (SCPA0-SCPA7). The upper four bits of the internal address bus (SCPA4-SCPA7) are decoded by three NAND gates **54**, **56** and **58**. More specifically, bits SCPA4 and SCPA5 are applied to inverting inputs of the NAND gate **54**. Bits SCPA6 and SCPA7 are applied to inverting inputs of the NAND gate **56**. The outputs of the two NAND gate **54** and **56** are applied to inverting inputs of the NAND gate **58**. The NAND gate **58** generates a signal (-SCPAHN) which indicates that the upper address bits (SCPA4-SCPA7) are low. This signal [(-SPAHN)] (-*SCPAHN*) is applied to an inverting enable input of a decoder/demultiplexer **60** and to an inverting input enable of a decoder/demultiplexer **62**. The decoder/demultiplexers **60** and **62** may be Motorola Model No. 74AC138.

The lower four bits (SCPA0-SCPA3) of the internal address bus (SCPA0-SCPA7) are also applied to the input (A0-A2) of the decoder/demultiplexers 60 and 62. Since the bit SCPA3 is low for addresses A0000H through A0007H and high for addresses [A00008H] A0008H through 10 [A0000CH] A000CH, it is applied to an inverting enable input of the decoder/demultiplexer 60 to generate address signals A0000H through [A00007H] A0007H] A0007H. The signal (-SCPA15), indicating an SCPI access, available at the output of an inverter 59, is applied to a non-inverting enable 15 input of the decoder/demultiplexer 60. Thus, address signals A0000H through [A00007H] A0007H are generated at the output of the decoder/demultiplexer 60. Thus, address signals A0000H through [A00007H] A0007H are generated at the output of the decoder 60 in response to the address bus bits SCPA0 through SCPA2.

The signals (-SCPAHN) and (-SCPA15) are also applied <sup>20</sup> to non-inverting and inverting enabling inputs of the decoder/demultiplexer **62**, respectively. The bit SCPA**3** is applied to an inverter **64** to produce an (-SCPA**3**) signal which is low for addresses above A0007H. The signal (-SCPA**3**) is applied to an inverting enable input of the <sup>25</sup> decoder/demultiplexer **62**. Since the signal (-SCPA**3**) is low for addresses [A0008H] *A0008H* through A000CH, the decoder/demultiplexer **62** can also decode these addresses from the address lines SCPA**2**.

Address signals (-A0000H through -A000CH) are generated at the output terminals (Y0-Y7) of the decoder/demultiplexers **60** and **62**. These address signals are further combined with other signals to generate memory mapped control signals. More specifically, the address signal -A0000H is applied to an inverting input of a NAND gate **64** along with a system control processor write signal (-SCPWR) to generate an output buffer write signal (-OBUFWR). The output buffer write signal (-OBUFWR) allows the SCP **26** to write a byte to the output buffer **32** at the address [a0000H] *A0000H*.

The address signals -A0000H and -A0001H are also applied to a NOR gate **66**. The output of the NOR gate **66** is applied to an inverting input of a NAND **5** gate **68**. A system control processor read signal (-SCPRD) is applied to NAND gate **68** along with the output of the NOR gate **66** to produce an input buffer read signal (-INBUFRD). The input buffer read signal (-INBUFRD) allows the SCP **26** to read the contents of the input buffer **30** at address A0000H or A0001H.

50 The address signal -A0001H is also applied to a NAND gate 70 along with an SCP write signal (-SCPWR) to generate a status register write signal (-STATWR). The status register write signal (-STATWR) allows the SCP 26 to write to the status register 34 at address A0001H. The  $_{55}$ address signals -A0002H through -A0004H allow the SCP 26 to access external ports P4-P6. These address signals are applied to inverting inputs of six NAND gates 72, 74, 76, 78, 80 and 82, along with system control processor write (-SCPWR) or system control processor read (-SCPRD) signals as shown in FIG. 4 to enable the SCP 26 to read and write to the external ports P4-P6 at addresses A0002H, A0003H and A0004H. Each external port can provide 8 additional input pins and 8 additional output pins for the SCP 26. 65

The address signal -A0005H is used as an SCP/CPU interface to generate a keyboard interrupt (IRQ1) logic 46.

More specifically, the address signal -A0005H is applied to an inverting input of a NAND gate 84. An SCP write signal (-SCPWR) is applied to another inverting input of the NAND gate 84. The output of the NAND gate 84 is applied 5 to the clock input (CLK) of a D-type flip-flop 86. One bit SCPAD0 of the external SCP address bus is applied to the D input of the flip-flop 86. The output from the NAND gate 84 is used to strobe the bit SCPAD0 into the flip-flop 86 to generate an IREQG signal. This signal (IREQG) is applied to the input of a NAND gate 88, along with an output buffer flag full signal (OBF). When bit SCPAD0 is high, the keyboard interrupt signal (IRQ1) is enabled when the SCP 26 writes to address A0005H. During such a condition when bit SCPAD0 is low, the keyboard interrupt signal (IRQ1) is disabled. During such a condition the NAND gate 88 allows an interrupt signal (IRQ1) to be generated by the SCPI 28 when the output buffer 32 is full.

The address signal (-A0006H) is applied to an inverting input of a NAND gate **90** along with an SCP read signal (-SCPRD). The output of the NAND gate **90** is an output buffer read signal (-OBUFRD) which allows the SCP **26** to read the output buffer **32** at address A0006H.

The address A0007H is applied to an inverting input of a NAND gate **92** along with an SCP read signal (-SCPRD). The output of the NAND gate **92** is a status register read signal (-STATRD) which allows the SCP **26** to read the status register **34** at address A0007H.

The address signals [A008H] A0008H, A0009H, and A000CH relate to the slow reset system. The address signals A000AH and A000BH are used to generate the A20 signal. These address signals will be discussed in detail below.

## CPU TO SCP INTERFACE

Communication between the CPU and the SCP 26 is by way of an input buffer 30, an output buffer 32 and a status register 34. The input buffer 30 is an eight bit register with tristate outputs (Q1-Q7), such as a Motorola type 74AC374. In such a device, a clock input (CLK) and output enable input (0C) are common to all eight bits. The output buffer 32 and the status register 34 are also eight bit registers. These registers 32 and 34 may be octal D-type flip-flops having separate D-type inputs (D0-D7) and separate tristate outputs (Q0-Q7), such as a Motorola type 74AC273. Such devices contain a clock input (CLK) and a clear (CLR) input, common to all eight flip-flops.

The input buffer **30** may be written to only by the CPU and read only by the SCP 26. The CPU writes to the input buffer 30 at addresses 60H or 64H by writing to the system data bus (SD0-SD7). The system data bus (SD0-SD7) is applied to the data inputs [(DO07)] (D0-D7) of the input buffer 30. The address is decoded by a CPU logic circuit 42 which does not form part of the present invention. A signal (-SCPCS) is generated by the CPU decode logic circuit 42 if the address is either 60H or 64H. The signal (-SCPCS) is applied to an inverting input of a NAND gate 94. A CPU input/output write signal (-IOW) iS applied to another inverting input of the NAND gate 94 to produce a signal (-IBCLK), which indicates that the CPU is writing to the input buffer 30 at either address 60H or 64H. The signal (-IBCLK) is applied to the clock input (CLK) of the input buffer 30. Thus, any time the CPU writes to address 60H or 64H, data on the system data bus 40 (SD0-SD7) is strobed into the input buffer 30.

The CPU can either write data or a command to the input buffer register **30**. Any time the CPU writes to the input

buffer **30**, a command data flag (CMD/DATA) is set in the status register **34** (bit **3**). This lets the SCP **26** know that a byte containing either a command or data is in the input buffer **30**. A write to **64**H represents a command (command data flag high), while a write to **60**H represents data (com- 5 mand data flag low).

The command data flag (CMD/DATA) is set by way of a flip-flop **96**. More particularly, bit SA**2** of the system address bus is applied to a D input of a flip-flop **96**. Bit SA**2** depending on whether it is high or low, determines whether 10 CPU addressed **60**H or **64**H. The signal (-IBCLK) is applied to the clock input (CLK) of the flip-flop **96**. The output signal (CMD/DATA) from the flip-flop **96** depending on whether it is high or low enables the SCP **26** to determine whether the last byte written to the input register **30** by the 15 CPU was command or data.

Each time the CPU writes to the input buffer **30**, an input buffer full flag (IBF), bit **1** of the status register **34**, is set as well as the CMD/DATA flag, as discussed above. The input buffer full flag (IBF) acts as an interrupt to the SCP **26** to let it know there is a byte in the input register **30** from the CPU which has not yet been read. The command/data flag tells the SCP **26** whether the last byte written by the CPU was a command (written to address **64**H) or data (written to address **60**H).

A [D type] *D-type* flip-flop **98** having its D input tied high is used for the input buffer full flag (IBF). A signal (-IBCLK) is applied to the clock input (CLK) of the flip-flop **98**. Thus, the input buffer flag (IBF) will be set each time the CPU writes to input buffer **30**.

30 Once the SCP **26** determines whether the byte in the input buffer 30 is command or data, it reads the byte in the input buffer 30 and the input buffer flag IBF is cleared by the SCPI 28. More particularly, the SCP 26 reads the byte out of the input buffer 80 by reading addresses A000H or A001H. More specifically, an input buffer read signal (-INBUFRD) 35 is applied to a NAND gate 100 along with a reset signal. The (-INBUFRD) signal is a decode of addresses A0000H and A0001H and is active any time the SCP 26 is attempting to read these addresses. The output of the NAND gate 100 is an input buffer output enable signal (-INBUFOE) which is applied to the enable input (OC) of the input buffer 30 which allows the byte to appear on the multiplexed system control processor address data bus SCPAD0-SCPAD7 to be read by the SCP 26. Prior to this state, the input buffer output 26 is in a high impedance state. 45

After the SCP 26 reads the input buffer 30, the input buffer full flag (IBF) is cleared automatically by a flip-flop 102. More particularly, the input buffer enable signal (-INBU-FOE) is applied to the clock input (CLK) of the flip-flop 102. The D input of this flip-flop is tied to system ground. Thus, once the byte 30 in the input buffer 30 is placed on the system control processor address data lines [(SCPAD0-SCPA07)] (*SCPAD0-SCPAD7*) and read, an input buffer clear signal (-IBFCLR) is generated by the flip-flop 102 and applied to the clear input (CLR) of a flip-flop 98. This clears the input buffer full flag (IBF). In order to avoid writing over a byte in the input buffer 30, the CPU should check the input buffer full flag (IBF) in the status register 34 prior to writing to the input buffer 30.

The system control processor SCP communicates back to the CPU through the output buffer **32** and the status register **34**. The output buffer **32** is read only by the CPU at address **60**H and read and written to by the SCP **26**. During normal operation, the SCP **26** can only write to the output buffer **32**. In order to avoid overwriting a byte in the output buffer **32** that has not yet been read by the CPU, the SCP **26** should 65 read the status register **34** before writing to the output buffer **32**. The status register **34** is an 8 bit register consisting of **8** D-type flip-flops with a common clock and an asynchronous reset, such as a Motorola type 74AC223. The status register **34** may be written to and read by the SCP **26**. The read capability enables the SCP **26** to read the output buffer full flag (OBF) and the command data flag (CMD/DATA). The status register **34** may be read any time by the CPU. Bit definitions for the status register **34** are provided in TABLE III.

The SCP 26 can write to the output buffer 32 by writing to address A0000H. As previously discussed, this generates an output buffer write signal (-OBUFWR) which is applied to the clock input (CLK) of the output buffer 32. The external SCP address data lines (SCPAD0-SCPAD7) arc applied to the inputs of the output buffer 32. The output bits of the output buffer (OB00-OB07) are applied to inputs of registers 104 and 106, which may be octal buffer and line drivers having tristate outputs, such as a Motorola type 74AC244.

The output lines of the register 106 are tied to the system data bus SD0-SD7 to allow the CPU to read the output buffer 32. More specifically, the CPU reads the register 106 at address 60H. This is accomplished with three NAND gates 108, 110 and 112. A signal (-SCPCS), indicative of an address 60H or 64H, and a signal (-IOR), indicative of a read operation by the CPU, are applied to inverting inputs of the NAND gate 108. The output of the NAND gate 108 is applied to an inverting input of the NAND gate 110. The output of the NAND gate 108 is a signal representing that the CPU is reading address 60H or 64H. A signal SA2, indicating whether the address is 60H or 64H, is applied to another inverting input of the NAND gate 110. If the address is 60H, an enable data signal (-ENDATA) is generated at the output of the NAND gate 110. This signal (-ENDATA) is applied to an inverting input of the NAND gate 112 to produce a data enable signal (-DATEN). The signal (-DATEN) is then applied to the enable inputs ENA/ENB of the register 106. This allows the CPU to read the register 106 which is representative of the byte contained in the output buffer 32.

Each time the SCP 26 writes to the output buffer 32, the output buffer full flag (OBF) is set automatically. The output buffer full flag (OBF) is available at the output of a flip-flop 114. This flag is set by applying an output buffer write signal (-OBUFWR) to the clock input (CLK) of the flip-flop 114. The (-OBUFWR) signal is generated any time the SCP 26 writes to the output buffer 32. More specifically, a D input of the flip-flop 114 is tied high. Thus, an output buffer full flag (OBF) will be generated any time the SCP writes to the output buffer 32.

Once the CPU reads the output buffer **32**, the output buffer full flag (OBF) is cleared by a flip-flop **116**. More particularly, the data enable signal (-DATEN) from the NAND gate **112** is applied to the clock input (CLK) of the flip-flop **116**. The (-DATEN) signal represents that CPU is reading the output buffer **32** at address **60**H. By applying this signal to the flip-flop **116**, an output buffer full flag clear signal (-OBFCLR) is generated at the output of the flip-flop **116** each time the CPU reads the register **106**. This signal (-OBFCLR) is applied to the clear CLR input of the flip-flop **114** to clear the output buffer full flag (OBF) each time the CPU reads the output buffer **32**.

A register **104** allows the SCP **26** to read the byte in the output buffer **32**. More specifically, the output of the register **104** is connected to the SCP address data lines (SCPAD0-SCPAD7). The SCP **26** reads the register **104** at address A0006H by producing an output buffer read signal (-OBU-FRD). This signal (-OBUFRD) is applied to enable inputs ENA/ENB of the register **104** to place the byte in this register on the SCP address data lines (SCPA00-SCPA07) to be read by the SCP **26**.

40

45

60

65

The SCP 26 can write to the status register 34 at address A0001H which generates a signal (-STATWR). This signal (-STATWR) is applied to the clock input CLK of the status register 34 to enable the SCP 26 to write to the status register 34 by way of the internal SCP address data lines (SCPAD0-SCPAD7). This data is then available on the status register output bus SR00-SR07 which is applied to registers 114 and 116. The registers 114 and 116 may be of the same type as registers 104 and 106.

The register **116** allows the SCP **26** to read the status register **34**. More specifically, the status register **34** may be <sup>10</sup> read by the SCP **26** at the output of the register **116** on the SCP address data bus (SCPAD**0**-SCPAD**7**) any time the SCP **26** reads address A0007H. During this condition, a status read signal (-STATRD) is generated and applied to the enable inputs ENA and ENB of register **116** which allows the SCP **26** to read this register **54**.

The CPU can read the output of the status register 34 at register 114. More specifically, the output of the register 56 is connected to the system data bus SDO-SD7. The CPU reads the output of the register 56 at address 64H by applying a status enable signal (-STATEN) to the enable 20 inputs ENA and ENB of the register 114. The signal (-STATEN) is generated by three gates 118, 120 and 122, and an inverter 124. More particularly; an SCP chip select signal (-SCPCS) is applied to an inverting input of the NAND gate 118. This signal represents that the CPU is 25 addressing either A60H or A64H. An I/O write signal (-IOR) is applied to another inverting input of the NAND gate 118. The output of the first NAND gate 118 represents that the CPU is reading at an address 60H or 64H. The output of the NAND gate  $\overline{118}$  is applied to an inverting input of the NAND gate 120. A signal SA2 is applied to the inverter 122 to generate a signal -SA2. The -SA2 signal indicates whether the address is A60H or A64H. The output of the inverter 122 is applied to another inverting input of the NAND gate **120**. The output of the NAND gate 120 is applied to an inverting 35 input of the NAND gate 124 which generates a status enable signal (-STATEN) any time the CPU is reading at an address A64H.

| TA | BL | Æ | Ш |

|----|----|---|---|

|    |    |   |   |

| STATUS REGISTER BIT DEFINITION                             |

|------------------------------------------------------------|

| The status register 34 is an eight bit register.           |

| Three bits are generated by the SCPI 28 while five bits    |

| are written by the SCP 26. Specifically, the output        |

| buffer full flag (OBF), the input buffer full flag (IBF)   |

| and the command data flag (CMD/DATA) are generated by      |

| the SCPI 28. The remaining bits are written by the SCP 26. |

| Definitions for the [7-bits] 7 bits are as follows:        |

|                                                            |

| BIT NUMBER                                | DEFINITION                                                                              |    |

|-------------------------------------------|-----------------------------------------------------------------------------------------|----|

| Bit 7<br>Bit 6<br>Bit 5<br>Bit 4<br>Bit 3 | Parity error<br>Receive time out<br>Transmit time out<br>Inhibit switch<br>Command/Data | 50 |

| Bit 2<br>Bit 1<br>Bit 0                   | System flag<br>Input buffer full flag<br>(IBF).<br>Output buffer full flag<br>(OBF)     | 55 |

The command/data bit indicates whether the last byte written by the CPU was a command or data.

The IBF signal indicates when the CPU has written a byte to the input buffer but the system control processor SCP has not yet read the byte out of the input buffer **30**. It can also be used by the CPU as a flag to indicate that the system control processor SCP is ready to receive a byte.

The OBF signal indicates when the SCP **26** has written a byte to the output buffer **32** which has not yet been read by

the CPU. The OBF signal can also be used by the SCP 26 as a flag to indicate that the CPU is ready to receive a byte.

## SLOW RESET

The slow reset signal (-RC) is an active low output signal to reset the CPU. It can be set by the CPU or set and cleared by the SCP 26. It is cleared when the SCPI 28 is reset by the reset pin. The SCP 26 can control the slow reset signal (-RC) by writing to addresses A0008H or [A90009H] A0009H. A write to address A0008H forces the slow reset signal active while a write to A0009H forces the slow reset signal (-RC) inactive. The data written to either location is ignored. All that is relevant is that a write takes place at the proper memory location.

More specifically, the address signal (-A0008H) is applied to a NAND gate **126** along with a SCP write signal (-SCPWR). The output of the NAND gate **126** is a slow reset active signal (-SCPSRC). This signal (-SCPSRC) is applied to the clock input (CLK) of a flip-flop **128**. The D input of a flip-flop **128** is tied to system ground. Thus, any time the address A0008H is written to by the SCP **26**, a slow reset signal (SSETRC) is generated at the output of the NAND gate **128**. This signal (SSETRC) along with input buffer read signal (-INBUFRD) is applied to inverting inputs of a NAND gate **130**. The output of the NAND gate **130** is applied to an inverting input of a NOR gate **132**. The output of the NOR gate **132** is applied to a preset input (PRE) of a flip-flop **134** to set the slow reset signal (-RC).

The slow reset signal (-RC) can be cleared by the SCP 26 by writing to the address A0009H. More specifically, the address signal (-A0009H) is applied to an inverting input of a NAND gate 136. The output of the NAND gate 136 is applied to the clear (CLR) input of the flip-flop 128.

The CPU can also set the slow reset signal (-RC) with a single write command unless it is prevented from doing so by the SCP 26 as discussed below. Specifically, the CPU can set the slow reset signal active by writing an even byte from FOH to FEH to address 64H. NAND gates 138 and 140 decode these bytes from the CPU. More specifically, system data bits SD4, SD5 and SD6 and SD7 are applied to the NAND gate 138. The output of the NAND gate 138 is applied to the NAND gate 140. System data bit SD0 is applied to an inverting input of the NAND gate 140. The output of the NAND gate 140 is a signal (-CPURC) representative of an even data byte between FOH and FEH. This signal (-CPURC) is applied to a NAND gate 142. A signal (-ENRC) is applied to another inverting input of the NAND gate 142. As will be discussed later, the signal (-ENRC) indicates whether CPU control of the slow reset signal has been disabled by the SCP 26. The output of the NAND gate 142 is applied to the D input of the slow reset flip-flop 134, A command clock signal (CMD/CLK), which represents that the CPU addressed the address 64H, is applied to the clock input (CLK) of the slow reset flip-flop 134.

The output of the flip-flop 134 is a signal representative of a slow reset signal (-RC), This signal (-RC) is applied to the input of a tristate device 144 which indicates the status of the slow reset signal (-RC) to be read by the SCP. More particularly, the output of the tristate device 144 is applied to a system control processor data line SCPAD0. The tristate device 144 is controlled by a NAND gate 146. An SCP read signal (-SCPRD) along with an address signal -A0008H is applied to inverting inputs of the NAND gate 146. The NAND gate 146 generates an enable signal (-RDRCOE) which enables the tristate device 144. Thus, whenever the SCP 26 reads address A0008H, the tristate device 144 is enabled to place the output of the slow reset flip-flop 134 on the system control address data bit SCPAD0. A logical 0

indicates that the slow reset is active while a logical 1 indicates that the slow reset signal is inactive.

The SCP **26** can also disable the CPU control of the slow reset by writing to address A000CH. More specifically, a signal representative of the address A000CH is applied to a 5 NAND gate **146** (FIG. **4**) along with the system control processor write signal (-SCPWR). The output of the NAND gate **146** is applied to a clock input (CLK) of a flip-flop **148**. The SCP data bit SCPAD1 is applied to a D input of the flip-flop **148**. If the data bit SCPAD1 is high the slow reset will be enabled. If the data bit SCPAD1 is low the slow reset will be disabled. The output of this flip-flop **148** is an enable reset signal (-ENRC) which is applied to the NAND gate **142** (FIG. 7) to either enable or disable the CPU from controlling the slow reset signal.

# A20 SIGNAL CONTROL

The A20 signal allows memory above one megabyte to be accessed. This A20 signal can be set by the SCP 26 directly or by the SCPI 28 in response to a CPU command. 5 The CPU controls the gate A20 with a two byte sequence. The first byte [is] D1H is a command byte written to the address 64H. The second byte is a data byte written to the address 60H. The system data bit SD1 determines whether the A20 is to be set or cleared. The data bit SD1 is applied to the D input of an A20 signal flip-flop 168. The output of the <sup>25</sup> flip-flop 168 is the A20 signal.

The CPU command signal (COMMAND) is available at a command flip-flop 150. The CPU command signal is generated when the CPU writes a byte D1H to address 64H. The command byte D1H is decoded by seven of NAND  $^{30}$ gates 152, 154, 156, 158, 160, 162 and 164 (FIG. 6). These NAND gates decode the system data bits SD0 through SD7 to provide a command data signal (CMDD1) when the CPU writes a command D1 to address 64H. More specifically, the system data bits (SD0-SD7) are applied to inverting inputs 35 of the NAND gates 152, 154, 156 and 158 as shown in FIG. 6. The outputs of NAND gates 152 and 154 are applied to a NAND gate 160. The outputs of the NAND gates 156 and 158 are applied to the NAND gate 162 along with a signal (ENA20). The outputs of the NAND gates 160 and 162 are  $_{40}$ applied to a NAND gate 164 which generates a command signal (CMDDL) any time the byte D1H is written to address 64H.

The signal (ENA20) is generated by a flip-flop 163. This flip-flop 163 enables SCP 26 to disable the A20 signal. More specifically, a bit SCPAD1 is applied to the D input of the flip-flop 163. If bit SCPAD1 is high, the A20 signal is enabled. If bit SCPAD1 is low, the A20 signal is disabled.

The signal (CMDD1) is applied to a D input of the command flip-flop **150**. Another signal, command clock <sup>50</sup> (-CMDCLK), iS applied to the clock input (CLK) of the command flip-flop **150**. The command clock signal (-CM-DCLK) is generated by a NAND gate **166** which receives signal (-IBCLK) and an input signal SA2. The IB clock signal (-IBCLK) represents that the address written to by the CPU is either **60**H or **64**H. The signal -SA2 identifies that <sup>55</sup> the address is **64**H. The output of the NAND gate **166** is the command clock signal (-CMDCLK).

In order to better understand the system, a state diagram for the A20 signal logic is provided in FIG. 8. The state equations for the state machine are illustrated in Appendix 1. <sup>60</sup> The states refer to the states of the command flip-flop **150**, the A20 signal flip-flop **168** and a dummy flip-flop **170**, respectively. The dummy flip-flop **170** is required because of the number of states. The states in FIG. 8 are numbered for the states of these flip-flops. For example, state 7 (binary <sup>65</sup> 111) represents that the flip-flops **150**, **168** and **170** are all set.

The system starts in state **0** where the flip-flops **150**, **168** and **178** are all clear. The system then proceeds to state **4** where the command flip-flop **150** is set as discussed above. Once the command flip-flop **166** is set, the system waits for the data byte from the CPU to either set or reset the gate A20. When the system data byte is received and the gate A20 is set as discussed above, the system proceeds to state **6**. In this state, both the command flip-flop **150** and the gate A20 flip-flop **162** have previously been set. An important feature of the invention relates to the fact that there was no waiting from the time the data byte was received from the CPU to set the gate A20. This greatly enhances the speed at which the gate A20 is set by the CPU.

The output of a NAND gate 172 is representative of 35 state 6. The NAND gate 172 receives a signal (COM-MAND) from the command flip-flop 150 and an [A 20] A20 signal from the A20 signal flip-flop 168. Also applied to the NAND gate 172 is a signal VCC and a signal from the dummy flip-flop 170, which is clear at state 6.

After state 6, the system can only proceed to state 2wherein the command flip-flop 150 is cleared. The command flip-flop 150 is cleared once the SCP 26 reads the data out of the input buffer **30**. This is accomplished by NAND gates 174 and 176 and NOR gates 178 and 180. More specifically, a signal representative of state 6 (-STATE6) is applied to an inverting input of the NAND gate 174, An input buffer read signal (-INBUFRD) is applied to another inverting input of the NAND gate 174. The output of the NAND gate 174 indicates that the SCP 26 has read the data in the input buffer 30. The output of the NAND gate 174 is applied to an inverting input of a NOR gate 178. The output of the NOR gate 178 is applied to an inverting input of the NOR gate 180. The output of the NOR gate 180 is representative of a command reset signal (-CMDRST) which is applied to the clear input (CLR) of the command flip-flop 150. This signal (CMDRST) thus resets the command flip-flop 150 once the SCP 26 has read the data byte in the input buffer 30. Once this occurs, the system proceeds to state 2.

In state 2, the command flip-flop 166 and the dummy flip-flop 170 remain clear and the A20 signal flip-flop 168 remains set. The system sits in state 2 waiting for another command from the CPU. If another command is received, the system proceeds to state 7 where the command flip-flop **150** is set. In state 7, the system waits for a data byte from the CPU to indicate what is to be done with Gate A20. Once the data is received, the dummy flip-flop 170 is set. More specifically, a command signal (COMMAND) from the command flip-flop 150 is applied to an AND gate 182 representing that the command flip-flop 156 has been set. A signal (-SA2) is applied to another input of the AND gate 182. The (-SA2) signal represents that a CPU command was written to address 64H. A signal (-SD1) is also applied to the AND gate 182 [gemerated] generated by way of an inverter 184. The output of the AND gate 182 is applied to one input of the OR gate 184. The output of the OR gate 184 is applied to the D input of the dummy flip-flop 170. An (-IBCLK) signal is applied to the clock input (CLK) of the dummy flip-flop 170. The (-IBCLK) signal is a decode and indicates that the CPU has written to either address 60H or 64H. Thus, the dummy flip-flop 170 is set in state 7 after a command has been written by the CPU to the command flip-flop 150,

The dummy flip-flop **170** may also be set by an AND gate **186**. More specifically, the output of the AND gate **186** is applied to another input of the OR gate **184**. The AND gate **186** has three inputs. One input is from the A20 signal flip-flop **168**. A second input is from the NAND gate **164** which indicates that the CPU has written a command D1. The last input is an SA2 signal which indicates that the command was written to address **64**H. Thus, the AND gate **186** will be enabled any time the gate A**20** has been set and a command has been written to address **64**H by the CPU.

Once the system is in state 7, if data is received indicating that the Gate A20 flip-flop 168 is to be disabled, the system proceeds to state 5. In state 5, the command flip-flop is cleared, the dummy flip-flop remains set and the A20 signal flip-flop 168 is cleared.

A signal representative of state 5 is generated by a NAND gate 188. Signals from the dummy flip-flop 170, the A20 signal flip-flop 168 (-A20 GATE), the command flip-flop 150 (COMMAND) and VCC are applied to the input of the NAND gate 188. The output of the NAND gate 188 is a signal (-STATE5) which is applied to the NAND gate 176 to <sup>10</sup> clear the command flip-flop 150 when the system is in state 5.

The A20 signal flip-flop **168** is cleared by the system data bit SD1 which is applied to the D input of the flip-flop **168**. If the SD1 signal is low the A20 signal flip-flop **168** is 15 cleared. The bit SD1 is strobed into the flip-flop **168** by a NAND gate **190**. A signal (-COMMAND) is applied to an inverting input of the NAND gate **190** from the command flip-flop **150**. A signal (-DATACLK) is applied to another inverting input of the NAND gate **190**. The (-DATACLK) is generated by a NAND gate **192**. A signal SA2 is applied to one inverting input of the NAND gate **192** while a signal (-IBCLIC) is applied to another inverting input to strobe the A**20** signal flip-flop **168** any time the CPU writes data to address **60**H.

After state 5, the system proceeds back to state 0 where 25 the command flip-flop 150 and the dummy flip-flop 170 are cleared. The command flip-flop 150 is cleared automatically in state 5 when the input buffer flag IBF is cleared. More specifically, once the SCP reads the input buffer 30 an input buffer read signal (-INBUFRD) is generated. This signal (INBUFRD) and a state **5** signal (-STATE**5**) are applied to 30 inverting inputs of the NAND gate 176. The output of the NAND gate 176 is applied to an inverting input of the NOR gate 178 which clears the command flip-flop 150. The output of the NAND gate 176 is also applied to an inverting input of a NOR gate 208. The output of the NOR gate 208 is 35 applied to the clear input (CLR) of the dummy flip-flop 170. Thus, the command flip-flop 150 and the dummy flip-flop 170 will be cleared in state 5 and the system will return to state 0 where the command flip-flop 150, the A20 gate flip-flop 168 and the dummy flip-flop 170 are all clear. 40

The SCP 26 can also gain control of the Gate A20 flip-flop 168 through memory map. Specifically, a write to address 000AH by the SCP 26 can clear the A20 signal flip-flop 168. More specifically, a signal representative of these addresses (-000AH) is applied to an inverting input of NAND gate 194. A SCP write signal (-SCPWR) is applied to another inverting input of the NAND gate 194. The output of the NAND gate 194 is applied to the clear input (CLR) of the A20 signal flip-flop 168 to enable the SCP 26 to clear the signal.

50 The SCP 26 can set the A20 signal by writing to address 000BH. Specifically, the address signal (-000BH) is applied to an inverting input of a NAND gate 96 along with an SCP write signal (-SCPWR). The output of the NAND gate 196 is applied to an inverting input of a NOR gate 198 whose 55 output is tied to the present input (PRE) of the A20 signal flip-flop 168. The SCP 26 can also read the status of the gate A20 flip-flop 168 by reading address 000AH. Specifically, a signal representative of the system control processor read signal (-SCPRD) is applied to an inverting input of a NAND gate 202. A signal representative of an address signal 60 (-000AH) is applied to another inverting input. The output of the NAND gate 202 is applied to a tristate device 204 to allow the data from the gate A20 flip-flop to be placed on the system control processor address data bus bit SCPAD 1 to be read by the SCP 26.

The Gate A20 can also be set active by the SCPI 28 when a command is received to set slow reset active or the SCPI is reset by the reset pin. More specifically, a reset signal and a slow reset signal (-RC) are applied to a NOR gate 206. The output of the NOR gate 206 is applied to an inverting input of the NOR gate 208 which clears the dummy flip-flop 170. The output of the NOR gate 206 is also applied to one input of the NOR gate 198 which sets the Gate A20 flip-flop 168. The output of the NOR gate 206 is also applied to an inverting input of the NOR gate 178 which, in turn, is connected to the NOR gate 180 which clears the command flip-flop 150.

An SCP write to either address 000AH or 000BH clears the command flip-flop 150. More specifically, the output of the NAND gates 194 and 196 are applied to inverting inputs of a NOR gate 200. The output of the NOR gate 200 is applied to an inverting input of the NOR gate 180. The output of the NOR gate 180 is applied to the clear input (CLR) of the command flip-flop 150.

#### RESET

A reset signal (-RESET) from the CPU is used to reset the system. Specifically, the reset signal is applied to an inverting input of the NOR gate **206** which clears the command flip-flop **150**, the A20 signal flip-flop **168** and the dummy flip-flop **120**. The reset signal is also applied to the clear input (CLR) of the flip-flop **86** to clear the interrupt signal IRQ1. Reset signals are also used to clear the input buffer **30**, output buffer **32**, the status register **34**, the input buffer full flag flip-flop **98** and the output buffer full flag flip-flop **114**.

#### ISOLATE

An isolate signal is an active low input signal to tristate certain signals on the SCPI **28** in the event that the SCP **26** and SCPI **28** are used in a manner where the rest of the system **[of]** *is* not powered, for example, during battery charging of a portable battery powered converter. Tristating the pins identified in TABLE IV below can avoid problems to the SCP **26**.

TABLE IV

| The pins in the SCPI that get tristated are as follows: |          |      |

|---------------------------------------------------------|----------|------|

| SCPAD 0:7                                               | IRQ1     | P4WR |

| -IBF                                                    | A20 gate | P4RD |

| SD 0:7                                                  | SLOWRST  | P5WR |

| -RAMOE                                                  | -RAMCS   | P5RD |

|                                                         | -RAMALE  | P6WR |

|                                                         |          | P6RD |

#### MOUSE KEYBOARD INTERFACE (MKI)

An important distinction between the SCPI 28 and the MKI is that the MKI does not need to interrupt the SCP 26 to allow the CPU to control the A20 signal. Consequently, the MKI allows for relatively faster switching of the A20 signal than the SCPI 28. More specifically, as described above, the CPU controls the A20 signal with a two byte sequence from the CPU to the input buffer 30. The first byte is a command byte D1 written to the address 64H. In the previous embodiment utilizing the SCPI 28, after the CPU writes the command byte, the Input Buffer Full (IBF) flag is set in the status register 34. This IBF flag is used to interrupt the SCP 26. After the SCP 26 reads the command byte D1H, the IBF full flag is cleared, which allows the CPU to write the second byte to the input buffer 30 which also requires processing by the SCP 26. As discussed above, the bit SD1 in the second byte determines whether the A20 signal is to be set or cleared.

35

40

45

50

55

With such a system there is inherently a certain amount of delay after a byte is written to the input buffer 30 until the SCP 26 can retrieve the command data bytes. The MKI allows for faster switching of the A20 signal by recognizing the command and data bytes from the CPU, thus eliminating 5the need to interrupt the SCP 26 which may be busy with other tasks. Since no interrupt is generated after the command byte D1H, the CPU can immediately send the data byte without waiting for the SCP 26 to read the input buffer **30**. The MKI can also recognize the data byte, thus eliminating the processing time of the SCP 26.

As illustrated in FIG. 10, the MKI, generally identified with the reference numeral 300 also allows the SCP 20 (FIG. 1) to be replaced with a relatively faster SCP 26, such as an Intel 8051 or other microprocessor that emulates a type Intel 8042 microprocessor to maintain IBM compatibility with type PC/AT machines. The MKI 300 is connected between the PC/AT system bus 40 and the SCP 26.

Similar to the SCPI 28, the MKI 300 allows communication between the CPU and the SCP 26 by way of three 20 registers; an input buffer, an output buffer and a status register (FIG. 15). As shown in FIG. 12 and 5 discussed below, the MKI 300 further includes address decode and RAM control logic 308 (FIGS. 13-14), CPU interface logic 310 (FIG. 15), Gate A20 control logic 312 (FIG. 16), Slow Reset logic 314 (FIG. 17) and IR12 control logic 316 (FIG. 25 18).

## MKI PIN DESCRIPTION

The MKI 300 is a forty-four pin integrated circuit as 30 illustrated in FIGS. 11-19, which may be formed as a gate array, such as by VLSI Technologies Inc. Pin descriptions are provided in TABLE V.

| PIN NO.           | TYPE          | NAME     | PIN DESCRIPTION             |  |  |  |

|-------------------|---------------|----------|-----------------------------|--|--|--|

|                   | CPU Interface |          |                             |  |  |  |

| 29                | I             | RESET    | Hardware reset of MKI       |  |  |  |

| 41                | I             | -IOW     | CPU I/O Write Strobe        |  |  |  |

| 40                | I             | -IOR     | CPU I/O Read Strobe         |  |  |  |

| 39                | I             | -SCPCS   | Decode of SA<9:0>.          |  |  |  |

|                   |               |          | Provide an active           |  |  |  |

|                   |               |          | signal when an access       |  |  |  |

|                   |               |          | to 062H-06EH (even)         |  |  |  |

|                   |               |          | happens                     |  |  |  |

| 38                | Ι             | SA2      | System Address Bus Bit<br>2 |  |  |  |

| 4, 5, 8           | в             | [SDO:7]  | System Data Bus Bits        |  |  |  |

| 9, 26, 27, 30, 31 | 1             | SD0:7    | 0_7                         |  |  |  |

| 37                | 0             | IRQL     | Keyboard Interrupt          |  |  |  |

| 35                | 0             | IRQ12    | [Auxilliary] Auxiliary      |  |  |  |

|                   |               |          | Keyboard                    |  |  |  |

|                   |               |          | Interrupt                   |  |  |  |

| 22                | 0             | A20 GATE | Enable access to the        |  |  |  |

|                   |               |          | memory above                |  |  |  |

|                   |               |          | 1 Megabyte                  |  |  |  |

| 15                | 0             | -SLOWRST | System Processor reset      |  |  |  |

| TABLE | V |

|-------|---|

|-------|---|

| PIN NO. | TYPE | NAME        | PIN DESCRIPTION   |    |

|---------|------|-------------|-------------------|----|

|         |      | External RA | AM Control        | 60 |

| 42      | 0    | RAMCS       | RAM Chip Select   |    |

| 44      | 0    | -RAMOE      | RAM Output Enable |    |

| 43      | 0    | RAMALE      | RAM Address Latch |    |

|         |      |             | Enable            |    |

|         |      | SCP In      | terface           | 65 |

| 18      | I    | SCPA15      | A15 from the SCP  |    |

TABLE V-continued

|               | TYPE | NAME        |                        |

|---------------|------|-------------|------------------------|

| PIN NO.       | TYPE | NAME        | PIN DESCRIPTION        |

| 2 2 10        | n    | 500400.7    | Processor              |

| 2, 3, 10,     | B    | SCPADO:7    | Multiplexed address    |

| 11, 24, 25, 3 |      | COMP        | data bus from the SCP  |

| 16            | I    | SCPALE      | Address Latch Enable   |

| <i>·</i>      |      | 00000       | for SCPADO:7           |

| 6             | I    | -SCPRD      | Memory Read Strobe     |

| 7             | I    | -SCPWR      | Memory Write Strobe    |

| 17            | I    | -PSEN       | Program Store Enable.  |

|               |      |             | Read strobe to         |

|               |      |             | external Program       |

|               |      |             | Memory                 |

| 19            | 0    | –IBF        | Input Buffer Full.     |

|               |      |             | Interrupt to SCP when  |

|               |      |             | the CPU has written to |

|               |      |             | the Input Buffer       |

|               |      | External Po | rt Control             |

| 14            | 0    | -P4WR       | Port 4 Write. Used to  |

|               |      |             | clock SCPADO:7 into 8  |

|               |      |             | external Flip-Flops.   |

|               |      |             | Provides 8 extra       |

|               |      |             | outputs for the SCP    |

| 13            | 0    | -P4RD       | Port 4 Read. Output    |

|               | Ū    | 1 1100      | enable a buffer to     |

|               |      |             | SCPAD<0:7> to          |

|               |      |             | provide 8 inputs       |

| 20            | 0    | –P5WR       | Port 5 Write. Used to  |

| 20            | U    | 15010       | clock SCPADO:7 into 8  |

|               |      |             | external Flip-Flops.   |

|               |      |             | Provides 8 extra       |

|               |      |             | outputs for the SCP    |

| 21            | 0    | -P5RD       | Port 5 Read. Output    |

| 21            | • ·  | 1510        | enable a buffer to     |

|               |      |             | SCPAD<0:7> to          |

|               |      |             | provide 8 inputs       |

| 36            | 0    | –P6WR       | Port 6 Write. Used to  |

| 50            | 0    | 1000        | clock SCPADO:7 into 8  |

|               |      |             | external Flip-Flops.   |

|               |      |             | Provides 8 extra       |

|               |      |             | outputs for the SCP.   |

|               |      | Power and   |                        |

| 20            | Ţ    |             |                        |

| 28            | I    | -ISOLATE    | In the event the SCP   |

|               |      |             | is operating while the |

|               |      |             | rest of the unit is    |

|               |      |             | not powered, this      |

|               |      |             | signal will isolate    |

|               |      |             | the rest of the        |

|               |      |             | signals.               |

| 1, 34         |      | VCC         | Power Supply           |

| 12, 23        |      | GND         | Ground                 |

The required output current driving capabilities of the pins are listed in TABLE VI.

|                                                                                           | TABLE VI                                                        |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| SCPAD<0:7><br>SD<0:7><br>IRQ1<br>IRQ12<br>-SLOWRST<br>A20GATE<br>-IBF<br>-RAMCS<br>-RAMOE | 12 mA<br>16 mA<br>4 mA<br>4 mA<br>12 mA<br>2 mA<br>2 mA<br>2 mA |

| RAMALE<br>-P4WR<br>-P4RD<br>-P5WR<br>-P5RD<br>-P6WR                                       | 2 mA<br>8 MA<br>8 mA<br>8 mA<br>8 mA<br>8 mA<br>8 mA            |

#### CONTROL LOGIC

Referring to FIG. 11, a VLSI top level block diagram is shown. As shown, pins 6, 7, 16, 17, 18, 28, 29, 38, 39, 40 and 41 are unidirectional input pins connected to the control logic, generally identified with the reference numeral 318 by way of buffers 320. Pins 13, 14, 15, 19, 20, 21, 22, 35, 36, 37, 42, 43 and 44 are unidirectional output pins with tristate outputs, connected to the control logic 318 by way of tristate devices 322. The tristate devices 322 are controlled by an ISOLATE signal which places the output pins in a high <sup>10</sup> impedance state during a test mode.