(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5635728号

(P5635728)

(45) 発行日 平成26年12月3日(2014.12.3)

(24) 登録日 平成26年10月24日(2014.10.24)

|              |             |

|--------------|-------------|

| (51) Int.Cl. | F 1         |

| H01L 21/822  | (2006.01)   |

| H01L 27/04   | (2006.01)   |

| H03K 19/00   | (2006.01)   |

| H03K 19/096  | (2006.01)   |

|              | HO1L 27/04  |

|              | HO1L 27/04  |

|              | HO3K 19/00  |

|              | HO3K 19/096 |

請求項の数 24 (全 13 頁)

(21) 出願番号 特願2008-234863 (P2008-234863)

(22) 出願日 平成20年9月12日 (2008.9.12)

(65) 公開番号 特開2010-67900 (P2010-67900A)

(43) 公開日 平成22年3月25日 (2010.3.25)

審査請求日 平成23年8月3日 (2011.8.3)

(73) 特許権者 513192281

ピースフォー ルクスコ エスエイアー

ルエル

P S 4 L u x c o S. a. r. l.

ルクセントルク大公国エルー2121、ル

クセントルク、ヴァル デ ポン マラテ

ス208

(74) 代理人 100101454

弁理士 山田 卓二

(72) 発明者 野田 浩正

東京都中央区八重洲二丁目2番1号 エル

ピーダメモリ株式会社内

審査官 宇多川 勉

最終頁に続く

(54) 【発明の名称】半導体装置、及びテスト方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の電圧を供給する第1の電源線と、

第2の電圧を供給する第2の電源線と、

前記第1及び前記第2の電源線の間に接続され、第1のモードにおける第1の状態であるときに、第1のインピーダンスで前記第1の電源線を前記第2の電源線と電気的に結合状態にし、前記第1のモードにおける第2の状態であるときに、前記第1のインピーダンスより高い第2のインピーダンスで前記第1の電源線を前記第2の電源線と電気的に減結合状態にし、第2のモードにおいて、前記第1のインピーダンスより低い第3のインピーダンスで前記第1の電源線を前記第2の電源線と電気的に結合状態にする回路と、

を備え、

前記第1の状態は、アクティブ状態であり、

前記第2の状態は、アイドル状態であり、

前記第1のモードは、電流消費を低減しているモードであり、

前記第2のモードは、電流消費を低減していないモードである

ことを特徴とする半導体装置。

## 【請求項 2】

前記回路は、

前記第1及び前記第2の電源線の間に接続され、前記第1のモードにおける前記第1の状態であるとき及び第2のモードにおいて、前記第1のインピーダンスで前記第1の電源

10

20

線を前記第2の電源線と電気的に結合状態にし、前記第1のモードにおける前記第2の状態であるとき、前記第2のインピーダンスで前記第1の電源線を前記第2の電源線と電気的に非結合状態にする第1のスイッチ回路と、

前記第1及び前記第2の電源線の間に接続され、前記第2のモードにおいて、前記第1の電源線を前記第2の電源線と電気的に結合状態にする第2のスイッチ回路と、

を備えていることを特徴とする請求項1に記載の半導体装置。

### 【請求項3】

前記回路は、サブスレッショルド電流低減回路を含んでいる

ことを特徴とする請求項1又は請求項2に記載の半導体装置。

### 【請求項4】

第1及び第2の状態を切り替える第1のスイッチ回路を含むサブスレッショルド電流低減回路と、

前記第1及び前記第2の状態を切り替え、前記第1のスイッチ回路の端子間の電源インピーダンスを低減させる第2のスイッチ回路と、

前記第1及び前記第2のスイッチ回路に接続され、第1のスイッチ回路を前記第1の状態に保持し、前記第2のスイッチ回路を前記第2の状態から前記第1の状態に切り替える制御回路と、

を備え、

前記制御回路は、

前記第2のスイッチ回路に接続される不揮発性回路であって、前記第2の状態から前記第1の状態に前記第2のスイッチ回路を切り替えるように書き込まれる不揮発性回路を備えている

ことを特徴とする半導体装置。

### 【請求項5】

第1の状態と第2の状態とを切り替える第1のスイッチ回路を含むサブスレッショルド電流低減回路と、

第1の状態と第2の状態とを切り替え、前記第1のスイッチ回路の第1の電源インピーダンスを低減する第2のスイッチ回路と、

前記第1のスイッチ回路及び前記第2のスイッチ回路に接続され、前記第1のスイッチ回路を前記第1の状態に保持し、前記第2のスイッチ回路を前記第2の状態から前記第1の状態に切り替える、制御回路と、

を有し、

前記制御回路は前記第2のスイッチ回路に接続された不揮発性回路を有し、

前記不揮発性回路が切断されて、前記第2のスイッチ回路を前記第2の状態から前記第1の状態に切り替える、

半導体装置。

### 【請求項6】

第1の電圧を供給するメイン電源線と、

前記第1の電圧と異なる第2の電圧を供給するサブ電源線と、

前記サブ電源線に接続された論理回路と、

前記メイン電源線及び前記サブ電源線の間に接続され、前記第1の状態と前記第2の状態を切り替えることにより前記論理回路に供給される前記第1の電圧及び前記第2の電圧を切り替える、第1のスイッチ回路と、

前記メイン電源線及び前記サブ電源線の間に接続され、前記第1の状態と前記第2の状態を切り替え、前記メイン電源線と前記サブ電源線との間の電源インピーダンスを低減する、第2のスイッチ回路と、

前記第1のスイッチ回路及び前記第2のスイッチ回路に接続され、前記第1のスイッチ回路を前記第1の状態に保持し、前記第2のスイッチ回路を前記第2の状態から前記第1の状態に切り替える制御回路と、

を有し、

10

20

30

40

50

前記制御回路は前記第2のスイッチ回路に接続された不揮発性回路を有し、

前記不揮発性回路が切斷されて、前記第2のスイッチ回路を前記第2の状態から前記第

1の状態に切り替える、

半導体装置。

【請求項7】

第1及び第2の状態を切り替える第1のスイッチ回路を含むサブスレッショルド電流低

減回路と、

前記第1及び前記第2の状態を切り替え、前記第1のスイッチ回路の第1の電源インピ

ーダンスを低減させる第2のスイッチ回路と、

前記第1及び前記第2のスイッチ回路に接続され、前記第1のスイッチ回路を前記第1

の状態に保持し、前記第2のスイッチ回路を前記第2の状態から前記第1の状態に切り替

える制御回路と、

10

を備え、

前記制御回路は、

前記第2のスイッチ回路に接続される不揮発性回路を備え、

前記不揮発性回路は、前記第2のスイッチ回路を前記第2の状態から前記第1の状態に

切り替えるようにプログラムされている

半導体装置。

【請求項8】

さらに、前記第1のスイッチ回路に接続された論理回路を備え、

20

前記第1のスイッチ回路は、前記論理回路に供給される電源電圧を切り替えるように前

記第1及び前記第2の状態を切り替える

ことを特徴とする請求項4、請求項5、及び請求項7のいずれか一項に記載の半導体装

置。

【請求項9】

前記第1及び前記第2のスイッチ回路は、前記制御回路に並列に接続されている

ことを特徴とする請求項4から請求項7のいずれか一項に記載の半導体装置。

【請求項10】

前記第1及び前記第2のスイッチ回路の前記第1の状態は、低いインピーダンス状態で

あり、

30

前記第1及び前記第2のスイッチ回路の前記第2の状態は、高いインピーダンス状態で

ある

ことを特徴とする請求項4又は請求項7に記載の半導体装置。

【請求項11】

前記不揮発性回路は、フューズ回路を含む

ことを特徴とする請求項4から請求項7のいずれか一項に記載の半導体装置。

【請求項12】

さらに、第1の電圧を供給するメイン電源線と、

第2の電圧を供給するサブ電源線と、

を備え、

40

前記第1及び前記第2のスイッチ回路は、前記メイン電源線と前記サブ電源線との間に

それぞれ接続されている

ことを特徴とする請求項4又は請求項7に記載の半導体装置。

【請求項13】

前記第1及び前記第2のスイッチ回路の前記第1の状態は、オン状態であり、

前記第1及び前記第2のスイッチ回路の前記第2の状態は、オフ状態である、

ことを特徴とする請求項5又は請求項6に記載の半導体装置。

【請求項14】

前記不揮発性回路が切斷されて、前記第1のスイッチ回路を前記第1の状態に保持し、

且つ、前記第2のスイッチ回路を前記第2の状態から前記第1の状態に切り替える、

50

ことを特徴とする請求項 5 又は請求項 6 に記載の半導体装置。

**【請求項 15】**

前記制御回路は、前記不揮発性回路と前記第 1 のスイッチ回路との間に接続されたサブスレッショルド電流低減制御回路をさらに有し、

前記不揮発性回路が切斷されるとすぐに、前記サブスレッショルド電流低減制御回路は前記第 1 のスイッチ回路を前記第 1 の状態に保持する、

ことを特徴とする請求項 6 に記載の半導体装置。

**【請求項 16】**

前記第 2 のスイッチ回路は複数のスイッチトランジスタ回路を含み、

各スイッチトランジスタ回路は、前記メイン電源線と前記サブ電源線との間に接続され 10

て、前記第 1 の状態と前記第 2 の状態とを切り替え、

前記不揮発性回路は、前記複数のスイッチトランジスタ回路に接続され、

前記不揮発性回路は切斷されて、前記複数のスイッチトランジスタ回路を前記第 2 の状

態から前記第 1 の状態に切り替え、

前記メイン電源線と前記サブ電源線との間の前記電源インピーダンスは前記第 1 のスイ

ッチ回路と前記スイッチトランジスタ回路の ON 抵抗により生成され、

前記電源インピーダンスは閾値以下である、

ことを特徴とする請求項 6 に記載の半導体装置。

**【請求項 17】**

前記サブスレッショルド電流低減制御回路の不使用の条件が満たされたときに、前記不

揮発性回路が切斷されて前記第 1 のスイッチ回路を前記第 1 の状態に保持し、前記第 2 の

スイッチ回路を前記第 2 の状態から前記第 1 の状態に切り替える、

ことを特徴とする請求項 6 に記載の半導体装置。

**【請求項 18】**

前記条件は前記論理回路に含まれるトランジスタの電流リークに関する、

ことを特徴とする請求項 17 に記載の半導体装置。

**【請求項 19】**

前記制御回路は、

第 1 のインバータと、

前記不揮発性回路は前記第 1 のインバータを介して前記第 2 のスイッチ回路に接続さ

れ、

前記第 1 のスイッチ回路に接続された第 2 のインバータと、

前記第 2 のインバータと前記不揮発性回路との間に接続されたサブスレッショルド電流

低減制御回路と、

をさらに有することを特徴とする請求項 5 に記載の半導体装置。

**【請求項 20】**

電源供給線と論理回路との間に接続され、サブスレッショルド電流リークを低減させる

サブスレッショルド電流低減回路と、前記電源供給線を低いインピーダンス又は高いイン

ピーダンスで前記論理回路と接続する前記サブスレッショルド電流低減回路を制御する制

御回路と、を含んでいる半導体装置をテストする手順と、

前記制御回路によって前記低いインピーダンスにされている前記サブスレッショルド電

流低減回路において半導体装置のサブスレッショルド電流を測定する手順と、

前記サブスレッショルド電流が予め定められた値より低い場合に、前記サブスレッショ

ルド電流低減回路が前記低いインピーダンスによって前記電源供給線を前記前記論理回路

と接続する制御を行うように制御回路に書き込む手順と、

を含むことを特徴とするテスト方法。

**【請求項 21】**

前記制御回路に書き込む手順は、

前記制御回路の不揮発性記憶部に書き込む手順を含む

ことを特徴とする請求項 20 に記載のテスト方法。

20

30

40

50

**【請求項 2 2】**

電源供給線を低いインピーダンス又は高いインピーダンスで論理回路と接続することにより、前記論理回路のサブスレッショルド電流リークを低減させる第1のトランジスタと、前記第1のトランジスタに並列した第2のトランジスタと、前記第1及び前記第2のトランジスタを制御する制御回路とを含む半導体装置をテストする手順と、

前記制御回路によって前記低いインピーダンスにされている前記第1のトランジスタにおいて半導体装置のサブスレッショルド電流を測定する手順と、

前記サブスレッショルド電流が予め定められた値より低い場合に、前記第2のトランジスタを低いインピーダンス状態にさせるように制御回路に書き込む手順と、

を含むことを特徴とするテスト方法。

10

**【請求項 2 3】**

前記制御回路に書き込む手順は、

前記サブスレッショルド電流が前記予め定められた値より低い場合に、前記第2のトランジスタを低いインピーダンス状態にさせるように前記制御回路の不揮発性記憶部に書き込む手順を含む

ことを特徴とする請求項 2 2 に記載のテスト方法。

**【請求項 2 4】**

前記制御回路に書き込む手順は、

前記制御回路の不揮発性記憶部に書き込む手順を含む

ことを特徴とする請求項 2 2 に記載のテスト方法。

20

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、例えば、トランジスタのリーク電流を軽減する S C R C 制御回路を備えた半導体装置に関する。

**【背景技術】****【0 0 0 2】**

D R A M (Dynamic Random Access Memory)などの半導体装置では低電源電圧化と動作スピードの向上、低消費電力化への要求が高まっている。低電源電圧化を図るために電源電圧を低下させた場合、トランジスタのオン電流を確保するためにはトランジスタのしきい電圧をスケーリング則に則して低下させる必要がある。しかし、しきい電圧の低下は、トランジスタのオフ電流、すなわちリーク電流の増加をもたらすことになる。

30

**【0 0 0 3】**

そこで、これまでに、特許文献 1 ~ 3 に示されるようなリーク電流を低減する回路方式がいくつか提案されており、その 1 方式として S C R C (Subthreshold Current Reduction Circuit) 方式が知られている。この方式は、メインの電源線とサブの電源線の 2 種類を設け、両者をスイッチM O S (Metal-Oxide-Semiconductor) のトランジスタで接続し、アイドル状態（待機状態）にはスイッチM O S をオフ状態にすることでサブ電源線へ流出するリーク電流を低減することを実現している。

**【0 0 0 4】**

40

ところで、近年、プロセスの微細化により、デバイス仕上がりバラツキを抑えることが難しくなっており、上記トランジスタのオフ状態でのリーク電流もトランジスタのしきい電圧が高めに仕上がった場合には、S C R C 方式のようなリーク電流低減方式を適用しなくともトランジスタのリーク電流が仕様電流値 (S P E C 電流値) 内に収まることがある。しかし、多くの場合、トランジスタのしきい電圧が低めに仕上がった場合を想定して、S C R C を実行する S C R C 制御回路を組み込んで構成されている。

【特許文献 1】特開 2 0 0 0 - 1 9 5 2 5 4 号公報

【特許文献 2】特開 2 0 0 0 - 0 3 0 4 4 3 号公報

【特許文献 3】特開 2 0 0 0 - 0 4 8 5 6 8 号公報

**【発明の開示】**

50

**【発明が解決しようとする課題】****【0005】**

しかしながら、一度S C R C制御回路を組み込んで半導体装置を構成してしまうと、トランジスタのしきい電圧が高めに仕上がった場合には、前述したようにS C R C制御回路を必要としないため、スイッチM O Sを常にオン状態にすることができる。このとき、常にオン状態とされるスイッチM O Sのオン抵抗により、そもそもS C R C制御回路を組み込まない構成に比べて電源インピーダンスが高くなってしまうという問題がある。

**【0006】**

この問題を解決する一般的な手法として、スイッチM O Sのゲート幅を大きくして、オン抵抗を低減するといった手法が考えられるが、スイッチM O Sのゲート幅を大きくしてしまうと、そのオン／オフを制御するドライバも大きな回路が必要となる。また、スイッチM O Sのオフ状態からオン状態への切り替えに要する時間も長くなり電力も増大してしまうなどの問題も発生する。

10

**【0007】**

本発明は、上記問題を解決すべくなされたもので、その目的は、リーク電流低減方式の制御に用いられるスイッチM O Sなどのスイッチ回路のゲート幅を大きくすることなく、リーク電流低減方式を必要としない場合に、スイッチ回路をオン状態とすることで増加する電源インピーダンスを低減することを可能とする半導体装置を提供することにある。

**【課題を解決するための手段】****【0008】**

20

上記問題を解決するために、本発明は、論理回路と、前記論理回路に供給する電圧を、動作状態がアクティブ状態にてオン状態となり前記動作状態がアイドル状態でオフ状態となることで切り替える第1のスイッチ回路と、前記第1のスイッチ回路と並列に接続され、前記第1のスイッチ回路の端子間の電源インピーダンスを低減させる第2のスイッチ回路と、フューズを有し、当該フューズを切断することにより前記第1のスイッチ回路を常にオン状態とし、前記第2のスイッチ回路をオフ状態からオン状態に切り替えるフューズ回路と、を備えたことを特徴とする半導体装置である。

**【0009】**

また、本発明は、メイン電源線と、前記メイン電源線と異なる電圧を供給するサブ電源線と、前記サブ電源線に接続される論理回路と、フューズを有し、フューズが切断された場合に出力信号を出力するフューズ回路と、前記メイン電源線と前記サブ電源線とに接続され、動作状態がアクティブ状態の場合、オン状態となり前記メイン電源線と前記サブ電源線とを結合状態とし、動作状態がアイドル状態の場合、オフ状態となり前記メイン電源線と前記サブ電源線とを非結合状態とし、前記出力信号に基づいて、前記動作状態に依存せず常に前記メイン電源線と前記サブ電源線とを結合する第1のスイッチ回路と、前記メイン電源線と前記サブ電源線とに接続され、前記動作状態に依存せず前記出力信号に基づいて、オフ状態からオン状態に切り替わり、前記メイン電源線と前記サブ電源線とを結合する第2のスイッチ回路とを備えたことを特徴とする半導体装置である。

30

**【0010】**

また、本発明は、上記に記載の発明において、前記論理回路はトランジスタを含んでおり、前記サブ電源線は、前記トランジスタのソース端子に接続されることを特徴とする。

40

**【0011】**

また、本発明は、上記に記載の発明において、前記動作状態がアクティブ状態の間、前記第1のスイッチ回路をオン状態とする信号を出力し、前記動作状態がアイドル状態の間、前記第1のスイッチ回路をオフ状態とする信号を出力するS C R C制御回路を備え、前記S C R C制御回路は、前記出力信号に基づいて、前記動作状態に依存せず前記第1のスイッチ回路を常にオン状態とする信号を出力することを特徴とする。

**【0012】**

また、本発明は、上記に記載の発明において、前記第1のスイッチ回路が、常にオン状態とされた場合に、前記第1のスイッチ回路のオン抵抗と前記第2のスイッチ回路のオン

50

抵抗を合成した電源インピーダンスが予め定められる電源インピーダンス値内となる個数分、前記第2のスイッチ回路が予め配置されることを特徴とする。

#### 【0013】

また、本発明は、上記に記載の発明において、前記動作状態をアイドル状態とし、前記第1のスイッチ回路をオン状態として測定される前記リーク電流が予め定められる仕様電流値内の場合に、前記フューズ回路のフューズが切断されることを特徴とする。

#### 【発明の効果】

#### 【0014】

この発明によれば、リーク電流低減方式の制御に用いられる第1のスイッチ回路のゲート幅を大きくすることなく、第2のスイッチ回路を第1のスイッチ回路と並列に接続し、リーク電流低減方式を必要としない場合に第1のスイッチ回路を常にオン状態とともに第2のスイッチ回路をオン状態とすることで、第1のスイッチ回路の存在により増加する電源インピーダンスを低減することが可能となる。10

#### 【発明を実施するための最良の形態】

#### 【0015】

以下、本発明の一実施形態を図面を参照して説明する。

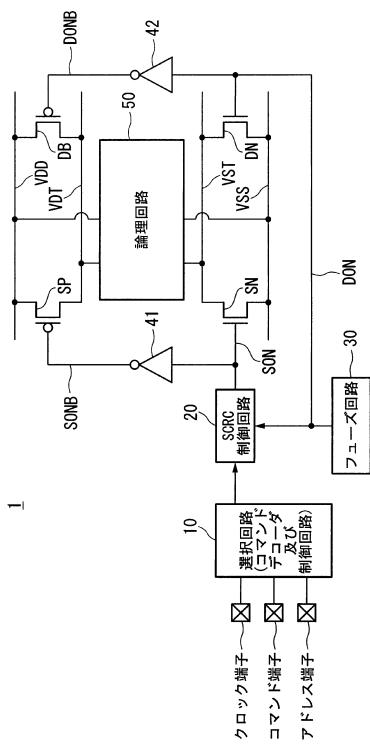

図1は、本実施形態による半導体装置1を示す概略ブロック図である。図1の半導体装置1は、リーク電流低減方式としてS C R C (Subthreshold Current Reduction Circuit) 方式が適用されており、論理回路50、メイン電源線V D D、V S Sと、サブ電源線V D T、V S Tと、メイン電源線とサブ電源線とに接続されるPチャネル型M O S (Metal-Oxide-Semiconductor)トランジスタ(以下、P M O Sという)のスイッチ回路S P、D Bと、Nチャネル型M O Sトランジスタ(以下、N M O Sという)のスイッチ回路S N、D Nと、インバータ41、42と、S C R C制御回路20と、フューズ回路30と、選択回路10とを備える。半導体装置1は、例えば、D R A M (Dynamic Random Access Memory)等に適用され、論理回路50は、例えば、図示しないメモリバンク内のメモリセルから読み出したデータを增幅するセンスアンプ等に適用される回路である。20

#### 【0016】

この構成を備えることにより、S C R C制御回路20からの出力に基づいて、例えば、メモリバンクがアクティブ状態の場合、スイッチ回路S Pとスイッチ回路S Nをオン状態にして、メイン電源線V D D、V S Sと、サブ電源線V D T、V S Tとを接続して、論理回路50を動作状態することができる。そして、メモリバンクがアイドル状態の場合、スイッチ回路S Pとスイッチ回路S Nをオフ状態として、論理回路50に含まれるM O Sトランジスタのリーク電流を低減することが可能となる。30

#### 【0017】

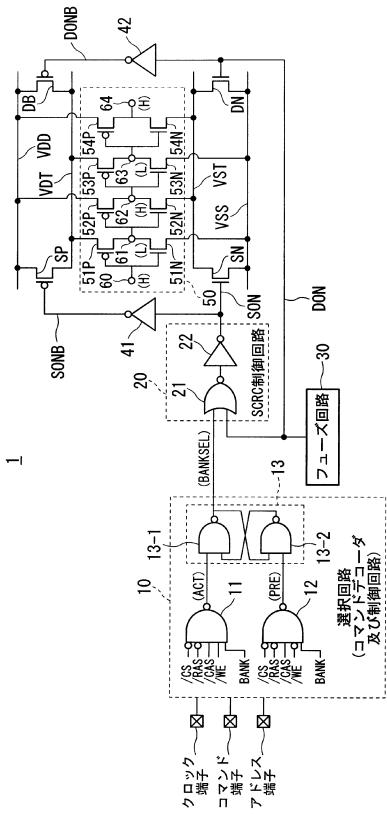

図2は、図1の半導体装置1の具体的な回路構成を示した図面であり、図1と同じ構成について同じ符号を付して示している。なお、図2においても図示していないが、半導体装置1は、複数のメモリバンクを備えており、論理回路50は、例えば、メモリバンク内のメモリセルから読み出したデータを增幅するセンスアンプ等に適用される回路であるものとする。

#### 【0018】

図2において、メイン電源線V D Dは、電源電圧を供給し、サブ電源線V D Tは、アクティブ状態ではV D Dと同電位、アイドル状態では当該電源電圧よりも低い電圧を供給する。また、メイン電源線V S Sは、接地されており、サブ電源線V S Tは、アクティブ状態ではV S Sと同電位、アイドル状態では0 Vよりも高い電圧を供給する。40

#### 【0019】

P M O Sであるスイッチ回路S Pと、スイッチ回路D Bは、ソース端子がメイン電源線V D Dに接続され、ドレイン端子がサブ電源線V D Tに接続される。また、N M O Sであるスイッチ回路S Nと、スイッチ回路D Nは、ソース端子がメイン電源線V S Sに接続され、ドレイン端子がサブ電源線V S Tに接続される。また、スイッチ回路S Pのゲート端子は、インバータ41を介してS C R C制御回路20の出力に接続され、スイッチ回路S50

Nのゲート端子は、S C R C 制御回路20の出力に接続される。また、スイッチ回路D Bのゲート端子は、インバータ42を介してフューズ回路30に接続され、スイッチ回路D Nのゲート端子は、フューズ回路30に接続される。

#### 【0020】

論理回路50は、4つのインバータから構成されており、それぞれのインバータは、P M O S 5 1 P 及びN M O S 5 1 N、P M O S 5 2 P 及びN M O S 5 2 N、P M O S 5 3 P 及びN M O S 5 3 N、P M O S 5 4 P 及びN M O S 5 4 Nの組み合わせで構成されている。

#### 【0021】

P M O S 5 1 P、5 3 Pのソース端子はサブ電源線V D Tに接続され、ドレイン端子が、それれN M O S 5 1 N、5 3 Nのドレイン端子に接続される。N M O S 5 1 N、5 3 Nのソース端子は、メイン電源線V S Sに接続される。また、P M O S 5 2 P、5 4 Pのソース端子はメイン電源線V D Dに接続され、ドレイン端子が、それれN M O S 5 2 N、5 4 Nのドレイン端子に接続される。N M O S 5 2 N、5 4 Nのソース端子は、サブ電源線V S Tに接続される。そして、本実施形態では、アイドル状態では論理回路50の入力端子60にH(High)レベルの信号が入力されることで、端子61にはL(Low)状態の信号が出力され、順に、端子62にはH状態の信号が出力され、端子63にはL状態の信号が出力され、出力端子64にはH状態の信号が出力されることになる。

#### 【0022】

選択回路10は、外部から入力されるコマンド信号をデコードするコマンドデコーダ及び半導体装置1の動作の制御を行う制御回路を備えており、外部端子であるクロック端子、コマンド端子、アドレス端子に接続され、それぞれの端子を介して半導体装置1の外部にある周辺回路からクロック信号、コマンド信号、アドレス信号が入力される。図2では、選択回路10の内部構成のうち、コマンド信号である/C S(Chip Select)信号、/R A S(Row Address Strobe)信号、/C A S(Column Address Strobe)信号、/W E(Word Enable)信号と、選択回路10の内部で生成されるB A N K信号とに基づいて、選択したメモリバンクをアクティブ状態とするB A N K S E L信号を出力する構成の部分の概略構成を示したものである。すなわち、本実施形態のS C R C方式では、本来メモリバンクの制御に用いられるB A N K S E L信号を、S C R C制御回路20にも入力することで、メモリバンクの動作状態に応じて論理回路50におけるリーク電流の低減を図る構成となっている。なお、コマンド端子は、/C S(Chip Select)信号、/R A S(Row Address Strobe)信号、/C A S(Column Address Strobe)信号、/W E(Word Enable)信号ごとにそれぞれ存在する。また、信号名に「/」が付けられたものは、Lレベルで活性状態となる信号である。

#### 【0023】

選択回路10は、N A N D回路11とN A N D回路12と、ラッチ13とを備えている。N A N D回路11は、/C S信号、/R A S信号が反転論理で入力され、/C A S信号、/W E信号、B A N K信号が入力される。そして、コマンド端子からA C Tコマンドとして/C S信号がL(Low)レベル、/R A S信号がLレベル、/C A S信号がH(High)レベル、/W EがHレベル、B A N K信号がHレベルで入力された場合、L状態の信号を出力し、それ以外の状態、例えば、P R Eコマンドが入力された場合、H状態の信号を出力する。

#### 【0024】

一方、N A N D回路12は、/C S信号、/R A S信号、/W E信号が反転論理で入力され、/C A S信号、B A N K信号が入力される。そして、コマンド端子からP R Eコマンドとして/C S信号がLレベル、/R A S信号がLレベル、/C A S信号がHレベル、/W EがLレベル、B A N K信号がHレベルで入力された場合、L状態の信号を出力し、それ以外の状態、例えば、A C Tコマンドが入力された場合、H状態の信号を出力する。

#### 【0025】

ラッチ13は、N A N D回路13-1、13-2を備えており、N A N D回路11とN

10

20

30

40

50

A N D 回路 1 2 の出力を入力として、N A N D 回路 1 3 - 1 の出力において各動作状態に応じた出力状態を保持する。すなわち、A C T コマンドが入力されてから次にP R E コマンドが入力されるまでのアクティブ状態でB A N K S E L 信号をH 状態で保持する。また、P R E コマンドが入力されてから次にA C T コマンドが入力されるまでのアイドル状態でB A N K S E L 信号をL 状態で保持する。

#### 【0026】

フューズ回路 3 0 は、内部にレーザフューズを有しており、レーザフューズが切断されていない場合、L 状態の信号を出力し、レーザフューズが切断された場合、H 状態の信号を出力する。S C R C ( Subthreshold Current Reduction Circuit ) 制御回路は、N O R 回路 2 1 と、インバータ 2 2 を備えており、フューズ回路 3 0 のレーザフューズが切断されていない場合、フューズ回路 3 0 からは、L 状態の信号が出力されるため、選択回路 1 0 から入力されるB A N K S E L 信号が、H レベルの場合、インバータ 2 2 の出力は、H 状態となり、B A N K S E L 信号が、L レベルの場合、インバータ 2 2 の出力は、L 状態となる。また、フューズ回路 3 0 のレーザフューズが切断された場合、フューズ回路 3 0 からは、常にH 状態の信号が出力されるため、インバータ 2 2 は、B A N K S E L 信号の状態に依存せずに、常にH 状態の信号を出力することになる。

#### 【0027】

次に、図 2 に示した半導体装置 1 におけるS C R C 方式のリーク電源低減方式を適用する場合の動作について説明する。S C R C 方式が適用される場合、フューズ回路 3 0 のレーザフューズは切断されていないため、フューズ回路 3 0 からはL 状態の信号が出力されている。まず、前述したB A N K S E L 信号がL レベル、すなわちP R E コマンドが入力されてアイドル状態となっている間、スイッチ回路S P 、S N のゲート端子には、それぞれ、H レベル、L レベルの信号が入力されるため、スイッチ回路S P 、S N は、オフ状態となる。一方、スイッチ回路D B 、D N は、S C R C 制御回路 2 0 の出力に依存しないため、常にオフ状態である。

#### 【0028】

このとき、論理回路 5 0 の入力端子 6 0 には、前述の通り、H レベルの信号が入力されており、P M O S 5 1 P とP M O S 5 3 P は、ゲート端子にL レベルの信号が入力されるためオフ状態でありリーク電流が発生する状態となっている。しかし、P M O S 5 1 P とP M O S 5 3 P のソース端子が、サブ電源線V D T に接続されていることから、ソース端子とゲート端子の相対的な電圧差は低下しており、リーク電流が低減されることになる。一方、N M O S 5 2 N と、N M O S 5 4 N は、ゲート端子にL レベルの信号が入力されているため、オフ状態でありリーク電流が発生する状態となっている。しかし、N M O S 5 2 N と、N M O S 5 4 N のソース端子がサブ電源線V S T に接続されていることから、ソース端子とゲート端子の相対的な電圧差は低下しており、リーク電流が低減されることになる。

#### 【0029】

この状態にて、次にA C T コマンドが入力されてアクティブ状態、すなわちB A N K S E L 信号がH 状態になると、スイッチ回路S P とスイッチ回路S N がオン状態となり、メイン電源線V D D とサブ電源線V D T が接続され、メイン電源線V S S とサブ電源線V S T が接続され、論理回路 5 0 の動作が開始されることになる。

#### 【0030】

前述したリーク電流が、予め定められる仕様電流値 ( S P E C ) 内の場合には、そもそもS C R C 方式を用いる必要がないため、フューズ回路 3 0 のレーザフューズを切断することにより、スイッチ回路S P 、S N を常にオン状態にしつつ、スイッチ回路D B 、D N も常にオン状態にすることが行われる。

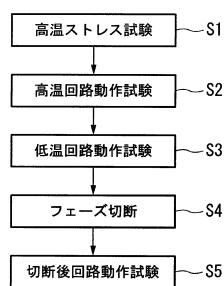

#### 【0031】

S C R C 方式を用いるか否かは、プロセスによるデバイス仕上がりのバラツキに依存する。したがって、図 3 に示すプローブテスト結果により、フューズ回路 3 0 のレーザフューズを切断するか否かを判定する。プローブテストは、図 3 に示すように、高温ストレス

10

20

30

40

50

試験（ステップS1）、高温回路動作試験（ステップS2）、低温回路動作試験（ステップS3）、レーザフューズ切断（ステップS4）、切断後回路動作試験（ステップS5）の順に行われる。すなわち、ステップS1～S3のデバイス仕上がりの判定結果に基づいてフューズ回路30のレーザフューズが切断されることになる。

#### 【0032】

ステップS1～S3の試験工程では、テストモードによりスイッチ回路SP、SNを強制的にオン状態として、論理回路50内のMOSトランジスタのリーク電流を測定する。そして、測定したリーク電流が予め定められる仕様電流値内であるか否かを判定し、仕様電流値内である場合には、フューズ回路30のレーザフューズを、ステップS4の工程において切断する。

10

#### 【0033】

ところで、フューズ回路30のレーザフューズが切断されることにより、前述したようにSRCRC制御回路20からは常にH状態の信号が出力されるため、スイッチ回路SP、SNは常にオン状態となり、メイン電源線VDD、VSTは、それぞれサブ電源線VDT、VSTに接続されることになる。このとき、スイッチ回路SP、SNのオン抵抗により、SRCRC方式の回路をそもそも適用しない場合に比べて電源インピーダンスが増加してしまう。

#### 【0034】

しかし、本実施形態では、フューズ回路30のレーザフューズが切断されることにより、スイッチ回路DB、DNもオン状態となる。スイッチ回路DB、DNは、スイッチ回路SP、SNと並列に、メイン電源線VDD、VSSと、サブ電源線VDT、VSTの間に接続されているため、オン状態とされることにより、スイッチ回路SP、SNの端子間のインピーダンス、すなわちメイン電源線VDDとサブ電源線VDTの間の電源インピーダンス、及びメイン電源線VSSとサブ電源線VSTの間の電源インピーダンスを低減させることができるとなる。

20

#### 【0035】

なお、図2では、メイン電源線VDD、VSSと、サブ電源線VDT、VSTの間にそれぞれに、1つずつスイッチ回路DB、DNを設ける構成として示しているが、この個数は、1つには限られない。すなわち、予め定められる電源インピーダンス値内となるよう必要な個数スイッチ回路DB、DNをメイン電源線VDD、VSSと、サブ電源線VDT、VSTの間に接続することで、SRCRC方式を適用しない場合においても、所望の電源インピーダンスを得ることが可能となる。なお、図2の構成では、フューズ回路30に設けるレーザフューズは、スイッチ回路SP、SN、スイッチ回路DB、DNで共有できるため、1つでもよく、当該1つのレーザフューズを切断することで、スイッチ回路SP、SN、スイッチ回路DB、DNをオン状態にすることができます。しかし、複数のスイッチ回路DB、DNを設ける場合には、オン状態にする個数を調整する必要があるため、その個数に相当する数のレーザフューズフューズ回路30を設けておき、該当するレーザフューズを切断して、電源インピーダンスが所望の値となるように調整することになる。

30

#### 【0036】

また、スイッチ回路SP、SNは、論理回路50の動作が始まる前にオン状態になっている必要があるが、スイッチ回路DB、DNは、スイッチ回路SP、SNのように立ち上がり時間を気にする必要がないため、比較的自由にあらかじめ設けておくことが可能である。

40

#### 【0037】

また、一般的に、レイアウト上では、スイッチ回路SP、SNは、ゲート幅の決まったPMOSとNMOSの組み合わせでユニットセルとして用意しておき、ユニットセルの倍数で必要数を設置されている。このとき、PMOSとNMOSを常に同数使うことは少なく、多くの場合、PMOSあるいはNMOSのいずれか一方は使用されない、すなわち図2のSON配線や、SONB配線には接続されないことになる。そこで、これらの使用されていないPMOSあるいはNMOSを、図2のDON配線や、DONB配線に接続する

50

ことにより、スイッチ回路DB、DNとすることができ、ダミーによるレイアウト面積の増加は、ダミーのゲート幅に単純に比例するわけではなくある程度抑えることが可能である。

#### 【0038】

上記の実施形態の構成により、プローブテスト時に個々のチップに対してデバイス仕上がりを判定してリーク電流が予め定められる仕様電流値内に収まる場合、すなわちMOSトランジスタのしきい電圧が高めに仕上がった場合には、フューズ回路30のレーザフューズを切断して、SRC制御回路20を不活性状態としつつ、SRC制御回路30からは独立して設けたスイッチ回路DB、DNを常にオン状態することで電源インピーダンスを低減させることができるとなる。それにより、SRC方式に用いられるスイッチ回路SP、SNのゲート幅を大きくすることなく電源インピーダンスを低減することが可能となる。10

#### 【0039】

また、上記の実施形態では、SRC方式のリーク電流低減方式に適用した場合であるが、SRC方式以外のリーク電流低減方式、例えばロックごとに電源線を細分化して、アイドル状態のロックの電源は落としてしまうような構成にも適用することができる。。

#### 【図面の簡単な説明】

#### 【0040】

【図1】本実施形態による半導体装置の概略ブロック図である。20

【図2】同実施形態における半導体装置の具体的なブロック図である。

【図3】同実施形態におけるプローブテストの工程を示したフローチャートである。

#### 【符号の説明】

#### 【0041】

1 半導体装置

10 選択回路

20 SRC制御回路

30 フューズ回路

41、42 インバータ

50 論理回路

VDD、VSS メイン電源線

VDT、VST サブ電源線

SP、SN スイッチ回路（第1のスイッチ回路）

DB、DN スイッチ回路（第2のスイッチ回路）30

【図1】

【図2】

【図3】

---

フロントページの続き

(56)参考文献 特開平08-227580(JP,A)

特開平07-211869(JP,A)

特開平09-261013(JP,A)

特開2009-246132(JP,A)

特開2001-053599(JP,A)

特開2000-058754(JP,A)

特開2004-221243(JP,A)

特表2009-500959(JP,A)

特表2008-532265(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 27/04

H03K 19/00

H03K 19/096