(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5254195号

(P5254195)

(45) 発行日 平成25年8月7日(2013.8.7)

(24) 登録日 平成25年4月26日(2013.4.26)

(51) Int.Cl.

H01L 21/20 (2006.01)

H01L 21/205 (2006.01)

F 1

H01L 21/20

H01L 21/205

請求項の数 9 外国語出願 (全 10 頁)

(21) 出願番号 特願2009-290190 (P2009-290190)

(22) 出願日 平成21年12月22日 (2009.12.22)

(65) 公開番号 特開2010-157721 (P2010-157721A)

(43) 公開日 平成22年7月15日 (2010.7.15)

審査請求日 平成24年7月20日 (2012.7.20)

(31) 優先権主張番号 61/140,503

(32) 優先日 平成20年12月23日 (2008.12.23)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 591060898

アイメック

1 M E C

ベルギー、ペー・3001ルーヴァン、カ

ペルドリーフ75番

(74) 代理人 100101454

弁理士 山田 阜二

(74) 代理人 100081422

弁理士 田中 光雄

(74) 代理人 100100479

弁理士 竹内 三喜夫

(74) 代理人 100112911

弁理士 中野 晴夫

最終頁に続く

(54) 【発明の名称】基板上に単結晶半導体層を作製する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に単結晶の半導体材料の層を形成する方法であって、

少なくとも部分的に露出した単結晶のシリコンからなる第2半導体材料、を含む基板を準備する工程と、

少なくとも单分子層で4分子層より少ない第1半導体材料を含むテンプレートを基板上にエピタキシャル成長する工程であって、第1半導体材料はゲルマニウムまたはSiGeであり、テンプレートは臨界膜厚より薄い膜厚を有し、臨界膜厚は転位の出現無しに第1半導体材料で達成できる最大の膜厚であり、テンプレートは第2半導体材料を覆って第2半導体材料と物理的に接続される工程と、

その後に、化学気相堆積により、テンプレート上に第1半導体材料のアモルファス層を堆積する工程と、

熱処理またはレーザアニールを行い、これにより全ての第1半導体材料のアモルファス層を、第1半導体材料の単結晶層に変える工程とを含み、

テンプレートをエピタキシャル成長する工程と、アモルファス層を堆積する工程とは、制御された雰囲気で、同じプロセスチャンバ中またはクラスタツール中で行われる方法。

## 【請求項 2】

第2半導体材料はSi(111)である請求項1に記載の方法。

## 【請求項 3】

テンプレートをエピタキシャル成長する工程は、分子線エピタキシ、低圧化学気相堆積

、大気圧化学気相堆積、プラズマ誘起化学気相堆積、および原子層堆積の1つを用いてテンプレートを成長する工程を含む請求項1に記載の方法。

【請求項4】

熱処理またはレーザーアニールを行う工程は、窒素雰囲気中でレーザーアニールを行う工程を含む請求項1に記載の方法。

【請求項5】

熱処理またはレーザーアニールを行う工程は、400と900との間の温度で熱処理を行う工程を含む請求項1に記載の方法。

【請求項6】

更に、第1半導体材料のアモルファス層にドーパント元素を注入する工程を含む請求項1に記載の方法。 10

【請求項7】

第1半導体材料のアモルファス層にドーパント元素を注入する工程は、ドーパント元素を有する第1半導体材料のアモルファス層を堆積しつつ、ドーパント元素を第1半導体材料のアモルファス層に注入する工程を含む請求項6に記載の方法。

【請求項8】

第1半導体材料のアモルファス層にドーパント元素を注入する工程は、ドーパント元素を有する第1半導体材料のアモルファス層の堆積後で、熱処理またはレーザーアニールを行う前に、第1半導体材料のアモルファス層にドーパント元素を注入する工程を含む請求項6に記載の方法。 20

【請求項9】

更に、第1半導体材料の単結晶層にドーパント元素を注入する工程を含む請求項1に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

シリコン上のエピタキシャルゲルマニウムが、従来のSi相補型金属酸化物半導体(CMOS)回路を拡大するために有用である。SiCMOS上に高速のゲルマニウムフォトダイオードとディテクタを集積することが、光相互接続のために使用される。更に、ゲルマニウムは、GaNと小さな格子不整合を示すのみで、それゆえにIII-VデバイスをSi上に集積するために実際の基板として使用される。Ge(111)層は、(GaNのような)III-V-窒化物のエピタキシャル成長にも使用される。 30

【0002】

従来のSiエレクトロニクスの拡大に加えて、シリコン上へのエピタキシャルゲルマニウムが、高性能応用のために、SiCMOSをGeエレクトロニクスにより置き換えることができる。より高いキャリア移動度のために、ゲルマニウムトランジスタはより速くなる。マーケットのニーズをカバーするには入手可能な材料が不十分であるため、CMOSのためにバルクゲルマニウム基板を使用することはできない。しかしながら、適当な基板上にゲルマニウムの薄層のみを用いることにより、この問題は回避できる。Si基板上へのGeのエピタキシャル成長を使用する重用な長所は、規模である。より大きな直径のゲルマニウム層が、単により大きなSi基板を使用することで得られる。 40

【0003】

エピタキシャル成長は、他の結晶材料上の結晶層を得るために最も用いられる。しかしながら、シリコン上へのゲルマニウムのヘテロエピタキシ成長は、2つの格子間で4%の大きな不整合を有するため、むしろ難しい。格子間距離のこの違いは、アイランド成長を導き、高い表面粗れと、Ge層中での高密度の貫通転位(TDD)を招く。追加のアニール工程や化学機械研磨(CMP)工程が、表面粗さを減らすためにしばしば必要となる。高品質で平坦な結晶ゲルマニウムを、直接シリコン上に形成することは、それ故に困難である。

【0004】

10

20

30

40

50

半導体プロセスでは、基板表面の粗さは、サブミクロンのトランジスタデバイスのチャネル移動度を低減するキーとなる問題の1つである。殆どの応用では、粗い表面はデバイスの処理を複雑にし、平坦な層から処理されるデバイスに比較して劣ったデバイスとなる。

#### 【0005】

一般に、粗さは、物理的な表面の高さの小規模なばらつきの測定である。これは、表面の形状や望まない「うねり」の双方の一部である、大規模なばらつきと対比される。二乗平均平方根（RMS）は、それらの小規模なばらつきの大きさの統計的な測定である。

#### 【0006】

ICプロセスで、化学機械研磨（CMP）技術は、基板表面の粗さを改良するために使用される。しかしながら、例えばゲルマニウムの場合、0.50 nmより小さい表面粗さのRMS値は、達成するのが非常に困難である。この値は、半導体の国際技術ロードマップ（ITRS）の最新の要求に合致するが、トランジスタが更に小型化された場合、単純で費用効果のある方法で表面粗さを更に改良するが更に重要になる。

#### 【0007】

単結晶基板上に単結晶層を形成するための公知の方法は、固相成長（SPE）である。単結晶基板は、その上に堆積されるアモルファス（非常に無秩序な）層に、その構造を押し付けるのに使用される。固相成長は、例えば、結晶シリコン層の上にエピタキシャルシリサイドを形成するために広く使用される。

#### 【0008】

Si(111)基板上への純ゲルマニウムの固相成長は、高真空中で堆積された、数ナノメータの厚さの層が繰り返される。しかしながら、この結果、高密度のアイランドとなる。エピタキシと固相成長の双方は、単結晶Ge層と基板（Si）との間の大きな格子不整合の問題が支配的であり、高い表面粗さやGe層中の高密度の貫通転位となるアイランド成長を示す。アモルファスのゲルマニウム上に堆積された、界面活性剤（例えばAs）が、Si上への固相成長中のアイランド形成を抑制するために使用されてきた。代わりに、Si層で覆われたアモルファスGeもまた、アイランド形成を抑制する。これらの対策は、Ge原子の表面拡散を低減し、これにより粗さを抑制するが、得られる結果は満足するものではない。

#### 【0009】

シリコン上に単結晶ゲルマニウム層を形成する改良された固相エピタキシ法が、本願発明の発明者により、文献WO2009/01324208059461に記載されている。この方法は、アモルファスゲルマニウム堆積とN含有雰囲気中での熱アニールとを含む、シリコン上へのゲルマニウムの固相エピタキシを開示する。得られた単結晶Ge層は平坦であり、0.7 nmの二乗平均平方根の表面粗さを有する（Si(111)上の100 nm結晶GeについてX線反射を用いて測定した）。しかしながら、上記方法により準備された試料のXRD（X線回折）による構造調査は、ゲルマニウムツインの存在を示す。

#### 【発明の目的】

#### 【0010】

本発明の目的は、技術的に知られた方法で得られたものより高品質の単結晶半導体層を形成することである。

#### 【発明の概要】

#### 【0011】

本発明は、添付の請求項に記載された方法に関する。これは、基板上に単結晶の半導体材料の層を形成する方法に関し、この方法は、

基板を準備する工程と、

基板上に少なくとも1つの半導体材料の単分子層（monolayer）を含むテンプレートをエピタキシャル成長する工程と、その後に、

テンプレート上に半導体材料のアモルファス層を堆積する工程と、

熱処理またはレーザアニールを行い、半導体材料のアモルファス層を、半導体材料の单

10

20

30

40

50

結晶層に完全に変える工程と、を含む。

好適な具体例では、少なくとも1つの単結晶は、その上に単結晶層が堆積される基板上の全ての部分を覆う。

【0012】

テンプレートは、好適には、臨界膜厚より小さい厚さを有し、この臨界膜厚は、基板の材料上に転位を発生させること無く堆積される、半導体材料の層の最大厚さとして定義される。

【0013】

好適には、テンプレートを成長する工程と、アモルファス材料の層(3)を堆積する工程とは、同じプロセスチャンバ内で行われる。

10

【0014】

本発明の方法では、基板は単結晶材料でも良く、または少なくとも部分的に露出した単結晶材料である。Siでも良く、またはより好適にはSi(111)である。

【0015】

テンプレートの半導体材料は、IV族半導体材料でも良い。1の具体例では、テンプレートの半導体材料はゲルマニウムである。後者の場合、テンプレートは好適には3~4単分子層より薄い厚さを有する。

【0016】

本発明は、同様に、シリコン基板上に単結晶Ge層を形成する方法であり、この方法は

20

、

基板(1)を準備する工程と、

少なくとも1つのGeの単分子層を含むテンプレートを、シリコン基板上にエピタキシャル成長する工程と、その後に、

テンプレート上にアモルファスGeの層(3)を堆積する工程と、

熱処理またはレーザアニールを行い、これによりアモルファスGeの層を完全に単結晶Geの層に変える工程とを含む。

【0017】

本発明は、同様に、CMOSデバイスの作製のための、本発明にかかる方法の使用に関する。

30

【図面の簡単な説明】

【0018】

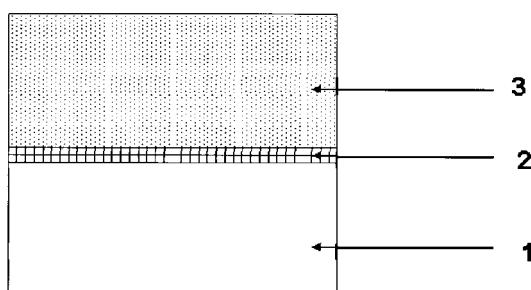

【図1】本発明の方法にかかるスタックを模式的に示す。(1)基板、(2)テンプレート、(3)アモルファス半導体層である。

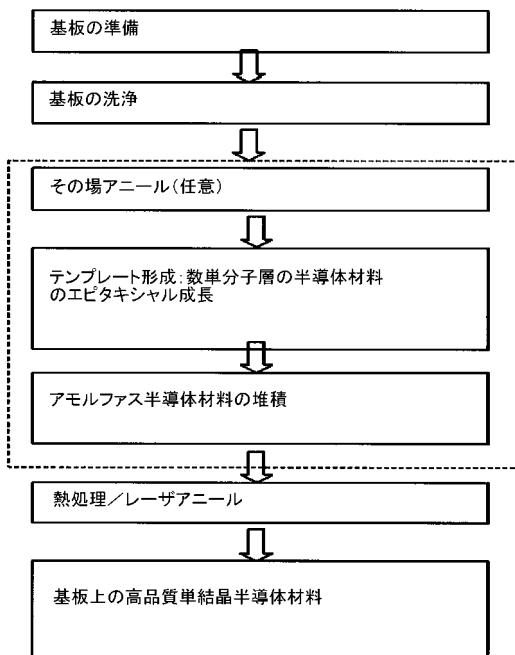

【図2】方法の工程とその順序を示すフローチャートを示す。

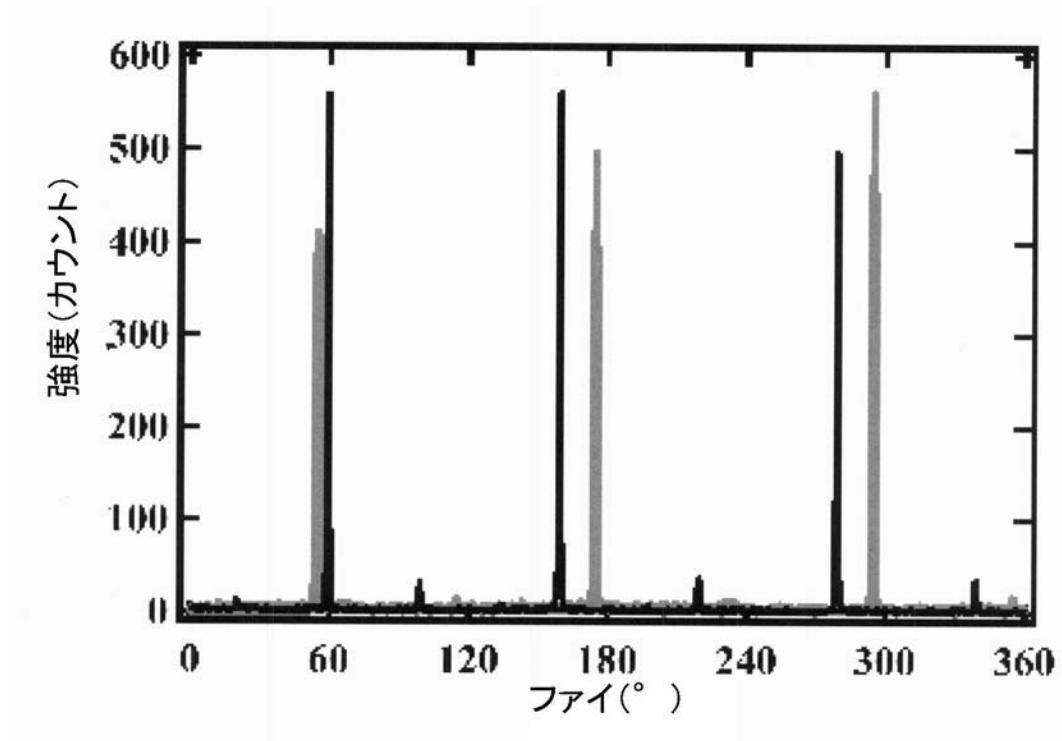

【図3】従来技術の方法と本発明の方法で得られた、Si(111)基板上の60nm単結晶Geからの、Ge(202)の歪対称反射のXRDファイスクランを示す。

【発明の詳細な説明】

【0019】

本発明の異なる具体例は、基板上に単結晶半導体層を形成する方法を開示する。本発明の多くの具体例は、シリコン基板上に単結晶ゲルマニウムを形成する方法について開示する。ゲルマニウム層は、平坦であり、および/またはGeツインの形成は無い。

40

【0020】

この方法は、基板上への単結晶半導体材料の形成まで拡大でき、アイランド形成無しに、レイヤ・バイ・レイヤメカニズムで、基板上に半導体材料がエピタキシャル成長できる。

【0021】

本発明は、基板上に単結晶半導体材料を形成する方法を開示し、この方法は、

基板(1)を準備する工程と、

少なくとも1つの半導体材料の単分子層を含み、または当該単分子層からなるテンプレート(2)を、基板上に、即ち、単結晶材料の層がその上に形成される基板の平坦な表面

50

上にエピタキシャル成長する工程と、その後に、

テンプレート上に、アモルファス半導体材料(3)の層を堆積する(即ち、半導体材料のアモルファス層を堆積する)工程と、

熱処理またはレーザアニールを行い、これによりアモルファス層を完全に単結晶の半導体材料層(即ち、半導体材料の単結晶層)に変える工程とを含む。括弧内の参照符号は、図1に関する。アモルファス層を堆積する工程と、熱処理またはレーザアニールを行う工程は、実際には、テンプレート層の上で行われる固相成長である。本発明の方法にかかるプロセス手順は、図2のフローチャートにより模式的に示される。

【0022】

有利なことに、テンプレートと半導体材料のアモルファス層とは、フローチャートに点線で示したように、制御された雰囲気(例えば、真空をブレークすること無くおよび/またはN<sub>2</sub>雰囲気)で、同じプロセスチャンバ中またはクラスタツール中で堆積される。

【0023】

本発明の方法を用いて形成された半導体材料の単結晶層は、説明中の他の部分で参照した例えは固相エピタキシ(SPE)により形成された、即ち、例えは単結晶Si基板上へのSPEによるGe堆積のように、基板上に直接形成された同様の層より良い品質を有する。より良い品質は、単結晶半導体材料中の、より少ない数の欠陥(例えはツイン)と、改良された粗さ(より平坦な層、またはより低いRMS値)を意味する。双方のパラメータは、単結晶半導体材料を用いて形成された半導体デバイスの性能にとって重要である。

【0024】

本発明の多くの具体例は、異なる材料(異なる化学成分を有する材料)からなる半導体材料と基板を開示する。好適には、半導体材料は、IV族半導体材料(例えは、Si、Ge、Sn)またはSi<sub>x</sub>Ge<sub>y</sub>(0 < x, y < 1)のようなこれらの組み合わせである。本発明の異なる具体例では、半導体材料はゲルマニウムである。

【0025】

本発明の異なる具体例では、基板は単結晶材料であり、または少なくとも部分的に露出した単結晶材料を含む。例えは、露出した単結晶材料の領域と、上面のアモルファス材料の領域とを有するパターニングされた基板である。好適には、基板の単結晶材料は、第2の半導体材料である。これらの具体例では、エピタキシャル成長したテンプレートが横たわり、少なくとも部分的に露出した第2半導体材料と接触する。

【0026】

本発明の異なる具体例では、第2の半導体材料は、Si、Geまたはこれらの組み合わせのようなIV族半導体材料である。好適には、第2半導体材料はSiである。有利なことに、第2の半導体材料は、本発明の方法により高品質の単結晶Ge層の形成が可能なSi(111)のような六方晶の配位(hexagonal orientation)を有する。有利なことは、第2の半導体材料は、GaAs、InP、InSb等のようなIII-V化合物である。

【0027】

他の具体例では、基板の単結晶材料は絶縁性材料である。絶縁性材料は、(La<sub>x</sub>Y<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>またはMgOのような単結晶材料である。これらの具体例では、エピタキシャル成長したテンプレートが横たわり、少なくとも部分的に露出した絶縁性材料と接触する。基板は、更に、バルクSi、サファイア、シリコン・オン・インシルレータ(SOI)、ゲルマニウム・オン・インシルレータ(GeOI)、ガラス、石英、または単結晶材料を支持するのに適した他の材料を含む。

【0028】

本発明の多くの具体例は、半導体材料と基板の間で少なくとも1%の格子不整合を示す。この結果、基板が第2の半導体材料をその上に含む場合、格子不整合は、半導体材料と第2の半導体材料との間の格子定数の差をいう。特別な具体例では、格子不整合は4%である。一般に、格子不整合は、異なった格子定数を有する2つの材料が、一方の材料を他の材料の上に堆積することにより一緒にになった状態をいう。格子不整合は、膜/層の厚さ

10

20

30

40

50

が所定の臨界膜厚より小さくない限り、欠陥の無いエピタキシャル膜／層の成長を妨げる。臨界膜厚より薄い層／膜では、格子不整合は膜の歪により調整される。臨界膜厚より厚い層／膜では、層／膜中の歪は、転位の形成により解放される。

【0029】

本発明の具体例では、第2層の堆積（レイヤ・バイ・レイヤ成長、アイランドの形成無し）が始まる前に、半導体材料の完全な単分子層が基板上に堆積できるように、半導体材料と基板が選択される。

【0030】

本発明の異なる具体例は、基板上に、数単分子層の半導体材料を含むテンプレートのエピタキシャル成長を開示する。単分子層（monolayer）は、1原子だけの厚さの密に詰まった原子の層として定義される。被覆が完全な場合、1単分子層の半導体材料は、テンプレートとして機能するのに十分であり、次の固相成長（即ち、アモルファス層の堆積、および熱処理またはレーザアニール）で形成される単結晶半導体材料の結晶品質および／または粗さを改良する。アモルファス層との直接接触が妨げられるように、全ての基板表面の原子がテンプレート層（少なくとも1層の原子）で覆われた場合に、完全な被覆が得られる。正確に1つの完全な単分子層の堆積を制御することは困難である。それ故に、多くの場合、完全に被覆するために、数単分子層が必要とされる。（材料のタイプに依存する）臨界膜厚に対応する堆積された所定の数の単分子層から始まって、アイランド形成が始まり、即ち所定の領域においてテンプレート材料が他の領域より厚くなりことが可能である。そのようなテンプレート、即ち完全に被覆するが一定でない膜厚を有するテンプレートは、請求項1でいうような、「少なくとも1つの単分子層を含む」テンプレート層の意味に含まれる。この点において、テンプレートの厚さは、転位の形成が制限される限り、（少なくとも幾つかの場所で）臨界膜厚より僅かに大きくても良い。1つの具体例では、テンプレート層の最大膜厚は、臨界膜厚の2倍より小さい。

10

20

【0031】

テンプレートは、例えば分子線成長（MBE）、低圧化学気相堆積（LPCVD）、大気圧化学気相成長（APCVD）、プラズマ誘起化学気相堆積（PECVD）、または原子層堆積（ALD）のような化学的または物理的な堆積技術によりエピタキシャル成長／堆積される。

【0032】

30

本発明は、基板上への単結晶半導体材料のテンプレートのエピタキシャル成長を開示し、このテンプレートは、臨界膜厚より薄い厚さを有する。半導体材料の臨界膜厚は、半導体材料と基板との間の格子不整合に依存する。

【0033】

本発明の具体例では、アモルファス半導体層の結晶化は、基板、テンプレート、およびアモルファス半導体層を含むスタックを、窒素雰囲気中でアニールして行われる。窒素雰囲気は、例えばNH<sub>3</sub>、N<sub>2</sub>、またはNプラズマを含んでも良い。

【0034】

好適な具体例では、シリコン基板上に単結晶Geの層を形成するための方法が開示され、この方法は、

40

（単結晶）シリコン基板を準備する工程と、

シリコン基板上に、少なくとも1つの単分子層のGeを含む、またはこれからなるテンプレートをエピタキシャル成長する工程と、その後に、

テンプレート上にアモルファスのGe層を堆積する工程と、

熱処理またはレーザアニールを行い、これによりアモルファスGeの層を、完全に単結晶Geの層に変える工程とを含む。単結晶シリコン基板は、汚染、粒子、および自然酸化物を除去するために化学的に洗浄される。その後にすぐ、試料は堆積チャンバ中に入れられる。追加のその場アニール工程（例えば、H<sub>2</sub>中でのアニール）は、テンプレートのエピタキシャル成長前に選択的に行われる。

【0035】

50

本発明の具体例では、Ge テンプレートは、少なくとも 1 単分子層の厚さを有する。好適には、Ge テンプレートは、この材料の組み合わせ (Si 上の Ge) に対する臨界膜厚に対応した 3 ~ 4 の単分子層の厚さを有する。

【0036】

本発明の具体例では、化学堆積方法 (PECVD) がアモルファスゲルマニウム堆積に使用された。PECVD によるアモルファスゲルマニウムの堆積は、数トールの圧力のプラズマ源中で、ゲルマン (GeH<sub>4</sub>) 分子をクラックして行われる。アモルファス Ge は、150 と 270 の間の温度で、1.0 μm/h の速度で堆積させた。選択的に、PECVD で水素化アモルファスゲルマニウムの堆積中に、層中にドーパントを導入しても良い。ホスフィン (PH<sub>3</sub>) は、n 型ドーピングのためのリンの導入に使用され、ジボラン (B<sub>2</sub>H<sub>6</sub>) は p 型ドーピングのためのホウ素の導入に使用される。

【0037】

本発明の具体例では、アモルファスゲルマニウム層は、熱処理またはレーザアニールにより結晶化される (アモルファスから単結晶に完全に変えられる)。熱処理は、400 と 900 の間の温度で、数分間 (例えば、450 より高い温度で 1 分間、または 400 で 1 時間) 行われる。好適には、熱アニールは N<sub>2</sub> または他の不活性ガス中で行われる。

【0038】

この方法は、更に、例えば、ドーパント元素をアモルファスゲルマニウム層に注入する提供工程を含んでも良い。本発明の具体例では、ドーパント元素の供給工程は、アモルファスゲルマニウム層の形成中に行なっても良い。本発明の他の具体例では、例えば、アモルファスゲルマニウム層の形成後で、アモルファスゲルマニウム層の結晶化前に、提供工程が行われても良い。代わりに、ドーパント元素の注入は、アモルファスゲルマニウム層の結晶化前に行なっても良い。

【0039】

X 線反射率 (XRR) が、単結晶 Ge 層の表面粗さ、シリコン - ゲルマニウム界面粗さ、単結晶 Ge 層の厚さの測定に用いられた。ゲルマニウム層の構造品質が、X 線回折 (XRD) により調べられた。Ge 層の電気的品質が、ホール移動度測定で調べられた。Si (001) と Ge (001) の移動度が、比較に使用された。N 含有雰囲気中で固相成長により形成された単結晶 Ge 層で得られる電子とホールの移動度は、バルク Si (001) よりも高く、バルク Ge (001) より低い。本発明にかかる方法によるツインの低減は、更に電気的品質を改良する。

【0040】

本発明は、半導体デバイス製造の異なる領域に適用できる。本発明は、Si 基板上への単結晶 Ge 層の形成とともに述べられたが、本発明の利益は他の半導体材料および / または基板に対しても適用できることは、当業者にとって明らかであろう。

【0041】

本発明の方法は、CMOS デバイスの製造にうまく適用でき、そこでは、比較的薄い (< 50 nm) 単結晶 Ge 層が、半導体基板上に形成される。代わりに、本発明の方法は、光起電デバイスの製造にうまく適用でき、そこでは、厚い (約 2 μm) 単結晶 Ge 層が、半導体基板上に形成される。

【比較例】

【0042】

第 1 の例では、約 60 nm のゲルマニウム層が、WO 2009/013242 に記載された方法に従って得られる。Si (111) 基板は化学的に洗浄されて、金属汚染、粒子、および自然酸化物が除去された。その後に、基板は、直ぐに真空装置中に入れられた。基板は脱ガスされた。約 60 nm 膜厚のアモルファス Ge 層が、Ge ソースの熱蒸着により、約 150 で堆積された。堆積中、0.6 sccm の N<sub>2</sub> フラックスが、基板に向かう。N<sub>2</sub> 雰囲気、600 で、1 分間、アニールが行われ、その間に、固相堆積により、アモルファスゲルマニウム層が結晶ゲルマニウム層に変えられた。

10

20

30

40

50

## 【0043】

本発明の第2の例では、Si(111)基板は化学的に洗浄されて、金属汚染、粒子、および自然酸化物が除去された。その後に、基板は、直ぐに真空装置に入れられた。基板は脱ガスされた。数分子層のGeが、400の基板温度で、Si基板の上にエピタキシャル成長された。続いて、基板温度が下げられて、約60nmのアモルファス層を堆積した。N<sub>2</sub>雰囲気、600で、1分間、アニールが行われ、その間に、固相堆積により、アモルファスゲルマニウム層が結晶ゲルマニウム層に変えられた。

## 【0044】

図3は、Si(111)基板上の60nmの結晶Geからの、Ge(202)の歪対称反射のXRGファイスキャンであり、固相堆積前のGeエピタキシがある場合(グレーのピーク)と無い場合(黒のポーク)とを示す。SPE前のGeエピタキシの無いゲルマニウム層は、より多くのツイン(小さいグレーのピークに比較して小さな黒いピーク)を示すことが明らかである。

10

【図1】

【図2】

【図3】

---

フロントページの続き

(72)発明者 ルーベン・リーテン

ベルギー、バー-3520ゾンホーフェン、モーレンウェッヒ106番

審査官 李 哲次

(56)参考文献 特開平01-244608(JP, A)

特開平08-139015(JP, A)

特開平08-158042(JP, A)

特開2001-126987(JP, A)

特開昭59-138331(JP, A)

特開平05-152539(JP, A)

特開平05-226254(JP, A)

国際公開第2007/066811(WO, A1)

特開平07-254560(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/20

H01L 21/205