(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6397265号

(P6397265)

(45) 発行日 平成30年9月26日(2018.9.26)

(24) 登録日 平成30年9月7日(2018.9.7)

(51) Int.Cl.

G03F 9/00 (2006.01)

G03F 7/20 (2006.01)

F 1

G03F 9/00

G03F 7/20H

521

請求項の数 12 (全 12 頁)

(21) 出願番号 特願2014-167957 (P2014-167957)

(22) 出願日 平成26年8月20日 (2014.8.20)

(65) 公開番号 特開2016-46329 (P2016-46329A)

(43) 公開日 平成28年4月4日 (2016.4.4)

審査請求日 平成29年7月28日 (2017.7.28)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 リソグラフィ装置、物品の製造方法、情報処理装置及び決定方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1ショットサイズのショット領域の配列を有する第1層上に、前記第1ショットサイズのショット領域を複数カバーする第2ショットサイズのショット領域の配列を有する第2層を形成するリソグラフィ装置であって、

前記第2層のショット領域の配列を示し、前記第1層のショットレイアウトに対して選択可能な複数の候補ショットレイアウトを仮定して、前記複数の候補ショットレイアウトのそれぞれで前記第2層を形成する場合における前記第1層の各ショット領域に形成されたパターンと前記第2層に形成されるパターンとの相対的な位置ずれ量を演算する演算部と、

前記複数の候補ショットレイアウトのうち、前記演算部で演算された前記位置ずれ量が許容範囲内に収まっている候補ショットレイアウトを、前記第2層を形成する際のショットレイアウトとして決定する決定部と、

を有することを特徴とするリソグラフィ装置。

## 【請求項 2】

前記決定部は、前記複数の候補ショットレイアウトのうち、前記演算部で演算された前記位置ずれ量が最小となる候補ショットレイアウトを、前記第2層を形成する際のショットレイアウトとして決定することを特徴とする請求項1に記載のリソグラフィ装置。

## 【請求項 3】

前記決定部は、前記演算部で演算された前記位置ずれ量が許容範囲内に収まっている前

記候補ショットレイアウトのうち、当該候補ショットレイアウトに含まれるショット領域の数が最小となる候補ショットレイアウトを、前記第2層を形成する際のショットレイアウトとして決定することを特徴とする請求項1に記載のリソグラフィ装置。

【請求項4】

前記第2層に形成されるパターンは、前記第2層を形成する際に用いられる原版のパターンであることを特徴とする請求項1乃至3のうちいずれか1項に記載のリソグラフィ装置。

【請求項5】

前記原版のパターンの位置の理想位置からの第1ずれ量、及び、前記第1層の各ショット領域に形成されたパターンの位置の理想位置からの第2ずれ量を記憶する記憶部を更に有し、

前記演算部は、前記記憶部に記憶された前記第1ずれ量及び前記第2ずれ量に基づいて、前記位置ずれ量を求ることを特徴とする請求項4に記載のリソグラフィ装置。

【請求項6】

前記第1層の各ショット領域に設けられたマークと、前記原版に設けられたマークとの相対位置を検出する検出部を更に有し、

前記演算部は、前記検出部によって検出された前記相対位置に基づいて、前記位置ずれ量を求ることを特徴とする請求項4に記載のリソグラフィ装置。

【請求項7】

前記原版のパターンの位置の理想位置からのずれ量を記憶する記憶部と、

前記第1層の各ショット領域に形成されたパターンの位置の理想位置からのずれ量を計測する計測部と、

を更に有し、

前記演算部は、前記記憶部に記憶された前記ずれ量、及び、前記計測部によって計測された前記ずれ量に基づいて、前記位置ずれ量を求ることを特徴とする請求項4に記載のリソグラフィ装置。

【請求項8】

前記原版のパターンを投影光学系によって基板に投影することで前記第2層を形成することを特徴とする請求項4乃至7のうちいずれか1項に記載のリソグラフィ装置。

【請求項9】

基板上のインプリント材を前記原版で成形することで前記第2層を形成することを特徴とする請求項4乃至7のうちいずれか1項に記載のリソグラフィ装置。

【請求項10】

請求項1乃至9のうちいずれか1項に記載のリソグラフィ装置を用いてパターンを基板に形成する工程と、

前記工程で前記パターンを形成された前記基板を処理する工程と、

を含むことを特徴とする物品の製造方法。

【請求項11】

第1ショットサイズのショット領域の配列を有する第1層上に、前記第1ショットサイズのショット領域を複数カバーする第2ショットサイズのショット領域の配列を有する第2層を形成するリソグラフィ装置におけるショットレイアウトを決定する情報処理装置であって、

前記第2層のショット領域の配列を示し、前記第1層のショットレイアウトに対して選択可能な複数の候補ショットレイアウトを仮定して、前記複数の候補ショットレイアウトのそれぞれで前記第2層を形成する場合における前記第1層の各ショット領域に形成されたパターンと前記第2層に形成されるパターンとの相対的な位置ずれ量を演算する演算部と、

前記複数の候補ショットレイアウトのうち、前記演算部で演算された前記位置ずれ量が許容範囲内に収まっている候補ショットレイアウトを、前記第2層を形成する際のショットレイアウトとして決定する決定部と、

10

20

30

40

50

を有することを特徴とする情報処理装置。

【請求項 1 2】

第1ショットサイズのショット領域の配列を有する第1層上に、前記第1ショットサイズのショット領域を複数カバーする第2ショットサイズのショット領域の配列を有する第2層を形成する際のショットレイアウトを決定する決定方法であって、

前記第2層のショット領域の配列を示し、前記第1層のショットレイアウトに対して選択可能な複数の候補ショットレイアウトを仮定して、前記複数の候補ショットレイアウトのそれぞれで前記第2層を形成する場合における前記第1層の各ショット領域に形成されたパターンと前記第2層を形成されるパターンとの相対的な位置ずれ量を演算する工程と、

前記複数の候補ショットレイアウトのうち、前記工程で演算された前記位置ずれ量が許容範囲内に収まっている候補ショットレイアウトを、前記第2層を形成する際のショットレイアウトとして決定する工程と、

を有することを特徴とする決定方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、リソグラフィ装置、物品の製造方法、情報処理装置及び決定方法に関する。

【背景技術】

【0002】

半導体デバイスなどを製造する際、露光装置やインプリント装置などのリソグラフィ装置が使用されている。半導体デバイスの回路パターンは、一般に、複数の層を重ね合わせて形成される。従って、リソグラフィ装置においては、基板上に既にパターニングされた層（下層）と、これからパターニングする層（上層）との重ね合わせ誤差の管理が重要となる。特に、高い解像度が必要な層をパターニングする場合には、下層と上層との重ね合わせ誤差を解像度の数パーセント以下に抑えなければならない。

【0003】

リソグラフィ装置では、生産性を向上させるために、ショットサイズを大きくする傾向にある。インプリント装置は、一般的には、下層の1つのショット領域に対して重ね合わせるパターンが1つだけ形成されたモールドを用いて上層を形成する。一方、生産性を向上させるために、下層の複数のショット領域に対して重ね合わせることができるパターンが形成されたモールドを用いて上層を形成するインプリント装置が提案されている（特許文献1参照）。このように、上層のショットサイズを大きくすると、基板1枚当たりのショット数が少なくなるため、生産性を向上させることができる。また、生産性の観点から、基板1枚当たりのショット数が最小となるようにショットレイアウトを決定する（画角を広げる）露光装置も提案されている（特許文献2参照）。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2012-204722号公報

【特許文献2】特開平7-211622号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

リソグラフィ装置においては、下層のショットサイズよりも大きいショットサイズで上層をパターニングする場合にも、下層と上層との重ね合わせ誤差を小さくすることが要求されている。しかしながら、下層のショットサイズよりも大きいショットサイズで上層をパターニングする場合において、生産性を向上させるための技術に関しては従来から提案されているが、重ね合わせ誤差を考慮した提案はなされていない。

【0006】

10

20

30

40

50

本発明は、このような従来技術の課題に鑑みてなされ、第1層と第2層との重ね合わせ誤差を低減するのに有利なりソグラフィ装置を提供することを例示的目的一とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明の一側面としてのリソグラフィ装置は、第1ショットサイズのショット領域の配列を有する第1層上に、前記第1ショットサイズのショット領域を複数カバーする第2ショットサイズのショット領域の配列を有する第2層を形成するリソグラフィ装置であって、前記第2層のショット領域の配列を示し、前記第1層のショットレイアウトに対して選択可能な複数の候補ショットレイアウトを仮定して、前記複数の候補ショットレイアウトのそれぞれで前記第2層を形成する場合における前記第1層の各ショット領域に形成されたパターンと前記第2層に形成されるパターンとの相対的な位置ずれ量を演算する演算部と、前記複数の候補ショットレイアウトのうち、前記演算部で演算された前記位置ずれ量が許容範囲内に収まっている候補ショットレイアウトを、前記第2層を形成する際のショットレイアウトとして決定する決定部と、を有することを特徴とする。

【0008】

本発明の更なる目的又はその他の側面は、以下、添付図面を参照して説明される好ましい実施形態によって明らかにされるであろう。

【発明の効果】

【0009】

本発明によれば、例えば、第1層と第2層との重ね合わせ誤差を低減するのに有利なりソグラフィ装置を提供することができる。

【図面の簡単な説明】

【0010】

【図1】本発明の第1の実施形態におけるリソグラフィ装置の構成を示す概略図である。

【図2】下層のショットレイアウトの一例を示す図である。

【図3】上層のショットレイアウトの一例を示す図である。

【図4】上層のショットレイアウトの一例を示す図である。

【図5】上層のショットレイアウトの一例を示す図である。

【図6】上層のショットレイアウトの一例を示す図である。

【図7】上層を形成する際に用いられるマスクのパターンのずれ量の一例を示す図である。

【図8】下層の各ショット領域のパターンのずれ量の一例を示す図である。

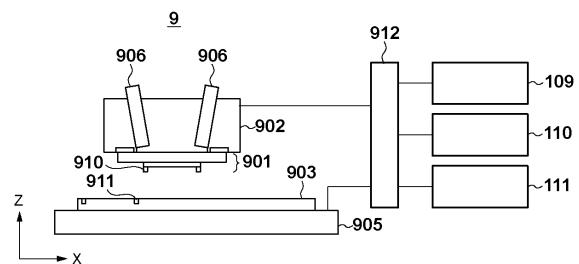

【図9】本発明の第2の実施形態におけるリソグラフィ装置の構成を示す概略図である。

【発明を実施するための形態】

【0011】

以下、添付図面を参照して、本発明の好適な実施の形態について説明する。なお、各図において、同一の部材については同一の参照番号を付し、重複する説明は省略する。

【0012】

<第1の実施形態>

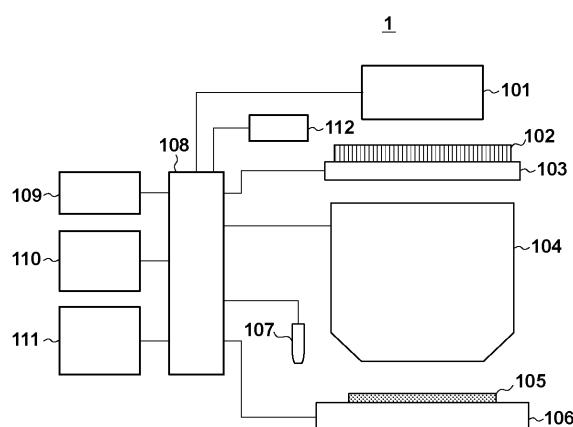

図1は、本発明の第1の実施形態におけるリソグラフィ装置1の構成を示す概略図である。リソグラフィ装置1は、半導体デバイスなどの製造工程であるリソグラフィ工程で使用され、本実施形態では、原版としてのマスクのパターンを投影光学系によって基板に投影して基板を露光する露光装置として具現化される。

【0013】

リソグラフィ装置1は、マスク102を照明する照明光学系101と、マスク102を保持して移動するマスクステージ103と、マスク102のパターンを基板105に投影する投影光学系104とを有する。また、リソグラフィ装置1は、基板105を保持して移動する基板ステージ106と、基板105に設けられたマークを計測する計測部107と、リソグラフィ装置1の全体を制御する制御部108とを有する。更に、リソグラフィ

10

20

30

40

50

装置1は、第1記憶部109と、演算部110と、第2記憶部111と、基板105の各ショット領域に設けられたマークとマスク102に設けられたマークとの相対位置を検出する検出部112とを有する。

【0014】

露光において、光源からの光は、照明光学系101を介してマスク102を照明する。マスク102のパターンを反映する光は、投影光学系104を介して基板105の上に結像する。これにより、マスク102のパターンが基板105に転写され、かかる基板105を現像することで基板上にパターンが形成される。

【0015】

リソグラフィ装置1は、本実施形態では、第1ショットサイズのショット領域の配列を有する第1層(下層)上に、第1ショットサイズのショット領域を複数カバーする第2ショットサイズのショット領域の配列を有する第2層(上層)を形成する。ここで、下層を形成した際の第1ショットサイズよりも大きい第2ショットサイズで上層を形成する際のショットレイアウトについて説明する。

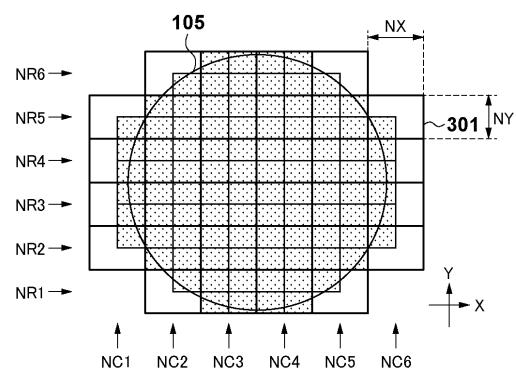

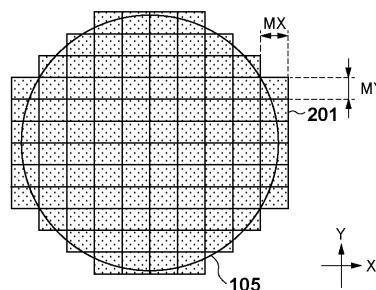

【0016】

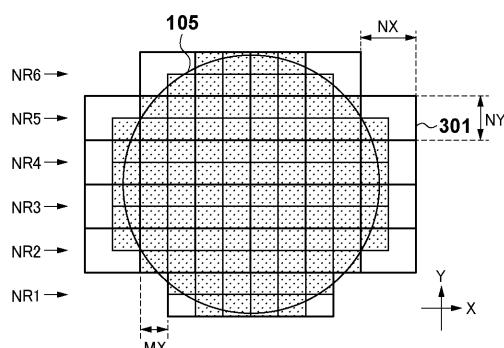

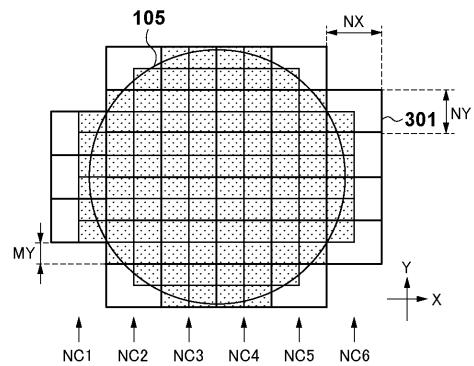

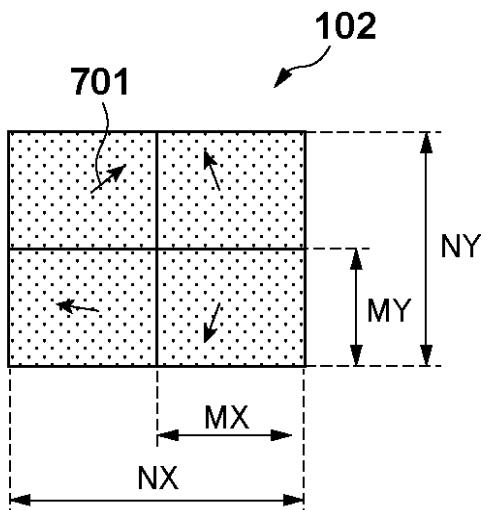

図2は、基板105の複数のショット領域201にパターンが形成された下層のショットレイアウトの一例を示す図である。下層の各ショット領域201のショットサイズは、図2に示すように、X方向をMX、Y方向をMYとする。図3は、図2に示す下層のショットレイアウトに対して選択可能な上層のショットレイアウト(候補ショットレイアウト)の一例を示す図である。上層の各ショット領域301のショットサイズは、下層の各ショット領域201よりも大きく、図3に示すように、X方向をNX、Y方向をNYとする。ショット領域301は、X方向に2つのショット領域201を含み、Y方向に2つのショット領域201を含んでいる(即ち、2行×2列のショット領域201を含んでいる)。図3に示す上層のショットレイアウトにおいては、X方向に6つのショット領域301が配列され、Y方向に6つのショット領域301が配列されている(即ち、6行×6列のショット領域301が配列されている)。図3において、NC1、NC2、NC3、NC4、NC5及びNC6は、X方向のショット領域301の行番号を示し、NR1、NR2、NR3、NR4、NR5及びNR6は、Y方向のショット領域301の列番号を示している。

【0017】

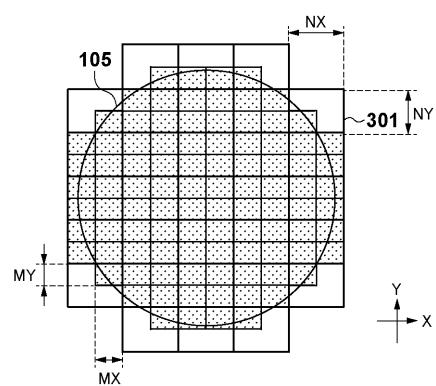

図2に示す下層のショットレイアウトに対して選択可能な上層のショットレイアウトは、図3に示すショットレイアウトの他に、例えば、図4に示すように、NR1列のショット領域301をX方向にMXだけずらしたショットレイアウトもある。図3に示すショットレイアウトにおいて、NR1列からNR6列までのショット領域301を個別にX方向にMXだけずらした場合のショットレイアウトは、図3に示すショットレイアウトを除いて、 $2^6 - 1 = 63$ 通りある。

【0018】

また、図2に示す下層のショットレイアウトに対して選択可能な上層のショットレイアウトは、例えば、図5に示すように、NC1行のショット領域301をY方向にMYだけずらしたショットレイアウトもある。図3に示すショットレイアウトにおいて、NC1行からNC6行までのショット領域301を個別にY方向にMYだけずらした場合のショットレイアウトは、図3に示すショットレイアウトを除いて、 $2^6 - 1 = 63$ 通りある。

【0019】

更に、図2に示す下層のショットレイアウトに対して選択可能な上層のショットレイアウトは、図6に示すように、図3に示すショットレイアウトにおいて全てのショット領域301をX方向にMX、Y方向にMYだけずらしたショットレイアウトもある。

【0020】

従って、図2に示す下層のショットレイアウトに対して選択可能な上層のショットレイアウトは、 $1 + 63 + 63 + 1 = 128$ 通りある。リソグラフィ装置1で上層をパターニングする際には、128通りの上層のショットレイアウトのうちいずれのショットレイア

10

20

30

40

50

ウトを用いてもよいため、本実施形態では、上層と下層との重ね合わせ誤差を考慮して上層のショットレイアウトを決定する。

#### 【0021】

マスク102のパターンは、マスク102の製造時に位置ずれが発生する。また、下層の各ショット領域におけるパターンは、下層の形成時に位置ずれが発生する。従って、上層と下層との重ね合わせ誤差は、マスク102のパターンのずれ量（第1ずれ量）及び下層の各ショット領域のパターンのずれ量（第2ずれ量）で決まる。ここで、マスク102のパターンのずれ量は、マスク102のパターンの位置の理想位置からのずれ量であり、下層の各ショット領域のパターンのずれ量は、下層の各ショット領域に形成されたパターンの位置の理想位置からのずれ量である。

10

#### 【0022】

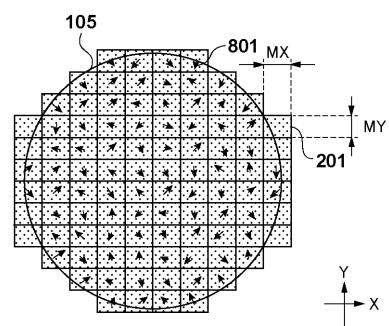

マスク102のパターンのずれ量及び下層の各ショット領域のパターンのずれ量は、本実施形態では、リソグラフィ装置1の外部の装置で検出され、第1記憶部109に記憶されている。図7は、上層を形成する（即ち、ショット領域301をパターニングする）際に用いられるマスク102のパターンのずれ量の一例を示す図である。図7において、ベクトル701は、マスク102のパターン、詳細には、下層の4つのショット領域201のそれぞれに対応するパターンのずれ量を表している。図8は、図2に示すショットレイアウトで形成された下層の各ショット領域201のパターンのずれ量の一例を示す図である。図8において、ベクトル801は、各ショット領域201のパターンのずれ量を表している。第1記憶部109は、上述したように、図7に示すようなマスク102のパターンのずれ量（ベクトル701）及び図8に示すような下層の各ショット領域201のパターンのずれ量（ベクトル801）を記憶する。

20

#### 【0023】

演算部110は、上層のショットレイアウトを仮定して、かかるショットレイアウトで上層を形成する場合における下層の各ショット領域に形成されたパターンとマスク102のパターンとの相対的な位置ずれ量を演算する。本実施形態では、演算部110は、第1記憶部109に記憶されたマスク102のパターンのずれ量及び各ショット領域201のパターンのずれ量に基づいて、各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量を演算する。また、図2に示す下層のショットレイアウトに対して選択可能な上層のショットレイアウトが128通りある。従って、演算部110は、128通りの上層のショットレイアウトのそれぞれについて、各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量を演算する。

30

#### 【0024】

第2記憶部111は、演算部110によって演算された下層の各ショット領域のパターンとマスク102のパターンとの相対的な位置ずれ量を記憶する。本実施形態では、第2記憶部111は、128通りの上層のショットレイアウトのそれぞれと、下層の各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量とを対応づけて記憶する。

#### 【0025】

制御部108は、本実施形態では、ショットレイアウトを決定する決定部として機能する。制御部108は、演算部110で演算された下層の各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量が許容範囲内に収まっているショットレイアウトを、上層を形成する際のショットレイアウトとして決定する。本実施形態では、128通りの上層のショットレイアウトのそれぞれについて、各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量が演算されている。従って、下層の各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量が許容範囲内に収まっているショットレイアウトが複数存在する場合がある。このような場合、制御部108は、かかる複数のショットレイアウトから、1つのショットレイアウトを、上層を形成する際のショットレイアウトとして決定する。この際、下層の各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量が最小とな

40

50

るショットレイアウトを、上層を形成する際のショットレイアウトとして決定するとよい。このように、下層の各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量に基づいて、上層を形成する際のショットレイアウトを決定することでき、上層と下層との重ね合わせ誤差を小さくすることができる。

#### 【0026】

また、リソグラフィ装置1は、投影光学系104を介してマスク102のパターンを基板105に投影するため、上層と下層との重ね合わせ誤差を低減する観点から、投影光学系104のディストーションも考慮するとよい。投影光学系104にディストーションが発生した場合、マスク102のパターンのずれ量に投影光学系104のディストーションに起因するずれ量が重畠されて基板105にパターンが形成される。投影光学系104のディストーションは、求め求めることが可能であるため、投影光学系104のディストーションも第1記憶部109に記憶させることができる。従って、演算部110は、第1記憶部109に記憶された投影光学系104のディストーションを用いて、下層の各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量を演算することができる。換言すれば、マスク102のパターンのずれ量及び各ショット領域201のパターンのずれ量に加えて、投影光学系104のディストーションにも基づいて、各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量が演算される。これにより、投影光学系104のディストーションも考慮して、上層を形成する際のショットレイアウトを決定することができるため、上層と下層との重ね合わせ誤差を小さくすることができる。また、第1記憶部109には、マスク102のパターンのずれ量の代わりに、マスク102に形成されているパターンの形状そのものを記憶してもよい。

#### 【0027】

本実施形態では、上述したように、図2に示す下層のショットレイアウトに対して選択可能な上層のショットレイアウトは、128通りある。但し、ショットサイズによっては、下層のショットレイアウトに対して選択可能な上層のショットレイアウトが数百通りになる場合がある。選択可能な上層のショットレイアウトの数は、下層のショット領域の大きさや上層のショット領域の大きさで変わる。下層のショットレイアウトに対して選択可能な上層のショットレイアウトの数が増えると、演算部110による演算回数が増加してしまうため、演算時間が長くなる。このような場合には、下層のショットレイアウトに対して選択可能な上層のショットレイアウトの全てについて、各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量を演算しなくてもよい。具体的には、1つのショットレイアウトに対する各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量を演算部110が演算するごとに、かかる位置ずれ量が許容範囲内に収まっているかを確認する。演算部110によって演算された各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量が許容範囲内に収まっているれば、演算部110によるそれ以降のショットレイアウトに対する演算を停止する。そして、各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量が許容範囲内に収まっているショットレイアウトを、上層を形成する際のショットレイアウトとして決定する。これにより、演算部110による演算時間を短縮しながらも、上層と下層との重ね合わせ誤差を許容範囲内、即ち、解像度の数パーセント以下に抑えることができる。

#### 【0028】

また、上層と下層との重ね合わせ誤差を最小にするためには、下層の各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量が最小となるショットレイアウトを、上層を形成する際のショットレイアウトとして決定する必要がある。但し、上層と下層との重ね合わせ誤差は、解像度の数パーセント以下に抑えられていればよい。従って、上層と下層との重ね合わせ誤差を抑えながら、リソグラフィ装置1の生産性も考慮することも可能である。具体的には、各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量が許容範囲内に収まっているショットレイアウトのうち、ショット領域の数が最小となるものを、上層を形成する際のショットレイアウトと

10

20

30

40

50

して決定する。これにより、上層と下層との重ね合わせ誤差を小さくしながらも、リソグラフィ装置1の生産性も維持することができる。

【0029】

また、リソグラフィ装置1は、マスク102と基板105とのアライメント（位置合わせ）としてグローバルアライメントを行うため、基板105に設けられたマークを計測する計測部107を有している。計測部107は、オフアクシススコープを含み、下層の各ショット領域201に設けられたマークを計測することができるため、各ショット領域201に形成されたパターンの位置の理想位置からのずれ量も計測することができる。従って、下層の各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量を演算する際に、第1記憶部109に記憶された各ショット領域201のパターンのずれ量の代わりに、計測部107の計測結果を用いてもよい。換言すれば、演算部110は、第1記憶部109に記憶されたマスク102のパターンのずれ量、及び、計測部107によって計測された各ショット領域201のパターンのずれ量に基づいて、相対的な位置ずれ量を演算してもよい。この場合、第1記憶部109は、下層の各ショット領域201のパターンのずれ量を記憶していなくてもよい。

10

【0030】

また、リソグラフィ装置1は、一般的に、基板105の各ショット領域に設けられたマークとマスク102に設けられたマークとの相対位置を検出する検出部112を有している。検出部112は、下層の各ショット領域201に設けられたマークとマスク102に設けられたマークとの相対位置を検出することができる。従って、下層の各ショット領域201のパターンとマスク102のパターンとの相対的な位置ずれ量を演算する際に、検出部112の検出結果を用いてもよい。換言すれば、演算部110は、検出部112によって検出された各ショット領域201に設けられたマークとマスク102に設けられたマークとの相対位置に基づいて、相対的な位置ずれ量を演算してもよい。この場合、リソグラフィ装置1は、第1記憶部109を有していなくてもよい。

20

【0031】

＜第2の実施形態＞

図9は、本発明の第2の実施形態におけるリソグラフィ装置9の構成を示す概略図である。リソグラフィ装置9は、半導体デバイスなどの製造工程であるリソグラフィ工程で使用され、本実施形態では、基板上のインプリント材を原版としてのモールドで成形して基板上のパターンを形成するインプリント装置として具現化される。リソグラフィ装置9は、モールドと基板上のインプリント材とを接触させた状態でインプリント材を硬化させ、基板上の硬化したインプリント材からモールドを引き離すことで基板上にパターンを形成するインプリント処理を行う。

30

【0032】

リソグラフィ装置9は、基板903に転写すべきパターンが形成されたモールド901を保持して移動するモールド保持部902と、基板903を保持して移動する基板ステージ904とを有する。また、リソグラフィ装置9は、モールド901に設けられたマーク910と基板903に設けられたマーク911との相対位置を検出する検出部906と、リソグラフィ装置9の全体を制御する制御部912とを有する。更に、リソグラフィ装置9は、第1記憶部109と、演算部110と、第2記憶部111とを有する。

40

【0033】

リソグラフィ装置9は、リソグラフィ装置1と同様に、第1ショットサイズのショット領域の配列を有する第1層上に、第1層（下層）の複数のショット領域をカバーする第2ショットサイズのショット領域の配列を有する第2層（上層）を形成する。ここで、図2に示すような下層のショットレイアウト及び図3に示すような上層のショットレイアウトを考えると、リソグラフィ装置9においても、図2に示す下層のショットレイアウトに対して選択可能な上層のショットレイアウトは、128通りある。リソグラフィ装置9で上層をパターニングする際には、128通りの上層のショットレイアウトのうちいずれのショットレイアウトを用いてもよい。従って、本実施形態においても、第1の実施形態と同

50

様に、上層と下層との重ね合わせ誤差を考慮して上層のショットレイアウトを決定すればよい。

#### 【0034】

モールド901のパターンのずれ量及び下層の各ショット領域のパターンのずれ量は、リソグラフィ装置9の外部の装置で予め検出することができる。従って、本実施形態では、第1記憶部109は、モールド901のパターンのずれ量及び下層の各ショット領域のパターンのずれ量を記憶する。

#### 【0035】

演算部110は、上層のショットレイアウトを仮定して、かかるショットレイアウトで上層を形成する場合における下層の各ショット領域に形成されたパターンとモールド901のパターンとの相対的な位置ずれ量を演算する。具体的には、演算部110は、第1記憶部109に記憶されたモールド901のパターンのずれ量及び各ショット領域201のパターンのずれ量に基づいて、各ショット領域201のパターンとモールド901のパターンとの相対的な位置ずれ量を演算する。また、演算部110は、128通りの上層のショットレイアウトのそれぞれについて、各ショット領域201のパターンとモールド901のパターンとの相対的な位置ずれ量を演算する。

#### 【0036】

第2記憶部111は、演算部110によって演算された下層の各ショット領域のパターンとモールド901のパターンとの相対的な位置ずれ量を記憶する。第2記憶部111は、128通りの上層のショットレイアウトのそれぞれと、下層の各ショット領域201のパターンとモールド901のパターンとの相対的な位置ずれ量とを対応づけて記憶する。

#### 【0037】

制御部912は、演算部110で演算された下層の各ショット領域201のパターンとモールド901のパターンとの相対的な位置ずれ量が許容範囲内に収まっているショットレイアウトを、上層を形成する際のショットレイアウトとして決定する。なお、上層を形成する際のショットレイアウトの具体的な決定方法は、第1の実施形態と同様であるため、ここでの詳細な説明は省略する。

#### 【0038】

リソグラフィ装置9は、下層の各ショット領域201のパターンとモールド901のパターンとの相対的な位置ずれ量に基づいて、上層を形成する際のショットレイアウトを決定することで、上層と下層との重ね合わせ誤差を小さくすることができる。また、リソグラフィ装置9は、モールド901に形成されたパターンの形状を、モールド901に力を加えることで変形させる機構を備えている場合がある。この場合、変形したモールド901のパターン形状で上層にパターンを形成した際の、下層の各ショット領域との相対的な位置ずれ量に基づいてショットレイアウトを決定することができる。

#### 【0039】

また、リソグラフィ装置9は、モールド901と基板903とのアライメントとしてダイバイダイアライメントを行うため、検出部906を有している。検出部906は、下層の各ショット領域201に設けられたマーク911とモールド901に設けられたマーク910との相対位置を検出することができる。従って、下層の各ショット領域201のパターンとモールド901のパターンとの相対的な位置ずれ量を演算する際に、検出部906の検出結果を用いてもよい。換言すれば、演算部110は、検出部906によって検出された各ショット領域201に設けられたマーク911とモールド901に設けられたマーク910との相対位置に基づいて、相対的な位置ずれ量を演算してもよい。この場合、リソグラフィ装置9は、第1記憶部109を有していなくてもよい。

#### 【0040】

##### <第3の実施形態>

第1記憶部109、演算部110及び第2記憶部111の機能は、リソグラフィ装置1の外部の情報処理装置が備えていてもよい。この場合、リソグラフィ装置1及び9は、演算部110によって演算された、或いは、第2記憶部111に記憶された下層の各ショッ

10

20

30

40

50

ト領域に形成されたパターンと原版のパターンとの相対的な位置ずれ量を情報処理装置から取得する。このように、第1記憶部109、演算部110及び第2記憶部111の機能を備えた情報処理装置も本発明の一側面を構成する。

【0041】

＜第4の実施形態＞

本発明の実施形態における物品の製造方法は、例えば、半導体デバイスなどの物品を製造するのに好適である。かかる製造方法は、リソグラフィ装置1又は9を用いて、パターンを基板に形成する工程と、パターンを形成された基板を処理する工程とを含む。また、かかる製造方法は、上述した工程に続いて、他の周知の工程（酸化、成膜、蒸着、ドーピング、平坦化、エッチング、レジスト剥離、ダイシング、ボンディング、パッケージングなど）を含みうる。本実施形態における物品の製造方法は、従来に比べて、物品の性能、品質、生産性及び生産コストの少なくとも1つにおいて有利である。

10

【0042】

以上、本発明の好ましい実施形態について説明したが、本発明はこれらの実施形態に限定されることはいうまでもなく、その要旨の範囲内で種々の変形及び変更が可能である。

【符号の説明】

【0043】

1、9：リソグラフィ装置 108、912：制御部 109：第1記憶部 11 1

0：演算部

20

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

---

フロントページの続き

(72)発明者 須崎 義夫

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 田口 孝明

(56)参考文献 特開2003-188071(JP, A)

特開2012-204722(JP, A)

特開2000-340493(JP, A)

特開2009-026962(JP, A)

特開2004-281434(JP, A)

特開平07-211622(JP, A)

特開平10-229039(JP, A)

国際公開第2007/013140(WO, A1)

特開平08-078317(JP, A)

(58)調査した分野(Int.Cl., DB名)

IPC H01L 21/30、

21/027、

21/46、

G03F 7/20-7/24、

9/00-9/02