(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-42349

(P2006-42349A)

(43) 公開日 平成18年2月9日(2006.2.9)

(51) Int.C1.

HO3K 19/0175 (2006.01)

F 1

HO3K 19/00

101A

テーマコード(参考)

HO3F 3/45 (2006.01)

HO3F 3/45

A

5J056

HO3F 3/45

Z

5J500

審査請求 未請求 請求項の数 19 O L (全 12 頁)

(21) 出願番号 特願2005-213960 (P2005-213960)

(22) 出願日 平成17年7月25日 (2005.7.25)

(31) 優先権主張番号 60/590,624

(32) 優先日 平成16年7月23日 (2004.7.23)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 11/141,337

(32) 優先日 平成17年5月31日 (2005.5.31)

(33) 優先権主張国 米国(US)

(71) 出願人 500587067

アギア システムズ インコーポレーテッド

アメリカ合衆国, 18109 ペンシルヴァニア, アレンタウン, アメリカン パークウェイ エヌイー 1110

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100106703

弁理士 産形 和央

(74) 代理人 100094112

弁理士 岡部 譲

最終頁に続く

(54) 【発明の名称】CMLバッファ用のコモンモード・シフティング回路

## (57) 【要約】

【課題】CMLデバイスのコモンモード出力電圧を任意の電圧にシフトするためのコモンモード・シフティング回路を開示する。

【解決手段】定電流源がCMLデバイスの各出力に設けられる。定電流はそれぞれコモンモード出力電圧を上昇させるまたは低下させる傾向がある正または負の電流とすることができる。定電流源は、好ましくはCMLデバイス用の電源よりも高い電圧を有する交番電圧源に接続される。本発明はさらに、2つまたはそれ以上の出力ポートを有する電流モード論理回路の出力信号を調節する方法であって、電流モード論理回路の各出力ポートにおいて定電流を与えるステップを備え、それによって前記電流モード論理回路の各出力ポートにおけるコモンモード電圧がレベル・シフトされる方法を提供する。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

2つの入力ポートおよびコモンモード電圧を有する2つの出力ポートを含む電流モード論理回路と、

各々が前記電流モード論理回路の前記2つの出力ポートの1つと第1の供給電圧との間にそれぞれ接続された2つの定電流源とを備え、

それによって前記定電流源が前記出力ポートにおける前記コモンモード電圧をシフトする電流を生成する、電流モード・シフティング回路。

**【請求項 2】**

前記第1の供給電圧が前記出力ポートにおける前記コモンモード電圧よりも大きく、それによって前記定電流源が前記出力ポートに電流を注入し、それによって前記出力ポートにおける前記コモンモード電圧を上昇させる、請求項1に記載の電流モード・シフティング回路。 10

**【請求項 3】**

前記第1の供給電圧が前記出力ポートにおける前記コモンモード電圧よりも小さく、それによって前記定電流源が前記出力ポートから電流をシンクし、それによって前記出力ポートにおける前記コモンモード電圧を低下させる、請求項1に記載の電流モード・シフティング回路。

**【請求項 4】**

前記第1の供給電圧が接地である、請求項3に記載の電流モード・シフティング回路。 20

**【請求項 5】**

前記電流モード論理回路が第2の供給電圧に接続される、請求項1に記載の電流モード・シフティング回路。

**【請求項 6】**

前記定電流源に接続された前記第1の供給電圧が前記電流モード論理回路に接続された第2の供給電圧に等しいかまたはそれよりも大きい、請求項5に記載の電流モード・シフティング回路。

**【請求項 7】**

前記電流モード論理回路の各出力ポートにおけるピーク電圧が前記第2の供給電圧よりも大きくなるほど十分高い値まで前記コモンモード電圧を上昇させるために、前記定電流源が前記出力ポートに十分な電流を注入する、請求項6に記載の電流モード・シフティング回路。 30

**【請求項 8】**

各々が前記電流モード論理回路の前記2つの出力ポートにそれぞれ接続され、負荷終端への接続が可能な2つのDCブロック・コンデンサ

をさらに備える、請求項1に記載の電流モード・シフティング回路。

**【請求項 9】**

各々が前記電流源の1つにそれぞれ直列に接続された2つの抵抗器をさらに備える、請求項1に記載の電流モード・シフティング回路。

**【請求項 10】**

前記電流モード論理回路が、

各々が供給電圧に接続された2つの負荷抵抗器と、

各々が電流供給端子、電流シンク端子および制御端子を有する2つの入力トランジスタであって、各入力トランジスタの前記電流供給端子がそれぞれ前記負荷抵抗器の1つおよび前記電流モード論理回路の出力ポートの1つに接続される、2つの入力トランジスタと、

電流供給端子、電流シンク端子および制御端子を有するテール電流トランジスタであって、前記テール電流トランジスタの前記電流供給端子が前記入力トランジスタの前記電流シンク端子に接続される、テール電流トランジスタと

を含む、請求項1に記載の電流モード・シフティング回路。 50

**【請求項 1 1】**

前記入力トランジスタの前記制御端子の各々にそれぞれ接続された 2 つの入力信号であって、前記入力信号が反対の極性を有し、それによって单一の差分入力信号を形成する、2 つの入力信号と、

前記電流モード論理回路の前記出力ポートの各々にそれぞれ接続された 2 つの出力信号であって、前記出力信号が反対の極性を有し、それによって单一の差分出力信号を形成する、2 つの出力信号と

をさらに備える、請求項 1 に記載の電流モード・シフティング回路。

**【請求項 1 2】**

2 つまたはそれ以上の入力ポートおよび 2 つまたはそれ以上の出力ポートを有し、第 1 10 の供給電圧に接続された電流モード論理回路の出力信号を調節する方法であって、

前記電流モード論理回路の各出力ポートにおいて定電流を与えるステップを含み、

それによって前記電流モード論理回路の各出力ポートにおける前記コモンモード電圧がレベル・シフトされるようになっている方法。

**【請求項 1 3】**

前記定電流が前記電流モード論理回路の各出力ポートから流れ出る電流であり、それによって前記電流モード論理回路の前記出力ポートにおける前記コモンモード電圧が低下する、請求項 1 2 に記載の方法。

**【請求項 1 4】**

各出力ポートにおける前記定電流が前記電流モード論理回路の出力ポート中に流れ込む電流であり、それによって前記電流モード論理回路の出力ポートにおける前記コモンモード電圧が上昇する、請求項 1 2 に記載の方法。

**【請求項 1 5】**

各出力ポートにおける前記定電流は前記電流モード論理回路の出力ポート中に流れ込む電流であり、各出力ポートにおける前記ピーク電圧が前記第 1 の供給電圧よりも大きくなるのに十分高い値まで前記コモンモード電圧を上昇させる、請求項 1 4 に記載の方法。

**【請求項 1 6】**

各出力ポートにおける前記定電流を直列抵抗器に通すステップをさらに含む、請求項 1 2 に記載の方法。

**【請求項 1 7】**

前記電流モード論理回路の前記 2 つまたはそれ以上の入力ポートの各々において入力信号を与えるステップと、

前記電流モード論理回路の前記 2 つまたはそれ以上の出力ポートの各々から出力信号を受け取るステップと

をさらに備える、請求項 1 2 に記載の方法。

**【請求項 1 8】**

前記入力信号が反対の極性を有し、それによって单一の差分入力信号を形成し、前記出力信号が反対の極性を有し、それによって单一の差分出力信号を形成する、請求項 1 7 に記載の方法。

**【請求項 1 9】**

2 つまたはそれ以上の負荷抵抗器を設けるステップと、

定テール電流を与えるステップと、

前記入力ポートにおける前記入力信号に基づいて、前記負荷抵抗器の 1 つに前記定テール電流を指向するステップと

をさらに備える、請求項 1 7 に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は一般に電流モード論理回路、特に高速入出力インターフェース回路における信号レベルに関する。

10

20

30

40

50

## 【背景技術】

## 【0002】

本出願は2004年7月23日に出願された米国仮出願第60/590624号の特典を主張する。

## 【0003】

高速通信装置、たとえば光トランシーバまたは高速入出力(I/O)インターフェース回路では、オフチップ抵抗型負荷を駆動するために電流モード論理('CML')バッファが頻繁に使用される。CMLバッファは一般に比較的低い電源で動作し、たとえばギガヘルツまたは数10ギガヘルツよりも速い非常に速いスイッチング高速を達成することが可能である。さらに、CMLバッファは差分信号を使用するので、それらはコモンモード・ノイズに比較的鈍感である。

## 【0004】

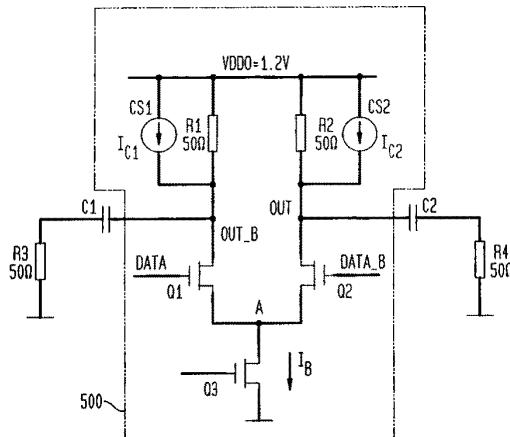

従来のCMLバッファ回路を図1に示す。CMLバッファ100は2つの局部(オンチップ)50オーム抵抗器R1およびR2、2つの入力トランジスタQ1およびQ2、ならびに「テール電流」トランジスタQ3を含む。図1に示すように、抵抗器R1およびR2はそれぞれ供給電圧V<sub>DD0</sub>とトランジスタQ1およびQ2の電流供給(または「ドレン」)端子との間に接続される。トランジスタQ1およびQ2の電流シンク(または「ソース」)端子はトランジスタQ3の電流供給端子にノードAにおいて一緒に接続される。最後に、トランジスタQ3の電流シンク端子は接地に接続される。

## 【0005】

従来、CMLバッファ100は、トランジスタQ1およびQ2の制御端子(「ゲート」)にそれぞれ印加される2つのシングルエンド信号DATAおよびDATA\_Bから形成される差分入力信号を有する。差分信号手法によれば、入力信号DATAおよびDATA\_Bは反対の極性を有する。CMLバッファ100はさらに、差分信号を同様に形成する2つの出力OUT\_BおよびOUTを有する。CMLバッファ100の出力OUT\_BおよびOUTはさらに、差分出力信号を受け取るチップの終端インピーダンスを表すオフチップ抵抗器R3およびR4に接続される。

## 【0006】

動作中、一定のバイアス電流I<sub>B</sub>がトランジスタQ3によってCMLバッファに導入される。電流I<sub>B</sub>は予め決定され(事前決定され)、I<sub>B</sub>電流源トランジスタのバイアス・レベルによって設定される。当技術分野においてよく知られているように、電流I<sub>B</sub>は電流ミラー接続を介してトランジスタQ3によって与えられる。

## 【0007】

入力信号DATAおよびDATA\_Bによって、電流I<sub>B</sub>は抵抗器R1およびトランジスタQ1によって形成された左側分岐または抵抗器R2およびトランジスタQ2によって形成された右側分岐のいずれかに指向される。たとえば、入力信号DATAが論理値「1」または「高」であり、入力信号DATA\_Bが論理値「0」または「低」である場合、トランジスタQ1を通る電流は増加することになり、トランジスタQ2を通る電流は減少することになる(ただしトランジスタQ1またはQ2をカットオフまたは活動状態にするほどではない)。したがって、より多くの電流が抵抗器R1を流れるので、抵抗器R1の両端間の電圧降下が生じることになり、出力OUT\_Bは「低」値をとることになる。同時に、より少ない電流が抵抗器R2を流れるので、抵抗器R2の両端間の電圧降下が低下することになり、出力OUTは「高」値をとることになる。代わりに、入力信号DATAが論理「0」信号である場合、電流は右側分岐に指向され、出力OUT\_Bは「高」値をとることになり、出力OUTは「低」値をとる。

## 【0008】

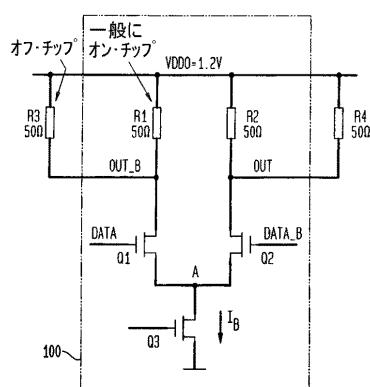

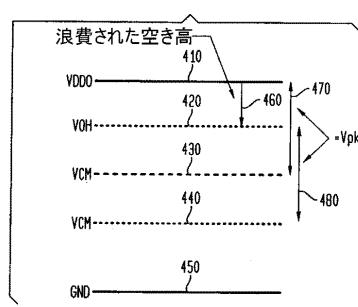

この従来のCMLバッファでは、図2を参照すると、各出力信号の(すなわち出力OUTおよびOUT\_Bにおける)電圧振れはほぼ供給電圧V<sub>DD0</sub>(図2の210)の最大出力電圧V<sub>OH</sub>(同じく図2の210)から、V<sub>DD0</sub>から抵抗器R2またはR4の両端間の電圧降下を引くことによって得られる最小出力電圧V<sub>OL</sub>(図2の230)までであ

10

20

30

40

50

る。出力信号の（すなわち出力OUTにおける）平均値は出力信号（図2の220）の「コモンモード電圧」 $V_{CM}$ を表す。コモンモード電圧 $V_{CM}$ は、以下の合成回路式を用いて、左側分岐および右側分岐を通る等しい電流流れを仮定することによって近似することができる。すなわち、

$$V_{CM} = V_{DDO} - (R2 + R4) / 2 \times I_B / 2$$

上式で、 $V_{CM}$ はコモンモード電圧、 $V_{DDO}$ は供給電圧、 $R2$ はオンチップ抵抗器、 $R4$ はオフチップ抵抗器、および $I_B$ はテール電流である。たとえば、 $R1 = R2 = R3 = R4 = 50$ オーム、 $V_{DDO} = 1.2$ オームおよび $I_B = 20$ mAに対して、合成コモンモード電圧 $V_{CM}$ は0.95ボルトになり、これは比較的高い（すなわち供給電圧 $V_{DDO}$ に近い）。さらに、出力信号（図2の250）のピークツーピーク電圧 $V_{pk}$ は最高出力レベル $V_{OH}$ での電圧 - 最低出力レベル $V_{OL}$ での電圧である。最大出力レベル $V_{OH}$ はほぼ供給電圧 $V_{DDO}$ （すなわちトランジスタQ2が「オフ」の場合に約1.2ボルト）である。（トランジスタQ2が「オン」の場合の）最小出力レベル $V_{OL}$ は次のように決定することができる。すなわち、

$$V_{OL} = V_{DDO} - (R2 \times R4) / (R2 + R4) \times I_B$$

上式で、 $V_{OL}$ は出力信号OUTのその最低出力レベルでの電圧、 $V_{DDO}$ は供給電圧、 $R2$ および $R4$ はそれぞれオンチップおよびオフチップ負荷抵抗器、ならびに $I_B$ はテール電流である。上記で使用した値、 $R2 = R4 = 50$ オームおよび $I_B = 20$ mAに対して、合成最小出力電圧 $V_{OL}$ は0.7Vになる。したがって、ピークツーピーク電圧 $V_{pk}$ は $V_{OH} - V_{OL}$ 、すなわち $1.2V - 0.7V = 0.5$ ボルトである。

#### 【0009】

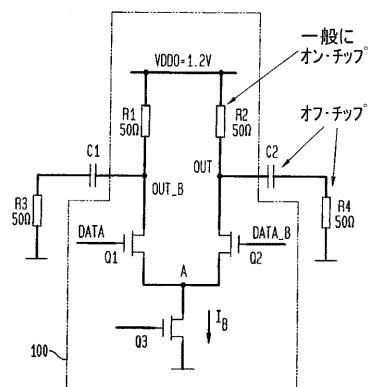

しかしながら、CMLバッファが（「AC結合モード」と呼ばれる）DCブロック・コンデンサを介して受信器に接続される場合、重要な問題が生じる。そのような接続を図3に示す。DCブロック・コンデンサC1およびC2は出力OUT\_BおよびOUTにおいて出力信号のAC部分を通過させるが、信号のDC部分をブロックする。出力OUT\_BおよびOUTがAC結合される場合、信号の動的（AC）部分は抵抗器R3またはR4の遠隔50オーム・インピーダンスと並列な抵抗器R1またはR2の局部50オーム・インピーダンスを「見る」ので、各出力について25オームの等価なACインピーダンスになる。一方、信号のDC部分（すなわちDCコモンモード電圧）は抵抗器R1またはR2の50局部オーム・インピーダンスのみを「見る」。DC部分によって見られる比較的高い50オーム・インピーダンスはコモンモード電圧の比較的低い電圧降下（「IR」降下）を引き起こす。実際に、DCインピーダンス（50オーム）はAC等価インピーダンス（25オーム）の2倍である。

#### 【0010】

AC結合CMLバッファのコモンモード電圧、最大出力レベル、および最小出力レベルは上記と同様な様式で計算することができる。コモンモード電圧は

$$V_{CM} = V_{DDO} - R2 \times I_B / 2 = 1.2V \times 50\text{オーム} \times 20\text{mA} / 2 = 0.7V$$

である。C1およびC2が大きいと仮定すると、AC観点からのピークツーピーク電圧は上記とほぼ同じ、すなわち0.5である。AC電圧は0.7Vのより低いDCコモンモード電圧上に重畠されるので、ここでの最大出力電圧 $V_{OH}$ は0.95V、最低出力電圧 $V_{OL}$ は0.45Vである。AC結合の場合の様々な電圧を図4に図式で示す。出力OUT\_BおよびOUTにおけるAC差分信号はコモンモード電圧 $V_{CM}$ （図4の430）の周りで、最高 $V_{OH}$ （図4の420）および接地450に対して $V_{OL}$ は（図4の440）まで振れる。

#### 【0011】

上記のことから、AC結合CMLバッファにおいて、DCコモンモード出力信号はDC結合の場合よりも著しく低くなり、AC出力信号は同じままであることが明らかである。しかしながら、コモンモード電圧 $V_{CM}$ における大きい下方シフトは使用可能な空き高（headroom）または電圧振れを制限することによってAC出力信号に負の影響を及

10

20

30

40

50

ぼす。結果として、低電力供給電圧（たとえば1.2ボルトまたはそれ以下）において、出力信号の「クリッピング」または歪みが起こることがある。より詳細には、CMLバッファにおいて、入力トランジスタQ1およびQ2とテール電流トランジスタQ3の両方を飽和モードにおいて動作させることが好ましい。しかしながら、最小出力電圧 $V_{OL}$ （0.45V）の非常に低いレベルはこれらの遷移を活動またはカットオフ・モードで動作させやすくし、歪みまたはクリッピングを引き起こす。

【特許文献1】米国仮出願第60/590624号

【発明の開示】

【発明が解決しようとする課題】

【0012】

AC結合CMLバッファにおいてより低いコモンモード電圧によって引き起こされる歪み問題に対する1つの可能な解決策はトランジスタQ1、Q2およびQ3の幅対長さ比を大きくすることであり、それによってそれらは比較的低いコモンモード電圧に対しても飽和モードに保たれる。しかしながら、実際には、高いW/L比の特典を、W/L比が増加するにつれて増加し、デバイスのスイッチング周波数を低減しやすいデバイスの寄生容量と釣り合わせなければならない。したがって、上述の低コモンモード電圧問題を被らず、高い周波数において動作することができるAC結合CMLバッファを提供することが望ましいであろう。

【課題を解決するための手段】

【0013】

手短に説明すると、本発明はCMLデバイスのコモンモード出力電圧を任意の電圧に、好ましくは電力供給レールの電圧の近くにシフトすることができる電流モード・レベル・シフティング回路である。回路は低電圧電源で動作するのに好適なコモンモード出力電圧を与える。本発明によれば、定電流源を介してそれぞれCMLデバイスの各出力において定電流が与えられる。各出力における定電流が出力中に流れ込む正電流である場合、コモンモード出力電圧は上昇することになる。代わりに、各出力における定電流が出力から流れ出る負電流である場合、コモンモード出力電圧は低下することになる。好ましくは、出力において与えられる定電流はほぼ同じである。定電流源はコモンモード出力電圧を上昇させるのに足りる電流を与えるのに十分な状態にバイアスされるPMOSトランジスタとして実装することができる。

【0014】

したがって、本発明は、2つの入力ポートおよびコモンモード電圧を有する2つの出力ポートを含む電流モード論理回路と、各々が前記電流モード論理回路の前記2つの出力ポートの1つと第1の供給電圧との間にそれぞれ接続された2つの定電流源とを備える、電流モード・シフティング回路として広く説明することができる。定電流源は出力ポートにおけるコモンモード電圧をシフトする電流を出力ポートにおいて生成する。一実施形態において、第1の供給電圧は出力ポートにおけるコモンモード電圧よりも大きく、それによって定電流源は出力ポートに電流を注入し、それによってコモンモード電圧を上昇させる。代わりに、第1の供給電圧は出力ポートにおけるコモンモード電圧よりも小さくすることができ、それによって定電流源は出力ポートから電流をシンクし、それによってコモンモード電圧を低下させる。電流モード・シフティング回路は、各々が電流モード論理回路の2つの出力ポートにそれぞれ接続され、負荷終端への接続が可能な2つのDCブロック・コンデンサをさらに備えることができる。

【0015】

さらなる実施形態において、電流モード論理回路は第2の電源電圧に接続される。好ましくは、（電流源に接続された）第1の供給電圧は（電流モード論理回路に接続された）第2の供給電圧に等しいかまたはそれよりも大きい。その場合、電流モード論理回路の各出力ポートにおけるピーク電圧が前記第1の供給電圧よりも大きくなるほど十分高い値までコモンモード電圧を上昇させるために、定電流源は出力ポートに十分な電流を注入することができる。それは電流源と電流モード論理回路の出力ポートとの間に接続された負荷

10

20

30

40

50

抵抗器をもさらに含むことができる。この実施形態において、また電流源に直列に接続された2つの抵抗器を設けることが好ましい。これらの抵抗器は電流制限抵抗器として働き、電流源を出力変動からバッファする。

#### 【0016】

本発明はさらに、2つの出力ポートを有し、第1の供給電圧に接続された電流モード論理回路の出力信号を調節する方法を提供する。本方法は、電流モード論理回路の各出力ポートにおいて定電流を与えるステップを備え、それによって電流モード論理回路の各出力ポートにおけるコモンモード電圧がレベル・シフトされる。定電流は各出力ポートから流れ出る負電流とることができ、それによってコモンモード電圧を低下させ、または各出力ポート中に流れ込む正電流とことができ、それによってコモンモード電圧を上昇させる。この後者の実施形態において、各出力ポートに注入される定電流は、好ましくは電流モード論理回路の各出力ポートにおけるピーク電圧が第1の供給電圧よりも大きくなるほど十分高い値までコモンモード電圧を上昇させる。本方法は、好ましくは各出力ポートにおける定電流を直列抵抗器に通すことをも含む。

10

次に本発明の様々な実施形態について添付の図面とともに詳細に説明する。

#### 【発明を実施するための最良の形態】

#### 【0017】

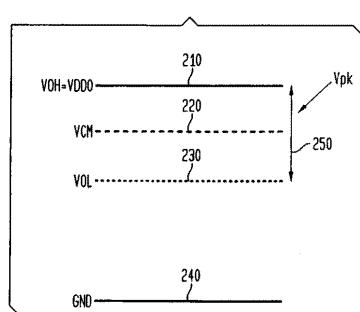

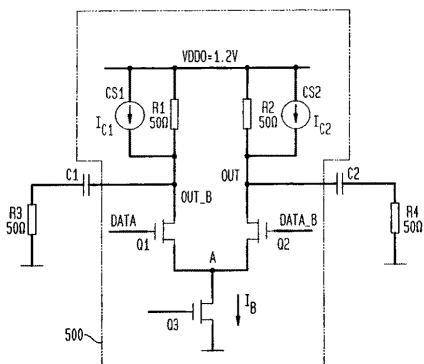

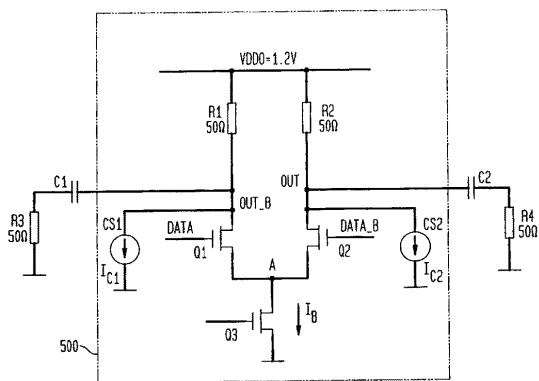

本発明による電流モード・シフティング回路を図5に示す。上述のCMLバッファ100と同様に、電流モード・シフティング回路500は2つの局部（オンチップ）50オーム抵抗器R1およびR2、2つの入力トランジスタQ1およびQ2、ならびに「テール電流」トランジスタQ3を含む。抵抗器R1およびR2はそれぞれ供給電圧VDDOとトランジスタQ1およびQ2の電流供給（または「ドレイン」）端子との間に接続される。トランジスタQ1およびQ2の電流シンク（または「ソース」）端子はノードAにおいてトランジスタQ3の電流供給端子に一緒に接続される。トランジスタQ3の電流シンク端子は接地に接続される。本発明の一実施形態によれば、電流モード・シフティング回路500はさらに、各々が電流モード・シフティング回路500の2つの出力OUT\_BおよびOUTにそれぞれ接続された2つの定電流源CS1およびCS2を含む。

20

#### 【0018】

上述のCMLバッファ100と同様に、電流モード・シフティング回路500は、トランジスタQ1およびQ2の制御端子（「ゲート」）にそれぞれ印加される2つのシングルエンド信号DATAおよびDATA\_Bから形成される差分入力信号を受け取り、入力信号ATAおよびDATA\_Bは反対の極性を有する。電流モード・シフティング回路500はさらに、単一の差分信号を同様に形成する2つの出力OUT\_BおよびOUTを有する。CMLバッファの出力OUT\_BおよびOUTは、DCブロッキング容量C1およびC2を介して、差分出力信号を受け取るチップの負荷インピーダンスを表すオンチップ抵抗器R3およびR4に接続される。

30

#### 【0019】

電流モード・シフティング回路500は次のように動作する。CMLバッファ100と同様に、電流モード・シフティング回路500におけるトランジスタQ3は、入力トランジスタQ1およびQ2をそれらの飽和領域において動作させる不切替え定バイアス電流IBを与える。入力信号DATAおよびDATA\_Bによって、CMLバッファ100に関して上述したように、電流IBは抵抗器R1およびトランジスタQ1によって形成された左側分岐または抵抗器R2およびトランジスタQ2によって形成された右側分岐のいずれかに指向される。したがって、たとえば、入力信号DATAが論理値「1」または「高」であり、入力信号DATA\_Bが論理値「0」または「低」である場合、トランジスタQ1を通る電流は増加し、トランジスタQ2を通る電流は減少する（ただしトランジスタQ1またはQ2をカットオフまたは活動状態にするほどではない）。したがって、より多くの電流が抵抗器R1を流れるので、抵抗器R1の両端間に電圧降下が生じ、出力OUT\_Bは「低」値をとる。同時に、より少ない電流が抵抗器R2を流れるので、抵抗器R2の両端間の電圧降下が低下し、出力OUTは「高」値をとる。代わりに、入力信号DATA

40

50

が論理「0」信号である場合、電流は右側分岐に指向され、出力OUT\_Bは「高」値をとり、出力OUTは「低」値をとる。

【0020】

本発明によれば、定電流源CS1およびCS2はそれぞれ定DC電流Ic1およびIc2を出力OUT\_BおよびOUTに同時に供給する。これらのDC電流Ic1およびIc2はトランジスタQ3によって要求された電流の一部をソーシングする効果を有し、それによって抵抗器R1およびR2を通る電流は対応して（すなわち量Ic1またはIc2が）減少する。より詳細には、定電流源CS1およびCS2の追加によって、抵抗器R1およびR2を通るコモンモード電流はそれぞれ値I\_B/2 - Ic1およびI\_B/2 - Ic2をとる。結果として、抵抗器R1およびR2の両端間の電圧降下はそれらを流れる電流の関数であり、出力OUT\_BおよびOUTにおけるコモンモード電圧はそれら自体それらの電圧降下によって決定されるので、出力OUT\_BおよびOUTにおけるコモンモード電圧はIc1またはIc2の関数として比例的に増加する傾向がある。実際に、電磁結合（誘導性と容量性の両方）の効果のために、出力OUT\_BおよびOUTにおける出力信号が供給電圧VDDoよりも上に振れさせられることさえある。有利には、Ic1およびIc2が交流電流ではなく直流電流なので、それらはDCブロッキング・コンデンサC1およびC2を通らず、したがってAC出力信号のピークツーピーク振幅に影響を及ぼさない。

10

【0021】

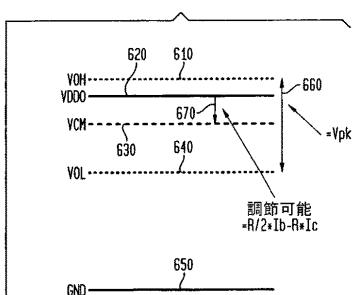

本発明のこの実施形態における様々な電圧を図6に示す。コモンモード電圧VcM（図6の630）は定電流Ic1およびIc2の値に応じて調節可能であることが分かる。各出力信号の（すなわち出力OUT\_BおよびOUTにおける）電圧振れは、すべて接地650を基準にして、供給電圧VDDo（図6の620）よりも大きくすることができる最大出力電圧Voh（図6の610）から、最小出力電圧Vol（図6の640）までである。AC出力信号（図6の660）のピークツーピーク電圧Vpkは上述の従来のCML回路と同じままであるが、コモンモード電圧で上にシフトされる。

20

【0022】

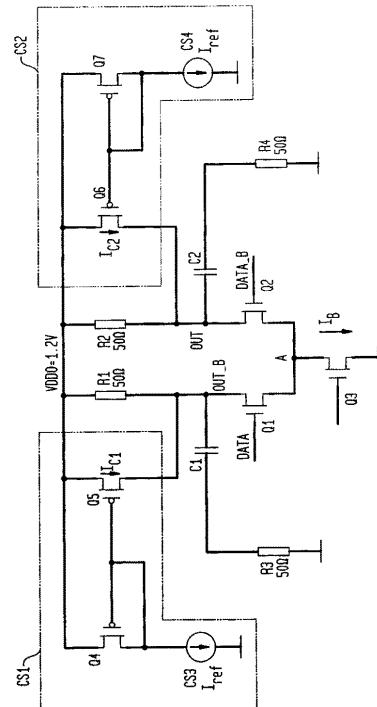

定電流源CS1およびCS2は、各々がコモンモード・シフティング回路500中に存在することができる様々な電圧にもかかわらず定電流を維持するすれば、特定の構成において実装する必要はない。一例として、図7において、定電流源CS1はPMOSトランジスタQとともに電流ミラー構成においてPMOSトランジスタQ5として実装され、トランジスタQ4およびQ5の電流供給（または「ドレイン」）端子はVDDoに接続され、トランジスタQ4およびQ5の制御端子（「ゲート」）は互いに、およびトランジスタQ4の電流シンク（または「ソース」）端子に、および基準電流源Irefを介して接地まで接続される。したがって、電流Ic1は事前決定され、トランジスタQ5の制御端子のバイアス・レベルによって本質的に設定される。定電流源CS1は同様に実装することができる。好ましくは、電流Ic1およびIc2は、コモンモード電圧が可能な最大範囲まで上昇するように可能な限り大きいが、トランジスタQ5およびQ6が飽和モードにおいて動作することができないほどは大きい。

30

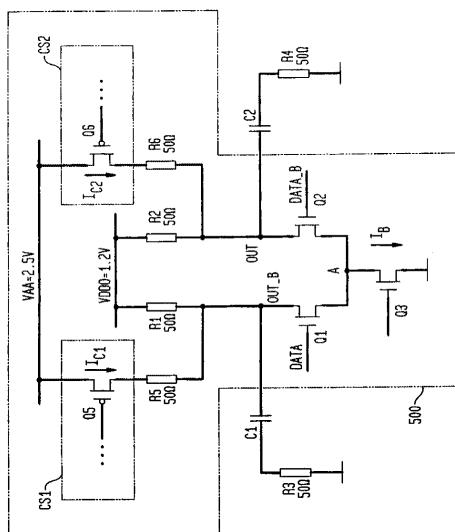

【0023】

図8は各定電流源CS1およびCS2が追加の電圧供給VAAに接続された本発明の代替実施形態を示す。この構成において、電圧供給VAAが電圧供給VDDoよりも大きい電圧を有する場合（たとえばVAA = 2.5V）、出力OUTおよびOUT\_Bにおけるコモンモード電圧を電圧供給VDDoのそれに近づく電圧まで上昇させることができる。増加したコモンモード電圧は回路中の追加の電圧空き高を与え、それによってトランジスタQ1、Q2およびQ3を飽和モードにより容易に保つことができる。さらに、供給電圧VAAによって与えられる追加の空き高によって、トランジスタQ5およびQ6を飽和モードで動作させることなしにトランジスタQ5およびQ6をトランジスタQ1、Q2およびQ3に対して非常に小さくすることができる。有利には、追加の電圧供給VAAの使用は、全DCテール電流IBが同じままなので、電流モード・シフティング回路500によ

40

50

る全電力消費にほとんどまたはまったく影響を及ぼさない。

【0024】

好みしくは、それぞれ定電流源CS1およびCS2においてトランジスタQ5およびQ6によって生成される寄生容量から出力OUTおよびOUT\_Bを分離するために、2つの追加の抵抗器R5およびR6が定電流源CS1およびCS2に直列に追加される。これらの抵抗器なしでは、トランジスタQ5およびQ6の寄生容量は電流モード・シフティング回路500のスイッチング速度を低下させ、抵抗器R3およびR4によって表される負荷終端とのインピーダンス不整合を生じる傾向がある。追加の抵抗器R5およびR6の抵抗は回路の全体的なスイッチング速度仕様または出力インピーダンス要件を満足するのに十分な任意の値とすることができます。

10

【0025】

図9は本発明の代替実施形態を示し、電流源CS1およびCS2がそれぞれ出力OUT\_BおよびOUTと、出力OUT\_BおよびOUTにおけるコモンモード電圧よりも低い供給電圧との間に接続される。たとえば、図9に示すように、電流源CS1およびCS2を接地に接続することができる。この実施形態において、定電流源CS1およびCS2はそれぞれ出力OUT\_BおよびOUTにおけるコモンモード電圧を低下させるまたは引き下げる定電流シンクとして働く。

【0026】

本発明は説明したCMOSプロセス技術ではなく、バイポーラBiCMOS技術とともに使用することができる。トランジスタは上述のものとは反対の型（たとえばn型の代わりにp型トランジスタ）とすることができます。さらに、AC出力終端はV<sub>DD</sub>、V<sub>SS</sub>または接地のいずれかに対しても行うことができる。本発明はさらにAC結合回路に加えてDC結合CML回路に適用することができる。

20

【0027】

以上、改善されたコモンモード電圧をもつ高速通信信号を生成することができる電流モード・シフティング回路について説明した。しかしながら、本発明の上記説明は例として行ったものにすぎず、変形は添付の特許請求の範囲に記載された本発明の範囲から逸脱することなしに当業者には明らかであろうことが理解されよう。

【図面の簡単な説明】

【0028】

30

【図1】DC結合出力端子を有する従来技術のCML回路の回路図である。

【図2】図1に示される回路における様々な電圧を示すグラフである。

【図3】AC結合出力端子を有する従来技術のCML回路の回路図である。

【図4】図3に示される回路における様々な電圧を示すグラフである。

【図5】本発明による電流モード・シフティング回路の回路図である。

【図6】図5に示される回路における様々な電圧を示すグラフである。

【図7】図5に示される電流モード・シフティング回路の好みしい実施形態の回路図である。

【図8】本発明による電流モード・シフティング回路の別の実施形態の回路図である。

【図9】本発明による電流モード・シフティング回路のさらに別の実施形態の回路図である。

40

【図1】

(従来技術)

【図2】

(従来技術)

【図3】

(従来技術)

【図4】

(従来技術)

【図5】

【図6】

【図7】

【図8】

【図9】

## フロントページの続き

(74)代理人 100096943

弁理士 臼井 伸一

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 カムラン アザデット

アメリカ合衆国 07751 ニュージャーシィ, モーガンヴィル, ベイル ドライヴ 622

(72)発明者 フジ ヤング

アメリカ合衆国 07733 ニュージャーシィ, ホルムデル, セイジ ストリート 55

(72)発明者 チュンビン グオ

アメリカ合衆国 18104 ペンシルヴァニア, アレンタウン, ウエスト セダー ストリート

3279

F ターム(参考) 5J056 AA03 BB22 BB60 CC01 CC02 DD27 DD52 FF08 GG10 GG14

5J500 AA01 AA12 AC53 AF10 AH10 AH25 AH29 AK02 AK05 AK09

AK12 AM21 AT02 DP02