(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4743839号

(P4743839)

(45) 発行日 平成23年8月10日(2011.8.10)

(24) 登録日 平成23年5月20日(2011.5.20)

(51) Int.Cl.

F 1

H04N 5/355 (2011.01)

H04N 5/374 (2011.01)H04N 5/335 550

H04N 5/335 740

請求項の数 17 (全 18 頁)

(21) 出願番号 特願2005-38321 (P2005-38321)

(22) 出願日 平成17年2月15日 (2005.2.15)

(65) 公開番号 特開2006-229362 (P2006-229362A)

(43) 公開日 平成18年8月31日 (2006.8.31)

審査請求日 平成20年2月14日 (2008.2.14)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(72) 発明者 岸 隆史

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換部と、前記光電変換部で発生した電荷を一時的に蓄積する半導体領域と、前記光電変換部から前記半導体領域に前記電荷を転送する転送スイッチと、前記半導体領域をリセットするリセットスイッチとを備えた少なくとも1つの画素と、

前記半導体領域から信号を読み出す信号読み出し部と、

前記光電変換部の露光期間において、前記転送スイッチがオフの状態で前記光電変換部から前記半導体領域に漏れこんだ電荷量が所定基準量よりも多い場合に、前記転送スイッチと前記リセットスイッチをそれぞれオンすることで前記光電変換部と前記半導体領域をリセットするように制御し、前記光電変換部の露光期間において前記光電変換部から前記半導体領域に漏れ込む電荷量が前記所定基準量よりも少ない場合に、前記転送スイッチをオンしないで前記リセットスイッチをオンすることで前記光電変換部をリセットしないで前記半導体領域をリセットするように制御する制御部と、

を有することを特徴とする撮像装置。

## 【請求項 2】

前記制御部は、1つの露光期間において、前記半導体領域に生じた信号と基準電位とを比較する比較器による比較動作を少なくとも2回行うように構成されていることを特徴とする請求項1に記載の撮像装置。

## 【請求項 3】

前記信号読み出し部は、前記転送スイッチによる転送動作に応じて前記半導体領域から

読み出される信号と前記転送スイッチによる転送動作前に前記半導体領域から読み出されるリセットレベル信号との差分を画素信号として読み出すように構成され、

前記制御部は、前記比較器による少なくとも2回の比較動作のうち最後の比較動作をリセットレベル信号の読み出し後に行い、前記比較器による少なくとも2回の比較動作のうち最後の比較動作以外の比較動作の結果に応じて前記光電変換部をリセットするように構成されていることを特徴とする請求項2に記載の撮像装置。

**【請求項4】**

前記制御部は、前記比較器による比較結果を蓄積するメモリを含むことを特徴とする請求項2又は請求項3に記載の撮像装置。

**【請求項5】**

前記制御部は、前記比較器による少なくとも2回の比較動作の結果をそれぞれ蓄積するメモリを含むことを特徴とする請求項2又は請求項3に記載の撮像装置。

**【請求項6】**

前記比較器による比較結果を出力する出力回路を更に備えることを特徴とする請求項2乃至請求項5のいずれか1項に記載の撮像装置。

**【請求項7】**

前記出力回路は、前記信号読み出し部によって読み出される画素信号と前記比較器による比較結果とを同一の信号線に対して互いに異なる期間に出力するように構成されていることを特徴とする請求項6に記載の撮像装置。

**【請求項8】**

前記出力回路は、前記信号読み出し部が1画素の画素信号を出力する期間と次の1画素の画素信号を出力する期間との間の期間において、前記比較器による比較結果を出力するように構成されていることを特徴とする請求項7に記載の撮像装置。

**【請求項9】**

前記基準電位を設定可能に構成されていることを特徴とする請求項2乃至請求項8のいずれか1項に記載の撮像装置。

**【請求項10】**

前記制御部が前記光電変換部をリセットするタイミングを設定可能に構成されていることを特徴とする請求項1乃至請求項9のいずれか1項に記載の撮像装置。

**【請求項11】**

前記制御部は、前記転送スイッチがオフの状態で前記光電変換部から前記半導体領域に漏れこんだ電荷量が前記所定基準量よりも多いことを示す信号と露光期間を制御する転送パルスとの論理和を演算してその演算結果によって前記転送スイッチを制御する転送スイッチ制御部を含むことを特徴とする請求項1乃至請求項10のいずれか1項に記載の撮像装置。

**【請求項12】**

前記制御部は、前記転送スイッチと並列に配置された第2転送スイッチを含み、前記転送スイッチは、露光期間を制御する転送パルスによって制御され、前記第2転送スイッチは、前記転送スイッチがオフの状態で前記光電変換部から前記半導体領域に漏れこんだ電荷量が前記所定基準量よりも多いことを示す信号によって制御されることを特徴とする請求項1乃至請求項10のいずれか1項に記載の撮像装置。

**【請求項13】**

前記信号読み出し部から出力される信号を処理する信号処理回路を更に備えることを特徴とする請求項1に記載の撮像装置。

**【請求項14】**

前記信号処理回路は、前記光電変換部の露光期間において前記光電変換部から前記半導体領域に漏れこんだ電荷が前記所定基準量よりも多い場合に、前記光電変換部と前記半導体領域のリセット後に前記光電変換部で発生し前記半導体領域に転送された電荷に対応して前記信号読み出し部から出力される信号を補正することを特徴とする請求項13に記載の撮像装置。

10

20

30

40

50

## 【請求項 15】

前記信号処理回路は、前記光電変換部の露光期間において前記光電変換部から前記半導体領域に漏れ込んだ電荷が前記所定基準量よりも多い場合に、前記光電変換部と前記半導体領域のリセット後に前記光電変換部で発生し前記半導体領域に転送された電荷に対応して前記信号読み出し部から出力される信号にゲインを掛けることを特徴とする請求項13に記載の撮像装置。

## 【請求項 16】

前記信号処理回路は、前記光電変換部の露光期間において前記光電変換部から前記半導体領域に漏れ込む電荷が前記所定基準量よりも多い場合に、前記光電変換部のリセットによる露光期間の短縮分を補うように、前記光電変換部と前記半導体領域のリセット後に前記光電変換部で発生し前記半導体領域に転送された電荷に対応して前記信号読み出し部から出力される信号にゲインを掛けることを特徴とする請求項15に記載の撮像装置。

10

## 【請求項 17】

前記信号読み出し部から出力される信号を処理する信号処理回路を更に備え、前記信号処理回路は、前記比較器による少なくとも2回の比較動作のうち最後の比較動作以外の比較動作の結果が、前記光電変換部の露光期間において前記光電変換部から前記半導体領域に漏れ込む電荷が所定基準量よりも多いことを示している場合に、前記光電変換部のリセットによる露光期間の短縮分を補うように、前記光電変換部と前記半導体領域のリセット後に前記光電変換部で発生し前記半導体領域に転送された電荷に対応して前記信号読み出し部から出力される信号にゲインを掛け、前記最後の比較動作の結果が、前記光電変換部の露光期間において前記光電変換部から前記半導体領域に漏れ込む電荷が前記所定基準量よりも多いことを示している場合に、前記光電変換部と前記半導体領域のリセット後に前記光電変換部で発生し前記半導体領域に転送された電荷に対応して前記信号読み出し部から出力される信号を飽和信号によって置き換えることを特徴とする請求項2に記載の撮像装置。

20

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、撮像装置に関する。

## 【背景技術】

30

## 【0002】

従来から撮像素子のダイナミックレンジの拡大方法として、多くの提案がされている。例えば、特許文献1には、画素部においてフォトダイオードに入射した光の対数に応じた信号を出力する構成が記載されている。また、特許文献2には、フォトダイオードとフローティングディフュージョンの両方で光電変換を行うことによってダイナミックレンジを拡大することが記載されている。特許文献3には、フォトダイオードで発生した電荷を複数回にわたってフローティングディフュージョンに転送することによって、ダイナミックレンジを拡大することが記載されている。

## 【0003】

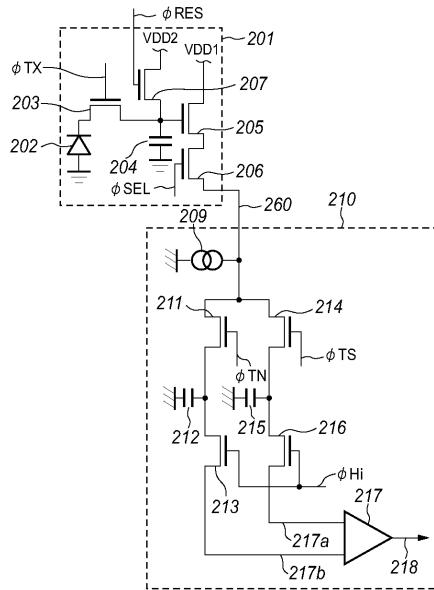

図2は、撮像素子における1画素の構成及びその画素から信号を読み出す回路の構成を示す図である。撮像素子において、2次元の画像を提供する画素アレイは、複数の画素を2次元アレイ状に配列して構成される。

40

## 【0004】

各画素201は、フォトダイオード(以下、PDとも記す)202、転送スイッチ203、フローティングディフュージョン部(以下、FDとも記す)204、リセットスイッチ207、増幅MOSアンプ205、及び、選択スイッチ206を含んで構成される。

## 【0005】

PD202は、光学系を通して入射する光を光電変換する光電変換部として機能する。PD202のアノードは接地ラインに接続され、カソードは転送スイッチ203のソースに接続される。転送スイッチ203は、そのゲート端子に入力される転送パルスTXに

50

よって駆動され、P D 2 0 2 で発生した電荷をF D 2 0 4 に転送する。F D 2 0 4 は、電荷を一時的に蓄積するとともに蓄積した電荷を電圧信号に変換する電荷電圧変換部として機能する。

【 0 0 0 6 】

増幅M O Sアンプ2 0 5は、ソースフォロアとして機能し、そのゲートにはF D 2 0 4 で電荷電圧変換された信号が入力される。また、増幅M O Sアンプ2 0 5は、そのドレインが第1電位を提供する第1電源線V D D 1 に接続され、そのソースが選択スイッチ2 0 6 に接続されている。選択スイッチ2 0 6 は、そのゲートに入力される垂直選択パルスS E L によって駆動され、そのドレインが増幅M O Sアンプ2 0 5 に接続され、そのソースが垂直信号線2 6 0 に接続されている。垂直選択パルスS E L がアクティブルベル(ハイレベル)になると、画素アレイの該当する行に属する画素の選択スイッチ2 0 6 が導通状態になり、増幅M O Sアンプ2 0 5 のソースが垂直信号線2 6 0 に接続される。 10

【 0 0 0 7 】

リセットスイッチ2 0 7 は、そのドレインが第2電位(リセット電位)を提供する第2電源線V D D 2 に接続され、そのソースがF D 2 0 4 に接続されていて、そのゲートに入力されるリセットパルスR E S によって駆動されて、F D 2 0 4 に蓄積されている電荷を除去する。

【 0 0 0 8 】

F D 2 0 4 及び増幅M O Sアンプ2 0 5 他、垂直信号線2 6 0 に定電流を供給する定電流源2 0 9 によってフローティングディフュージョンアンプが構成される。選択スイッチ2 0 6 で選択された行を構成する各画素において、F D 2 0 4 に転送される電荷がF D 2 0 4 で電圧信号に変換されて、フローティングディフュージョンアンプを通じて対応する信号読み出し部2 1 0 に出力される。 20

【 0 0 0 9 】

スイッチ2 1 1 は、F D 2 0 4 のリセット電位をリセットレベル信号として読み出すためのスイッチであり、リセットレベル読み出しパルスT N により駆動される。リセットレベル蓄積容量2 1 2 には、画素信号の読み出しの直前にリセットレベル信号(F D 2 0 4 のリセットレベルに応じた電位の信号)が蓄積される。

【 0 0 1 0 】

スイッチ2 1 4 は、P D 2 0 2 で発生した電荷信号に応じた電圧信号を読み出すためのスイッチであり、信号読み出しパルスT S により駆動される。信号レベル蓄積容量2 1 5 には、画素信号の読み出し時に、その画素信号(P D 2 0 2 からF D 2 0 4 に転送された電荷に応じた電位の信号)が蓄積される。 30

【 0 0 1 1 】

差動アンプ2 1 7 は、リセットレベル蓄積容量2 1 2 に蓄積された信号のレベルと信号レベル蓄積容量2 1 5 に蓄積された信号のレベルとの差分を出力線2 1 8 に出力するアンプである。スイッチ2 1 3 、2 1 6 は、水平信号選択パルスH i によって駆動されて、それぞれ容量2 1 2 、2 1 5 の電位を差動アンプ2 1 7 に伝達する。出力線2 1 8 には、P D 2 0 2 からF D 2 0 4 に転送される電荷に対応する電位とリセット状態のF D 2 0 4 の電位との差分を増幅した値が画素信号として出力される。 40

【 0 0 1 2 】

ここで、差動アンプ2 1 7 の入力端子に接続された共通出力線2 1 7 a 、2 1 7 b には、典型的には、水平信号選択パルスH 1 ~ H ( i - 1 ) 、H ( i + 1 ) ~ H n で駆動される他の列のスイッチ2 1 3 、2 1 6 も接続される(nは、画素アレイ1 0 1 の列数)。

【 0 0 1 3 】

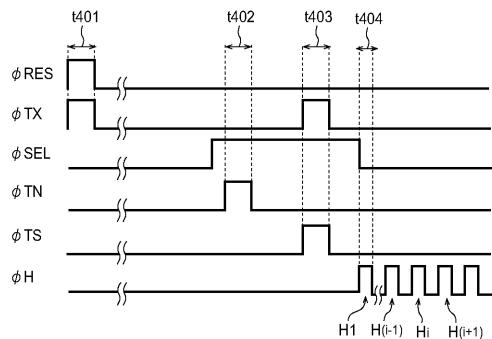

図4は、図2に示す撮像素子の駆動パターンを示している。期間t 4 0 1 においてパルスR E S とパルスT X が印加されてリセットスイッチ2 0 7 と転送スイッチ2 0 3 がオンし、P D 2 0 2 とF D 2 0 4 の電位が初期電位にリセットされて、そのリセットの終了とともに新たな露光期間が開始される。その後、パルスS E L が印加されて選択スイ 50

ツチ 206 をオンすることによって読み出し行が選択される。期間  $t_{402}$  においてパルス  $T_N$  が印加されてスイッチ 211 がオンすることによって、FD204 のリセット電位に応じた値がリセットレベル蓄積容量 212 に書き込まれる。

【0014】

期間  $t_{403}$  においてパルス  $T_X$  とパルス  $T_S$  が印加される。これによってスイッチ 203、214 がオンして PD202 に蓄積されていた電荷が FD204 に転送されるとともに FD204 に転送された電荷に応じた電位が信号レベル蓄積容量 215 に書き込まれる。期間  $t_{404}$  においてパルス  $H$  が印加されると、スイッチ 213、スイッチ 216 がオンし、信号レベル蓄積容量 215 に格納された信号とリセットレベル蓄積容量 212 に格納された信号との差分がアンプ 217 によって増幅されて出力線 218 に出力される。 10

【0015】

以上のような撮像素子によれば、信号レベルとリセットレベルとの差分を増幅して出力することによって、撮像素子の固定パターンノイズを低減し、また画素のリセットスイッチのばらつきによるノイズを低減することができる。

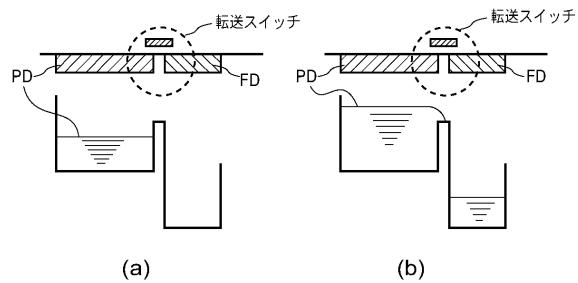

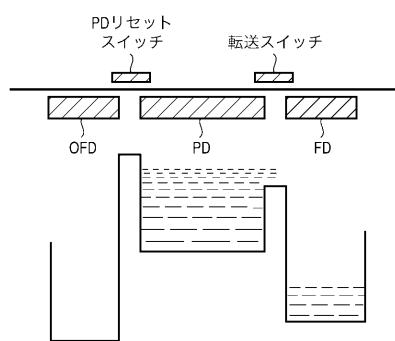

【0016】

しかしながら、このような撮像素子では、PD に溜まった電荷が該 PD の寄生容量を超えたときに、ポテンシャルの障壁の低いところに漏れこんでしまうという問題がある。このような問題について図 7 を参照して説明する。図 7 において、上部には PD、FD 及び転送スイッチの位置関係が示され、下部にはこれらのポテンシャル状態が示されている。理想的には、図 7 (a) に示すように、PD で発生した電荷の全てが PD の寄生容量に蓄積される。しかしながら、PD で発生した電荷が多いときには、図 7 (b) に示すように、ポテンシャル障壁の低い転送スイッチの下を通過し、FD に漏れ込んでしまう。このような構造の画素をもつ撮像素子において、前述のような信号レベルとリセットレベルとの差分を演算すると、図 7 (a) のように理想的な場合には、出力信号は、PD で発生した電荷に比例する。しかしながら、図 7 (b) のように PD から FD に電荷が漏れこんだ場合には、出力信号は、PD で発生し FD に漏れ込んだ電荷の分だけ小さくなってしまう。 20

【0017】

特許文献 4 には、PD から FD へ電荷が漏れ込んだ後は、出力信号を飽和信号に置き換えることによって、出力信号が小さくなることを防止することが記載されている。また、特許文献 5 には、この現象を利用し、FD に漏れこんだ電荷分の信号を PD で発生した電荷と足し合わせることで、ダイナミックレンジを拡大することが記載されている。 30

【特許文献 1】特開平 11-313257 号公報

【特許文献 2】特開 2000-59688 号公報

【特許文献 3】特開 2001-177775 号公報

【特許文献 4】特開 2000-287131 号公報

【特許文献 5】特開 2003-87665 号公報

【発明の開示】

【発明が解決しようとする課題】

【0018】

しかしながら、特許文献 4 に記載された方法では、PD から FD に電荷が漏れ込んだ画素については、それから読み出された画素信号が全て同一画素値として扱われる。したがって、高輝度側の階調性が失われ、結果としてダイナミックレンジが縮小することになる。また、特許文献 5 に記載された方法では、PD で発生した電荷が FD のみに漏れ込む撮像素子では、入射光量に比例した出力が得られるが、そうでない撮像素子では、FD に漏れ込んだ電荷による出力と、PD が飽和していない場合 (PD から電荷が溢れない場合) における出力との間に感度差が生じる。そのため、それらを足し合わせた出力は、PD が飽和した段階でニーポイントを持ち、PD が飽和するレベルや、PD から FD への電荷の漏れこみ量に画素ごとの差異があった場合には、画素間でニーポイントがばらついてしまう。 40 50

## 【0019】

本発明は、上記の課題認識を基礎としてなされたものであり、画質の低下を抑制しつつダイナミックレンジを拡大することを目的とし、より具体的な例を挙げれば、例えば、光電変換部から電荷電圧変換部への電荷の漏れ込みによるダイナミックレンジの縮小問題、及び／又は、画素間におけるニーポイントのばらつき問題を解消或いは緩和することを目的とする。

## 【課題を解決するための手段】

## 【0020】

本発明の撮像装置は、光電変換部と、前記光電変換部で発生した電荷を一時的に蓄積する半導体領域と、前記光電変換部から前記半導体領域に前記電荷を転送する転送スイッチと、前記半導体領域をリセットするリセットスイッチとを備えた少なくとも1つの画素と、前記半導体領域から信号を読み出す信号読み出し部と、前記光電変換部の露光期間において、前記転送スイッチがオフの状態で前記光電変換部から前記半導体領域に漏れこんだ電荷量が所定基準量よりも多い場合に、前記転送スイッチと前記リセットスイッチをそれぞれオンすることで前記光電変換部と前記半導体領域をリセットするように制御し、前記光電変換部の露光期間において前記光電変換部から前記半導体領域に漏れ込む電荷量が前記所定基準量よりも少ない場合に、前記転送スイッチをオンしないで前記リセットスイッチをオンすることで前記光電変換部をリセットしないで前記半導体領域をリセットするように制御する制御部とを有する。

10

## 【発明の効果】

20

## 【0039】

本発明によれば、撮像素子によって撮像される画像の画質の低下を抑制しつつダイナミックレンジを拡大することができる。より具体的な例を挙げれば、本発明によれば、例えば、光電変換部から電荷電圧変換部への電荷の漏れ込みによるダイナミックの縮小問題、及び／又は、画素間におけるニーポイントのばらつき問題を解消或いは緩和することができる。

## 【発明を実施するための最良の形態】

## 【0040】

以下、添付図面を参照しながら本発明の好適な第1実施形態を説明する。

## 【0041】

30

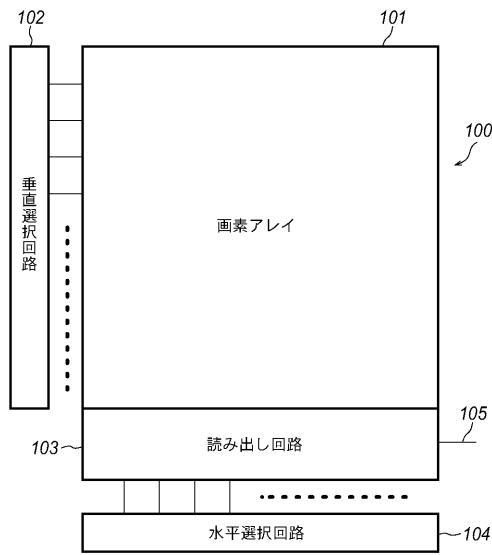

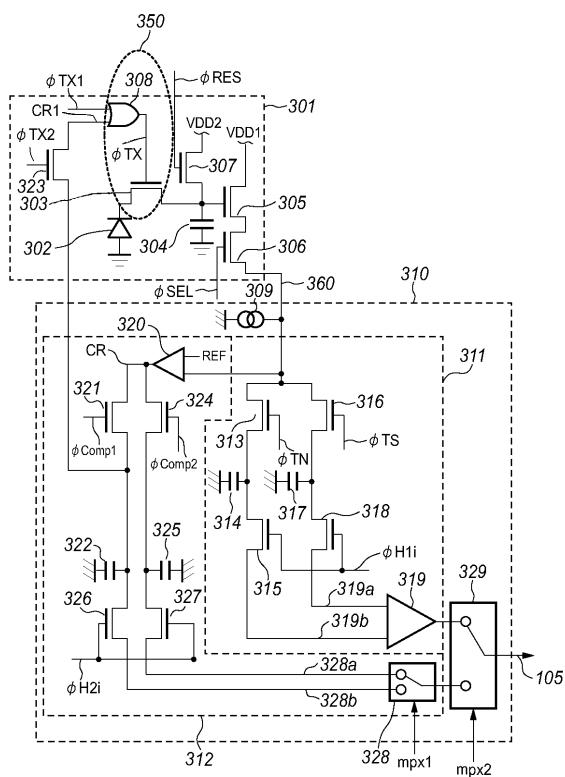

図1は、本発明の好適な実施形態の撮像素子100の全体構成を概略的に示す図、図3は、図1に示す撮像素子100における1画素の構成及びその画素から信号を読み出す回路の構成を示す図である。撮像素子100は、画素アレイ101と、画素アレイ101における行を選択する垂直選択回路102、画素アレイ101における列を選択する水平選択回路104、画素アレイ101中の画素のうち垂直選択回路102及び水平選択回路104によって選択される画素の信号を読み出す読み出し回路103を含んで構成される。なお、撮像素子100は、図示された構成要素以外にも、例えば、垂直選択回路102、水平選択回路104、信号読み出し部103等にタイミングを提供するタイミングジェネレータ或いは制御回路等を備えうる。

## 【0042】

40

典型的には、垂直選択回路102は、画素アレイ101の複数の行を順に選択し、水平選択回路104は、垂直選択回路102によって選択されている行を構成する複数の画素を順に選択するように画素アレイの複数の列を順に選択する。

## 【0043】

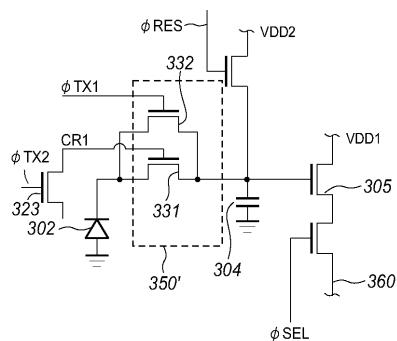

画素アレイ101は、2次元の画像を提供するために、複数の画素を2次元アレイ状に配列して構成される。図3に示すように、各画素301は、フォトダイオード(PD)302、転送スイッチ303、フローティングディフュージョン部(FD；半導体領域)304、リセットスイッチ307、増幅MOSアンプ305、選択スイッチ306、転送スイッチ制御部308及び比較結果転送スイッチ323を含んで構成される。

## 【0044】

50

P D 3 0 2 は、光学系を通して入射する光を光電変換する光電変換部として機能する。P D 3 0 2 のアノードは接地ラインに接続され、カソードは転送スイッチ 3 0 3 のソースに接続される。転送スイッチ 3 0 3 は、そのゲート端子に入力される転送パルス T X によって駆動され、P D 2 0 2 で発生した電荷を F D 2 0 4 に転送する。F D (半導体領域) 2 0 4 は、電荷を一時的に蓄積するとともに蓄積した電荷を電圧信号に変換する電荷電圧変換部として機能する。

【 0 0 4 5 】

転送スイッチ制御部 3 0 8 は、露光期間を制御する垂直転送パルス T X 1 と後述の第 1 比較結果信号 (リセット制御信号) C R 1 との論理和を演算して転送パルス T X を発生する。転送スイッチ 3 0 3 及び転送スイッチ制御部 3 0 8 は、垂直転送パルス T X 1 及び第 1 比較結果信号 C R 1 の少なくとも一方がアクティブレベル (ここでは、ハイレベル) になった時に、P D 3 0 2 で発生した電荷を F D 3 0 4 に転送する転送制御部 3 5 0 を構成する。

【 0 0 4 6 】

図 8 は、転送制御部の他の構成例を示す図である。図 8 に示す転送制御部 3 5 0 ' は、P D 3 0 2 のカソードと F D 3 0 4 との間に並列接続された転送スイッチ 3 3 1、3 3 2 で構成され、転送スイッチ 3 3 1 のゲートには第 1 比較結果信号 C R 1 が接続され、転送スイッチ 3 3 2 のゲートには露光期間を制御する垂直転送パルス T X 1 が接続されている。したがって、図 8 に示す転送制御部 3 5 0 ' は、垂直転送パルス T X 1 及び第 1 比較結果信号 C R 1 の少なくとも一方がアクティブレベル (ここでは、ハイレベル) になった時に、P D 2 0 2 で発生した電荷を F D 2 0 4 に転送する転送制御部 3 5 0 を構成する。

【 0 0 4 7 】

増幅M O S アンプ 3 0 5 は、ソースフォロアとして機能し、そのゲートが F D 3 0 4 に接続されていて、F D 3 0 4 で電荷電圧変換された信号が入力される。また、増幅M O S アンプ 3 0 5 は、そのドレインが第 1 電位を提供する第 1 電源線 V D D 1 に接続され、そのソースが選択スイッチ 3 0 6 に接続されている。選択スイッチ 3 0 6 は、そのゲートに対して垂直選択回路 1 0 2 から提供される垂直選択パルス S E L によって駆動され、そのドレインが増幅M O S アンプ 3 0 5 に接続され、そのソースが垂直信号線 3 6 0 に接続されている。垂直選択パルス S E L がアクティブレベル (ここでは、ハイレベル) になると、画素アレイ 1 0 1 の該当する行に属する画素の選択スイッチ 3 0 6 が導通状態になり、増幅M O S アンプ 3 0 5 のソースが垂直信号線 3 6 0 に接続される。

【 0 0 4 8 】

スイッチ 3 2 3 は、第 1 比較結果メモリ 3 2 2 に格納された比較結果を第 1 比較結果信号 C R 1 として転送制御部 3 5 0 (図 8 に示す例では、転送制御部 3 5 0 ') に伝達するためのスイッチで、垂直選択回路 1 0 2 から提供される比較結果転送パルス T X 2 により駆動される。

【 0 0 4 9 】

リセットスイッチ 3 0 7 は、そのドレインが第 2 電位 (リセット電位) を提供する第 2 電源線 V D D 2 に接続され、そのソースが F D 3 0 4 に接続されていて、そのゲートに入力されるリセットパルス R E S によって駆動されて F D 3 0 4 に蓄積されている電荷を除去する。

【 0 0 5 0 】

F D 3 0 4 及び増幅M O S アンプ 3 0 5 の他、垂直信号線 3 6 0 に定電流を供給する定電流源 3 0 9 によってフローティングディフュージョンアンプが構成される。選択スイッチ 3 0 6 で選択された行を構成する各画素において、F D 3 0 4 に転送される電荷が F D 3 0 4 で電圧信号に変換されて、フローティングディフュージョンアンプを通じて対応する読み出し部 3 1 0 に出力される。

【 0 0 5 1 】

読み出し部 3 1 0 は、信号読み出し部 3 1 1 、飽和検出部 3 1 2 及び信号選択回路 3 2

10

20

30

40

50

9を含んで構成されうる。

【0052】

まず、信号読み出し部311について説明する。スイッチ313は、FD304のリセット電位をリセットレベル信号として読み出すためのスイッチであり、リセットレベル読み出しパルス TNにより駆動される。リセットレベル蓄積容量314には、画素信号の読み出しの直前にリセットレベル信号(FD304のリセットレベルに応じた電位の信号)が蓄積される。

【0053】

スイッチ316は、PD302で発生した電荷信号に応じた電圧信号を読み出すためのスイッチであり、信号読み出しパルス TSにより駆動される。信号レベル蓄積容量317には、画素信号の読み出し時に、その画素信号(PD302からFD304に転送された電荷に応じた電位の信号)が蓄積される。

10

【0054】

差動アンプ319は、リセットレベル蓄積容量314に蓄積された信号のレベルと信号レベル蓄積容量317に蓄積された信号のレベルとの差分を出力線105に出力するアンプである。スイッチ315、318は、水平選択回路104から提供される水平信号選択パルス H1iによって駆動されて、それぞれ容量314、317の電位を差動アンプ319に伝達する。出力線105には、PD302からFD304に転送される電荷に対応する電位とリセット状態のFD304の電位との差分を増幅した値が画素信号として出力される。

20

【0055】

ここで、差動アンプ319の入力端子にそれぞれ接続された共通出力線319a、319bには、水平信号選択パルス H11～H1(i-1)、H1(i+1)～H1nで駆動される他の列のスイッチ315、318も接続される(nは、画素アレイ101の列数)。水平信号選択パルス H1i(i=1～n)は、水平選択回路104によって、例えば、i～nの順に印加される。

【0056】

次に、飽和検出部312について説明する。比較回路320は、増幅MOSアンプ305及び選択スイッチ306を通して垂直信号線360上に読み出される電荷蓄積期間(露光期間)におけるFD304の電位と所定の基準電位REFとを比較して、その比較結果を比較結果信号CRとして出力する。

30

【0057】

ここで、比較結果信号CRは、比較結果に応じて、第1論理レベル又は第2論理レベルを有することになる。具体的には、比較回路320は、増幅MOSアンプ305及び選択スイッチ306を通して垂直信号線360上に読み出されるFD304の電位が基準電位REFよりも低い場合、すなわち、PD302からFD304に対して電荷が基準量を超えて漏れ込んだ場合は、第1論理レベルVDDCOMP(ここでは、ハイレベル)を出力する。また、比較回路320は、増幅MOSアンプ305及び選択スイッチ306を通して垂直信号線360上に読み出されるFD304の電位が基準電位REFよりも高い場合は、すなわち、PD302からFD304に対して電荷が漏れ込んでいない場合又は漏れ込みが基準量に満たない場合は、第2論理レベルGNDCOMP(ここでは、ローレベル)を出力する。

40

【0058】

撮像素子100は、基準電位REFを任意に設定可能に構成されることが好ましい。例えば、基準電位REFを撮像素子100の外部から印加するように撮像素子100を構成にすることによって、基準電位REFを任意の電位に設定することができる。或いは、撮像素子100に変換器を備えて、撮像素子100の外部から提供されるデータ或いはコードにしたがって該変換器によって基準電位REFを発生してもよい。

【0059】

スイッチ321、324は、比較回路320による比較結果(VDDCOMP又はGNDCOMP)

50

D C O M P ) をそれぞれ第 1 比較結果メモリ 3 2 2 、第 2 比較結果メモリ 3 2 5 に伝達するためのスイッチである。スイッチ 3 2 1 、 3 2 4 は、それぞれ第 1 格納パルス C o m p 1 、第 2 格納パルス C o m p 2 によって駆動される。

#### 【 0 0 6 0 】

撮像素子 1 0 0 は、比較結果転送パルス T X 2 のタイミングを任意に設定可能に構成されることが好ましい。スイッチ 3 2 6 、 3 2 7 は、第 1 比較結果メモリ 3 2 2 、第 2 比較結果メモリ 3 2 5 に格納された比較結果を飽和検出信号選択回路 3 2 8 に伝達するためのスイッチであり、水平比較信号選択パルス H 2 i によって駆動される。飽和検出信号選択回路 3 2 8 は、飽和検出信号選択信号 m p x 1 が第 1 論理レベル ( ここでは、ハイレベル ) のときは第 1 比較メモリ 3 2 2 を選択し、第 2 論理レベル ( ここでは、ローレベル ) のときは第 2 比較メモリ 3 2 5 を選択する。 10

#### 【 0 0 6 1 】

ここで、飽和検出信号選択回路 3 2 8 の入力端子にそれぞれ接続された共通出力線 3 2 8 a 、 3 2 8 b には、水平比較信号選択パルス H 1 1 ~ H 1 ( i - 1 ) 、 H 1 ( i + 1 ) ~ H 1 n で駆動される他の列のスイッチ 3 2 6 、 3 2 7 も接続される ( n は、画素アレイ 1 0 1 の列数 ) 。水平比較信号選択パルス H 2 i ( i = 1 ~ n ) は、水平選択回路 1 0 4 によって、例えば、 i ~ n の順に印加される。

#### 【 0 0 6 2 】

次に信号選択回路 3 2 9 について説明する。信号選択回路 3 2 9 は、選択信号 m p x 2 にしたがって信号読み出し部 3 1 1 の出力信号 ( 画素信号 ) 及び飽和検出部 3 1 2 の出力信号 ( 比較結果 ) のいずれか一方を選択して出力線 1 0 5 に出力する。具体的には、信号選択回路 3 2 9 は、選択信号 m p x 2 が第 1 論理レベル ( ここでは、ハイレベル ) のときは信号読み出し部 3 1 1 の出力信号 ( 画素信号 ) を選択し、第 2 論理レベル ( ここでは、ローレベル ) のときは飽和検出部 3 1 2 の出力信号 ( 比較結果 ) を選択する。 20

#### 【 0 0 6 3 】

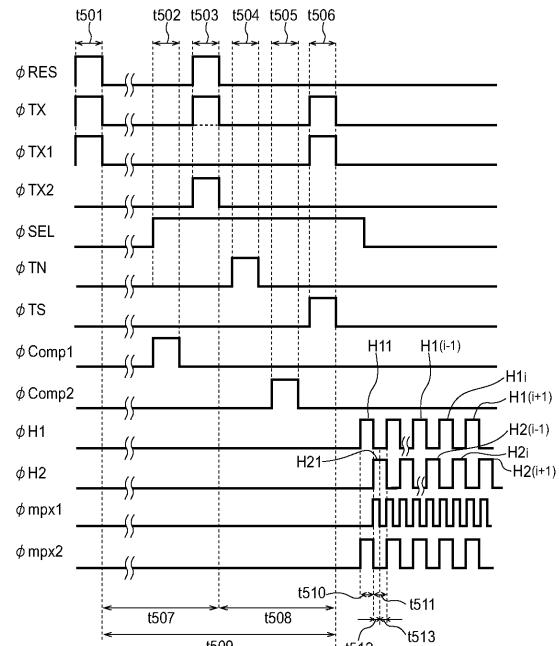

図 5 は、図 1 及び図 3 に示す撮像素子 1 0 0 の駆動パターンを示している。以下、図 1 、図 3 及び図 5 を参照しながら撮像素子 1 0 0 の動作を説明する。

#### 【 0 0 6 4 】

期間 t 5 0 1 においてタイミングジェネレータ ( 或いは制御回路、以下同様 ) からパルス R E S とパルス T X 1 が印加されると、パルス T X が生成され、パルス R E S によってリセットスイッチ 3 0 7 がオンされるとともにパルス T X 1 によって転送スイッチ 3 0 3 がオンされる。これによって、 P D 3 0 2 と F D 3 0 4 の電位が初期電位にリセットされて、そのリセットの終了とともに新たな露光期間 ( 蓄積期間 ) t 5 0 9 が開始される。なお、露光期間 t 5 0 9 は、リセットの終了時から垂直転送パルス T X 1 の終了時までである。 30

#### 【 0 0 6 5 】

その後、タイミングジェネレータから画素アレイ 1 0 1 の該読み出し対象行についてのパルス S E L が印加されて選択スイッチ 3 0 6 がオンすることによって読み出し行が選択される。

#### 【 0 0 6 6 】

露光期間内の期間 t 5 0 2 において、タイミングジェネレータからパルス C o m p 1 が印加されてスイッチ 3 2 1 がオンする。これによって、 F D 3 0 4 に存在する電荷に対応する電位が増幅 M O S アンプ 3 0 5 によって垂直信号線 3 6 0 上に増幅された電位と基準電位 R E F とが比較器 3 2 0 によって比較されて、その比較結果が比較結果信号 C R として出力されて、第 1 比較結果メモリ 3 2 2 に書き込まれる。図 7 の ( b ) に示すように P D 3 0 2 から F D 3 0 4 への漏れ込みある場合は、第 1 比較結果メモリ 3 2 2 には、第 1 論理レベル V D D C O M P ( ここでは、ハイレベル ) が書き込まれる。一方、 P D 3 0 2 から F D 3 0 4 への漏れ込みがない場合は、第 1 比較結果メモリ 3 2 2 には、第 2 論理レベル G N D C O M P ( ここでは、ローレベル ) が書き込まれる。 40

#### 【 0 0 6 7 】

露光期間内の期間  $t_{503}$ において、タイミングジェネレータからリセットパルス  $R_{ES}$ と比較結果転送パルス  $TX_2$ が印加される。ここで、第1比較結果メモリ  $322$ に第1論理レベル  $VDDCOMP$ が書き込まれている場合は、転送パルス  $TX$ が発生して、 $PD302$ と  $FD304$ がリセットされる。一方、第1比較結果メモリ  $322$ に第2論理レベル  $GNDCOMP$ が書き込まれている場合は、転送パルス  $TX$ が発生しないので、リセットパルス  $R_{ES}$ によって  $FD304$ だけがリセットされる。

#### 【0068】

露光期間内の期間  $t_{504}$ において、タイミングジェネレータからパルス  $TN$ が印加されてスイッチ  $313$ をオンすることによって、 $FD304$ のリセット電位に応じた値がリセットレベル蓄積容量  $314$ に書き込まれる。

10

#### 【0069】

露光期間内の期間  $t_{505}$ において、タイミングジェネレータからパルス  $Comp_2$ が印加されられてスイッチ  $324$ がオンする。これによって、 $PD302$ から  $FD304$ に漏れ込んだ電荷に対応する電位（漏れ込みがない場合には、リセットレベル）が増幅  $MOS$ アンプ  $305$ によって垂直信号線  $360$ 上に増幅される。そして、垂直信号線  $360$ 上の電位と基準電位  $REF$ とが比較器  $320$ によって比較されて、その比較結果が比較結果信号  $CR$ として出力されて、第2比較結果メモリ  $325$ に書き込まれる。

#### 【0070】

期間  $t_{506}$ において、パルスジェネレータから垂直転送パルス  $TX_1$ と信号読み出しパルス  $TS$ が印加される。垂直転送パルス  $TX_1$ の終了は、露光期間の終了を意味する。垂直転送パルス  $TX_1$ の印加によって転送パルス  $TX$ が生成され、これによってスイッチ  $303$ がオンし、 $PD302$ に蓄積された電荷が  $FD304$ に転送される。また、信号読み出しパルス  $TS$ の印加によってスイッチ  $316$ がオンし、これによって  $FD304$ に転送された電荷に応じた電位が信号レベル蓄積容量  $317$ に格納される。

20

#### 【0071】

その後、画素アレイ  $101$ の各列（第1列～第  $n$ 列）について、（a）信号レベル蓄積容量  $317$ に蓄積された信号とリセットレベル蓄積容量  $314$ に格納された信号との差分（つまり、画素信号）、（b）第1比較結果メモリ  $322$ に格納された信号、（c）第2比較結果メモリ  $325$ に格納された信号が出力される。ここで、（b）及び（c）の信号の出力は、（a）の画像信号の出力の合間（第  $i$ 列の画素信号の出力と第  $(i+1)$ 列の画素信号の出力との合間）、すなわち、共通出力線  $319a$ 、 $319b$ を不図示のリセット手段によってリセットする期間においてなされる。

30

#### 【0072】

（a）、（b）、（c）の信号の出力シーケンスについて、画素アレイ  $101$ の第1列を代表例として説明する。期間  $t_{510}$ において、タイミングジェネレータによって水平信号選択パルス  $H11$ （ $H1i$ ；  $i = 1$ ）が印加されるとともに選択信号  $mp \times 2$ が第1論理レベル（ここでは、ハイレベル）にされると（水平比較信号選択パルス  $H2i$ （ $H2i$ ；  $i = 1 \sim n$ の全て）はインアクティブ状態）、スイッチ  $315$ 、 $318$ がオンし、信号レベル蓄積容量  $317$ とリセットレベル蓄積容量  $314$ の差分がアンプ  $319$ によって増幅して出力線  $105$ 上に出力される。

40

#### 【0073】

期間  $t_{511}$ において、タイミングジェネレータによって水平比較信号選択パルス  $H21$ （ $H2i$ ；  $i = 1$ ）が印加されるとともに選択信号  $mp \times 2$ が第2論理レベル（ここでは、ローレベル）にされると（水平信号選択パルス  $H1i$ （ $H1i$ ；  $i = 1 \sim n$ の全て）はインアクティブ状態）、選択回路  $329$ は、飽和検出部  $312$ の出力を出力線  $105$ 上に出力する。ここで、期間  $t_{511}$ は、飽和検出信号選択信号  $mp \times 1$ が第1論理レベル（ここでは、ハイレベル）となる期間  $t_{512}$ と、第2論理レベル（ここでは、ローレベル）になる期間  $t_{513}$ とを含む。期間  $t_{512}$ において、第1比較結果メモリ  $322$ に格納された信号が出力線  $105$ 上に出力され、期間  $t_{514}$ において、第2比較結果メモリ  $325$ に格納された信号が出力線  $105$ 上に出力される。

50

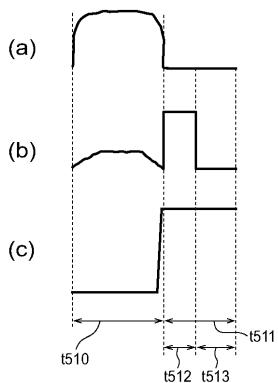

## 【0074】

図6は、出力線105上に出力される信号の3つのタイプを例示的に示している。図6(a)は、第1比較結果メモリ322、第2比較結果メモリ325の双方に第2論理レベルGNDCOMPが書き込まれている場合で、PD302からFD304への電荷の漏れ込みが一度もなかった場合の例である。図6(b)は、第1比較結果メモリ322に第1論理レベルVDDCOMPが書き込まれ、第2比較結果メモリ325に第2論理レベルGNDCOMPが書き込まれている場合である。この場合は、期間t507においてPD302からFD304への電荷の漏れ込みがあり、そのために期間t507においてPD302に蓄積された電荷とFD304に漏れ込んだ電荷がリセットされる。のために、PD302における実質的な露光期間或いは蓄積時間(出力線105から出力される画素信号に反映される蓄積時間)は、期間t508になる。図6(c)は、第1比較結果メモリ322、第2比較結果メモリ325の双方に第1論理レベルVDDCOMPが格納されている場合であり、期間t507、期間t508の双方において、PD302からFD304への電荷の漏れ込みがあった場合である。

## 【0075】

画素アレイ101の一部の画素においてPD302からFD304への基準量を超える電荷の漏れがあった場合において、出力線105からの信号は、そのままでは画像信号として有効ではない。なぜなら、第1比較結果メモリ322に格納された値に反映されるように、PD302における実質的な露光期間或いは蓄積時間が画素ごとに異なっているからである。そのため、撮像素子100の後段に配置される信号処理回路(例えば、後述の信号処理回路8(図9))において、画像信号の各画素値を適正な値に補正する必要がある。

## 【0076】

この補正方法を説明すると、図6(a)に示す場合は、出力線105上に出力される画像(撮像装置100から出力される画像信号)信号をそのまま画像信号として使用する。図6(b)の場合は、画像信号にゲインを掛ける。ゲインは、PD302の露光期間(t509)に対する実質的な露光期間或いは蓄積時間(t508)の不足分を補うように決定すればよい。すなわち、出力線105上に出力される画像信号に対して、ゲインとして(蓄積時間t509)/(蓄積時間t508)を掛ければよい。図6(c)の場合は、飽和した信号を画像信号とする。図6(c)の信号は、FD304への漏れこみ電荷分の信号がPD302に蓄積された電荷に相当する信号から引き算されたもので、信頼性に乏しいためである。

## 【0077】

以上のように、本発明の好適な実施形態によれば、撮像装置における各画素の実質的な蓄積時間をPDからFDへの電荷の漏れ込みに応じて変化させることにより、ダイナミックレンジを拡大することができる。

## 【0078】

上記の実施形態では、露光期間におけるPDのリセットを一度のみなされるが、第1比較結果メモリに相当するメモリを複数設けることで、露光期間におけるリセットの回数を複数回にすることができ、この場合、更にダイナミックレンジを拡大することができる。

## 【0079】

また、上記の実施形態では、第1、第2比較結果メモリの値をそのまま出力するが、第1、第2比較結果メモリの一方の値を反転させて出力することにより、出力線上の信号変動を低減することができる場合がある。

## 【0080】

また、上記の実施形態では、画素の飽和検出出力を信号出力のリセット期間を利用して出力するが、このような構成をとることで、飽和検出信号のように、画像信号に付随する情報を出力ピンを新たに設けることなく出力することができる。また、出力ピンの増加が可能な場合には、飽和検出信号を別のピンから出力することも可能である。

## 【0081】

10

20

30

40

50

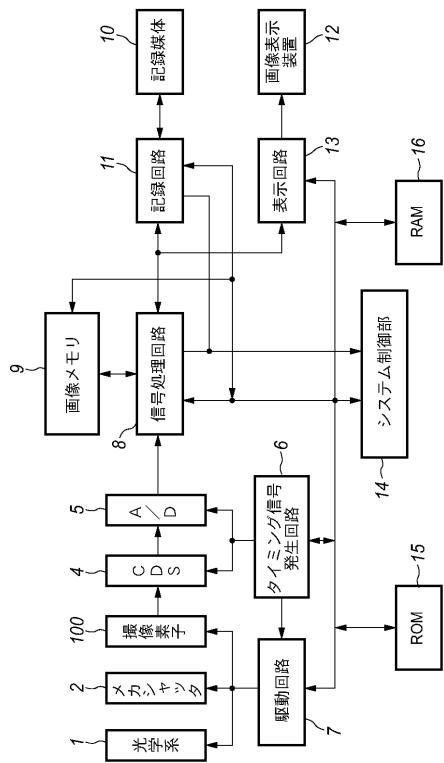

次に、上記の撮像素子 100 の応用例として、これを組み込んだ撮像装置について説明する。図9は、本発明の好適な実施形態の撮像装置一実施形態を示す図である。

【0082】

上記の実施形態の撮像素子 100 には、絞り機構及びレンズを有する光学系 1 を通して光線が入射する。光学系 1 と撮像素子 100 との間、又は光学系 1 内にメカニカルシャッタ 2 が配置されうる。光学系 1 、メカニカルシャッタ 2 及び撮像素子 100 は、駆動回路 7 によって駆動される。CDS回路 4 は、撮像素子 100 の出力信号に対して CDS (Correlated Double Sampling) 処理を施し、A/D変換器 5 は、CDS回路 4 で処理されたアナログ信号をデジタル信号に変換する。タイミング信号発生回路 6 は、撮像素子 100 、CDS回路 4 及び A/D変換器 5 に提供するタイミング信号を発生する。信号処理回路 8 は、A/D変換された画像データに対して前述の信号処理の他、種々の信号処理を施す。画像メモリ 9 は、信号処理された画像データを記憶する。

【0083】

記録回路 11 は、信号処理された画像データを記録媒体 10 に記録する。表示回路 13 は、信号処理された画像データを画像表示装置 12 に提供し画像を表示させる。

【0084】

不揮発性メモリ等の ROM 15 は、制御プログラム、プログラムを実行する際に使用されるパラメータやテーブル等の制御データ、及び、キズアドレス等の補正データを記憶する。RAM 16 には、ROM 15 に記憶されたプログラム、制御データ及び補正データが転送され、撮像装置全体を制御するシステム制御部 14 によって使用される。

【0085】

撮影動作に先立ち、撮像装置の電源投入時等のシステム制御部 14 の動作開始時において、ROM 15 から必要なプログラム、制御データ及び補正データが RAM 16 に転送される。光学系 1 は、システム制御部 14 から送られてくる制御信号に応じて、絞りとレンズを駆動して、適切な明るさに設定された被写体像を撮像素子 3 上に結像させる。次に、メカニカルシャッタ 2 は、システム制御部 14 から送られてくる制御信号に応じて、撮像素子 3 の動作に合わせて撮像素子 1003 を遮光するように駆動される。撮像素子 100 は、システム制御部 14 により制御されるタイミング信号発生回路 1006 が発生する動作パルスを基にして駆動回路 7 で生成される駆動パルスで駆動され、被写体像を光電変換により電気信号に変換してアナログ画像信号として出力する。撮像素子 100 から出力されたアナログの画像信号は、システム制御部 14 により制御されるタイミング信号発生回路 6 が発生する動作パルスにより、CDS回路 4 でクロック同期性ノイズが除去され、A/D変換器 5 でデジタル画像信号に変換される。次に、システム制御部 14 により制御される信号処理回路 8 において、デジタル画像信号に対して、色変換、ホワイトバランス、ガンマ補正等の画像処理、解像度変換処理、画像圧縮処理等がなされる。画像メモリ 9 は、信号処理中のデジタル画像信号を一時的に記憶したり、信号処理されたデジタル画像信号である画像データを記憶したりするために用いられる。信号処理回路 8 で信号処理された画像データや画像メモリ 9 に記憶されている画像データは、記録回路 11 において画像記録媒体 10 に適したデータ（例えば階層構造を持つファイルシステムデータ）に変換されて記録媒体 10 に記録したり、信号処理回路 8 で解像度変換処理を実施された後、表示回路 13 において画像表示装置 11 に適した信号（例えばNTSC方式のアナログ信号等）に変換されて画像表示装置 11 に表示されたりする。

【0086】

ここで、信号処理回路 8 においては、信号処理をせずにデジタル画像信号をそのまま画像データとして画像メモリ 9 や記録回路 11 に出力してもよい。また、信号処理回路 8 は、システム制御部 14 から要求があった場合に、信号処理の過程で生じたデジタル画像信号や画像データの情報、例えば、画像の空間周波数、指定領域の平均値、圧縮画像のデータ量等の情報、あるいは、それらから抽出された情報をシステム制御部 14 に出力する。更に、記録回路 11 は、システム制御部 14 から要求があった場合に、画像記録媒体 10 の種類や空き容量等の情報をシステム制御部 14 に出力する。

10

20

30

40

50

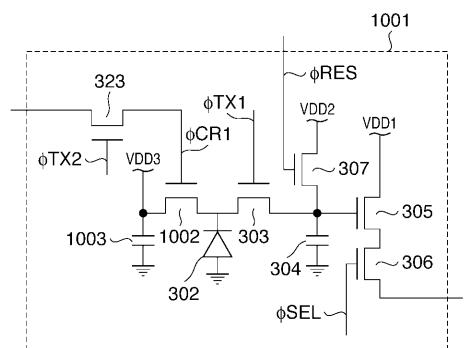

## 【0087】

以下、添付図面を参照しながら本発明の好適な第2実施形態を説明する。この第2実施形態は、図3に示す画素301を図10に示す構成で置き換えたものである。図10に示すように、各画素1001は、フォトダイオード(PD)302、転送スイッチ303、フローティングディフュージョン部(FD)304、リセットスイッチ307、増幅MOSアンプ305、選択スイッチ306、比較結果転送スイッチ323、オーバーフロードレンイン領域(以下OFD)1003及びPDリセットスイッチ1002を含んで構成される。

## 【0088】

転送スイッチ303は、PD302のカソードとFD304との間に接続され、ゲートには露光期間を制御する垂直転送パルスTX1が接続されている。PDリセットスイッチ1002はPD302のカソードとOFD1003との間に接続され、ゲートには第1比較結果信号CR1が接続されている。OFD1003は第3電源線VDD3に接続されている。従って、垂直転送パルスTX1がアクティブ(ここでは、ハイレベル)になった時に、PD202で発生した電荷をFD204に転送し、比較結果信号CR1がアクティブ(ここでは、ハイレベル)になった時には、PD202で発生した電荷をOFD1003に排出する。

## 【0089】

図11において、上部にはPD、FD、OFD、PDリセットスイッチ及び転送スイッチの位置関係が示され、下部にはこれらのポテンシャル状態が示されている。垂直転送パルスTX1とCR1がともにローレベルになっているときに、PDで発生した電荷がOFDの側に漏れこまず、FDの側にもれこむよう、ポテンシャル設計がされている。画素構成以外の構成例は実施形態1と同様である。また、駆動シーケンスにおいても実施形態1と同様であるが、TX2とRESはTX2は必ずしも同一の時間帯を持つ必要はない。

## 【図面の簡単な説明】

## 【0090】

【図1】本発明の好適な実施形態の撮像素子の全体構成を概略的に示す図である。

【図2】本発明の課題を例示的に説明するために撮像素子における1画素の構成及びその画素から信号を読み出す回路の構成を示す図である。

【図3】図1に示す撮像素子における1画素の構成及びその画素から信号を読み出す回路の構成を示す図である。

【図4】図2に示す撮像素子の駆動パターンを示す図である。

【図5】図1及び図3に示す撮像素子の駆動パターンを示す図である。

【図6】出力線上に出力される信号についての3つのタイプを例示的に示す図である。

【図7】フォトダイオードとフローティングディフュージョンのポテンシャルを示す図である。

【図8】転送制御部の他の構成例を示す図である。

【図9】本発明の好適な実施形態の撮像装置或いは処理装置の一実施形態を示す図である。

【図10】図1に示す撮像素子における1画素の構成及びその画素から信号を読み出す回路の構成を示す図である。

【図11】フォトダイオード、フローティングディフュージョン及びオーバーフロードレンイン領域のポテンシャルを示す図である。

## 【符号の説明】

## 【0091】

105 出力線

301 画素

302 フォトダイオード(光電変換部)

303 転送スイッチ

10

20

30

40

50

|       |                           |    |

|-------|---------------------------|----|

| 3 0 4 | フローティングディフュージョン部(電荷電圧変換部) |    |

| 3 0 5 | 増幅MOSアンプ                  |    |

| 3 0 6 | 選択スイッチ                    |    |

| 3 0 7 | リセットスイッチ                  |    |

| 3 0 8 | 転送スイッチ制御部                 |    |

| 3 0 9 | 定電流源                      |    |

| 3 1 0 | 読み出し部                     |    |

| 3 1 1 | 信号読み出し部                   |    |

| 3 1 2 | 飽和検出部                     |    |

| 3 1 3 | リセットレベル読み出しスイッチ           | 10 |

| 3 1 4 | リセットレベル蓄積容量               |    |

| 3 1 5 | 水平選択スイッチ                  |    |

| 3 1 6 | 信号レベル読み出しスイッチ             |    |

| 3 1 7 | 信号レベル蓄積容量                 |    |

| 3 1 8 | 水平選択スイッチ                  |    |

| 3 1 9 | 差動アンプ                     |    |

| 3 2 0 | 比較回路                      |    |

| 3 2 1 | 第1比較結果転送スイッチ              |    |

| 3 2 2 | 第1比較メモリ                   |    |

| 3 2 3 | 比較結果転送スイッチ                | 20 |

| 3 2 4 | 第2比較結果転送スイッチ              |    |

| 3 2 5 | 第2比較メモリ                   |    |

| 3 2 6 | 第1比較メモリ出力スイッチ             |    |

| 3 2 7 | 第2比較メモリ出力スイッチ             |    |

| 3 2 8 | 飽和検出信号選択回路                |    |

| 3 2 9 | 信号選択回路                    |    |

| 3 3 0 | 出力線 3 5 0 転送制御部           |    |

| 3 6 0 | 垂直信号線                     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

審査官 鈴木 肇

(56)参考文献 特開平08-223490(JP, A)

特開2002-158928(JP, A)

特開2003-018471(JP, A)

特開平04-189081(JP, A)

特開2005-039741(JP, A)

特開2003-143485(JP, A)

特開平04-207589(JP, A)

特表2002-528970(JP, A)

特開2000-165755(JP, A)

特開2006-148621(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762

H04N 1/024 - 1/036