(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5253722号

(P5253722)

(45) 発行日 平成25年7月31日(2013.7.31)

(24) 登録日 平成25年4月26日(2013.4.26)

(51) Int.Cl.

F 1

|             |              |                  |      |       |

|-------------|--------------|------------------|------|-------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/36  |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20  |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G09G | 3/20  |

|             |              |                  | G09G | 3/20  |

|             |              |                  | GO2F | 1/133 |

|             |              |                  |      | 5 7 5 |

請求項の数 3 (全 17 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2006-197665 (P2006-197665) |

| (22) 出願日     | 平成18年7月20日 (2006.7.20)       |

| (65) 公開番号    | 特開2007-25701 (P2007-25701A)  |

| (43) 公開日     | 平成19年2月1日 (2007.2.1)         |

| 審査請求日        | 平成21年6月1日 (2009.6.1)         |

| (31) 優先権主張番号 | 10-2005-0065808              |

| (32) 優先日     | 平成17年7月20日 (2005.7.20)       |

| (33) 優先権主張国  | 韓国 (KR)                      |

## 前置審査

(73) 特許権者 512187343

三星ディスプレイ株式會社

Samsung Display Co., Ltd.

大韓民国京畿道龍仁市器興区三星二路95

95, Samsung 2 Ro, Gih

eung-Gu, Yongin-City

, Gyeonggi-Do, Korea

(74) 代理人 110000671

八田国際特許業務法人

李昇祐

大韓民国ソウル特別市衿川区始興2洞26

6番地 冠岳山碧山タウン519棟160

1号

最終頁に続く

(54) 【発明の名称】表示装置の駆動装置

## (57) 【特許請求の範囲】

## 【請求項 1】

各々第1及び第2副画素を含み、全体的に行列形態に配列されており、画像信号に対応する画像をそれぞれ表示する複数の画素を含む表示装置の駆動装置であって、

階調基準電圧に対するデジタルデータを記憶するメモリ、

前記デジタルデータを読み取って、読み取った前記デジタルデータと共にクロック信号及び少なくとも一つの選択信号を出力する制御部、

集積回路からなって、前記制御部からの前記デジタルデータを受信して階調基準電圧の集合を生成する階調電圧生成部、

前記階調基準電圧の集合を受信して複数の階調電圧を生成し、前記複数の階調電圧のうち、前記画像信号に該当する階調電圧を選択して前記選択された階調電圧をデータ信号として前記第1及び第2副画素に印加するデータ駆動部を含み、

前記階調電圧生成部は、

前記デジタルデータに基づいて、前記第1副画素に入力されるデータ電圧に適用されるデジタル階調基準データ及び前記第2副画素に入力されるデータ電圧に適用されるデジタル階調基準データをそれぞれ記憶する第1レジスター及び第2レジスター、

前記第1及び第2レジスターからの出力を受信して、前記第1副画素に対する前記デジタル階調基準データと前記第2副画素に対する前記デジタル階調基準データのうちの1つを選択する複数のマルチプレクサーを含む選択部、

前記マルチプレクサーの出力端子に各々連結されており、前記マルチプレクサーで選択

10

20

されたデジタルデータをアナログ電圧に変換して前記階調基準電圧を生成する複数のデジタルアナログ変換器を含む変換部を含み、

前記マルチプレクサーには、前記第1及び第2レジスターからの一対の出力が入力され

前記デジタルアナログ変換器に連結されているバッファーを含み、

前記選択信号は前記マルチプレクサーに入力される、表示装置の駆動装置。

### 【請求項2】

各々第1及び第2副画素を含み、全体的に行列形態に配列されており、画像信号に対応する画像をそれぞれ表示する複数の画素を含む表示装置の駆動装置であって、

階調基準電圧に対するデジタルデータを記憶するメモリ、

10

前記デジタルデータを読み取って、読み取った前記デジタルデータと共にクロック信号及び少なくとも一つの選択信号を出力する制御部、

集積回路からなって、前記制御部からの前記デジタルデータを受信して階調基準電圧の集合を生成する階調電圧生成部、

前記階調基準電圧の集合を受信して複数の階調電圧を生成し、前記複数の階調電圧のうち、前記画像信号に該当する階調電圧を選択して前記選択された階調電圧をデータ信号として前記第1及び第2副画素に印加するデータ駆動部を含み、

前記階調電圧生成部は、

前記デジタルデータに基づいて、前記第1副画素に入力されるデータ電圧に適用されるデジタル階調基準データ及び前記第2副画素に入力されるデータ電圧に適用されるデジタル階調基準データをそれぞれ記憶する第1レジスター及び第2レジスター、

20

前記第1及び第2レジスターからの出力を受信して、前記第1副画素に対する前記デジタル階調基準データと前記第2副画素に対する前記デジタル階調基準データのうちの1つを選択する複数のマルチプレクサーを含む選択部、

前記マルチプレクサーの出力端子に各々連結されており、前記マルチプレクサーで選択されたデジタルデータをアナログ電圧に変換して前記階調基準電圧を生成する複数のデジタルアナログ変換器を含む変換部を含み、

前記マルチプレクサーには、前記第1及び第2レジスターからの少なくとも二対以上の出力が入力され、

前記デジタルアナログ変換器に連結されている少なくとも二つのサンプル及びホールド回路を含み、

30

前記選択信号のうちの一つは前記マルチプレクサーに入力され、残りは前記サンプル及びホールド回路に入力される、表示装置の駆動装置。

### 【請求項3】

各々第1及び第2副画素を含み、全体的に行列形態に配列されており、画像信号に対応する画像をそれぞれ表示する複数の画素を含む表示装置の駆動装置であって、

階調基準電圧に対するデジタルデータを記憶するメモリ、

前記デジタルデータを読み取って、読み取った前記デジタルデータと共にクロック信号及び少なくとも一つの選択信号を出力する制御部、

集積回路からなって、前記制御部からの前記デジタルデータを受信して前記第1副画素に係る階調基準電圧の集合、または前記第2副画素に係る階調基準電圧の集合を生成する階調電圧生成部、

40

前記階調基準電圧の集合を受信して複数の階調電圧を生成し、前記複数の階調電圧のうち、前記画像信号に該当する階調電圧を選択して前記選択された階調電圧をデータ信号として前記第1及び第2副画素に印加するデータ駆動部を含み、

前記階調電圧生成部は、

複数の第1階調基準電圧を生成する抵抗列、

前記デジタルデータに基づくデジタル階調基準データを記憶するレジスター、

前記レジスターからの出力を受信する複数のデジタルアナログ変換器を含む変換部、そして

50

前記デジタルアナログ変換器及び前記抵抗列にそれぞれ連結された2つの入力端子を含み、前記デジタルアナログ変換器には、前記選択信号が入力されるスイッチング素子を通じて連結されている演算増幅器を含み、

前記演算増幅器は、前記スイッチング素子が遮断される場合、前記第1階調基準電圧を前記第1副画素に対する階調基準電圧として出力し、前記スイッチング素子が導通される場合、前記第1階調基準電圧と前記デジタルアナログ変換器の出力との和で決められる電圧を前記第2副画素に対する第2階調基準電圧として出力する、表示装置の駆動装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

10

本発明は表示装置の駆動装置に関する。

**【背景技術】**

**【0002】**

液晶表示装置は、現在最も一般的に使用されている平板表示装置のうちの一つであって、画素電極及び共通電極などの電界生成電極が形成されている二枚の表示板、及びその間に形成されている液晶層からなって、電界生成電極に電圧を印加して液晶層に電界を生成し、これによって液晶層の液晶分子の配向方向を決定して入射光の偏光を制御することによって、画像を表示する。

**【0003】**

20

一方、このような液晶表示装置は、スイッチング素子を含む画素及び表示信号線が形成されている表示板、階調基準電圧を生成する階調電圧生成部、そして階調基準電圧を利用して複数の階調電圧を生成し、生成された階調電圧のうちの画像信号に該当する階調電圧をデータ信号として表示信号線のうちのデータ線に印加するデータ駆動部を含む。

**【0004】**

また、このような液晶表示装置の中でも、電界が生成されていない状態で液晶分子の長軸を上下表示板に対して垂直に配向した垂直配向モード液晶表示装置は、コントラスト比が大きくて、基準視野角を広くすることが容易であるため、脚光を浴びている。ここで、基準視野角とは、コントラスト比が1：10の視野角、または階調間の輝度反転限界角度を意味する。

**【0005】**

30

垂直配向モード液晶表示装置で、広視野角を実現するための手段としては、電界生成電極に切開部を形成する方法や、電界生成電極上に突起を形成する方法などがある。切開部及び突起によって液晶分子が傾く方向を決定することができるので、これらを使用して液晶分子の傾く方向を多方向に分散させることによって、基準視野角を広くすることができる。

**【0006】**

しかし、垂直配向モード液晶表示装置は、前面視認性に比べて側面視認性が低い問題点がある。例えば、切開部が形成されたPVA(patterned vertical alignment aligned)方式の液晶表示装置の場合には、側面に向かうほど画像が明るくなり、これが著しくなると、高い階調の間の輝度差がなくなって、画像がゆがんで見える場合もある。

40

**【0007】**

このような問題点を改善するために、一つの画素を二つの副画素に分割し、二つの副画素を容量性結合させた後、一つの副画素には直接電圧を印加し、もう一つの副画素には容量性結合による電圧の降下を起こして、二つの副画素の電圧を異ならせることによって、透過率を異ならせる方法が提示された。

**【0008】**

この時、透過率を異ならせるために、印加されるデータ電圧が異ならなければならないが、これは、結局、二つの副画素に異なる階調電圧を印加しなければならないという意味であり、階調電圧生成部は、二つの副画素に印加される階調電圧または階調基準電圧を生

50

成する。このような階調電圧生成部は、抵抗列、スイッチング素子、及び演算増幅器からなって、他の駆動回路と印刷回路基板 (printed circuit board, PCB) に実装されている。しかし、階調電圧生成部は、別途の部品からなるため、PCB 上の面積を多く占めるのはもちろん、価格の面でも不利である。

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明が目的とする技術的課題は、実装面積を減少させて、原価競争力を確保することができる、階調電圧生成部及びこれを含む表示装置を提供することにある。

【課題を解決するための手段】

【0010】

本発明の一特徴によれば、各々第1及び第2副画素を含み、全体的に行列形態に配列されており、画像信号に対応する画像をそれぞれ表示する複数の画素を含む表示装置の駆動装置であって、階調基準電圧に対するデジタルデータを記憶するメモリ、前記デジタルデータを読み取って、読み取った前記デジタルデータと共にクロック信号及び少なくとも一つの選択信号を出力する制御部、集積回路からなって、前記制御部からの前記デジタルデータを受信して階調基準電圧の集合を生成する階調電圧生成部、前記階調基準電圧の集合を受信して複数の階調電圧を生成し、前記複数の階調電圧のうち、前記画像信号に該当する階調電圧を選択して前記選択された階調電圧をデータ信号として前記第1及び第2副画素に印加するデータ駆動部を含み、前記階調電圧生成部は、前記デジタルデータに基づいて、前記第1副画素に入力されるデータ電圧に適用されるデジタル階調基準データ及び前記第2副画素に入力されるデータ電圧に適用されるデジタル階調基準データをそれぞれ記憶する第1レジスター及び第2レジスター、前記第1及び第2レジスターからの出力を受信して、前記第1副画素に対する前記デジタル階調基準データと前記第2副画素に対する前記デジタル階調基準データのうちの1つを選択する複数のマルチブレクサーを含む選択部、前記マルチブレクサーの出力端子に各々連結されており、前記マルチブレクサーで選択されたデジタルデータをアナログ電圧に変換して前記階調基準電圧を生成する複数のデジタルアナログ変換器を含む変換部を含み、前記マルチブレクサーには、前記第1及び第2レジスターからの一対の出力が入力され、前記デジタルアナログ変換器に連結されているバッファーを含み、前記選択信号は前記マルチブレクサーに入力される。

また、本発明の他の一特徴によれば、各々第1及び第2副画素を含み、全体的に行列形態に配列されており、画像信号に対応する画像をそれぞれ表示する複数の画素を含む表示装置の駆動装置であって、階調基準電圧に対するデジタルデータを記憶するメモリ、

前記デジタルデータを読み取って、読み取った前記デジタルデータと共にクロック信号及び少なくとも一つの選択信号を出力する制御部、集積回路からなって、前記制御部からの前記デジタルデータを受信して階調基準電圧の集合を生成する階調電圧生成部、前記階調基準電圧の集合を受信して複数の階調電圧を生成し、前記複数の階調電圧のうち、前記画像信号に該当する階調電圧を選択して前記選択された階調電圧をデータ信号として前記第1及び第2副画素に印加するデータ駆動部を含み、前記階調電圧生成部は、前記デジタルデータに基づいて、前記第1副画素に入力されるデータ電圧に適用されるデジタル階調基準データ及び前記第2副画素に入力されるデータ電圧に適用されるデジタル階調基準データをそれぞれ記憶する第1レジスター及び第2レジスター、前記第1及び第2レジスターからの出力を受信して、前記第1副画素に対する前記デジタル階調基準データと前記第2副画素に対する前記デジタル階調基準データのうちの1つを選択する複数のマルチブレクサーを含む選択部、前記マルチブレクサーの出力端子に各々連結されており、前記マルチブレクサーで選択されたデジタルデータをアナログ電圧に変換して前記階調基準電圧を生成する複数のデジタルアナログ変換器を含む変換部を含み、前記マルチブレクサーには、前記第1及び第2レジスターからの少なくとも二対以上の出力が入力され、前記デジタルアナログ変換器に連結されている少なくとも二つのサンプル及びホールド回路を含み、前記選択信号のうちの一つは前記マルチブレクサーに入力され、残りは前記サンプル及び

10

20

30

40

50

ホールド回路に入力される。

【0014】

さらに本発明の他の特徴によれば、各々第1及び第2副画素を含み、全体的に行列形態に配列されており、画像信号に対応する画像をそれぞれ表示する複数の画素を含む表示装置の駆動装置であって、階調基準電圧に対するデジタルデータを記憶するメモリ、前記デジタルデータを読み取って、読み取った前記デジタルデータと共にクロック信号及び少なくとも一つの選択信号を出力する制御部、集積回路からなって、前記制御部からの前記デジタルデータを受信して前記第1副画素に係る階調基準電圧の集合、または前記第2副画素に係る階調基準電圧の集合を生成する階調電圧生成部、前記階調基準電圧の集合を受信して複数の階調電圧を生成し、前記複数の階調電圧のうち、前記画像信号に該当する階調電圧を選択して前記選択された階調電圧をデータ信号として前記第1及び第2副画素に印加するデータ駆動部を含み、前記階調電圧生成部は、複数の第1階調基準電圧を生成する抵抗列、前記デジタルデータに基づくデジタル階調基準データを記憶するレジスター、前記レジスターからの出力を受信する複数のデジタルアナログ変換器を含む変換部、そして前記デジタルアナログ変換器及び前記抵抗列にそれぞれ連結された2つの入力端子を含み、前記デジタルアナログ変換器には、前記選択信号が入力されるスイッチング素子を通じて連結されている演算增幅器を含み、前記演算增幅器は、前記スイッチング素子が遮断される場合、前記第1階調基準電圧を前記第1副画素に対する階調基準電圧として出力し、前記スイッチング素子が導通される場合、前記第1階調基準電圧と前記デジタルアナログ変換器の出力との和で決められる電圧を前記第2副画素に対する第2階調基準電圧として出力する。10

【0015】

この時、前記選択信号は前記スイッチング素子に入力されることができる。

【発明の効果】

【0026】

本発明によれば、本発明による構造の階調電圧生成部を一つのチップ形態で提供することによって、印刷回路基板上で占める面積を減少させるのはもちろん、原価競争力を向上させることができる。

【発明を実施するための最良の形態】

【0027】

添付した図面を参照して、本発明の実施形態について、本発明が属する技術分野における通常の知識を有する者が容易に実施することができるように詳細に説明する。しかし、本発明は多様な相異した形態で実現でき、ここで説明する実施形態に限定されない。30

【0028】

それでは、本発明の実施形態による階調電圧生成部及びこれを含む表示装置について、図面を参照して詳細に説明する。ここでは、液晶表示装置を一例として説明する。

【0029】

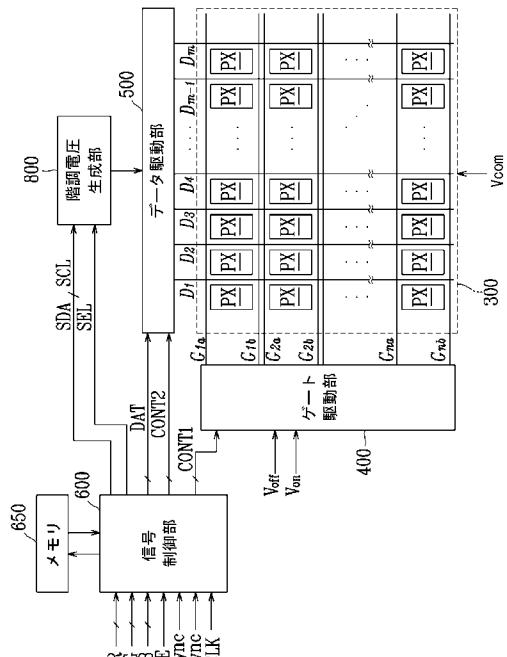

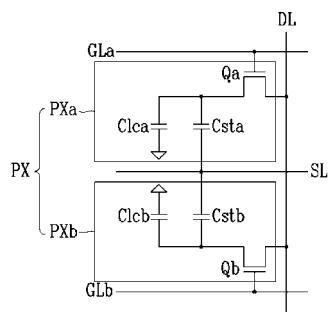

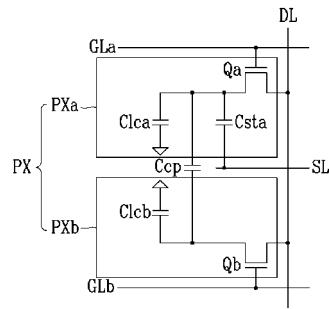

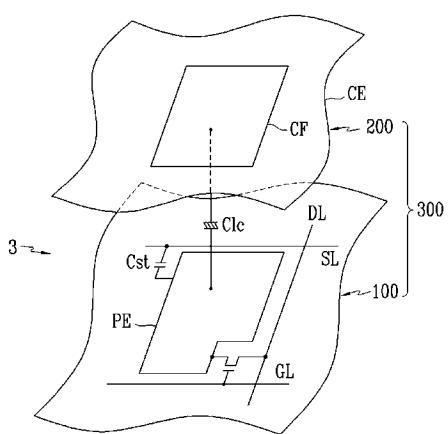

図1は本発明の一実施形態による液晶表示装置のブロック図であり、図2A及び図2Bは本発明の実施形態による液晶表示装置の一つの画素に対する等価回路図であり、図3は本発明の一実施形態による液晶表示装置の一つの副画素に対する等価回路図である。40

【0030】

図1を参照すれば、本発明の一実施形態による液晶表示装置は、液晶表示板組立体(liquid crystal panel assembly)300、これに連結されているゲート駆動部400及びデータ駆動部500、データ駆動部500に連結されている階調電圧生成部800、そしてこれらを制御する信号制御部600を含む。

【0031】

液晶表示板組立体300は、等価回路で見る時、複数の表示信号線、及びこれに連結されていて、ほぼ行列形態に配列されている複数の画素(PX)を含む。

【0032】

これに対して、図3に示した構造で見る時、液晶表示板組立体300は、互いに対向す50

る下部及び上部表示板 100、200、これらの間に形成されている液晶層 3 を含む。

**【0033】**

表示信号線は、下部表示板 100 に形成されていて、ゲート信号（走査信号ともいう）を伝達する複数のゲート線（G1a - Gnb）及びデータ信号を伝達するデータ線（D1 - Dm）を含む。ゲート線（G1a - Gnb）は、概ね行方向にのびていて、互いにほぼ平行であり、データ線（D1 - Dm）は、概ね列方向にのびていて、互いにほぼ平行である。

**【0034】**

図 2A 及び図 2B には表示信号線及び画素の等価回路が示されているが、図面符号 GLa、GLb で示したゲート線及び図面符号 DL で示したデータ線の他にも、表示信号線は 10 、ゲート線（G1 - G2b）とほぼ平行にのびている維持電極線（SL）を含む。

**【0035】**

図 2A を参照すれば、各画素（PX）は、一対の副画素（PXa、PXb）を含み、各副画素（PXa、PXb）は、当該ゲート線（GLa、GLb）及びデータ線（DL）に連結されているスイッチング素子（Qa、Qb）、これに連结されている液晶キャパシタ（liquid crystal capacitor）（Clca、Clcb）、そしてスイッチング素子（Qa、Qb）及び維持電極線（SL）に連結されているストレージキャパシタ（storage capacitor）（Csta、Cstb）を含む。ストレージキャパシタ（Csta、Cstb）は、必要に応じて省略することができ、この場合には維持電極線（SL）も省略することができる。 20

**【0036】**

図 2B を参照すれば、各画素（PX）は、一対の副画素（PXa、PXb）、及びこれらの間に連結されている結合キャパシタ（Ccp）を含み、各副画素（PXa、PXb）は、当該ゲート線（GLa、GLb）及びデータ線（DL）に連結されているスイッチング素子（Qa、Qb）、及びこれに連結されている液晶キャパシタ（liquid crystal capacitor）（Clca、Clcb）を含む。そして、二つの副画素（PXa、PXb）のうちの一つ（PXa）は、スイッチング素子（Qa）及び維持電極線（SL）に連結されているストレージキャパシタ（storage capacitor）（Csta）を含む。 30

**【0037】**

図 3 を参照すれば、各副画素（PXa、PXb）のスイッチング素子（Q）は、下部表示板 100 に形成されている薄膜トランジスタなどからなり、各々ゲート線（GL）に連結されている制御端子、データ線（DL）に連結されている入力端子、そして液晶キャパシタ（Clc）及びストレージキャパシタ（Cst）に連結されている出力端子を含む三端子素子である。 40

**【0038】**

液晶キャパシタ（Clc）は、下部表示板 100 の副画素電極（PE）及び上部表示板 200 の共通電極（CE）を二つの端子とし、二つの電極（PE、CE）の間の液晶層 3 は、誘電体として機能する。副画素電極（PE）はスイッチング素子（Q）に連結され、共通電極（CE）は上部表示板 200 の全面に形成されて、共通電圧（Vcom）の印加を受ける。図 3 とは異なって、共通電極（CE）は下部表示板 100 に形成されることもでき、この時には、二つの電極（PE、CE）のうちの少なくとも一つが線状または棒状に形成されることができる。

**【0039】**

液晶キャパシタ（Clc）の補助的な役割を果たすストレージキャパシタ（Cst）は、下部表示板 100 に形成されている維持電極線（SL）及び画素電極（PE）が絶縁体を間ににおいて重畳して構成され、維持電極線（SL）には、共通電圧（Vcom）などの決められた電圧が印加される。しかし、ストレージキャパシタ（Cst）は、副画素電極（PE）及びその真上の前段ゲート線が絶縁体を間ににおいて重畳して構成されることもできる。 50

**【0040】**

一方、色表示を実現するためには、各画素が原色 (primary color) のうちの一つを固有に表示したり（空間分割）、各画素が時間によって交互に三原色を表示するようにして（時間分割）、これら三原色の空間的、時間的合計によって所望の色相が認識されるようにする。原色の例としては、赤色、緑色、及び青色がある。

**【0041】**

図3は空間分割の一例であって、上部表示板200の各画素の領域に原色のうちの一つを示す色フィルター(CF)が形成されることを示している。図3とは異なって、色フィルター(CF)は、下部表示板100の副画素電極(PE)上または下に形成されることもできる。

10

**【0042】**

図1を参照すれば、ゲート駆動部400は、ゲート線(G1a-Gnb)に連結されて、外部からのゲートオン電圧(Von)及びゲートオフ電圧(Voff)の組み合わせからなるゲート信号をゲート線(G1a-Gnb)に印加する。

**【0043】**

階調電圧生成部(gray voltage generator)800は、I2Cインターフェース(interface)方式で連結されて、データ(SDA)及びクロック信号(SCL)を受信して、画素の透過率に関する二つの階調基準電圧の集合を生成する。二つの階調基準電圧の集合は、一つの画素を構成する二つの副画素に独立的に提供されるものであって、各階調基準電圧の集合は、共通電圧(Vcom)に対して正の値を有するもの及び負の値を有するものを含む。しかし、二つの基準階調電圧の集合の代わりに、一つの階調基準電圧の集合のみを生成することもできる。

20

**【0044】**

メモリ650は、信号制御部600に連結されて、階調基準電圧に対するデジタルデータを記憶しておいて、信号制御部600に出力する。

**【0045】**

データ駆動部500は、液晶表示板組立体300のデータ線(D1-Dm)に連結されて、階調電圧生成部800からの階調基準電圧を分圧して全ての階調に対する階調電圧を生成し、この中からデータ電圧を選択する。

**【0046】**

30

信号制御部600は、ゲート駆動部400及びデータ駆動部500などの動作を制御する。

**【0047】**

このようなゲート駆動装置400、データ駆動部500、信号制御部600、階調電圧生成部800の各々は、少なくとも一つの集積回路チップの形態で液晶表示板組立体300上に直接装着されたり、可撓性印刷回路膜(flexible printed circuit film)(図示せず)上に装着されてTCP(tape carrier package)の形態で液晶表示板組立体300に付着されたり、別途の印刷回路基板(printed circuit board)(図示せず)上に装着されることもできる。

40

**【0048】**

また、これらとは異なって、これらゲート駆動装置400、データ駆動部500、信号制御部600、階調電圧生成部800は、信号線(G1a-Gnb、D1-Dm)及び薄膜トランジスタのスイッチング素子(Qa、Qb)などと共に液晶表示板組立体300に集積されることもできる。また、ゲート駆動装置400、データ駆動部500、信号制御部600、階調電圧生成部800は、单一チップに集積されることもでき、この場合、これらのうちの少なくとも一つまたはこれらを構成する少なくとも一つの回路素子が单一チップの外側に位置することもできる。

**【0049】**

それでは、このような液晶表示装置の表示動作について、詳細に説明する。

50

## 【0050】

信号制御部600は、外部のグラフィック制御機（図示せず）から入力画像信号（R、G、B）及びその表示を制御する入力制御信号、例えば垂直同期信号（Vsync）及び水平同期信号（Hsync）、メインクロック（MCLK）、データタイネーブル信号（DE）などの印加を受ける。

## 【0051】

信号制御部600の入力画像信号（R、G、B）及び入力制御信号に基づいて、画像信号（R、G、B）を液晶表示板組立体300の動作条件に合うように適切に処理して、ゲート制御信号（CONT1）及びデータ制御信号（CONT2）などを生成した後、ゲート制御信号（CONT1）をゲート駆動部400に出力し、データ制御信号（CONT2）及び処理した画像信号（DAT）をデータ駆動部500に出力し、階調電圧生成部800を制御する選択信号（SEL）を生成して出力する。

10

## 【0052】

ゲート制御信号（CONT1）は、走査開始を指示する走査開始信号（STV）及びゲートオン電圧（Von）の出力時間を制御するクロック信号（CPV）を含む。

## 【0053】

データ制御信号（CONT2）は、一対の画素（PX）に対するデータの伝送を知らせる水平同期開始信号（STH）、データ線（D1 - Dm）に当該データ電圧の印加を指示するロード信号（LOAD）、及びデータクロック（HCLK）を含む。データ制御信号（CONT2）は、また、共通電圧（Vcom）に対するデータ電圧の極性（以下、「共通電圧に対するデータ電圧の極性」を略して、「データ電圧の極性」とする）を反転させる反転信号（RVS）を含むことができる。

20

## 【0054】

選択信号（SEL）は、階調電圧生成部800が生成した二つの階調基準電圧の集合のうちの一つの選択を指示する信号であって、水平同期開始信号（STH）、ロード信号（TP）などと周期が同一である。一方、前記で、ゲート制御信号（CONT1）のうちのクロック信号の周期は水平同期開始信号（STH）の2倍であってもよく、この場合、これを選択信号（SEL）として使用することもできる。

## 【0055】

信号制御部600からのデータ制御信号（CONT2）によって、データ駆動部500は一対の副画素（PX）に対するデジタル画像信号（DAT）を受信して、各デジタル画像信号（DAT）に対応する階調電圧を選択することによって、デジタル画像信号（DAT）をアナログデータ信号に変換した後に、これを当該データ線（D1 - Dm）に印加する。

30

## 【0056】

ゲート駆動部400は、信号制御部600からのゲート制御信号（CONT1）によって、ゲートオン電圧（Von）をゲート線（G1a - Gnb）に印加して、このゲート線（G1a - Gnb）に連結されたスイッチング素子（Qa、Qb）を導通させ、それによって、データ線（D1 - Dm）に印加されたデータ電圧が導通されたスイッチング素子（Qa、Qb）を通じて当該副画素（Pxa、Pxb）に印加される。

40

## 【0057】

副画素（Pxa、Pxb）に印加されたデータ電圧及び共通電圧（Vcom）の差は、液晶キャパシタ（Clc）の充電電圧、つまり画素電圧として現れる。液晶分子は、画素電圧の大きさによってその配向が異なり、それによって、液晶層3を通過する光の偏光が変化する。このような偏光の変化は、表示板100、200に付着された偏光子（図示せず）によって光の透過率の変化として現れる。

## 【0058】

1/2水平周期（または1/2H）[水平同期信号（Hsync）及びゲートクロック（CPV）の一周期]を単位として、データ駆動部500及びゲート駆動部400は、同一な動作を繰り返す。このような方式で、1フレーム（frame）の間に全てのゲート

50

線 (G<sub>1a</sub> - G<sub>n b</sub>) に対して順次にゲートオン電圧 (V<sub>on</sub>) を印加し、全ての画素にデータ電圧を印加する。

【0059】

1 フレームが終了すれば次のフレームが開始されて、各画素に印加されるデータ電圧の極性が直前のフレームでの極性と反対になるように、データ駆動部 500 に印加される反転信号 (RVS) の状態が制御される (フレーム反転)。この時、1 フレーム内でも反転信号 (RVS) の特性によって一つのデータ線を通じて流れるデータ電圧の極性が反対になったり (例: 行反転、点反転)、隣接するデータ線を通じて同時に流れるデータ電圧の極性が互いに反対になることがある (例: 列反転、点反転)。

【0060】

以下、本発明の実施形態による階調電圧生成部について、図 4 乃至図 10 を参照して詳細に説明する。

【0061】

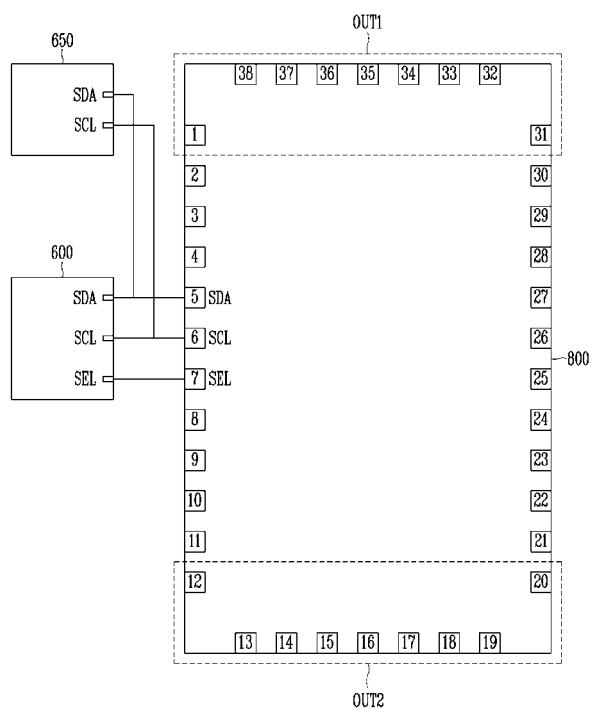

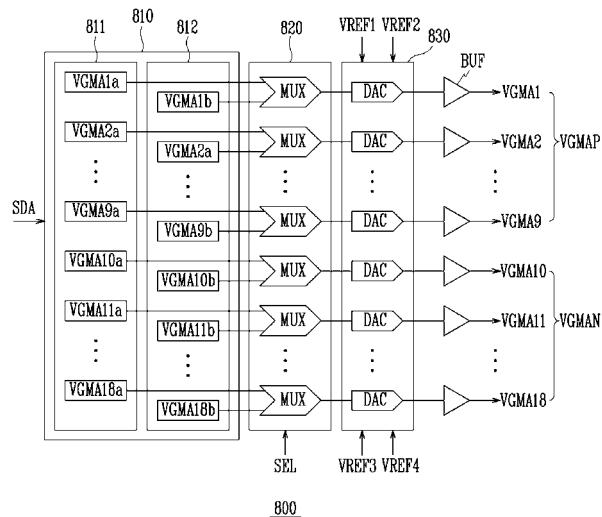

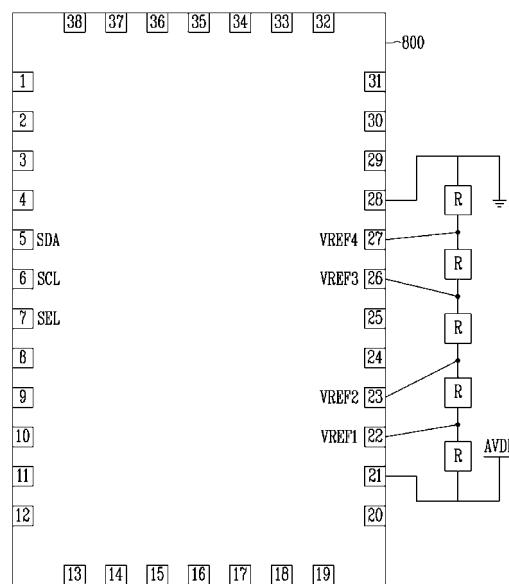

図 4 は本発明の一実施形態による液晶表示装置の駆動装置のブロック図であり、図 5 は本発明の一実施形態による階調電圧生成部に基準電圧を印加する一例を示す図面であり、図 6 は本発明の一実施形態による階調電圧生成部のブロック図である。

【0062】

図 4 を参照すれば、本発明の一実施形態による階調電圧生成部 800 は、集積回路の形態の一つのチップで実現されていて、図示したように、例えば 1 番乃至 38 番までの 38 個のピンを含む。その中で、1 番ピン及び 32 番乃至 38 番ピンまでの 9 個のピン、12 番乃至 20 番ピンまでの 9 個のピンは各々出力部 (OUT1, OUT2) を構成し、5 番乃至 7 番ピンは各々データ (SDA)、クロック信号 (SCL) 及び選択信号 (SEL) が入力されるピンである。

【0063】

また、前記のように、メモリ 650 は、階調基準電圧に対するデジタルデータ (SDA) を記憶しておいて、信号制御部 600 の読み取りによって信号制御部 600 にデータを出力し、信号制御部 600 は、このデータ (SDA) を受信して再び階調電圧生成部 800 に出力する。

【0064】

図 5 を参照すれば、本発明の一実施形態による階調電圧生成部 800 は、一対のデジタルレジスター 811, 812 を含むレジスター部 810、デジタルレジスター 811, 812 に連結されている複数のマルチプレクサー (MUX) を含むデータ選択部 820、及びマルチプレクサー (MUX) に各々連結されている複数のデジタルアナログ変換器 (DAC) を含む変換部 830、そして各デジタルアナログ変換器 (DAC) に連結されているバッファー (BUF) を含む。

【0065】

二つのデジタルレジスター 811, 812 は、互いに異なるデジタル階調基準データの集合 (VGMA1a - VGMA18a, VGMA1b - VGMA18b) を記憶し、二つの階調基準データの集合 (VGMA1a - VGMA18a, VGMA1b - VGMA18b) は対をなして互いに対応する。

【0066】

各マルチプレクサー (MUX) は、二つのデジタルレジスター 811, 812 から対応する一対のデータ (VGMA1a · VGMA1b, ..., VGMA18a · VGMA18b) を受信して、選択信号 (SEL) によって二つのうちの一つを選択して出力する。

【0067】

各デジタルアナログ変換器 (DAC) 及びバッファー (BUF) は、マルチプレクサー (MUX) からのデジタルデータをアナログ電圧 (AGMA1 - VGMA18) に変換及び増幅して出力する。

【0068】

以下では、正極性及び負極性のアナログ電圧 (VGMAP, VGMAN) を各々 9 個ずつ

10

20

30

40

50

つ、総計で 18 個を生成することを一例として説明し、入力されるデジタルデータ (S D A) などによって生成されるアナログ電圧の数はこれと異なることもある。

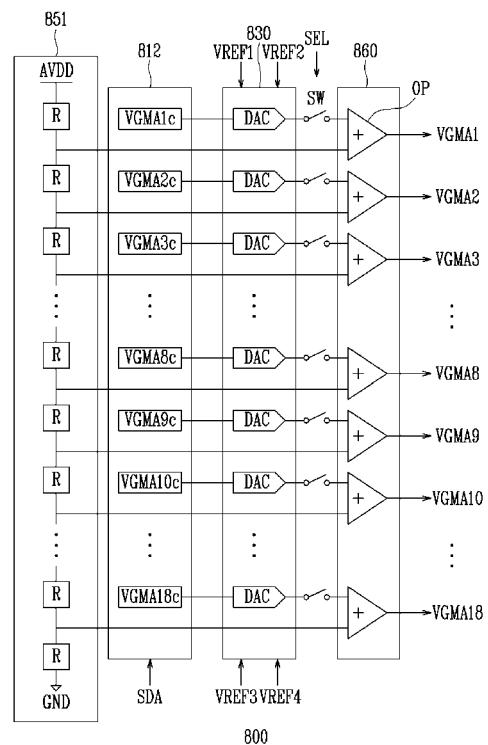

#### 【0069】

この時、図 6 に示したように、階調電圧生成部 800 の外側に、駆動電圧 (A V D D) 及び接地電圧の間に連結されている複数の抵抗 (R) が連結されている抵抗列が形成されていて、この抵抗列は、駆動電圧 (A V D D) を分圧して、デジタルアナログ変換器 (D A C) に入力される基準電圧 (V R E F 1 - V R E F 4) を提供する。例えば、基準電圧 (V R E F 1、V R E F 2) は共通電圧 (V c o m) に対して正の値を、基準電圧 (V R E F 3、V R E F 4) は共通電圧 (V c o m) に対して負の値を有することができる。これとは異なって、階調電圧生成部 800 内に抵抗列を形成して、基準電圧を提供することもできる。10

#### 【0070】

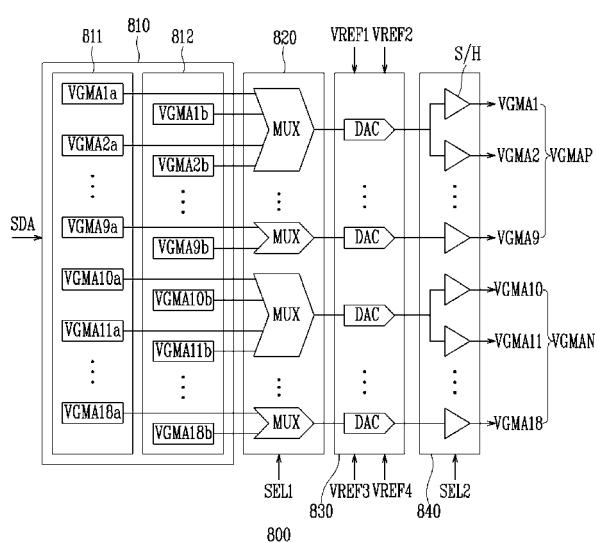

一方、図 7 に示した本発明の他の実施形態による階調電圧生成部 800 は、図 5 に示した階調電圧生成部 800 とほぼ同一である。つまり、一対のデジタルレジスター 811、812 を含むレジスター部 810、デジタルレジスター 811、812 に連結されている複数のマルチプレクサー (M U X) を含むデータ選択部 820、及びマルチプレクサー (M U X) に各々連結されている複数のデジタルアナログ変換器 (D A C) を含む変換部 830 を含む。

#### 【0071】

ただしここで、変換部 830 のマルチプレクサー (M U X) には、一対のデータが入力されるのではなく、二対または一対のデータが入力される。ここで、極性別に二対が入力されれば、データ (V G M A 9 a · V G M A 9 b、V G M A 18 a · V G M A 18 b) の場合には一対が入力される。これとは異なって、極性の区別なく二対に組み合わせることもできる。例えばデータ (V G M A 9 a · V G M A 9 b、V G M A 10 a · V G M A 10 b) を一対に組み合わせて一つのマルチプレクサー (M U X) に入力することができる。さらには、二対以上に組み合わせることもできる。20

#### 【0072】

このような方式は、図 5 に示した階調電圧生成部 800 に比べてマルチプレクサー (M U X) 及びデジタルアナログ変換器 (D A C) の数を減少させることができる。

#### 【0073】

一方、一つのデジタルアナログ変換器 (D A C) には、二つまたは一つのサンプル及びホールド回路 (S H) が連結されている。マルチプレクサー (M U X) に選択信号 (S E L 1) が入力され、サンプル及びホールド回路 (S H) にも選択信号 (S E L 2) が入力される。サンプル及びホールド回路 (S H) は、互いに異なる二対のアナログデータが一つのデジタルアナログ変換器 (D A C) を通じて出力されるので、これを最終的に分離し、このようなサンプル及びホールド回路 (S H) は、前記バッファ (B U F) 及びスイッチング素子を結合したものと見ることができる。30

#### 【0074】

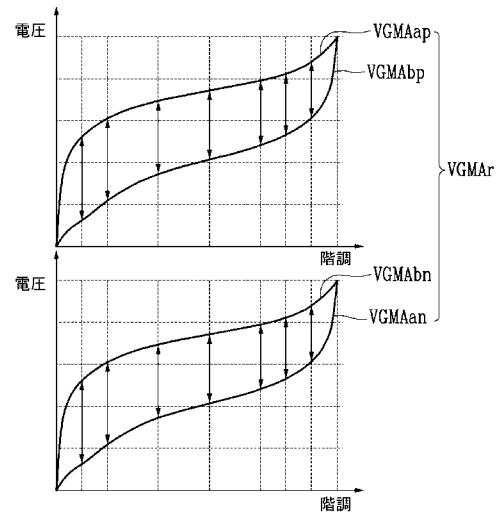

図 8 A 及び図 8 B を参照すれば、本発明の他の実施形態による階調電圧生成部 800 は、駆動電圧 (A V D D) 及び接地電圧 (G N D) の間に連結されている複数の抵抗 (R) を含み、アナログ階調基準電圧を生成する電圧生成部 851、複数のデジタルデータ (V G M A 1 c - V G M A 18 c) を記憶するデジタルレジスター 812、デジタルレジスター 812 に連結されている複数のデジタルアナログ変換器 (D A C) を含む変換部 830、そして電圧生成部 851 の抵抗 (R) の間及びスイッチング素子 (S W) を通じてデジタルアナログ変換器 (D A C) に連結されている演算増幅器 (O P) を含む演算部 860 を含む。40

#### 【0075】

ここで、演算増幅器 (O P) は、スイッチング素子 (S W) の動作によって電圧生成部 851 からの電圧のみを出力したり、電圧生成部 851 からの電圧及びデジタルアナログ変換器 (D A C) からの出力を足して出力する。つまり、スイッチング素子 (S W) が遮50

断されて、電圧生成部 851 で生成される電圧だけが出力される場合には、図 8B に示したように、アナログ階調基準電圧 (VGMApp, VGMAn) が生成され、スイッチング素子 (SW) が導通される場合には、デジタルアナログ変換器 (DAC) からの電圧との合計によって決定されるアナログ階調基準電圧 (VGMAbp, VGMAbn) が生成される。図 8B では、矢印で示した差だけを足して副画素 (Px b) に印加されるアナログ階調基準電圧 (VGMAbp, VGMAbn) を生成することを一例に示した。

#### 【0076】

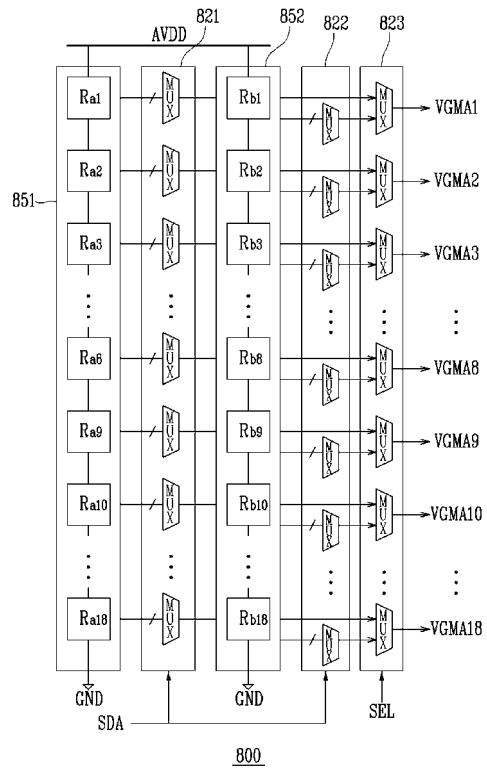

図 9A は本発明の他の実施形態による階調電圧生成部 800 を示したブロック図であり、図 9B は図 9A に示した階調電圧生成部 800 の一部を拡大して示した図面である。

#### 【0077】

図 9A 及び図 9B を参照すれば、本発明の他の実施形態による階調電圧生成部 800 は、抵抗列集合 (Ra1 - Ra18) を含む第 1 電圧生成部 851、第 1 電圧生成部 851 に連結されているマルチプレクサー (MUX) を含む第 1 デコーダー 821、抵抗列集合 (Rb1 - Rb18) を含む第 2 電圧生成部 852、第 2 電圧生成部 852 に連結されているマルチプレクサー (MUX) を含む第 2 デコーダー 822、そして第 1 及び第 2 デコーダー 821、822 のマルチプレクサー (MUX) に連結されている複数のマルチプレクサー (MUX) を含む変換部 823 を含む。

#### 【0078】

ここで、抵抗列集合 (Ra1 - Ra18, Rb1 - Rb18) のうちで、例えば抵抗列 (Ra1, Rb1) は、デジタルデータ (SDA) のビット数に該当する階調基準電圧を生成する。例えば、デジタルデータ (SDA) が 8 ビットであれば、抵抗列 (Ra1, Rb1) は各々 256 個の電圧を生成し、この時、デジタルデータ (SDA) は、選択信号 (SEL) と同様に生成された電圧のうちの一つを選択する。それによって、選択部 823 のマルチプレクサー (MUX31) は、一対の階調基準電圧 (VGMA1a, VGMA1b) のうちの一つを選択信号 (SEL) によって出力する。

#### 【0079】

このように、階調基準電圧の数はデジタルデータのビット数によって決まる事になる。これは、表示装置で表示される階調数と同一である。

#### 【0080】

図 9A 及び図 9B に示した階調電圧生成部 800 は、回路の構成が簡単な抵抗列集合 (Ra1 - Ra18, Rb1 - Rb18) 及びマルチプレクサー (MUX) を使用して実現することができる。

#### 【0081】

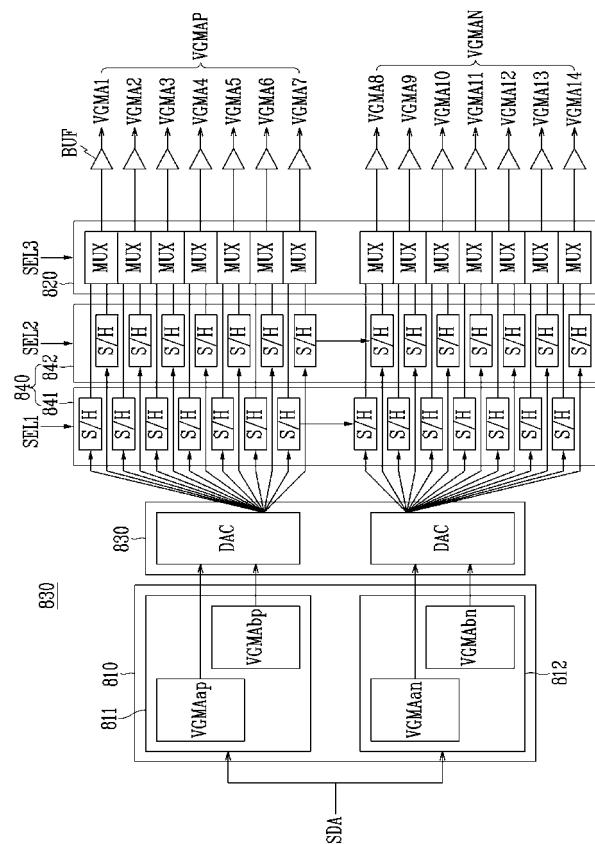

図 10 は本発明の他の実施形態による階調電圧生成部 800 を示したブロック図である。

#### 【0082】

図 10 を参照すれば、本発明の他の実施形態による階調電圧生成部 800 は、一対のデジタルレジスター 811、812 を含むレジスター部 810、デジタルレジスター 811、812 に連結されている複数のデジタルアナログ変換器 (DAC) を含む変換部 830、デジタルアナログ変換器 (DAC) に連結されている複数のサンプル及びホールド回路 (S/H) を含む維持回路 841、842 を含む維持部 840、二つの維持回路 841、842 に連結されている複数のマルチプレクサー (MUX) を含む選択部 820、そして選択部 820 に連結されている複数のバッファー (BUF) を含む。

#### 【0083】

各デジタルレジスター 811、812 は、一対のデジタルデータ (VGMAap・VGMAan, VGMAbp・VGMAbn) を記憶して、変換部 820 もこれに合わせて一対のデジタルアナログ変換器 (DAC) を含む。その代わりに、サンプル及びホールド回路 (S/H) は、生成しようとする階調基準電圧の数だけ存在する。図 10 には正極性及び負極性用階調基準電圧 (VGMAP、VGMAN) を 7 個ずつ生成することを一例として、各維持回路 841、842 は、14 個のサンプル及びホールド回路 (S/H) を含む

10

20

30

40

50

。二つの維持回路 841、842 及び選択部 820 には、サンプル及びホールド回路 (S/H) 及びマルチプレクサー (MUX) を選択するための選択信号 (SEL1、SEL2、SEL3) が各々入力される。

#### 【0084】

図 10 に示した階調電圧生成部 800 は、最も広い面積を占めるデジタルアナログ変換器 (DAC) の数を減少させて、階調電圧生成部 800 の面積を減少させることができる。

#### 【0085】

また、図 7 に示した階調電圧生成部 800 のように、サンプル及びホールド回路 (S/H) が出力端に位置すれば、ノイズ (noise) に脆弱であるが、図 10 に示したように、階調電圧生成部 800 のサンプル及びホールド回路 (S/H) が中央に位置すれば、ノイズに脆弱な短所を補完することができる。

#### 【0086】

以上で、本発明の好ましい実施形態について詳細に説明したが、本発明の権利範囲はこれに限定されず、請求の範囲で定義している本発明の基本概念を利用した当業者の多様な变形及び改良形態も、本発明の権利範囲に属する。

#### 【図面の簡単な説明】

#### 【0087】

【図 1】本発明の一実施形態による液晶表示装置のブロック図である。

【図 2A】本発明の実施形態による液晶表示装置の一つの画素に対する等価回路図である。

【図 2B】本発明の実施形態による液晶表示装置の一つの画素に対する等価回路図である。

【図 3】本発明の一実施形態による液晶表示装置の一つの副画素に対する等価回路図である。

【図 4】本発明の一実施形態による液晶表示装置の駆動装置のブロック図である。

【図 5】本発明の一実施形態による階調電圧生成部のブロック図である。

【図 6】本発明の一実施形態による階調電圧生成部に基準電圧を印加する一例を示す図面である。

【図 7】本発明の他の実施形態による階調電圧生成部のブロック図である。

【図 8A】本発明の他の実施形態による階調電圧生成部のブロック図である。

【図 8B】は図 8A に示した階調電圧生成部で生成される階調による電圧を示すグラフである。

【図 9A】本発明の他の実施形態による階調電圧生成部のブロック図である。

【図 9B】図 9A に示した抵抗列及び選択部を拡大して示した図面である。

【図 10】本発明の他の実施形態による階調電圧生成部のブロック図である。

#### 【符号の説明】

#### 【0088】

3 … 液晶層、

100 … 下部表示板、

200 … 上部表示板、

300 … 液晶表示板組立体、

400 … ゲート駆動部、

500 … データ駆動部、

600 … 信号制御部、

650 … メモリ、

800 … 階調電圧生成部、

810 … レジスター部、

811、812 … レジスター、

820、821、822、823 … 選択部、

10

20

30

40

50

8 3 0 ... 変換部、

8 4 0、8 4 1、8 4 2 ... 維持部、

8 5 1、8 5 2 ... 抵抗列、

8 6 0 ... 演算部、

R、G、B ... 入力画像信号、

D E ... データイネーブル信号、

M C L K ... メインクロック、

H s y n c ... 水平同期信号、

V s y n c ... 垂直同期信号

C O N T 1 ... ゲート制御信号、

C O N T 2 ... データ制御信号、

D A T ... デジタル画像信号、

P X ... 画素、

P X a、P X b ... 副画素、

C l c ... 液晶キャパシタ、

C s t ... ストレージキャパシタ、

Q ... スイッチング素子、

S L ... 維持電極線、

D L ... データ線、

G L ... ゲート線、

P E ... 画素電極、

C F ... 色フィルター、

C E ... 共通電極、

S D A ... デジタルデータ、

S C L ... クロック信号、

S E L ... 選択信号、

D A C ... デジタルアナログ変換器、

O P ... 演算増幅器、

V G M A ... 階調電圧、

V R E F ... 基準電圧。

10

20

30

【図1】

【図2 A】

【図2 B】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8A】

【図 8 B】

【図 9 A】

800

【図 9 B】

【図 10】

---

フロントページの続き

(72)発明者 金 太 星

大韓民国京畿道水原市靈通区靈通洞 シンナムシル信元アパート642棟1501号

(72)発明者 朴 宰 亨

大韓民国京畿道龍仁市器興邑農書里7-1番地

審査官 中村 直行

(56)参考文献 国際公開第2005/038766 (WO, A1)

特開平09-026765 (JP, A)

特開2004-240428 (JP, A)

特開2003-186457 (JP, A)

特開2005-316211 (JP, A)

特開平03-078790 (JP, A)

特開2004-220021 (JP, A)

特開平08-248385 (JP, A)

特開平06-308454 (JP, A)

特開2003-280615 (JP, A)

特開平11-337909 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 00 - 3 / 38

G 02 F 1 / 133