(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5401774号

(P5401774)

(45) 発行日 平成26年1月29日(2014.1.29)

(24) 登録日 平成25年11月8日(2013.11.8)

|                       |               |

|-----------------------|---------------|

| (51) Int.Cl.          | F 1           |

| HO2M 1/08 (2006.01)   | HO2M 1/08 A   |

| HO3K 17/16 (2006.01)  | HO3K 17/16 F  |

| HO3K 17/567 (2006.01) | HO3K 17/56 C  |

| HO3K 17/687 (2006.01) | HO3K 17/687 A |

請求項の数 4 (全 9 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2007-219244 (P2007-219244) |

| (22) 出願日  | 平成19年8月27日 (2007.8.27)       |

| (65) 公開番号 | 特開2009-55696 (P2009-55696A)  |

| (43) 公開日  | 平成21年3月12日 (2009.3.12)       |

| 審査請求日     | 平成22年6月15日 (2010.6.15)       |

前置審査

|           |                                             |

|-----------|---------------------------------------------|

| (73) 特許権者 | 000005234<br>富士電機株式会社<br>神奈川県川崎市川崎区田辺新田1番1号 |

| (74) 代理人  | 100150441<br>弁理士 松本 洋一                      |

| (72) 発明者  | 山城 啓輔<br>東京都日野市富士町1番地 富士電機アドバンストテクノロジー株式会社内 |

| (72) 発明者  | 田久保 拡<br>東京都日野市富士町1番地 富士電機アドバンストテクノロジー株式会社内 |

| 審査官       | 永田 和彦                                       |

最終頁に続く

(54) 【発明の名称】半導体素子のゲート駆動回路

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体素子のゲートに少なくとも正の電圧を供給してオン・オフ制御する半導体素子のゲート駆動回路において、

直流電源間に第1MOSFETと第2MOSFETとを直列に接続し、前記半導体素子のゲート端子を前記第1MOSFETの負電位側端子および前記第2MOSFETの正電位側端子に接続し、半導体素子のエミッタ端子を第2MOSFETの負電位側端子に接続するとともに、第2MOSFETと並列に、コンデンサと第3MOSFETとの直列回路および第4MOSFETを接続し、

前記第2MOSFETのオン抵抗を、第3、第4MOSFETのオン抵抗よりも大きくし、

半導体素子をターンオフさせるときは、第1MOSFETをオフさせた状態で前記第2MOSFETと同時もしくは前記第2MOSFETより前に前記第3MOSFETをオンさせることを特徴とする半導体素子のゲート駆動回路。

## 【請求項 2】

前記第4MOSFETは、前記半導体素子がオフ状態へ移行したとき、オンさせることを特徴とする請求項1に記載の半導体素子のゲート駆動回路。

## 【請求項 3】

半導体素子のゲートに少なくとも正の電圧を供給してオン・オフ制御する半導体素子のゲート駆動回路において、

10

20

直流電源間に第1MOSFETと第2MOSFETとを直列に接続し、前記半導体素子のゲート端子を前記第1MOSFETの負電位側端子および前記第2MOSFETの正電位側端子に接続し、半導体素子のエミッタ端子を第2MOSFETの負電位側端子に接続するとともに、第2MOSFETと並列に、コンデンサと第3MOSFETとの直列回路および第4MOSFETを接続し、

前記第4MOSFETのオン抵抗を、第2，第3MOSFETのオン抵抗よりも小さくし、

半導体素子をターンオフさせるときは、第1MOSFETをオフさせた状態で前記第2MOSFETと同時もしくは前記第2MOSFETより先に前記第3MOSFETをオンし、前記半導体素子がオフへ移行したとき、前記第4MOSFETをオンさせることを特徴とする半導体素子のゲート駆動回路。

#### 【請求項4】

前記第4MOSFETのオン抵抗を、第2，第3MOSFETのオン抵抗よりも小さくすることを特徴とする請求項2に記載の半導体素子のゲート駆動回路。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

この発明は、パワー半導体素子のゲート駆動回路、特に、半導体素子のターンオフ時に発生するノイズを低減し、かつノイズとトレードオフの関係にあるスイッチング損失を低減することができる半導体素子のゲート駆動回路に関する。

##### 【背景技術】

##### 【0002】

近年、EMI (Electromagnetic Interference) 規制が厳しくなる中、インバータなどの様々な産業分野で、ノイズの低減が技術課題となっている。特に、これら機器の主要部品である半導体素子、およびこれらを搭載したモジュールが、スイッチングすることにより発生するノイズの低減について、然るべき対策が必要とされている。その対策には、ノイズ発生ループに対する処置として、コンデンサやフェライトコアなどの部品や、これらを組み合わせて作成した各種フィルタを追加する方法や、放射ノイズに関しては、その発生ループの面積を削減する方法などがあり、用途や対策装置の状況に応じて様々な対策が採られている。

##### 【0003】

また、発生源となるスイッチング波形の改善によるノイズ対策も行なわれている。例えば、IGBT (Insulated Gate Bipolar Transistor : 絶縁ゲート型バイポーラトランジスタ) にゲート駆動回路を内蔵しモジュール化したIPM(Intelligence Power Module)では、内蔵したゲート駆動回路でノイズ対策を行なうことにより、フェライトコアなどの外部の部品を追加することなく、モジュール単体で低ノイズ化を実現できるため、付加価値を高める上からも非常に有効である。このような理由から、IPMでは例えば非特許文献1に示すような対策が行なわれ、実用化されている。

##### 【0004】

すなわち、ゲート駆動回路に対し、IGBTのコレクタ電流によって2段階に切り換える機能を付加することにより、FWD (flywheel diode : 帰還ダイオード) のターンオフ $dV/dt$ が大きくなる低電流領域でゲート電圧の立ち上がりを緩めて、ソフトスイッチングさせることができる。このようにノイズ低減を志向した駆動回路を搭載したIPMは、すでに製品化されている。

##### 【0005】

一方、ゲート駆動回路における対策として、例えば特許文献1, 2に示すような方法が開示されている。すなわち、半導体素子のターンオフ損失を低減する効果を狙って、ドライブ回路内の抵抗に並列にコンデンサを設け、ターンオフスイッチングの直後からコンデンサが充電完了するまでの間は、ゲート抵抗を用いるよりも速い時定数で当該半導体素子のゲート・エミッタ間容量を放電させることにより、ターンオフミラー時間を短縮し、損

10

20

30

40

50

失を低減する方法である。

**【0006】**

【非特許文献1】三菱電機技報, Vol.77, No.9・2003, pp.567-570

【特許文献1】特許第3666843号明細書

【特許文献2】米国特許第6333665号明細書

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0007】**

上記非特許文献1に記載のIPMのドライブ回路対策は、ノイズを低減するには有用な手段の1つである。しかし、FWDのターンオフ電圧変化率 $dV/dt$ が大きくなる低電流領域でゲート抵抗を大きく設定するため、対策期間中はトレードオフの関係にあるスイッチング損失を大きく犠牲にして、低ノイズ化を実現していることが難点となる。10

**【0008】**

また、ゲート抵抗の切り替えはモジュール内で自動的に行なわれるため、ユーザはいつ電流値が切り替えられたのか分からず。その上、ユーザ自身が切り替えの有無や電流値をコントロールできないという問題がある。具体的には、例えばインバータに本IPMを搭載した場合には、運転中に様々な電流値によるスイッチングが行なわれるが、電流値によりゲート抵抗が自動的に切り替ってしまうため、デッドタイムの管理や、モジュールの損失管理が困難になるという点である。

**【0009】**

一方、ターンオフスイッチングによる損失を低減するために、特許文献2, 3ではゲート抵抗に並列にコンデンサを設ける対策が施されており、ターンオフスピードを早くすることにより、ターンオフ時のスイッチング損失は改善される。しかし、コンデンサを並列に接続する本対策のみでは、ターンオフ時のスイッチング損失だけが低減され、トレードオフの関係にあるノイズはむしろ増えることが問題となる。20

**【0010】**

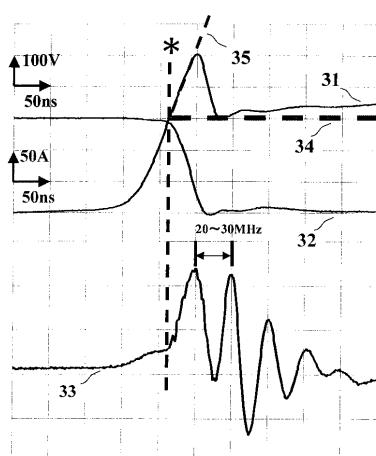

このように、スイッチング損失とノイズはトレードオフの関係にあるため、両者を低減しトレードオフ特性を改善するためには、スイッチング波形におけるどの部分がノイズとの相関性が強く、発生原因となっているかを把握した上で、発生原因でない部位は高速化することが重要である。そこで、ターンオフスイッチング時のスイッチング波形と、ノイズとの関連性を調査した。IGBTにより直流電圧をターンオフした場合のスイッチング波形と、ノイズの指標となるサーチコイル波形を同期して評価した結果を、図3に示す。30

**【0011】**

図3の符号31はIGBTのコレクタ・エミッタ間電圧Vce、32はコレクタ電流Ic、33はサーチコイル波形、34は直流電圧レベルVdcを示す。

図3より、ターンオフ初期には、サーチコイル波形33の振動は殆ど見られず、コレクタ・エミッタ間電圧Vce31が直流電圧Vdc34に達した"\*"のタイミングと同期して、急激にサーチコイル波形33が振動することが分かる。

**【0012】**

従って、Vce31がVdc34に達した以降のスイッチング波形の挙動が重要であり、Vce > Vdcにおける電圧変化率 $dV/dt$ はノイズとの依存性が大きい。逆に、図3の"\*"のタイミング以前のスイッチング波形の挙動は、ノイズとの関連性は低い。このことから、"\*"以前は高速化してターンオフスイッチングの損失を減らし、"\*"以後はできるだけ遅くしてノイズを抑制することが望まれることになる。40

**【0013】**

以上のような観点から、この発明の課題は、ターンオフスイッチング時に発生するノイズおよび損失のトレードオフ特性を改善することにある。

**【課題を解決するための手段】**

**【0014】**

上記課題を解決するため、請求項1の発明では、半導体素子のゲートに少なくとも正の50

電圧を供給してオン・オフ制御する半導体素子のゲート駆動回路において、

直流電源間に第1MOSFETと第2MOSFETとを直列に接続し、前記半導体素子のゲート端子を前記第1MOSFETの負電位側端子および前記第2MOSFETの正電位側端子に接続し、半導体素子のエミッタ端子を第2MOSFETの負電位側端子に接続するとともに、第2MOSFETと並列に、コンデンサと第3MOSFETとの直列回路および第4MOSFETを接続し、

前記第2MOSFETのオン抵抗を、第3、第4MOSFETのオン抵抗よりも大きくし、

半導体素子をターンオフさせるときは、第1MOSFETをオフさせた状態で前記第2MOSFETと同時もしくは前記第2MOSFETより先に前記第3MOSFETをオンさせることを特徴とする。

10

#### 【0015】

請求項2の発明の発明は、上記請求項1の発明においては、前記第4MOSFETは、前記半導体素子がオフ状態へ移行したとき、(例えば、前記半導体素子のゲート・エミッタ間電圧がしきい値以下になったとき)、オンさせることを特徴する子である。

#### 【0017】

さらに、請求項3の発明は、半導体素子のゲートに少なくとも正の電圧を供給してオン・オフ制御する半導体素子のゲート駆動回路において、

直流電源間に第1MOSFETと第2MOSFETとを直列に接続し、前記半導体素子のゲート端子を前記第1MOSFETの負電位側端子および前記第2MOSFETの正電位側端子に接続し、半導体素子のエミッタ端子を第2MOSFETの負電位側端子に接続するとともに、第2MOSFETと並列に、コンデンサと第3MOSFETとの直列回路および第4MOSFETを接続し、

20

前記第4MOSFETのオン抵抗を、第2、第3MOSFETのオン抵抗よりも小さくし、

半導体素子をターンオフさせるときは、第1MOSFETをオフさせた状態で前記第2MOSFETと同時もしくは前記第2MOSFETより先に前記第3MOSFETをオンし、前記半導体素子がオフへ移行したとき、前記第4MOSFETをオンさせることを特徴とするものである。

#### 【0018】

30

さらに、また、請求項4の発明は、請求項2の発明においては、前記第4MOSFETのオン抵抗を、第2、第3MOSFETのオン抵抗よりも小さくすることを特徴とするものである。

#### 【発明の効果】

#### 【0019】

この発明によれば、ターンオフ時の初期にはターンオフスピードを早くするようにしたので、ターンオフ損失を低減することができる。また、ターンオフスピードを早めるための手段が簡単な回路で済むことから、大きなメリットとなる。さらに、この発明をIPMのようにゲート駆動回路込みの製品として適用する場合は、ノイズ発生源となるスイッチング波形自体を改善できるため、フィルタなどのコストの掛かる外付け部品の追加を不要にすることができる。

40

#### 【発明を実施するための最良の形態】

#### 【0020】

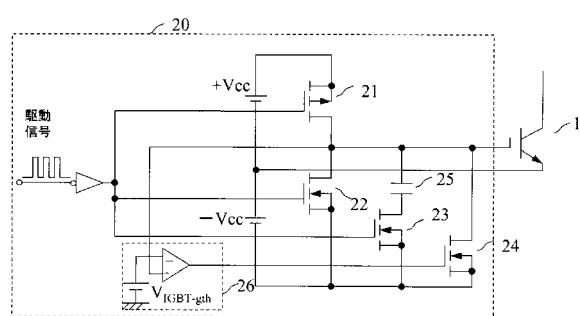

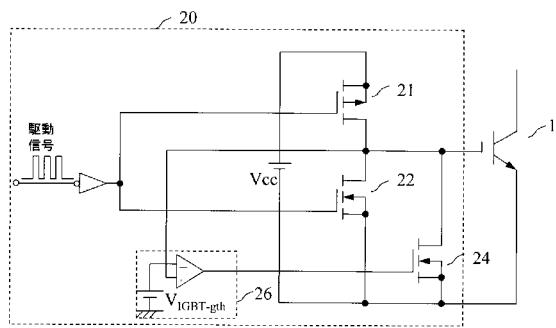

図1はこの発明の実施の形態を示す回路図である。

対象とする半導体素子はIGBT1であり、その駆動回路が符号20で示されている。この駆動回路20は、第1MOSFETとしてのPチャネルMOSFET21と、第2MOSFETとしてのNチャネルMOSFET22と、第3MOSFETとしてのNチャネルMOSFET23と、第4MOSFETとしてのNチャネルMOSFET24と、MOSFET23に直列に接続されたコンデンサ25と、MOSFET24の制御回路26などから構成される。制御回路26は、IGBT1のターンオフ保持用の制

50

御回路である。また、V<sub>cc</sub>は、IGBT 1 のゲート端子に、ゲート電圧を印加するための直流電源であり、第 1 MOSFET 2 1 と第 2 MOSFET 2 2との直列回路の両端に接続されている。

#### 【 0 0 2 1 】

すなわち、IGBT 1 のゲート端子には第 1 MOSFET の負電位側端子（ソース端子）、および第 2 MOSFET の正電位側端子（ドレイン端子）が接続される。また、IGBT 1 のエミッタ端子には第 2 , 第 3 および第 4 MOSFET 2 2 ~ 2 4 の負電位側端子（ソース端子）が、それぞれ接続されて構成される。第 1 ~ 第 3 MOSFET 2 1 ~ 2 3 の各ゲートには、図示のような駆動信号が供給される。

#### 【 0 0 2 2 】

図 1 の回路において、IGBT 1 をターンオンさせるときは第 1 MOSFET 2 1 のみをオンさせ、直流電源V<sub>cc</sub>の電圧をIGBT 1 のゲートに印加する。IGBT 1 をターンオフさせるときは第 1 MOSFET 2 1 はオフとして、第 2 , 第 3 MOSFET 2 2 , 2 3 をオンさせる。これにより、ターンオン時の動作は従来と変わらないが、ターンオフ時の初期にはコンデンサ 2 5 によって、IGBT 1 のゲート・エミッタ間に溜まった電荷を急速に引き抜くことで高速化を図り、損失を低減することができる。そして、IGBTのターンオフ動作中のノイズの影響が大きい期間では、オン抵抗を大きく設定した第 2 MOSFET 2 2 を通してIGBT 1 のゲート・エミッタ間に溜まった電荷を引き抜くことで低速化を図り、ノイズを抑制することができる。

#### 【 0 0 2 3 】

つまり、IGBT1のターンオフ時の初期に、IGBT 1 のゲート・エミッタ間に溜まった電荷をコンデンサ 2 5 に流せばよい。例えば、第 3 MOSFET 2 3 の方が第 2 MOSFET 2 2 よりも早くオンすれば良く、そのためには第 2 MOSFET 2 2 のゲートに遅延回路を設けて駆動信号を遅延させたり、第2MOSFET 2 2 のゲート抵抗を大きくして第2MOSFET22のターンオン時間を長くするとよい。あるいは、第 2 MOSFET 2 2 のオン抵抗を第 3 MOSFET 2 3 より大きくしておけばよく、そのためには、第2MOSFET 2 2 のチャネル長を第3MOSFET 2 3 よりも大きくするとよい。このように、第2、第3MOSFET ( 2 2 , 2 3 ) のオンのタイミングやオン抵抗はMOSFETデバイスの面積を変えたり、微細化することで可能である。このように、ノイズと損失の両者を抑制するためには、第 2 MOSFET 2 2 のオン抵抗は、第 3 , 第 4 MOSFET 2 3 , 2 4 のオン抵抗より大きいことが好ましい。

#### 【 0 0 2 4 】

なお、第 3 MOSFET 2 3 は、ゲート・エミッタ間の配線インダクタンス L と、図 1 の回路に設けられているコンデンサ 2 5 の容量 C とによる LC 共振を抑制する、ダンピング用として用いられる。また、第 4 MOSFET 2 4 は、IGBT 1 がオフ状態に移行したときにオンするものである。IGBT 1 のオフ状態は、例えば、制御回路 2 6 にて IGBT 1 のゲート電圧をそのしきい値  $V_{IGBT-gth}$  と比較し、IGBT 1 のゲート電圧がしきい値以下になったことをもって、IGBT 1 のオフ状態と判断するとよい。他にも、IGBT 1 のコレクタ - エミッタ間電流や、コレクタ - エミッタ間電圧の検出によっても IGBT 1 のオフ状態を検出可能である。

#### 【 0 0 2 5 】

そして、IGBT 1 がオフ状態に移行したことを検出すると、第 4 MOSFET 2 4 をオンする。第 4 MOSFET がオンすることで、IGBT 1 のオフ状態を保持し安定電位を確保するものである。このため、第 4 MOSFET 2 4 のオン抵抗はできるだけ小さい方が望ましく、第 2 , 第 3 MOSFET 2 2 , 2 3 のオン抵抗より小さいことが要求される。この第 4 MOSFET 2 4 は短絡を目的とするもので、特にMOSFETである必要はなく、バイポーラトランジスタでも良く、場合によっては機械的スイッチを用いても良い。

#### 【 0 0 2 6 】

また、第 3 MOSFET 2 3 のオン抵抗により上記LC 共振を十分に抑制し、オフ保持をしなくても誤動作が生ぜずに電位が安定していれば、オフ保持用の第 4 MOSFET 2 4 は省略することができる。上記コンデンサ 2 5 の容量は、IGBT 1 のゲート・エミッタ間の接合容量に対し、同等以上であれば効果が高いことが経験的に判っているが、その範囲の容量でなくても一定の効果は得られるので、容量に対する数値的な規定は特には必要ない。

#### 【 0 0 2 7 】

10

20

30

40

50

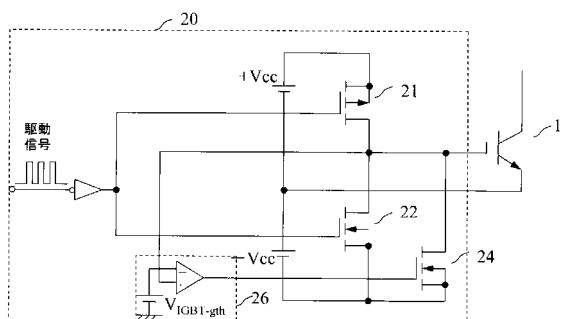

図1は、ゲート駆動回路に逆バイアスを用いず、第1MOSFET2\_1と第2MOSFET2\_2を直列に接続した両端にVccを設けた場合である。これに対し、図2はIGBT1のゲート電位を基準とした場合に正負の電圧を供給できるように、+Vccと-Vccを個別に設けた場合の回路構成図である。すなわち、図1も図2も基本的な動作は同様なので、この発明は正負電源の有無に関わらず適用することができる。

#### 【0028】

この発明との比較例として、一般的なゲート駆動回路を図5、図6に示す。

図5は、ゲートの電位を基準とした場合に正の電源のみで、ゲートへ逆バイアスを供給しない場合の例である。これに対し、図6はゲートの電位を基準とした場合に正負の電源を備え、ゲートへ逆バイアスを供給できる場合の例である。なお、図5、図6とも、図1または図2に示すコンデンサ2\_5と第3MOSFET2\_3を有していない点を除けば、図1または図2と同じなので説明は省略する。10

#### 【0029】

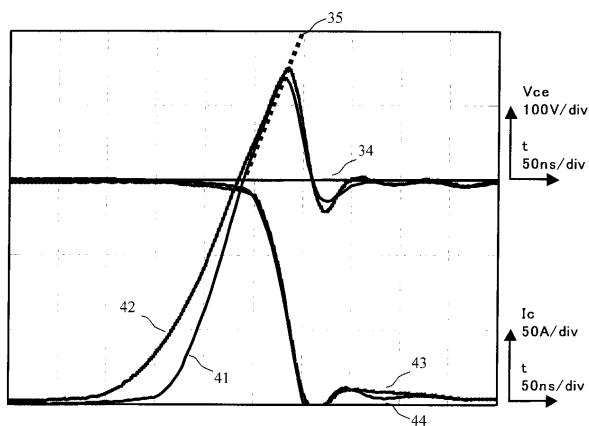

この発明のゲート駆動回路と、図5、図6に示す一般的なゲート駆動回路を用いた場合の、ターンオフスイッチング時の実測波形例を図4に示す。ここでは、逆バイアスあり(±15V)の波形例を示す。この発明のゲート駆動回路を用いた場合のVce波形を符号4\_1、Ic波形を4\_3、一般的なゲート駆動回路を用いた場合のVce波形を符号4\_2、Ic波形を4\_4にそれぞれ示す。この発明のゲート駆動回路を用いた場合は、一般的なゲート駆動回路を用いた場合に比べ、直流電圧Vdcに達する前の領域でのスピードを早く(Vceの電圧変化率dV/dtを大きく)しつつ、Vce > Vdcの領域におけるdV/dtは従来方式とほぼ同程度に抑えられていることが分かる。20

#### 【0030】

以上のことから、コンデンサ2\_5の容量、第2MOSFET2\_2および第3MOSFET2\_3のオン抵抗の選び方によって、ノイズを重点的に抑制するか、または損失を抑制するかを或る程度調整可能なことが分かる。表1に、条件1~3に選んだ場合の実測結果を例示している。図4の例は、表1の条件3と対応している。

すなわち、この発明のゲート駆動回路を用いることで、従来に比べてトレードオフ特性を改善できる。また、正負電源の有無により動作原理は変わらないが、負の電源がある場合の方が、トレードオフ特性の改善効果はやや高いことができる。

#### 【0031】

##### 【表1】

| ゲート駆動回路<br>逆バイアス有無 | 回路条件 | 放射ノイズ*    | ターンオフ損失 |

|--------------------|------|-----------|---------|

| 無(+15V、-0V)        | 条件1  | -3 dBuV/m | ±0%     |

| 有(±15V)            | 条件2  | -6 dBuV/m | -2%     |

|                    | 条件3  | -2dBuV/m  | -17%    |

#### 【0032】

ゲート駆動回路を主としてMOSFETで構成したが、これは集積化を容易にし、回路規模を小さく(部品点数を少なく)するためである。また、図1の回路の変形例として、MOSFET2\_2のソースを、コンデンサ2\_5とMOSFET2\_3との接続点に接続するようにしても良い。

#### 【図面の簡単な説明】

#### 【0033】

##### 【図1】この発明の実施の形態を示す構成図

##### 【図2】図1で逆バイアスが供給可能な例を示す回路図

##### 【図3】一般的なゲート駆動回路を用いた場合のターンオフ動作説明図

##### 【図4】この発明によるゲート駆動回路を用いた場合のターンオフ動作説明図

##### 【図5】図1に対応する一般的な回路を示す回路図

10

20

30

40

50

【図6】図2に対応する一般的な回路を示す回路図

【符号の説明】

【0034】

1 ... IGBT (絶縁ゲートバイポーラトランジスタ)、20...ゲート駆動回路、21, 22, 23, 24...MOSFET (金属酸化膜型電界効果トランジスタ)、25...コンデンサ、26...ターンオフ保持用制御回路、Vcc,+ Vcc,- Vcc...直流電源。

【図1】

【図3】

【図2】

【図4】

【図6】

【図5】

---

フロントページの続き

(56)参考文献 特開2000-333441(JP,A)

特開平10-313570(JP,A)

特許第3666843(JP,B2)

特開2000-59189(JP,A)

特開2007-19844(JP,A)

特開2001-223571(JP,A)

特開平11-97994(JP,A)

特開2003-304678(JP,A)

特開2003-158868(JP,A)

特開平11-262243(JP,A)

特表2007-505544(JP,A)

五十嵐尚,外2名,「新di/dt制御機能搭載 低損失・低ノイズIPM“Lシリーズ”」,三菱電機技報,2003年 9月25日,Vol. 77, No. 9, p. 15 18(567 570)

(58)調査した分野(Int.Cl., DB名)

H02M 1/00, 1/08 - 1/096,

H03K 17/00 - 17/98