(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-252104

(P2005-252104A)

(43) 公開日 平成17年9月15日(2005.9.15)

(51) Int.CI.<sup>7</sup>

H01G 4/12

H01G 4/30

F 1

H01G 4/12 352

H01G 4/30 301D

テーマコード(参考)

5E001

5E082

審査請求 未請求 請求項の数 7 O L (全 20 頁)

(21) 出願番号

特願2004-62861 (P2004-62861)

(22) 出願日

平成16年3月5日(2004.3.5.)

(71) 出願人 000006231

株式会社村田製作所

京都府長岡市東神足1丁目10番1号

(74) 代理人 100092071

弁理士 西澤 均

(72) 発明者 吉川 祐司

京都府長岡市天神二丁目26番10号

株式会社村田製作所内

F ターム(参考) 5E001 AB03 AC07 AC09 AE02 AE03

AE04 AF06 AH01 AH05 AH07

AH08 AH09 AJ01

5E082 AB03 BC36 EE23 EE35 FG06

FG26 FG54 GG10 GG26 GG28

(54) 【発明の名称】積層セラミックコンデンサ

## (57) 【要約】

【課題】積層セラミックコンデンサの実装時および実装後の熱的、機械的応力の集中などにより発生するクラックを、所定のクラック誘導経路に導いて、クラックが内部電極に達することを防止して、所望の特性が確保されるようにする。

【解決手段】内部電極3a, 3bの、セラミック素子1の端面への引き出し位置のうち、実装時に最も下側になる引き出し位置から、当該端面に形成され、実装時に下面側となるセラミック素子1の側面にまで回り込んだ外部電極4a, 4bの先端まで仮想線Xを引いた場合に、実装時に下側になる下側外層部B2に配設されたダミー電極7(ダミー電極層7a, 7b(7n), 7x)のうち、少なくとも一部のダミー電極が仮想線Xと接する位置に達するか、または仮想線Xと交差し、その先端が仮想線Xと当該外部電極4a, 4bにより規定される領域Rにまで達するように配設する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

セラミック素子と、セラミック素子の端面および該端面に連続する側面の両端部に形成された外部電極を具備する積層セラミックコンデンサにおいて、

セラミック素子が、セラミック層を介して、複数の内部電極が互いに対向するように配設された内部電極配設部と、内部電極配設部の上側および下側に配設されたセラミック層である上側外層部および下側外層部とを備え、

少なくとも実装時に下側になる下側外層部には、積層セラミックコンデンサの機能に影響を与えないダミー電極が配設され、かつ、

前記内部電極の、前記セラミック素子の端面への引き出し位置のうち、実装時に最も下側になる引き出し位置から、当該端面に形成され、実装時に下面側となる前記セラミック素子の側面にまで回り込んだ前記外部電極の先端まで仮想線を引いた場合に、前記下側外層部に配設された前記ダミー電極の先端が、前記仮想線と当該外部電極により規定される領域の外側から前記仮想線と接する位置に達するか、または、前記仮想線と交差し、前記仮想線と当該外部電極により規定される領域にまで達しており、実装状態で積層セラミックコンデンサに応力が加わった場合に前記下側外層部に発生するクラックを通過させるクラック誘導経路が形成され、前記クラックが積層セラミックコンデンサの機能に影響を与える内部電極を切断することなく、前記下側外層部を通過するように構成されていることを特徴とする積層セラミックコンデンサ。10

**【請求項 2】**

前記ダミー電極がセラミックグリーンシート層を介して積層された複数のダミー電極層から構成されており、かつ、前記下側外層部に積層されたダミー電極のうち、積み重ね方向における最も上側の、内部電極に最も近接したダミー電極の先端が、前記仮想線と接する位置に達するか、または、前記仮想線と交差し、前記仮想線と当該外部電極により規定される領域にまで達していることを特徴とする請求項 1 記載の積層セラミックコンデンサ。20

**【請求項 3】**

前記ダミー電極がセラミックグリーンシート層を介して積層された複数のダミー電極層から構成されており、かつ、前記下側外層部に積層されたダミー電極のうち、積み重ね方向における最も下側の、内部電極から最も離れたダミー電極の先端が、前記仮想線と接する位置に達するか、または、前記仮想線と交差し、前記仮想線と当該外部電極により規定される領域にまで達していることを特徴とする請求項 1 または 2 記載の積層セラミックコンデンサ。30

**【請求項 4】**

前記ダミー電極がセラミックグリーンシート層を介して積層された複数のダミー電極層から構成されており、かつ、前記下側外層部に積層されたすべてのダミー電極の先端が、前記仮想線と接する位置に達するか、または、前記仮想線と交差し、前記仮想線と当該外部電極により規定される領域にまで達していることを特徴とする請求項 1 記載の積層セラミックコンデンサ。

**【請求項 5】**

前記ダミー電極がセラミックグリーンシート層を介して積層された複数のダミー電極層から構成されており、かつ、前記下側外層部に積層されたダミー電極の、積み重ね方向における最も上側の、内部電極に最も近接したダミー電極のほうが、積み重ね方向における最も下側の、内部電極から最も離れたダミー電極よりも長いことを特徴とする請求項 1 ~ 4 記載の積層セラミックコンデンサ。40

**【請求項 6】**

前記ダミー電極がセラミックグリーンシート層を介して積層された複数のダミー電極層から構成されており、実装時に上方に位置するダミー電極層ほど、先端が外部電極に近い位置まで達するように構成されていることを特徴とする請求項 5 記載の積層セラミックコンデンサ。50

**【請求項 7】**

(a)少なくとも一方の先端部が前記仮想線と当該外部電極により規定される領域内に達する前記ダミー電極と、(b)一端側が前記ダミー電極の前記領域に達する先端部との間に所定の隙間が形成される位置にまで達し、他端側が外部電極に接続されるような態様で、前記仮想線と当該外部電極により規定される領域に配設された外部電極側ダミー電極とを備え、

前記ダミー電極と、前記外部電極側ダミー電極との隙間が、前記クラックが通過するクラック誘導経路となるように構成されていること

を特徴とする請求項 1 ~ 6 記載の積層セラミックコンデンサ。

**【発明の詳細な説明】**

10

**【技術分野】****【0001】**

本願発明は、セラミック素子中にセラミック層を介して複数の内部電極が積層、配設され、かつ、表面に外部電極が形成された構造を有する積層セラミックコンデンサに関する。

**【背景技術】****【0002】**

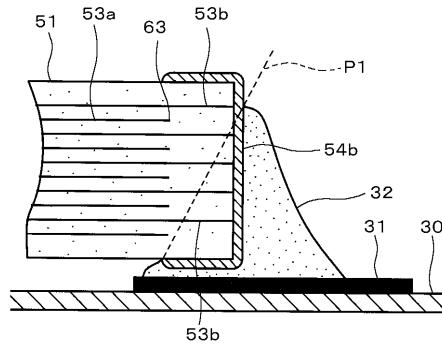

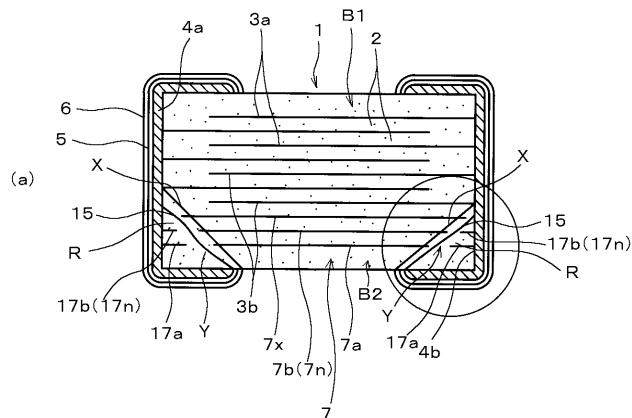

セラミックコンデンサの代表的なものの 1 つに、図 15 に示すような積層セラミックコンデンサがある。この積層セラミックコンデンサは、複数の内部電極 53a, 53b がセラミック層 52 を介して互いに対向するように配設され、かつ、その一端側が交互に異なる側の端面に引き出されたセラミック素子 51 の両端側に、内部電極 53a, 53b と導通するように一对の外部電極 54a, 54b が配設された構造を有している。

20

**【0003】**

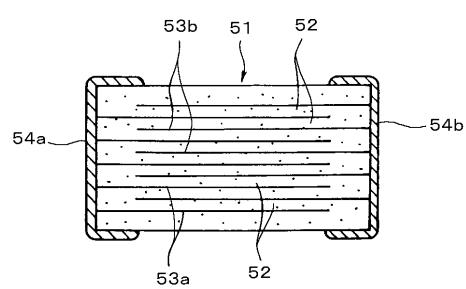

そして、上述のような積層セラミックコンデンサは、通常、図 16 に示すように、回路基板 30 上のランド電極 31 に、外部電極 54a, 54b をはんだ付けすることにより実装される。なお、図 16 において、図 15 と同一符号を付した部分は同一または相当する部分を示す。

**【0004】**

しかし、実装工程で、はんだフィレット 32 が熱収縮する際の応力により、セラミック素子 51 の外部電極 54a, 54b が配設された端部近傍にクラック 55 が発生する場合がある。そして、セラミック素子 51 にクラック 55 が発生すると、クラック 55 に水分が入り込んでクラック 55 に露出した内部電極 53a, 53b が短絡し、回路基板 30 に形成された電子回路に悪影響を与える可能性がある。

30

**【0005】**

このような問題を解決するために、図 17 に示すように、実装時のはんだフィレット 32 が熱収縮する際の応力により、セラミック素子 51 にクラックが発生すると考えられる仮想線 P1 を想定し、セラミック素子 51 の一方側に引き出された内部電極（図 17 では 53a）の先端 63 が仮想線 P1 に至らないように、内部電極 53a を配設し（他方側に引き出された内部電極 53b についても同様にする）、仮想線 P1 にクラックが発生したとしても、一方の外部電極（図 17 では 54b）に接続された内部電極 53b のみにクラックが及ぶようにし、内部電極 53a と 53b が短絡することを防止するようにした積層セラミックコンデンサが提案されている。なお、図 17 において、図 15, 16 と同一符号を付した部分は同一または相当する部分を示す。

40

**【0006】**

しかしながら、この方法の場合、静電容量の形成に寄与する内部電極にクラックが入ることになるため、内部電極が断線して取得される静電容量が低下するという問題点がある。

**【特許文献 1】特開 2003-22929 号公報****【発明の開示】****【発明が解決しようとする課題】**

50

## 【0007】

本願発明は、上記問題点を解決するものであり、積層セラミックコンデンサの実装時および実装後の熱的、機械的応力の集中などにより、外部電極端部付近からクラックが発生した場合にも、クラックが内部電極にまで達することを防止して、所望の特性を確保することが可能な信頼性の高い積層セラミックコンデンサを提供することを課題とする。

## 【課題を解決するための手段】

## 【0008】

上記課題を解決するために、本願発明（請求項1）の積層セラミックコンデンサは、セラミック素子と、セラミック素子の端面および該端面に連続する側面の両端部に形成された外部電極を具備する積層セラミックコンデンサにおいて、

セラミック素子が、セラミック層を介して、複数の内部電極が互いに対向するように配設された内部電極配設部と、内部電極配設部の上側および下側に配設されたセラミック層である上側外層部および下側外層部とを備え、

少なくとも実装時に下側になる下側外層部には、積層セラミックコンデンサの機能に影響を与えないダミー電極が配設され、かつ、

前記内部電極の、前記セラミック素子の端面への引き出し位置のうち、実装時に最も下側になる引き出し位置から、当該端面に形成され、実装時に下面側となる前記セラミック素子の側面にまで回り込んだ前記外部電極の先端まで仮想線を引いた場合に、前記下側外層部に配設された前記ダミー電極の先端が、前記仮想線と当該外部電極により規定される領域の外側から前記仮想線と接する位置に達するか、または、前記仮想線と交差し、前記仮想線と当該外部電極により規定される領域にまで達しており、実装状態で積層セラミックコンデンサに応力が加わった場合に前記下側外層部に発生するクラックを通過させるクラック誘導経路が形成され、前記クラックが積層セラミックコンデンサの機能に影響を与える内部電極を切断することなく、前記下側外層部を通過するように構成されていることを特徴としている。

## 【0009】

また、請求項2の積層セラミックコンデンサは、前記ダミー電極がセラミックグリーンシート層を介して積層された複数のダミー電極層から構成されており、かつ、前記下側外層部に積層されたダミー電極のうち、積み重ね方向における最も上側の、内部電極に最も近接したダミー電極の先端が、前記仮想線と接する位置に達するか、または、前記仮想線と交差し、前記仮想線と当該外部電極により規定される領域にまで達していることを特徴としている。

## 【0010】

また、請求項3の積層セラミックコンデンサは、前記ダミー電極がセラミックグリーンシート層を介して積層された複数のダミー電極層から構成されており、かつ、前記下側外層部に積層されたダミー電極のうち、積み重ね方向における最も下側の、内部電極から最も離れたダミー電極の先端が、前記仮想線と接する位置に達するか、または、前記仮想線と交差し、前記仮想線と当該外部電極により規定される領域にまで達していることを特徴としている。

## 【0011】

また、請求項4記載の積層セラミックコンデンサは、前記ダミー電極がセラミックグリーンシート層を介して積層された複数のダミー電極層から構成されており、かつ、前記下側外層部に積層されたすべてのダミー電極の先端が、前記仮想線と接する位置に達するか、または、前記仮想線と交差し、前記仮想線と当該外部電極により規定される領域にまで達していることを特徴としている。

## 【0012】

また、請求項5の積層セラミックコンデンサは、前記ダミー電極がセラミックグリーンシート層を介して積層された複数のダミー電極層から構成されており、かつ、前記下側外層部に積層されたダミー電極の、積み重ね方向における最も上側の、内部電極に最も近接したダミー電極のほうが、積み重ね方向における最も下側の、内部電極から最も離れたダ

10

20

30

40

50

ミー電極よりも長いことを特徴としている。

【0013】

また、請求項6の積層セラミックコンデンサは、前記ダミー電極がセラミックグリーンシート層を介して積層された複数のダミー電極層から構成されており、実装時に上方に位置するダミー電極層ほど、先端が外部電極に近い位置まで達するように構成されていることを特徴としている。

【0014】

また、請求項7の積層セラミックコンデンサは、(a)少なくとも一方の先端部が前記仮想線と当該外部電極により規定される領域内に達する前記ダミー電極と、(b)一端側が前記ダミー電極の前記領域に達する先端部との間に所定の隙間が形成される位置にまで達し、他端側が外部電極に接続されるような態様で、前記仮想線と当該外部電極により規定される領域に配設された外部電極側ダミー電極とを備え、

10

前記ダミー電極と、前記外部電極側ダミー電極との隙間が、前記クラックが通過するクラック誘導経路となるように構成されていること

を特徴としている。

【発明の効果】

【0015】

本願発明(請求項1)の積層セラミックコンデンサは、セラミック素子が、内部電極配設部と、内部電極配設部の上側および下側に配設された上側外層部および下側外層部とを備え、実装時に下側になる下側外層部に、積層セラミックコンデンサの機能に影響を与えないダミー電極を配設し、かつ、内部電極の、セラミック素子の端面への引き出し位置のうち、実装時に最も下側になる引き出し位置から、当該端面に形成され、実装時に下面側となるセラミック素子の側面にまで回り込んだ外部電極の先端まで仮想線を引いた場合に、ダミー電極の先端が、仮想線と外部電極により規定される領域の外側から仮想線と接する位置に達するか、または、仮想線と交差し、仮想線と当該外部電極により規定される領域にまで達しているので、実装状態で積層セラミックコンデンサに応力が加わった場合に下側外層部に発生するクラックを通過させるクラック誘導経路を形成して、クラックが積層セラミックコンデンサの機能に影響を与える内部電極を切断することなく、下側外層部を通過させることができることになる。

20

【0016】

すなわち、本願請求項1の積層セラミックコンデンサにおいては、ダミー電極により、クラックを通過させるクラック誘導経路を形成するようにしているので、積層セラミックコンデンサに応力が加わった場合に発生するクラックを、積層セラミックコンデンサの機能に影響を与える内部電極を切断しない領域に導くことが可能になり、実装時および実装後の熱的、機械的応力の集中などによりセラミック素子にクラックが発生した場合にも、特性が損なわれることがなく、信頼性の高い積層セラミックコンデンサを提供することが可能になる。

30

【0017】

また、請求項2の積層セラミックコンデンサのように、ダミー電極を複数のダミー電極層から構成し、下側外層部に積層されたダミー電極のうち、積み重ね方向における最も上側の、内部電極に最も近接したダミー電極の先端が、仮想線と接する位置に達するか、または、仮想線と交差し、仮想線と当該外部電極により規定される領域にまで達するようにした場合、実装状態で積層セラミックコンデンサに応力が加わった場合に発生するクラックを、積層セラミックコンデンサの機能に影響を与える内部電極を切断しない領域に確実に導くことが可能になり、実装時および実装後の熱的、機械的応力の集中などによりセラミック素子にクラックが発生した場合にも、特性が損なわれることがなく、信頼性の高い積層セラミックコンデンサを提供することが可能になる。

40

【0018】

なお、この請求項2の積層セラミックコンデンサにおいては、少なくとも、積み重ね方

50

向における最も上側のダミー電極（セラミック素子の表面から最も遠いダミー電極）により、積層セラミックコンデンサの機能に影響を与える内部電極を切断しない領域にクラックを確実に導くことが可能になる。

#### 【0019】

また、請求項3の積層セラミックコンデンサのように、ダミー電極を複数のダミー電極層から構成し、かつ、下側外層部に積層されたダミー電極のうち、積み重ね方向における最も下側の、内部電極から最も離れたダミー電極の先端が、仮想線と接する位置に達するか、または、仮想線と交差し、仮想線と当該外部電極により規定される領域にまで達するようにした場合にも、実装状態で積層セラミックコンデンサに応力が加わった場合に発生するクラックを、積層セラミックコンデンサの機能に影響を与える内部電極を切断しない領域に確実に導くことが可能になり、実装時および実装後の熱的、機械的応力の集中などによりセラミック素子にクラックが発生した場合にも、特性が損なわれることがなく、信頼性の高い積層セラミックコンデンサを提供することが可能になる。10

#### 【0020】

なお、この請求項3の積層セラミックコンデンサにおいては、少なくとも、積み重ね方向における最も下側のダミー電極（セラミック素子の表面に最も近いダミー電極）により、積層セラミックコンデンサの機能に影響を与える内部電極を切断しない領域にクラックを確実に導くことが可能になる。

#### 【0021】

また、請求項4の積層セラミックコンデンサのように、ダミー電極を複数のダミー電極層から構成し、かつ、下側外層部に積層されたすべてのダミー電極の先端が、仮想線と接する位置に達するか、または、仮想線と交差し、仮想線と当該外部電極により規定される領域にまで達するようにした場合、複数層のダミー電極のそれぞれにより、さらに確実に、クラックを積層セラミックコンデンサの機能に影響を与える内部電極を切断しない領域に導くことが可能になる。20

#### 【0022】

また、請求項5の積層セラミックコンデンサのように、ダミー電極を複数のダミー電極層から構成し、かつ、下側外層部に積層されたダミー電極の、積み重ね方向における最も上側の、内部電極に最も近接したダミー電極を、積み重ね方向における最も下側の、内部電極から最も離れたダミー電極よりも長くした場合、少なくとも、内部電極に最も近接したダミー電極により、クラックを積層セラミックコンデンサの機能に影響を与える内部電極を切断しない領域に導くことが可能になる。30

#### 【0023】

また、請求項6の積層セラミックコンデンサのように、ダミー電極を、セラミックグリーンシート層を介して積層された複数のダミー電極層から構成し、実装時に上方に位置するダミー電極層ほど、先端が外部電極に近い位置まで達するように構成することにより、さらに確実にクラックを積層セラミックコンデンサの機能に影響を与える内部電極を切断しない領域に導くことが可能になり、本願発明を実効あらしめることが可能になる。

#### 【0024】

また、請求項7の積層セラミックコンデンサのように、少なくとも一方の先端部が前記仮想線と当該外部電極により規定される領域内に達するダミー電極と、一端側が前記ダミー電極の前記領域に達する先端部との間に所定の隙間が形成される位置にまで達し、他端側が外部電極に接続されるような態様で、前記仮想線と当該外部電極により規定される領域に配設された外部電極側ダミー電極とを備えた構成とし、ダミー電極と、外部電極側ダミー電極との隙間を、クラックが通過するクラック誘導経路とした場合、さらに確実にクラックの通過するクラック誘導経路を所望の位置に形成することが可能になる。40

なお、ダミー電極は、両方の先端部が前記仮想線と当該外部電極により規定される領域内に達するように構成されていてもよく、一方の先端部のみが前記仮想線と当該外部電極により規定される領域内に達し、他方は外部電極に接続された構成とすることも可能である。また、ダミー電極および外部電極側ダミー電極の配設数に制約はなく、一つまたは二50

つ以上の任意のダミー電極および外部電極側ダミー電極を配設することが可能である。

**【発明を実施するための最良の形態】**

**【0025】**

以下に本願発明の実施例を示して、本願発明の特徴とするところをさらに詳しく説明する。

**【実施例】**

**【0026】**

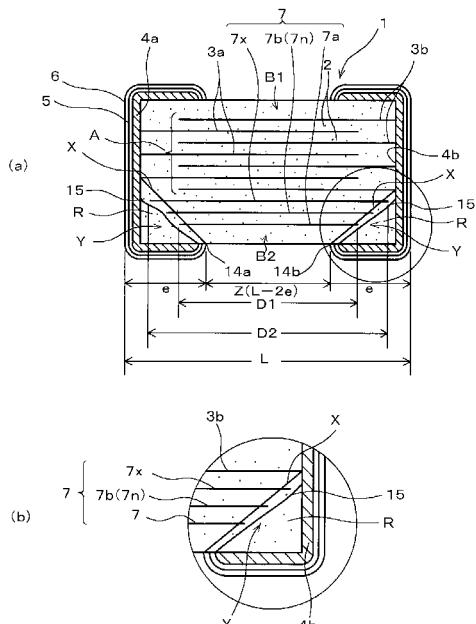

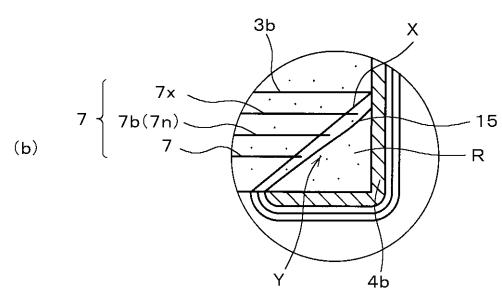

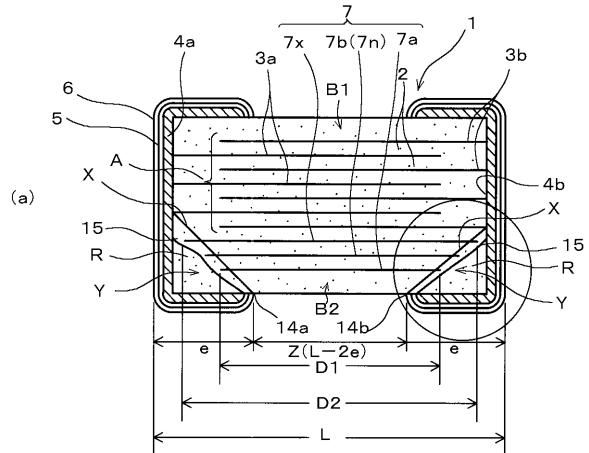

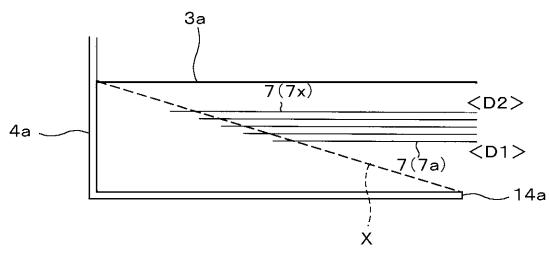

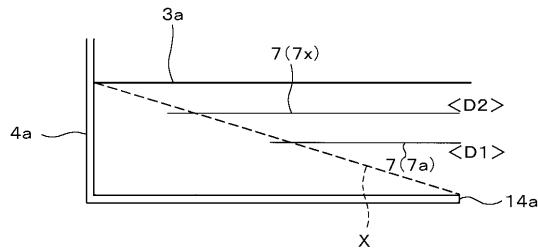

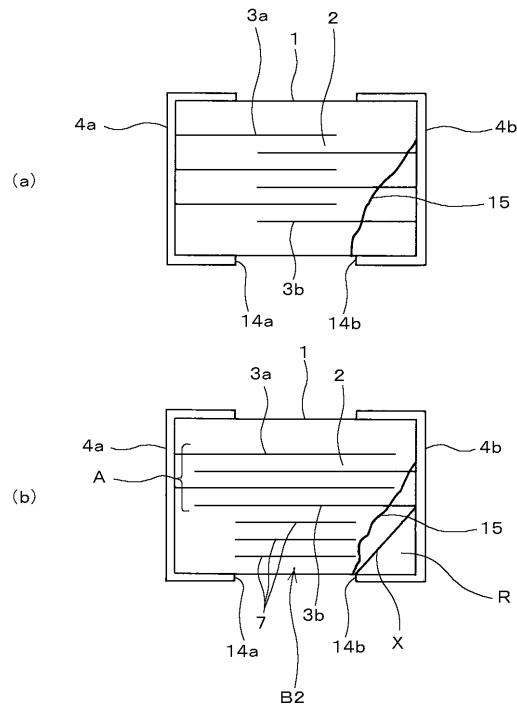

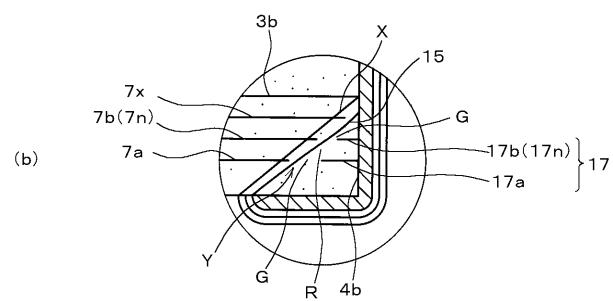

図1(a)は、本願発明の一実施例にかかる積層セラミックコンデンサを示す断面図、図1(b)は要部を拡大して示す図である。

この積層セラミックコンデンサは、複数の内部電極3a, 3bがセラミック層2を介して互いに対向するように配設され、かつ、その一端側が交互に異なる側の端面に引き出されたセラミック素子1の両端側に、内部電極3a, 3bと導通するように一对の外部電極4a, 4bが配設され、外部電極4a, 4bの表面には、はんだくわれを防止するためのNiめっき膜5が形成され、その表面にはんだ付け性を向上させるためのSnめっき膜6が形成された構造を有している。

**【0027】**

そして、セラミック素子1は、セラミック層2を介して、複数の内部電極3a, 3bが互いに対向するように配設された内部電極配設部Aと、内部電極配設部Aの上側および下側に配設されたセラミック層である上側外層部B1および下側外層部B2とを備えており、実装時に下側になる下側外層部B2には、外部電極4a, 4bに接続されず、製品である積層セラミックコンデンサの機能に影響を与えないダミー電極7が配設されている。

**【0028】**

ダミー電極7は、内部電極3a, 3bの、セラミック素子1の端面への引き出し位置のうち、実装時に最も下側になる引き出し位置から、当該端面に形成され、実装時に下面側となるセラミック素子1の下面側となる側面にまで回り込んだ外部電極4a, 4bの先端14a, 14bまで仮想線Xを引いた場合に、実装時に下側になる下側外層部B2に配設されたダミー電極7が仮想線Xと交差し、その先端が仮想線Xと当該外部電極4a, 4bにより規定される領域Rにまで達している。

**【0029】**

なお、図1に示す実施例では、ダミー電極7は、複数のダミー電極層7a, 7b(7n), ..., 7xから構成されており(図1(a), (b)では3層のダミー電極層を示しているが、実際には5層のダミー電極層を備えている)、実装時に下方に位置することになるダミー電極層7aから、上方に位置することになるダミー電極層7b(7n), ..., 7xの順に、長さが長くなるように構成されている。

また、ダミー電極7は、その両端部が外部電極4a, 4bに接続されていない浮遊電極となっている。

**【0030】**

この実施例のような態様でダミー電極7(ダミー電極層7a, 7b(7n), ..., 7x)を配設した積層セラミックコンデンサにおいては、ダミー電極7によりクラック誘導経路Y(図1(b))が形成されており、例えば、積層セラミックコンデンサを回路基板上に実装した状態で、リフロー炉はんだ付けの方法により積層セラミックコンデンサを実装した場合、はんだフィレットが熱収縮する際の応力により、セラミック素子1の外部電極4a, 4bが配設された端部近傍にクラックが発生したとしても、そのクラック15を、クラック誘導経路Y(図1(b))に導いて、クラック15が積層セラミックコンデンサの機能に影響を与える内部電極3a, 3bを切斷することなく、下側外層部B2を通過することになり、積層セラミックコンデンサの機能に影響が出ることを防止することができる。

**【0031】**

次に、上記積層セラミックコンデンサの製造方法について説明する。

(1)まず、 $BaTiO_3$ ,  $BaCO_3$ ,  $MgO$ ,  $Dy_2O_3$ ,  $MnCO_3$ ,  $SiO_2$ からなるセラミックス混合粉末に、バインダ、可塑剤、および有機溶剤を加え、混合することによ

10

20

30

40

50

りセラミックスラリーを得た。

【0032】

(2) それから、このセラミックスラリーを使用し、厚み $13\text{ }\mu\text{m}$ のセラミックグリーンシートを作製した。

【0033】

(3) そして、このセラミックグリーンシート上に、内部電極(容量形成用の内部電極およびダミー電極)形成用のNi粉末を導電成分とする導電性ペーストを塗布し、乾燥した後、セラミックグリーンシートを所定枚数積層し、さらにその上下両面側に、内部電極が形成されていないセラミックグリーンシート(ダミーシート)を積層、圧着してマザー積層体を形成した。

10

【0034】

(4) それから、得られたマザー積層体をカットして個々の素子に分割した後、焼成することにより、複数の内部電極3a, 3bがセラミック層2を介して互いに対向するように配設され、その一端側が交互に異なる側の端面に引き出されているとともに、図1(a), (b)に示すような態様でダミー電極が配設された積層セラミックコンデンサ素子(未焼成のセラミック素子1)を得た。

【0035】

(5) 次に、得られた未焼成の積層セラミックコンデンサ素子(セラミック素子)を、大気中280℃に加熱することによりバインダの燃焼、分解を行い、次にN<sub>2</sub>、H<sub>2</sub>、およびH<sub>2</sub>Oからなる所定の雰囲気中で、1200℃、2時間の焼成を行った。

20

【0036】

(6) そして、得られたセラミックス焼結体(セラミック素子)1をバレル研磨した後、外部電極形成用の、Cu粉末を導電成分とする導電性ペーストを塗布して焼き付けることにより外部電極4a, 4bを形成した後、その表面にNiめっき、Snめっきを施し、Niめっき膜5およびSnめっき膜6を形成することにより、図1(a), (b)に示すような構造を有する積層セラミックコンデンサ(実施例1の試料)を得た。

【0037】

なお、積層セラミックコンデンサの寸法は、長さL:3.2mm、幅W:1.6mm、厚さT:1.15mmとした。また、内部電極3a, 3bの厚みは $1\text{ }\mu\text{m}$ 、内部電極3a, 3b間に存在するセラミック層(誘電体層)の厚みは平均 $10\text{ }\mu\text{m}$ とした。

30

この積層セラミックコンデンサ(実施例1の試料)のその他の条件については表1に示す。

表1において、外部電極回り込み部分の長さeは、図1において、外部電極4a, 4bの、セラミック素子1の側面にまで回り込んだ部分の距離(e)(mm)を示している。

また、外部電極端間距離Z(L-2e)は、図1において、セラミック素子1の側面に回り込んだ外部電極4a, 4bの先端14aと14bの間の距離(Z)(mm)を示している。

また、ダミー電極最外層長さD1は、複数のダミー電極層7a, 7b……のうち、最もセラミック素子1の下面に近い(内部電極から離れた)ダミー電極7aの長さ(D1)の値(mm)を示している。

40

また、ダミー電極最内層長さD2は、ダミー電極層7a, 7b……7xのうち、最も内部電極配設部Aに近い(上側の)ダミー電極7xの長さ(D2)(mm)を示している。

【0038】

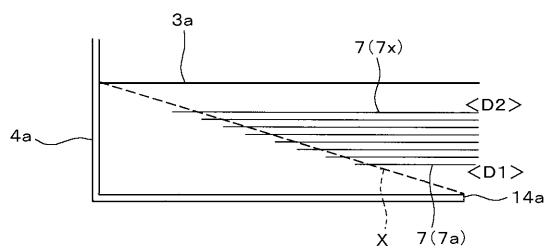

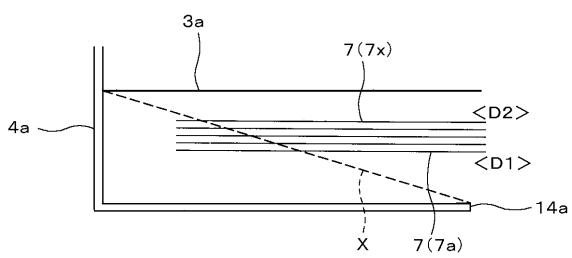

また、同様にして、図3～9および表1～3に示す、実施例2, 実施例3, 実施例4, 実施例5, 実施例6, 実施例7, 実施例8, および実施例9の積層セラミックコンデンサ(試料)を作製した。

【0039】

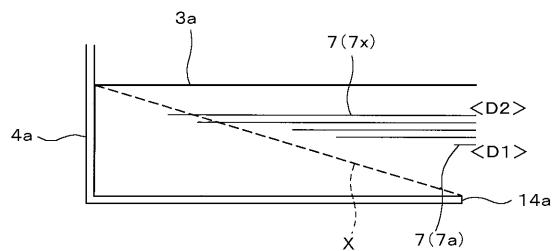

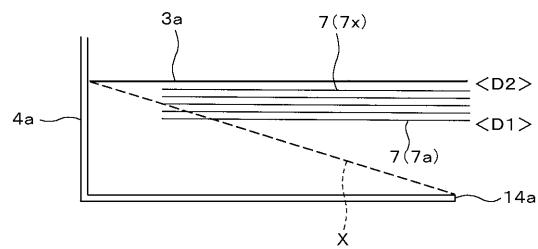

図2～図9は、各実施例の積層セラミックコンデンサの要部構成を示す図である。なお、図2は、比較しやすいように、上述の実施例1に示す積層セラミックコンデンサの要部構成を示したものである。

50

## 【0040】

図3は、実施例2にかかる積層セラミックコンデンサの要部構成を示す図であり、この積層セラミックコンデンサにおいては、ダミー電極7を2層のダミー電極層から構成している。

## 【0041】

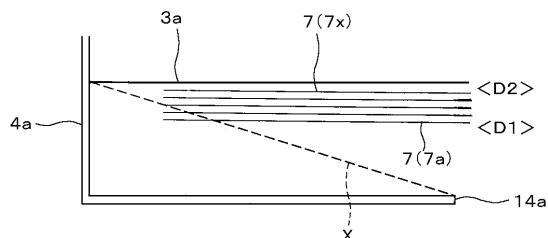

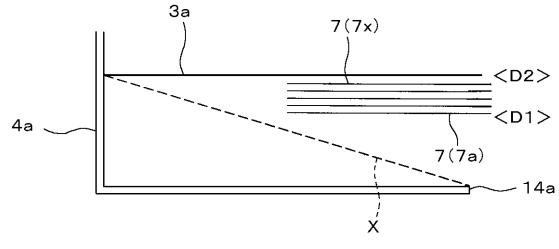

また、図4は、実施例3にかかる積層セラミックコンデンサの要部構成を示す図であり、この積層セラミックコンデンサにおいては、ダミー電極7を8層に増やしている。

なお、上記実施例1～3の積層セラミックコンデンサはいずれも、複数のダミー電極層が、実装時に上方に位置するダミー電極層ほど、先端が外部電極に近い位置まで達するよう構成されており、かつ、各ダミー電極層の両側の先端はそれぞれ仮想線と交差し、仮想線と当該外部電極により規定される領域にまで達している。

10

## 【0042】

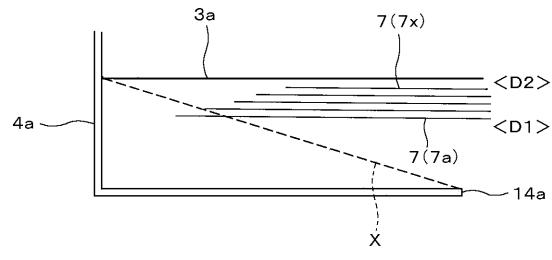

また、図5は、実施例4にかかる積層セラミックコンデンサの要部構成を示す図であり、この積層セラミックコンデンサにおいては、複数(5層)のダミー電極7のうち上側の2層のみ、両側の先端が仮想線Xと交差し、他のダミー電極7は仮想線Xと交差しないように構成されている。

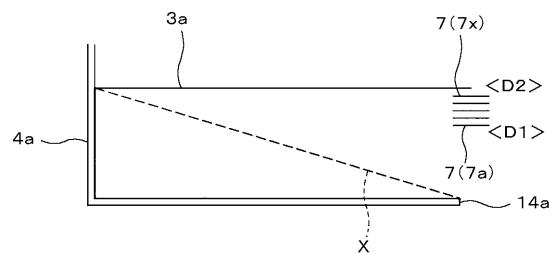

## 【0043】

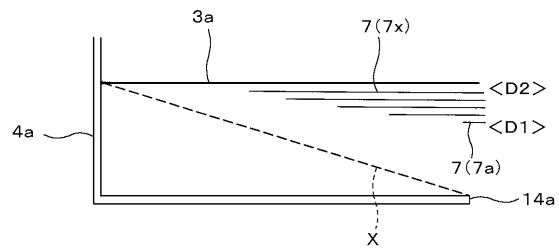

また、図6は、実施例5にかかる積層セラミックコンデンサの要部構成を示す図であり、この積層セラミックコンデンサにおいては、複数(5層)のダミー電極7はすべて長さが同じで、いずれのダミー電極7も両端部が仮想線Xと交差している。

20

また、実施例6の積層セラミックコンデンサは、ダミー電極の一方の端部が外部電極に接続され、他方の端部のみが浮いたいわゆる片側ダミー電極である。ダミー電極の外部電極に接続されていない方の先端は、仮想線Xと交差するよう構成されており、この構成は、実施例5の積層セラミックコンデンサのダミー電極の先端が仮想線Xと交差している状態を示す図6の場合と同様であるので、特に図示していない。

10

## 【0044】

また、図7は、実施例7にかかる積層セラミックコンデンサの要部構成を示す図であり、この積層セラミックコンデンサにおいては、複数(5層)のダミー電極7と内部電極3a(3b)の距離が、実施例1～実施例6よりも小さくなっているとともに、下側の3層のダミー電極7が、仮想線Xにまで達するか、仮想線Xと交差するよう構成されている。また、この実施例7のダミー電極7は一方の端部が外部電極に接続され、他方の端部のみが浮いたいわゆる片側ダミー電極であり、ダミー電極7の図7に示されていない方の端部は外部電極に接続されている。

30

## 【0045】

また、また、図8は、実施例8にかかる積層セラミックコンデンサの要部構成を示す図であり、この積層セラミックコンデンサにおいては、複数(5層)のダミー電極7と内部電極3a(3b)の距離が、実施例1～実施例6よりも小さくなっているとともに、内部電極3a(3b)に近いダミー電極7ほど、長さが短くなってしまい、下側の2層のダミー電極7のうち、上側のダミー電極7の両側の先端が仮想線Xにまで達し、下側のダミー電極7の両側の先端が仮想線Xと交差するよう構成されている。

40

## 【0046】

また、図9は、実施例9にかかる積層セラミックコンデンサの要部構成を示す図であり、この積層セラミックコンデンサにおいては、複数(5層)のダミー電極7と内部電極3a(3b)の距離が、実施例1～実施例6よりも小さくなっているとともに、ダミー電極7はいずれも長さが同じであり、下側の3層のうち、上側のダミー電極7の両側の先端が仮想線Xにまで達し、下側の2層のダミー電極7の両側の先端が仮想線Xと交差するよう構成されている。

## 【0047】

また、比較のため、図10～12に示すような比較例1，2，3の積層セラミックコンデンサを作製した。

50

**【 0 0 4 8 】**

図10は、比較例1の積層セラミックコンデンサの要部構成を示す図であり、この積層セラミックコンデンサにおいては、複数(5層)のダミー電極7と内部電極3a(3b)の距離が、実施例1～実施例6よりも小さくなっており、かつ、ダミー電極7は長さが短く、すべてのダミー電極7は仮想線Xに達していない。

**【 0 0 4 9 】**

また、図11は、比較例2の積層セラミックコンデンサの要部構成を示す図であり、この積層セラミックコンデンサは、複数(5層)のダミー電極7と内部電極3a(3b)の距離が、実施例1～実施例6よりも小さくなっており、各ダミー電極7はすべて長さが同じで、いずれのダミー電極7も仮想線Xに達していない。また、この比較例2のダミー電極7は一方の端部が外部電極に接続され、他方の端部のみが浮いたいわゆる片側ダミー電極であり、ダミー電極7の図11に示されていない方の端部は外部電極に接続されている。

10

**【 0 0 5 0 】**

また、図12は、比較例3の積層セラミックコンデンサの要部構成を示す図であり、この積層セラミックコンデンサは、複数(5層)のダミー電極7と内部電極3a(3b)の距離が、実施例1～実施例6よりも小さくなっており、各ダミー電極7はすべて長さが同じで、いずれのダミー電極7も仮想線Xに達していない。

**【 0 0 5 1 】**

また、比較のため、ダミー電極を備えていない従来の積層セラミックコンデンサ(従来例1)を作製した。

20

**【 0 0 5 2 】**

それから、上述のようにして作製した各積層セラミックコンデンサにつき、実装時の静電容量低下の程度を比較するため、たわみ強度試験を行った。なお、たわみ強度試験は、JIS-C6429に準じて行った。

たわみ強度試験では、基板としてガラスエポキシ基板を用い、リフロー炉はんだ付け、加圧速度1mm/秒の条件で基板をたわませ、静電容量が-12.5%低下時の基板変位量をたわみ量とした(n=20ヶ)。

**【 0 0 5 3 】**

また、得られた積層セラミックコンデンサの熱応力に対する信頼性を確認するため、はんだ耐熱試験を行った。

30

はんだ耐熱試験は、積層セラミックコンデンサをはんだに浸漬しその際のショート発生率を比較した。なお、はんだ耐熱試験は、はんだ温度：室温+350、はんだ浸漬速度：40mm/秒、浸漬時間：3秒、n=50ヶの条件で行った。

**【 0 0 5 4 】**

その結果を表1、表2、表3、表4に示す。

**【 0 0 5 5 】**

【表1】

| 条件                                      | 実施例1         | 実施例2         | 実施例3         | 実施例4         |

|-----------------------------------------|--------------|--------------|--------------|--------------|

|                                         | ダミー有り        | ダミー有り        | ダミー有り        | ダミー有り        |

|                                         | 浮遊電極         | 浮遊電極         | 浮遊電極         | 浮遊電極         |

| 外層部厚み(μm)                               | 150          | 150          | 150          | 150          |

| セラミック層厚み(μm)                            | 9            | 9            | 9            | 9            |

| 積層数(枚)                                  | 85           | 85           | 85           | 85           |

| 製品サイズ<br>L*W*T(mm)                      | 3.2*1.6*1.15 | 3.2*1.6*1.15 | 3.2*1.6*1.15 | 3.2*1.6*1.15 |

| 外部電極回り込み部分の長さe(mm)                      | 0.50         | 0.50         | 0.50         | 0.50         |

| 外部電極端間距離Z(L-2e)(mm)                     | 2.20         | 2.20         | 2.20         | 2.20         |

| ダミー電極最外層長さD1(mm)                        | 2.70         | 2.70         | 2.50         | 2.20         |

| ダミー電極最内層長さD2(mm)                        | 3.00         | 3.00         | 3.00         | 3.00         |

| ダミー電極層数(枚)                              | 5            | 2            | 8            | 5            |

| 内部電極とダミー電極の間のセラミック層数(枚)                 | 3            | 3            | 3            | 3            |

| たわみ強度(平均値)(mm)(n=20)                    | 6.5          | 6.0          | 6.8          | 5.7          |

| たわみ強度(最小値)(mm)(n=20)                    | 4.5          | 4.0          | 4.9          | 4.0          |

| はんだ耐熱試験<br>ショット発生率(%)<br>ΔT=350°C(n=50) | 0.0          | 0.0          | 0.0          | 0.0          |

| D1とD2の長さの比                              | D1<D2        | D1<D2        | D1<D2        | D1<D2        |

| D1の端部が仮想線に達しているか                        | ○            | ○            | ○            | ×            |

| D2の端部が仮想線に達しているか                        | ○            | ○            | ○            | ○            |

【0056】

【表2】

| 条件                                                              | 実施例5         | 実施例6         | 実施例7         | 実施例8         |

|-----------------------------------------------------------------|--------------|--------------|--------------|--------------|

|                                                                 | ダミー有り        | ダミー有り        | ダミー有り        | ダミー有り        |

|                                                                 | 浮遊電極         | 片側電極         | 片側電極         | 浮遊電極         |

| 外層部厚み(μm)                                                       | 150          | 150          | 150          | 150          |

| セラミック層厚み(μm)                                                    | 9            | 9            | 9            | 9            |

| 積層数(枚)                                                          | 85           | 85           | 85           | 85           |

| 製品サイズ<br>L*W*T(mm)                                              | 3.2*1.6*1.15 | 3.2*1.6*1.15 | 3.2*1.6*1.15 | 3.2*1.6*1.15 |

| 外部電極回り込み部分の長さe(mm)                                              | 0.50         | 0.50         | 0.50         | 0.50         |

| 外部電極端間距離Z<br>(L-2e)(mm)                                         | 2.20         | 2.20         | 2.20         | 2.20         |

| ダミー電極最外層長さ<br>D1(mm)                                            | 3.00         | 3.00         | 3.00         | 3.00         |

| ダミー電極最内層長さ<br>D2(mm)                                            | 3.00         | 3.00         | 3.00         | 2.70         |

| ダミー電極層数(枚)                                                      | 5            | 5            | 5            | 5            |

| 内部電極とダミー電極の間のセラミック層数(枚)                                         | 3            | 3            | 0            | 0            |

| たわみ強度(平均値)<br>(mm) (n=20)                                       | 6.2          | 5.1          | 3.6          | 3.6          |

| たわみ強度(最小値)<br>(mm) (n=20)                                       | 4.2          | 3.5          | 2.7          | 2.6          |

| はんたん耐熱試験<br>ショット発生率(%)<br>$\Delta T=350^{\circ}\text{C}$ (n=50) | 0.0          | 0.0          | 2.0          | 4.0          |

| D1とD2の長さの比                                                      | D1=D2        | D1=D2        | D1=D2        | D1>D2        |

| D1の端部が仮想線に達しているか                                                | ○            | ○            | ○            | ○            |

| D2の端部が仮想線に達しているか                                                | ○            | ○            | ×            | ×            |

【0057】

【表3】

| 条件                                                             | 実施例9         | 従来例1         |

|----------------------------------------------------------------|--------------|--------------|

|                                                                | ダミー有り        | ダミーなし        |

|                                                                | 浮遊電極         |              |

| 外層部厚み(μm)                                                      | 150          | 150          |

| セラミック層厚み<br>(μm)                                               | 9            | 9            |

| 積層数(枚)                                                         | 85           | 85           |

| 製品サイズ<br>L*W*T(mm)                                             | 3.2*1.6*1.15 | 3.2*1.6*1.15 |

| 外部電極回り込み部分の長さ e(mm)                                            | 0.50         | 0.50         |

| 外部電極端間距離 Z<br>(L-2e)(mm)                                       | 2.20         | 2.20         |

| ダミー電極最外層長さ<br>D1(mm)                                           | 3.00         | -            |

| ダミー電極最内層長さ<br>D2(mm)                                           | 3.00         | -            |

| ダミー電極層数<br>(枚)                                                 | 5            | -            |

| 内部電極とダミー電極<br>の間のセラミック層数(枚)                                    | 0            | -            |

| たわみ強度(平均値)<br>(mm) (n=20)                                      | 3.5          | 2.8          |

| たわみ強度(最小値)<br>(mm) (n=20)                                      | 2.5          | 2.1          |

| はんだ耐熱試験<br>ショット発生率(%)<br>$\Delta T=350^{\circ}\text{C}$ (n=50) | 4.0          | 8.0          |

| D1 と D2 の長さの比                                                  | D1=D2        | -            |

| D1 の端部が仮想線に<br>達しているか                                          | ○            | -            |

| D2 の端部が仮想線に<br>達しているか                                          | ×            | -            |

10

20

30

40

【0058】

【表4】

| 条件                                                             | 比較例1         | 比較例2         | 比較例3         |

|----------------------------------------------------------------|--------------|--------------|--------------|

|                                                                | ダミ-有り        | ダミ-有り        | ダミ-有り        |

|                                                                | 浮遊電極         | 片側電極         | 浮遊電極         |

| 外層部厚み(μm)                                                      | 150          | 150          | 150          |

| セラミック層厚み(μm)                                                   | 9            | 9            | 9            |

| 積層数(枚)                                                         | 85           | 85           | 85           |

| 製品サイズ<br>L*W*T(mm)                                             | 3.2*1.6*1.15 | 3.2*1.6*1.15 | 3.2*1.6*1.15 |

| 外部電極回り込み部分の長さ e(mm)                                            | 0.50         | 0.50         | 0.50         |

| 外部電極端間距離 Z<br>(L-2e)(mm)                                       | 2.20         | 2.20         | 2.20         |

| ダミ-電極最外層長さ<br>D1(mm)                                           | 2.20         | 2.70         | 2.20         |

| ダミ-電極最内層長さ<br>D2(mm)                                           | 2.80         | 2.70         | 2.20         |

| ダミ-電極層数<br>(枚)                                                 | 5            | 5            | 5            |

| 内部電極とダミ-電極の間のセラミック層数(枚)                                        | 0            | 0            | 0            |

| たわみ強度(平均値)<br>(mm) (n=20)                                      | 2.9          | 3.0          | 2.8          |

| たわみ強度(最小値)<br>(mm) (n=20)                                      | 2.3          | 2.3          | 2.2          |

| はんだ耐熱試験<br>ショット発生率(%)<br>$\Delta T=350^{\circ}\text{C}$ (n=50) | 6.0          | 6.0          | 6.0          |

| D1 と D2 の長さの比                                                  | D1 < D2      | D1 = D2      | D1 = D2      |

| D1 の端部が仮想線に達しているか                                              | ×            | ×            | ×            |

| D2 の端部が仮想線に達しているか                                              | ×            | ×            | ×            |

【0059】

表3から明らかなように、従来例1の積層セラミックコンデンサの場合、たわみ強度が平均値で2.8mmとなっているのに対し、実施例の積層セラミックコンデンサの場合、最も効果の小さい実施例7(図7), 8(図8), 9(図9)の積層セラミックコンデンサ

10

20

30

40

50

でも、たわみ強度は平均値で3.5～3.6mmに向上し、他の実施例1～6(図2～図6)の積層セラミックコンデンサの場合、実施例4(図5)および実施例6の積層セラミックコンデンサでは、たわみ強度が平均値で5mm以上、実施例1、2、3および5の積層セラミックコンデンサ(図2，3，4，6)では、たわみ強度が平均値で6mm以上にまで向上することが確認された。また、ダミー電極は設けているが本願発明の要件を満たしていない比較例1～3の試料の場合、たわみ強度の向上は不十分であることが確認された。

#### 【0060】

また、はんだ耐熱性試験におけるショート発生率についてみた場合、従来例1の積層セラミックコンデンサの場合、ショート発生率が8.0%となっているのに対し、実施例の積層セラミックコンデンサの場合、最も効果の小さい実施例7(図7)，8(図8)，9(図9)の積層セラミックコンデンサでも、ショート発生率は、2.0～4.0%であり、他の実施例1～6(図2～図6)の積層セラミックコンデンサの場合、ショート発生率は0%であり、本願発明の実施例の積層セラミックコンデンサにおいては、優れたはんだ耐熱性が実現されていることが確認された。

#### 【0061】

なお、比較例1～3の試料ではショート発生率が6.0%となっており、必ずしも十分な効果が得られないことが確認された。

#### 【0062】

なお、図13(a)，(b)は、積層セラミックコンデンサへのクラックの発生態様の典型例を模式的に示す図であり、図13(a)は、ダミー電極を備えていない積層セラミックコンデンサ(従来例1)にクラックが発生した状態を示しており、図13(b)は、ダミー電極を配設しているがダミー電極の長さが短く、仮想線Xに達していない積層セラミックコンデンサ(比較例2および3)にクラックが発生した状態を示している。図13(a)，(b)のようにクラックが発生した場合、静電容量不足やショート不良が発生し、製品は不良品となる。なお、図13において、図1と同一符号を付した部分は、同一または相当部分を示している。

#### 【0063】

上述の実施例の結果から、ダミー電極を複数のダミー電極層から構成し、内部電極の、セラミック素子の端面への引き出し位置のうち、実装時に最も下側になる引き出し位置から、当該端面に形成され、実装時に下面側となるセラミック素子の下面側となる側面にまで回り込んだ外部電極の先端まで仮想線を引いた場合に、実装時に下側になる下側外層部に配設されたダミー電極(ダミー電極層)のうち、少なくとも一部のダミー電極層が仮想線に達するか、または仮想線Xと交差するようにした場合、積層セラミックコンデンサの実装時および実装後の熱的、機械的応力の集中により、外部電極端部付近から発生するクラックを、ダミー電極の端部付近の、容量取得用の内部電極を切断しない領域(クラック誘導経路)に導くことが可能になり、静電容量、絶縁抵抗の低下およびショートの発生を抑制し、信頼性の高い積層セラミックコンデンサを得ることが可能になることがわかる。

#### 【0064】

##### [本願発明の他の実施例]

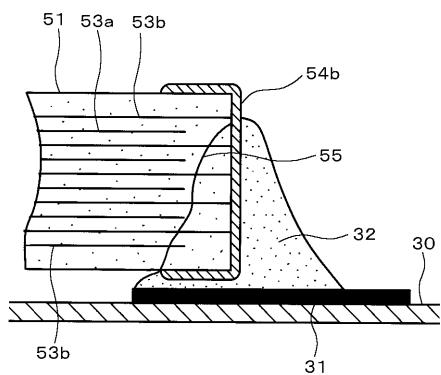

図14(a)，(b)は、本願発明の他の実施例にかかる積層セラミックコンデンサを示す断面図である。なお、図14(a)，(b)において、図1と同一符号を付した部分は、同一または相当部分を示している。

#### 【0065】

この積層セラミックコンデンサは、上記実施例1(図1)の積層セラミックコンデンサと基本的には同様の構成を備えているが、ダミー電極のみではなく、外部電極側ダミー電極を備えている点において構成が異なっている。

すなわち、この積層セラミックコンデンサにおいては、図14に示すように、セラミック素子1の下側外層部B2には、セラミック素子1の下面側から順に3層のダミー電極層7a，7b(7n)……7xが配設されており、このダミー電極層7a，7b(7n)……7xからダミー電極7が構成されている。

10

20

30

40

50

なお、図14では、3層のダミー電極層を持つ場合について説明したが、層数はこれに限られるものではない。

ダミー電極層7a, 7b(7n)……7xは、セラミック素子1の中央側領域に配設され、先端部が仮想線Xと当該外部電極4a, 4bにより規定される領域R内に達している。

また、セラミック素子1の中央側領域に配設されたダミー電極層7a, 7b(7n)の両側には、一端側がダミー電極層7a、および7b(7n)の端部との間に所定の隙間(ギャップ)Gが形成される位置にまで達し、他端側が外部電極4a, 4bに接続されるような態様で、仮想線Xと当該外部電極4a, 4bにより規定される領域Rに配設された外部電極側ダミー電極層17a、および外部電極側ダミー電極層17b(17n)が配設されている。なお、外部電極側ダミー電極層17a, 17b(17n)から外部電極側ダミー電極17が構成されている。

ただし、ダミー電極層7xの両端側には、外部電極側ダミー電極層は配設されていない。

#### 【0066】

この実施例の積層セラミックコンデンサにおいては、セラミック素子1の中央側領域に配設されたダミー電極層7a, 7b(7n)と、その両側に配設された、外部電極側ダミー電極層17a, 17b(17n)の隙間Gがクラック誘導経路Yとして機能することになり、クラック誘導経路Yがより確実に規定されるため、さらに確実にクラックを容量取得用の内部電極を切断しない領域(クラック誘導経路)に導くことが可能になる。

なお、ダミー電極を、一方の先端部のみが仮想線と外部電極により規定される領域内に達し、他方は外部電極に接続された構成とすることも可能である。また、ダミー電極層および外部電極側ダミー電極層の配設数に制約はなく、一つまたは二つ以上の任意のダミー電極および外部電極側ダミー電極層を配設することが可能である。

#### 【0067】

なお、本願発明は、上記の各実施例に限定されるものではなく、ダミー電極および外部電極側ダミー電極層の具体的な形状や積層数、セラミック素子の具体的な構成(内部電極の積層数、下側および上側外層部の厚み、内部電極配設部の厚みなど)、外部電極の具体的な配設態様などに関し、発明の要旨の範囲内において、種々の応用、変形を加えることが可能である。

#### 【産業上の利用可能性】

#### 【0068】

上述のように、本願発明によれば、積層セラミックコンデンサの実装時および実装後の熱的、機械的応力の集中により、外部電極端部付近から発生するクラックを、ダミー電極を配設することにより形成されたクラック誘導経路(例えば、容量取得用の内部電極を切断しない領域)に導くことが可能になり、外部電極端部付近からクラックが発生した場合にも、クラックが内部電極にまで達することを防止して、所望の特性を確保することが可能な信頼性の高い積層セラミックコンデンサを得ることが可能になる。

したがって、本願発明は、セラミック素子中にセラミック層を介して複数の内部電極が積層配設され、かつ、表面に外部電極が形成された構造を有する積層セラミックコンデンサに広く適用することが可能である。

#### 【図面の簡単な説明】

#### 【0069】

【図1】(a)は本願発明の実施例にかかる積層セラミックコンデンサを示す断面図であり、(b)は要部を拡大して示す図である。

【図2】本願発明の実施例1の積層セラミックコンデンサの要部構成を示す図である。

【図3】本願発明の実施例2の積層セラミックコンデンサの要部構成を示す図である。

【図4】本願発明の実施例3の積層セラミックコンデンサの要部構成を示す図である。

【図5】本願発明の実施例4の積層セラミックコンデンサの要部構成を示す図である。

【図6】本願発明の実施例5の積層セラミックコンデンサの要部構成を示す図である。

10

20

30

40

50

【図7】本願発明の実施例7の積層セラミックコンデンサの要部構成を示す図である。

【図8】本願発明の実施例8の積層セラミックコンデンサの要部構成を示す図である。

【図9】本願発明の実施例9の積層セラミックコンデンサの要部構成を示す図である。

【図10】比較例1の積層セラミックコンデンサの要部構成を示す断面図である。

【図11】比較例2の積層セラミックコンデンサの要部構成を示す断面図である。

【図12】比較例3の積層セラミックコンデンサの要部構成を示す断面図である。

【図13】(a), (b)は積層セラミックコンデンサへのクラックの発生態様を示す図である。

【図14】(a)は本願発明の他の実施例にかかる積層セラミックコンデンサを示す断面図であり、(b)は要部を拡大して示す図である。

10

【図15】従来の積層セラミックコンデンサを示す断面図である。

【図16】回路基板上に、従来の積層セラミックコンデンサを実装した状態を示す図である。

【図17】回路基板上に、従来の他の積層セラミックコンデンサを実装した状態を示す図である。

#### 【符号の説明】

##### 【0070】

|                         |                               |  |

|-------------------------|-------------------------------|--|

| 1                       | セラミック素子                       |  |

| 2                       | セラミック層                        |  |

| 3 a , 3 b               | 内部電極                          |  |

| 4 a , 4 b               | 外部電極                          |  |

| 5                       | Niめっき膜                        |  |

| 6                       | Snめっき膜                        |  |

| 7                       | ダミー電極                         |  |

| 7 a , 7 b ( 7 n ) , 7 x | ダミー電極層                        |  |

| 14 a , 14 b             | セラミック素子の側面に回り込んだ外部電極の先端       |  |

| 15                      | クラック                          |  |

| 17                      | 外部電極側ダミー電極                    |  |

| 17 a , 17 b ( 17 n )    | 外部電極側ダミー電極層                   |  |

| A                       | 内部電極配設部                       |  |

| B 1                     | 上側外層部                         |  |

| B 2                     | 下側外層部                         |  |

| D 1                     | ダミー電極最外層長さ                    |  |

| D 2                     | ダミー電極最内層長さ                    |  |

| e                       | 外部電極のセラミック素子の側面への回り込み部分の長さ    |  |

| G                       | 隙間                            |  |

| L                       | セラミック積層素子の長さ                  |  |

| R                       | 仮想線と外部電極により規定される領域            |  |

| X                       | 仮想線                           |  |

| Y                       | クラック誘導経路                      |  |

| Z                       | 外部電極の先端間の距離(外部電極端間距離)(L - 2e) |  |

20

30

40

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】