(19)

OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 885 683**

(51) Int. Cl.:

**H04B 3/30** (2006.01)

**H04L 25/02** (2006.01)

**H04L 25/03** (2006.01)

(12)

## TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Fecha de presentación y número de la solicitud internacional: **28.05.2015 PCT/US2015/032898**

(87) Fecha y número de publicación internacional: **30.12.2015 WO15199883**

(96) Fecha de presentación y número de la solicitud europea: **28.05.2015 E 15730899 (0)**

(97) Fecha y número de publicación de la concesión europea: **23.06.2021 EP 3161969**

---

(54) Título: **Control de sesgo para comunicación trifásica**

(30) Prioridad:

**25.06.2014 US 201462016937 P**

**27.05.2015 US 201514722271**

(45) Fecha de publicación y mención en BOPI de la traducción de la patente:

**15.12.2021**

(73) Titular/es:

**QUALCOMM INCORPORATED (100.0%)**

**5775 Morehouse Drive**

**San Diego, CA 92121-1714, US**

(72) Inventor/es:

**DUAN, YING;**

**DANG, HARRY, HUY y**

**LEE, CHULKYU**

(74) Agente/Representante:

**FORTEA LAGUNA, Juan José**

ES 2 885 683 T3

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

## DESCRIPCIÓN

Control de sesgo para comunicación trifásica

5    **Reivindicación de prioridad**

[0001] La presente solicitud reivindica la prioridad de la solicitud de patente de EE. UU. de n.º de serie 62/016.937 presentada el 25 de junio, de 2014 y titulada "SKEW CONTROL FOR THREE-PHASE COMMUNICATION [CONTROL DE SESGO PARA COMUNICACIÓN TRIFÁSICA]".

10    [0002] La presente solicitud también reivindica la prioridad de la solicitud de patente de EE. UU. de n.º de serie 14/722.271 presentada el 27 de mayo de 2015 y titulada "SKEW CONTROL FOR THREE-PHASE COMMUNICATION [CONTROL DE SESGO PARA COMUNICACIÓN TRIFÁSICA]".

15    **Antecedentes**

I. **Campo de la divulgación**

20    [0003] La tecnología de la divulgación se refiere en general a la admisión de cámaras digitales en dispositivos de comunicación y, más en particular, a la admisión de cámaras digitales que usan la interfaz serie para cámara (CSI) de MIPI® Alliance.

II. **Antecedentes**

25    [0004] Los dispositivos de comunicación móvil se han vuelto cada vez más comunes en la sociedad actual. El predominio de estos dispositivos de comunicación móvil está impulsado en parte por las numerosas funciones que están ahora habilitadas en dichos dispositivos. El incremento de las capacidades de procesamiento en dichos dispositivos significa que los dispositivos de comunicación móvil, inicialmente meras herramientas de comunicación, han evolucionado hasta convertirse en centros de entretenimiento móviles avanzados, que proporcionan de este modo una mayor satisfacción al usuario.

30    [0005] Muchos usuarios finales consideran que la formación de imágenes digitales es una de las características más cruciales en los dispositivos de comunicación móvil. Como resultado, los sensores de cámara digital altamente avanzados se integran en los dispositivos de comunicación móvil para proporcionar una mayor resolución y una mejor sensibilidad en las aplicaciones de formación de imágenes digitales. Después de que se captén las imágenes digitales, los datos digitales sin procesar asociados con las imágenes digitales se transmiten desde el sensor de cámara digital a un procesador de imágenes para un procesamiento y una reproducción adicionales. Debido a que los datos digitales sin procesar se transmiten a través de diversas líneas y/o interfaces de transmisión, los datos digitales sin procesar se pueden distorsionar debido a la interferencia entre símbolos (ISI), reflejos y diafonía causada por líneas de transmisión con pérdidas. A este respecto, los dispositivos de comunicación móvil no pueden producir imágenes digitales de alta calidad a pesar de tener los sensores de cámara digital altamente avanzados. Por consiguiente, es deseable reducir al mínimo las distorsiones causadas por las líneas de transmisión con pérdidas en los dispositivos de comunicación móvil. El documento US 2009/058480 describe un transmisor multífásico configurado para cambiar la impedancia para proporcionar control de sesgo. El documento US 2012/146686 describe un transmisor para reducir pérdidas de señal en las líneas de transmisión detectando una transición en un flujo de datos, ajustar una resistencia de determinación de fuente y obtener una ganancia de la resistencia de determinación de fuente ajustada.

50    **Breve explicación de la divulgación**

[0006] Los aspectos divulgados en la descripción detallada incluyen control de sesgo para la comunicación trifásica. En un ejemplo no limitante, se puede admitir el control de sesgo para la comunicación trifásica en dispositivos de comunicación móvil que usan la especificación de la interfaz serie para cámara trifásica (CSI-3) MIPI® Alliance. Una comunicación trifásica implica tres ramales de señal. Se puede producir un sesgo de señal cuando un ramal de señal se acopla a una tensión de modo común mientras que otro ramal de señal se desacopla de la tensión de modo común. A este respecto, en un aspecto, se introduce una desadaptación de impedancia en el ramal de señal que se acopla a la tensión de modo común para ayudar a desplazar hacia la izquierda un último cruce de la derecha del sesgo de señal. En otro aspecto, una fuente de corriente o un sumidero de corriente se acopla al ramal de señal que se desacopla de la tensión de modo común para ayudar a desplazar hacia la derecha un último cruce de la izquierda del sesgo de señal. Más específicamente, la fuente de corriente o el sumidero de corriente se acoplan al ramal de señal si el ramal de señal se conmuta desde la tensión de modo común a una tensión menor o a una tensión mayor. Al desplazar el último cruce de la derecha hacia la izquierda y el último cruce de la izquierda hacia la derecha, es posible reducir el sesgo de señal, dando lugar por tanto a una fluctuación reducida y una integridad de datos mejorada en la comunicación trifásica.

- 5 [0007] A este respecto, en un aspecto, se proporciona un transmisor trifásico. El transmisor trifásico comprende un primer ramal de señal, un segundo ramal de señal y un tercer ramal de señal. Cada uno del primer ramal de señal, el segundo ramal de señal y el tercer ramal de señal comprende una impedancia de ramal respectiva y una impedancia de excitación respectiva. Si se selecciona un ramal de señal de entre el primer ramal de señal, el segundo ramal de señal y el tercer ramal de señal para que funcione como un ramal de modo común al acoplarse a una tensión de modo común, el transmisor trifásico está configurado para configurar la impedancia de excitación respectiva del ramal de señal seleccionado para que sea menor que la impedancia de ramal respectiva del ramal de señal seleccionado.

- 10 [0008] En otro aspecto, se proporciona un procedimiento para reducir un sesgo de señal en un transmisor trifásico. El procedimiento comprende identificar un ramal de señal de entre un primer ramal de señal, un segundo ramal de señal y un tercer ramal de señal de un transmisor trifásico, en el que el ramal de señal se selecciona para que funcione como un ramal de modo común al acoplarse a una tensión de modo común. El procedimiento también comprende configurar una impedancia de excitación respectiva del ramal de señal seleccionado para que sea menor que una impedancia de ramal respectiva del ramal de señal seleccionado. La presente invención está definida por las reivindicaciones adjuntas y solo está limitada por su alcance.

#### Breve descripción de las figuras

- 20 [0009]

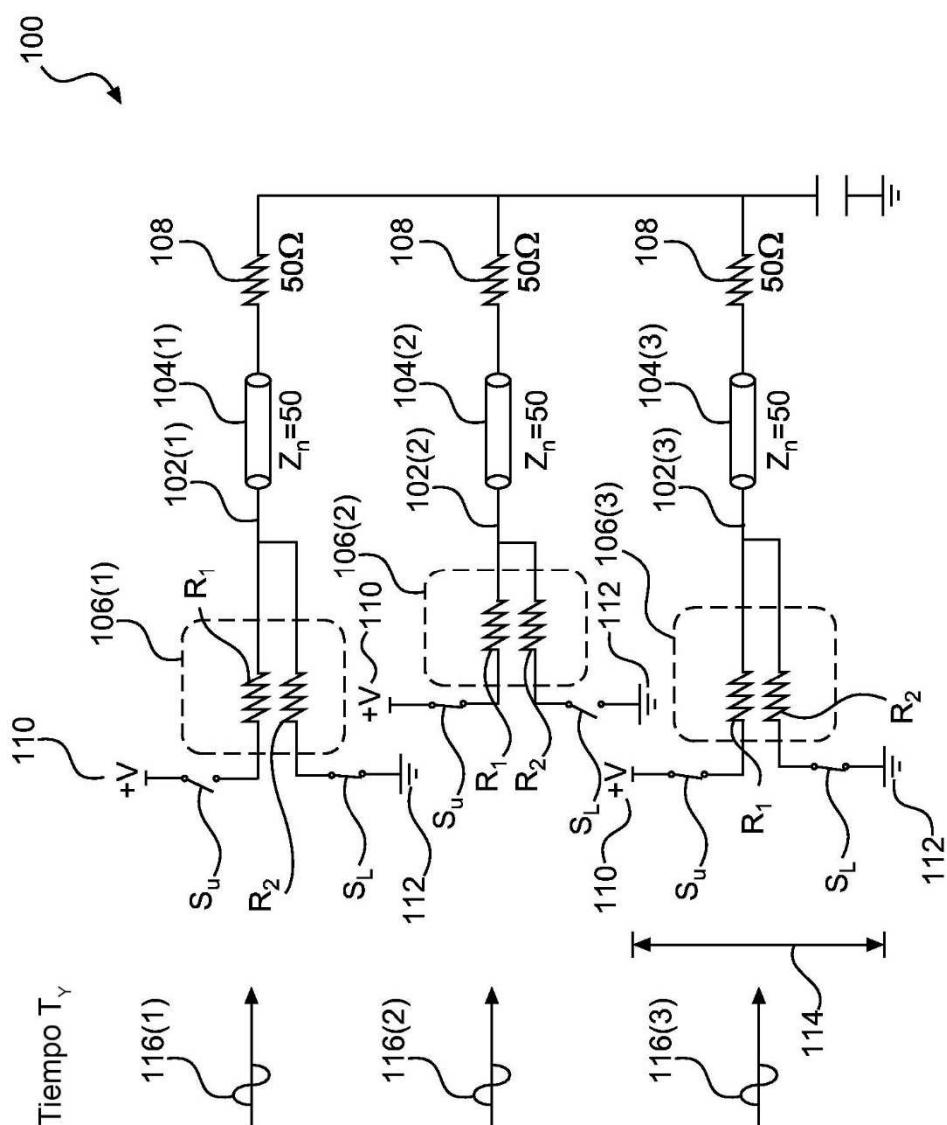

- La figura 1 es un diagrama esquemático de un transmisor trifásico convencional ejemplar de acuerdo con la especificación de interfaz serie para cámara trifásica (CSI-3) MIPI® Alliance;

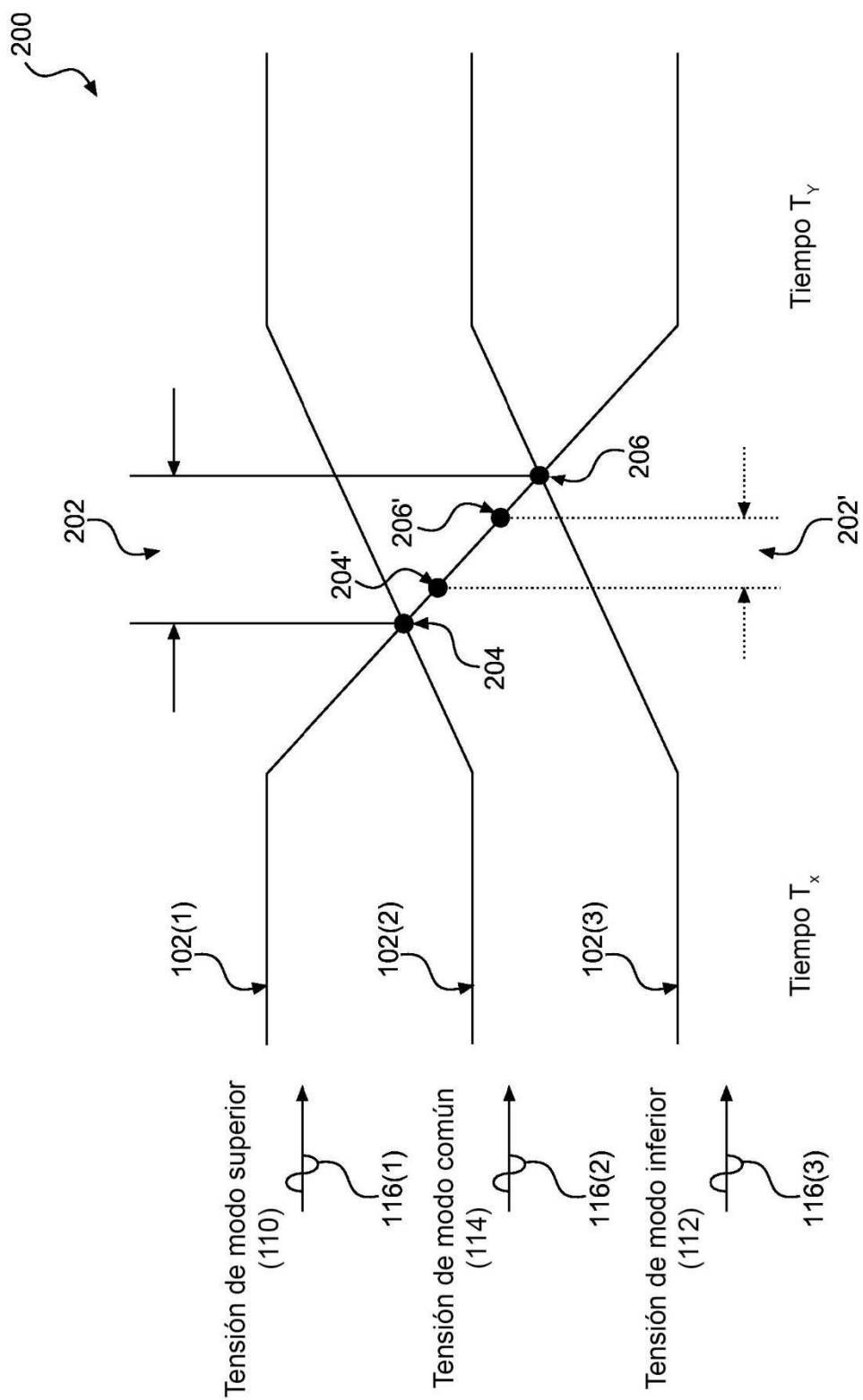

- 25 la figura 2A es un gráfico ejemplar que ilustra un aspecto de un sesgo de señal producido por el transmisor trifásico convencional de la figura 1;

- 30 la figura 2B es un gráfico ejemplar que ilustra otro aspecto del sesgo de señal producido por el transmisor trifásico convencional de la figura 1;

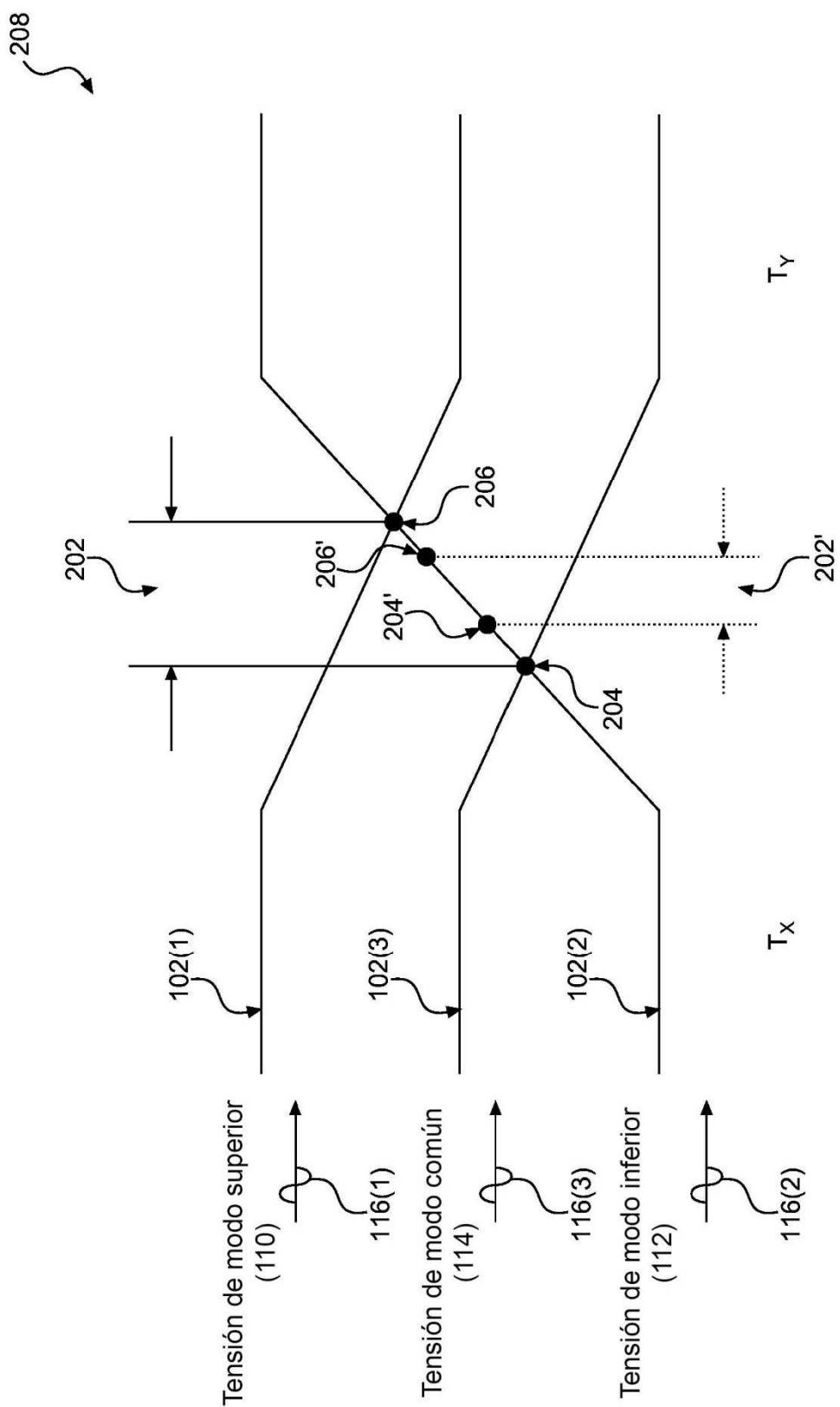

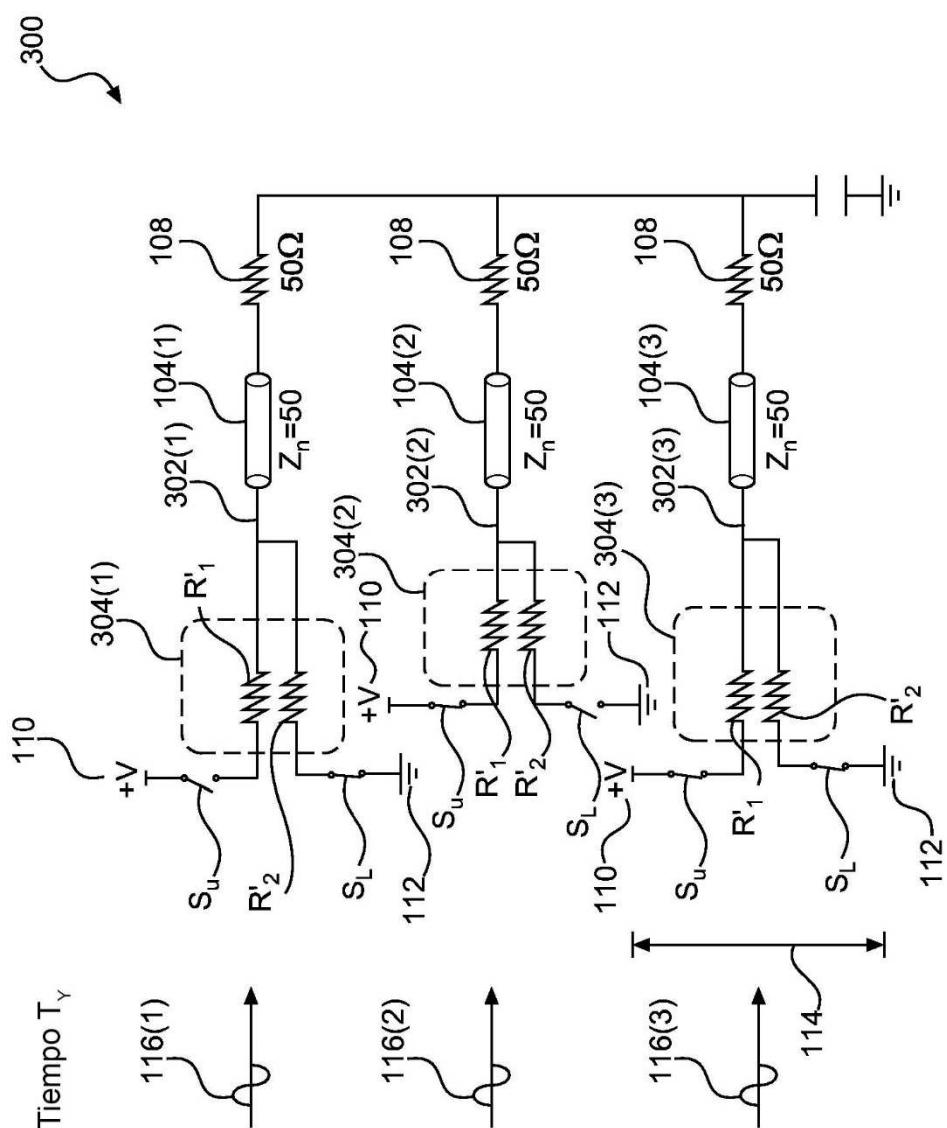

- 35 la figura 3 es un diagrama esquemático de un transmisor trifásico ejemplar configurado para desplazar hacia la izquierda un último cruce de la derecha para reducir el sesgo de señal ilustrado en las figuras 2A y 2B;

- 40 la figura 4 es un diagrama esquemático de un circuito de comunicación trifásico ejemplar que comprende un detector de patrones configurado para desplazar hacia la derecha un último cruce de la izquierda para reducir el sesgo de señal ilustrado en las figuras 2A y 2B;

- 45 la figura 5A es un gráfico ejemplar que ilustra un aspecto de una reducción de sesgo de señal proporcionada por el transmisor trifásico de la figura 3 y el circuito de comunicación trifásico de la figura 4;

- 50 la figura 5B es un gráfico ejemplar que ilustra otro aspecto de la reducción de sesgo de señal proporcionada por el transmisor trifásico de la figura 3 y el circuito de comunicación trifásico de la figura 4;

- 55 la figura 6 es un diagrama de flujo que ilustra un procedimiento de control de sesgo ejemplar empleado por el transmisor trifásico de la figura 3 para desplazar hacia la izquierda el último cruce de la derecha.

- la figura 7 es un diagrama de flujo que ilustra otro procedimiento de control de sesgo ejemplar empleado por el circuito de comunicación trifásico de la figura 4 para desplazar hacia la derecha el último cruce de la izquierda;

- la figura 8 ilustra un ejemplo de sistema basado en procesador que puede emplear el transmisor trifásico de la figura 3 y el circuito de comunicación trifásico de la figura 4; y

- la figura 9 ilustra un ejemplo de cámara digital que puede emplear el circuito de comunicación trifásico de la figura 4.

#### Descripción detallada

- 60 [0010] Con referencia ahora a las figuras de los dibujos, se describen varios aspectos ejemplares de la presente divulgación. El término "ejemplar" se usa en el presente documento en el sentido de "que sirve de ejemplo, caso o ilustración". Cualquier aspecto descrito en el presente documento como "ejemplar" no se ha de interpretar necesariamente como preferente o ventajoso con respecto a otros aspectos.

- 65 [0011] Los aspectos divulgados en la descripción detallada incluyen control de sesgo para la comunicación trifásica. En un ejemplo no limitante, se puede admitir el control de sesgo para la comunicación trifásica en dispositivos de comunicación móvil que usan la especificación de la interfaz serie para cámara trifásica (CSI-

3) MIPI® Alliance. Una comunicación trifásica implica tres ramales de señal. Se puede producir un sesgo de señal cuando un ramal de señal se acopla a una tensión de modo común mientras que otro ramal de señal se desacopla de la tensión de modo común. A este respecto, en un aspecto, se introduce una desadaptación de impedancia en el ramal de señal que se acopla a la tensión de modo común para ayudar a desplazar hacia la izquierda un último cruce de la derecha del sesgo de señal. En otro aspecto, una fuente de corriente o un sumidero de corriente se acopla al ramal de señal que se desacopla de la tensión de modo común para ayudar a desplazar hacia la derecha un último cruce de la izquierda del sesgo de señal. Más específicamente, la fuente de corriente o el sumidero de corriente se acoplan al ramal de señal si el ramal de señal se conmuta desde la tensión de modo común a una tensión menor o a una tensión mayor. Al desplazar el último cruce de la derecha hacia la izquierda y el último cruce de la izquierda hacia la derecha, es posible reducir el sesgo de señal, dando lugar por tanto a una fluctuación reducida y una integridad de datos mejorada en la comunicación trifásica.

**[0012]** Antes de analizar unos aspectos del control de sesgo para una comunicación trifásica que incluyen aspectos específicos de la presente divulgación, en las figuras 1, 2A y 2B se proporciona una breve visión general de un transmisor trifásico convencional, que se puede usar, en un ejemplo no limitante, en una cámara como parte de la especificación CSI-3, y una ilustración de un sesgo de señal asociado con el transmisor trifásico convencional. A continuación, comienza el análisis de aspectos ejemplares específicos del control de sesgo para la comunicación trifásica, con referencia a la figura 3. Para ayudar a describir eventos basados en el tiempo que se producen durante la comunicación trifásica, a continuación, en el presente documento se hace referencia a un tiempo Tx y un tiempo Ty para representar un tiempo presente y un tiempo futuro, respectivamente.

**[0013]** A este respecto, la figura 1 es un diagrama esquemático de un transmisor trifásico 100 convencional exemplar de acuerdo con la especificación de interfaz serie para cámara trifásica (CSI-3) MIPI® Alliance. El transmisor trifásico 100 convencional comprende un primer ramal de señal 102(1), un segundo ramal de señal 102(2) y un tercer ramal de señal 102(3). El primer ramal de señal 102(1), el segundo ramal de señal 102(2) y el tercer ramal de señal 102(3) incluyen unas respectivas impedancias de ramal 104(1)-104(3) y unas respectivas impedancias de excitación 106(1)-106(3). En un ejemplo no limitante, cada una de las respectivas impedancias de ramal 104(1)-104(3) es igual a cincuenta ohmios ( $50\ \Omega$ ). El primer ramal de señal 102(1), el segundo ramal de señal 102(2) y el tercer ramal de señal 102(3) terminan cada uno con una resistencia de  $50\ \Omega$ . Cada una de las respectivas impedancias de excitación 106(1)-106(3) incluye una primera resistencia ( $R_1$ ) y una segunda resistencia ( $R_2$ ) dispuestas en una disposición paralela. En un ejemplo no limitante, la  $R_1$  y la  $R_2$  tienen resistencias de cien ohmios ( $100\ \Omega$ ).

**[0014]** Cada uno del primer ramal de señal 102(1), el segundo ramal de señal 102(2) y el tercer ramal de señal 102(3) se puede acoplar selectivamente a una tensión de modo superior 110, una tensión de modo inferior 112 o una tensión de modo común 114 mediante un conmutador  $S_u$  y/o un conmutador  $S_L$ . En un ejemplo no limitante, la tensión de modo superior 110, la tensión de modo inferior 112 o la tensión de modo común 114 es de trescientos milivoltios (300 mV), cien milivoltios (100 mV) y doscientos milivoltios (200 mV), respectivamente. Una señal de primer ramal 116(1), una señal de segundo ramal 116(2) y una señal de tercer ramal 116(3), respectivamente, accionan las posiciones del conmutador  $S_u$  y del conmutador  $S_L$  en el primer ramal de señal 102(1), el segundo ramal de señal 102(2) y el tercer ramal de señal 102(3). En un ejemplo no limitante, el primer ramal de señal 102(1), el segundo ramal de señal 102(2) y el tercer ramal de señal 102(3) están acoplados a la tensión de modo superior 110, la tensión de modo común 114 y la tensión de modo inferior 112, respectivamente, en el tiempo Tx. Cuando la señal de primer ramal 116(1) hace que el primer ramal de señal 102(1) haga una transición desde estar acoplado a la tensión de modo superior 110 a estar acoplado a la tensión de modo inferior 112 en el tiempo Ty, el conmutador  $S_L$  del primer ramal de señal 102(1) se cierra y el conmutador  $S_u$  del primer ramal de señal 102(1) se abre. A este respecto, la respectiva impedancia de excitación 106(1) viene determinada por la  $R_2$ . Cuando la señal de segundo ramal 116(2) hace que el segundo ramal de señal 102(2) haga una transición desde estar acoplado a la tensión de modo común 114 a estar acoplado a la tensión de modo superior 110 en el tiempo Ty, el conmutador  $S_u$  del segundo ramal de señal 102(2) se cierra y el conmutador  $S_L$  del segundo ramal de señal 102(2) se abre. A este respecto, el segundo ramal de señal 102(2) está haciendo una transición para salir de un modo común, y la  $R_1$  determina la respectiva impedancia de excitación 106(2).

**[0015]** Continuando en referencia con la figura 1, cuando la señal de tercer ramal 116(3) hace que el tercer ramal de señal 102(3) haga una transición desde estar acoplado a la tensión de modo inferior 112 a estar acoplado a la tensión de modo común 114 en el tiempo Ty, el conmutador  $S_L$  y el conmutador  $S_u$  del tercer ramal de señal 102(3) están ambos cerrados. A este respecto, el tercer ramal de señal 102(3) está haciendo una transición al modo común y funciona como un ramal de modo común. La respectiva impedancia de excitación 106(3) viene determinada por la  $R_1$  y la  $R_2$  que están dispuestas en una disposición paralela. Dado que las resistencias de la  $R_1$  y la  $R_2$  son ambas de  $100\ \Omega$ , la impedancia de excitación respectiva 106(3) es de  $50\ \Omega$  y coincide con la impedancia de ramal respectiva 104(3) del tercer ramal de señal 102(3). Cuando el segundo ramal de señal 102(2) hace una transición para salir del modo común mientras que el tercer ramal de señal 102(3) está haciendo una transición al modo común, se puede producir un sesgo de señal. Para ilustrar el sesgo de señal producido por el transmisor trifásico 100 convencional, se proporcionan las figuras 2A y 2B.

[0016] A este respecto, la figura 2A es un gráfico 200 exemplar que ilustra un aspecto de un sesgo de señal 202 producido por el transmisor trifásico 100 convencional de la figura 1. Los elementos de la figura 1 se mencionan en relación con la figura 2A y no se volverán a describir en el presente documento.

[0017] Un sesgo de señal se refiere a la diferencia entre los retardos de propagación de dos señales cualesquiera en transiciones idénticas. Como se ilustra en la figura 2A, en el tiempo  $T_x$ , el primer ramal de señal 102(1), el segundo ramal de señal 102(2) y el tercer ramal de señal 102(3) se acoplan respectivamente a la tensión de modo superior 110, la tensión de modo común 114, y la tensión de modo inferior 112 mediante la señal de primer ramal 116(1), la señal de segundo ramal 116(2) y la señal de tercer ramal 116(3). Posteriormente, en el tiempo  $T_y$ , la señal de primer ramal 116(1), la señal de segundo ramal 116(2) y la señal de tercer ramal 116(3) hacen respectivamente que el primer ramal de señal 102(1), el segundo ramal de señal 102(2) y el tercer ramal de señal 102(3) se acoplen a la tensión de modo inferior 112, la tensión de modo superior 110 y la tensión de modo común 114. A este respecto, en el tiempo  $T_y$ , el tercer ramal de señal 102(3) hace una transición al modo común y se convierte en el ramal de modo común mientras el segundo ramal de señal 102(2) está haciendo una transición para salir del modo común. La diferencia entre los retardos de propagación causados por el tercer ramal de señal 102(3), que hace una transición al modo común en el tiempo  $T_y$ , y el segundo ramal de señal 102(2), que hace una transición para salir del modo común en el tiempo  $T_y$ , da como resultado el sesgo de señal 202 en el transmisor trifásico 100 convencional de la figura 1.

[0018] Como se ilustra en la figura 2A, el sesgo de señal 202 está definido por un último cruce de la izquierda 204 y un último cruce de la derecha 206. El último cruce de la izquierda 204 está determinado por el segundo ramal de señal 102(2) que hace una transición para salir del (o abandona el) modo común y el último cruce de la derecha 206 está determinado por el tercer ramal de señal 102(3) que hace una transición al (o entra en el) modo común. Cuanto más separados están el último cruce de la izquierda 204 y el último cruce de la derecha 206, más intenso es el sesgo de señal 202. Si el sesgo de señal 202 se examina usando un diagrama de ojo, cuanto más separados están el último cruce de la izquierda 204 y el último cruce de la derecha 206, más pequeña es la abertura del ojo en el diagrama de ojo. El sesgo de señal 202 puede causar distorsiones de señal y, en consecuencia, pérdidas de datos en el transmisor trifásico 100 convencional de la figura 1. Por tanto, es deseable reducir el sesgo de señal 202 desplazando hacia la derecha el último cruce de la izquierda 204 hasta un nuevo último cruce de la izquierda 204' y desplazando hacia la izquierda el último cruce de la derecha 204 hasta un nuevo último cruce de la derecha 206'. A medida que el nuevo último cruce de la izquierda 204' y el nuevo último cruce de la derecha 206' se acercan entre sí, se puede lograr una distorsión de señal reducida 202' en el transmisor trifásico 100 convencional de la figura 1.

[0019] La figura 2B es un gráfico 208 exemplar que ilustra otro aspecto del sesgo de señal 202 producido por el transmisor trifásico 100 convencional de la figura 1. Como se ilustra en la figura 2B, en el tiempo  $T_x$ , el primer ramal de señal 102(1), el segundo ramal de señal 102(2) y el tercer ramal de señal 102(3) se acoplan respectivamente a la tensión de modo superior 110, la tensión de modo inferior 112 y la tensión de modo común 114 mediante la señal de primer ramal 116(1), la señal de segundo ramal 116(2) y la señal de tercer ramal 116(3). Posteriormente, en el tiempo  $T_y$ , la señal de primer ramal 116(1), la señal de segundo ramal 116(2) y la señal de tercer ramal 116(3), respectivamente, hacen que el primer ramal de señal 102(1), el segundo ramal de señal 102(2) y el tercer ramal de señal 102(3) se acoplen a la tensión de modo común 114, la tensión de modo superior 110 y la tensión de modo inferior 112. A este respecto, en el tiempo  $T_y$ , el primer ramal de señal 102(1) está haciendo una transición al modo común y se está convirtiendo en el ramal de modo común mientras el tercer ramal de señal 102(3) está haciendo una transición para salir del modo común. La diferencia entre los retardos de propagación causados por el primer ramal de señal 102(1), que hace una transición al modo común en el tiempo  $T_y$ , y el tercer ramal de señal 102(3), que hace una transición para salir del modo común en el tiempo  $T_y$ , da como resultado el sesgo de señal 202 en el transmisor trifásico 100 convencional de la figura 1.

[0020] Como se analiza en referencia a las figuras 2A y 2B, el sesgo de señal 202 se puede reducir hasta el sesgo de señal reducido 202' desplazando hacia la derecha el último cruce de la izquierda 204 hasta el nuevo último cruce de la izquierda 204' y desplazando hacia la izquierda el último cruce de la derecha 206 hasta el nuevo último cruce de la derecha 206'. Para ayudar a comprender los mecanismos para desplazar el último cruce de la izquierda 204 hasta el nuevo último cruce de la izquierda 204' y desplazar el último cruce de la derecha 206 hasta el nuevo último cruce de la derecha 206', se proporcionan las figuras 3 y 4. Los elementos comunes entre las figuras 1, 2A, 2B, 3 y 4 se muestran en estas con números de elementos comunes y no se volverán a describir en el presente documento.

[0021] A este respecto, la figura 3 es un diagrama esquemático de un transmisor trifásico 300 exemplar configurado para desplazar hacia la izquierda el último cruce de la derecha 206 para reducir el sesgo de señal 202. El transmisor trifásico 300 comprende un primer ramal de señal 302(1), un segundo ramal de señal 302(2) y un tercer ramal de señal 302(3). El primer ramal de señal 302(1), el segundo ramal de señal 302(2) y el tercer ramal de señal 302(3) incluyen las respectivas impedancias de ramal 104(1)-104(3) y las respectivas impedancias de excitación 304(1)-304(3). Cada una de las respectivas impedancias de excitación 304(1)-

304(3) incluye una primera resistencia ( $R'_1$ ) y una segunda resistencia ( $R'_2$ ) dispuestas en una disposición paralela.

**[0022]** Con referencia a la figura 3, en el tiempo  $T_Y$ , el transmisor trifásico 300 recibe la señal de primer ramal 116(1), la señal de segundo ramal 116(2) y la señal de tercer ramal 116(3). La señal de primer ramal 116(1) hace que el primer ramal de señal 302(1) haga una transición desde estar acoplado a la tensión de modo superior 110 a estar acoplado a la tensión de modo inferior 112. Así pues, el conmutador  $S_U$  del primer ramal de señal 302(1) está abierto y el conmutador  $S_L$  del primer ramal de señal 302(1) está cerrado. La respectiva impedancia de excitación 304(1) es igual a la  $R'_2$ . La señal de segundo ramal 116(2) hace que el segundo ramal de señal 302(2) haga una transición desde estar acoplado a la tensión de modo común 114 a estar acoplado a la tensión de modo superior 110. Como resultado, el conmutador  $S_L$  del segundo ramal de señal 302(2) está abierto y el conmutador  $S_U$  del segundo ramal de señal 302(2) está cerrado. A este respecto, el segundo ramal de señal 302(2) hace una transición para salir del modo común y la respectiva impedancia de excitación 304(2) es igual a la  $R'_1$ .

**[0023]** La señal de tercer ramal 116(3) hace que el tercer ramal de señal 302(3) haga una transición desde estar acoplado a la tensión de modo inferior 112 a estar acoplado a la tensión de modo común 114. En consecuencia, tanto el conmutador  $S_U$  como el conmutador  $S_L$  del tercer ramal de señal 302(3) están cerrados. A este respecto, la señal de tercer ramal 116(3) hace que el tercer ramal de señal 302(3) haga una transición al modo común y funcione como el ramal de modo común. Dado que la  $R'_1$  y la  $R'_2$  están dispuestas en paralelo, la respectiva impedancia de excitación 304(3) es igual a un promedio de la resistencia de la  $R'_1$  y la resistencia de la  $R'_2$  ( $(R'_1 + R'_2) / 2$ ). Las resistencias de la  $R'_1$  y la  $R'_2$  se seleccionan para asegurar que la respectiva impedancia de excitación 304(3) sea menor que la respectiva impedancia de ramal 104(3). En un ejemplo no limitante, la  $R'_1$  y la  $R'_2$  se pueden seleccionar para proporcionar la respectiva impedancia de excitación 304(3) como una mitad de la respectiva impedancia de ramal 104(3). En otro ejemplo no limitante, la  $R'_1$  y la  $R'_2$  pueden tener cada una resistencia de  $50 \Omega$ , configurándose de este modo la respectiva impedancia de excitación 304(3) en  $25 \Omega$ . Creando una desadaptación entre la respectiva impedancia de excitación 304(3) y la respectiva impedancia de ramal 104(3), es posible agilizar la configuración resistencia-condensador (RC) en el transmisor trifásico 300. Como se ilustra más adelante en las figuras 5A y 5B, la configuración RC agilizada puede ayudar a desplazar hacia la izquierda el último cruce de la derecha 206 hasta el nuevo último cruce de la derecha 206', reduciéndose de este modo el sesgo de señal 202 en el transmisor trifásico 300.

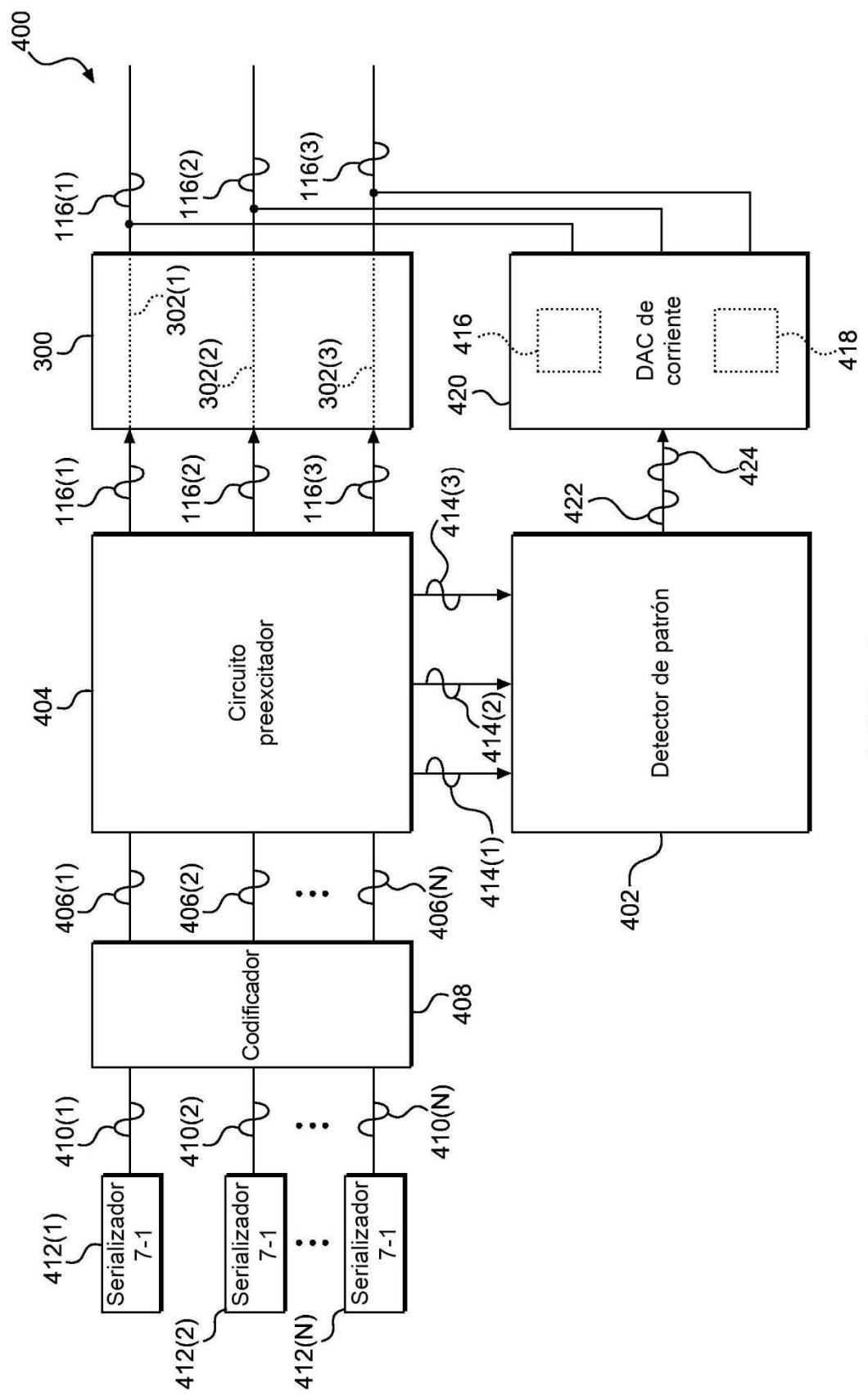

**[0024]** La figura 4 es un diagrama esquemático de un circuito de comunicación trifásico 400 exemplar que comprende un detector de patrones 402 configurado para desplazar hacia la derecha el último cruce de la izquierda 204 para reducir el sesgo de señal 202. El circuito de comunicación trifásico 400 comprende el transmisor trifásico 300 de la figura 3. El transmisor trifásico 300 está configurado para recibir la señal de primer ramal 116(1), la señal de segundo ramal 116(2) y la señal de tercer ramal 116(3) desde un circuito preexcitador 404. El circuito preexcitador 404 genera la señal de primer ramal 116(1), la señal de segundo ramal 116(2) y la señal de tercer ramal 116(3) en base a una pluralidad de flujos de entrada 406(1)-406(N) recibidos desde un codificador 408. El codificador 408 genera la pluralidad de flujos de entrada 406(1)-406(N) en base a una pluralidad de flujos de datos serializados 410(1)-410(N) recibidos desde una pluralidad de serializadores 412(1)-412(N), respectivamente. En un ejemplo no limitante, cada uno de la pluralidad de serializadores 412(1)-412(N) es un serializador siete a uno (7-1).

**[0025]** Continuando en referencia a la figura 4, en el tiempo  $T_X$ , el primer ramal de señal 302(1), el segundo ramal de señal 302(2) y el tercer ramal de señal 302(3) están acoplados a la tensión de modo superior 110, la tensión de modo común 114 y la tensión de modo inferior 112, respectivamente. A este respecto, el segundo ramal de señal 302(2) está en el modo común y funciona como el ramal de modo común (el presente ramal de modo común) en el tiempo  $T_X$ . En el tiempo  $T_Y$ , la señal de primer ramal 116(1), la señal de segundo ramal 116(2) y la señal de tercer ramal 116(3) respectivamente hacen que el primer ramal de señal 302(1), el segundo ramal de señal 302(2) y el tercer ramal de señal 302(3) se acoplen a la tensión de modo inferior 112, la tensión de modo superior 110 y la tensión de modo común 114. A este respecto, el tercer ramal de señal 302(3) está en el modo común y funciona como el ramal de modo común (el futuro ramal de modo común) en el tiempo  $T_Y$ . Por tanto, en el tiempo  $T_Y$ , el presente ramal de modo común, que es el segundo ramal de señal 302(2), sale del modo común y se desacopla de la tensión de modo común 114 mientras el futuro ramal de modo común, que es el tercer ramal de señal 302(3), pasa al modo común y se acopla a la tensión de modo común 114. Así pues, es posible predecir que el tercer ramal de señal 302(3) se convertirá en el ramal de modo común en el tiempo  $T_Y$  examinando la señal de tercer ramal 116(3) en el tiempo  $T_X$ .

**[0026]** A este respecto, el circuito preexcitador 404 está configurado para generar una primera señal de patrón 414(1), una segunda señal de patrón 414(2) y una tercera señal de patrón 414(3) que se corresponden con el primer ramal de señal 302(1), el segundo ramal de señal 302(2) y el tercer ramal de señal 302(3), respectivamente. Cada una de la primera señal de patrón 414(1), la segunda señal de patrón 414(2) y la tercera señal de patrón 414(3) indica una presente tensión respectiva (no mostrada) y una futura tensión respectiva (no mostrada) de un correspondiente ramal de señal de entre el primer ramal de señal 302(1), el segundo ramal de señal 302(2) y el tercer ramal de señal 302(3). Por ejemplo, la primera señal de patrón 414(1) indica la

5 presente tensión respectiva y la futura tensión respectiva del primer ramal de señal 302(1) en el tiempo Tx y el tiempo Ty, respectivamente. La segunda señal de patrón 414(2) indica la presente tensión respectiva y la futura tensión respectiva del segundo ramal de señal 302(2) en el tiempo Tx y el tiempo Ty, respectivamente. La tercera señal de patrón 414(3) indica la presente tensión respectiva y la futura tensión respectiva del tercer ramal de señal 302(3) en el tiempo Tx y el tiempo Ty, respectivamente.

10 [0027] Continuando en referencia a la figura 4, en el tiempo Tx, el detector de patrón 402 examina la primera señal de patrón 414(1), la segunda señal de patrón 414(2) y la tercera señal de patrón 414(3) para determinar el presente ramal de modo común de entre el primer ramal de señal 302(1), el segundo ramal de señal 302(2) y el tercero ramal de señal 302(3). Un ramal de señal de entre el primer ramal de señal 302(1), el segundo ramal de señal 302(2) y el tercero ramal de señal 302(3) se puede considerar como el presente ramal de modo común si la presente tensión respectiva del ramal de señal es igual a la tensión de modo común 114. Por ejemplo, el segundo ramal de señal 302(2) es el presente ramal de modo común si la presente tensión respectiva indicada por la segunda señal de patrón 414(2) es igual a la tensión de modo común 114. Una vez que se determina el presente ramal de modo común, el detector de patrón 402 puede determinar además la futura tensión respectiva del presente ramal de modo común en base a la futura tensión respectiva indicada por la señal de patrón respectiva. Por ejemplo, si el segundo ramal de señal 302(2) es el presente ramal de modo común, el detector de patrón 402 puede determinar la futura tensión del segundo ramal de señal 302(2) en base a la segunda señal de patrón 414(2).

20 [0028] Continuando en referencia a la figura 4, para desplazar el último cruce de la izquierda 204 (no mostrado) hasta el nuevo último cruce de la izquierda 204' (no mostrado), el detector de patrón 402 acopla una fuente de corriente 416 al presente ramal de modo común si el presente ramal de modo común está haciendo una transición a la futura tensión respectiva que es menor que la tensión de modo común 114. Por el contrario, el detector de patrón 402 acopla un sumidero de corriente 418 al presente ramal de modo común si el presente ramal de modo común está haciendo una transición a la futura tensión respectiva que es mayor que la tensión de modo común 114. En un ejemplo no limitante (no mostrado), la fuente de corriente 416 y el sumidero de corriente 418 se pueden proporcionar en un circuito de convertidor digital-analógico (DAC) de corriente 420. En un segundo ejemplo no limitante (no mostrado), la fuente de corriente 416 y el sumidero de corriente 418 pueden estar integrados en el detector de patrón 402.

30 [0029] Continuando en referencia a la figura 4, el circuito preexcitador 404 está configurado para mantener la sincronización entre la señal de primer ramal 116(1), la señal de segundo ramal 116(2), la señal de tercer ramal 116(3), la señal de fuente de corriente 422 y la señal de sumidero de corriente 424. A este respecto, la fuente de corriente 416 o el sumidero de corriente 418 se pueden acoplar al presente ramal de modo común cuando el presente ramal de modo común hace una transición para salir del modo común en el tiempo Ty.

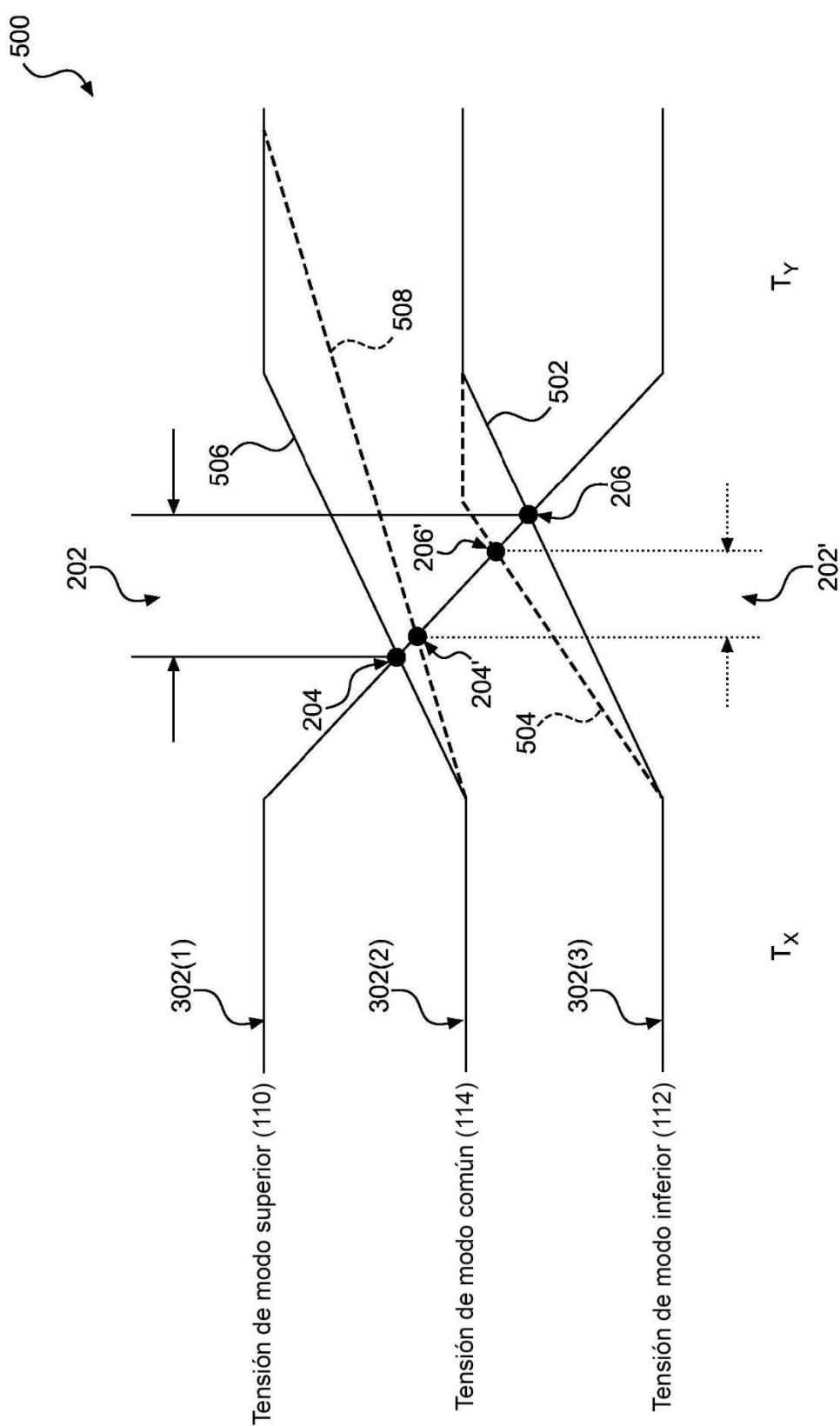

40 [0030] La figura 5A es un gráfico 500 ejemplar que ilustra un aspecto de la reducción del sesgo de señal proporcionada por el transmisor trifásico 300 de la figura 3 y el circuito de comunicación trifásica 400 de la figura 4. Los elementos de la figura 2A se mencionan en relación con la figura 5A y no se volverán a describir en el presente documento.

45 [0031] Como se analiza en la figura 3, cuando la señal de tercer ramal 116(3) hace que el tercer ramal de señal 302(3) haga una transición al modo común y funcione como el ramal de modo común en el tiempo Ty, el transmisor trifásico 300 está configurado para agilizar la configuración RC en el transmisor trifásico 300. La configuración RC agilizada en el transmisor trifásico 300 ayuda a desplazar una curva de transición original 502 hasta una nueva curva de transición 504. En otras palabras, la configuración RC agilizada hace que la nueva curva de transición 504 sea más pronunciada que la curva de transición original 502, desplazándose de este modo hacia la izquierda el último cruce de la derecha 206 hasta el nuevo último cruce de la derecha 206'.

50 [0032] Como se analiza en la figura 4, el detector de patrón 402 acopla el sumidero de corriente 418 al presente ramal de modo común si el presente ramal de modo común está haciendo una transición a la futura tensión respectiva que es mayor que la tensión de modo común 114. Como se ilustra en la figura 5A, cuando el segundo ramal de señal 302(2), que es el presente ramal de modo común, está haciendo una transición desde estar acoplado a la tensión de modo común 114 a estar acoplado a la tensión de modo superior 110 (la futura tensión respectiva), una curva de transición previa 506 se desplaza hasta una presente curva de transición 508 acoplando el sumidero de corriente 418 al segundo ramal de señal 302(2). Como resultado, el último cruce de la izquierda 204 se desplaza hacia la derecha hasta el nuevo último cruce de la izquierda 204' a medida que la presente curva de transición 508 se vuelve menos pronunciada que la curva de transición previa 506.

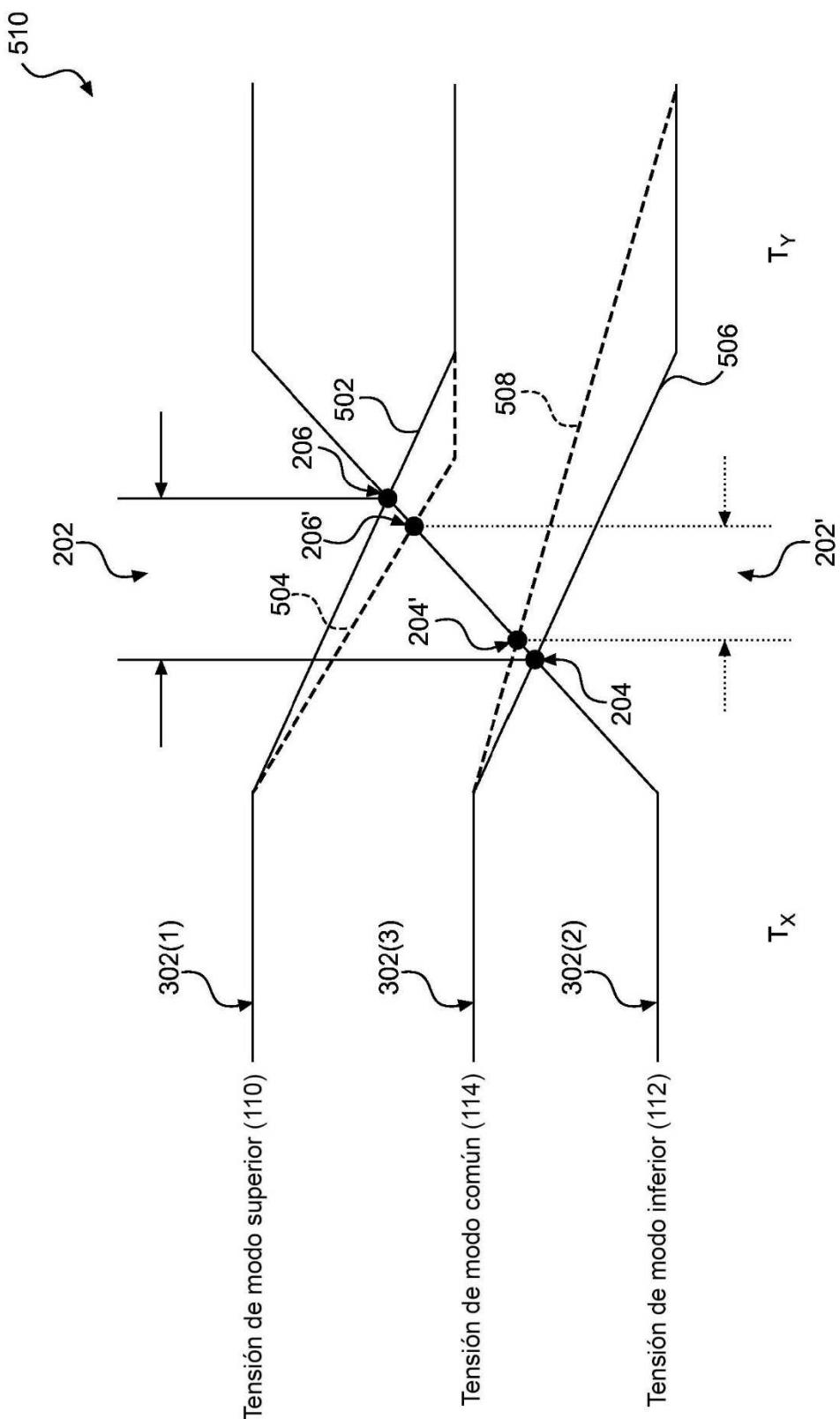

60 [0033] De forma similar a la figura 5A, la figura 5B es un gráfico 510 ejemplar que ilustra otro aspecto de la reducción de sesgo de señal proporcionada por el transmisor trifásico 300 de la figura 3 y el circuito de comunicación trifásico 400 de la figura 4.

5 [0034] Como se analiza en la figura 4, el detector de patrón 402 acopla la fuente de corriente 416 al presente ramal de modo común si el presente ramal de modo común está haciendo una transición a la futura tensión respectiva que es menor que la tensión de modo común 114. Como se ilustra en la figura 5B, cuando el tercer ramal de señal 302(3), que es el presente ramal de modo común, está haciendo una transición desde estar acoplado a la tensión de modo común 114 a estar acoplado a la tensión de modo inferior 112 (la futura tensión respectiva), la curva de transición previa 506 se desplaza hasta la presente curva de transición 508 acoplando la fuente de corriente 416 al tercer ramal de señal 302(3). Como resultado, el último cruce de la izquierda 204 se desplaza hacia la derecha hasta el nuevo último cruce de la izquierda 204' a medida que la presente curva de transición 508 se vuelve menos pronunciada que la curva de transición previa 506.

10 [0035] Asimismo, cuando la señal de primer ramal 116(1) hace que el primer ramal de señal 302(1) haga una transición al modo común y funcione como el ramal de modo común en el tiempo  $T_Y$ , el transmisor trifásico 300 está configurado para agilizar la configuración RC en el transmisor trifásico 300. La configuración RC agilizada ayuda a desplazar la curva de transición original 502 hasta la nueva curva de transición 504. En otras palabras, la configuración RC agilizada hace que la nueva curva de transición 504 sea más pronunciada que la curva de transición original 502, desplazándose de este modo hacia la izquierda el último cruce de la derecha 206 hasta el nuevo último cruce de la derecha 206'.

20 [0036] La figura 6 es un diagrama de flujo que ilustra un procedimiento de control de sesgo 600 ejemplar empleado por el transmisor trifásico 300 de la figura 3 para desplazar hacia la izquierda el último cruce de la derecha 206. De acuerdo con el procedimiento de control de sesgo 600, el transmisor trifásico 300 identifica un ramal de señal de entre el primer ramal de señal 302(1), el segundo ramal de señal 302(2) y el tercer ramal de señal 302(3), en el que el ramal de señal se selecciona para que funcione como el ramal de modo común al acoplarse a la tensión de modo común 114 (bloque 602). Una vez que se identifica el ramal de modo común, el transmisor trifásico 300 configura la respectiva impedancia de excitación 304(1)-304(3) del ramal de señal seleccionado para que sea menor que la respectiva impedancia de ramal 104(1)-104(3) del ramal de señal seleccionado (bloque 604).

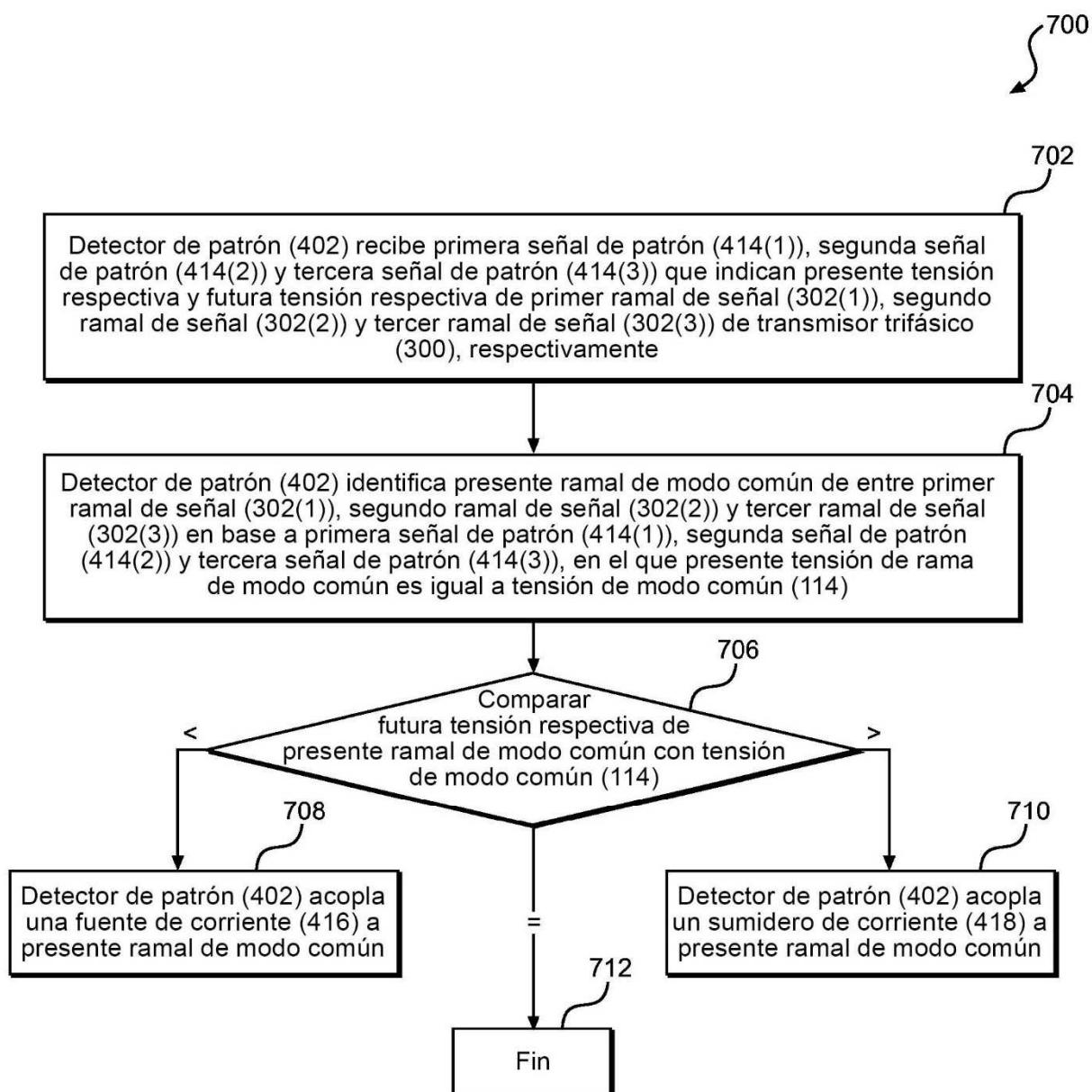

30 [0037] La figura 7 es un diagrama de flujo que ilustra otro procedimiento de control de sesgo 700 ejemplar empleado por el circuito de comunicación trifásico 400 de la figura 4 para desplazar hacia la derecha el último cruce de la izquierda 204. De acuerdo con el procedimiento de control de sesgo 700, el detector de patrón 402 recibe la primera señal de patrón 414(1), la segunda señal de patrón 414(2) y la tercera señal de patrón 414(3) que indican la presente tensión respectiva y la futura tensión respectiva del primer ramal de señal 302(1), el segundo ramal de señal 302(2) y el tercer ramal de señal 302(3), respectivamente (bloque 702). El detector de patrón 402 identifica a continuación el presente ramal de modo común de entre el primer ramal de señal 302(1), el segundo ramal de señal 302(2) y el tercer ramal de señal 302(3) en base a la primera señal de patrón 414(1), la segunda señal de patrón 414(2) y la tercera señal de patrón 414(3), en el que la presente tensión respectiva del presente ramal de modo común es igual a la tensión de modo común 114 (bloque 704). El detector de patrón 402 compara la futura tensión respectiva del presente ramal de modo común con la tensión de modo común 114 (bloque 706). Si la futura tensión respectiva del presente ramal de modo común es menor que la tensión de modo común 114, el detector de patrón 402 está configurado para acoplar la fuente de corriente 416 al presente ramal de modo común (bloque 708). Por el contrario, si la futura tensión respectiva del presente ramal de modo común es mayor que la tensión de modo común 114, el detector de patrón 402 está configurado para acoplar el sumidero de corriente 418 al presente ramal de modo común (bloque 710). El procedimiento de control de sesgo 700 termina si la futura tensión respectiva del presente ramal de modo común es igual a la tensión de modo común 114 (bloque 712).

40 [0038] El control de sesgo para la comunicación trifásica de acuerdo con los aspectos divulgados en el presente documento se puede proporcionar o integrar en cualquier dispositivo basado en procesador. Los ejemplos, sin limitación, incluyen un decodificador, una unidad de entretenimiento, un dispositivo de navegación, un dispositivo de comunicaciones, una unidad de datos de ubicación fija, una unidad de datos de ubicación móvil, un teléfono móvil, un teléfono celular, un ordenador, un ordenador portátil, un ordenador de sobremesa, un asistente digital personal (PDA), un monitor, un monitor de ordenador, un televisor, un sintonizador, una radio, una radio por satélite, un reproductor de música, un reproductor de música digital, un reproductor de música portátil, un reproductor de vídeo digital, un reproductor de vídeo, un reproductor de discos de vídeo digital (DVD) y un reproductor de vídeo digital portátil.

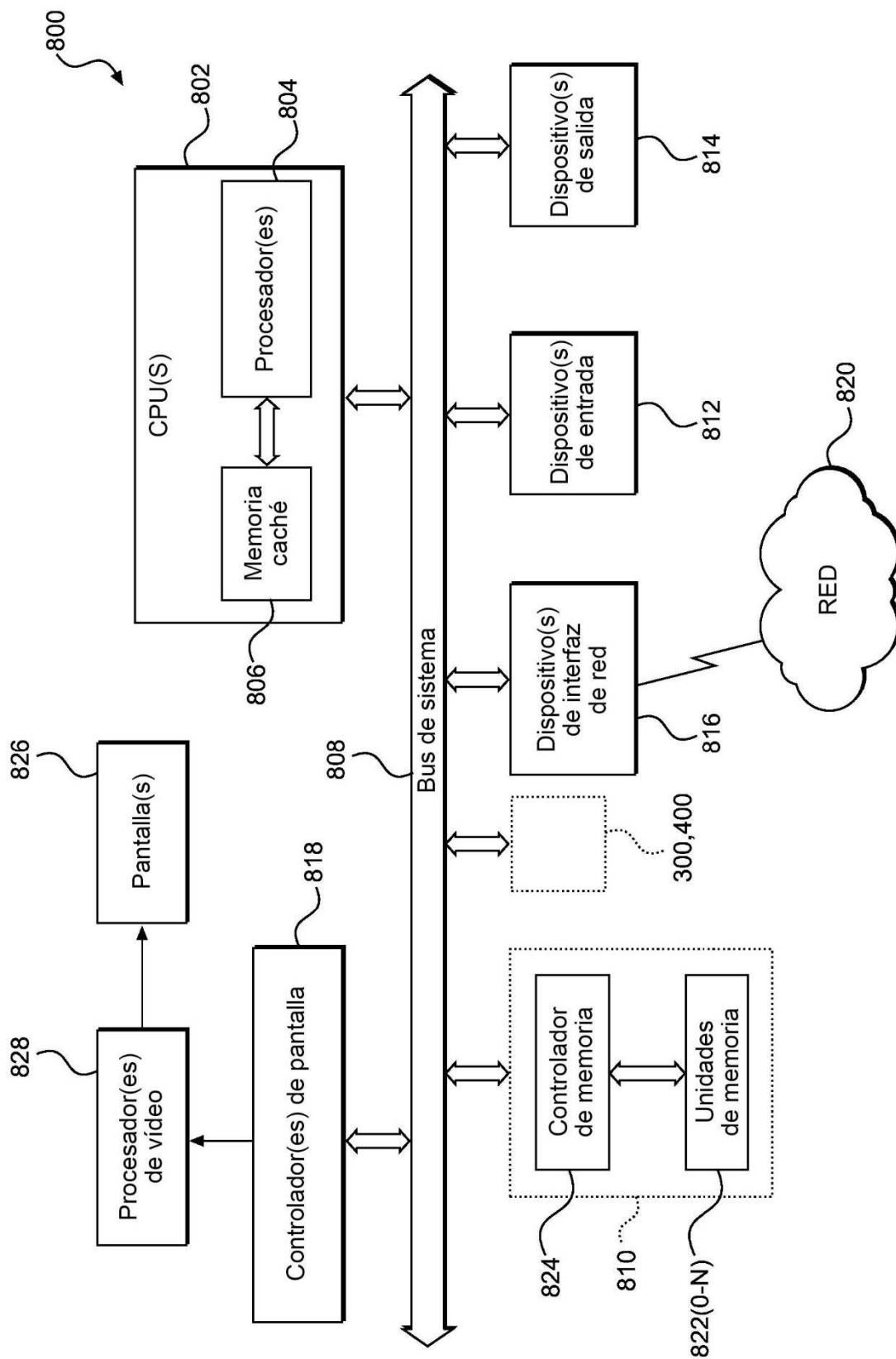

50 [0039] A este respecto, la figura 8 ilustra un ejemplo de sistema basado en procesador 800 que puede emplear el transmisor trifásico 300 de la figura 3 y el circuito de comunicación trifásico 400 de la figura 4. En este ejemplo, el sistema basado en procesador 800 incluye una o más unidades centrales de procesamiento (CPU) 802, que incluyen uno o más procesadores 804 cada una. La(s) CPU 802 puede(n) tener una memoria caché 806 acoplada al (a los) procesador(es) 804 para un rápido acceso a unos datos almacenados temporalmente. La(s) CPU 802 está(n) acoplada(s) a un bus de sistema 808. Como se conoce bien, la(s) CPU 802 se comunica(n) con estos otros dispositivos intercambiando información de dirección, control y datos a través del bus de sistema 808. Aunque no se ilustra en la figura 8, se podrían proporcionar múltiples buses de sistema 808, en los que cada bus 808 de sistema constituye una estructura diferente.

[0040] Otros dispositivos maestros y esclavos se pueden conectar al bus de sistema 808. Como se ilustra en la figura 8, estos dispositivos pueden incluir un sistema de memoria 810, uno o más dispositivos de entrada 812, uno o más dispositivos de salida 814, uno o más dispositivos de interfaz de red 816 y uno o más controladores de pantalla 818, como ejemplos. El transmisor trifásico 300 de la figura 3 y el circuito de comunicación trifásico 400 de la figura 4 también se pueden conectar al bus de sistema 808. El (los) dispositivo(s) de entrada 812 puede(n) incluir cualquier tipo de dispositivo de entrada, incluyendo, pero sin limitarse a, teclas de entrada, pulsadores, procesadores de voz, etc. El (los) dispositivo(s) de salida 814 puede(n) incluir cualquier tipo de dispositivo de salida, incluyendo, pero sin limitarse a, audio, vídeo, otros indicadores visuales, etc. El (los) dispositivo(s) de interfaz de red 816 puede(n) ser cualquier dispositivo configurado para permitir el intercambio de datos hacia y desde una red 820. La red 820 puede ser cualquier tipo de red, incluyendo, pero sin limitarse a, una red alámbrica o inalámbrica, una red privada o pública, una red de área local (LAN), una red inalámbrica de área local (WLAN), una red de área amplia (WAN), una red BLUETOOTH™ o Internet. El (los) dispositivo(s) de interfaz de red 816 se puede(n) configurar para admitir cualquier tipo de protocolo de comunicaciones deseado. El sistema de memoria 810 puede incluir una o más unidades de memoria 822(0-N) y un controlador de memoria 824.

[0041] La(s) CPU 802 también se puede(n) configurar para acceder al (a los) controlador(es) de pantalla 818 a través del bus de sistema 808 para controlar la información enviada a una o más pantallas 826. El (los) controlador(es) de pantalla 818 envía(n) a la(s) pantalla(s) 826 información que se va a visualizar por medio de uno o más procesadores de vídeo 828, que procesan la información que se va a visualizar en un formato adecuado para la(s) pantalla(s) 826. La(s) pantalla(s) 826 puede(n) incluir cualquier tipo de pantalla, incluyendo, pero sin limitarse a, un tubo de rayos catódicos (CRT), una pantalla de cristal líquido (LCD), una pantalla de plasma, una pantalla de diodos emisores de luz (LED), etc.

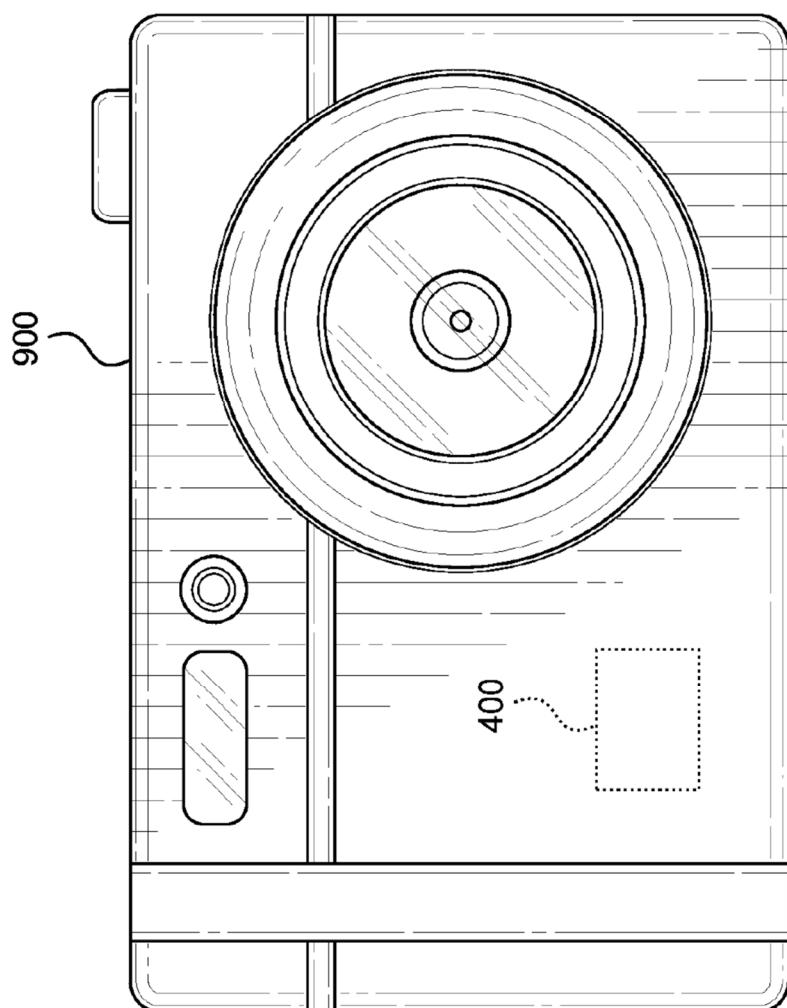

[0042] El circuito de comunicación trifásico 400 de la figura 4 también se puede proporcionar en una cámara digital 900 como se ilustra en el diagrama esquemático ejemplar de la figura 9.

[0043] Los expertos en la técnica apreciarán además que los diversos bloques lógicos, módulos, circuitos y algoritmos ilustrativos descritos en relación con los aspectos divulgados en el presente documento se pueden implementar como hardware electrónico, instrucciones almacenadas en memoria o en otro medio legible por ordenador y ejecutadas por un procesador u otro dispositivo de procesamiento, o combinaciones de ambos. Los dispositivos maestros y los dispositivos esclavos descritos en el presente documento se pueden emplear en cualquier circuito, componente de hardware, circuito integrado (CI) o chip de CI, como ejemplos. La memoria divulgada en el presente documento puede ser una memoria de cualquier tipo y tamaño y se puede configurar para almacenar cualquier tipo de información deseada. Para ilustrar claramente esta intercambiabilidad, anteriormente se han descrito, en general, diversos componentes, bloques, módulos, circuitos y etapas ilustrativos en términos de su funcionalidad. El modo en que se implementa dicha funcionalidad depende de la aplicación, las opciones de diseño elegidas y/o las limitaciones de diseño particulares impuestas al sistema global. Los expertos en la técnica pueden implementar la funcionalidad descrita de formas diferentes para cada aplicación particular, pero no se debe interpretar que dichas decisiones de implementación suponen apartarse del alcance de la presente divulgación.

[0044] Los diversos bloques lógicos, módulos y circuitos ilustrativos descritos en relación con los aspectos divulgados en el presente documento se pueden implementar o realizar con un procesador, un procesador de señales digitales (DSP), un circuito integrado específico de la aplicación (ASIC), una matriz de puertas programables *in situ* (FPGA) u otro dispositivo lógico programable, lógica de puertas o de transistores discretos, componentes de hardware discretos o cualquier combinación de los mismos diseñada para realizar las funciones descritas en el presente documento. Un procesador puede ser un microprocesador, pero, como alternativa, el procesador puede ser cualquier procesador, controlador, microcontrolador o máquina de estados convencional. Un procesador también se puede implementar como una combinación de dispositivos informáticos (por ejemplo, una combinación de un DSP y un microprocesador, una pluralidad de microprocesadores, uno o más microprocesadores junto con un núcleo de DSP o cualquier otra configuración de este tipo).

[0045] Los aspectos divulgados en el presente documento se pueden incorporar en hardware y en instrucciones que se almacenan en hardware, y pueden residir, por ejemplo, en memoria de acceso aleatorio (RAM), memoria flash, memoria de solo lectura (ROM), ROM eléctricamente programable (EPROM), ROM eléctricamente programable borrable (EEPROM), unos registros, un disco duro, un disco extraíble, un CD-ROM o cualquier otra forma de medio legible por ordenador conocida en la técnica. Un medio de almacenamiento ejemplar está acoplado al procesador de modo que el procesador puede leer información de, y escribir información en, el medio de almacenamiento. De forma alternativa, el medio de almacenamiento puede estar integrado en el procesador. El procesador y el medio de almacenamiento pueden residir en un ASIC. El ASIC puede residir en una estación remota. Como alternativa, el procesador y el medio de almacenamiento pueden residir como componentes discretos en una estación remota, una estación base o un servidor.

- [0046] Cabe señalar, además, que las etapas operativas descritas en cualquiera de los aspectos ejemplares en el presente documento se describen para proporcionar ejemplos y análisis. Las operaciones descritas se pueden realizar en numerosas secuencias diferentes distintas a las secuencias ilustradas. Además, las operaciones descritas en una única etapa operativa se pueden realizar realmente en un número de etapas 5 diferentes. Adicionalmente, se pueden combinar una o más etapas operativas analizadas en los aspectos ejemplares. Se entenderá que las etapas operativas ilustradas en los diagramas de flujo se pueden someter a numerosas modificaciones diferentes, como resultará fácilmente evidente para un experto en la técnica. Los expertos en la técnica también entenderán que la información y las señales se pueden representar usando 10 cualquiera de una variedad de tecnologías y técnicas diferentes. Por ejemplo, los datos, las instrucciones, los comandos, la información, las señales, los bits, los símbolos y los chips que se pueden haber mencionado a lo largo de la descripción anterior se pueden representar mediante tensiones, corrientes, ondas electromagnéticas, campos o partículas magnéticos, campos o partículas ópticos, o cualquier combinación de 15 los mismos.

- [0047] La descripción previa de la divulgación se proporciona para permitir que cualquier experto en la técnica realice o use la divulgación. Diversas modificaciones de la divulgación resultarán fácilmente evidentes a los expertos en la técnica, y los principios genéricos definidos en el presente documento se pueden aplicar a otras variantes sin apartarse del alcance de la divulgación. Por tanto, no se pretende limitar la divulgación a los 20 ejemplos y diseños descritos en el presente documento, sino que se le ha de conceder el alcance más amplio consecuente con las características novedosas divulgadas en el presente documento.

## REIVINDICACIONES

1. Un transmisor trifásico, que comprende:

- 5 un primer ramal de señal (102(1)), un segundo ramal de señal (102(2)), y un tercer ramal de señal (102(3)), en el que cada uno del primer ramal de señal, el segundo ramal de señal, y el tercer ramal de señal comprende una impedancia de ramal (104(1)-104(3)) respectiva y una impedancia de excitación (106(1)-106(3)) respectiva;

- 10 en el que el transmisor trifásico está **caracterizado por** estar configurado para configurar la impedancia de excitación respectiva de un ramal de señal seleccionado para que sea menor que la impedancia de ramal respectiva del ramal de señal seleccionado cuando un ramal de señal de entre el primer ramal de señal, el segundo ramal de señal, y el tercer ramal de señal está seleccionado para que funcione como un ramal de modo común al acoplarse a una tensión de modo común.

- 15 2. El transmisor trifásico de la reivindicación 1, en el que la tensión de modo común es de doscientos milivoltios (200 mV).

- 20 3. El transmisor trifásico de la reivindicación 1, en el que cuando el transmisor trifásico está configurado para configurar la impedancia de excitación respectiva del ramal de señal seleccionado para que sea menor que la impedancia de ramal respectiva del ramal de señal seleccionado, la impedancia de excitación respectiva del ramal de señal seleccionado es una mitad de la impedancia de ramal respectiva del ramal de señal seleccionado.

- 25 4. El transmisor trifásico de la reivindicación 1, en el que cuando el transmisor trifásico está configurado para configurar la impedancia de excitación respectiva del ramal de señal seleccionado para que sea menor que la impedancia de ramal respectiva del ramal de señal seleccionado, la impedancia de excitación respectiva del ramal de señal seleccionado es de veinticinco ohmios (25 Ω).

- 30 5. El transmisor trifásico de la reivindicación 4, en el que la impedancia de excitación respectiva del ramal de señal seleccionado se proporciona mediante dos resistencias de cincuenta ohmios (50 Ω) dispuestas de acuerdo con una disposición paralela.

- 35 6. El transmisor trifásico de la reivindicación 4, en el que la impedancia de ramal respectiva del ramal de señal seleccionado es de 50 Ω.

7. El transmisor trifásico de la reivindicación 1 integrado en una interfaz serie para cámara trifásica (CSI-3).

- 40 8. El transmisor trifásico de la reivindicación 1 integrado en un dispositivo seleccionado del grupo que consiste en: un decodificador; una unidad de entretenimiento; un dispositivo de navegación; un dispositivo de comunicaciones; una unidad de datos de ubicación fija; una unidad de datos de ubicación móvil; un teléfono móvil; un teléfono celular; un ordenador; un ordenador portátil; un ordenador de sobremesa; un asistente digital personal (PDA); un monitor; un monitor de ordenador; un televisor; un sintonizador; una radio; una radio por satélite; un reproductor de música; un reproductor de música digital; un reproductor de música portátil; un reproductor de video digital; un reproductor de video; un reproductor de disco de video digital (DVD); y un reproductor de video digital portátil.

- 45 9. Un procedimiento para reducir un sesgo de señal en un transmisor trifásico, que comprende:

- 50 identificar un ramal de señal de entre un primer ramal de señal, un segundo ramal de señal, y un tercer ramal de señal del transmisor trifásico, comprendiendo cada uno del primer ramal de señal, el segundo ramal de señal, y el tercer ramal de señal una impedancia de ramal (104(1)-104(3)) respectiva y una impedancia de excitación (106(1)-106(3)) respectiva,

- 55 en el que el ramal de señal está seleccionado para que funcione como un ramal de modo común al acoplarse a una tensión de modo común; y el procedimiento está **caracterizado por que** comprende, además:

- 60 configurar la impedancia de excitación respectiva del ramal de señal seleccionado para que sea menor que la impedancia de ramal respectiva del ramal de señal seleccionado.

- 65 10. El procedimiento de la reivindicación 9, que comprende además configurar la impedancia de excitación respectiva del ramal de señal seleccionado para que sea una mitad de la impedancia de ramal respectiva del ramal de señal seleccionado.

11. El procedimiento de la reivindicación 9, que comprende además configurar la respectiva impedancia de excitación del ramal de señal seleccionado en veinticinco ohmios ( $25 \Omega$ ).

12. Un circuito de comunicación trifásico, que comprende:

un transmisor trifásico de acuerdo con la reivindicación 1 y que comprende, además;

un circuito preexcitador configurado para generar una primera señal de patrón, una segunda señal de patrón y una tercera señal de patrón correspondientes al primer ramal de señal, el segundo ramal de señal, y el tercer ramal de señal, respectivamente, en el que cada una de la primera señal de patrón, la segunda señal de patrón, y la tercera señal de patrón indica una presente tensión respectiva y una futura tensión respectiva de un ramal de señal correspondiente de entre el primer ramal de señal, el segundo ramal de señal, y el tercer ramal de señal; y un detector de patrón configurado para:

determinar un presente ramal de modo común de entre el primer ramal de señal, el segundo ramal de señal, y el tercer ramal de señal en base a la primera señal de patrón, la segunda señal de patrón, y la tercera señal de patrón, en el que la presente tensión respectiva del presente ramal de modo común es igual a la tensión de modo común;

acoplar una fuente de corriente al presente ramal de modo común si la futura tensión respectiva del presente ramal de modo común es menor que la tensión de modo común; y

acoplar un sumidero de corriente al presente ramal de modo común si la futura tensión respectiva del presente ramal de modo común es mayor que la tensión de modo común.

13. El circuito de comunicación trifásico de la reivindicación 12, que comprende, además:

una pluralidad de serializadores configurados para generar una pluralidad de flujos de datos serializados; y

un codificador configurado para codificar la pluralidad de flujos de datos serializados para proporcionar una pluralidad de flujos de entrada al circuito preexcitador.

14. El procedimiento para reducir un sesgo de señal en el transmisor trifásico de la reivindicación 9, que comprende, además:

recibir una primera señal de patrón (414(1)), una segunda señal de patrón (414(2)), y una tercera señal de patrón (414(3)) que indican una presente tensión respectiva y una futura tensión respectiva del primer ramal de señal (302(1)), el segundo ramal de señal (302(2)), y el tercer ramal de señal (302(3)) del transmisor trifásico, respectivamente; y **caracterizado por**:

identificar un presente ramal de modo común de entre el primer ramal de señal, el segundo ramal de señal, y el tercer ramal de señal en base a la primera señal de patrón, la segunda señal de patrón, y la tercera señal de patrón, en el que la presente tensión respectiva del presente ramal de modo común es igual a la tensión de modo común;

acoplar una fuente de corriente al presente ramal de modo común si la futura tensión respectiva del presente ramal de modo común es menor que la tensión de modo común; y

acoplar un sumidero de corriente al presente ramal de modo común si la futura tensión respectiva del presente ramal de modo común es mayor que la tensión de modo común.

15. El procedimiento de la reivindicación 14, que comprende, además:

identificar un futuro ramal de modo común de entre el primer ramal de señal, el segundo ramal de señal, y el tercer ramal de señal del transmisor trifásico en base a la primera señal de patrón, la segunda señal de patrón, y la tercera señal de patrón, en el que la futura tensión respectiva del futuro ramal de modo común es igual a la tensión de modo común; y

configurar una respectiva impedancia de excitación del futuro ramal de modo común para que sea menor que una respectiva impedancia de ramal del futuro ramal de modo común.

**FIG. 1**

**FIG. 2A**

**FIG. 2B**

**FIG. 3**

**FIG. 4**

**FIG. 5A**

**FIG. 5B**

**FIG. 6**

**FIG. 7**

**FIG. 8**

**FIG. 9**