(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7155455号**

**(P7155455)**

(45)発行日 令和4年10月18日(2022.10.18)

(24)登録日 令和4年10月7日(2022.10.7)

(51)国際特許分類

F I

|         |                 |         |             |

|---------|-----------------|---------|-------------|

| H 0 1 S | 5/0239(2021.01) | H 0 1 S | 5/0239      |

| H 0 1 S | 5/0233(2021.01) | H 0 1 S | 5/0233      |

| H 0 1 S | 5/183(2006.01)  | H 0 1 S | 5/183       |

| H 0 1 S | 5/042(2006.01)  | H 0 1 S | 5/042 6 3 0 |

| H 0 1 S | 5/0225(2021.01) | H 0 1 S | 5/0225      |

請求項の数 13 (全28頁) 最終頁に続く

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2022-516276(P2022-516276) |

| (86)(22)出願日       | 令和3年6月22日(2021.6.22)        |

| (86)国際出願番号        | PCT/JP2021/023664           |

| (87)国際公開番号        | WO2021/261496               |

| (87)国際公開日         | 令和3年12月30日(2021.12.30)      |

| 審査請求日             | 令和4年3月11日(2022.3.11)        |

| (31)優先権主張番号       | 特願2020-107020(P2020-107020) |

| (32)優先日           | 令和2年6月22日(2020.6.22)        |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                     |

| (31)優先権主張番号       | 特願2021-52423(P2021-52423)   |

| (32)優先日           | 令和3年3月25日(2021.3.25)        |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                     |

| 早期審査対象出願          |                             |

|          |                                                |

|----------|------------------------------------------------|

| (73)特許権者 | 000131430<br>シチズン電子株式会社<br>山梨県富士吉田市上暮地1丁目23番1号 |

| (73)特許権者 | 000001960<br>シチズン時計株式会社<br>東京都西東京市田無町六丁目1番12号  |

| (74)代理人  | 100099759<br>弁理士 青木 篤                          |

| (74)代理人  | 100123582<br>弁理士 三橋 真二                         |

| (74)代理人  | 100114018<br>弁理士 南山 知広                         |

| (74)代理人  | 100180806<br>弁理士 三浦 剛                          |

最終頁に続く

(54)【発明の名称】 V C S E L モジュール

**(57)【特許請求の範囲】****【請求項1】**

表面に配置されるV C S E L 第1端子、及び、裏面に配置されるV C S E L 第2端子を有するV C S E Lと、

第1側面、前記第1側面に直交する第2側面及び第3側面、前記第1側面と対向する第4側面、上面、及び下面を備える矩形の平板形状を有し且つ前記V C S E Lの下に配置され、前記V C S E L 第2端子と電気的に接続されたV C S E L用のスイッチング素子が内部に形成される半導体装置と、

前記第1側面に沿って配置される金属製の第1電極と、

前記半導体装置の下に配置される金属製の第2電極と、を有し、

前記半導体装置は、

前記第1側面に沿う辺、前記第1側面に直交し且つ前記第1側面に沿う辺よりも短い一对の辺、及び前記第1側面に沿う辺に対向する辺により形成される矩形の平面形状を有し、前記上面の端部に配置され、且つ、第1電極及び前記V C S E L 第1端子と接続される第1端子と、

前記上面の中央部に配置され、前記V C S E L 第2端子と接続される第2端子と、

前記第2電極と接続される第3端子と、

を更に有する、ことを特徴とするV C S E Lモジュール。

**【請求項2】**

前記半導体装置は、前記V C S E Lを流れる電流を制御する電流制御素子を有し、前記

電流制御素子は、前記第2端子と前記スイッチング素子との間、又は、前記スイッチング素子と前記第3端子との間に接続される、請求項1に記載のVCSELモジュール。

**【請求項3】**

前記第3端子は、前記第2側面又は前記第3側面に沿った前記上面の端部に配置される、請求項2に記載のVCSELモジュール。

**【請求項4】**

前記第1電極と前記第1端子とは、複数のボンディングワイヤで接続されている、請求項3に記載のVCSELモジュール。 10

**【請求項5】**

前記第2電極と前記第3端子とは、複数のボンディングワイヤで接続されている、請求項3又は4に記載のVCSELモジュール。

**【請求項6】**

前記半導体装置は、前記VCSELの温度、前記VCSELを流れる電流、又は、前記VCSELから出射される光の光量を関する監視回路を有し、

前記監視回路と接続される監視回路用端子は、前記半導体装置の表面の前記第4側面に沿った端部に配置される、請求項3～5の何れか一項に記載のVCSELモジュール。

**【請求項7】**

前記監視回路用端子と接続される第3電極を更に有する、請求項6に記載のVCSELモジュール。 20

**【請求項8】**

前記第1電極及び前記第2電極の表面の一部、及び、前記第1端子及び第3端子の表面の一部を覆うように形成される樹脂製のフレームを更に有する、請求項2～7の何れか一項に記載のVCSELモジュール。

**【請求項9】**

前記フレームは、前記VCSELが視認可能な開口部が形成される支持面を有する、請求項8に記載のVCSELモジュール。

**【請求項10】**

前記支持面に支持され、前記VCSELから出射された光を透過する光学素子を更に有する、請求項9記載のVCSELモジュール。 30

**【請求項11】**

前記フレームは、前記光学素子の位置決めをするために、前記支持面の上方で、且つ、当該フレームの外壁から内側に迫り出した凸部を有する、請求項10に記載のVCSELモジュール。

**【請求項12】**

前記VCSELからの放熱を前記第2電極へ向けて伝達するための放熱経路が、前記半導体装置において、前記第2端子と前記半導体装置の前記下面との間に形成される、請求項3～11の何れか一項に記載のVCSELモジュール。

**【請求項13】**

前記半導体装置は、前記第2電極と接続される第4端子、を有し、

前記第4端子は、前記第3端子が配置された前記第2側面又は前記第3側面の他方に沿った前記上面の端部に配置され、 40

前記VCSEL第2端子から前記半導体装置内に流入した電流は、前記第3端子及び前記第4端子により、前記半導体装置の左右に分かれて前記第2電極へ流れる、請求項3～12の何れか一項に記載のVCSELモジュール。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、VCSEL(Vertical Cavity Surface Emitting Laser)を光源とするVCSELモジュールに関する。

**【背景技術】**

10

20

30

40

50

**【 0 0 0 2 】**

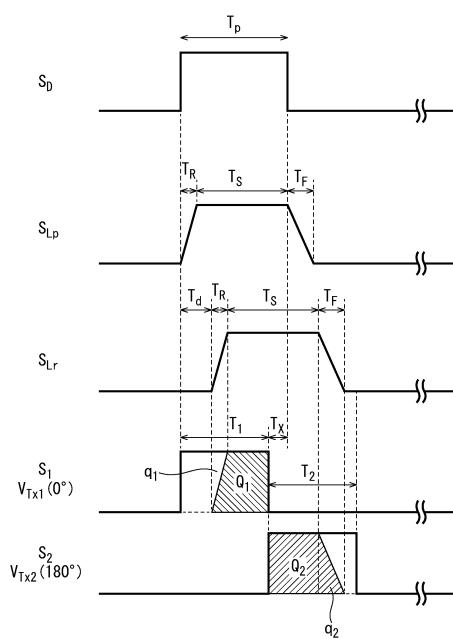

特開2016-45066号公報には、光源から発したパルス光が対象物で反射して戻ってきた光（以下「反射光」という。）に基づいて距離を測定する測距装置が記載されている。上記の測距装置は、距離画像センサと、光源と、制御ユニットとを備えている。距離画像センサは、電荷振り分け型の距離画像センサであり、光源は、VCSELモジュール等のレーザ光照射装置やLEDなどで構成される。制御ユニットは、光源に駆動信号SDを印加しパルス光（光強度信号SLP）を出射させるとともに、第1転送信号S1及び第2転送信号S2を距離画像センサに出力する。

**【 0 0 0 3 】**

図24は、上記の測距装置において距離を測定する方法を説明するためのタイミングチャートである。上記の測距装置では、測距精度に対する光強度信号SLPの立ち上がり期間TP及び立下り期間TFの影響が低減され、測距精度が向上する。10

**【 0 0 0 4 】**

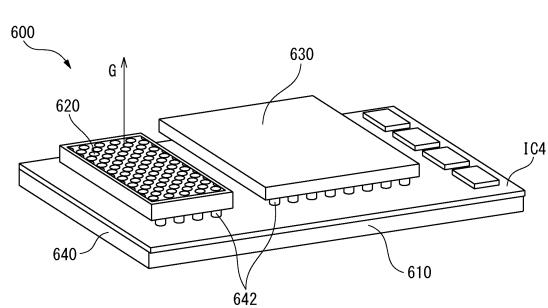

米国特許出願公開第2018/0278011号には、光源の立ち上がりを改善したレーザダイオードモジュール600が記載されている。図25は、上記のレーザダイオードモジュール600の斜視図である。レーザダイオードモジュール600は、基板610、複数のレーザダイオードDLを含むレーザダイオード620、コンデンサC1、C2を含むコンデンサ630、及び、レーザダイオードDLと直列接続するトランジスタTLを含むドライバ回路640を含むIC4等を有している。レーザダイオード620からは、矢印Gの方向に光が出射する。20

**【 0 0 0 5 】**

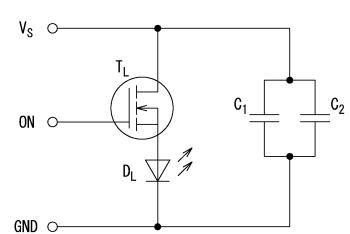

図26は、図25に示すレーザダイオードモジュール600の回路図である。レーザダイオードモジュール600は、電源端子Vs、制御端子ON及びグランド端子GNDを備えている。電源端子Vsとグランド端子GNDの間でスイッチング用のトランジスタTLとレーザダイオードDLが直列接続し、この直列回路にコンデンサC1、C2が並列接続している。制御端子ONは、トランジスタTLのゲート電極に接続している。

**【 0 0 0 6 】**

特開2009-105240号公報には、VCSELと、抵抗が正の温度特性を有し且つVCSELに直列接続される抵抗素子とを有する発光装置が記載される。上記の発光装置は、VCSELに直列接続される抵抗素子がVCSELのインピーダンス特性の温度変化を補償することで、インピーダンス不整合による高周波ノイズの発生及び駆動信号の劣化を防止することができる。30

**【 0 0 0 7 】**

特開2004-31456には、表面にICドライバを配置し且つ裏面にVCSELを配置したサブマウント基板を、基板の上部に配置して、小型化を図った光インタコネクション装置が記載されている。

**【 0 0 0 8 】**

米国特許第8488921号の図16には、プリント配線基板の上部にサブマウントを配置し、サブマウントの上部にICチップを配置し、ICチップの上部にVCSELを配置した装置が記載されている。40

**【 0 0 0 9 】**

特開2009-8721号公報の図2には、プリント基板の上部に発光素子アレイを配置し、発光素子アレイの上部に駆動ICを配置し、駆動ICの上部にメモリICを配置した光モジュールが記載されている。

**【発明の概要】****【 0 0 1 0 】**

しかしながら、基板の上部にスイッチング素子が配置され、スイッチング素子の上部にVCSELが配置された3段階構造を有するVCSELモジュールは、何れの文献にも記載されていなかった。

**【 0 0 1 1 】**

10

20

30

40

50

そこで、本発明に係るV C S E L モジュールは、V C S E L 及びスイッチング素子が一体化され且つ小型化が可能なV C S E L モジュールを提供することを目的とする。

【 0 0 1 2 】

本V C S E L モジュールの一実施形態によると、V C S E L と、V C S E L の下に配置され、V C S E L と電気的に接続されたV C S E L 用のスイッチング素子と、スイッチング素子の下に配置され、スイッチング素子と電気的に接続された基板と、を有する。

【 0 0 1 3 】

上記のV C S E L モジュールでは、V C S E L とスイッチング素子との間、又は、スイッチング素子と基板との間に配置された電流制御素子を有し、

電流制御素子は、V C S E L 及びスイッチング素子と直列に電気的に接続される、ことが好ましい。 10

【 0 0 1 4 】

上記のV C S E L モジュールでは、基板上に形成された配線電極を、さらに有し、

スイッチング素子又は電流制御素子は、配線電極と、半田ボール、スタッドバンプ、又

は、金属片を介して電気的に接続されている、ことが好ましい。

【 0 0 1 5 】

上記のV C S E L モジュールでは、電流制御素子のゲート電極と接続する配線電極の接

続部分は、他の部分より厚く形成されている、ことが好ましい。

【 0 0 1 6 】

上記のV C S E L モジュールでは、V C S E L と電気的に接続されたコンデンサ、をさ

らに有する、ことが好ましい。 20

【 0 0 1 7 】

上記のV C S E L モジュールでは、金属製の第1電極を更に有し、

基板は金属製の第2電極として機能し、

V C S E L は、表面に配置されるV C S E L 第1端子、及び、裏面に配置されるV C S

E L 第2端子を有し、スイッチング素子は半導体装置内に形成され、

半導体装置は、第1電極及びカソードと接続される第1端子、カソードと接続される第

2端子、及び、前記第2電極と接続される第3端子、を有することが好ましい。

【 0 0 1 8 】

上記のV C S E L モジュールでは、半導体装置は、V C S E L を流れる電流を制御する

電流制御素子を有し、電流制御素子は、第2端子とスイッチング素子との間、又は、スイ

ッチング素子と第3端子との間に接続される、ことが好ましい。 30

【 0 0 1 9 】

上記のV C S E L モジュールでは、半導体装置は、第1側面、第1側面に直交する第2

側面及び第3側面、第1側面と対向する第4側面、上面、及び下面を備える、矩形の平板

形状を有し、

第1端子は、第1電極に近接する第1側面に沿った上面の端部に配置され、

第2端子は、上面の中央部に配置され、

第3端子は、第2側面又は第3側面に沿った上面の端部に配置される、ことが好ましい。

【 0 0 2 0 】

上記のV C S E L モジュールでは、第1電極と第1端子とは、複数のボンディングワ

イヤで接続されている、ことが好ましい。 40

【 0 0 2 1 】

上記のV C S E L モジュールでは、第2電極と第3端子とは、複数のボンディングワ

イヤで接続されている、ことが好ましい。

【 0 0 2 2 】

上記のV C S E L モジュールでは、半導体装置は、V C S E L の温度、V C S E L を流

れる電流、又は、V C S E L から出射される光の光量を関する監視回路を有し、

監視回路と接続される監視回路用端子は、半導体装置の表面の第4面に沿った端部に配

置される、ことが好ましい。 50

**【0023】**

上記のV C S E L モジュールでは、監視回路用端子と接続される第3電極を更に有する、ことが好ましい。

**【0024】**

上記のV C S E L モジュールでは、第1電極及び第2電極の表面の一部、及び、第1端子及び第3端子の表面の一部を覆うように形成される樹脂製のフレームを更に有する、ことが好ましい。

**【0025】**

上記のV C S E L モジュールでは、フレームは、V C S E L が視認可能な開口部が形成される支持面を有する、ことが好ましい。

10

**【0026】**

上記のV C S E L モジュールでは、支持面に支持され、V C S E L から出射された光を透過する光学素子を更に有する、ことが好ましい。

**【0027】**

上記の発光装置では、フレームは、光学素子の位置決めをするために、支持面の上方で、且つ、フレームの外壁から内側に迫り出した凸部を有する、ことが好ましい。

**【0028】**

上記のV C S E L モジュールでは、V C S E L からの放熱を第2電極へ向けて伝達するための放熱経路が、半導体装置において、第2端子と半導体装置の下面との間に形成される、ことが好ましい。

20

**【0029】**

上記のV C S E L モジュールでは、半導体装置は、第2電極と接続される第4端子、を有し、

第4端子は、第3端子が配置された第2側面又は第3側面の他方に沿った上面の端部に配置され、

V C S E L のカソードから半導体装置内に流入した電流は、第3端子及び第4端子により、半導体装置の左右に分かれて第2電極へ流れる、ことが好ましい。

**【0030】**

実施形態に係るV C S E L モジュールでは、V C S E L 及びスイッチング素子が一体化され且つ小型化が可能なV C S E L モジュールを提供することが可能となる。

30

**【図面の簡単な説明】****【0031】**

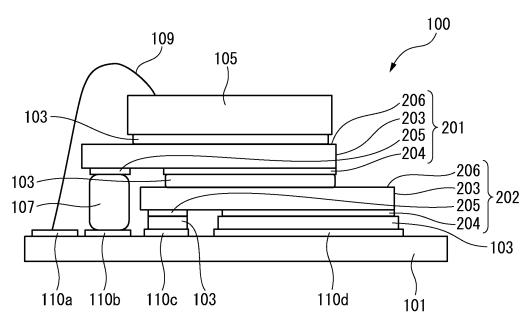

【図1】第1の実施形態に係るV C S E L モジュール100の側面図である。

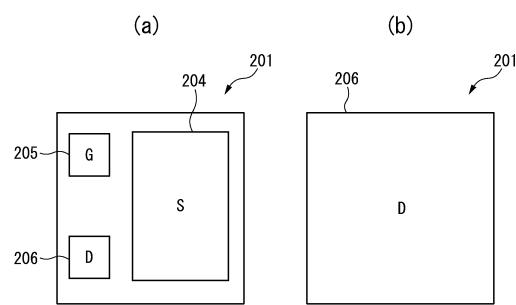

【図2】( a )はV C S E L モジュール100に含まれる第1のF E T 2 0 1の底面図であり、( b )は第1のF E T 2 0 1の上面図である。

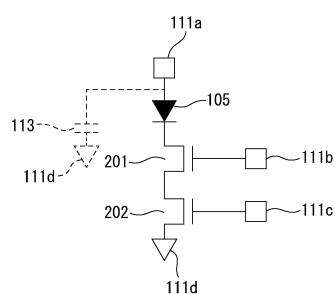

【図3】図1に示すV C S E L モジュール100の回路図である。

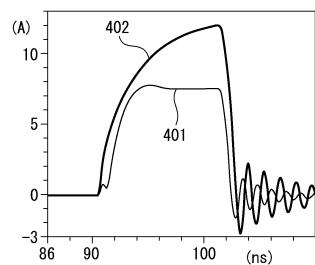

【図4】図1に示すV C S E L モジュール100の特性図である。

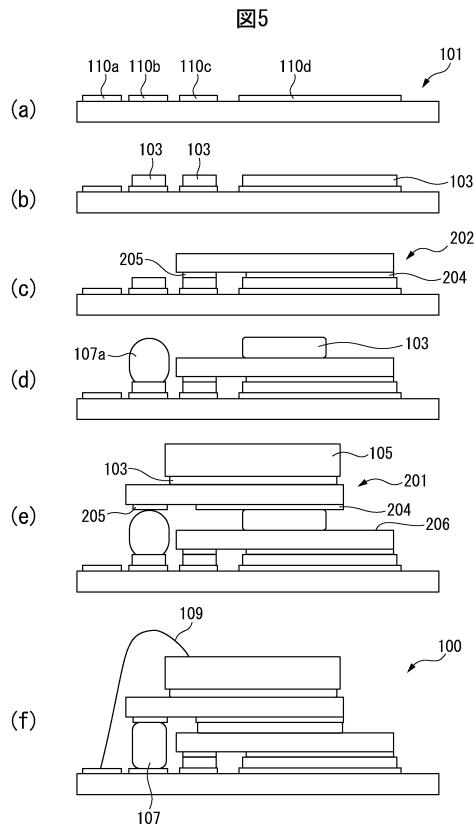

【図5】( a )～( f )は、V C S E L モジュール100の製造方法の説明図である。

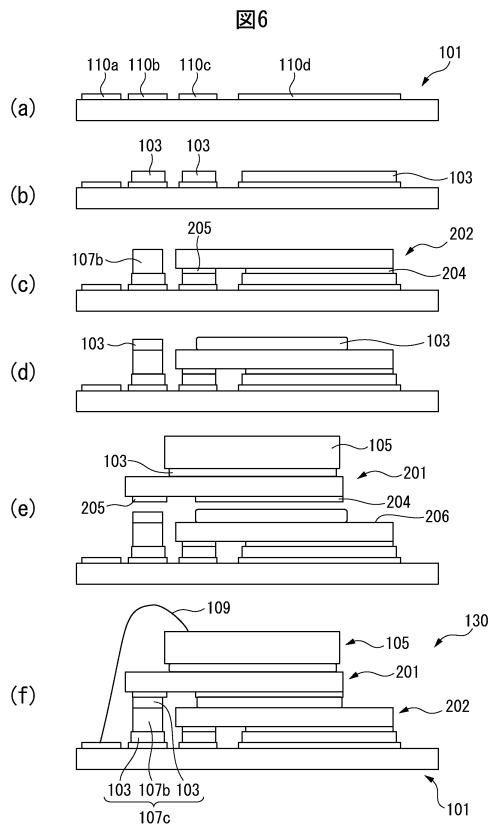

【図6】( a )～( f )は、V C S E L 100モジュールの第1変形例であるV C S E L モジュール130の製造方法の説明図である。

40

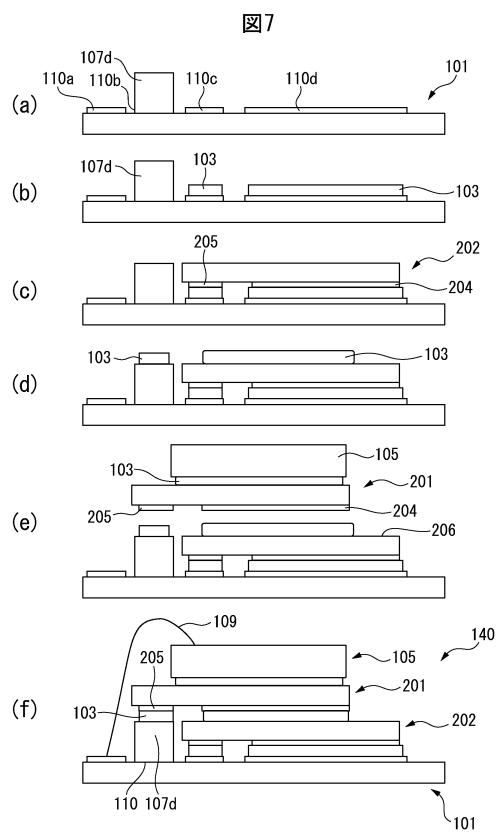

【図7】( a )～( f )は、V C S E L 100モジュールの第2変形例であるV C S E L モジュール140の製造方法の説明図である。

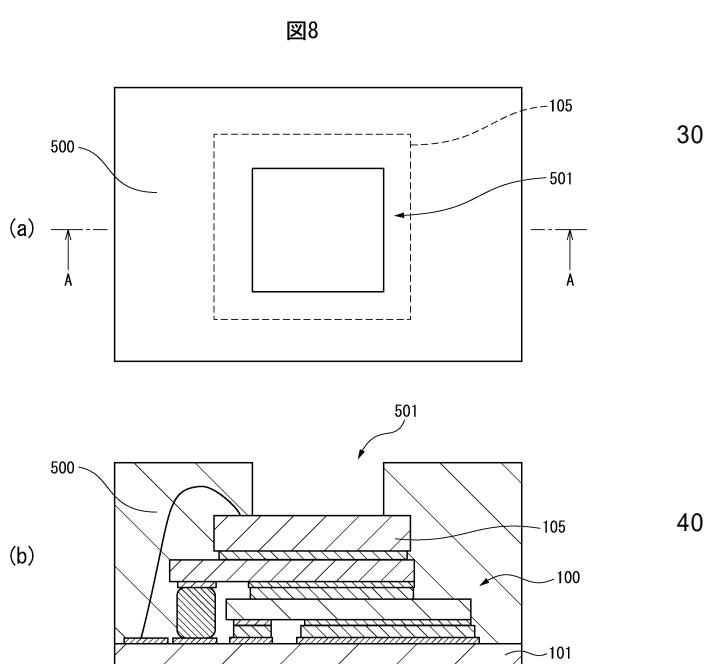

【図8】( a )はフレーム付きV C S E L 100モジュール100の上面図であり、( b )は( a )に示すA - A線に沿う断面図である。

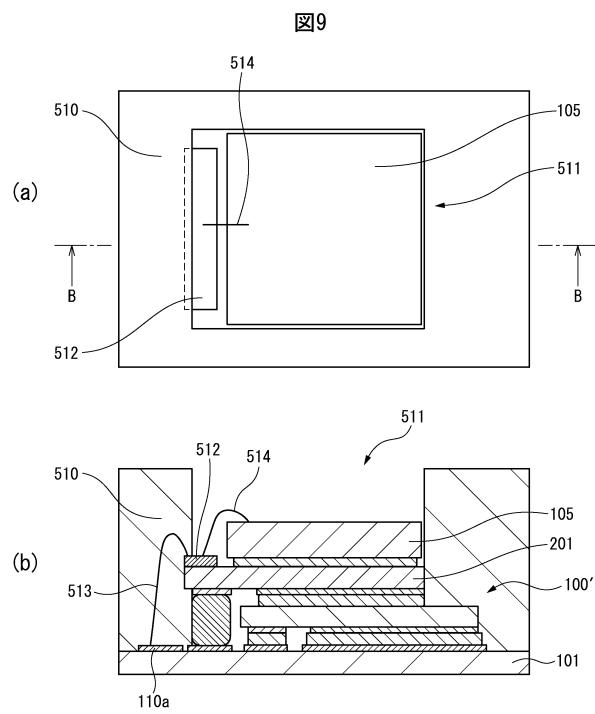

【図9】( a )はフレーム付きV C S E L 100モジュール100'の上面図であり、( b )は( a )に示すB - B線に沿う断面図である。

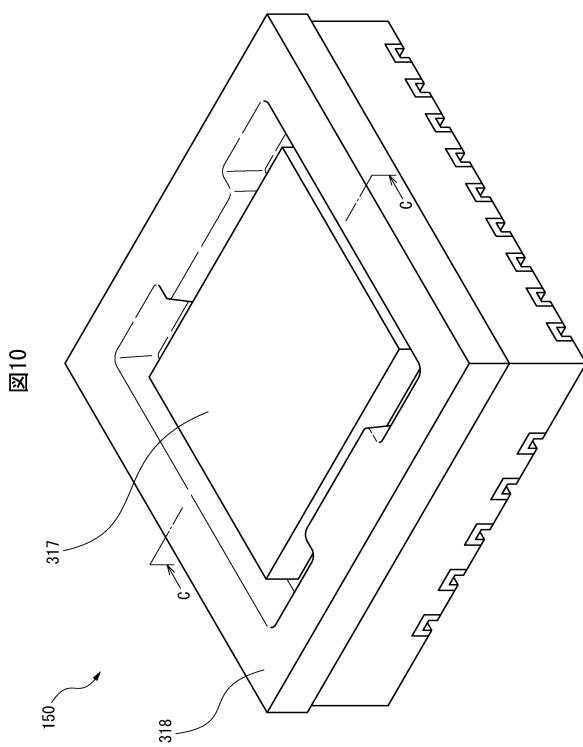

【図10】第2の実施形態に係るV C S E L モジュール150の斜視図である。

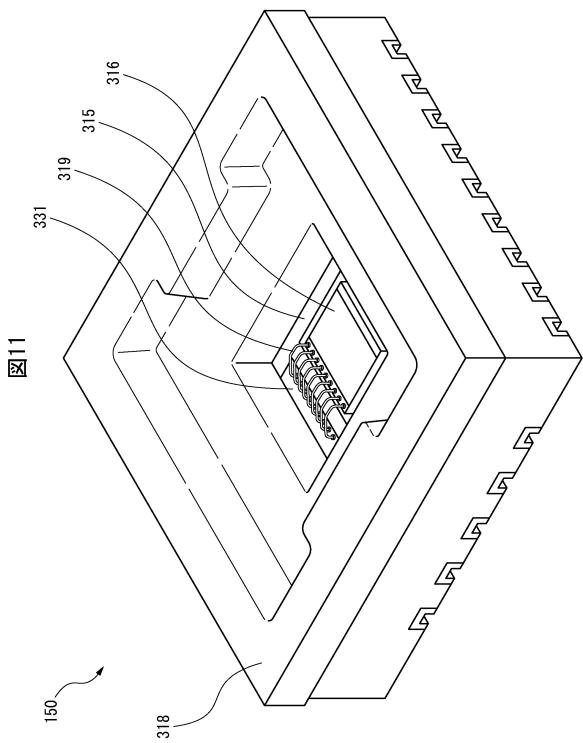

【図11】光学素子を除く図10に示すV C S E L モジュール150の斜視図である。

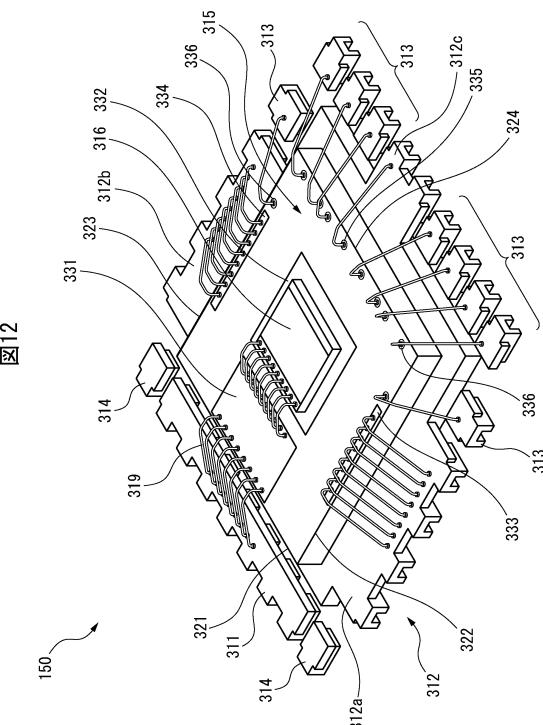

【図12】光学素子及びフレームを除く図10に示すV C S E L モジュール150の斜視図である。

50

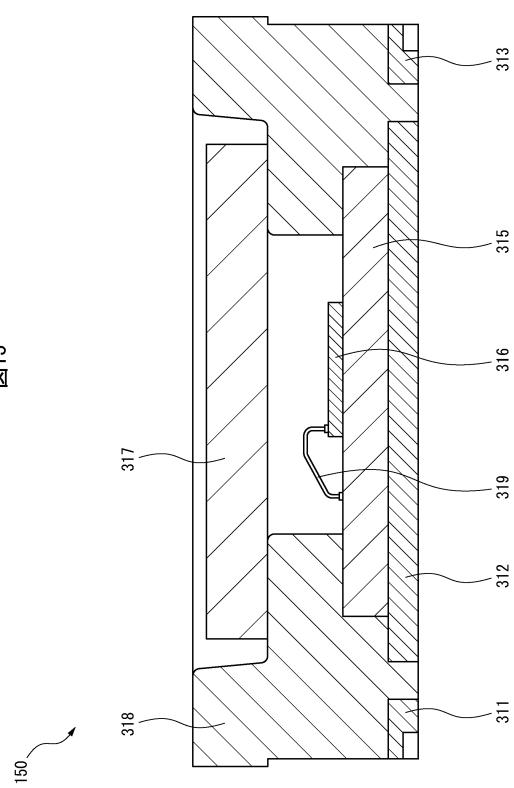

【図13】図10に示すC-C線に沿うVCSELモジュール150の断面図である。

【図14】図10に示すフレームの斜視図である。

【図15】図10に示すVCSELモジュール150の回路図である。

【図16】図10に示す第2電極、半導体装置及び発光素子の接続関係を概略的に示す図である。

【図17】図10に示すVCSELモジュール150の製造方法の説明図である。

【図18】図17に示す電極準備工程に対応する上面図である。

【図19】図17に示す半導体装置実装工程に対応する上面図である。

【図20】図17に示す発光素子実装工程に対応する上面図である。

【図21】図17に示すポンディングワイヤ工程に対応する上面図である。

【図22】図17に示すフレーム形成工程に対応する上面図である。

【図23】(a)はVCSELモジュール150においてフレーム318の基部以外を除いた部分の平面図であり、(b)は(a)のD-D線に沿う断面図であり、(c)は(a)のE-E線に沿う断面図である。

【図24】従来技術として示す測距装置のタイミングチャートである。

【図25】従来技術として示すレーザダイオードモジュール600の斜視図である。

【図26】図25に示すレーザダイオードモジュール600の回路図である。

#### 【発明を実施するための形態】

##### 【0032】

以下、VCSELモジュールの好ましい一実施形態を、図を参照して説明する。但し、本発明の技術範囲はそれらの実施形態に限定されず、特許請求の範囲に記載された発明とその均等物に及ぶものである。なお、図面の説明において、同一または相当要素には同一の符号を付し、重複する説明は省略する。説明のため部材の縮尺は適宜変更している場合がある。

##### 【0033】

図1は、第1の実施形態に係るVCSELモジュール100の側面図である。図1に示すように、VCSELモジュール100は、基板101、VCSEL105、第1のFET201、第2のFET202を備えている。基板101上には、第2のFET202、第1のFET201、VCSEL105が、図の下側からこの順番で積層している。なお、基板101には、コンデンサ113(図3参照)が実装されており、外部回路と接続するための端子電極が形成されたりするが、図1では、スタック構造を構成する部材、すなわち、VCSEL105、第1のFET201、第2のFET202、及び、これらの実装に係る部材のみを図示している。なお、レンズ等のVCSEL105の配光を制御する光学部品をVCSEL105上に配置したり、スタック構造の外側に壁状構造体を設けたりすることもあるが、これらについては後述する。

##### 【0034】

基板101は、基材が窒化アルミからなる平板であり、上面にパターン化した金属層(配線電極110a~110d等)を備えている。基材は、窒化アルミに限らず、FR4等の樹脂であっても良い。

##### 【0035】

VCSEL105は、上面にアノードが、下面にカソードが配置されたレーザダイオードの集合体である面発光型の光源である。アノードは、ポンディングワイヤ109により配線電極110aに接続し、カソードは、第1導電性接着部材103を介して第1のFET201のドレイン電極206に接続している。VCSEL105は、厚さが200μm、平面サイズが1.0mm×1.0mmであるが、大きさはこれに限定されない。

##### 【0036】

第1のFET201は、FETダイ203の上面全体にわたってドレイン電極206が設けられるとともに、下面にソース電極204とゲート電極205を備えている。第1のFET201に含まれるソース電極204は、第1導電性接着部材103を介して第2のFET202に含まれるドレイン電極206に接続し、ゲート電極205は、第2導電性

10

20

30

40

50

部材 107 を介して配線電極 110b に接続している。第 2 の FET 202 は、第 1 の FET 201 と同じものであり、第 2 の FET 202 に含まれるソース電極 204 及びゲート電極 205 は、それぞれ第 1 導電性接着部材 103 を介して配線電極 110d 及び配線電極 110c に接続している。第 1 及び第 2 の FET 201、202 は、厚さが 100 μm、平面サイズが 1.4 mm × 1.4 mm であり、各電極 204 ~ 206 は、Ni - Au メッキされている。

#### 【0037】

第 1 導電性接着部材 103 は、焼結 Ag、AuSn、半田など、接着性と導電性を有する部材であり、接着性と導電性を備えていればこれらに限定されるものではない。第 2 導電性部材 107 は、高さを出せる部材として、半田ボール 107a (図 5 参照) を含む。その他、第 2 導電性部材 107 に、はんだプレート、金バンプ、金属プレートなどが使用できる。第 1 導電性接着部材 103 及び第 2 導電性部材 107 は、電気抵抗率の低い金属材料が好ましい。インピーダンスを低く抑えることができ、VCSEL モジュール 100 は、短い期間に大きな電流を流しやすくなる。

10

#### 【0038】

図 2 は、VCSEL モジュール 100 に含まれる第 1 の FET 201 の底面図 (a) と上面図 (b) である。図 2 (a) に示すように、第 1 の FET 201 を底面には、「D」と示した小面積のドレイン電極 206、「S」と示した大面積のソース電極 204、「G」と示した小面積のゲート電極 205 が配置されている。図 2 (b) に示すように、第 1 の FET 201 の上面には、「D」と示した上面全体を占めるドレイン電極 206 が配置されている。

20

#### 【0039】

裏面のドレイン電極 206 は、上面のドレイン電極 206 と第 1 の FET 201 の内部で接続しているが、基板 101 (図 1 参照) の配線電極 110a ~ 110d 等とは接続していない。第 1 の FET 201 は、トレンチ構造をとっているため、電流が上面から下面に向かって流れる。また、第 2 の FET 202 は、第 1 の FET 201 と構造や特性が全く同じものなので説明は省略する。

#### 【0040】

図 3 は、VCSEL モジュール 100 の回路図である。図 1 では、回路素子として、VCSEL 105、第 1 及び第 2 の FET 201、202 が示されているだけであるが、前述のように、基板 101 にはコンデンサ 113 も実装されている。そこで、図 3 では、コンデンサ 113 及びコンデンサ 113 に係る回路を点線で示した。

30

#### 【0041】

図 3 に示すように、VCSEL モジュール 100 は、電源端子 111a、第 1 の FET 201 のゲート端子 111b、第 2 の FET 202 のゲート端子 111c、及び、ソース端子 111d を有する。図 3 に示すように、電源端子 111a とソース端子 111d の間に、VCSEL 105、第 1 の FET 201 及び第 2 の FET 202 が直列接続しており、コンデンサ 113 は、この直列回路に並列接続している。それぞれの端子 111a ~ 111d は、外部の装置と接続するために基板 101 の下面に形成された端子電極であり、配線電極 110a ~ 110d とは基板 101 に設けられたスルーホールやビアを介して電気的に接続されている。

40

#### 【0042】

外部電源 (不図示) は、主に非発光時、電源端子 111a を介してコンデンサ 113 を充電する。一方、発光時、VCSEL モジュール 100 には、10 (ns) 程度しかない短い期間に大きな電流を流す必要があるが、外部電源は、この期間には応答することができず、電源端子 111a からだけではこの 10 (ns) の期間に必要な電流が供給できない。そこで、VCSEL 105 を発光させる電流は、ほとんどがコンデンサ 113 の放電によるものとなる。

#### 【0043】

ゲート端子 111b には、外部から所定の定電圧が印加され、第 1 の FET 201 を電

50

流制御素子として機能させている。ゲート端子 111c には、外部から幅が 10 (ns) 程度の制御パルスが印加され、第 2 の FET 202 をスイッチング素子として機能させている。

#### 【0044】

図 4 は、ゲート端子 111c (図 3 参照) に幅が 10 (ns) の制御パルスを印加したとき、VCSEL 105 に流れる電流 401 をシミュレーションにより求めた特性図である。縦軸は電流 (A) を表しており、横軸は時間 (ns) を表している。図 4 には、比較のため、従来例として図 25 及び図 26 に示したレーザダイオードモジュール 600 のレーザダイオード DL に流れる電流 402 も示した。

#### 【0045】

シミュレーションでは、コンデンサ 113 から VCSEL 105 を経てコンデンサ 113 に戻る電流径路のインダクタンスを 1 (nH) としている。図 4 に示されるように、VCSEL 105 は、ゲート端子 111c に制御パルスが印加されると、電流の立ち上がりから 1 (ns) 以内に定電流動作に入る。一方、従来例の電流 402 は、制御パルスが印加されると、制御パルスの印加が終了するまで電流値が上昇し続ける。このように、VCSEL モジュール 100 では、VCSEL 105 の電流 401 の波形は、制御パルスに対し、立ち上がりが 1 (ns) 以下で頂部が平坦となり、平坦部が 8 (ns) 程度確保できている。VCSEL 105 からの出射光の光量は入力される電流に比例するので、平坦部の期間では VCSEL 105 からの出射光の光量を一定に保つことが可能となる。

#### 【0046】

図 5 は、VCSEL モジュール 100 の製造方法の説明図である。図 5 (a) ~ (f) では、各工程における特徴的な状態の側面図を示している。図 5 (a) ~ (f) では、図 1 と同様に、VCSEL 105、第 1 及び第 2 の FET 201、202、及び、これらに係る部材以外は図示していない。

#### 【0047】

図 5 (a) に示すように、最初に、上面に配線電極 110a ~ 110d 等を備えた基板 101 を準備する。次に、図 5 (b) に示すように、ボンディングワイヤ用の配線電極 110a を除き、配線電極 110b ~ 110d の上面に第 1 導電性接着部材 103 を塗布する。次に、図 5 (c) に示すように、第 2 の FET 202 を、基板 101 に接続する。このとき、第 1 導電性接着部材 103 を介して、ゲート電極 205 とソース電極 204 がそれぞれ配線電極 110c、110d に重なるよう第 2 の FET 202 を配置する。

#### 【0048】

次に、図 5 (d) に示すように、半田ボール 107a を配線電極 110b 上に配置するとともに、第 2 の FET 202 の上面に第 1 導電性接着部材 103 を塗布する。なお、半田ボール 107a と配線電極 110b の間にはんだボール 107a を固定するため第 1 導電性接着剤 103 が介在しているが、フラックスなど他の方法ではんだボール 107a を固定できれば、第 1 導電性接着部材 103 は必ずしも必要ではない。

#### 【0049】

次に、図 5 (e) に示すように、第 1 の FET 201 を第 2 の FET 202 の上面に接続する。なお、第 1 の FET 201 の上面には、予め VCSEL 105 が第 1 導電性接着部材 103 で接続しているものとする。また、第 1 の FET 201 に含まれるゲート電極 205 は、半田ボール 107a に接続し、ソース電極 204 は、第 1 導電性接着部材 103 を介して第 2 の FET 202 のドレイン電極 206 と接続する。

#### 【0050】

最後に、図 5 (f) に示すように、VCSEL モジュール 100 を加熱して接続状態を安定化する。このとき、まず、最初の加熱で第 1 導電性接着部材 103 を硬化させる。次に、温度を上げて半田ボール 107a を溶融させ、半田ボール 107a を第 1 導電性接着部材 103 と接続する。このとき、半田ボール 107a と第 2 の FET 202 のゲート電極 205 も接続する。このようにして、半田ボール 107a と第 1 導電性接着部材 103 の接続により第 2 導電性部材 107 が完成する。その後、ボンディングワイヤ 109 で V

10

20

30

40

50

CSEL105のアノードと配線電極110aの間を接続する。なお、第2導電性部材107において第1導電性接着部材103を使用しない場合、半田ボール107は、電極110bに直接的に接続される。

#### 【0051】

前述のように、VCSELモジュール100は、VCSEL105と、電流制御素子である第1のFET201と、スイッチング素子である第2のFET202と、基板101と4段に積み重なる様な構造を有している。また、第1のFET201は必ずしも必要がないので、VCSELモジュール100は、VCSEL105と、スイッチング素子となる第2のFET202と、基板101とが、3段に積み重なる様な構造（3段スタック構造）を有していても良い。

10

#### 【0052】

VCSEL105では、上面のアノードから下面のカソードに向かってほぼ直線的に電流が流れる。同様に、第1のFET201及び第2のFET202も、上面のドレイン電極206から下面のソース電極204に向かってほぼ直線的に電流が流れる。つまり、VCSEL105と第1及び第2のFET201、202からなるスタック構造では、短い距離で、上部から下部に向かって電流が直線的に流れる。この結果、VCSELモジュール100のスタック構造では、インダクタンスが最小化するため、電流の立ち上り及び立ち下がり特性が改善する。また、このスタック構造は、電流径路中に電流制御素子として機能する第1のFET201を備えているため、極めて短いパルス電流が印加されたとしても、その間で電流が上昇し続けることがなくなる（図4の電流401参照）。

20

#### 【0053】

以上のように、VCSELモジュール100は、VCSEL105を含む電流径路のインダクタンスを最小化することにより、VCSEL105に流れるパルス電流の立ち上り及び立ち下り時間を1（ns）以下に抑えられるのに加え、制御パルス幅が極めて短くても、その制御パルス幅の中で、電流制御素子として機能する第1のFET201により電流波形の頂部を平坦にする。したがって、VCSELモジュール100は、VCSEL105に流すパルス電流の波形が方形波に近づくように改善する（図4の電流401参照）。

#### 【0054】

VCSELモジュール100では、第1のFET201を電流制御素子として機能させ、第2のFET202をスイッチング素子として機能させていたが、第1のFET201及び第2のFET202の配置を上下で逆にしても良い。

30

#### 【0055】

図5（e）で説明したように、第1のFET201上に予めVCSEL105が実装されている状態で、第1のFET201を第2のFET202の上部に配置していたが、第1のFET201を第2のFET202の上部に配置してから第1のFET201上にVCSEL105を実装しても良い。

#### 【0056】

VCSELモジュール100では、第1のFET201及び第2のFET202に同じ素子を利用していたが、それぞれにサイズの異なるFETを用いてもスタック構造を実現することは可能であり、そのようにしても同様の効果を得ることができる。

40

#### 【0057】

図6は、VCSELモジュール100の第1変形例であるVCSELモジュール130とその製造方法の説明図である。図6（a）～（f）では、各工程における特徴的な状態の側面図を示している。なお、図6（a）～（f）でも、コンデンサ113（図3参照）など、VCSEL105、第1及び第2のFET201、202並びにこれらの実装に係る部材以外は表示していない。また、付加する可能性がある光学素子やフレームも図示していない。

#### 【0058】

前述のように、第1のFET201のゲート電極205と基板101の配線電極110bとを接続する第2導電性部材107は、半田ボール107aを含む部材に限られない。

50

そこで、V C S E L モジュール 130 では、第 2 導電性部材 107 に金属片を含む V C S E L モジュール 130 について説明する。

#### 【0059】

最初に、図 6 (f) を用いて、V C S E L モジュール 130 の構造を説明する。図 6 (f) に示すように、V C S E L モジュール 130 でも、基板 101 上に、第 2 の F E T 202、第 1 の F E T 201、V C S E L 105 が、図の下側からこの順番で積層している。このとき、第 2 導電性部材 107c では、下から、第 1 導電性接着部材 103、金属片 107b、第 1 導電性接着部材 103 が積層している。図 6 (f) と図 1 とを比較すると、V C S E L モジュール 130 は、V C S E L モジュール 100 に対し、基本的な構造は共通であり、第 1 の F E T 201 のゲート電極 205 と配線電極 110b とを接続する第 2 導電性部材 107c だけが相違する。なお、V C S E L モジュール 100 と同様に、V C S E L モジュール 130 においても、必ずしも第 1 の F E T 201 は必要ではない。

10

#### 【0060】

図 6 (a) に示すように、最初に、上面に配線電極 110a ~ 110d を備えた基板 101 を準備する。次に、図 6 (b) に示すように、ボンディングワイヤ用の配線電極 110a を除き、配線電極 110b ~ 110d の上面に第 1 導電性接着部材 103 を塗布する。次に、図 6 (c) に示すように、第 2 の F E T 202 と金属片 107b を、基板 101 に接続する。このとき、第 1 導電性接着部材 103 を介して、ゲート電極 205 とソース電極 204 がそれぞれ配線電極 110c、110d に重なるよう、第 2 の F E T 202 を配置する。同時に、第 1 導電性接着部材 103 を介して、配線電極 110b に重なるよう、金属片 107b を配置する。

20

#### 【0061】

次に、図 6 (d) に示すように、金属片 107b 及び第 2 の F E T 202 の上面に第 1 導電性接着部材 103 を塗布する。次に、図 6 (e) に示すように、V C S E L 105 を搭載した第 1 の F E T 201 を金属片 107b 及び第 2 の F E T 202 の上面に接続する。最後に、図 6 (f) に示すように、V C S E L モジュール 100 を加熱して第 1 導電性接着部材 103 を硬化させる。このとき、第 2 導電性部材 107c も完成する。

30

#### 【0062】

第 2 導電性部材 107 が半田ボール 107a を含む V C S E L モジュール 100 では、配線電極 110b 上の硬化した第 1 導電性接続部材 103 に半田ボール 107a を溶融させて接続させることとなるため、温度プロファイルが複雑化し製造条件が難しくなる。これに対し、V C S E L モジュール 130 では、第 1 導電性接続部材 103 の硬化だけで金属片 107b との接続が完了するので、V C S E L モジュール 130 の温度プロファイルが簡略化する。つまり、加熱に対し、主に第 1 導電性樹脂 103 の硬化だけを考慮すればよいので、製造条件が容易になる。また、金属片 107b は、図 6 (c) に示す工程内での第 2 の F E T 202 と一緒に配置されるため、同工程の負担増は僅かである。また、金属片 107b は、半田ボール 107 に比べ外形形状のばらつきが少ないことも製造工程の容易化に寄与する。

#### 【0063】

図 7 は、V C S E L モジュール 100 の第 2 変形例である V C S E L モジュール 140 とその製造方法の説明図である。図 7 (a) ~ (f) では、各工程における特徴的な状態の側面図を示している。なお、図 7 (a) ~ (f) でも、コンデンサ 113 (図 3 参照)、V C S E L 105、第 1 及び第 2 の F E T 201、202 並びにこれらの実装に係る部材以外は表示していない。また、付加する可能性がある光学素子やフレームも図示していない。

40

#### 【0064】

V C S E L モジュール 100 及び V C S E L モジュール 130 は、それぞれ半田ボール 107a 及び金属片 107b を含む第 2 導電性部材 107、107c を採用していた。しかしながら、必ずしも第 1 の F E T 201 のゲート電極 205 と基板 101 の配線電極 110b との接続に第 2 導電性部材 107 を必要としない。そこで、第 2 導電性部材 107

50

、107b等を使用しないVCSELモジュール140について説明する。

#### 【0065】

最初に、図7(f)により、VCSELモジュール140の構造を説明する。図7(f)に示すように、VCSELモジュール140も、基板101上に、第2のFET202、第1のFET201、VCSEL105が、図の下側からこの順番で積層している。このとき、配線電極110bの上部には、厚銅メッキ層107が形成され、第1のFET201のゲート電極205は、第1導電性接着部材103及び厚銅メッキ層107dを介して配線電極110bと接続している。図7(f)と図1とを比較すると、VCSELモジュール140は、VCSELモジュール100に対し、基本的な構造は共通であり、第1のFET201のゲート電極205と配線電極110bとを接続する構造だけが相違する。なお、VCSELモジュール100と同様に、VCSELモジュール130においても、必ずしも第1のFET201は必要ではない。

10

#### 【0066】

図7(a)に示すように、最初に、上面に配線電極110a～110d等を備えた基板101を準備する。このとき、配線電極110bは、上部にメッキ法で形成した厚銅メッキ層107dを備え、他の配線電極110a、110c、110dよりも厚くなっている。次に、図7(b)に示すように、ポンディングワイヤ用の配線電極110a及び厚銅メッキ層107dを備える配線電極110bを除き、配線電極110c、110dの上面に第1導電性接着部材103を塗布する。次に、図7(c)に示すように、第2のFET202を、基板101に接続する。このとき、第1導電性接着部材103を介して、ゲート電極205とソース電極204がそれぞれ配線電極110c、110dに重なるよう第2のFET202を配置する。

20

#### 【0067】

次に、図7(d)に示すように、厚銅メッキ層107d及び第2のFET202の上面に第1導電性接着部材103を塗布する。次に、図7(e)に示すように、VCSEL105を搭載した第1のFET201を厚銅メッキ層107d及び第2のFET202の上面に接続する。最後に、図7(f)に示すように、VCSELモジュール140を加熱して第1導電性接着部材103を硬化させる。このとき、第2のFET202のゲート電極205と配線電極110bとの接続も完成する。

30

#### 【0068】

図7(b)～(f)に示したVCSELモジュール140の製造工程は、図6(b)～(f)に示したVCSELモジュール130の製造工程よりも簡略化している。すなわち、VCSELモジュール140の製造工程では、第2導電性部材107cを構成する工程がない。

#### 【0069】

図8は、第1フレーム500を追加したVCSELモジュール100を示す図である。図8(a)は上面図を示し、図8(b)は図8(a)のA-A線に沿う断面図である。

#### 【0070】

第1フレーム500は、黒色の樹脂製の部材であり、中央の開口部501の部分からVCSEL105の一部が露出している箇所を除いて、VCSELモジュール100全体を覆うように基板101の上部に配置される。第1フレーム500によってVCSELモジュール100が覆われることによって、環境耐性が向上し、長期間の使用に適した状態となる。VCSEL105から出射した光は、開口部501を介して外部に出射される。

40

#### 【0071】

所定の光学特性を有する光学素子を、開口部501を覆うように配置しても良い。光学素子としては、例えばポリアリレート樹脂等の熱可塑性樹脂、シリコーン樹脂等の熱硬化性樹脂、及びエポキシ樹脂等の紫外線硬化樹脂で形成された光透過性部材を利用することができます。光学素子を利用することにより、VCSEL105から出射された光を成形及び均一化することで、所望の配光分布を有する光を出射することが可能となる。

#### 【0072】

50

図9は、第2フレーム510を追加したVCSELモジュール100'を示す図である。図9(a)は上面図を示し、図9(b)は図9(a)のB-B線に沿う断面図である。

#### 【0073】

VCSELモジュール100'は、VCSELモジュール100をボンディングワイヤ109の代わりに、第1のFET201の上面に配置された中継電極512、第1ボンディングワイヤ513、及び、第2ボンディングワイヤ514を用いたものであって、他の構成は同一である。配線電極110aと中継電極512とが第1ボンディングワイヤ513で接続され、中継電極512とVCSEL105のアノードが第2ボンディングワイヤ514で接続される。

#### 【0074】

第2フレーム510は、黒色の樹脂製の部材であり、中央の開口部511の部分からVCSEL105全体及び中継電極512の一部が露出している箇所を除いて、VCSELモジュール100'全体を覆うように基板101の上部に配置される。第2フレーム510によってVCSELモジュール100'が覆われることによって、環境耐性が向上し、長期間の使用に適した状態となる。VCSEL105から出射した光は、開口部511を介して外部に出射される。なお、図8の例と同様に、所定の光学特性を有する光学素子を、開口部511を覆うように配置しても良い。

10

#### 【0075】

図9の例では、開口部511の開口面積を大きくしたので、VCSEL105及び第2ボンディングワイヤ514を除いたVCSELモジュール100'をフレーム510で覆った後に、VCSEL105を実装し且つ第2ボンディングワイヤ514で接続することが可能となった。これにより、設計の自由度が増加する。

20

#### 【0076】

本実施形態に係るVCSELモジュールによれば、光源として実装面に対し垂直方向に面発光する垂直共振器型面発光レーザ(VCSEL)に流すパルス電流が短いパルス幅であっても、立ち上がり時間を1(ns)以下に抑え、さらに、この波形が方形波に近づくよう改善されたVCSELモジュールを提供することが可能となる。

#### 【0077】

VCSELモジュールの一実施形態によると、VCSELと、VCSELの下に配置された第1のFETと、第1のFETの下に配置された第2のFETとを備え、第1のFET又は第2のFETの一方は、スイッチング素子であって、他方は、電流制御素子であることを特徴とする。

30

#### 【0078】

上記のVCSELモジュールでは、VCSELとスイッチング素子と電流制御素子が4段スタック構造を構成している。VCSELモジュールに含まれるVCSELは、上面のアノードから下面のカソードに向かってほぼ直線的に電流が流れる。同様に、スイッチング素子及び電流制御素子として使用する第1及び第2のFETも、上面のドレイン電極から下面のソース電極に向かってほぼ直線的に電流が流れる。したがって、VCSELと第1及び第2のFETからなるスタック構造では、上部から下部に向かって電流が直線的に流れる。この結果、このスタック構造は、電流径路が直線的で短くなっているため、インダクタンスが最小化する。また、スタック構造は、電流径路中に電流制御素子を備えているため、パルス幅で与えられる短い期間中、電流が上昇し続けることがなくなる。

40

#### 【0079】

上記のVCSELモジュールでは、さらに、VCSELに電流を供給するコンデンサを備えていても良い。

#### 【0080】

上記のVCSELモジュールでは、さらに、回路基板を備え、第1のFETのゲート電極と回路基板の配線電極とは、半田ボール、スタッズバンプ又は金属片を介して接続していくても良い。

#### 【0081】

50

上記のV C S E L モジュールでは、さらに、回路基板を備え、前記第1のF E T のゲート電極と接続する前記回路基板の配線電極は、前記回路基板に形成された他の配線電極より厚くても良い。

#### 【 0 0 8 2 】

上記のV C S E L モジュールでは、V C S E L を含む電流径路のインダクタンスを最小化することにより、V C S E L に流れるパルス電流の立ち上りが1 n s 以下に抑えられるのに加え、パルス電流の幅で与えられる短い期間中であっても、電流制御素子により電流波形の頂部が平坦になる。したがって、上記のV C S E L モジュールでは、V C S E L に流すパルス電流の波形が方形波に近づくよう改善される。

#### 【 0 0 8 3 】

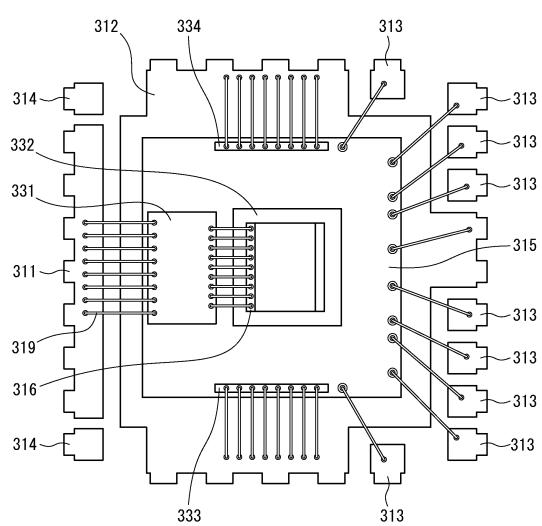

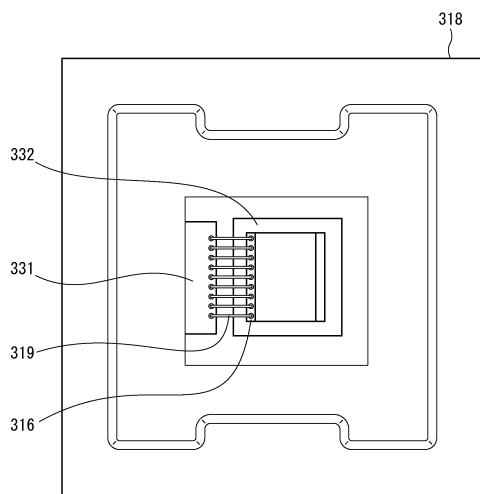

図10は、第2の実施形態に係るV C S E L モジュール150の斜視図であり、図11は光学素子を除く図10に示すV C S E L モジュール150の斜視図であり、図12は光学素子及びフレームを除く図10に示すV C S E L モジュール150の斜視図であり、図13は図10に示すC - C 線に沿うV C S E L モジュール150の断面図である。

#### 【 0 0 8 4 】

V C S E L モジュール150は、第1電極311と、第2電極312と、9個の監視制御電極313と、一対のダミー電極314と、半導体装置315と、V C S E L 316と、光学素子317と、フレーム318と、複数のボンディングワイヤ319とを有するリードフレームパッケージである。V C S E L モジュール150では、第2電極312、半導体装置315及びV C S E L 316は、重畠して配置される。半導体装置315は、矩形の平面形状を有し、第1辺321、第2辺322、第3辺323及び第4辺324を有する。

10

#### 【 0 0 8 5 】

第1電極311、第2電極312、9個の監視制御電極313及び一対のダミー電極314のそれぞれは、アルミニウム及び銅等の放熱性が高い導電性部材で形成され、互いに離隔して配置される。なお、電極の数は一例であって、上記に限定されない。第1電極311は、長手方向が延伸する略矩形状の平面形状を有し、矩形の平面形状を有する半導体装置315の第1辺321の延伸方向に平行に長手方向が延伸するように配置される。第1電極311は、第1辺321の延伸方向に沿って配置される複数のボンディングワイヤ319を介して半導体装置315の表面に配置される第1端子31を介してV C S E L 316のアノードに電気的に接続される。

20

#### 【 0 0 8 6 】

第2電極312は、半導体装置315が実装され、半導体装置315の第2辺322、第3辺323及び第4辺324のそれぞれに近接して配置される第1突出部312a、第2突出部312b及び第3突出部312cを有する。第2電極312は、一端が第1突出部312a、第2突出部312b及び第3突出部312cに接続される複数のボンディングワイヤ319を介して半導体装置315に電気的に接続される。第2電極312は、金属を含有する樹脂材等の熱伝導率が高い接着部材を介して半導体装置315に熱的に接続される。

30

#### 【 0 0 8 7 】

9個の監視制御電極313のうち、5個の監視制御電極313は、第1突出部312aと第3突出部312cとの間に半導体装置315の第2辺322及び第4辺324に沿うように配置される。9個の監視制御電極313の他の4個の監視制御電極313は、第2突出部312bと第3突出部312cとの間に半導体装置315の第3辺323及び第4辺324に沿うように配置される。9個の監視制御電極313のそれぞれは、ボンディングワイヤ319を介して半導体装置315に電気的に接続される。

40

#### 【 0 0 8 8 】

一対のダミー電極314は、第1電極311の長手方向の両端のそれぞれに第1電極311から離隔して配置される。

#### 【 0 0 8 9 】

50

半導体装置 315 は、第1端子 331 と、第2端子 332 と、第3端子 333 と、第4端子 334 と、第5端子 335 と、9個の監視制御端子 336 を有し、VCSEL 316 のアノードとカソードとの間に流れる駆動電流を監視制御する。

#### 【0090】

第1端子 331 は、矩形の平面形状を有し、第1電極 311 に対向する第1辺 321 に沿って半導体装置 315 の表面に配置される。第1端子 331 の第1電極 311 に対向する第1辺 321 に沿う辺の長さは、VCSEL 316 の第1電極 311 に対向する第1辺 321 に沿う辺よりも長い方が好ましい。VCSEL 316 の少なくとも1つの辺のほぼ全てに配置されるアノード端子からのワイヤの数を最大とすることができ、配線抵抗による電圧降下が抑制される。また、第1端子 331 の第1電極 311 に対向する第1辺 321 に直交する辺の長さは、VCSEL 316 の第1電極 311 に対向する第1辺 321 に沿う辺よりも短い方が好ましい。経路が短くなるので、配線抵抗による電圧降下が抑制される。なお、第1端子 331 の第1電極 311 に対向する第1辺 321 に直交する辺の長さは、半導体装置 315 及び VCSEL 316 のサイズに応じて決定され、第1電極 311 に対向する第1辺 321 に沿う辺よりも長くてもよく、同一であってもよい。第1端子 331 の第1辺 321 に近接する領域には、第1電極 311 と第1端子 331 との間を電気的に接続する複数のボンディングワイヤ 319 が第1辺 321 の延伸方向に沿って配置される。第1端子 331 の第1辺 321 から離隔する領域には、第1電極 311 と VCSEL 316 のアノードとの間を電気的に接続する複数のボンディングワイヤ 319 が第1辺 321 の延伸方向に沿って配置される。

10

#### 【0091】

第2端子 332 は、矩形の平面形状を有し、半導体装置 315 の表面の中央に配置される。第2端子 332 には、VCSEL 316 が実装され、第2端子 332 と VCSEL 316 のカソードとの間が電気的に接続される。

20

#### 【0092】

第3端子 333 及び第4端子 334 のそれぞれは、第1辺 321 に直交する第2辺 322 及び第3辺 323 に長手方向が延伸する矩形状の平面形状を有し、第2辺 322 及び第3辺 323 のそれぞれに沿って半導体装置 315 の表面に配置される。第3端子 333 には、第1突出部 312a と第3端子 333 との間を電気的に接続する複数のボンディングワイヤ 319 が第2辺 322 の延伸方向に沿って配置される。第4端子 334 には、第2突出部 312b と第4端子 334 との間を電気的に接続する複数のボンディングワイヤ 319 が第3辺 323 の延伸方向に沿って配置される。

30

#### 【0093】

第5端子 335 は、矩形の平面形状を有し、第4辺 324 の中央部の近傍に配置される。第5端子 335 には、第3突出部 312c と第5端子 335 との間を電気的に接続するボンディングワイヤ 319 が配置される。

#### 【0094】

9個の監視制御端子 336 のそれぞれは、矩形の平面形状を有し、第2辺 322、第3辺 323 及び第4辺 324 の近傍に配置される。9個の監視制御端子 336 のそれぞれには、9個の監視制御電極 313 との間を電気的に接続するボンディングワイヤ 319 が配置される。

40

#### 【0095】

半導体装置 315 は、複雑な回路構成が可能な片面の配線板とも言え、配線設計の自由度が高い。なお、配線設計の自由度が高いとは、配線の幅が  $1 \mu m$  以上、 $5 \mu m$  以上、又は  $10 \mu m$  以上であり、 $50 \mu m$  以下、 $100 \mu m$  以下、又は  $200 \mu m$  よりも狭くてよく、配線のピッチが  $1 \mu m$  以上、 $5 \mu m$  以上、又は  $10 \mu m$  以上であり、 $50 \mu m$  以下、 $100 \mu m$  以下、又は  $200 \mu m$  よりも狭く構成された配線があることである。また、例えば、半導体装置 315 の各辺の好適な位置に、第1端子 331、第2端子 332、第3端子 333、第4端子 334、第5端子 335、9個の監視制御端子 336 を容易に配置できる。このとき、ワイヤ長が最短となるように、それぞれの端子の近傍に、第1電極 3

50

11、第2電極312、監視制御電極313、ダミー電極314を配置することも容易であり、各端子と各電極のワイヤ長を最短にできるから、ボンディングワイヤ319が断線するリスクが低くなる。また、各電極の配置が容易であるから、配線設計の自由度が低いリードフレームを使用できる。なお、配線設計の自由度が低いとは、例えば、配線の幅が200μm以上、又は300μm以上であり、配線のピッチが200μm以上である。リードフレームは、例えば、銅などの金属材料で構成されてもよく、單一や单層の金属材料で構成されてもよく、また、表層には、全周に渡って、金及び銀などのメッキが形成されてもよい。

#### 【0096】

V C S E L 3 1 6 では、レーザ光を出射する複数のエミッタが表面に等間隔にアレイ状に配置される。V C S E L 3 1 6 は、例えば364(26×14)個のエミッタを有し、364個のエミッタは、0.0385mmのピッチで配列される。V C S E L 3 1 6 は、表面に配置されるアノードと、裏面に配置されるカソードとを有し、アノードとカソードとの間に電流が供給されることに応じて発光する。10

#### 【0097】

光学素子317は、例えばポリアリレート樹脂等の熱可塑性樹脂、シリコーン樹脂等の熱硬化性樹脂、及びエポキシ樹脂等の紫外線硬化樹脂で形成された光透過性部材である。光学素子317の表面及び裏面の少なくとも一方には、V C S E L 3 1 6 から出射された光を拡散するシボ加工等された拡散面が形成される。光学素子317は、V C S E L 3 1 6 から出射された光を成形及び均一化することで、所望の配光分布を有する光を出射する。光学素子317は、V C S E L モジュール150の発光効率が低下しないようにV C S E L 3 1 6 から出射された光の波長を透過する材質であることが好ましい。光学素子317の透過率は、90%以上が好ましく、95%以上が更に好ましい。20

#### 【0098】

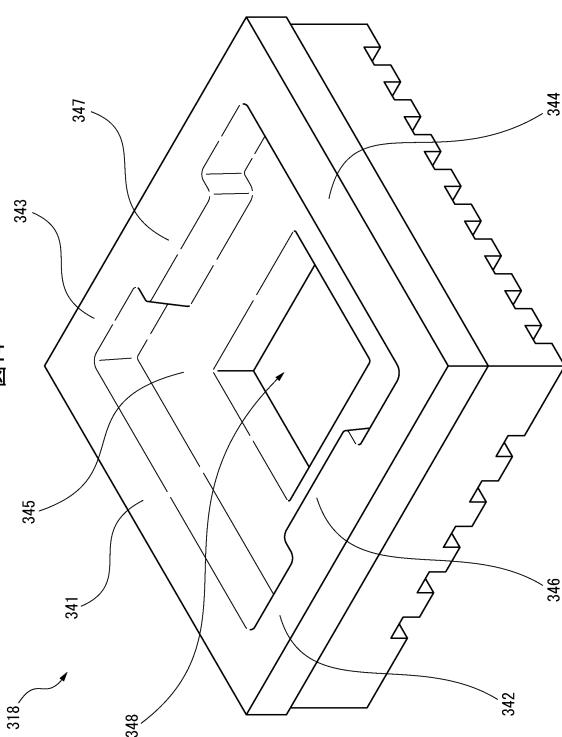

図14は、フレーム318の斜視図である。

#### 【0099】

フレーム318は、黒色の樹脂製の部材であり、第1壁部341と、第2壁部342と、第3壁部343と、第4壁部344と、支持面345と、第1凸部346と、第2凸部347とを有する。フレーム318は、第1電極311及び第2電極312の表面、及び第1端子331の一部、及び第3端子333及び第4端子334を覆うように配置される。なお、第1電極311、第2電極312、監視制御電極313及びダミー電極314の底面は、フレーム318に覆われない。フレーム318の底面は、第1電極311、第2電極312、監視制御電極313及びダミー電極314の底面と同一面を形成する。第1電極311、第2電極312、監視制御電極313及びダミー電極314の底面は、例えば、不図示のヒートシンクに面接触可能であるから、大きな放熱経路を有すると言える。30

#### 【0100】

第1壁部341、第2壁部342、第3壁部343及び第4壁部344のそれぞれは、半導体装置315の第1辺321、第2辺322、第3辺323及び第4辺24のそれに平行に延伸する。支持面345は、第1壁部341、第2壁部342、第3壁部343及び第4壁部344に囲まれ、且つV C S E L 3 1 6 が視認可能な矩形の開口部348が中央に形成される。40

#### 【0101】

第1凸部346は、第2壁部342に対向する第3壁部343の方向に突出するよう、第2壁部342の内壁の中央部に配置される。第2凸部347は、第3壁部343に対向する第2壁部342の方向に突出するよう、第3壁部343の内壁の中央部に配置される。第1凸部346及び第2凸部347のそれぞれは、光学素子317の端部に対向するよう配置される。

#### 【0102】

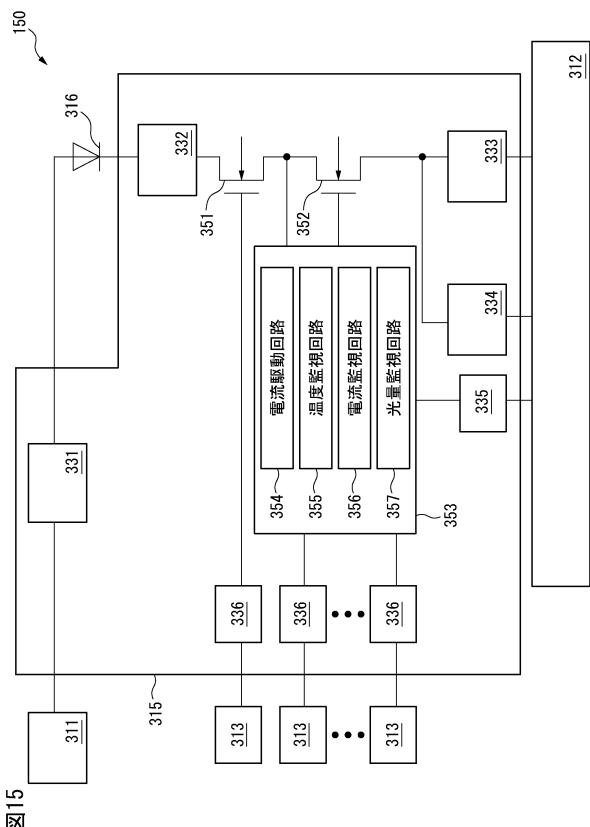

図15は、V C S E L モジュール150の回路図である。

#### 【0103】

50

半導体装置 315 は、電流制御素子 351 と、スイッチング素子 352 と、監視制御回路 353 とを更に有する。半導体装置 315 は、V C S E L 316 に直列接続される電流制御素子 351 及びスイッチング素子 352 を制御すると共に、監視制御回路 353 が V C S E L 316 に流れる電流等を監視することで、V C S E L 316 の発光を監視制御する。

#### 【0104】

電流制御素子 351 及びスイッチング素子 352 は、n 型の金属酸化膜半導体電界効果トランジスタ (Metal-Oxide-Semiconductor Field Effect Transistor、M O S F E T) である。電流制御素子 351 及びスイッチング素子 352 は、V C S E L 316 を介して第 2 端子 332 と、第 3 端子 333 及び第 4 端子 334 に接続され、電流制御素子 351 は駆動電流量を制御し、スイッチング素子 352 は、駆動電流のオンとオフの切り替えを制御する駆動素子である。

#### 【0105】

電流制御素子 351 のゲートは、監視制御端子 336 の 1 つを介して監視制御電極 313 の 1 つに接続される。電流制御素子 351 のソースはスイッチング素子 352 のドレインに接続され、電流制御素子 351 のドレインは第 2 端子 332 を介して V C S E L 316 のカソードに接続される。スイッチング素子 352 のゲートは監視制御回路 353 に接続され、スイッチング素子 352 のソースは第 3 端子 333 及び第 4 端子 334 を介して第 2 電極に接続される。

#### 【0106】

電流制御素子 351 は、監視制御電極 313 に印加される電流設定信号に基づいて、V C S E L 316 のアノード (V C S E L 第 1 端子とも言う) とカソード (V C S E L 第 2 端子とも言う)との間及び電流制御素子 351 のソースとドレインとの間に流れる駆動電流の電流量を制御する。

#### 【0107】

スイッチング素子 352 は、監視制御回路 353 によって生成される周期信号に基づいてオンオフすることで、V C S E L 316 のアノードとカソードとの間及びスイッチング素子 352 のソースとドレインとの間に流れる駆動電流を所定の周期でオンオフする。。

#### 【0108】

監視制御回路 353 は、電流駆動回路 354 と、温度監視回路 355 と、電流監視回路 356 と、光量監視回路 357 とを有する。電流駆動回路 354 は、監視制御端子 336 を介して監視制御電極 313 から入力される信号に基づいて周期信号を生成し、生成した周期信号をスイッチング素子 352 のゲートに印加する。監視制御回路 353 は、監視制御端子 336 から電源電圧が供給されると共に、第 5 端子 335 を介して第 2 電極 312 に接続されることで、接地される。

#### 【0109】

温度監視回路 355 は、サーミスタを有し、半導体装置 315 の表面に配置される V C S E L 316 の温度を測定し、サーミスタによって測定される温度が所定の閾値温度を越えたとき、警報信号を、監視制御端子 336 を介して監視制御電極 313 から出力する。光量監視回路 357 は、V C S E L 316 から出射される光の光量を示す光量信号が不図示の光電変換素子から入力され、入力される光量信号に対応する光量が所定の光量範囲を外れたとき、警報信号を、監視制御端子 336 を介して監視制御電極 313 から出力する。なお、V C S E L モジュール 150 では、監視制御回路 353 は、電流駆動回路 354 と、温度監視回路 355 、電流監視回路 356 及び光量監視回路 357 を、必ずしも全て有していないが、少なくとも何れか 1 つは有していることが好ましい。

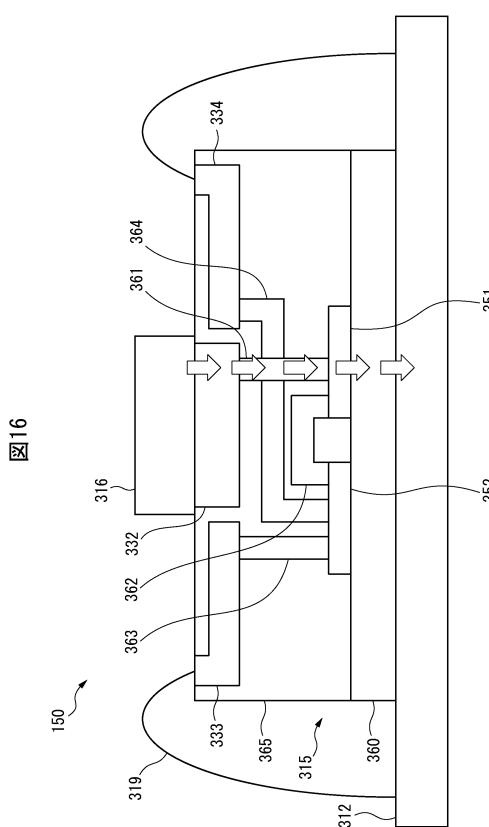

#### 【0110】

図 16 は、第 2 電極 312 、半導体装置 315 及び V C S E L 316 の接続関係を概略的に示す図である。

#### 【0111】

半導体装置 315 は、シリコン基板 360 と、第 1 配線層 361 と、第 2 配線層 362

10

20

30

40

50

と、第3配線層363と、第4配線層364と、絶縁層365とを更に有する。シリコン基板360は、ホウ素等がドープされたp型半導体、リン等がドープされたn型半導体等が表面に形成される。シリコン基板360の表面に形成されるn型半導体、p型半導体は、電流制御素子351、スイッチング素子352及び監視制御回路353のそれぞれに含まれる半導体素子を形成する。

#### 【0112】

第1配線層361～第4配線層364のそれぞれは、アルミ等の導電性部材により形成される複数の配線層、及びビアとも称され、複数の配線層の間を接続する層間接続部を有する。第1配線層361は第2端子332と電流制御素子351との間を電気的に接続し、第2配線層362は電流制御素子351とスイッチング素子352との間を電気的に接続する。第3配線層363は第3端子333とスイッチング素子352との間を電気的に接続し、第4配線層364は第4端子334とスイッチング素子352との間を電気的に接続する。絶縁層365は、シリコン酸化膜であり、第1配線層361～第4配線層364のそれぞれの層間を絶縁する。図16では、絶縁層365はシリコン基板360に比べて厚く記載しているが、これは層構造の説明の為であり、実際は絶縁層365は数1000と薄い膜であり、シリコン基板360は200μmと厚い構造となっている。

10

#### 【0113】

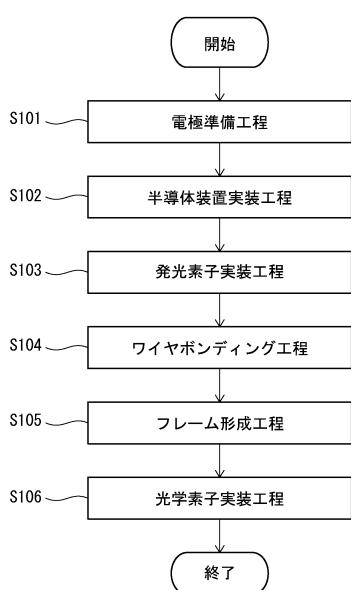

図17は、VCSelモジュール150の製造方法を示すフローチャートである。図18は図17に示す電極準備工程に対応する平面図であり、図19は図17に示す半導体装置実装工程に対応する平面図であり、図20は図17に示す発光素子実装工程に対応する平面図である。図21は図17に示すワイヤボンディング工程に対応する平面図であり、図22は図17に示すフレーム形成工程に対応する平面図である。図17～図22では、単一のVCSelモジュール150が製造される製造方法を示しているが、図17～図22を参照して説明される製造方法と同様な製造方法によって複数のVCSelモジュール150を同時に製造し、その後個別化するようにしても良い。

20

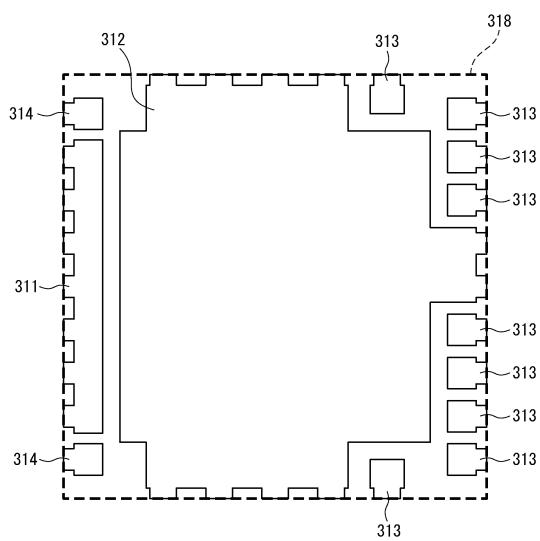

#### 【0114】

まず、図18に示すように、電極準備工程において、第1電極311、第2電極312、複数の監視制御電極313及び一対のダミー電極314のそれぞれは、互いに離隔する所定の位置に配置される(S101)。なお、図18では、フレーム形成工程で追加されるフレーム318の外形を点線で示している。

30

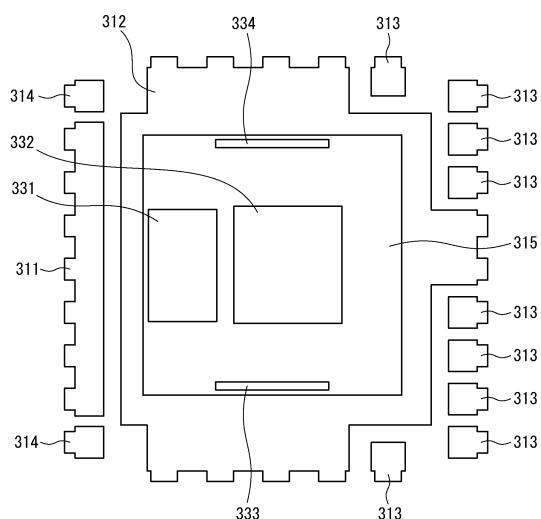

#### 【0115】

次に、図19に示すように、半導体装置実装工程において、半導体装置315は、第2電極312に実装される(S102)。半導体装置315は、金属を含有する樹脂材等の熱伝導率が高い導電性接着部材を介して第2電極312の表面に接着することで、第2電極312に実装される。

30

#### 【0116】

次に、図20に示すように、発光素子実装工程において、VCSel316は、半導体装置315の表面に配置される第2端子332に実装される(S103)。VCSel316のカソードは、金錫はんだ等の導電性の接着部材を介して第2端子332の表面に接着することで、第2端子332と電気的に接続される。VCSel316は、第2電極312及び半導体装置315に重畠して配置される。

40

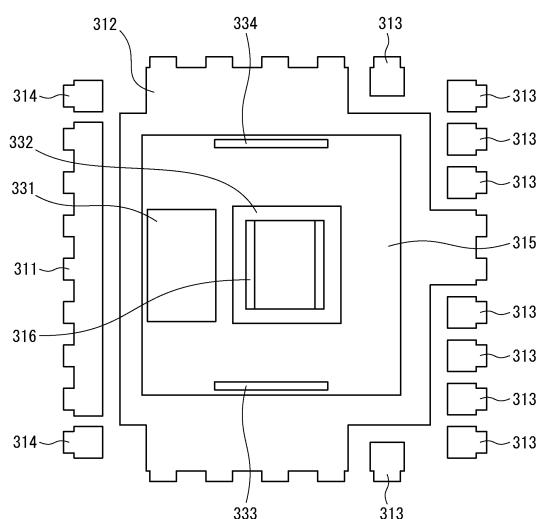

#### 【0117】

次に、図21に示すように、ワイヤボンディング工程において、第1電極311等の電極と第1端子331等の端子の間、及び第1端子331とVCSel316のアノードの間がボンディングワイヤ319によって電気的に接続される(S104)。第1電極311等の電極と第1端子331等の端子の間、及び第1端子331とVCSel316のアノードの間がボンディングワイヤ319によって電気的に接続されることで、外部装置に電気的に接続可能な電極と、半導体装置315及びVCSel316との間が電気的に接続される。

#### 【0118】

50

次に、図22に示すように、フレーム形成工程において、フレーム318は、第1電極311及び第2電極312の表面、及び第1端子331の一部、及び第3端子333及び第4端子334を覆うように形成される(S105)。フレーム318は、フレーム318の形状に対応する形状を有する金型にフレーム318の原材料を注入した後に、フレーム318の原材料を加熱して固化することで、形成される。

#### 【0119】

次に、光学素子実装工程において、光学素子317は、フレーム318の支持面345に実装され(S106)、VCSELモジュール150が完成される。光学素子317は、シリコーン樹脂等の樹脂材料により形成される接着剤を介して支持面345に接着することで、支持面345に実装される。

10

#### 【0120】

VCSELモジュール150では、VCSEL316がVCSEL316を駆動する駆動装置である半導体装置315に重畠するように配置されるので、半導体装置315とVCSEL316とが一体化され且つ小型化が可能である。さらに、VCSELモジュール150では、VCSEL316と、VCSEL316を駆動(スイッチング)する半導体装置315と、半導体装置315を接地する第2電極312とが、3段に積み重なる様な構造(3段スタック構造)を有しているので、更なる小型化が可能である。

#### 【0121】

VCSELモジュール150では、発光中にVCSEL316から放射される熱は、半導体装置315を介して、熱伝導率が高い材料で形成される第2電極312に放熱されるので、VCSELモジュール150は、良好な放熱特性を有する。図16において矢印で示すように、VCSEL316から放射される熱は、第2端子332、第1配線層361、絶縁層365、及び電流制御素子351とスイッチング素子352などが形成されているシリコン基板360を介して第2電極312に放熱される。主の構成部材となるシリコン基板360は熱伝導率が160W/mKと高いため良好な放熱を実現できる。また、前述したように絶縁層365の熱伝導率は、シリコン基板360に比べると低いが、絶縁層365は数1000と薄いため放熱性に影響はない。

20

#### 【0122】

VCSELモジュール150では、第1電極311と第1端子331との間は、複数のボンディングワイヤ319によって接続される。例えば、第1端子331にVCSEL316を実装するとき、半導体装置315の第1辺321からはみ出さないように、第1辺321の上端から離隔した位置に配置されるので、離隔した距離だけボンディングワイヤ319の長さが長くなる。また、VCSEL316と第1電極311との間を接続するボンディングワイヤ319は、半導体装置315の第1辺の上端に触れないように第1辺の上端のVCSELモジュール1506から離れる方向へ離隔させるから、離隔した距離だけワイヤが長くなる。一方、VCSELモジュール150は、第1端子331の第1辺321の近傍にボンディングワイヤ319が配置できるから、VCSELモジュール150は、第1端子331にVCSEL316を実装したときよりも、第1電極311と第1端子331との間の配線の抵抗による電圧降下が抑制される。例えば、VCSEL316から第1電極311へのワイヤは半導体装置315の第1辺の上端に触れないように第1辺の上端のVCSELモジュール1506から離れる方向へ離隔させるから、離隔した距離だけボンディングワイヤ319の長さが長くなる。一方、VCSELモジュール150は、VCSEL316から発光素子の高さだけ低い位置にある第1端子331にボンディングワイヤ319を直接接続でき、面積が大きく幅も広く配線抵抗が小さい第1端子331を経由して、前述のワイヤ経路で第1電極1に接続できるから、VCSELモジュール150は、VCSEL316と第1電極311との間をボンディングワイヤ319により接続したときよりも、第1電極311とアノードとの間の配線抵抗による電圧降下が抑制されるとともに、配線のインダクタンスも低減する。また、VCSELモジュール150では、第2電極312と第3端子333及び第4端子334のそれぞれとの間は、複数のボンディングワイヤ319によって接続されるので、接地される第2電極312と半導体裝

30

40

50

置 3 1 5 との間の配線抵抗による電圧上昇が抑制される。

【 0 1 2 3 】

V C S E L モジュール 1 5 0 では、第 1 端子 3 3 1 は第 1 電極 3 1 1 に対向する第 1 辺 3 2 1 に沿って配置され、第 2 端子 3 3 2 は半導体装置 3 1 5 の表面の中央に配置され、第 3 端子 3 3 3 及び第 4 端子 3 3 4 は第 2 辺 3 2 2 及び第 3 辺 3 2 3 に沿って配置される。V C S E L モジュール 1 5 0 では、第 1 端子 3 3 1 と、第 2 端子 3 3 2 と、第 3 端子 3 3 3 及び第 4 端子 3 3 4 とを離隔して配置することで、第 1 端子 3 3 1 、第 2 端子 3 3 2 、第 3 端子 3 3 3 及び第 4 端子 3 3 4 の間に流れる駆動電流が干渉して、駆動電流にノイズが発生するおそれを低くすることができる。

【 0 1 2 4 】

V C S E L モジュール 1 5 0 は、監視制御回路 3 5 3 に接続される複数の監視制御端子 3 3 6 は、第 4 辺 3 2 4 に沿って配置されるので、監視制御回路 3 5 3 から入出力される信号に駆動電流が干渉してノイズが発生するおそれを低くすることができる。また、複数の監視制御端子 3 3 6 のそれぞれに接続される監視制御電極 3 1 3 は、第 4 辺 3 2 4 に沿って配置されるので、監視制御回路 3 5 3 から入出力される信号に駆動電流が干渉して、駆動電流にノイズが発生するおそれを更に低くすることができる。

【 0 1 2 5 】

V C S E L モジュール 1 5 0 では、第 1 電極 3 1 1 及び第 2 電極 3 1 2 の表面、第 1 端子 3 3 1 の一部、並びに前記第 3 端子 3 3 3 及び第 4 端子 3 3 4 は、ワイヤボンディング工程の後に配置される樹脂製のフレーム 3 1 8 によって覆われる。V C S E L モジュール 1 5 0 は、枠材として機能するフレーム 3 1 8 を配置する前にワイヤボンディング工程が実行されるので、ワイヤボンディング工程における離隔距離を確保することなく小型化が可能である。

【 0 1 2 6 】

V C S E L モジュール 1 5 0 は、第 2 電極 3 1 2 及び半導体装置 3 1 5 がフレーム 3 1 8 によって固定されるので、第 2 電極 3 1 2 と半導体装置 3 1 5 との間の接着強度がフレーム 3 1 8 によって補強され、半導体装置 3 1 5 が第 2 電極 3 1 2 から剥離することを防止できる。

【 0 1 2 7 】

V C S E L モジュール 1 5 0 では、光学素子 3 1 7 は、第 1 壁部 3 4 1 、第 2 壁部 3 4 2 、第 3 壁部 3 4 3 及び第 4 壁部 3 4 4 に囲まれ且つ V C S E L 3 1 6 が視認可能な開口部 3 4 8 が中央に形成される支持面 3 4 5 によって支持される。V C S E L モジュール 1 5 0 では、光学素子 3 1 7 が支持面 3 4 5 によって支持されるので、製造コストが高い光学素子 3 1 7 の大きさを最小化できるので、V C S E L モジュール 1 5 0 の製造コストを低減することができる。

【 0 1 2 8 】

V C S E L モジュール 1 5 0 では、フレーム 3 1 8 は、光学素子 3 1 7 を挟むように配置される一対の第 1 凸部 3 4 6 及び第 2 凸部 3 4 7 を有するので、V C S E L モジュール 1 5 0 を製造するときに、光学素子 3 1 7 の配置位置を容易に決定することができる。

【 0 1 2 9 】

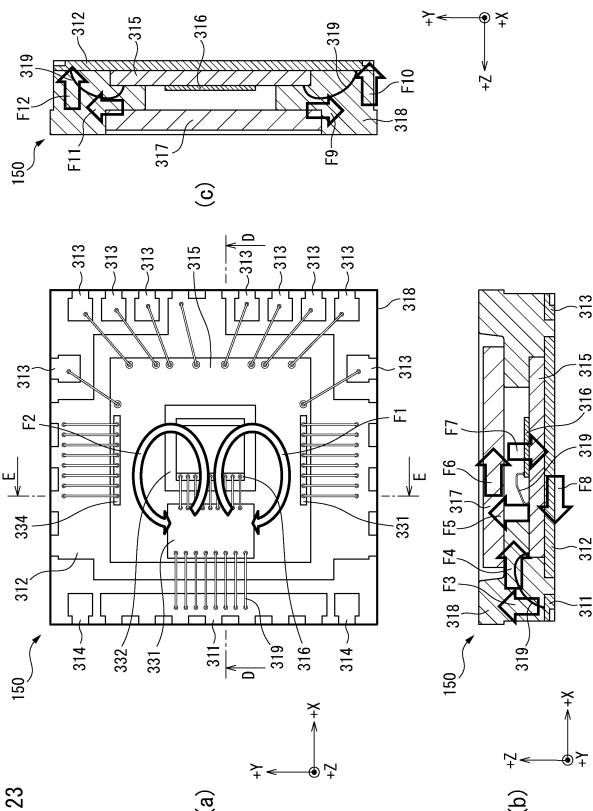

図 2 3 は、V C S E L モジュール 1 5 0 における電流の流れを説明するための図である。図 2 3 ( a ) はフレーム 3 1 8 の基部以外を除いた V C S E L モジュール 1 5 0 の平面図であり、図 2 3 ( b ) は図 2 3 ( a ) の D - D 線に沿う V C S E L モジュール 1 5 0 の断面図であり、図 2 3 ( c ) は図 2 3 ( a ) の E - E 線に沿う V C S E L モジュール 1 5 0 の断面図である。図 2 3 ( a ) ~ ( c ) において、V C S E L モジュール 1 5 0 の厚さ方向を + Z 方向、図 2 3 ( a ) における図面中の上方向を + Y 方向、図面中の左方向を + X 方向とする。

【 0 1 3 0 】

図 2 3 ( b ) の矢印 F 3 及び F 4 に示すように、第 1 電極 3 1 1 から流入した電流はボンディングワイヤ 3 1 9 を介して半導体装置 3 1 5 の第 1 端子 3 3 1 に流入する (+ Z 方

10

20

30

40

50

向から + X 方向)。次に、矢印 F 5 及び F 6 に示すように、第 1 端子 331 からボンディングワイヤ 319 を介して VCEL316 のアノード (VCEL105 の表面に配置) に流入する (+ Z 方向から + X 方向)。次に、矢印 F 7 に示すように、VCEL316 のアノードに流入した電流は、VCEL316 のカソード (VCEL105 の裏面に配置) から半導体装置 315 に流入する (- Z 方向)。さらに、半導体装置 315 から流出した電流は、第 2 電極 312 へ戻り、矢印 F 8 の方向 (- X 方向) へ回り込む。

#### 【0131】

図 23 (c) の矢印 F 9 及び F 10 に示すように、半導体装置 315 に流入した電流は、半導体装置 315 内に形成される電流制御素子 351 とスイッチング素子 352 を介して第 3 端子 333 からボンディングワイヤ 319 を介して第 2 電極 312 へ流れ (- Y 方向から - Z 方向)、矢印 F 11 及び F 12 に示すように、半導体装置 315 の第 4 端子 334 からボンディングワイヤ 319 を介して第 2 電極 312 へ流れる (+ Y 方向から - Z 方向)。矢印 F 9 及び F 10 と矢印 F 11 及び F 12 のそれぞれの電流ループは対象な形状となる。全体でみると、図 23 (a) に示すように、図中の左側から下側周り (矢印 F 1 方向) 及び上側周り (矢印 F 2 方向) に、電流ループが形成されることとなる。この結果、VCEL モジュール 150 では、スタック構造を有することと相まって、小さい電流ループが X 方向、Y 方向及び Z 方向に、同時に、立体的に形成されることから、全体のインダクタンスを低くすることが可能となった。

#### 【0132】

VCEL モジュール 150 では、VCEL316、半導体装置 315、第 2 電極が、Z 方向において 3 段スタック構造となっているため、VCEL316 から流出する電流経路を短くすることが可能となっている。また、電流ループを小さくすることができている。また、VCEL316 と半導体装置 315 との間は、ボンディングワイヤではなく、金属同士を接続しているため、インダクタンスを低くすることができ、高周波スイッチング特性が向上する構成となっている。また、半導体装置 315 から流出する電流を、一方向ではなく、図中の上下 2 方向 ( $\pm$  Y 方向) に均等に分割しているので、さらにインダクタンスの低い電流経路を確保することが可能となっている。

#### 【0133】

また、VCEL316 のアノードに流入する電流経路の方向 (+ X 方向) に対して、垂直な方向 (- Z 方向、及び / 又は、 $\pm$  Y 方向) に VCEL316 から電流が流出するようにしたので、インダクタンスの低い電流経路を確保することが可能となっている。

10

20

30

40

50

【図面】

【図1】

図1

【図2】

図2

10

【図3】

図3

【図4】

図4

20

30

40

50

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図 1 3】

図13

【図 1 4】

図14

10

20

【図 1 5】

【図 1 6】

30

40

50

【図17】

図17

【図18】

図18

10

20

【図19】

図19

【図20】

図20

30

40

50

【図21】

【 図 2 2 】

図21

図22

【図23】

【 図 2 4 】

20

图24

30

40

【図25】

図25

【図26】

図26

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

|        |                |     |        |       |

|--------|----------------|-----|--------|-------|

| H 01 S | 5/024(2006.01) | F I | H 01 S | 5/024 |

| H 01 S | 5/023(2021.01) |     | H 01 S | 5/023 |

## (74)代理人 100160716

弁理士 遠藤 力

## (72)発明者 秋山 貴

山梨県富士吉田市上暮地1丁目23番1号 シチズン電子株式会社内

## (72)発明者 内村 仁

山梨県富士吉田市上暮地1丁目23番1号 シチズン電子株式会社内

## (72)発明者 相原 健志

山梨県富士吉田市上暮地1丁目23番1号 シチズン電子株式会社内

## (72)発明者 原 博昭

山梨県富士吉田市上暮地1丁目23番1号 シチズン電子株式会社内

## 審査官 百瀬 正之

(56)参考文献

国際公開第2020/054257 (WO, A1)

米国特許出願公開第2018/0278011 (US, A1)

特開平06-237016 (JP, A)

米国特許出願公開第2020/0185875 (US, A1)

国際公開第2018/100082 (WO, A1)

特開2019-158693 (JP, A)

特開2012-037276 (JP, A)

国際公開第2014/017256 (WO, A1)

国際公開第2020/044817 (WO, A1)

特表2010-531546 (JP, A)

米国特許出願公開第2020/0006271 (US, A1)

## (58)調査した分野 (Int.Cl., DB名)

H 01 S 5 / 00 - 5 / 50

G 01 S 7 / 48 - 7 / 51

G 01 S 17 / 00 - 17 / 95

H 01 L 25 / 065

H 01 L 25 / 07

H 01 L 25 / 18