(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4606565号

(P4606565)

(45) 発行日 平成23年1月5日(2011.1.5)

(24) 登録日 平成22年10月15日(2010.10.15)

(51) Int.Cl.

F 1

G 11 C 11/406 (2006.01)

G 11 C 11/34 363 N

G 11 C 11/4076 (2006.01)

G 11 C 11/34 354 C

G 11 C 11/407 (2006.01)

G 11 C 11/34 362 S

G 11 C 11/34 363 L

請求項の数 9 (全 19 頁)

(21) 出願番号

特願2000-335603 (P2000-335603)

(22) 出願日

平成12年11月2日 (2000.11.2)

(65) 公開番号

特開2002-140891 (P2002-140891A)

(43) 公開日

平成14年5月17日 (2002.5.17)

審査請求日

平成18年8月24日 (2006.8.24)

(73) 特許権者 308014341

富士通セミコンダクター株式会社

神奈川県横浜市港北区新横浜二丁目10番

23

(74) 代理人 100117385

弁理士 田中 裕人

(72) 発明者 東保 充洋

愛知県春日井市高蔵寺町二丁目1844番

2 富士通ヴィエルエスアイ株式会社内(72) 発明者 佐藤 一

愛知県春日井市高蔵寺町二丁目1844番

2 富士通ヴィエルエスアイ株式会社内

審査官 高野 芳徳

最終頁に続く

(54) 【発明の名称】同期型半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

周期的にメモリセルのリフレッシュを必要とする同期型半導体記憶装置において、

定常的に入力される外部基本クロックと周波数及び位相が一致する内部基本クロックが

生成される際の前記周波数の高低を、常時検出する検出手段と、

前記検出手段より出力される周波数検出信号に基づきリフレッシュ周期を制御する周期

制御手段とを備え、

前記周期制御手段は、

前記外部基本クロックの周波数が高いほど、前記リフレッシュ周期を短くするように制

御することを特徴とする同期型半導体記憶装置。

10

## 【請求項 2】

前記周期制御手段は、

前記リフレッシュ周期を計測するための周期計測手段と、

計測される前記リフレッシュ周期を前記周波数検出信号に基づき可変とする計測周期変

更手段とを備えることを特徴とする請求項1に記載の同期型半導体記憶装置。

## 【請求項 3】

前記周期計測手段は、発振回路を備え、

前記計測周期変更手段は、前記発振回路の駆動電流を前記周波数検出信号に基づき可変

とする電流源回路を備えることを特徴とする請求項2に記載の同期型半導体記憶装置。

## 【請求項 4】

20

前記周期計測手段は、発振回路を備え、

前記計測周期変更手段は、前記発振回路の電源電圧を前記周波数検出信号に基づき可変とする電圧源回路を備えることを特徴とする請求項2に記載の同期型半導体記憶装置。

【請求項 5】

前記周期計測手段は、発振回路を備え、

前記計測周期変更手段は、前記発振回路におけるループ状に接続された奇数段の反転回路の段数を前記周波数検出信号に基づき可変とする段数切替回路を備えることを特徴とする請求項2に記載の同期型半導体記憶装置。

【請求項 6】

前記周期計測手段は、発振回路と分周回路とを備え、

10

前記計測周期変更手段は、前記分周回路の分周比を前記周波数検出信号に基づき可変とする分周比切替回路を備えることを特徴とする請求項2に記載の同期型半導体記憶装置。

【請求項 7】

前記検出手段は、

前記外部基本クロックと前記内部基本クロックとの周波数及び位相を比較する位相比較手段と、

前記位相比較手段から出力される比較結果に応じて、前記内部基本クロックの周波数及び位相を調整する調整信号を出力する調整手段とを備え、

前記調整信号を前記周波数検出信号とする特徴とする請求項1乃至6の少なくとも何れか1に記載の同期型半導体記憶装置。

20

【請求項 8】

前記周波数検出信号がデジタル信号である場合、

前記周波数検出信号をアナログ信号に変換する第1変換回路を備えることを特徴とする請求項3又は4に記載の同期型半導体記憶装置。

【請求項 9】

前記周波数検出信号がアナログ信号である場合、

前記周波数検出信号をデジタル信号に変換する第2変換回路を備えることを特徴とする請求項5又は6に記載の同期型半導体記憶装置。

【発明の詳細な説明】

【0001】

30

【発明の属する技術分野】

本発明は、同期型半導体記憶装置におけるリフレッシュ動作に関するものであり、特に、セルフリフレッシュ動作における低消費電流化を図る同期型半導体記憶装置に関するものである。

【0002】

【従来の技術】

近年、動画描画やその他の先進機能を実現するコンピュータ技術の進展に伴い、ダイナミックランダムアクセスメモリ(DRAM)等に代表される半導体記憶装置には大容量化や高速化に対する要求が強くなってきており、大容量の同期型DRAMに代表される同期型半導体記憶装置も開発されてきている。一方で、この要求は必然的に回路動作における消費電流の増大を招くものであるため、同期型半導体記憶装置の低消費電流化が望まれている。

40

【0003】

特に、同期型DRAM等のメモリセルのリフレッシュ動作においては、所定のリフレッシュ周期で行なう必要があり、リフレッシュ動作周期を、メモリセルの電荷保持特性から判断される電荷保持時間の実力値に合わせて長く設定することによりリフレッシュ動作に伴う消費電流の低減を図っている。

【0004】

また、同期型半導体記憶装置では、外部基本クロックに同期して動作するため、外部基本クロックの高速化による動作電流の増大に伴い同期型半導体記憶装置のデバイス温度が

50

上昇する。メモリセルの電荷保持特性はデバイス温度に大きく依存し温度上昇と共に電荷の保持時間が減少するので、高温域ではリフレッシュ周期を短くする必要があり、外部基本クロックの周波数に応じて変化するデバイス温度に適合したリフレッシュ周期を設定することが必要となる。

#### 【0005】

従来技術では例えば、特開平5-217369号公報においては、メモリセルのリフレッシュ動作を必要とする半導体記憶装置のリフレッシュ信号を出力するリフレッシュタイマにおいて、所定周波数の発振信号を出力する発振手段と、発振信号の周波数を分周する分周手段と、分周手段の分周周期をメモリセルのリフレッシュ周期に適合する値に調整可能な調整手段とを備える半導体記憶装置のリフレッシュタイマが記載されている。

10

#### 【0006】

かかる半導体記憶装置のリフレッシュタイマでは、比較的時間精度の悪い発振手段を用いても、半導体記憶装置毎に製造後において必要とするリフレッシュサイクルに正確に調整することが可能となるものである。

#### 【0007】

また、特開平5-307883号公報においては、高電位電源線と低電位電源線との間に、所定数のPMOSトランジスタ及び所定数のNMOSトランジスタを順に直列接続してなるインバータ回路と、高電位電源線と低電位電源線との間に、ゲートに低電位電源線の電位レベルを入力する第1PMOSトランジスタ及び抵抗を順に直列接続し、第1PMOSトランジスタと抵抗との接続点を低電位出力端とする第1抵抗手段と、高電位電源線と低電位電源線との間に、抵抗及びゲートに高電位電源線の電位レベルを入力する第1NMOSトランジスタを順に直列接続し、抵抗と第1NMOSトランジスタとの接続点を高電位出力端とする第2抵抗手段とを備え、第1抵抗手段の低電位出力端をインバータ回路における最も高電位電源線寄りのPMOSトランジスタのゲートに接続するとともに、第2抵抗手段の高電位出力端をインバータ回路における最も低電位電源線寄りのNMOSトランジスタのゲートに接続し、インバータ回路を複数段環状に接続して所定のクロック周期を生成するオシレータ回路が記載されている。

20

#### 【0008】

半導体記憶装置では、温度上昇に従ってメモリセルの電荷の保持時間が減少するので、電荷を保持しておくためにリフレッシュ周期の温度特性は温度に対して負の相関を持つように設定すべきであることに鑑み、かかるオシレータ回路では、発振周期における温度特性を、電荷を保持しておくためのリフレッシュ周期の温度特性と同様の相関を持たせることにより、温度の上昇に従いリフレッシュ周期を短縮して高い温度でのメモリセルの電荷保持の信頼性を高めると共に、通常使用温度ではリフレッシュ周期が長く設定できるために、リフレッシュ時の動作電流を低く抑えることができ、低消費電流化を図ることが可能となるものである。

30

#### 【0009】

更に、特開平7-73668号公報においては、リフレッシュサイクル時間を設定するマスタクロック信号を発生する半導体メモリ装置のセルフリフレッシュ周期調節回路において、外部制御信号によるリフレッシュモード設定に応じて所定周期のパルス列を発生し、これを順次分周して相互に異なる周期を有する多数の分周パルス列を出力するパルス列発生手段と、内部に設定された基準レベルに対する周辺温度の変化を感知して温度検出信号を出力する少なくとも1つの温度検出手段と、温度検出信号に応じて分周パルス列のいずれかを選択し、選択した分周パルス列を基にマスタクロック信号を出力するマスタクロック発生手段とを備える半導体メモリ装置のセルフリフレッシュ周期調節回路が記載されている。

40

#### 【0010】

かかるセルフリフレッシュ周期調節回路では、周辺温度の変化に応じて、能動的にセルフリフレッシュの周期の調整が可能となり、多様な動作環境に適応して自動的にセルフリフレッシュ周期を調整することが可能なものである。

50

**【0011】****【発明が解決しようとする課題】**

特開平5-217369号公報では、比較的時間精度の悪い発振手段を用いても、製造後に半導体記憶装置毎に必要とするリフレッシュサイクルに正確に調整することが可能となるものではある。

**【0012】**

しかしながら、この調整は、個々の半導体記憶装置に対して、トリミング回路等の調整手段を使用して行なう必要があり、製造ばらつき等に起因する個体間の特性変動を個々に測定しなければ最適なリフレッシュ周期を決定することができず、測定すべき特性に温度特性を含むことを考えれば調整前の特性測定の試験に多大な時間を要することとなり、半導体記憶装置の生産性を向上させることができず問題である。

10

**【0013】**

更に、トリミング回路等の調整手段で調整されるリフレッシュ周期は常に一定の周期でリフレッシュ動作を行うこととなるが、この周期は、メモリセルの電荷保持特性における最も厳しい条件（例えば、低電源電圧時、高温時等）でも電荷保持ができるように設定する必要があるため、通常の使用条件においてはメモリセルの電荷保持特性から必要とされる周期より短いリフレッシュ周期で動作することとなり、リフレッシュ動作に伴う電流消費が必要以上に大きくなるという問題がある。

**【0014】**

特開平5-307883号公報では、温度の上昇に従いセルフリフレッシュ周期を短縮して高温でのメモリセルの電荷保持の信頼性を高めると共に、通常使用温度ではセルフリフレッシュ周期を長く設定し低消費電流化を図るものではある。また、特開平7-73668号公報では、周辺温度の変化に応じて、能動的にセルフリフレッシュの周期を調整するものではある。

20

**【0015】**

しかしながら、メモリセルの電荷保持特性の温度特性、特開平5-307883号公報におけるオシレータ回路によるセルフリフレッシュ周期の温度に対する相関特性若しくは特開平7-73668号公報における温度検出手段の検出特性は、製造ばらつきにより所定の分布を持って広がるものであり、オシレータ回路や、温度検出手段の動作定数はこの分布の限界値である最悪条件に設定する必要がある。従って、製造条件を緩く設定して広い特性分布の広がりを許容することとすると、分布中心の固体に対しては特性から必要される周期より短いリフレッシュ周期で動作することとなりリフレッシュ動作に伴う電流消費が必要以上に大きくなってしまい問題である。また、特性分布の広がりを狭く抑えれば、リフレッシュ動作において低消費電流を実現できるが特性分布を狭い分布範囲に収めるための製造における負荷は多大なものとなり問題である。

30

**【0016】**

本発明は前記従来技術の問題点を解消するためになされたものであり、製造ばらつきに影響されることなく、リフレッシュ時間の調整前に多大な特性測定のための試験時間を要することもなく、電荷保持特性時間に最適なリフレッシュ周期を提供し、リフレッシュ動作における消費電流の低減を図ることができる同期型半導体記憶装置を提供することを目的とする。

40

**【0017】****【課題を解決するための手段】**

前記目的を達成するために、請求項1に係る同期型半導体記憶装置は、リフレッシュ動作を必要とする同期型半導体記憶装置において、定常的に入力される外部基本クロックと周波数及び位相が一致する内部基本クロックが生成される際の周波数の高低を、常時検出手段と、検出手段からの周波数検出信号に基づきリフレッシュ周期を制御する周期制御手段とを備え、周期制御手段は、外部基本クロックの周波数が高いほど、リフレッシュ周期を短くするように制御することを特徴とする。

**【0018】**

50

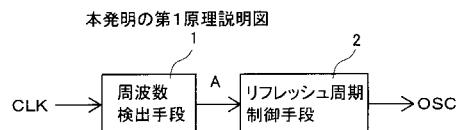

請求項 1 の同期型半導体記憶装置では、図 1 の第 1 原理説明図に示すように、定常的に入力され内部基本クロックと周波数及び位相が一致する外部基本クロック C L K の周波数を、周波数検出手段 1 が受け周波数の高低に応じた周波数検出信号 A を常時出力する。出力された周波数検出信号 A はリフレッシュ周期制御手段 2 に入力され、周波数検出信号 A に基づき制御されたリフレッシュ周期を有するリフレッシュ信号 O S C を出力する。

【 0 0 1 9 】

これにより、外部基本クロック C L K の周波数の高低に応じて変化する同期型半導体記憶装置のデバイス温度毎のメモリセルの電荷保持特性に適合して、リフレッシュ周期が設定されるので、リフレッシュ周期を、メモリセルの電荷保持の温度特性の測定試験をして、同期型半導体記憶装置個々に設定する必要はない。

10

【 0 0 2 0 】

また、製造ばらつきにより検出精度の確保が難しい温度検出手段を必要とせず、外部基本クロックという安定した信号を温度センサーとして利用できるので、簡便且つ確実にデバイス温度に適合したリフレッシュ周期を設定でき、全デバイス温度範囲に渡って最適なリフレッシュ周期を実現でき消費電流の低減を図ることができる。

【 0 0 2 1 】

【 0 0 2 2 】

また、外部基本クロックの周波数が高くなり、同期型半導体記憶装置における動作電流が増大してデバイス温度が上昇すると、リフレッシュ周期を短くするように制御される。

【 0 0 2 3 】

これにより、外部基本クロックの高速化に伴うデバイス温度の上昇によりメモリセルの電荷保持時間が減少しても、外部基本クロックに応じてリフレッシュ周期が短くなるので、動作周波数の変化によりデバイス温度が変化しても、常に最適なリフレッシュ周期にてリフレッシュ動作が行われ、メモリセルの電荷保持の信頼性を外部基本クロックという安定した信号を利用して簡便且つ確実に確保することができる。

20

【 0 0 2 4 】

また、請求項 2 に係る同期型半導体記憶装置は、請求項 1 に記載の同期型半導体記憶装置において、周期制御手段は、リフレッシュ周期の周期計測手段と、リフレッシュ周期を周波数検出信号に基づき可変とする計測周期変更手段とを備えることを特徴とする。

【 0 0 2 5 】

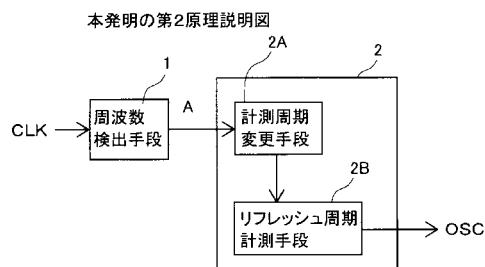

請求項 2 の同期型半導体記憶装置では、図 2 の第 2 原理説明図に示すように、外部基本クロック C L K を周波数検出手段 1 が受け周波数に応じた周波数検出信号 A を出力する。出力された周波数検出信号 A はリフレッシュ周期制御手段 2 における計測周期変更手段 2 A に入力され周波数検出信号 A に基づき設定されたリフレッシュ周期を出力し、この設定周期に応じてリフレッシュ周期計測手段 2 B が動作することによりリフレッシュ信号 O S C を出力する。

30

【 0 0 2 6 】

これにより、計測周期変更手段 2 A が、周波数検出信号 A に応じてリフレッシュ周期を可変して設定するので、リフレッシュ周期計測手段 2 B の動作周期を外部基本クロックに応じて調整することができる。

40

【 0 0 2 7 】

また、請求項 3 又は 4 に係る同期型半導体記憶装置は、請求項 2 に記載の同期型半導体記憶装置において、周期計測手段は、発振回路を備えており、更に、請求項 3 では、計測周期変更手段は、発振回路の駆動電流を周波数検出信号に基づき可変とする電流源回路を備え、請求項 4 では、計測周期変更手段は、発振回路の電源電圧を周波数検出信号に基づき可変とする電圧源回路を備えることを特徴とする。

【 0 0 2 8 】

周期計測手段としての発振回路の動作周期を、請求項 3 の同期型半導体記憶装置では発振回路の駆動電流を制御することにより、また、請求項 4 の同期型半導体記憶装置では電源電圧を制御することにより、外部基本クロックに応じて検出手段から出力される周波数

50

検出信号に基づき制御する。

【0029】

これにより、周期計測手段としての発振回路の動作周期を、発振回路の駆動電流や電源電圧といったアナログ信号により制御することができる。

【0030】

また、請求項5又は6に係る同期型半導体記憶装置は、請求項2に記載の同期型半導体記憶装置において、周期計測手段は、発振回路を備えており、加えて請求項6においては分周回路を備え、更に、請求項5では、計測周期変更手段は、発振回路におけるループ状に接続された奇数段の反転回路の段数を周波数検出信号に基づき可変とする段数切替回路を備え、請求項6では、計測周期変更手段は、発振回路における分周回路の分周比を周波数検出信号に基づき可変とする分周比切替回路を備えることを特徴とする。

10

【0031】

周期計測手段としての発振回路の動作周期を、請求項5の同期型半導体記憶装置では発振回路のループ段数を切り替えることにより、また、請求項6の同期型半導体記憶装置では分周比を切り替えることにより、外部基本クロックに応じて検出手段から出力される周波数検出信号に基づき制御する。

【0032】

これにより、周期計測手段としての発振回路の動作周期を、発振回路のループ段数や分周比の切替といったデジタル信号により制御することができる。

【0033】

20

また、請求項7に係る同期型半導体記憶装置は、請求項1乃至6の少なくとも何れか1に記載の同期型半導体記憶装置において、外部基本クロックと内部基本クロックとの周波数及び位相を比較する位相比較手段と、位相比較手段から出力される比較結果に応じて、内部基本クロックの周波数及び位相を調整する調整信号を出力する調整手段とを備え、調整信号を周波数検出信号とすることを特徴とする。

【0034】

これにより、外部基本クロックの高周波数化が進展した際の同期型半導体記憶装置における高速な同期動作を保証するために、位相比較手段を使用して外部基本クロックと内部基本クロックとの周波数及び位相を比較する位相比較手段から比較結果が出力される。調整手段からは比較結果に応じて調整信号が出力される。調整信号を周波数検出信号として内部基本クロックの周波数及び位相が調整される。

30

【0035】

また、請求項8に係る同期型半導体記憶装置は、請求項3又は4に記載の同期型半導体記憶装置において、デジタル信号として出力される周波数検出信号をアナログ信号に変換する第1変換回路を備え、請求項9に係る同期型半導体記憶装置は、請求項5又は6に記載の同期型半導体記憶装置において、アナログ信号として出力される周波数検出信号をデジタル信号に変換する第2変換回路を備えることを特徴とする。

【0036】

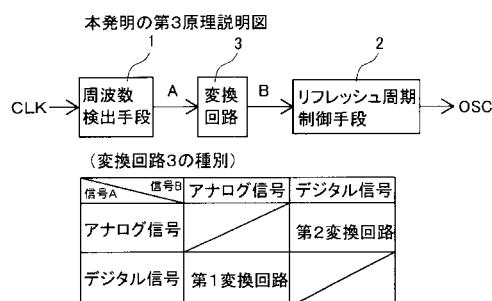

請求項8又は9の同期型半導体記憶装置では、図3の第3原理説明図に示すように、外部基本クロックC L Kを周波数検出手段1が受け周波数に応じた周波数検出信号Aを出力する。出力された周波数検出信号Aとリフレッシュ周期制御手段2への入力信号Bとの信号レベルを調整するため必要に応じて、周波数検出信号Aは変換回路3を介して入力信号Bに変換される。変換された入力信号Bはリフレッシュ周期制御手段2に入力され、適宜リフレッシュ周期を制御してリフレッシュ信号O S Cを出力する。

40

【0037】

変換回路3として必要となる回路は、デジタル信号の周波数検出信号Aに対して入力信号Bとしてアナログ信号を受け付けるリフレッシュ周期制御手段2を組合わせる場合には、第1変換回路により信号変換し、アナログ信号の周波数検出信号Aに対して入力信号Bとしてデジタル信号を受け付けるリフレッシュ周期制御手段2を組合わせる場合には、第2変換回路により信号変換する。尚、周波数検出信号Aと入力信号Bとが、共にアナログ

50

信号であるかデジタル信号である場合には、変換回路3は不要である。

【0038】

これにより、相互に信号レベルの異なる場合にも変換回路3を適宜選択することにより適當なインターフェースをとることができる。

【0039】

【発明の実施の形態】

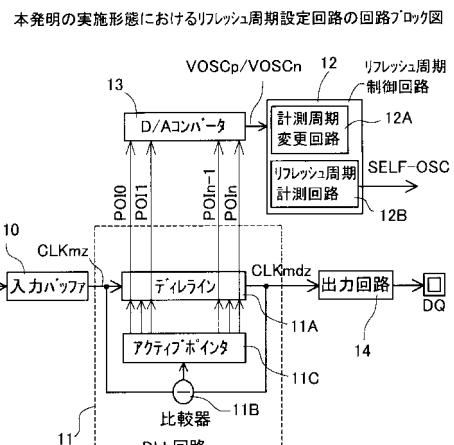

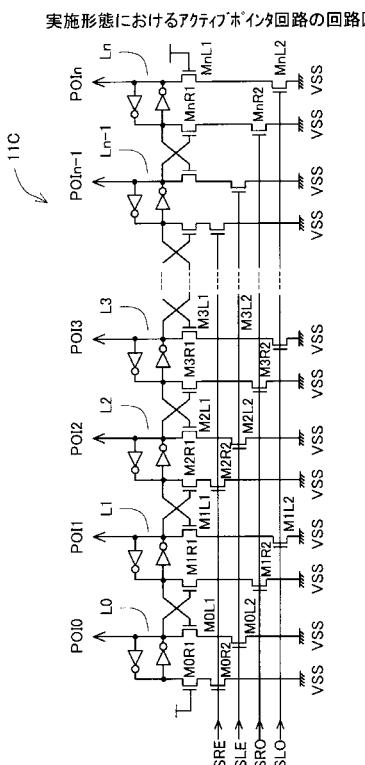

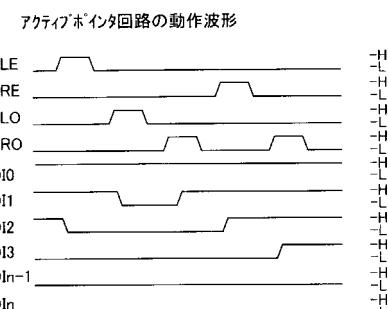

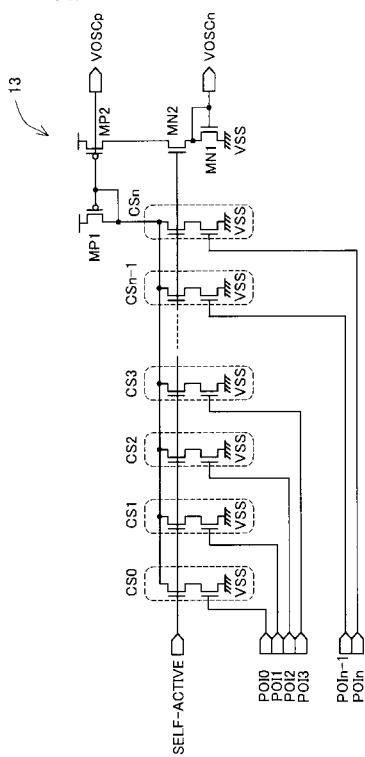

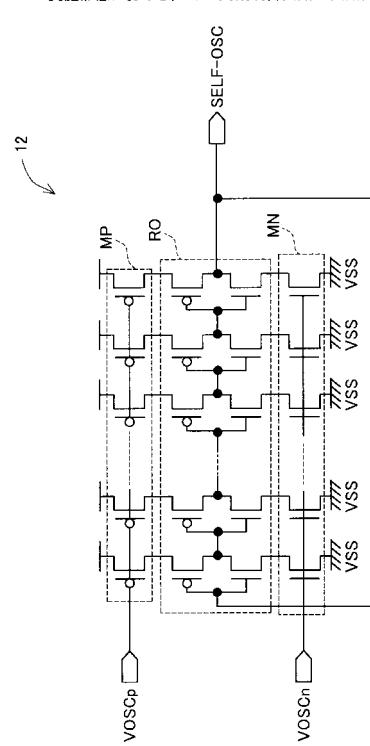

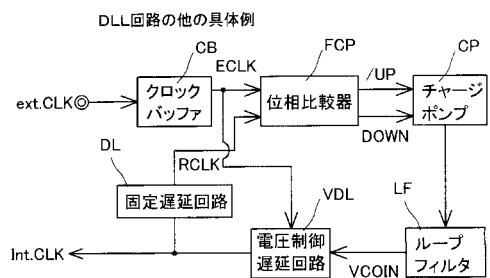

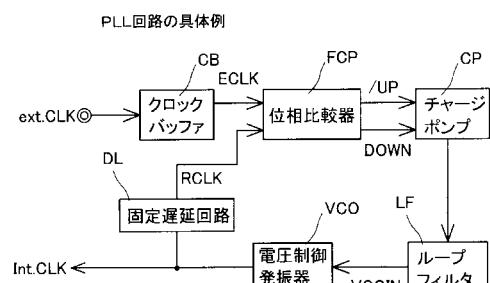

以下、本発明の同期型半導体記憶装置について具体化した実施形態を図4乃至図14に基づき図面を参照しつつ詳細に説明する。図4は、本発明の実施形態におけるリフレッシュ周期設定用回路を示す回路ブロック図である。図5は、本実施形態におけるアクティブポイント回路を示す回路図である。図6は、アクティブポイント回路の動作波形である。図7は、本実施形態におけるD/Aコンバータ回路を示す回路図である。図8は、本実施形態におけるリフレッシュ周期制御回路を示す回路図(第1具体例)である。図9は、リフレッシュ周期制御回路の第2具体例を示す回路図である。図10は、リフレッシュ周期制御回路の第3具体例を示す回路図である。図11は、リフレッシュ周期制御回路の第4具体例を示す回路図である。図12は、DLL回路の他の具体例を示す回路ブロック図である。図13は、他の具体例のDLL回路における電圧制御遅延回路を示す回路図である。図14は、PLL回路の具体例を示す回路ブロック図である。

10

【0040】

図4に示す本発明の実施形態におけるリフレッシュ周期設定回路の回路ブロックは、図3に示す第3原理説明図のうち、変換回路3を第1変換回路とした場合の実施形態を示している。周波数検出手段1としてDLL回路11を使用し、DLL回路11における位相比較信号であるアクティブポイント回路11Cの出力信号POI0乃至nをデジタル信号として出力する。アクティブポイント回路11Cから出力されたデジタル信号POI0乃至nは、D/Aコンバータ回路13に入力され、定電流源回路の電流値を決定するVOSCP/VOSCnのアナログ信号(電圧値)を出力する。VOSCP/VOSCnを受けたりフレッシュ周期制御回路12内の計測周期変更回路12Aは、VOSCP/VOSCnの電圧値に応じた電流値を出力する定電流源回路(図8中、MP、MN)を構成しており、この定電流によりリフレッシュ周期計測回路12B(図8中、RO)の駆動能力を制御することにより、リフレッシュ用の発振信号SELFOSCを出力する。

20

【0041】

以下、個々の構成について詳述する。外部基本クロックCLKは入力バッファ10に受け入れられた後、信号CLKmzとしてDLL回路11におけるディレイライン回路11Aに入力される。ディレイライン回路11Aは、遅延ゲート回路を多段に直列接続した構成を有しており、後述のアクティブポイント回路11Cの出力信号POI0乃至nにより信号CLKmzが伝播する遅延ゲート回路の段数を制御することにより遅延量を調整して、ディレイライン回路11Aの出力信号である内部基本クロックCLKmdzと入力バッファ10の出力信号CLKmzとの位相を一致させると共に、調整した遅延量から両クロック信号CLKmz、CLKmdzの周波数を検出する回路である。ここで内部基本クロックCLKmdzは、例えば出力回路14に供給されることにより、外部基本クロックCLKとの位相を保持してデータをDQピンに出力するために使用されるものであり、外部基本クロックCLKの高速化が進展した場合に同期動作維持のために有効な内部クロック信号を提供するものである。

30

【0042】

さて、ディレイライン回路11Aの入出力信号CLKmz、CLKmdzは、比較器11Bにて位相比較が行なわれ、位相差に応じた位相比較信号PSRE、PSLE、PSRO、PSLOがアクティブポイント回路11Cに出力される。アクティブポイント回路11Cは、出力信号POI0乃至nのうちPOI0乃至k(0 < k < n)の論理信号レベルをハイレベルに、POIk乃至nの論理信号レベルをローレベルとして出力する回路であり、論理レベルの異なる境界点の信号POIk、POIk+1に応じた遅延量をディレイライン回路11Aに設定する回路である。例えば、大きなk値に対して設定されるディレ

40

50

イライン回路 11A の遅延量を小さくしておけば、高周波数のクロック信号  $C_{LKMz}$ 、 $C_{LKmdz}$  において、論理レベルがハイレベルとなるアクティブポインタ回路 11C の出力信号  $POI_0$  乃至  $k$  が多くなる（ $k$  が大きくなる。）ように位相比較信号  $PSRE$ 、 $PSLE$ 、 $PSRO$ 、 $PSLO$  が出力される。

【0043】

位相比較信号  $PSRE$ 、 $PSLE$ 、 $PSRO$ 、 $PSLO$  は、アクティブポインタ回路 11C において、出力信号  $POI_0$  乃至  $n$  の論理レベルの境界となる信号  $POIk$ 、 $POIk+1$  をクロック信号  $C_{LKMz}$ 、 $C_{LKmdz}$  間の位相ズレに応じて調整する信号である。

【0044】

具体的な信号  $POIk$ 、 $POIk+1$  の設定動作について、図 5、6 に基づき説明する。先ず、図 5 よりアクティブポインタ回路 11C の回路構成を説明する。出力信号  $POI_0$  乃至  $n$  の論理レベルラッチ回路  $L_0$  乃至  $n$  と、各ラッチ回路  $L_0$  乃至  $n$  の出力信号  $POIk$  乃至  $n$  及びその反転信号を接地電位  $VSS$  に接続する 2 つの NMOS トランジスタスイッチ ( $M_{kR1}$  及び  $M_{kR2}$ 、 $M_{kL1}$  及び  $M_{kL2}$ 、 $k = 0$  乃至  $n$ ) が直列に接続されている。

10

【0045】

直列接続されている 2 つの NMOS トランジスタスイッチ ( $M_{kR1}$  及び  $M_{kR2}$ 、 $M_{kL1}$  及び  $M_{kL2}$ 、 $k = 0$  乃至  $n$ ) のうち、ドレイン端子がラッチ回路  $L_0$  乃至  $n$  の出力信号  $POIk$  乃至  $n$  のノードに接続されている第 1 NMOS トランジスタ ( $M_{kL1}$ 、 $k = 0$  乃至  $n$ ) のゲート端子には次段ラッチ回路の反転信号ノードが接続され、ソース端子は第 2 NMOS トランジスタ ( $M_{kL2}$ 、 $k = 0$  乃至  $n$ ) のドレイン端子に接続されている。同様に、ラッチ回路  $L_0$  乃至  $n$  の反転信号ノードに接続されている第 1 NMOS トランジスタ ( $M_{kR1}$ 、 $k = 0$  乃至  $n$ ) のゲート端子は前段ラッチ回路の出力信号  $POIk$  乃至  $n$  のノードが接続され、ソース端子は第 2 NMOS トランジスタ ( $M_{kR2}$ 、 $k = 0$  乃至  $n$ ) のドレイン端子に接続されている。

20

【0046】

第 2 NMOS トランジスタ ( $M_{kL2}$ 、 $M_{kR2}$ 、 $k = 0$  乃至  $n$ ) のソース端子は接地電位  $VSS$  に接続されている。更に偶数段のラッチ回路  $L_i$  ( $i$  は 0 以上の偶数値) の出力信号  $POIk_i$  ( $i$  は 0 以上の偶数値) のノードに接続されている第 2 NMOS トランジスタ ( $M_{iL2}$ 、 $i$  は 0 以上の偶数値) のゲート端子には位相比較信号  $PSLE$  が接続され、偶数段のラッチ回路  $L_i$  ( $i$  は 0 以上の偶数値) の反転信号ノードに接続されている第 2 NMOS トランジスタ ( $M_{iR2}$ 、 $i$  は 0 以上の偶数値) のゲート端子には位相比較信号  $PSRE$  が接続されている。

30

【0047】

同様に、奇数段のラッチ回路  $L_j$  ( $j$  は 1 以上の奇数値) の出力信号  $POIk_j$  ( $j$  は 1 以上の奇数値) のノードに接続されている第 2 NMOS トランジスタ ( $M_{jL2}$ 、 $j$  は 1 以上の奇数値) のゲート端子には位相比較信号  $PSLO$  が接続され、奇数段のラッチ回路  $L_j$  ( $j$  は 1 以上の奇数値) の反転信号ノードに接続されている第 2 NMOS トランジスタ ( $M_{jR2}$ 、 $j$  は 1 以上の奇数値) のゲート端子には位相比較信号  $PSRO$  が接続されている。

40

【0048】

次に、図 6 よりアクティブポインタ回路 11C の動作を説明する。図 6 では、初期状態として出力信号  $POI_0$  乃至  $2$  の論理レベルがハイレベルであり、 $POI_3$  乃至  $n$  の論理レベルがローレベルであるとする。この状態から位相比較信号  $PSLE$  信号が入力されると、偶数段のラッチ回路  $L_i$  ( $i$  は 0 以上の偶数値) の出力信号ノードに接続されている第 2 NMOS トランジスタ ( $M_{iL2}$ 、 $i$  は 0 以上の偶数値) はオン状態となる。ここで、第 1 NMOS トランジスタのうちオンしているのは、ラッチ回路  $L_3$  乃至  $n$  の反転信号が入力されている第 1 NMOS トランジスタ ( $M_{mL1}$ 、 $m = 2$  乃至  $n$ ) である。従って、出力信号  $POI_2$  乃至  $n$  は接地電位  $VSS$  に接続されることとなり、このうち最下位の

50

出力信号 P O I 2 の論理レベルがハイレベルからローレベルに反転する。即ち、位相比較信号 P S L E が入力されることにより、アクティブポインタ回路 1 1 C の出力信号の境界点は 1 ビットだけ下位側にシフトする。

【 0 0 4 9 】

次のサイクルでは、位相比較信号 P S L O が入力される。この場合は、奇数段のラッチ回路 L j ( j は 1 以上の奇数値 ) の出力信号ノードに接続されている第 2 N M O S トランジスタ ( M j L 2 、 j は 1 以上の奇数値 ) がオン状態となる。第 1 N M O S トランジスタについてはラッチ回路 L 2 乃至 n の反転信号が入力されている第 1 N M O S トランジスタ ( M m L 1 、 m = 1 乃至 n ) がオンしているので、出力信号 P O I 1 乃至 n は接地電位 V S S に接続されることとなり、このうち最下位の出力信号 P O I 1 の論理レベルがハイレベルからローレベルに反転する。即ち、位相比較信号 P S L O が入力されることにより、アクティブポインタ回路 1 1 C の出力信号の境界点は 1 ビットだけ下位側にシフトする。

【 0 0 5 0 】

更に、次のサイクルで位相比較信号 P S R O が入力されると、奇数段のラッチ回路 L j ( j は 1 以上の奇数値 ) の反転信号ノードに接続されている第 2 N M O S トランジスタ ( M j R 2 、 j は 1 以上の奇数値 ) がオン状態となり、第 1 N M O S トランジスタについては、ラッチ回路 L 0 の出力信号 P O I 0 が入力されている第 1 N M O S トランジスタ M 1 R 1 のみがオンしているので、ラッチ回路 L 1 の反転出力ノードが接地電位 V S S に接続され、出力信号 P O I 1 の論理レベルがローレベルからハイレベルに反転する。即ち、位相比較信号 P S R O が入力されることにより、アクティブポインタ回路 1 1 C の出力信号の境界点は 1 ビットだけ上位側にシフトする。

【 0 0 5 1 】

続いて、次のサイクルで位相比較信号 P S R E が入力されると、偶数段のラッチ回路 L i ( i は 0 以上の偶数値 ) の反転信号ノードに接続されている第 2 N M O S トランジスタ ( M i R 2 、 i は 0 以上の偶数値 ) がオン状態となり、ラッチ回路 L 0 及び 1 の出力信号 P O I 0 、 1 が入力されている第 1 N M O S トランジスタ ( M m L 1 、 m = 0 乃至 2 ) がオンしているので、ラッチ回路 L i ( i = 0 , 2 ) の反転出力ノードが接地電位 V S S に接続され、出力信号 P O I 2 の論理レベルがローレベルからハイレベルに反転する。即ち、位相比較信号 P S R E が入力されることにより、アクティブポインタ回路 1 1 C の出力信号の論理レベル境界点は 1 ビットだけ上位側にシフトする。

【 0 0 5 2 】

更に、位相比較信号 P S R O が入力されれば、アクティブポインタ回路 1 1 C の出力信号の境界点は更に 1 ビットだけ上位側にシフトする。即ち、位相比較信号 P S R E 、 P S R O は出力信号の境界点を上位側に 1 ビットづつシフトし、位相比較信号 P S L E 、 P S L O は出力信号の境界点を下位側に 1 ビットづつシフトする働きをする信号である。後述の D / A コンバータ回路 1 3 及びリフレッシュ周期制御回路 1 2 の回路構成より、アクティブポインタ回路 1 1 C において、論理レベルがハイレベルを示す出力信号の数に比例してリフレッシュ周期が短くなる構成となっているので、高周波数の外部基本クロック C L K に対しては、位相比較信号 P S R E 、 P S R O が所定パルス数だけ入力されてアクティブポインタ回路 1 1 C の出力信号の論理レベル境界点を上位側にシフトし、低周波数においては、位相比較信号 P S L E 、 P S L O が所定パルス数だけ入力されてアクティブポインタ回路 1 1 C の出力信号の論理レベル境界点を下位側にシフトする制御を行なうこととなる。

【 0 0 5 3 】

D L L 回路 1 1 において検出された外部基本クロック C L K の周波数検出信号であるアクティブポインタ回路 1 1 C の出力信号 P O I 0 乃至 n は、デジタル信号であるため、後述のアナログ制御のリフレッシュ周期制御回路 1 2 を制御するためには、デジタル信号 P O I 0 乃至 n をアナログ信号に変換する必要がある。図 7 に示す D / A コンバータ回路 1 3 により、この動作を説明する。

【 0 0 5 4 】

10

20

30

40

50

図7のD/Aコンバータ回路13は、アクティブポインタ回路11Cからのデジタル信号POI0乃至nの論理ハイレベルのビット数に比例する電流値を、駆動電流として後述のリフレッシュ周期制御回路12に供給するための定電流源回路(図8中、MP、MN)のゲートバイアス電圧VOSCp、VOSCrを出力する。PMOSトランジスタMP1は電源電圧端子からのソース駆動電流を各定電流源回路(図8中、MP)が出力するためのゲートバイアス電圧VOSCpを設定する電流設定用トランジスタであり、そのドレン端子には、電流設定回路CS0乃至nにより生成されるデジタル信号POI0乃至nのハイレベルのビット数に対応する電流値が入力される。

#### 【0055】

定電流源回路を構成しているPMOSトランジスタMP1、MP2は、電流設定回路CS0乃至nにより生成されPMOSトランジスタMP1に入力される電流をシンク駆動電流として供給するために電流方向を変換する部分であり、PMOSトランジスタMP2からの電流出力は、電流制限用のNMOSトランジスタMN2を介してNMOSトランジスタMN1に入力される。NMOSトランジスタMN1は接地端子VSSへのシンク駆動電流を各定電流源回路(図9中、MN)が出力するためのゲートバイアス電圧VOSCrを設定する電流設定用トランジスタである。

#### 【0056】

電流設定回路CS0乃至nは、アクティブ信号SELF ACTIVEの電圧値により許容電流値が可変制御される電流制限用NMOSトランジスタと、ゲート端子にアクティブポインタ回路11Cからのデジタル信号POI0乃至nが入力されたNMOSトランジスタとを介して接地電位VSSに接続されている。デジタル信号POI0乃至nのうち論理ハイレベルとなるビット信号が入力されているNMOSトランジスタはオンするので、該当する電流設定回路CS0乃至nに電流制限用NMOSトランジスタにより制限された電流が流れ、この総和電流がPMOSトランジスタMP1における電流となる。従って、デジタル信号POI0乃至nのうち論理ハイレベルとなるビット数に比例した電流がPMOSトランジスタMP1に流れることとなる。

#### 【0057】

図7に示すD/Aコンバータ回路13によりデジタル信号からアナログ信号に変換された周波数検出信号は、アナログ信号VOSCp、VOSCrとして図8のリフレッシュ周期制御回路12に入力される。

#### 【0058】

リフレッシュ周期制御回路12は、インバータ論理ゲート回路を奇数段ループ状に接続した発振回路部分ROをリフレッシュ周期計測回路12Bとして発振回路のゲート遅延時間に対応した周期で発振する発振信号SELF OSCをリフレッシュ周期の源信号として使用する構成である。

#### 【0059】

発振回路部分ROの各インバータ論理ゲート回路のPMOSトランジスタ及びNMOSトランジスタのソース端子は、それぞれPMOSトランジスタ(MPの構成トランジスタ)及びNMOSトランジスタ(MNの構成トランジスタ)を介して電源電圧及び接地電位VSSに接続されている。このPMOSトランジスタ(MPの構成トランジスタ)のゲート端子は、アナログ信号VOSCpが接続されPMONトランジスタMP1との間で定電流源回路を構成し、またNMOSトランジスタ(MNの構成トランジスタ)のゲート端子は、アナログ信号VOSCrが接続されNMOSトランジスタMN1との間で定電流源回路を構成して、発振回路部分ROの各インバータ論理ゲート回路の駆動電流値を規定している。従って、インバータ論理ゲート回路は駆動電流値に応じて伝播遅延時間が制御されることとなり、発振回路部分ROの周期が制御されリフレッシュ周期が制御される。

#### 【0060】

上記の実施形態においては、周波数検出手段1としてDLL回路11を使用し、出力される周波数検出信号Aがデジタル信号POI0乃至nである場合に、リフレッシュ周期制御手段2として、駆動電流値が制御されるリフレッシュ周期制御回路12に対して、入力

10

20

30

40

50

信号 B に電流値設定電圧であるアナログ信号 V O S C p、V O S C n を入力するため、変換回路 3 として D / A コンバータ回路 13 により信号変換してインターフェースをとる手段について詳述した。

#### 【 0 0 6 1 】

周波数検出手段 1、リフレッシュ周期制御手段 2 は、従来より各々個別に様々な回路方式が提案されているが、それぞれの回路方式について両者を有機的に組み合わせて相互の関連をもたせることは、両者のインターフェース信号が異なる場合には必要に応じて変換回路 3 を付加してインターフェース信号の整合をとってやれば可能であり、様々な回路方式に対して両者を有機的に結びつけて相互に関連づけることにより本発明を実現することができる。

10

#### 【 0 0 6 2 】

以下に、各回路方式の具体例を示す。

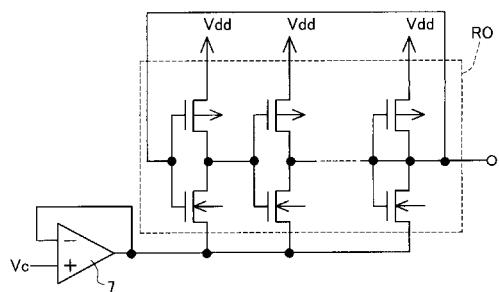

先ず、リフレッシュ周期制御手段 2 の他の具体例を示す。図 9 は、第 2 具体例である。発振回路部分 R O については図 8 の第 1 具体例と同一の構成を示している。第 2 具体例では、発振周期を制御する駆動能力の制御を電源電圧を制御することにより実現している。コントロール電圧 V c が入力されるバッファ回路 7 の出力端子を発振回路部分 R O の低電圧側端子に接続することにより低電圧側端子の電圧値を V c とすることで発振回路部分 R O の駆動電源電圧 ( V d d - V c ) をコントロール電圧 V c を可変として制御する方式である。第 2 具体例のリフレッシュ周期制御手段は、特開平 6 - 2 1 7 7 6 号公報に記載されている公知の回路方式である。

20

#### 【 0 0 6 3 】

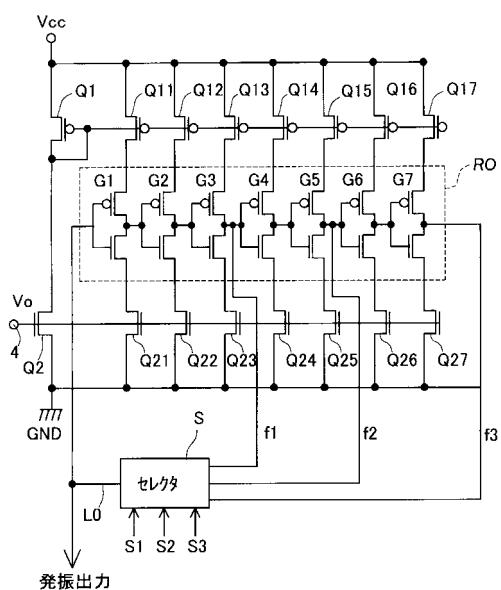

図 10 に示す第 3 具体例は、駆動電流を制御した発振回路として図 8 の第 1 具体例と同一の構成を有している。第 3 具体例では、更にセレクタ S により、発振回路部分 R O のループ段数を切り替えることにより発振周期を可変とした構成である。切替はセレクタ S に入力される信号 S 1 乃至 3 により行なわれる。セレクタ S は、具体的にはデジタル信号 S 1 乃至 3 により発振回路のループを形成するスイッチの開閉を切り替える構成が考えられる。第 3 具体例のリフレッシュ周期制御手段は、特開平 7 - 2 5 4 8 4 7 号公報に記載されている公知の回路方式である。

#### 【 0 0 6 4 】

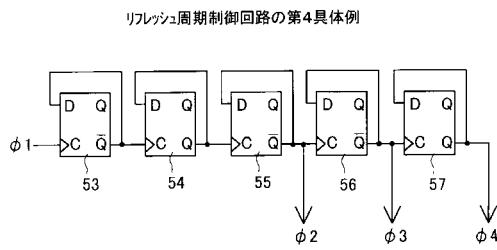

第 4 具体例は、図 11 に示す方式である。この回路は、D 型フリップフロップを直列に接続した分周回路を構成しており、初段の入力信号 1 として図示しない発振回路からの発振信号を入力して所定分周比の発振信号 ( 2、3、4 ) を適宜選択する構成である。分周された発振信号 ( 2、3、4 ) の選択は、図示しないセレクト回路により行なうことができ、第 3 具体例におけるセレクタ S を利用できる他、一般的なセレクト回路が使用可能である。第 4 具体例のリフレッシュ周期制御手段は、特開平 4 - 3 1 3 8 8 8 号公報に記載されている公知の回路方式である。

30

#### 【 0 0 6 5 】

次に、周波数検出手段の他の具体例を示す。図 12 は、D L L 回路の他の具体例でありアナログ制御方式の D L L 回路を示す。クロックバッファ C B と、位相比較器 F C P と、チャージポンプ C P と、ループフィルタ L F と、電圧制御遅延回路 V D L と、固定遅延回路 D L とを備えており、クロックバッファ C B にてバッファリングされた外部クロック信号 e x t . C L K をクロック信号 E C L K として出力して、位相比較器 F C P において内部クロック信号 i n t . C L K から生成するクロック信号 R C L K との位相比較を行なう。チャージポンプ C P では、位相比較結果の制御信号 / U P 、 D O W N を受けて出力電圧が出力され、ループフィルタ L F において平滑されたアナログ制御信号 V O I N として電圧制御遅延回路 V D L に供給され、内部クロック信号 i n t . C L K の周波数が調整される。

40

#### 【 0 0 6 6 】

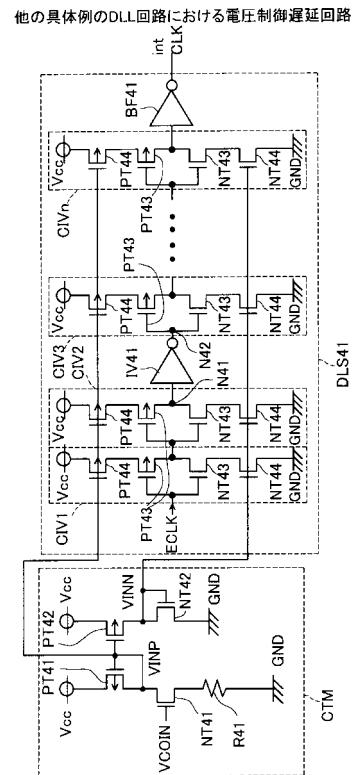

図 13 に、電圧制御遅延回路 V D L の回路構成例を示す。アナログ制御信号 V C O I N により電圧制御抵抗として動作する N M O S トランジスタ N T 4 1 により、P M O S トランジ

50

ンジスタ P T 4 1、P T 4 4 で構成されるソース電流供給用の定電流源回路の電流値とN M O SトランジスタN T 4 2、N T 4 4 で構成されるシンク電流供給用の定電流源回路の電流値とが調整されることにより、遅延回路D L S 4 1 における各反転回路C I V 1 乃至n のゲート伝播遅延時間が調整されてD L L 動作を行う。他の具体例におけるD L L 回路では、遅延時間の調整はアナログ制御信号V C O I N で行なわれることとなる。

#### 【0067】

更に、周波数検出手段として、P L L 回路を使用することも可能である。図14にアナログ制御方式のP L L 回路を示す。クロックバッファC Bと、位相比較器F C Pと、チャージポンプC Pと、ループフィルタL Fと、電圧制御発振器V C O と、固定遅延回路D L とを備えており、電圧制御発振器V C O を除き前述のD L L 回路の他の具体例(図12、参照)と同様の動作をする。また電圧制御発振器V C O は、一般的に使用される回路であるのでここでの説明は省略する。

10

#### 【0068】

従って、このP L L 回路においても、遅延時間の調整はアナログ制御信号V C O I N で行なわれることとなる。これらの周波数検出手段1は、特開2000-196444号公報に記載されている公知の回路方式である。この他に、デジタル回路方式のP L L 回路を使用すれば、遅延時間の調整はデジタル制御信号で行なわれることとなる。

20

#### 【0069】

以上の周波数検出手段1とリフレッシュ周期制御手段2とを適宜に組み合わせることによつても、本発明を実現することができる。

20

#### 【0070】

即ち、デジタル信号P O I 0 乃至n を出力信号とするD L L 回路1 1 と、アナログ信号のコントロール電圧V c を入力信号とするリフレッシュ周期制御回路(図9)とを組み合わせるために、デジタル信号P O I 0 乃至n をアナログ信号のコントロール電圧V c に変換するD / A コンバータ回路を変換回路3として備えればよい。

#### 【0071】

また、デジタル信号P O I 0 乃至n を出力信号とするD L L 回路1 1 と、同じくデジタル信号のセレクト信号(図10ではS 1 乃至3、図11では不図示)を入力信号とするリフレッシュ周期制御回路(図10、1 1 )とを組み合わせるために、デジタル信号P O I 0 乃至n をセレクト信号に変換するデコーダ回路を変換回路3として備えればよい。

30

#### 【0072】

また、アナログ制御信号V C O I N を有するD L L 回路(図12)と、アナログ信号の電流値設定電圧V O S C p 、V O S C n を入力信号とするリフレッシュ周期制御回路1 2 やアナログ信号のコントロール電圧V c を入力信号とするリフレッシュ周期制御回路(図9)とを組み合わせるために、アナログ制御信号V C O I N をレベル変換あるいは電圧電流変換する回路を変換回路3として備えればよい。

#### 【0073】

また、アナログ制御信号V C O I N を有するD L L 回路(図12)と、デジタル信号のセレクト信号(図10ではS 1 乃至3、図11では不図示)を入力信号とするリフレッシュ周期制御回路(図10、1 1 )とを組み合わせるために、アナログ制御信号V C O I N をセレクト信号に変換するA / D コンバータ回路を変換回路3として備えればよい。

40

#### 【0074】

P L L 回路についても、位相比較信号としてデジタル信号を使用するもの、あるいはアナログ信号を使用するものがそれぞれ考えられるが、これらとリフレッシュ周期制御手段2とのインターフェースについても、前述のD L L 回路についてのものと同様に構成することができる。

#### 【0075】

以上詳細に説明したとおり、本実施形態に係る同期型半導体記憶装置では、周波数検出手段1であるD L L 回路(1 1 、図12)やP L L 回路(図14)と、リフレッシュ周期制御手段2である第1乃至4具体例(1 2 、図9乃至1 1 )とを関連づけることにより、

50

外部基本クロック C L K の周波数に応じて変化する同期型半導体記憶装置のデバイス温度でのメモリセルの電荷保持特性に適合して、自動的にリフレッシュ周期を設定することができるので、メモリセルの電荷保持の温度特性の測定試験をして同期型半導体記憶装置毎にリフレッシュ周期を設定する必要はない。

【 0 0 7 6 】

また、製造ばらつきにより検出精度の確保が難しい温度検出手段を必要とせず、外部基本クロック C L K という安定した信号を温度センサーとして利用できるので、簡便且つ確実にデバイス温度に適合したリフレッシュ周期を設定でき、全デバイス温度範囲において最適なリフレッシュ周期を自動的に実現でき、消費電流の低減を図ることができる。

【 0 0 7 7 】

更に、外部基本クロック C L K の高速化に伴うデバイス温度の上昇により、メモリセルの電荷保持時間が減少しても、外部基本クロック C L K に応じてリフレッシュ周期が短くなるので、動作周波数の変化によりデバイス温度が変化しても、常に最適なリフレッシュ周期にてリフレッシュ動作が行われ、メモリセルの電荷保持の信頼性を外部基本クロック C L K という安定した信号を利用して簡便且つ確実に確保することができる。

【 0 0 7 8 】

また、周波数検出手段 1 である D L L 回路 ( 1 1 、 図 1 2 ) や P L L 回路 ( 図 1 4 ) と、リフレッシュ周期制御手段 2 である第 1 乃至 4 具体例 ( 1 2 、 図 9 乃至 1 1 ) との関連づけに際しては、インターフェース信号の信号変換を行なう変換回路 3 としては、周波数検出手段 1 からの出力信号及びリフレッシュ周期制御手段 2 への入力信号における信号形式に応じて、D / A コンバータ回路 1 3 の他、他の方式の D / A コンバータ回路、デコーダ回路、レベル変換あるいは電圧電流変換する回路、または A / D コンバータ回路等の変換回路 3 を、信号間のインターフェースをとるために必要に応じて挿入してやれば、種々の信号形式に対してインターフェースをとることができるので、周波数検出手段 1 及びリフレッシュ周期制御手段 2 の回路方式を選ぶことなく本発明の構成を実現することができる。

【 0 0 7 9 】

従って、リフレッシュ周期制御手段 2 として、発振回路の動作周期を駆動電流や電源電圧といったアナログ信号により制御する場合 ( 駆動電流の回路方式として図 8 を参照、電源電圧の回路方式として図 9 を参照 ) 、また発振回路のループ段数を切り替える回路方式 ( 図 1 0 の回路方式 ) や発振回路出力の分周比を切り替える方式 ( 図 1 1 の回路方式 ) といったデジタル信号により制御する場合の何れの場合に対しても、周波数検出手段 1 である D L L 回路 ( 1 1 、 図 1 2 ) や P L L 回路 ( 図 1 4 ) 、更にデジタル出力の P L L 回路を組み合わせることができる。

【 0 0 8 0 】

尚、本発明は前記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内で種々の改良、変形が可能であることは言うまでもない。

本実施形態においては、周波数検出手段 1 として D L L 回路や P L L 回路を例にとり説明したが、回路方式はこれに限定されるものではなく、例えば、所定時間内の外部基本クロックのエッジ数をカウントしたり、エッジ間の時間を計測する回路構成により外部基本クロックの周波数や周期を検出できる回路であれば適用することができる。

【 0 0 8 1 】

また、リフレッシュ周期制御手段 2 についても、発振回路に限定されることはなく、例えば、所定コンデンサの充電電圧が所定電位になるまでの時間を計測するアナログタイマにおいて、充電電流を外部基本クロックの周波数に応じて制御するような回路方式等、可変時間を計測する機能を有する回路構成であれば適用可能である。

【 0 0 8 2 】

更に、インターフェース信号の変換回路 3 についても、D / A コンバータ回路、A / D コンバータ回路、デコーダ回路、レベル変換回路、あるいは電圧電流変換回路等の他にも、周波数を変換する方式や外部基本クロックとリフレッシュ周期とのマッピングテーブル

10

20

30

40

50

を備えておく方式等を利用することも可能である。具体的には、例えば、周波数変換回路方式として外部基本クロックをメモリセルのリフレッシュ周期に適した周波数にまで分周する分周回路を備えることにより外部基本クロックの分周信号としてリフレッシュ周期を設定する制御を行なう方式や、マッピングテーブルとして、外部基本クロックとそれに適合したリフレッシュ周期との対応関係をテーブルとして記憶しておき、入力される外部基本クロックに応じて該当するリフレッシュ周期をテーブルから読み出すことにより制御する方式も可能である。

【0083】

(付記1)周期的にメモリセルのリフレッシュを必要とする同期型半導体記憶装置において、

10

外部基本クロックの周波数を検出する検出手段と、

前記検出手段より出力される周波数検出信号に基づきリフレッシュ周期を制御する周期制御手段とを備えることを特徴とする同期型半導体記憶装置。

【0084】

(付記2)前記周期制御手段は、

前記外部基本クロックの周波数が高いほど、前記リフレッシュ周期を短くするように制御することを特徴とする付記1に記載の同期型半導体記憶装置。

【0085】

(付記3)前記周期制御手段は、

前記リフレッシュ周期を計測するための周期計測手段と、

20

計測される前記リフレッシュ周期を前記周波数検出信号に基づき可変とする計測周期変更手段とを備えることを特徴とする付記1又は2に記載の同期型半導体記憶装置。

【0086】

(付記4)前記周期計測手段は、発振回路を備え、

前記計測周期変更手段は、前記発振回路の駆動電流を前記周波数検出信号に基づき可変とする電流源回路を備えることを特徴とする付記3に記載の同期型半導体記憶装置。

【0087】

(付記5)前記周期計測手段は、発振回路を備え、

前記計測周期変更手段は、前記発振回路の電源電圧を前記周波数検出信号に基づき可変とする電圧源回路を備えることを特徴とする付記3に記載の同期型半導体記憶装置。

30

【0088】

(付記6)前記周期計測手段は、発振回路を備え、

前記計測周期変更手段は、前記発振回路におけるループ状に接続された奇数段の反転回路の段数を前記周波数検出信号に基づき可変とする段数切替回路を備えることを特徴とする付記3に記載の同期型半導体記憶装置。

【0089】

(付記7)前記周期計測手段は、発振回路と分周回路とを備え、

前記計測周期変更手段は、前記分周回路の分周比を前記周波数検出信号に基づき可変とする分周比切替回路を備えることを特徴とする付記3に記載の同期型半導体記憶装置。

【0090】

(付記8)前記検出手段は、

前記外部基本クロックと周波数及び位相が一致する内部基本クロックを生成する位相比較手段を備え、該位相比較手段から前記周波数検出信号が output されることを特徴とする付記1乃至7の少なくとも何れか1に記載の同期型半導体記憶装置。

40

【0091】

(付記9)前記周波数検出信号がデジタル信号である場合、

前記周波数検出信号をアナログ信号に変換する第1変換回路を備えることを特徴とする付記4又は5に記載の同期型半導体記憶装置。

【0092】

(付記10)前記周波数検出信号がアナログ信号である場合、

50

前記周波数検出信号をデジタル信号に変換する第2変換回路を備えることを特徴とする付記6又は7に記載の同期型半導体記憶装置。

【0093】

(付記11)周期的にメモリセルのリフレッシュを必要とする同期型半導体記憶装置のリフレッシュ方法において、

外部基本クロックの周波数を検出する検出工程と、

前記検出工程より出力される周波数検出信号に基づきリフレッシュ周期を制御する周期制御工程とを有することを特徴とする同期型半導体記憶装置のリフレッシュ方法。

【0094】

(付記12)前記周期制御工程は、

10

前記外部基本クロックの周波数が高いほど、前記リフレッシュ周期を短くするように制御することを特徴とする付記11に記載の同期型半導体記憶装置のリフレッシュ方法。

【0095】

【発明の効果】

本発明によれば、製造ばらつきに影響されることなく、リフレッシュ時間の調整前に多大な特性測定のための試験時間を必要とすることもなく、リフレッシュ保持特性時間に最適なリフレッシュ周期を提供し、リフレッシュ動作における消費電流の低減を図ることができる同期型半導体記憶装置を提供することが可能となる。

【図面の簡単な説明】

【図1】本発明の第1原理説明図である。

20

【図2】本発明の第2原理説明図である。

【図3】本発明の第3原理説明図である。

【図4】本発明の実施形態におけるリフレッシュ周期設定回路を示す回路ブロック図である。

【図5】本実施形態におけるアクティブポインタ回路を示す回路図である。

【図6】アクティブポインタ回路の動作波形である。

【図7】本実施形態におけるD/Aコンバータ回路を示す回路図である。

【図8】本実施形態におけるリフレッシュ周期制御回路を示す回路図(第1具体例)である。

【図9】リフレッシュ周期制御回路の第2具体例を示す回路図である。

30

【図10】リフレッシュ周期制御回路の第3具体例を示す回路図である。

【図11】リフレッシュ周期制御回路の第4具体例を示す回路図である。

【図12】DLL回路の他の具体例を示す回路ブロック図である。

【図13】他の具体例のDLL回路における電圧制御遅延回路を示す回路図である。

【図14】PLL回路の具体例を示す回路ブロック図である。

【符号の説明】

1 周波数検出手段

2 リフレッシュ周期制御手段

2A 計測周期変更手段

2B リフレッシュ周期計測手段

40

3 変換回路

11 DLL回路

11A ディレイライン回路

11B 比較器

11C アクティブポインタ回路

12 リフレッシュ周期制御回路

12A 計測周期変更回路

12B リフレッシュ周期計測回路

13 D/Aコンバータ回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

実施形態におけるD/Aコンバータ回路の回路図

【図8】

実施形態におけるリフレッシュ周期制御回路の回路図(第1具体例)

【図9】

リフレッシュ周期制御回路の第2具体例

【図10】

リフレッシュ周期制御回路の第3具体例

【図 1 1】

【図 1 3】

【図 1 2】

【図 1 4】

---

フロントページの続き

(56)参考文献 特開2001-210074(JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/40-11/4099