## (10) **DE 10 2012 108 142 B4** 2017.01.26

(12)

## **Patentschrift**

(21) Aktenzeichen: 10 2012 108 142.5

(22) Anmeldetag: 03.09.2012(43) Offenlegungstag: 09.01.2014

(45) Veröffentlichungstag

der Patenterteilung: 26.01.2017

(51) Int Cl.: **H01L 29/78** (2006.01)

**H01L 29/06** (2006.01) **H01L 27/088** (2006.01) **H01L 21/761** (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

13/541,539 03.07.2012 US

(73) Patentinhaber:

Taiwan Semiconductor Manufacturing Co., Ltd., Hsinchu, TW

(74) Vertreter:

BOEHMERT & BOEHMERT Anwaltspartnerschaft mbB - Patentanwälte Rechtsanwälte, 28209 Bremen, DE (72) Erfinder:

Chou, Hsueh-Liang, Jhubei, Hsinchu, TW; Ng, Chun-Wai, Hsinchu, TW; Su, Po-Chih, New Taipei City, TW; Liu, Ruey-Hsin, Hsin-Chu, TW

(56) Ermittelter Stand der Technik:

US 6 365 932 B1 US 5 485 028 A

#### (54) Bezeichnung: MOS-Transistor

(57) Hauptanspruch: Transistor, der aufweist:

einen ersten Transistor, der ein erstes Gate, eine erste Source, einen ersten Drain und einen ersten Aufbaukontakt aufweist, wobei:

der erste Aufbaukontakt und die erste Source in der Draufsicht abwechselnd ausgebildet sind; und

die erste Source in einem ersten gestapelten Wallabschnitt ausgebildet ist, wobei der erste gestapelte Wallabschnitt aufweist:

einen ersten Bereich mit einer ersten Leitfähigkeit, der über einem Substrat mit einer ersten Leitfähigkeit ausgebildet ist; und

einen zweiten Bereich mit der ersten Leitfähigkeit, der in den ersten Bereich eingebettet ist;

einen zweiten Transistor, der ein zweites Gate, eine zweite Source, einen zweiten Drain und einen zweiten Aufbaukontakt aufweist, wobei der erste Drain und der zweite Drain miteinander verbunden sind, und wobei:

der zweite Aufbaukontakt und die zweite Source in der Draufsicht abwechselnd ausgebildet sind;

die zweite Source in einem zweiten gestapelten Wallabschnitt ausgebildet ist, wobei der zweite gestapelte Wallabschnitt aufweist:

einen dritten Bereich mit der ersten Leitfähigkeit, der über dem Substrat ausgebildet ist; und

einen vierten Bereich mit der ersten Leitfähigkeit, der in dem dritten Bereich eingebettet ist; und

einen Aufbauaufnahmering, der den ersten Transistor und den zweiten Transistor umgibt,

dadurch gekennzeichnet, dass der Transistor weiterhin die folgenden Merkmale aufweist:

einen ersten leicht dotierten Source/Drain-Bereich mit der ersten Leitfähigkeit, der angrenzend an die erste Source in dem zweiten Bereich angeordnet ist; und

einen zweiten leicht dotierten Drain/Source-Bereich mit der ersten Leitfähigkeit, der angrenzend an den ersten Drain in dem Substrat ausgebildet ist, wobei der zweite leicht dotierte Drain/Source-Bereich unter dem ersten Gate angeordnet ist.

#### **Beschreibung**

#### HINTERGRUND

**[0001]** Die Erfindung geht von einem Transistor mit den Merkmalen des Oberbegriffs des Patentanspruchs 1 aus. Ähnliche Transistoren sind aus der US 6 365 932 B1 und aus der US 5 485 028 A bekannt.

[0002] Die Halbleiterindustrie hat aufgrund von Fortschritten bei der Integrationsdichte einer Vielzahl elektronischer Bauelemente (z. B. Transistoren, Dioden, Widerstände, Kondensatoren, usw.) ein rasches Wachstum erfahren. Die Verbesserung der Integrationsdichte ist größtenteils in dem Zusammenschrumpfen des Halbleiterprozessknotens begründet (z. B. Einschrumpfen des Prozessknotens bis unterhalb des 20 nm-Knotens). Mit dem Verkleinern der Halbleiterbauteile werden neue Technologien benötigt, um die Leistungsfähigkeit der elektronischen Bauteile von Generation zu Generation aufrecht zu erhalten. Für Starkstromanwendungen sind beispielsweise niedrige Gate-to-drain-Kapazitäten und hohe Durchbruchspannungen des Transistors wünschenswert.

[0003] Mit der Weiterentwicklung der Halbleitertechnologien werden heutzutage Metalloxidhalbleiterfeldeffekttransistoren (MOSFET) in weiten Bereichen der integrierten Schaltkreise verwendet. MOSFETs sind spannungsgesteuerte Bauteile. Wenn eine Steuerspannung an das Gate eines MOSFETs angelegt wird und die Steuerspannung größer als der Grenzwert des MOSFETs ist, bildet sich ein leitfähiger Kanal zwischen der Drain und der Source des MOSFETs. Dies resultiert dann, dass ein Strom zwischen der Drain und der Source des MOSFETs fließt. Andererseits wird der MOSFET dementsprechend deaktiviert, wenn die Steuerspannung geringer als ein Schwellwert des MOSFETs ist.

**[0004]** MOSFETs können in zwei Hauptkategorien unterteilt werden. Die eine sind n-Kanal-MOSFETs; die anderen sind p-MOSFETs. Aufgrund von Strukturunterschieden können MOSFETs in zwei weitere Unterkategorien unterteilt werden, nämlich Trench-Power-MOSFETs und Lateral-Power-MOSFETs.

[0005] Während die Prozessknoten weiter schrumpfen, sinken die physikalischen Abmessungen der MOSFETs. Die verkleinerte Struktur der MOSFETs kann zu einer Änderung der elektrischen Eigenschaften der MOSFETs aufgrund von Kurzkanaleffekten führen. Zum Beispiel wird eine kürzere Kanallänge verwendet, um den On-Widerstand zu verringern und um einen MOSFET mit niedrigem On-Widerstand zu erhalten. Jedoch kann solch eine kürzere Kanallänge den Kurzkanaleffekt verursachen. Genauer kann im Ergebnis das Risiko von Durchschlagfehlern anstei-

gen, wenn der Drainbereich oder der Sourcebereich des MOSFETs dichter aneinanderrücken.

**[0006]** Es ist daher die Aufgabe der Erfindung, einen gattungsgemäßen Transistor derart weiter zu entwickeln, dass das Risiko von Durchschlagfehlern minimiert wird.

#### ZUSAMMENFASSUNG

**[0007]** Diese Aufgabe wird durch einen Transistor mit den Merkmalen des Anspruchs 1 gelöst. Die abhängigen Ansprüche betreffen jeweils vorteilhafte Ausführunggsformen.

[0008] Die Erfindung stellt einen Transistor bereit, der aufweist: einen ersten Transistor, der eine erste Gate, eine erste Source, einen ersten Drain und einen ersten Aufbaukontakt aufweist, wobei: der erste Aufbaukontakt und die erste Source sind in der Draufsicht abwechselnd ausgebildet; und die erste Source ist in einem ersten gestapelten Wallabschnitt ausgebildet, wobei der erste gestapelte Wallabschitt aufweist: einen ersten Abschnitt mit einer ersten Leitfähigkeit, der über einem Substrat der ersten Leitfähigkeit ausgebildet ist; und einen zweiten Bereich mit der ersten Leitfähigkeit, der in dem ersten Bereich eingebettet ist; einen zweiten Transistor, der eine zweite Gate, eine zweite Source, einen zweiten Drain und einen zweiten Aufbaukontakt aufweist, wobei der erste Drain und der zweite Drain miteinander verbunden sind, und wobei: der erste Aufbaukontakt und die zweite Drain sind in der Draufsicht abwechselnd ausgebildet, wobei die zweite Source in einem zweiten gestapelten Wallabschnitt ausgebildet ist, wobei der gestapelte Wallabschnitt aufweist: einen dritten Abschnitt mit der ersten Leitfähigkeit, der über dem Substrat ausgebildet ist; und einen vierten Abschnitt mit der ersten Leitfähigkeit, der in die dritte Region eingebettet ist; und einen Aufbauaufnahmering, der den ersten Transistor und den zweiten Transistor umgibt.

[0009] Der Transistor zeichnet sich dadurch aus, dass er weiterhin die folgenden Merkmale aufweist: einen ersten leicht dotierten Source/Drain-Bereich mit der ersten Leitfähigkeit, der an die erste Source in dem zweiten Bereich angrenzt; und einen zweiten leicht dotierten Drain/Source-Bereich mit der ersten Leitfähigkeit der angrenzend an den ersten Drain in dem Substrat ausgebildet ist, wobei der zweite leicht dotierte Drain/Source-Bereich unter der ersten Gate angeordnet ist.

**[0010]** Der Transistor kann darüber hinaus einen Aufbauaufnahmering mit der ersten Leitfähigkeit, der den ersten Transistor und den zweiten Transistor in dem Substrat umgibt, aufweisen.

**[0011]** Der zweite Bereich kann eine höhere Dotierungsdichte als der erste Bereich aufweisen.

#### KURZE BESCHREIBUNG DER FIGUREN

**[0012]** Für ein umfassenderes Verständnis der vorliegenden Offenbarung und deren Vorteile wird nunmehr auf die nachstehende Beschreibung in Verbindung mit den begleitenden Figuren Bezug genommen, in welchen:

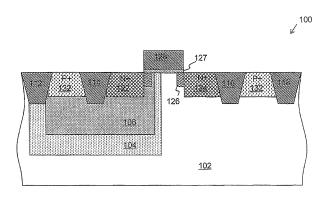

**[0013] Fig.** 1 eine vereinfachte Querschnittsansicht eines MOS-Transistors mit überlagerten Wällen gemäß einer Ausführungsform veranschaulicht;

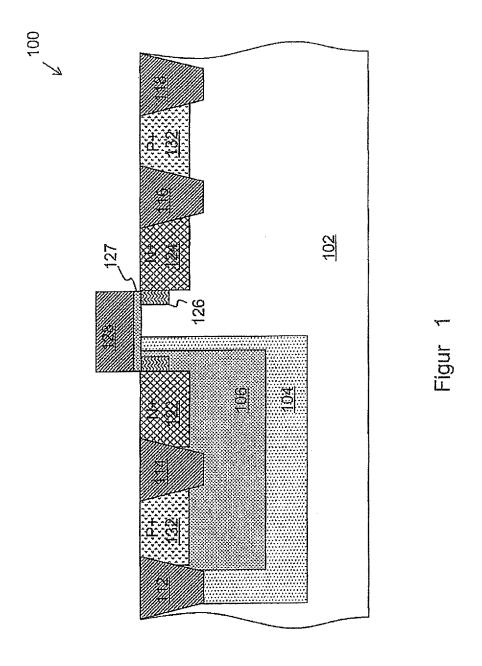

**[0014] Fig.** 2 zwei Graphen veranschaulicht, die den Unterschied in der Dotierungsdichte zwischen einem herkömmlichen MOS-Transistor mit einem p-Wall von 5 V und einem MOS-Transistor mit zwei überlagerten p-Wällen veranschaulicht;

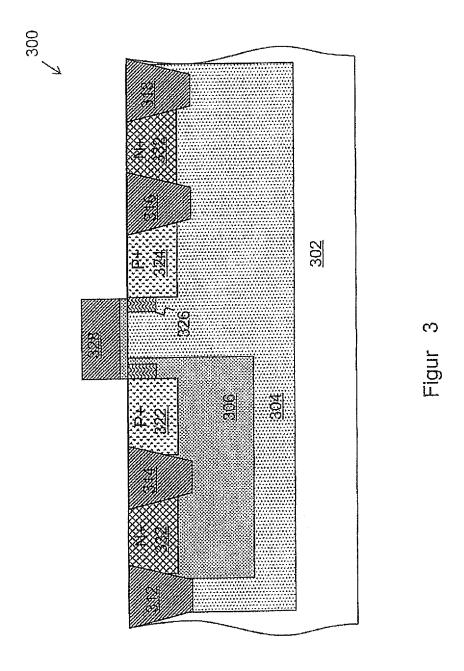

**[0015] Fig.** 3 eine vereinfachte Querschnittsansicht eines MOS-Transistors mit überlagerten Wällen gemäß einer weiteren Ausführungsform der Erfindung veranschaulicht:

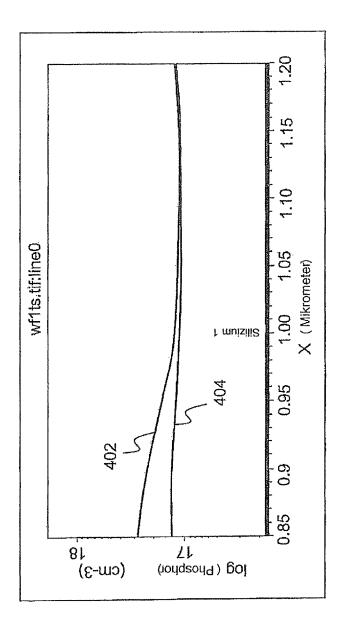

**[0016]** Fig. 4 zwei Graphen veranschaulicht, die den Unterschied in der Dotierungsdichte zwischen einem herkömmlichen MOS-Transistor mit einem p-Wall von 5 V und dem in Fig. 3 gezeigten MOS-Transistor veranschaulichen;

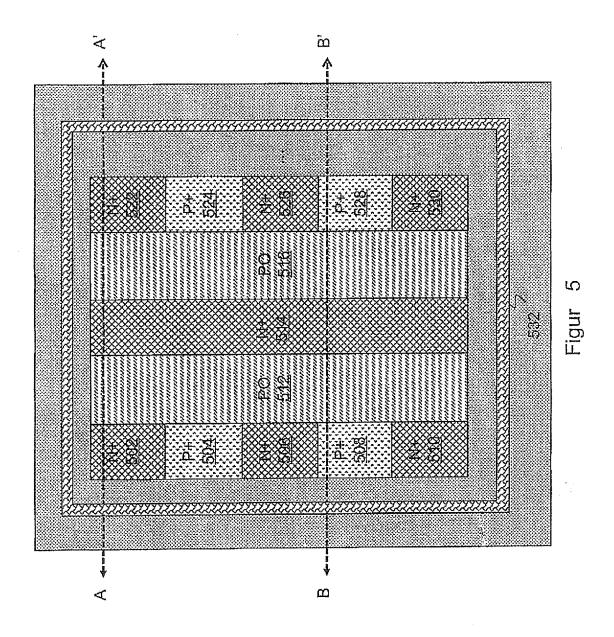

**[0017] Fig.** 5 eine vereinfachte Draufsicht auf eine MOS-Transistoranordnung gemäß einer Ausführungsform veranschaulicht;

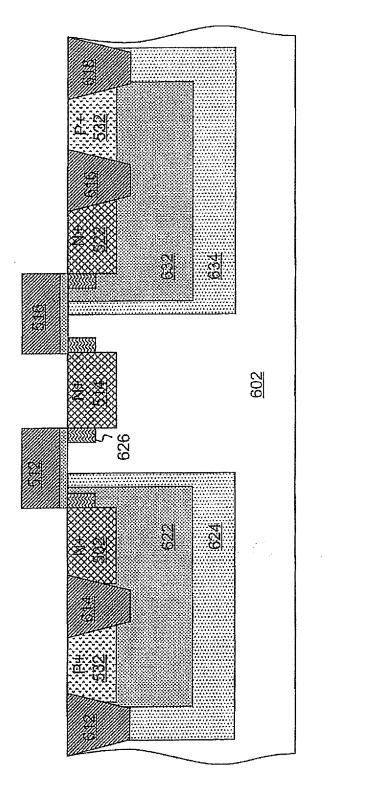

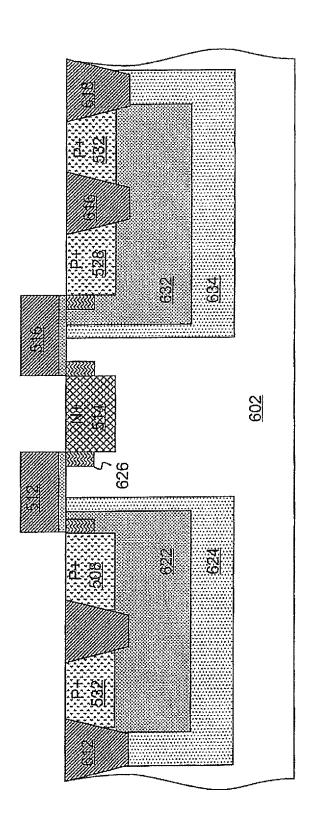

**[0018] Fig.** 6 eine Querschnittsansicht der in **Fig.** 5 gezeigten MOS-Transistoranordnung gemäß einer Ausführungsform veranschaulicht;

**[0019] Fig.** 7 eine weitere Querschnittsansicht der in **Fig.** 5 gezeigten MOS-Transistoranordnung gemäß einer Ausführungsform veranschaulicht;

**[0020] Fig.** 8 eine vereinfachte Draufsicht auf die MOS-Transistoranordnung gemäß einer weiteren Ausführungsform veranschaulicht;

**[0021] Fig.** 9 eine Querschnittsansicht des in **Fig.** 8 gezeigten MOS-Transistoraufbaus gemäß einer Ausführungsform veranschaulicht; und

[0022] Fig. 10 eine weitere Querschnittsansicht des in Fig. 8 gezeigten MOS-Transistoraufbaus gemäß einer Ausführungsform veranschaulicht.

**[0023]** Übereinstimmende Bezugszeichen und Symbole in den verschiedenen Figuren betreffen grundsätzlich übereinstimmende Bestandteile, falls dies nicht anderweitig angegeben ist. Die Figuren wurden gezeichnet, um die relevanten Aspekte der verschiedenen Ausführungsformen klar zu veranschaulichen,

und sie sind nicht notwendigerweise maßstabsgetreu gezeichnet.

# GENAUE BESCHREIBUNG DER VERANSCHAULICHENDEN AUSFÜHRUNGSFORMEN

[0024] Die Herstellung und Verwendung der vorliegenden Ausführungsformen werden nachstehend im Detail diskutiert. Es sollte jedoch berücksichtigt werden, dass die vorliegende Offenbarung eine Vielzahl umsetzbarer erfindungsgemäßer Konzepte bereitstellt, die in einem großen Bereich bestimmter Zusammenhänge umgesetzt werden können. Die diskutierten genauen Ausführungsformen sind lediglich zur Veranschaulichung bestimmter Wege zur Herstellung und Verwendung der Ausführungsformen der Offenbarung gedacht, und sollen den Umfang der Offenbarung nicht beschränken.

**[0025]** Die vorliegende Offenbarung wird mit Bezug auf Ausführungsformen in einem bestimmten Zusammenhang, nämlich mit Bezug auf eine laterale Metalloxidhalbleiter(MOS)-Vorrichtung mit überlagerten Wällen beschrieben. Die Ausführungsformen der Offenbarung können jedoch auch auf eine Vielfalt von Halbleiterbauteilen angewendet werden.

[0026] Die Fig. 1 veranschaulicht eine vereinfachte Querschnittsansicht eines MOS-Transistors mit überlagerten Wällen gemäß einer Ausführungsform. Der MOS-Transistor 100 umfasst ein Substrat 102, vorzugsweise des P-Typs, einen ersten P-Typbereich 104 und einen zweiten P-Typbereich 106, die in dem Substrat 102 ausgebildet sind. Genauer ist der zweite P-Typbereich 106 in den ersten P-Typbereich 104 eingebettet.

[0027] Ein P+-Bereich 132 und ein erster N+-Bereich 122 sind in dem zweiten P-Typbereich 106 ausgebildet. Ein zweiter N+-Bereich 124 und ein zweiter P+-Bereich 132 sind in dem Substrat 102 ausgebildet. Wie in Fig. 1 gezeigt ist, sind der erste N+-Bereich 122 und der zweite N+-Bereich 124 auf gegenüberliegenden Seiten einer Gelelektrode 128 ausgebildet.

[0028] Um die Leistungsfähigkeit des MOS-Transistors 100 zu verbessern, sind zwei leicht dotierte Drain/Source(LDD)-Bereiche 126 angrenzend an ihren entsprechenden N+-Bereich (erster N+-Bereich 122 und zweiter N+-Bereich 124) ausgebildet. Gemäß einer Ausführungsform wirkt der erste N+-Bereich 122 wie ein Source-Bereich des MOS-Transistors; der zweite N+-Bereich wirkt wie ein Drain-Bereich des MOS-Transistors 100. Die LDD-Bereiche 126 wirken als Erweiterungen ihrer entsprechenden Drain-Bereiche 124 und Source-Bereiche 122. Der MOS-Transistor 100 weist weiterhin eine dielektrische Gateschicht 127 auf, und die Gateelektrode 128

ist über der dielektrischen Gateschicht 127 ausgebildet.

[0029] Das Substrat 102 kann aus Lithium, Silizium-Germanium, Siliziumkarbid oder dergleichen ausgebildet sein. Alternativ kann das Substrat 102 ein Silizium-auf-Isolator(SOI)-Substrat sein. Das SOI-Substrat kann eine Schicht eines Halbleitermaterials (z. B. Silizium, Germanium und dergleichen) aufweisen, das über einer Isolatorschicht (z. B. einem verdeckten Oxid und dergleichen), welches in einem Siliziumsubstrat ausgebildet ist, ausgebildet sein. Andere Substrate, die verwendet werden können, umfassen Vielschichtsubstrate, Gradientensubstrate, hybridorientierte Substrate und dergleichen.

[0030] Der erste P-Typbereich 104 und der zweite P-Typbereich 106 können durch das Einbringen von P-Typ-Dotiermaterial wie Bor, Gallium, Aluminium, Indium, Kombinationen dieser oder dergleichen ausgebildet werden. Alternativ können die P-Typbereiche 106 mittels eines Diffusionsprozesses ausgebildet werden. Gemäß einer Ausführungsform wird ein komplementärer 5 V Metalloxidhalbleiter(CMOS)-Prozess angewendet, um den ersten P-Typwall 104 auszubilden. Ein 1,8 V CMOS-Prozess wird angewendet, um den zweiten P-Typwall 106 auszubilden.

[0031] Da der zweite P-Typwall 106 in den ersten P-Typwall 104 eingebettet ist, ist die kombinierte Dotierungsdichte größer als bei konventionellen P-Wällen, die mittels eines einzigen 5 V-CMOS-Prozesses ausgebildet worden sind. Die kombinierte Dotierungsdichte der P-Wälle bewegt sich in einem Bereich von ungefähr 10<sup>17</sup>/cm³ bis ungefähr 10<sup>18</sup>/cm³. Es sollte festgehalten werden, dass der Bildungsprozess des ersten P-Typbereichs 104 und des zweiten P-Typbereichs 106 kompatibel mit den bestehenden Herstellungsprozessen für MOS-Transistoren ist. Mit anderen Worten können die in Fig. 1 gezeigten überlagerten Wälle ohne zusätzliche Herstellungsschritte gebildet werden.

[0032] Der erste N+-Bereich 122 wird über dem zweiten P-Typwall 106 gebildet. Gemäß einer Ausführungsform wirkt der erste N+-Bereich 122 als die Source des MOS-Transistors 100. Der Sourcebereich kann durch die Einbindung eines Dotand des n-Typs, wie Phosphor, mit einer Konzentration zwischen ungefähr 10<sup>19</sup>/cm³ und ungefähr 10<sup>20</sup>/cm³ ausgebildet werden. Wie in Fig. 1 gezeigt ist, wird der Drainbereich auf gegenüberliegenden Seiten der Source (der erste N+-Bereich 122) ausgebildet.

[0033] Der in Fig. 1 gezeigte P+-Bereich 132 kann Bestandteil eines P+-Aufnahmerings sein. Der P+-Aufnahmering kann die Drain- und Source-Bereiche des MOS-Transistors 100 umgeben. Somit können dort zwei P+-Bereiche 132 vorliegen, die in Fig. 1 in der Querschnittsansicht des MOS-Transistors 100

gezeigt sind. Ein erster P+-Bereich 122 ist angrenzend an den ersten N+-Bereich 122 und durch einen Isolierbereich 114 getrennt von dem ersten N+-Bereich 122 ausgebildet. Der zweite P+-Bereich 132 ist angrenzend an den zweiten N+-Bereich 124 und mittels eines weiteren Isolierabschnitts 116 getrennt von dem zweiten N+-Bereich 124 ausgebildet.

[0034] Der P+-Bereich 132 kann durch Einbinden eines Dotands des p-Typs wie Bor bei einer Konzentration zwischen ungefähr 10<sup>19</sup>/cm³ und ungefähr 10<sup>20</sup>/cm³ ausgebildet werden. Der P+-Bereich 132 kann mit dem p-Typaufbau (das Substrat 102) des MOS-Transistors 100 über den zweiten P-Typwall 106 und den ersten P-Typwall 104 verbunden werden. Um den Aufbaueffekt zu unterbinden kann der P+-Bereich 132 unmittelbar über den Source-Kontakt (nicht dargestellt) mit der Source 122 verbunden werden.

[0035] Die dielektrische Gateschicht 127 ist zwischen dem ersten N+-Bereich und dem zweiten N+-Bereich 124 ausgebildet. Die dielektrische Gateschicht 127 kann aus Siliziumoxid, Siliziumoxinitrid, Hafniumoxid, Zirkoniumoxid oder dergleichen gebildet sein.

[0036] Gemäß einer Ausführungsform besitzt die dielektrische Gateschicht 127 eine Dicke zwischen ungefähr 10 nm und ungefähr 20 nm (100 A und ungefähr 200 A). Auf der dielektrischen Gateschicht 127 ist eine Gateelektrode 128 ausgebildet. Die Gateelektrode 128 kann aus Polysilizium, Polysilizium-Germanium, Nickelsilizium oder einem anderen Metall, einer Metalllegierung oder dergleichen ausgebildet sein.

[0037] Wie in Fig. 1 gezeigt ist, können vier Isolierbereiche vorliegen, nämlich ein erster Isolierbereich 112, ein zweiter Isolierbereich 114, ein dritter Isolierbereich 116 und ein vierter Isolierbereich 118. Die Isolierbereiche werden dazu verwendet, um aktive Bereiche zu isolieren, so dass Leckströme gehindert werden, zwischen den aneinandergrenzenden aktiven Bereichen zu fließen. Der Isolierbereich (z. B. der erste Isolierbereich 112) kann auf verschiedene Weise (z. B. thermisch gewachsen, abgeschieden) und aus verschiedenen Materialien (z. B. Siliziumoxid, Siliziumnitrid) ausgebildet sein. Bei dieser Ausführungsform werden die Isolierbereiche durch eine Shallow-Trench-Isolation (STI)-Technik hergestellt.

[0038] Fig. 2 zeigt zwei Graphen, welche die Unterschiede in der Dotierungsdichte zwischen einem herkömmlichen MOS-Transistor mit einem 5 V p-Wall und einem MOS-Transistor mit drei überlagerten p-Wällen, wie er in Fig. 1 gezeigt ist, veranschaulichen. Die horizontale Achse der Fig. 2 repräsentiert den Abstand des Source-Bereichs (erster N+-Bereich 122) zu dem Drain-Bereich (zweiter N+-Bereich 124) des MOS-Transistors 100, der in Fig. 1 gezeigt ist. Mit anderen Worten repräsentiert der Anfangspunkt

der horizontalen Achse den p-Wall-Bereich, der an die Source (den ersten N+-Bereich 122, der in Fig. 1 gezeigt ist) angrenzt. Der Endpunkt der horizontalen Achse repräsentiert den an den Drain (den zweiten N+-Bereich 124, der in Fig. 1 gezeigt ist) angrenzenden Substratbereich. Die vertikale Achse der Fig. 3 repräsentiert die Dotierungsdichte.

[0039] Ein Graph 202 und ein Graph 204 veranschaulichen den Unterschied der Dotierungsdichte zwischen einem herkömmlichen MOS-Transistor mit einem 5 V p-Wall und dem MOS-Transistor mit überlagerten p-Wällen. Wie in Fig. 2 gezeigt ist, ist in den Bereichen, welche die überlagerten p-Wälle aufweisen, die Dotierungsdichte des MOS-Transistors 100, der in Fig. 1 gezeigt ist, höher als diejenige des herkömmlichen MOS-Transistors. Auf der anderen Seite ist in dem Bereich ohne einen 5 V p-Wall, etwa in den Substratbereichen, die an den Drain des MOS-Transistors 100 angrenzen, die Dotierungsdichte des in Fig. 1 gezeigten MOS-Transistors 100 geringer als die des herkömmlichen MOS-Transistors, weil ein 5 V p-Wall unter dem Drain des herkömmlichen MOS-Transistors ausgebildet werden kann.

[0040] Gemäß einer Ausführungsform ist die Dotierungsdichte des in Fig. 2 gezeigten, herkömmlichen MOS-Transistors ungefähr einheitlich. Die Dotierdichte bewegt sich in einem Bereich zwischen ungefähr 8 ×  $10^{16}$ /cm<sup>3</sup> und ungefähr 6 ×  $10^{17}$ /cm<sup>3</sup>. Im Gegensatz dazu ist die Dotierungsdichte des in Fig. 1 gezeigten MOS-Transistors 100 eine Kurve, welche in Bereichen, die an die Source angrenzen, eine höhere Dotierungsdichte, und in Bereichen, die an den Drain angrenzen, eine geringere Dotierungsdichte aufweist. Gemäß einer Ausführungsform beträgt die Dotierungsdichte des in Fig. 1 gezeigten MOS-Transistors zwischen ungefähr 8 × 10<sup>15</sup>/cm³ und ungefähr 8 × 10<sup>17</sup>/cm<sup>3</sup>. Es sollte festgehalten werden, dass der zweite P-Typwall 106 eine geringere Dotierungskonzentration im Vergleich zu dem ersten P-Typwall 104 aufweist, weil der zweite P-Typwall 106 mittels eines 1,8 V CMOS-Prozesses und der erste P-Typwall 104 mithilfe eines 5 V CMOS-Prozesses ausgebildet worden ist.

**[0041] Fig.** 2 zeigt, dass der MOS-Transistor mit überlagerten p-Wällen eine höhere Dotierungsdichte in Bereichen erreichen kann, die an die Source angrenzen. Eine solche höhere Dotierungsdichte hilft dabei, das Durchlassfenster des MOS-Transistors **100** zu verbessern. Auf diese Weise kann eine kürzere Kanallänge angewendet werden, um den Pitch- sowie den On-Widerstand des MOS-Transistors **100** weiter zu verringern.

[0042] Darüber hinaus veranschaulicht die Fig. 2, dass die Dotierungsdichte des Aufbaubereichs zwischen den P-Typwällen und zu dem zweiten N+-Bereich 124 des MOS-Transistors 100 geringer ist als

die des herkömmlichen MOS-Transistors. Die geringere Dotierungsdichte in dem Aufbaubereich hilft dabei, den Aufbauwiderstand des MOS-Transistors 100 zu verringern. Der verringerte Aufbauwiderstand hilft dabei, zu vermeiden, dass der schädliche Aufbautransistor falsch eingeschaltet wird. Daraus resultiert, dass die Zuverlässigkeit des MOS-Transistors 100, wie die Safe Operating Area (SOA) verbessert werden können.

[0043] Fig. 3 veranschaulicht eine vereinfachte Querschnittsansicht des MOS-Transistors mit überlagerten Wällen gemäß einer weiteren Ausführungsform. Die Querschnittsansicht gemäß Fig. 3 ist ähnlich zu der Querschnittsansicht gemäß Fig. 4, mit der Ausnahme, dass der MOS-Transistor 300, der in Fig. 3 gezeigt ist, ein p-Typ-MOS-Transistor anstelle eines n-Typ-MOS-Transistors 100, wie er in Fig. 1 gezeigt ist, ist. Daher wurden die p-Wälle, die in Fig. 1 gezeigt sind, durch ihre entsprechenden n-Wälle 304 bzw. 306 ersetzt.

[0044] Die Source- und Drain-Bereiche gemäß Fig. 3 werden durch P+-Bereiche 322 bzw. 324 ersetzt. Genauso werden die Aufbaukontakte 332 durch die Verwendung von N+-Bereichen realisiert. Die genaue Struktur und der Herstellungsprozess jedes in Fig. 3 gezeigten Elementes sind ähnlich zu denen gemäß Fig. 1, so dass dies hier nicht näher diskutiert wird. Es sollte festgehalten werden, dass in Fig. 3 der 5 V n-Wall größer ist als sein entsprechender Teil, der in Fig. 1 gezeigt ist. Wie in Fig. 3 gezeigt ist, ist der 5 V n-Wall sowohl unterhalb des Source-Bereiches (P+-Bereich 322) als auch unterhalb des Drain-Bereiches (P+-Bereich 324) ausgebildet. Daher ist die Dotierungsdichte des in Fig. 3 gezeigten MOS-Transistors 300 ähnlich zu der des herkömmlichen MOS-Transistors, mit Ausnahme des Bereichs **306**.

[0045] Fig. 4 veranschaulicht zwei Graphen, die die Unterschiede in der Dotierungsdichte zwischen einem herkömmlichen MOS-Transistor mit einem 5 V p-Wall und dem in Fig. 3 gezeigten MOS-Transistor veranschaulichen. Die horizontale Achse von Fig. 4 repräsentiert den Abstand des Source-Bereiches (P+-Bereich 322) zu dem Drain-Bereich (P+-Bereich 324) des in Fig. 3 gezeigten MOS-Transistors 300. Die vertikale Achse von Fig. 3 repräsentiert die Dotierungsdichte.

[0046] Ein Graph 402 und ein Graph 404 veranschaulichen den Unterschied in der Dotierungsdichte zwischen einem herkömmlichen MOS-Transistor mit einem 5 V p-Wall und dem MOS-Transistor 300 mit überlagerten n-Wällen. Wie in Fig. 4 gezeigt ist, ist in den Bereichen, die die überlagerten n-Wälle aufweisen, die Dotierungsdichte des in Fig. 3 gezeigten MOS-Transistors 300 höher als die des herkömmlichen MOS-Transistors. Andererseits weist der übrige

Bereich des in **Fig.** 3 gezeigten MOS-Transistors **300** eine ähnliche Dotierungsdichte wie der herkömmliche MOS-Transistor auf.

[0047] Gemäß einer Ausführungsform ist die Dotierungsdichte eines herkömmlichen, in Fig. 4 gezeigten MOS-Transistors ungefähr gleichbleibend. Die Dotierungsdichte bewegt sich in einem Bereich zwischen ungefähr 1 × 10¹7/cm³ und ungefähr 6 × 10¹7/cm³. Im Gegensatz dazu schwankt die Dotierungsdichte des in Fig. 3 gezeigten MOS-Transistors 300 in einem größeren Bereich, welcher eine höhere Dotierungsdichte in dem Bereich, der an die Source (P+-Bereich 322) angrenzt, aufweist. Gemäß einer Ausführungsform befindet sich die Dotierungsdichte des in Fig. 3 gezeigten MOS-Transistors 300 in einem Bereich zwischen ungefähr 1 × 10¹7/cm³ und ungefähr 8 × 10¹7/cm³.

[0048] Fig. 4 zeigt, dass der MOS-Transistor mit den überlagerten p-Wällen eine höhere Dotierungsdichte in den Bereichen, die an die Source (P+-Bereich 322) angrenzen, erreichen kann. Solch eine höhere Dotierungsdichte hilft dabei, das Durchschlagsfenster der MOS-Transistoren 300 zu verbessern. Dabei kann eine kürzere Kanallänge angewendet werden, um den Pitch- und den On-Widerstand des MOS-Transistors 300 weiter zu verringern.

[0049] Fig. 5 veranschaulicht eine vereinfachte Draufsicht einer MOS-Transistoranordnung gemäß einer Ausführungsform. Die MOS-Transistoranordnung kann aus N-TypTransistoren ausgebildet sein. Die MOS-Transistoranordnung kann zwei MOS-Transistoren aufweisen, von denen jeder zwei überlagerte p-Wälle (nicht dargestellt, jedoch in Fig. 1 gezeigt) aufweist. Die MOS-Transistoren teilen sich einen Drain-Bereich, nämlich einen N+-Bereich 514. Der erste MOS-Transistor umfasst eine Gateelektrode 512, einen Source-Bereich, der aus einer Vielzahl N+-Bereiche, wie 502, 506 und 510 gebildet ist, und einen Aufbaukontakt, der durch eine Vielzahl P+-Bereiche, wie 504 und 508, gebildet ist.

[0050] Ebenso umfasst der zweite MOS-Transistor eine Gateelektrode 516 und einen Sourcebereich, der aus einer Vielzahl N+-Bereiche, wie 522, 526 und 530 gebildet ist. Der zweite MOS-Transistor weist weiterhin einen Aufbaukontakt auf, der aus einer Vielzahl P+-Bereiche, wie 524 und 528, gebildet ist. Es sollte festgehalten werden, dass die N+-Bereiche (z. B. der N+-Bereich 502) und die P+-Bereiche (z. B. der P+-Bereich 504) nicht maßstabsgetreu gezeichnet sind. Gemäß einer Ausführungsform beträgt das tatsächliche Verhältnis zwischen dem N+-Bereich (beispielsweise dem N+-Bereich 502) und einem angrenzenden P+-Bereich (beispielsweise dem N+-Bereich 502) zwischen ungefähr 10:1 und ungefähr 2:1.

[0051] Die MOS-Transistoranordnung weist weiterhin einen P+-Aufnahmering 532 auf, der den ersten MOS-Transistor und den zweiten MOS-Transistor umgibt. Der P+-Aufnahmering 532 kann mit den Sources des MOS-Transistoraufbaus verbunden werden. Der P+-Aufnahmering 532 hilft dabei, den Aufbaueffekt des MOS-Transistoraufbaus zu verringern.

[0052] Im Vergleich zu den traditionellen MOS-Transistoren zeigt die Draufsicht gemäß Fig. 5, dass die Source-Bereiche (z. B. die N+-Bereiche 502, 506 und 510) und die Aufbaukontakte (z. B. die P+-Bereiche 504 und 508) abwechselnd ausgebildet sind. Daraus resultiert, dass die Aufbaukontakte (z. B. der P+-Bereich 504) wesentlich näher an den Source-Bereichen (z. B. der N+-Bereich 502) angeordnet sind. Die Nähe zwischen den Aufbaukontakten und den Source-Bereichen hilft dabei, die Stromableiteffizienz des Aufbauwiderstand verringert werden kann. Darüber hinaus hilft die Maßnahme, die Source-Bereiche und die Aufbaukontakte abwechselnd auszubilden, dabei den Pitch des MOS-Transistors zu verringern.

[0053] Fig. 6 veranschaulicht eine Querschnittsansicht der in Fig. 5 gemäß einer Ausführungsform gezeigten MOS-Transistoranordnung. Der Querschnitt verläuft entlang der in Fig. 5 gezeigten Linie A-A'. Der erste MOS-Transistor und der zweite MOS-Transistor teilen sich denselben Drain (N+-Bereich 514). Zusätzlich sind der erste MOS-Transistor und der zweite MOS-Transistor symmetrisch zu dem Drain (N+-Bereich 514) angeordnet. Jeder MOS-Transistor weist eine zu der in Fig. 1 gezeigten ähnliche Struktur auf und wird somit an dieser Stelle nicht diskutiert, um Wiederholungen zu vermeiden.

[0054] Fig. 7 veranschaulicht eine andere Querschnittsansicht der in Fig. 5 gemäß einer Ausführungsform gezeigten MOS-Transistoranordnung. Die Querschnittsansicht verläuft entlang der in Fig. 5 gezeigten Linie W-W'. Die Querschnittsansicht gemäß Fig. 7 ähnelt der gemäß Fig. 6, mit der Ausnahme, dass die N+-Bereiche 502 und 522 durch P+-Bereiche 508 und 528 ersetzt sind. Wie zuvor mit Bezug auf Fig. 5 bereits beschrieben wurde, wirken die P+-Bereiche 508 und 528 als Aufbaukontakte. Indem Aufbaukontakte angrenzend an die N+-Bereiche 502 und 522 (jeweils nicht dargestellt, jedoch in Fig. 5 gezeigt) angeordnet werden, kann im Ergebnis die Stromableiteffizienz des Aufbaus verbessert werden.

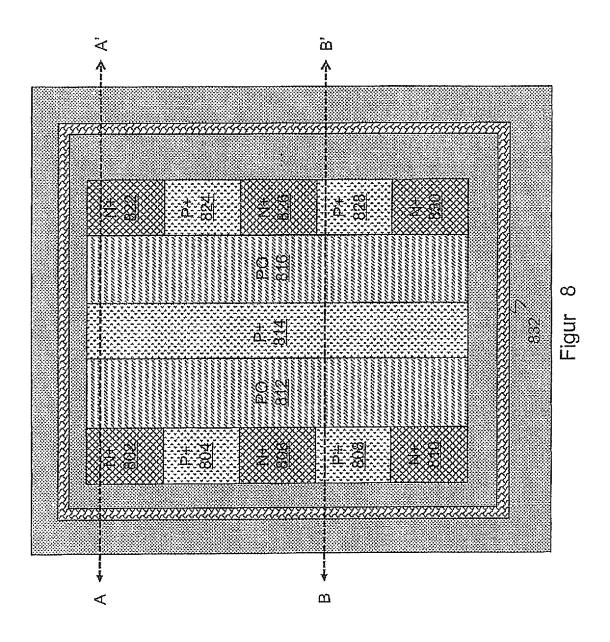

**[0055] Fig.** 8 veranschaulicht eine vereinfachte Draufsicht der MOS-Transistoranordnung gemäß einer anderen Ausführungsform. Die in **Fig.** 8 gezeigte MOS-Transistoranordnung kann aus P-Typtransistoren ausgebildet sein. Die MOS-Transistoranordnung kann zwei MOS-Transistoren aufweisen, von denen

jeder zwei überlagerte n-Wälle (nicht dargestellt, jedoch in

**[0056] Fig.** 3 gezeigt) aufweist. Die MOS-Transistoren teilen sich einen Drain-Bereich, nämlich einen P+Bereich **814**.

[0057] Der erste MOS-Transistor umfasst eine Gateelektrode 812, einen Source-Bereich, der aus einer Vielzahl P+-Bereiche, wie 804 und 808 ausgebildet ist, und einen Aufbaukontakt, der aus einer Vielzahl N+-Bereiche wie 802, 806 und 807, ausgebildet ist. Ebenso umfasst der zweite MOS-Transistor eine Gateelektrode 816, einen Source-Bereich, der aus einer Vielzahl P+-Bereiche, wie 824 und 828, ausgebildet ist, und einen Aufbaukontakt, der aus einer Vielzahl N+-Bereiche, wie 822, 826 und 830 ausgebildet ist. Es sollte festgehalten werden, dass die N+-Bereiche (z. B. der N+-Bereich 802) und die P+-Bereiche (z. B. der P+-Bereich 804) nicht maßstabsgetreu gezeichnet sind. Das tatsächliche Verhältnis der Abmessungen zwischen einem N+-Bereich und seinem angrenzenden P+-Bereich beträgt zwischen ungefähr 1:2 und ungefähr 1:10.

**[0058]** Die MOS-Transistoranordnung weist weiterhin einen N+-Aufnahmering **832** auf, der den ersten MOS-Transistor und den zweiten MOS-Transistor umgibt. Der N+-Aufnahmering **832** kann mit einem Hochspannungspotential (nicht dargestellt) der MOS-Transistoranordnung verbunden sein. Der N+-Aufnahmering **832** hilft dabei, den Aufbaueffekt der MOS-Transistoranordnung zu verringern.

[0059] Ähnlich zu der in Fig. 8 gezeigten Struktur sind die Source-Bereiche (z. B. die P+-Bereiche 804 und 808) und die Aufbaukontakte (z. B. die N+-Bereiche 802, 806 und 808) abwechselnd ausgebildet. Daraus resultiert, dass die Aufbaukontakte wesentlich näher an den Source-Bereichen angeordnet sind. Die Nähe zwischen den Aufbaukontakten und den Source-Bereichen hilft dabei, die Stromableiteffizienz des Aufbaus zu verbessern. Daraus resultiert, dass der Aufbauwiderstand verringert werden kann. Zusätzlich hilft der Umstand, dass die Source-Bereiche und die Aufbaukontakte abwechselnd ausgebildet sind, dabei, den Pitch des MOS-Transistors zu verringern.

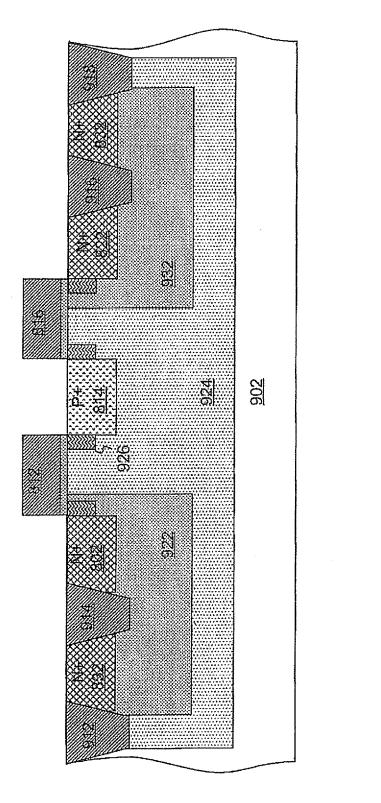

[0060] Fig. 9 veranschaulicht eine Querschnittsansicht der in Fig. 8 gemäß einer Ausführungsform gezeigten MOS-Transistoranordnung. Die Querschnittsansicht verläuft entlang der in Fig. 8 gezeigten Linie A-A'. Der erste MOS-Transistor und der zweite MOS-Transistor teilen sich denselben Drain. Zusätzlich sind der erste MOS-Transistor und der zweite MOS-Transistor symmetrisch in Bezug auf den Drain (P+-Bereich 814) angeordnet. Jeder MOS-Transistor weist eine zu der in Fig. 3 gezeigten ähn-

liche Struktur auf und wird daher nicht weiter diskutiert, um Wiederholungen zu vermeiden.

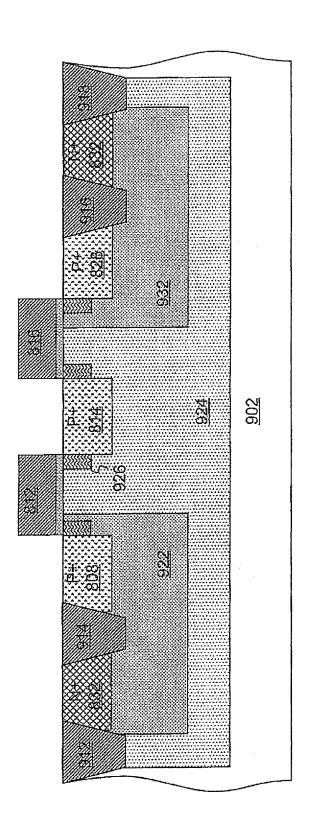

[0061] Fig. 10 veranschaulicht eine weitere Querschnittsansicht der in Fig. 8 gemäß einer Ausführungsform gezeigten MOS-Transistoranordnung. Die Querschnittsansicht verläuft entlang der in Fig. 8 gezeigten Linie B-B'. Die Querschnittsansicht von Fig. 10 ähnelt der von Fig. 9, mit der Ausnahme, dass die N+-Bereiche 802 und 822 sich durch P+-Bereich 808 und 828 ersetzt sind, und werden daher an dieser Stelle nicht weiter diskutiert.

[0062] Obwohl Ausführungsformen der vorliegenden Offenbarung und deren Vorteile im Detail beschrieben worden sind, sollte verstanden werden, dass verschiedene Änderungen, Ersetzungen und Abwandlungen davon durchgeführt werden können, ohne dass dadurch vom Gegenstand der Offenbarung, wie er in den anhängenden Ansprüchen angegeben ist, abgewichen wird.

#### **Patentansprüche**

#### 1. Transistor, der aufweist:

einen ersten Transistor, der ein erstes Gate, eine erste Source, einen ersten Drain und einen ersten Aufbaukontakt aufweist, wobei:

der erste Aufbaukontakt und die erste Source in der Draufsicht abwechselnd ausgebildet sind; und die erste Source in einem ersten gestapelten Wall-

abschnitt ausgebildet ist, wobei der erste gestapelte Wallabschnitt aufweist:

einen ersten Bereich mit einer ersten Leitfähigkeit, der über einem Substrat mit einer ersten Leitfähigkeit ausgebildet ist; und

einen zweiten Bereich mit der ersten Leitfähigkeit, der in den ersten Bereich eingebettet ist;

einen zweiten Transistor, der ein zweites Gate, eine zweite Source, einen zweiten Drain und einen zweiten Aufbaukontakt aufweist, wobei der erste Drain und der zweite Drain miteinander verbunden sind, und wobei:

der zweite Aufbaukontakt und die zweite Source in der Draufsicht abwechselnd ausgebildet sind;

die zweite Source in einem zweiten gestapelten Wallabschnitt ausgebildet ist, wobei der zweite gestapelte Wallabschnitt aufweist:

einen dritten Bereich mit der ersten Leitfähigkeit, der über dem Substrat ausgebildet ist; und

einen vierten Bereich mit der ersten Leitfähigkeit, der in dem dritten Bereich eingebettet ist; und

einen Aufbauaufnahmering, der den ersten Transistor und den zweiten Transistor umgibt,

**dadurch gekennzeichnet,** dass der Transistor weiterhin die folgenden Merkmale aufweist:

einen ersten leicht dotierten Source/Drain-Bereich mit der ersten Leitfähigkeit, der angrenzend an die erste Source in dem zweiten Bereich angeordnet ist; und

### DE 10 2012 108 142 B4 2017.01.26

einen zweiten leicht dotierten Drain/Source-Bereich mit der ersten Leitfähigkeit, der angrenzend an den ersten Drain in dem Substrat ausgebildet ist, wobei der zweite leicht dotierte Drain/Source-Bereich unter dem ersten Gate angeordnet ist.

- 2. Transistor nach Anspruch 1, der weiterhin aufweist: einen Aufbauaufnahmering mit der ersten Leitfähigkeit, der den ersten Transistor und den zweiten Transistor in dem Substrat umgibt.

- 3. Transistor nach Anspruch 1 oder 2, bei dem der zweite Bereich eine höhere Dotierungsdichte als der erste Bereich aufweist.

Es folgen 10 Seiten Zeichnungen

## Anhängende Zeichnungen

Figur 2

Figur 4

Figur 6

Figur 7

Figur 9

Figur 10