(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4617941号

(P4617941)

(45) 発行日 平成23年1月26日(2011.1.26)

(24) 登録日 平成22年11月5日(2010.11.5)

|                     |             |

|---------------------|-------------|

| (51) Int.Cl.        | F 1         |

| H05K 3/46 (2006.01) | H05K 3/46 G |

| H05K 3/00 (2006.01) | H05K 3/46 N |

|                     | H05K 3/46 X |

|                     | H05K 3/00 X |

請求項の数 6 (全 10 頁)

(21) 出願番号 特願2005-76815 (P2005-76815)

(22) 出願日 平成17年3月17日 (2005.3.17)

(65) 公開番号 特開2006-261390 (P2006-261390A)

(43) 公開日 平成18年9月28日 (2006.9.28)

審査請求日 平成20年3月13日 (2008.3.13)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100109667

弁理士 内藤 浩樹

(74) 代理人 100109151

弁理士 永野 大介

(74) 代理人 100120156

弁理士 藤井 兼太郎

(72) 発明者 西井 利浩

大阪府門真市大字門真1006番地 松下

電子部品株式会社内

審査官 川上 佳

最終頁に続く

(54) 【発明の名称】回路形成基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

(1) 金属箔、もしくは支持体に張り付けられた金属箔、もしくは支持体に張り付けられ回路パターンを形成された金属箔

(2) 層間接続手段を備えたBステージ状態基板材料

(3) 回路、金属箔、層間接続手段のうち一つ以上を備えたBステージ状態基板材料

(4) 回路もしくは金属箔を備えたCステージ状態基板材料もしくは回路もしくは金属箔と層間接続手段を備えたCステージ状態基板材料

のうち、

少なくとも1種以上の前記Bステージ状態基板材料及び2種以上の前記金属箔もしくは前記基板材料を積層物として積層し仮止めする積層工程と、

前記積層物の表層に回路を形成し多層の回路形成基板とする工程とを備え、

前記回路形成基板は複数の個別回路形成基板で構成される集合回路形成基板が複数配置されたものであり、

前記積層物を積層し仮止めする積層工程は、

1枚の前記Bステージ状態基板材料に対して2枚の前記Cステージ状態基板材料を互いに当接して積層し、

前記集合回路形成基板のいくつかは2枚の前記Cステージ状態基板材料をまたがる形で配置されることを特徴とする回路形成基板の製造方法。

## 【請求項 2】

積層工程の前に、前記積層工程において積層する2枚以上のCステージ状態基板材料が当接する部分を所望寸法まで切断する切断工程を備えることを特徴とする請求項1に記載の回路形成基板の製造方法。

**【請求項3】**

前記当接する部位は少なくとも1つの集合回路形成基板内の互いに隣接する個別回路形成基板の間に位置することを特徴とする請求項1に記載の回路形成基板の製造方法。

**【請求項4】**

Cステージ状態基板材料は互いに当接する部分は、嵌合する形状に形成されていることを特徴とする請求項1に記載の回路形成基板の製造方法。

**【請求項5】**

切断は、ダイシング法で行うことを特徴とする請求項2に記載の回路形成基板の製造方法。

**【請求項6】**

Cステージ状態基板材料は表面に回路および導電ペーストで形成された層間接続部を備え、多層の回路形成基板の表層はレーザービアを備えることを特徴とする請求項3または請求項4に記載の回路形成基板の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、各種電子機器に利用される回路形成基板の製造方法および回路形成基板の製造用材料に関するものである。

**【背景技術】**

**【0002】**

近年の電子機器の小型化・高密度化に伴って、電子部品を搭載する回路形成基板も従来の片面基板から両面、多層基板の採用が進み、より多くの回路および部品を基板上に集積可能な高密度基板が開発されている。

**【0003】**

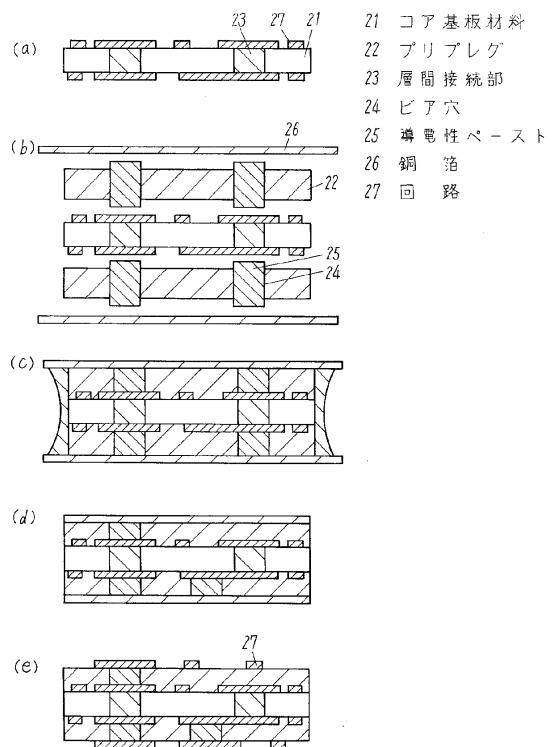

従来例について図5を用いて以下に説明する。

**【0004】**

図5(a)に示すコア基板材料21は表面に回路27を形成した回路形成基板である。導電ペーストを層間接続部23として備える両面板として図示しているが、多層板の使用も可能であるし、層間接続部23には導電ペースト以外にもめっき、半田等多様な方法が使用できる。

**【0005】**

次に、図5(b)に示すようにコア基板材料21の両側にビア穴24に充填された導電性ペースト25を備えるBステージ基板材料としてのプリプレグ22および銅箔26を必要に応じて位置決めして配置する。

**【0006】**

その際にはプリプレグ22が半硬化の樹脂分を含むためにヒータツール等で銅箔26とプリプレグ22もしくはプリプレグ22とコア基板材料21を部分的に仮圧着することで以降のハンドリング時の位置ずれを防止することもできる。

**【0007】**

次に、熱プレス装置(図示せず)により加熱加圧を加えて図5(c)に示すようにプリプレグ22を硬化させ一体化する。その際に導電性ペースト25も硬化および圧縮を受けて導電性を発現し層間の電気的接続を形成する。

**【0008】**

次に端面の余分な部分を切断して図5(d)に示すような4層板を得て、表面の銅箔26をエッティング加工することで回路27を形成して、図5(e)に示すような4層の回路形成基板を得る。

10

20

30

40

50

**【0009】**

必要であれば図5(e)の回路形成基板の表面に半田付け用のソルダーレジストや回路27表面への金めっきもしくはフラックス処理あるいは半田レベラー等の表面処理を施し、金型やルータ加工等で所望のシートサイズに切断して電気機器の組み立て工程等に回路形成基板として供給される。

**【0010】**

なお、この出願の発明に関連する先行技術文献情報としては、例えば、特許文献1が知られている。

**【特許文献1】特開平6-268345号公報****【発明の開示】**

10

**【発明が解決しようとする課題】****【0011】**

しかしながら、上記のような回路形成基板の製造法では、プリプレグ22のサイズを大きくする場合に制限が生じる。

**【0012】**

すなわち、プリプレグ22には未硬化の導電性ペースト25が配設されているために治具等に接触させることができない。接触した場合には導電性ペースト25が周囲に拡がってしまい回路形成基板として回路間の電気的ショートの要因になったり、層間接続の信頼性が失われる等の問題が起こる。

**【0013】**

20

導電性ペースト25にダメージを加えないためには中空の支持治具にて保管し、積層工程でプリプレグ22をハンドリングする際にもプリプレグ22の端面しか掴むことができない。

**【0014】**

ゆえに、プリプレグ22のサイズを大きくするとともに積層工程の困難度は高まり、回路形成基板の製造として品質信頼性も不確実なものとなってしまう。

**【0015】**

また、プリプレグ22に配設した導電性ペースト25の位置がばらつくと回路形成基板の設計ルールが微細になった場合はコア基板材料21上の回路27との位置決めが困難になってしまふが、プリプレグ22のサイズが大きくなるに従い前記位置ばらつきは大きくなるものである。

30

**【0016】**

しかしながら、回路形成基板の製造コストを低減するためには、プリプレグ22のサイズすなわち、製造上のワークサイズを大きくすることが効率の面から有効であるため、ワークサイズの大きな回路形成基板を安定に製造する方法が所望されていた。

**【課題を解決するための手段】****【0017】**

本発明の回路形成基板の製造方法においては、積層工程において同一のBステージ状態基板材料に対して2枚以上のCステージ状態基板材料を特定部位で互いに当接して積層する構成としたものである。

40

**【0018】**

この本発明によれば、製造上のワークサイズを大きくしても安定かつ高品質な回路形成基板の製造が行えるものである。

**【0019】**

本発明の請求項1に記載の発明は、

(1)金属箔、もしくは支持体に張り付けられた金属箔、もしくは支持体に張り付けられ回路パターンを形成された金属箔

(2)層間接続手段を備えたBステージ状態基板材料

(3)回路、金属箔、層間接続手段のうち一つ以上を備えたBステージ状態基板材料

(4)回路もしくは金属箔を備えたCステージ状態基板材料もしくは回路もしくは金属箔

50

と層間接続手段を備えた C ステージ状態基板材料

のうち、

少なくとも 1 種以上の前記 B ステージ状態基板材料及び 2 種以上の前記金属箔もしくは前記基板材料を積層物として積層し仮止めする積層工程と、

前記積層物の表層に回路を形成し多層の回路形成基板とする工程とを備え、

前記回路形成基板は複数の個別回路形成基板で構成される集合回路形成基板が複数配置されたものであり、

前記積層物を積層し仮止めする積層工程は、1 枚の前記 B ステージ状態基板材料に対して 2 枚の前記 C ステージ状態基板材料を互いに当接して積層し、

前記集合回路形成基板のいくつかは 2 枚の前記 C ステージ状態基板材料をまたがる形で配置されることを特徴とする回路形成基板の製造方法としたものであり、ワークサイズの大きな回路形成基板の製造が可能となり、また、積層後のワークサイズでの有効範囲すなわち回路形成基板としての使用可能範囲が増加することにより、集合回路形成基板の取り数を増加させ、効率的かつ低コストの回路形成基板の製造が可能となる等の効果を有する。

さらに、使用する基板材料の歩留まりを向上させ、個別回路形成基板の生産性を高める等の効果を有する。

#### 【 0 0 2 0 】

本発明の請求項 2 に記載の発明は、積層工程の前に、前記積層工程において積層する 2 枚以上の C ステージ状態基板材料について C ステージ状態基板材料が当接する部分を所望寸法まで切断する切断工程を備えることを特徴とする請求項 1 に記載の回路形成基板の製造方法としたものであり、積層後のワークサイズでの有効範囲すなわち回路形成基板としての使用可能範囲が増加し効率的かつ低コストの回路形成基板の製造が可能となる等の効果を有する。

#### 【 0 0 2 2 】

本発明の請求項 3 に記載の発明は、前記当接する部位は少なくとも 1 つの集合回路形成基板内の互いに隣接する個別回路形成基板の間に位置することを特徴とする請求項 1 に記載の回路形成基板の製造方法としたものであり、積層後のワークサイズでの有効範囲すなわち回路形成基板としての使用可能範囲が増加することにより、個別回路形成基板の取り数を増加させ、効率的かつ低コストの回路形成基板の製造が可能となる等の効果を有する。

#### 【 0 0 2 3 】

本発明の請求項 4 に記載の発明は、C ステージ状態基板材料は互いに当接する部分は、嵌合する形状に形成されていることを特徴とする請求項 1 に記載の回路形成基板の製造方法としたものであり、この構成により集合回路形成基板の強度を高めることができるという効果を有する。

#### 【 0 0 2 4 】

本発明の請求項 5 に記載の発明は、切断は、ダイシング法で行うこと特徴とする請求項 2 に記載の回路形成基板の製造方法としたものであり、ダイシング法を採用することにより、2 枚の C ステージ状態基板材料の間隔を  $100 \mu m$  にすることも可能であり、C ステージ状態基板材料は互いに当接する部分を高精度で特定することができるという効果を有する。

#### 【 0 0 2 5 】

本発明の請求項 6 に記載の発明は、C ステージ状態基板材料は表面に回路および導電ペーストで形成された層間接続部を備え、多層の回路形成基板の表層はレーザービアを備えることを特徴とする請求項 3 または請求項 4 に記載の回路形成基板の製造方法としたものであり、ワークサイズが大きい場合においても多層の回路形成基板を容易に製造することができる、製造コストの低減を図ることができるという効果を有する。

#### 【 発明の効果 】

#### 【 0 0 2 6 】

この本発明によれば、回路形成基板の製造時のワークサイズを大きくした場合にも基板

10

20

30

40

50

材料をハンドリングを安定させ、従来の製造方法に比較してより薄くサイズの大きな基板材料を用いて回路形成基板の製造が可能になるものである。

**【0027】**

また積層後のワークサイズでの回路形成基板としての使用可能範囲が増加することにより、個別回路形成基板の取り数を増加させ、効率的かつ低コストの回路形成基板の製造が可能となる等の効果を有する。

**【0028】**

特に、基板材料としてのプリプレグの補強材にガラス等の纖維を用いた織布を用いた場合には、織布の持つ寸法安定性などの利点を生かしながら、織布の持つプリプレグ状態での剛性の不足を補い積層作業を安定化できるという格別の効果を発揮するものである。

10

**【0029】**

以上の結果として、導電性ペースト等の層間接続手段を用いた層間の電気的接続の信頼性をも大幅に向上させながら、高品質の高密度回路形成基板を提供できるものである。

**【発明を実施するための最良の形態】**

**【0030】**

(実施の形態)

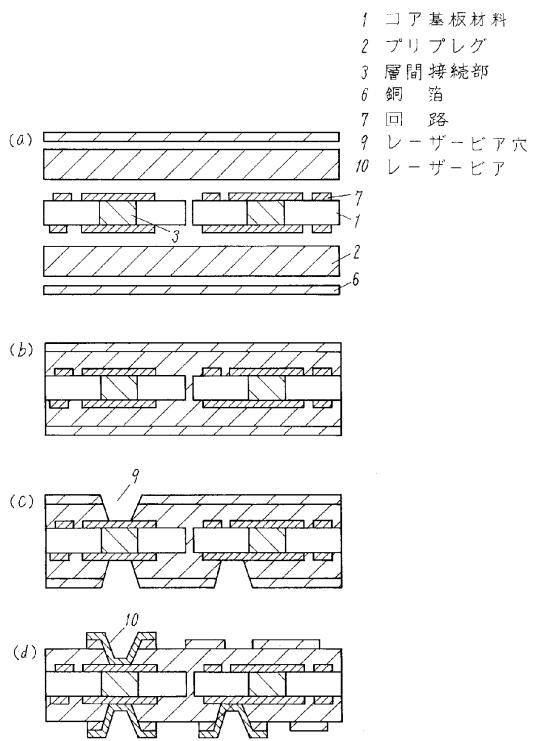

図1(a)～(d)は本発明の実施の形態における回路形成基板の製造方法を示す工程断面図である。

**【0031】**

図1(a)に示すCステージ状態基板材料としてのコア基板材料1は、表面に回路7および内部に層間接続部3を形成した回路形成基板である。

20

**【0032】**

コア基板材料1は、導電ペーストを層間接続手段として備える両面板として図示しているが、多層板の使用も可能である。

**【0033】**

従来例で述べたように、大きなワークサイズでコア基板材料1を製作することが難しい場合に、製造することが容易なワークサイズでコア回路形成基板1を製造する。特にコア基板材料1の厚みが薄い場合にワークサイズを大きくすることが難しくなることが多い。

**【0034】**

上記コア基板材料1の両面を近接した状態で2枚並べ、その上下をBステージ状態基板材料としてのプリプレグ2で挟み込み、さらに金属箔としての銅箔6で挟み込む状態に積層する。

30

**【0035】**

その際に必要に応じてヒータツール(図示せず)等で仮止めをすることも有効である。

**【0036】**

本実施の形態ではプリプレグ2に層間接続手段等を設けていないので相互の位置決めは概略で良いが、後の工程で必要な場合にはプリプレグ2に位置決めマーク等を配設し相互の位置決めをすることも有効である。また、プリプレグ2に導電性ペースト等による層間接続手段を形成した場合には相互の位置決めが重要になる。

**【0037】**

40

次に図1(a)に示すように積層した状態で加熱加圧し図1(b)に示すような一体成型された状態の積層物を得る。

**【0038】**

次に図1(c)に示すように前記積層物にレーザー加工法等によりレーザービア穴9を加工する。

**【0039】**

次に銅めっき、パターン形成等の工程を実施し、図1(d)に示すようなレーザービア10を形成した多層の回路形成基板を得る。

**【0040】**

図1(c)から図1(d)までの工程はプリプレグビルドアップ法と呼ばれる工法で、

50

ワークサイズが大きい場合にも比較的適用し易い工法であり、ワークサイズが大きい方が勿論単位面積あたりのコストは低減できる。

#### 【0041】

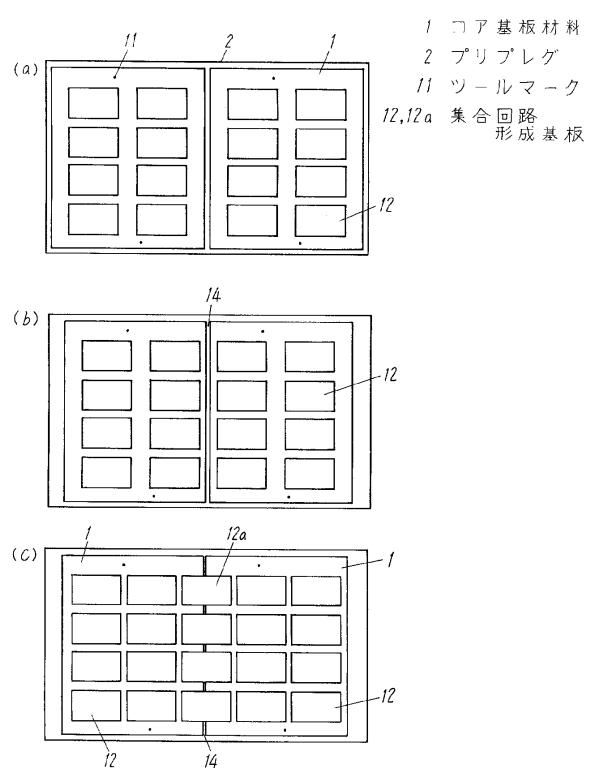

一般に製品として利用される回路形成基板は製造時のワークサイズより小さく、図2(a)に示すように、複数の集合回路形成基板12を一面に備えたワークサイズの状態から、金型打ち抜きやルータ加工等で切り出して個々の集合回路形成基板12を得る場合が多い。また、集合回路形成基板12も複数の個別回路形成基板13(後述)から構成されることが一般的である。

#### 【0042】

その際に、ワークサイズと集合回路形成基板のサイズ(以下製品サイズと記載)の整合性が製品コストに大きく影響する。

10

#### 【0043】

すなわち、図2(a)の左右方向の大きさが500mmであったときに、製品サイズが100mmであれば、図2(a)に回路形成基板を上方より見た図を示すように、ツールマーク11等の有効でない部分を除いても左右方向に2枚の集合回路形成基板を並べて配置した際に効率良く設計が出来る。

#### 【0044】

しかしながら、製品サイズが150mmの場合や集合回路形成基板を少しでも多く配置したい場合には2枚のコア基板材料1をまたがる形で集合回路形成基板を配置せざるを得ない。

20

#### 【0045】

そのような配置を実現するために、あらかじめ2枚のコア形成基板材料1の当接する辺を制度良く切断しておき、2枚のコア形成基板材料1の間隔を極小にすることが有効である。

#### 【0046】

図2(b)に積層工程前にコア形成基板材料1を切断した例を示す。2枚のコア形成基板材料1が互いに当接する部位は、集合回路形成基板12を互いに隣接する部位とする。

#### 【0047】

図2(c)に2枚のコア基板材料1をまたがる形で集合回路形成基板12aを配置した例を示す。

30

#### 【0048】

一般に集合回路形成基板12には携帯電話やデジタルスチルカメラのセットの一台分の個別回路形成基板を複数配置する場合が多い。セットを組み立てる際には集合回路形成基板12の状態で電子部品を実装し、その後に最終製品毎に個別回路形成基板に分割するのが実装効率の面から普通である。

#### 【0049】

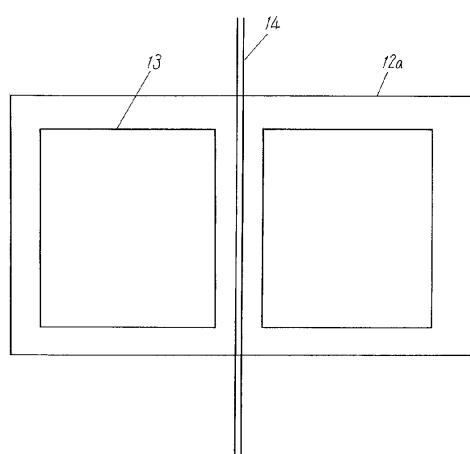

図3にその集合回路形成基板12aを上方より見た図を示す。

#### 【0050】

個別回路形成基板13の間に2枚のコア基板材料が当接する部位14が位置するように設計することが望ましい。

40

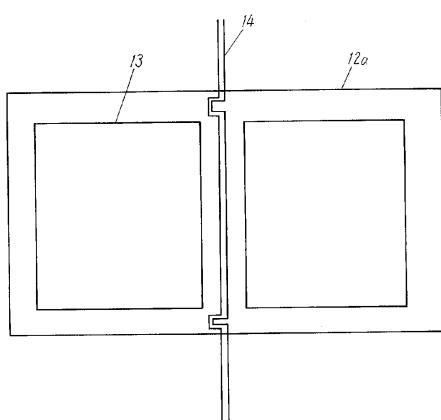

#### 【0051】

コア基板材料当接部14は図3では直線状であるが製品状態回路形成基板の強度を増すために、図4に示すように2枚のコア形成基板材料1が噛み合う形状にすることも有効である。

#### 【0052】

発明者の検討では、切断方法にダイシング法を用い、2枚のコア回路形成基板材料1の間隔を100μmにすることも可能であった。

#### 【0053】

切断方法には、ダイシング法の他にスリッタ刃を用いたり、レーザーによる切断法等の多くの方法が採用可能である。

50

**【0054】**

本実施の形態では1枚のプリプレグ2に対して2枚のコア基板材料1を積層しているが、コア基板材料1の枚数を3枚以上の構成も採用可能であるし、2枚のプリプレグを並べて複数枚のコア基板材料1を積層する等の多様な組み合わせが採用できる。

**【0055】**

また、プリプレグ2とコア基板材料1の組み合わせを厚み方向に多数段積層して高多層回路形成基板を製造することも可能である。

**【産業上の利用可能性】****【0056】**

以上述べたように、本発明の構成によれば、回路形成基板の製造時のワークサイズを大きくした場合にも基板材料をハンドリングを安定させ、従来の製造方法に比較してより薄くサイズの大きな基板材料を用いて回路形成基板の製造が可能になり、その結果、導電性ペースト等の層間接続手段を用いた層間の電気的接続の信頼性をも大幅に向上させながら、高品質の高密度回路形成基板を提供することができ、産業上の利用可能性は大といえる。

10

**【図面の簡単な説明】****【0057】**

【図1】本発明の実施の形態における回路形成基板の製造方法を示す工程断面図

【図2】本発明の実施の形態における回路形成基板の製造方法を示す平面図

20

【図3】本発明の実施の形態における回路形成基板の製造方法を示す平面図

【図4】本発明の実施の形態における回路形成基板の製造方法を示す平面図

【図5】従来例の回路形成基板の製造方法を示す工程断面図

**【符号の説明】****【0058】**

1 コア基板材料

30

2 プリプレグ

3 層間接続部

4 ビア穴

5 導電性ペースト

6 銅箔

7 回路

8 シート

9 レーザービア穴

10 レーザービア

11 ツールマーク

12、12a 集合回路形成基板

13 個別回路形成基板

14 コア基板材料当接部

【図1】

【図2】

【図3】

12a 集合回路形成基板

13 個別回路形成基板

14 ポア基板材料当接部

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開平04-286188(JP,A)

特開2000-307246(JP,A)

特開2001-024326(JP,A)

特開2000-151102(JP,A)

特開2000-133912(JP,A)

特開2000-216518(JP,A)

特開平8-116171(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 05 K        3 / 4 6

H 05 K        3 / 0 0