(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4486288号

(P4486288)

(45) 発行日 平成22年6月23日(2010.6.23)

(24) 登録日 平成22年4月2日(2010.4.2)

(51) Int.Cl.

F 1

G06F 9/445 (2006.01)

G06F 1/24 (2006.01)G06F 9/06 610K

G06F 1/00 350C

請求項の数 8 (全 29 頁)

(21) 出願番号 特願2001-357612 (P2001-357612)

(22) 出願日 平成13年11月22日 (2001.11.22)

(65) 公開番号 特開2002-287978 (P2002-287978A)

(43) 公開日 平成14年10月4日 (2002.10.4)

審査請求日 平成16年11月22日 (2004.11.22)

審判番号 不服2007-14636 (P2007-14636/J1)

審判請求日 平成19年5月21日 (2007.5.21)

(31) 優先権主張番号 09/721,398

(32) 優先日 平成12年11月22日 (2000.11.22)

(33) 優先権主張国 米国(US)

(73) 特許権者 500046438

マイクロソフト コーポレーション

アメリカ合衆国 ワシントン州 9805

2-6399 レッドmond ウェイ

クロソフト ウェイ

(74) 代理人 100077481

弁理士 谷 義一

(74) 代理人 100088915

弁理士 阿部 和夫

(74) 復代理人 100129171

弁理士 柿沼 健一

(72) 発明者 ポール イングランド

アメリカ合衆国 98008 ワシントン

州 ベルビュー ノースラップ ウェイ

16659

最終頁に続く

(54) 【発明の名称】コンピュータにおいてトラステッドコア初期化プロセスを安全に実行するためのプログラム、方法、メモリコントローラ、装置及びコンピュータ

## (57) 【特許請求の範囲】

## 【請求項 1】

1つまたは複数の中央処理装置、1つまたは複数のバスマスター、メモリ及びメモリコントローラを備えたコンピュータにおいて、トラステッドコア初期化プロセスを実行するためのプログラムであって、

前記コンピュータが、必ずしも安全ではないコードに基づいて動作している間に、前記必ずしも安全ではないコードの制御下で、前記メモリコントローラが、トラステッドコアをメモリにロードするステップと、

前記メモリコントローラが、前記トラステッドコアが正常に前記メモリにロードされた後に、前記コンピュータにおける前記1つまたは複数の中央処理装置の各々および前記1つまたは複数のバスマスターの各々が前記メモリにアクセスするのを防止するステップと、

前記メモリへのアクセスが防止された後に、前記1つまたは複数の中央処理装置のうちの1つをリセットするステップであって、

前記メモリコントローラが、中央処理装置リセットベクトルを、初期化ベクトルにマップするステップと、

前記メモリコントローラが、前記中央処理装置リセットベクトルに対応する読み取り要求を、前記1つまたは複数の中央処理装置のうちの1つから受信するステップと、

前記メモリコントローラが、前記読み取り要求に応答して、前記初期化ベクトルを前記1つまたは複数の中央処理装置のうちの1つに返すステップと、

前記メモリコントローラが、前記1つまたは複数の中央処理装置のうちの1つが、前

10

20

記初期化ベクトルで始まる前記メモリにアクセスできるようにするステップと

を含む、ステップと、

前記 1 つまたは複数の中央処理装置のうちの 1 つがリセットされた後に、前記メモリコントローラが、前記 1 つまたは複数の中央処理装置のうちの 1 つが前記メモリにアクセスして前記トラステッドコアに含まれるトラステッドコア初期化コードを読み出すことができるようになるステップであって、前記 1 つまたは複数の中央処理装置のうちの 1 つが前記トラステッドコア初期化コードを実行することにより、前記トラステッドコアを初期化することができるようになる、ステップと、

前記トラステッドコアが初期化された後、前記メモリコントローラが、前記コンピュータにおける他のいかなる中央処理装置およびいかなるバスマスターも前記メモリにアクセスできるようになるステップと

10

を順に実行させるためのプログラム。

#### 【請求項 2】

コンピュータに、

前記初期化ベクトルを前記 1 つの中央処理装置に返した後に、前記メモリコントローラが、前記中央処理装置リセットベクトルを追加の中央処理装置開始ベクトルに再マップするステップと、

前記メモリコントローラが、別の中の中央処理装置からの、前記中央処理装置リセットベクトルに対応する、他のいかなる読み取り要求にも応答して、前記追加の中央処理装置開始ベクトルを返すステップとをさらに実行させることを特徴とする請求項 1 に記載のプログラム。

20

#### 【請求項 3】

コンピュータに、

前記中央処理装置をリセットした後に、マイクロコードを、前記メモリにおけるトラステッドコアから前記 1 つの中央処理装置へロードするステップをさらに実行させるための請求項 1 に記載のプログラム。

#### 【請求項 4】

1 つまたは複数の中央処理装置、1 つまたは複数のバスマスター、メモリ及びメモリコントローラを備えたコンピュータにおいて、トラステッドコア初期化プロセスを実行するための方法であって、

30

前記コンピュータが、必ずしも安全ではないコードに基づいて動作している間に、前記必ずしも安全ではないコードの制御下で、前記メモリコントローラが、トラステッドコアをメモリにロードするステップと、

前記メモリコントローラが、前記トラステッドコアが正常に前記メモリにロードされた後に、前記コンピュータにおける前記 1 つまたは複数の中央処理装置の各々および前記 1 つまたは複数のバスマスターの各々が前記メモリにアクセスするのを防止するステップと、

前記メモリへのアクセスが防止された後に、前記 1 つまたは複数の中央処理装置のうちの 1 つをリセットするステップであって、

前記メモリコントローラが、中央処理装置リセットベクトルを、初期化ベクトルにマップするステップと、

40

前記メモリコントローラが、前記中央処理装置リセットベクトルに対応する読み取り要求を、前記 1 つまたは複数の中央処理装置のうちの 1 つから受信するステップと、

前記メモリコントローラが、前記読み取り要求に応答して、前記初期化ベクトルを前記 1 つまたは複数の中央処理装置のうちの 1 つに返すステップと、

前記メモリコントローラが、前記 1 つまたは複数の中央処理装置のうちの 1 つが、前記初期化ベクトルで始まる前記メモリにアクセスできるようになるステップと

を含む、ステップと、

前記 1 つまたは複数の中央処理装置のうちの 1 つがリセットされた後に、前記メモリコントローラが、前記 1 つまたは複数の中央処理装置のうちの 1 つが前記メモリにアクセスして前記トラステッドコアに含まれるトラステッドコア初期化コードを読み出すことであ

50

きるようとするステップであって、前記1つまたは複数の中央処理装置のうちの1つが前記トラステッドコア初期化コードを実行することにより、前記トラステッドコアを初期化することができるようとする、ステップと、

前記トラステッドコアが初期化された後、前記メモリコントローラが、前記コンピュータにおける他のいかなる中央処理装置およびいかなるバスマスターも前記メモリにアクセスできるようにするステップと

を有することを特徴とする方法。

#### 【請求項5】

前記1つまたは複数の中央処理装置が、前記トラステッドコアの実行を終了するステップと、

10

前記1つまたは複数の中央処理装置が、前記トラステッドコアの実行を、前記コンピュータをリブートすることなく、再び開始するステップと、

をさらに含むことを特徴とする請求項4に記載の方法。

#### 【請求項6】

前記1つまたは複数の中央処理装置が、前記トラステッドコアの実行を終了するステップと、

前記メモリコントローラが、別のトラステッドコアをメモリにロードするステップと、

前記メモリコントローラが、前記トラステッドコアの実行を開始した手順と同様の手順で、前記別のトラステッドコアの実行を開始するステップと、

をさらに含むことを特徴とする請求項4に記載の方法。

20

#### 【請求項7】

前記メモリコントローラが、前記初期化ベクトルを前記1つの中央処理装置に返した後に、前記中央処理装置リセットベクトルを追加の中央処理装置開始ベクトルに再マップするステップと、

前記メモリコントローラが、前記1つまたは複数の中央処理装置の別の中央処理装置からの、前記中央処理装置リセットベクトルに対応する、他のいかなる読み取り要求にも応答して、前記追加の中央処理装置開始ベクトルを返すステップと、

をさらに含むことを特徴とする請求項4に記載の方法。

#### 【請求項8】

請求項1乃至3のいずれかに記載のプログラムを記録したコンピュータ読取可能な記録媒体。

30

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、安全なコード実行に関し、より詳細には、コンピュータにおいてトラステッドコア初期化プロセスを安全に実行するためのプログラム、方法、メモリコントローラ、装置及びコンピュータに関する。

##### 【0002】

##### 【従来の技術】

人々がコンピュータを信用できるようにすることは、ますます重要なゴールとなってきている。この信用は一般に、コンピュータが格納あるいは受信する情報を正しく使用することを信用できることに集中している。厳密にこの信用が何を内含するかは、環境に基づいて変わる可能性がある。たとえば、マルチメディアコンテンツプロバイダは、コンピュータが不適切にそれらのコンテンツをコピーしないことを信用できることを望む。もう1つの例として、ユーザは自分のコンピュータが内密の金融情報（たとえば、銀行口座番号）を適切な宛先のみに転送すること（たとえば、この情報を自分の銀行に渡すことはできるが、それ以外のところには渡すことができないようのこと）を信用できることを望む。残念ながら、大抵のコンピュータの一般に開かれた特性が与えられると、幅広い範囲のアプリケーションを大抵の現在のコンピュータ上で、ユーザが知ることなく実行させることができ、これらのアプリケーションがこの信用を損なう（たとえば、ユーザの金融情報

40

50

を、ある他の宛先へ不当な使用のために転送する)おそれがある。

#### 【0003】

これらの信用の問題に対処するため、コンピュータまたはその一部を信用できるようにする、異なる機構が提案されている(また、新しい機構が開発されている)。一般に、これらの機構は、ある種類の認証手順を内含しており、コンピュータが、少なくともその一部(たとえば、メモリのある領域、あるアプリケーションなど)が少なくともそれらがそれら自体を提示するものと同じように信用できること(たとえば、コンピュータまたはアプリケーションが実際に、それが主張するものであること)を認証あるいは証明することができる。すなわち、これらの機構は、不当なアプリケーションが別のアプリケーションのふりをすること(あるいは、コンピュータが別のコンピュータのふりができるようにすること)を防止する。このような機構を確立することができるようになった後、ユーザまたは他者(たとえば、コンテンツプロバイダ)が、特定のアプリケーションを信用できるものとして受け入れるかどうかについての判断を行うことができる(たとえば、コンピュータが、特定のアプリケーションがそれ自体の主張するアプリケーションであるという、コンテンツプロバイダの満足を証明することができるようになった後、マルチメディアコンテンツプロバイダが、特定のアプリケーションを信用できるものとして受け入れることができる)。しかし、このような機構をコンピュータ上に設置することは困難である可能性があり、これは、この機構に干渉する不当なアプリケーション(たとえば、信用されている機構のふりをする不当なアプリケーション)に対する保護が必要となるからである。

#### 【0004】

1つの解決策は、コンピュータをブートするための信用できる機構を含むコンピュータを構築することである。しかし、コンピュータをブートすることは、典型的には、様々なコード片を使用することを含み、これはしばしば基本入出力システム(BIOS)と呼ばれ、また、潜在的に多数のオプションの読み取り専用メモリ(ROM)またはBIOS拡張機能を使用することを含み、これはオペレーティングシステムを有する他の記憶デバイス(典型的にはハードディスクドライブ)からロードするように動作する。したがって、コンピュータをブートするための信用できる機構は、BIOSが信用できるものであり、オプションの各ROMが信用できるものであり、各BIOS拡張機能が信用できるものであることを、信用できるオペレーティングシステムをコンピュータにロードできるようになる前に必要とする。これらの各構成要素を信用できるものにすることが困難であるだけでなく、BIOS、オプションのROM、およびBIOS拡張機能が頻繁に、コンピュータにおいて再書き込みすることができるデバイス(たとえば、フラッシュメモリ)上に格納され、したがって、これらの保全性が損なわれる。したがって、コンピュータをブートするための信用できる機構を含むコンピュータを構築することは、問題がある可能性がある。

#### 【0005】

##### 【発明が解決しようとする課題】

よって本発明の目的は、これらの欠点に対処し、コンピュータにおいてトラステッドコア初期化プロセスを安全に実行するためのプログラム、方法、メモリコントローラ、装置及びコンピュータを提供することにある。

#### 【0006】

##### 【課題を解決するための手段】

コンピュータにおいてトラステッドコア初期化プロセスを安全に実行するためのプログラム、方法、メモリコントローラ、装置及びコンピュータが本明細書に記載されている。

#### 【0007】

本発明の一形態によれば、メモリコントローラが、CPUおよび他のI/Oバスマスターがコード(たとえば、OS、マイクロカーネル、または他のトラステッドコア)初期化プロセス中にメモリにアクセスするのを防止する。メモリコントローラは、CPUをコンピュータにおいてリセットし、CPUがメモリの特定の場所(CPUに対してメモリコントローラによって識別される)でアクセスを開始できるようにする。初期化プロセスがそのCPUによって実行された後、コードが動作状態であり、他のいかなるCPUも(リセット

10

20

30

40

50

された後に)メモリにアクセスすることができ、(開始されたコードによって課せられたいかなる制御も受ける)他のいかなるバスマスターもメモリにアクセスすることができる。

【0008】

請求項1に係る本発明は、コンピュータに、暴走する可能性のある信用されていないコードに基づいて前記コンピュータの動作が正常に開始された場合、前記信用されていないコードの制御下で、トラステッドコアをメモリにロードするステップと、前記トラステッドコアが正常に前記メモリにロードされた場合、前記コンピュータにおける1つまたは複数の中央処理装置の各々および1つまたは複数のバスマスターの各々が前記メモリにアクセスするのを防止するステップと、前記メモリへのアクセスが防止された後に、前記1つまたは複数の中央処理装置の各々をリセットするステップと、前記リセットがなされた後に、1つの中央処理装置が前記メモリにアクセスして、前記トラステッドコアに含まれるトラステッドコア初期化コードを実行することにより、前記トラステッドコアを初期化するステップと、前記トラステッドコアが初期化された後、前記コンピュータにおける他のいかなる中央処理装置およびいかなるバスマスターも前記メモリにアクセスできるようにするステップとを順に実行させるための1又は複数の実行制御用のプログラムである。10

請求項2に係る本発明は、コンピュータに、中央処理装置リセットベクトルを、初期化ベクトルにマップするステップと、前記中央処理装置リセットベクトルに対応する読み取り要求を、前記1つの中央処理装置から受信するステップと、前記読み取り要求に応答して、前記初期化ベクトルを前記1つの中央処理装置に返すステップと、前記1つの中央処理装置が、前記初期化ベクトルで開始して、前記メモリにアクセスできるようにするステップをさらに実行させるための請求項1に記載のプログラムである。20

請求項3に係る本発明は、コンピュータに、前記初期化ベクトルを前記1つの中央処理装置に返した後に、前記中央処理装置リセットベクトルを追加の中央処理装置開始ベクトルに再マップするステップと、別の中央処理装置からの、前記中央処理装置リセットベクトルに対応する、他のいかなる読み取り要求にも応答して、前記追加の中央処理装置開始ベクトルを返すステップとをさらに実行させるための請求項2に記載のプログラムである。

請求項4に係る本発明は、コンピュータに、前記中央処理装置をリセットした後に、マイクロコードを、前記メモリにおけるトラステッドコアから前記1つの中央処理装置へロードするステップをさらに実行させるための請求項1に記載のプログラムである。

請求項5に係る本発明は、メモリコントローラ、メモリ、トラステッドコア、中央処理装置及びバスマスターを備えたコンピュータが行う安全な初期化方法において、前記中央処理装置が、暴走する可能性のある信用されていないコードに基づいて、前記コンピュータをブートするステップと、前記ブートが正常に行われた場合、前記メモリコントローラが、トラステッドコアをメモリにロードするステップと、前記トラステッドコアが正常に前記メモリにロードされた場合、前記トラステッドコアの安全な実行を開始するにあたり、前記メモリコントローラが、前記コンピュータにおける1つまたは複数の中央処理装置の各々が前記メモリにアクセスするのを防止するステップと、前記メモリコントローラが、前記コンピュータにおける1つまたは複数のバスマスターの各々が前記メモリにアクセスするのを防止するステップと、前記メモリコントローラが、前記1つまたは複数の中央処理装置の各々が前記メモリにアクセスするのを防止された後であって、かつ、前記1つまたは複数のバスマスターの各々が前記メモリにアクセスするのを防止された後に、前記1つまたは複数の中央処理装置の各々をリセットするステップと、前記メモリコントローラが、前記リセットの後に、前記1つまたは複数の中央処理装置の各々が前記メモリにアクセスして前記トラステッドコアを読み込み、該トラステッドコアに含まれるトラステッドコア初期化コードを実行するトラステッドコア初期化プロセスを実行できるようにするステップと、前記トラステッドコア初期化プロセスが実行された後、前記メモリコントローラが、他のいかなる中央処理装置およびいかなる前記1つまたは複数のバスマスターも前記メモリにアクセスできるようにするステップと、を含むことを特徴とする方法である。40

請求項6に係る本発明は、前記トラステッドコアが、前記トラステッドコアの実行を終了するステップと、前記トラステッドコアが、前記トラステッドコアの実行を、前記コン50

ピュータをリブートすることなく、再び開始するステップと、をさらに含むことを特徴とする請求項 5 に記載の方法である。

請求項 7 に係る本発明は、前記トラステッドコアが、前記トラステッドコアの実行を終了するステップと、前記メモリコントローラが、別のトラステッドコアをメモリにロードするステップと、前記メモリコントローラが、前記トラステッドコアの実行を開始した手順と同様の手順で、前記別のトラステッドコアの実行を開始するステップと、をさらに含むことを特徴とする請求項 5 に記載の方法である。

請求項 8 に係る本発明は、中央処理装置が、暴走する可能性のある信用できないコードに基づいて、コンピュータをブートするステップと、正常に前記ブートが行われた場合、メモリコントローラが、トラステッドコアをメモリにロードするステップと、前記トラステッドコアが正常に前記メモリにロードされた場合、前記メモリコントローラが、前記トラステッドコアの安全な実行を開始するにあたり、中央処理装置リセットベクトルを、初期化ベクトルにマップするステップと、前記メモリコントローラが、前記コンピュータにおける 1 または複数の中央処理装置の各々をリセットするステップと、前記メモリコントローラが、前記マップおよび前記リセットの後に、前記中央処理装置リセットベクトルに対応する読み取り要求を、前記 1 つまたは複数の中央処理装置のいずれか 1 つから受信するステップと、前記メモリコントローラが、前記読み取り要求に応答して、前記初期化ベクトルを前記 1 つの中央処理装置に返すステップと、前記メモリコントローラが、前記 1 つの中央処理装置が前記初期化ベクトルで開始して前記メモリにアクセスすることを許可するステップと、を含むことを特徴とする方法である。

請求項 9 に係る本発明は、前記メモリコントローラが、前記初期化ベクトルを前記 1 つの中央処理装置に返した後に、前記中央処理装置リセットベクトルを追加の中央処理装置開始ベクトルに再マップするステップと、前記メモリコントローラが、前記 1 つまたは複数の中央処理装置の別の中央処理装置からの、前記中央処理装置リセットベクトルに対応する、他のいかなる読み取り要求にも応答して、前記追加の中央処理装置開始ベクトルを返すステップと、をさらに含むことを特徴とする請求項 8 に記載の方法である。

請求項 10 に係る本発明は、コンピュータに、暴走する可能性のある信用されていないコードに基づいて前記コンピュータが正常にブートされた場合、トラステッドコアをメモリにロードするステップと、前記トラステッドコアが正常に前記メモリにロードされた場合、前記トラステッドコアの安全な実行を開始するにあたり、前記コンピュータにおける 1 または複数の中央処理装置の各々が前記メモリにアクセスするのを防止するステップと、前記コンピュータにおける 1 または複数のバスマスターの各々が前記メモリにアクセスするのを防止するステップと、前記 1 または複数の中央処理装置の各々が前記メモリにアクセスするのを防止された後であって、かつ、前記 1 または複数のバスマスターの各々が前記メモリにアクセスするのを防止された後に、前記 1 または複数の中央処理装置の各々をリセットするステップと、前記リセットの後に、前記 1 または複数の中央処理装置の各々が前記メモリにアクセスして前記トラステッドコアを読み込み、該トラステッドコアに含まれるトラステッドコア初期化コードを実行するトラステッドコア初期化プロセスを実行できるようにするステップと、前記トラステッドコア初期化プロセスが実行された後、他のいかなる中央処理装置およびいかなる前記 1 または複数のバスマスターも前記メモリにアクセスできるようにするステップと、を順に実行させるための 1 又は複数の実行制御用のコンピュータプログラムを記録したコンピュータ読み取り可能な記録媒体である。

請求項 11 に係る本発明は、暴走する可能性のある信用できないコードに基づいて、動作を開始するステップと、前記動作が正常に開始された場合、前記コンピュータが、前記信用できないコードの制御下で、任意の種類のコードをメモリにロードするステップと、前記トラステッドコアが正常にメモリにロードされた場合、前記コンピュータが、前記任意の種類のコードの実行を、請求項 5 に記載されたトラステッドコア初期化プロセスの実行と同様の手順で開始するステップと、を含むことを特徴とする方法である。

請求項 12 に係る本発明は、前記コンピュータが、中央処理装置リセットベクトルを、初期化ベクトルにマップするステップと、前記コンピュータが備えるメモリコントローラ

10

20

30

40

50

が、前記中央処理装置リセットベクトルに対応する読み取り要求を、前記コンピュータが備える1つの中央処理装置から受信するステップと、前記メモリコントローラが、前記読み取り要求に応答して、前記初期化ベクトルを前記1つの中央処理装置に返すステップと、

前記メモリコントローラが、前記1つの中央処理装置が前記初期化ベクトルで開始して前記メモリにアクセスすることを許可するステップと、をさらに含むことを特徴とする請求項11に記載の方法である。

請求項13に係る本発明は、前記メモリコントローラが、前記初期化ベクトルを前記1つの中央処理装置に返した後に、前記中央処理装置リセットベクトルを追加の中央処理装置開始ベクトルに再マップするステップと、前記メモリコントローラが、別の中央処理装置からの、前記中央処理装置リセットベクトルに対応する、他のいかなる読み取り要求にも応答して、前記追加の中央処理装置開始ベクトルを返すステップと、をさらに含むことを特徴とする請求項12に記載の方法である。10

請求項14に係る本発明は、前記メモリコントローラが、中央処理装置がリセットされた後に実行を開始するアドレスに現れるように、前記任意の種類のコードを再マップするステップをさらに含む、ことを特徴とする請求項11に記載の方法である。

請求項15に係る本発明は、前記メモリコントローラが、中央処理装置から、中央処理装置リセットベクトルに対応する読み取り要求を受信するステップと、前記メモリコントローラが、前記トラステッドコアの開始場所へジャンプさせるための命令により、前記中央処理装置からの前記読み取り要求に応答するステップと、をさらに含むことを特徴とする請求項11に記載の方法である。20

請求項16に係る本発明は、コンピュータに、暴走する可能性のある信用できないコードに基づいて前記コンピュータの動作が正常に開始された場合、前記信用できないコードの制御下で、任意の種類のコードをメモリにロードするステップと、前記トラステッドコアが正常に前記メモリにロードされた場合、前記任意の種類のコードの実行を、請求項5に記載されたトラステッドコア初期化プロセスの実行と同様の手順で開始するステップと、を順に実行させるための1又は複数の実行制御用のコンピュータプログラムを記録したコンピュータ読み取可能な記録媒体である。

請求項17に係る本発明は、プロセッサとの通信を可能にするための第1のインターフェースと、システムメモリとの通信を可能にするための第2のインターフェースと、前記第1のインターフェースおよび前記第2のインターフェースに結合されたコントローラであって、前記プロセッサをリセットし、他のいかなるプロセッサによる前記システムメモリへのアクセスもが防止されている間に前記プロセッサにコード初期化プロセスを実行させ、プロセッサリセットベクトルを初期化ベクトルにマップし、前記プロセッサリセットベクトルに対応する読み取り要求を前記プロセッサから受信し、前記読み取り要求に応答して、前記プロセッサに前記初期化ベクトルを返し、前記プロセッサが前記初期化ベクトルで開始して前記メモリにアクセスできるようにし、前記プロセッサに前記初期化ベクトルを返した後に、前記プロセッサリセットベクトルを追加のプロセッサ開始ベクトルに再マップし、別のプロセッサからの、前記プロセッサリセットベクトルに対応する他のいかなる読み取り要求にも応答して、前記追加のプロセッサ開始ベクトルを返すコントローラとを含むことを特徴とするメモリコントローラである。30

請求項18に係る本発明は、前記コントローラはさらに、前記プロセッサが前記コード初期化プロセスを実行できるようにし、いかなるバスマスターもが前記システムメモリにアクセスするのを防止するためのものであることを特徴とする請求項17に記載のメモリコントローラである。

請求項19に係る本発明は、前記コントローラはさらに、前記プロセッサが前記コード初期化プロセスを実行できるようにする前に、前記メモリコントローラに結合された、他のいかなるプロセッサをリセットし、前記1つの処理が前記コード初期化プロセスを実行するまで、前記メモリコントローラに結合された、他のいかなるプロセッサおよびいかなるバスマスターもが、前記システムメモリにアクセスするのを防止し、前記コード初期化プロセスの実行後、前記メモリコントローラに結合された、他のいかなる中央処理装置、50

および、前記メモリコントローラに結合されたいかなるバスマスターも前記メモリにアクセスできるようにするためのものであることを特徴とする請求項 1\_7 に記載のメモリコントローラである。

請求項 2\_0 に係る本発明は、プロセッサへのリセット信号をアサートするプロセッサリセット部と、前記プロセッサが、トラステッドコア初期化プロセスの実行を完了するまではいかなるバスマスターもメモリにアクセスするのを防止し、かつ、前記プロセッサが前記トラステッドコア初期化プロセスの実行を完了した後にはいかなる前記バスマスターも前記メモリにアクセスすることを許すメモリ保護部と、プロセッサリセットベクトルを初期化ベクトルにマップし、前記プロセッサリセットベクトルに対応する読み取り要求を前記プロセッサから受信し、前記読み取り要求に応答して、前記プロセッサに前記初期化ベクトルを返し、前記プロセッサが前記初期化ベクトルで開始して前記メモリにアクセスできるようにし、前記プロセッサに前記初期化ベクトルを返した後に、前記プロセッサリセットベクトルを追加のプロセッサ開始ベクトルに再マップし、別のプロセッサからの、前記プロセッサリセットベクトルに対応する他のいかなる読み取り要求にも応答して、前記追加のプロセッサ開始ベクトルを返すコントローラとを含むことを特徴とする装置である。

請求項 2\_1 に係る本発明は、前記コントローラはさらに、前記プロセッサが前記トラステッドコア初期化プロセスの実行を完了するまで、別のプロセッサからのメモリアクセス要求も前記メモリに出力しないことにより前記別のプロセッサがメモリにアクセスするのを防止することを特徴とする請求項 2\_0 に記載の装置である。

請求項 2\_2 に係る本発明は、プロセッサへのリセット信号をアサートするプロセッサリセット部と、前記プロセッサが、トラステッドコア初期化プロセスの実行を完了するまではいかなるバスマスターもメモリにアクセスするのを防止するメモリ保護部と、前記メモリ保護部に結合されたコントローラであって、プロセッサリセットベクトルを初期化ベクトルにマップし、前記プロセッサリセットベクトルに対応した読み取り要求を、前記プロセッサから受信し、前記読み取り要求に応答して、前記初期化ベクトルを前記プロセッサに返し、前記プロセッサが、前記初期化ベクトルで開始して、前記メモリにアクセスできるようにし、前記プロセッサに前記初期化ベクトルを返した後に、前記プロセッサリセットベクトルを追加のプロセッサ開始ベクトルに再マップし、別のプロセッサからの、前記プロセッサリセットベクトルに対応する別の読み取り要求に応答して、前記追加のプロセッサ開始ベクトルを返すコントローラと、を含む、ことを特徴とする装置である。

請求項 2\_3 に係る本発明は、前記コントローラはさらに、前記初期化ベクトルを前記プロセッサに返した後に、前記プロセッサリセットベクトルを、追加のプロセッサ開始ベクトルに再マップし、別のプロセッサからの、前記プロセッサリセットベクトルに対応した、別の読み取り要求に応答して、前記追加のプロセッサ開始ベクトルを返す、ことを特徴とする請求項 2\_2 に記載の装置である。

請求項 2\_4 に係る本発明は、前記トラステッドコアの一部が格納される記憶部をさらに含む、ことを特徴とする請求項 2\_0 に記載の装置である。

請求項 2\_5 に係る本発明は、プロセッサと、バスマスターと、システムメモリと、前記プロセッサ、前記バスマスターおよび前記システムメモリに結合されたメモリコントローラとを含み、前記メモリコントローラは、暴走する可能性のある信用できないコードに基づいて正常に動作した場合、前記プロセッサおよび前記バスマスターからの前記システムメモリへのアクセスを正常に中継し、前記プロセッサを、トラステッドコア初期化プロセスを開始するためにリセットし、前記バスマスターが前記システムメモリにアクセスすることを、前記トラステッドコア初期化プロセスが完了される後まで防止するように構成される、ことを特徴とするコンピュータである。

請求項 2\_6 に係る本発明は、複数の追加のプロセッサをさらに含み、前記複数の追加のプロセッサが前記システムメモリにアクセスすることを、前記トラステッドコア初期化プロセスが完了される後まで防止する、ことを特徴とする請求項 2\_5 に記載のコンピュータである。

請求項 2\_7 に係る本発明は、コンピュータにおける異なるトラステッドコアの実行を、

10

20

30

40

50

前記コンピュータをリブートする必要なく、逐次開始するステップを含む、ことを特徴とする、前記コンピュータが実行する方法である。

請求項 2\_8 に係る本発明は、前記開始するステップは、前記異なるトラステッドコアの実行を、任意の回数で開始するステップをさらに含む、ことを特徴とする請求項 2\_7 に記載の前記コンピュータが実行する方法である。

請求項 2\_9 に係る本発明は、前記メモリコントローラは、さらに加えて、前記プロセッサの状態をクリアすることにより、前記プロセッサをリセットするように構成されている、ことを特徴とする請求項 2\_5 に記載のコンピュータである。

請求項 3\_0 に係る本発明は、前記メモリコントローラは、さらに加えて、前記プロセッサへのリセット信号をプロセッサバス上にてアサートすることにより、前記プロセッサをリセットするように構成されている、ことを特徴とする請求項 2\_5 に記載のコンピュータである。 10

請求項 3\_1 に係る本発明は、前記メモリコントローラは、さらに加えて、前記プロセッサへの RESET # 信号をアサートすることにより、前記プロセッサをリセットするように構成されている、ことを特徴とする請求項 2\_5 に記載のコンピュータである。

請求項 3\_2 に係る本発明は、中央処理装置が、コンピュータの動作を、暴走する可能性のある信用されていないコードに基づいて開始させるステップと、前記コンピュータの動作が正常に開始された場合、メモリコントローラが、前記信用されていないコードの制御下で、前記コンピュータのトラステッドコアをメモリにロードするステップと、前記トラステッドコアが正常に前記メモリにロードされた場合、前記メモリコントローラが、前記コンピュータにおける1つまたは複数の中央処理装置の各々および1つまたは複数のバスマスターの各々が前記メモリにアクセスするのを防止するステップと、前記メモリコントローラが、前記1つまたは複数の中央処理装置の各々における状態をクリアするステップと、1つの中央処理装置が、前記トラステッドコアを初期化するために、前記メモリにアクセスし前記トラステッドコアに含まれるトラステッドコア初期化コードを実行するステップと、前記メモリコントローラが、前記トラステッドコアが初期化された後、前記コンピュータにおける他のいかなる中央処理装置およびいかなるバスマスターも前記メモリにアクセスできるようにするステップと、を具備したことを特徴とする方法である。 20

#### 【0078】

##### 【発明の実施の形態】

以下、図面を参照して、本発明の実施の形態を詳細に説明する。なお、図面全体で同じ番号を使用して、同様の構成要素および / または特徴を表す。 30

#### 【0079】

コンピュータにおけるコード（たとえば、ソフトウェア命令）の安全な初期化を可能にするための方法およびシステムが、本明細書に記載されている。この安全なコード初期化プロセス(secure code initialization process)は、主として、コンピュータにおいてトラステッドコア(trusted core)を初期化することに関連して記載してある。しかし、安全なコード初期化プロセスを使用して、幅広い種類のタイプのコードのいずれをも、コードがどの程度信用できるかに関わらず、安全に初期化することができる。本明細書で記載された機構(mechanism)は、特定の関心のあるものであり、これは、コアCPU(core-CPU)に対する変更が必要とされず、ロジックをサポートするCPUに対する変更がほとんど必要とされないからである。 40

#### 【0080】

本明細書で使用されるように、「トラステッド（信用されている：trusted）」コードは、特性(nature)において不变であり、識別(identity)において不变であるコードを指す。トラステッドコードは、コンピュータの他の部分（たとえば、コード）により不正に変更されることを免れており、信頼性を有して、かつ曖昧でなく識別することができる。すなわち、「このコードは誰か」と尋ねる他のいかなるエンティティ(entity)または構成要素(component)にも、「これはコード x y z である」と伝えることができ、このコードが（ある詐称者ではなく）真にコード x y z であること、および、コード x y z が本物であるこ 50

とを保証することができる。信用(trust)は、コードのいかなる質または有用性の面をも扱わず、特性の不变性および識別の不变性のみを扱う。本明細書に記載された方法およびシステムを使用して、トラステッドコード(trusted code)が、それが順序正しい状態で実行を開始したことを知ることができるようにし、初期化の不变性(immutability of initialization)を提供することができる。

#### 【0081】

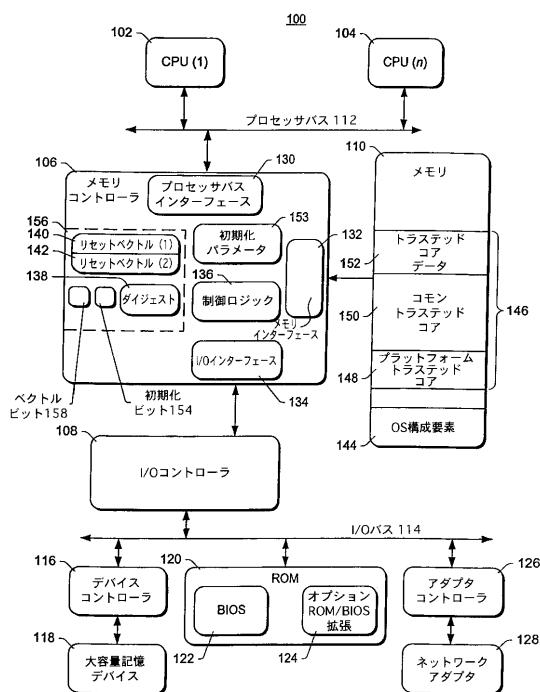

図1は、本発明のある実施形態による、例示的コンピュータ100を例示するブロック図である。コンピュータ100は、幅広い種類のコンピューティングデバイスを表すことを意図するものであり、これらは、パーソナルコンピュータ(PC)、ハンドヘルドまたはポケットデバイス、携帯情報端末(PDA)、ゲーム用コンソール、インターネット器具、マルチプロセッサまたはシングルプロセッサシステム、マイクロプロセッサベースまたはプログラマブル消費者電化製品、ネットワークPC、ミニコンピュータ、メインフレームコンピュータ、埋め込み型システムなどである。

10

#### 【0082】

コンピュータ100は、1つまたは複数の中央処理装置(CPU)またはプロセッサ102、104、メモリコントローラ106、I/Oコントローラ108、およびシステムメモリ110を含む。CPU102および104は、幅広い種類のプロセッサのいずれかを表し、これらは、x86アーキテクチャ(または互換性のある)プロセッサ、PowerPCアーキテクチャ(または互換性のある)プロセッサなどである。多数(n)のCPU102、104が図1において例示されるが、コンピュータ100は、他の実施形態として、単一のCPUのみと共に実施することができる。CPU102、104は共に、メモリコントローラ106へ、プロセッサバス112を介して結合される。

20

#### 【0083】

メモリコントローラ106は、分離した構成要素として例示されるが、他の実施形態として、割り込みコントローラ、AGP(accelerated graphics port)などを含むブリッジなど、別の構成要素またはデバイスに組み込むことができる。メモリコントローラ106は、CPU102、104、I/Oコントローラ108、およびメモリ110と通信する。メモリ110は、ランダムアクセスメモリ(RAM)など、システムメモリを表す。I/Oコントローラ108は、I/Oバス114、および、コンピュータ100内の他の構成要素に結合された、様々なI/Oデバイスの間のブリッジまたはインターフェースとして動作する。幅広い種類の従来のI/Oデバイスのいずれも、I/Oバス114に結合することができる。例示された例では、大容量記憶デバイスコントローラ116がバス114および大容量記憶デバイス(たとえば、ハードディスク)118に結合され、ROM120(BIOS122、および、オプションのROMおよび/またはBIOS拡張機能124を含む)がバス114に結合され、アダプタコントローラ126がバス114およびネットワークアダプタ128(たとえば、ネットワークインターフェースカード(NIC)またはモデム)に結合される。

30

#### 【0084】

メモリコントローラ106は、プロセッサバスインターフェース130、メモリインターフェース132、I/Oインターフェース134、制御ロジック(プロセッサまたはコントローラとも呼ばれる)136、ダイジェスト138、2つのリセットベクトル140、142、および初期化パラメータ(initialization parameter)153を含む。プロセッサバスインターフェース130は、メモリコントローラ106とプロセッサバス112との間のインターフェースとして動作し、メモリコントローラ106がコマンドおよび要求をCPU102、104から受信し、さらに、応答およびコマンドをCPU102、104に送ることができるようになる。メモリインターフェース132は、システムメモリ110へのインターフェースとして動作し、コントローラ106が、メモリ110に格納されたデータを読み取り、データをメモリ110に書き込むことができるようになる。I/Oインターフェース134は、I/Oコントローラ108へのインターフェースとして動作し、I/Oコントローラ108を介して、I/O構成要素118、120および128がメ

40

50

モリコントローラ 106 と通信し、メモリコントローラ 106 が I/O 構成要素 118、120 および 128 と通信することができるようとする。例示された例では、コントローラ 106 の内部の構成要素（たとえば、制御ロジック 136、リセットベクトル 140、142 など）へ、かつ／または、それからの通信が、適切なインターフェースを介して渡される。

#### 【0085】

I/O バス 114 に結合された I/O 構成要素のうち選択されたものが、バスマスターとして動作することができる。バスマスターは、アドレスバス信号および他のバス制御信号をバス上で駆動することができるデバイス（典型的には、CPU 以外）を指す。バスマスターの例は、大容量記憶デバイスコントローラ 116 およびネットワークアダプタコントローラ 126 である。バスマスターは、メモリ 110 と、I/O コントローラ 108 および 106 を介して通信して、メモリ 110 へ、かつ／または、それからの直接メモリアクセス（DMA）転送を実行することなどができる、それにより、CPU 102, 104 がこのような転送を直接管理しなければならないことを軽減する。

10

#### 【0086】

図 1 の例示された例では、I/O コントローラ 108 がメモリコントローラ 106 と直接通信する。他の実施形態として、これらの通信が、メモリコントローラ 106 を通過せず、プロセッサを介して I/O ブリッジ（図示せず）を通ることができる。加えて、I/O ブリッジへのプロセッサも、I/O コントローラ 108 と CPU 102, 104 の間の、プロセッサバス 112 上の通信を可能にする。一実施形態では、メモリコントローラ 106 が「チップセット」の一部として含まれ、これも I/O ブリッジへのプロセッサなどを含む。チップセットは、コンピュータのサブシステムの間のインターフェースを提供する 1 つまたは複数のチップのセットを指し、CPU, メモリ, I/O デバイスなどが対話することができるようとするためのバスおよび電子機器を含む。

20

#### 【0087】

制御ロジック 136 は、トラステッドコアをコンピュータ 100 において安全にロードできることを保証（ensure）するように動作し、メモリ 110 へのアクセスを特定の環境下でのみ可能とし、これについては以下でより詳細に論じる。制御ロジック 136 は、マイクロコード（マイクロコントローラのみがアクセス可能である不揮発性の安全な場所（たとえば、コントローラ 106 内）に格納されたもの）を実行するマイクロコントローラ、プログラマブルロジックデバイス、または他の特定用途向け集積回路（ASIC）など、様々な方法のいずれにおいても実施することができる。

30

#### 【0088】

コンピュータ 100 の起動（たとえば、電源を入れるか、あるいはリセットすること）において、メモリ 110 の状態は一般的には保証されない。メモリ 110 は一般的にはダイナミック RAM (DRAM) であり、これは、その状態を維持するために定期的なリフレッシュを必要とし、そのため、コンピュータ 100 の電源が入っていなかったときにいかなる状態も失われているようになる。メモリ 110 は、電源を入れたときに特定の状態（たとえば、すべてのゼロまたはすべての 1 を格納する）となるように構成することができ、あるいは、他の実施形態として、メモリ 110 がランダム値を格納することができる（たとえば、電源が入っている間に、個々のメモリセルがどのような値に安定されるかに関わらず）。それにも関わらず、メモリ 110 は、信頼性のあるデータまたは命令を、電源を入れるときに格納しない。コンピュータシステム全体または単にメモリの起動時に、メモリの内容が幾分ランダムであることに留意されたい。しかし、CPU の電源を入れること、および／または、リセットすることは、通常、メモリの状態を変えない（そのため、メモリの内容は、CPU を単にリセットした後に必ずしもランダムではない）。

40

#### 【0089】

コンピュータ 100 の電源が入れられた後、CPU 102, 104 のうちの 1 つが、最終的に命令の実行を開始する。CPU 102, 104 のうちの 1 つのみが最初に命令の実行を開始することができるか、あるいは他の実施形態として、CPU 102, 104 のうち

50

の1つを、コンピュータのブートを開始するために選択することができる。幅広い種類のアービトレーション機構(arbitration mechanism)のいずれかを使用して、多数のCPUのどれがコンピュータのブートを開始するためのものであるかを決定することができ、これらは、事前に構成された(pre-configured)デフォルトプロセッサ、分散アービトレーション方式(distributed arbitration scheme)、プロセッサバス112に結合されたアービトレーションデバイスまたは構成要素(component)(図示せず)などである。

#### 【0090】

CPUの数、または、どのCPUが命令の実行を開始するかに関わらず、少なくとも1つのCPUが命令の実行を開始する。コンピュータ100の電源がちょうど入れられたとき、命令はCPUのキャッシュメモリに(あるいは、コンピュータ100において存在することができる、他のいかなるキャッシュメモリにも)格納されていない。CPUは命令をBIOS122から得て、これらの命令の実行を開始する。一実施形態では、CPUが、最初に特定のアドレス(たとえば、FFF FFFF 0<sub>16</sub>)のための読み取り要求を、プロセッサバス112上に配置するように構成される。メモリコントローラ106は、CPUが命令の実行を開始するべきである、BIOSブートブロックのアドレス(BIOS122におけるアドレス)により応答する。メモリコントローラ106によって返されたこのアドレスは、リセットベクトル(reset vector)と呼ばれ、この(一般的な)例では、外部ロジックによって提供される。代替実施では、CPUが単に命令を特定の場所(たとえば、00000000 0<sub>16</sub>)から直接取り出すことを開始し、そのため、この場合、リセットベクトルが固定される。

10

20

#### 【0091】

次いで、CPUが、このリセットベクトルで開始して、命令のロードおよび実行を開始する。ロードされた命令はROM120からのものであり、BIOS122、ならびに1つまたは複数のオプションのROMおよび/またはBIOS拡張機能124からの命令を含むことができる。ROM120からのいくつかの命令は、命令がメモリ110に(ROM120、または、大容量記憶デバイス118など、別のデバイスから)ロードされる結果となり、これらが、次いで、CPUによってロードされ、実行される。

#### 【0092】

したがって、オペレーティングシステムの様々な構成要素144がメモリ110へ、ROM120および/または他のデバイス(たとえば、記憶デバイス118)からロードされる。構成要素(component)144は、BIOS122、ならびにオプションのROMおよびBIOS拡張機能(extension)124の一部を含むことができる。OS構成要素144は、ワシントン州レドモンドのMicrosoft Corp.から入手可能なオペレーティングシステムのWindows(登録商標)ファミリのいずれかなど、汎用オペレーティングシステムの選択された構成要素も含むことができる。

30

#### 【0093】

最終的に、トラステッドコア(trusted core)がメモリ110にロードされる。これは、たとえば、BIOS122、オプションのROMまたはBIOS拡張機能124、OS構成要素144または別のアプリケーション(図示せず)における命令に応答して行うことができる。トラステッドコアは、信用できるコード(たとえば、ソフトウェア命令)を指し、これは、コンピュータ100の動作の少なくとも一部を制御し、それ自体をコンピュータ100の特定のハードウェア上で(少なくともある範囲まで)保護する方法を知っているものである。それ自体を保護することにおいて、トラステッドコアは、トラステッドコアの制御下で動作中の他のアプリケーションも保護することができる。トラステッドコアによって提供された保護の量、ならびに、このような保護がトラステッドコアによって提供される方法は、コンピュータ、コンピュータ(またはCPU)のアーキテクチャ、およびトラステッドコアの間で変わる可能性がある。トラステッドコアは、一般的なオペレーティングシステムの機能性のすべて、または、他の実施形態として、選択された機能性のみを含むことができる。トラステッドコアは一般的には、ある方法において暗号により証明され、トラステッドコアの保全性を後に検証できるようにする。たとえば、トラステッ

40

50

ドコアの暗号化措置(cryptographic measure)を、トラステッドコアから抽出(extract)し、トラステッドコアと共に大容量記憶デバイス118上(あるいは、あるリモートデバイス上)に格納することができる。トラステッドコアが後にメモリ110にロードされたとき、コンピュータ100の構成要素が、メモリ110におけるトラステッドコアの暗号化措置を、格納された暗号化措置と比較するために抽出することができ、2つの措置(measure)が合致した場合、トラステッドコアがデバイス118上あるいはメモリ110内にある間に(たとえば、不当なユーザまたはプログラムによって)改変されていないことを安全に保証することができる。

#### 【0094】

例示された例では、抽出された暗号化措置(cryptographic measure)がダイジェスト138に格納される。ダイジェスト138は、トラステッドコアがロードされたときにその暗号化措置を格納するために使用される1つまたは複数のレジスタ(または、他の記憶機構)を指す。1つのそのような手段が「暗号化ダイジェスト(cryptographic digest)」であり、これは、SHA-1(Secure Hash Algorithm 1)など、一方向ハッシュ演算を使用して計算される。暗号化ダイジェストは、ダイジェストされたときに同じハッシュ値(hash value)を生成する第2のプレイメージ(pre-image)(この場合、第2のトラステッドコア)を見つけることが極度に困難であるという特性を有する。よって、ダイジェストレジスタ(digest-register)は、使用中のトラステッドコアを一意に表すものと見なすことができる値を含む。暗号手法の基本的な紹介については、Bruce Schneier著のテキスト「Applied Cryptography: Protocols, Algorithms, and Source Code in C」, John Wiley & Sons, 著作権1994年(または、著作年1996年の第2版)を参照されたい。

#### 【0095】

他の実施形態として、ダイジェスト以外の手段を使用することができる。たとえば、ロジックが、トラステッドコアにデジタル証明書が添付されることを必要とする可能性がある。チップセット(chipset)は、証明書がトラステッドコアイメージに合致することを保証することができ、次いで、証明書、証明書から得られた公開鍵、またはレジスタにおける証明書のダイジェストを保存することができる。

#### 【0096】

最終的に、コンピュータは、動作中のコンピュータのための「信用の根元(root of trust)」を提供する構成要素をロードかつ初期化するための準備ができる。以前のコンピュータにおいて直面した著しい問題は、CPUまたは他のデバイスが不正を働くようにプログラムすることによって、事前に実行したすべてのコードが、トラステッドコアの実行をくつがえす可能性があることである。たとえば、悪質なOSローダは、バスマスクティングコントローラが、短い遅延の後、新しい構成要素を、信用されていないコードをその上に書き込むことによって、くつがえすべきであるように構成することができる。本明細書に記載された本発明は、事前に実行するすべてのコードを信用のあるチェーン(trust chain)から除去する。

#### 【0097】

トラステッドコア(trusted core)は、幅広い種類の方法のいずれにおいても、それ自体を信用できるようにするために動作することができる。トラステッドコアが動作する方法は変わること可能性があり、同じように、トラステッドコアによって提供された安全性または信用可能性の量も変わる可能性がある。図2および図3は、トラステッドコアを実施することができる例示的方法を例示する。しかし、図2および図3は、トラステッドコアを実施することができる方法の例のみを例示し、トラステッドコアを実際には異なる方法において実施することができる。一般に、トラステッドコアは、リング(ring), カーテニング(ceiling)など、コンピュータ構成要素によって提供されるどのような機構も使用して、実行できるようになった後にそれ自体を保護することができる。

#### 【0098】

10

20

30

40

50

本明細書に記載された本発明は、コードの特性を、「信用の根元」を含むものであると限定しないことに留意されたい。このコードが、それ自体を、それが動作する可能性のあるコード、またはそれがプログラムする可能性のあるデバイスから、保護するための手段(CPUメモリコントローラのプログラミングなど)を取ることが予想される。しかし、「信用の根元」を、完全なOS、マイクロカーネル、ハイパーテザ、または、特定の安全性のサービスを提供する、ある小型の構成要素にすることができる。以下で、このような構成要素を「トラステッドコア」と称する。

#### 【0099】

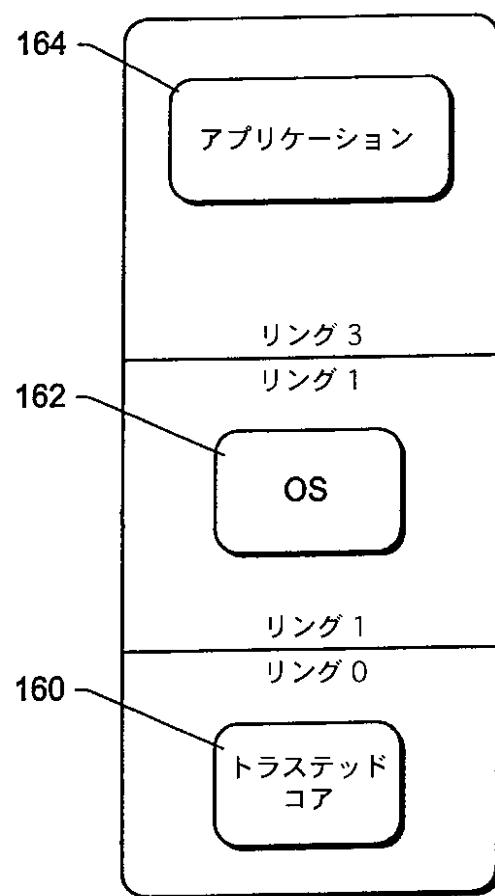

図2では、トラステッドコアが、図1のCPU102, 104の異なる特権レベル(privilege level)(たとえば、x86アーキテクチャプロセッサにおけるリング)を利用することによって実施される。例示された例では、これらの特権レベルがリングと呼ばれるが、異なるプロセッサアーキテクチャを使用する代替実施は、異なる名称を使用することができる。多数のリングが、ソフトウェアが実行することができる、優先順序が付けられたレベルのセットを提供し、これはしばしば4レベル(リング0, 1, 2および3)を含む。リング0は通常、もっとも特権のあるリング(most privileged ring)と呼ばれる。リング0において実行するソフトウェア処理は通常、より特権の少ないリングにおいて実行する処理より多い機能(たとえば、命令)にアクセスすることができる。さらに、特定のリングにおいて実行するプロセッサは、より高い優先順位のリングにおけるコードまたはデータを改変することができない。例示された例では、トラステッドコア160がリング0において実行し、オペレーティングシステム162がリング1において実行し、アプリケーションがリング3において実行する。したがって、トラステッドコア160が、より特権の多いレベルで動作し、オペレーティングシステム162の実行を、このレベルから制御することができる。加えて、トラステッドコア160(リング0において実行)のコードおよび/またはデータを、オペレーティングシステム162(リング1において実行)またはアプリケーション164(リング3において実行)によって直接改変することができない。むしろ、このようないかなる改変も、オペレーティングシステム162またはアプリケーション164が、トラステッドコア160に改変を行うように要求すること(たとえば、メッセージを、トラステッドコア160に送信すること、トラステッドコア160の機能を呼び出すこと、などによる)によって行われなければならない。

#### 【0100】

他の実施形態として、オペレーティングシステムを、トラステッドコア160として動作するメモリ管理構成要素と、OS162として動作するオペレーティングシステムの残りに分離することができる。次いで、トラステッドコア160が、すべてのページマップ(page map)を制御し、したがって、リング3において実行するトラステッドエージェント(trusted agent)を他の構成要素(OS162を含む)から遮蔽(shield)することができる。この代替方法では、追加の制御を(たとえば、図1のメモリコントローラ106において)追加して、トラステッドコアを、リング特権に従わない他のバスマスターから保護する必要もある。

#### 【0101】

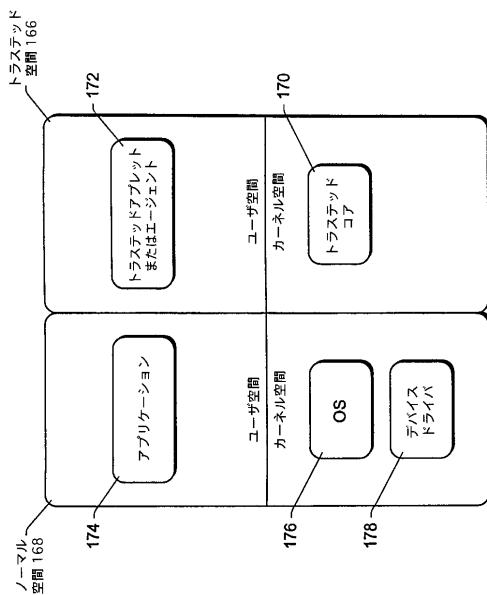

図3では、トラステッドコアが、コンピュータ100内で2つの分離した「空間(space)」を確立することによって実施される。すなわち、トラステッド空間(trusted space)166(保護された並列領域(parallel area)、またはカーテニングされたメモリ(curtained memory)とも呼ばれる)、およびノーマル(信用されていない:untrusted)空間168である。これらの空間を、たとえば、コンピュータ100内の1つまたは複数のアドレス範囲にすることができる。トラステッド空間166もノーマル空間168も、ユーザ空間およびカーネル空間を含み、トラステッドコア170は、トラステッド空間166のカーネル空間において実施される。様々なトラステッドアプレット(trusted applet)、アプリケーション、および/またはエージェントが、トラステッド空間166のユーザ空間内で、トラステッドコア170の制御下で実行することができる。しかし、ノーマル空間168において実行するいかなるアプリケーション174、オペレーティングシステム176

10

20

30

40

50

、またはデバイスドライバ 178 も、トラステッドコア 170 によって、トラステッド空間 166 にアクセスするのを防止される。したがって、トラステッド空間 166 におけるアプリケーションまたはデータに改変を行うことは、トラステッドコア 170 によって承認されない限りできない。

#### 【0102】

図 1 に戻ると、トラステッドコア 146 が 3 つの部分において例示されている。すなわち、プラットフォームトラステッドコア部(platform trusted core portion) 148、コモントラステッドコア部(common trusted core portion) 150、および、トラステッドコアデータ部(trusted core data portion) 152 である。これらの部分 148, 150 および 152 は、メモリ 110 において隣接して配置されるように例示されるが、これらの部分をそのように配置する必要はない。たとえば、異なる部分を、異なる、隣接していない領域に格納することができ、各部の異なるセクションを、異なる、隣接していない領域に格納することができる。他の実施形態として、トラステッドコア 146 が実行時に動作する方法に応じて、これらの部分を、メモリ 110 内で物理的に隣接した場所に配置する必要のある可能性がある(つまり、実際には、RAM の物理的に隣接した場所に格納され、仮想メモリによる別のデバイスにページアウトされない)。

10

#### 【0103】

トラステッドコアデータ部 152 は、メモリ 110 の、トラステッドコアによって使用されたデータを格納するために使用される領域である。プラットフォームトラステッドコア部 148 は、コンピュータ 100 において使用された特定のハードウェアに固有であるコードを含む(たとえば、特定のタイプの CPU、そのタイプのチップセットなど)。コモントラステッドコア部は、トラステッドコアの動作および機能性を実施するが、コンピュータ 100 において使用された特定のハードウェアに固有ではないコードを含む。2 つの部分 148 および 150 を分離することによって、コンピュータ 100 のハードウェアとの対話方法の細部(たとえば、タイマを設定する方法)を、部分 148 によって部分 150 に抽象化することができ、そのため、同じコモン トラステッドコア部を異なるコンピュータ上で使用することができる。たとえば、コモン トラステッドコアコード 150 は、すべてのタイマが同じ方法で設定されたかのように動作することができ、プラットフォームトラステッドコアコード 148 は、コード 150 からの命令を、その下にあるコンピュータ 100 のハードウェアによって実際に理解されるコマンドに変換するように動作する。

20

#### 【0104】

トラステッドコア 146 をメモリ 110 に、同じソース、または他の実施形態として、異なるソースからロードすることができる。例として、プラットフォームトラステッドコア部 148 をメモリ 110 に、コンピュータ 100 のチップセット(チップセットは、バスおよび電子機器を含む、コンピュータのサブシステムの間のインターフェースを提供して、CPU, メモリ, I/O デバイスなどが対話することができるようにする、1 つまたは複数のチップのセットを指し、これは、メモリコントローラ 106, I/O コントローラ 108、および、バス 112 および 114 を含むことができる)からロードすることができ、コモン トラステッドコア部 150 をメモリ 110 に、大容量記憶デバイス 118 からロードすることができる。もう 1 つの例として、1 つの部分 148, 150 または 152 をメモリ 110 に、ネットワークアダプタ 128 から(たとえば、リモートサーバから)ロードすることができ、あるいは、これらの部分をすべてネットワークアダプタ 128 からロードすることができるが異なるソース(たとえば、異なるリモートサーバ)からはロードできない。加えて、1 つまたは複数の部分 148, 150 および 152 の異なる部分を、異なるソースからロードすることができる(たとえば、部分 150 の一部をメモリ 110 に、大容量記憶デバイス 118 からロードすることができ、部分 150 の別の一部をリモートサーバから、ネットワークアダプタ 128 を介してロードすることができる)。

30

#### 【0105】

加えて、各部を、1 つまたは複数のソースからの様々なオーバーレイされた部分を結合することによって、生成することができる。たとえば、第 1 部をあるソース(たとえば、口

40

50

ーカルのディスク)から読み取ることができ、第2部を別のソース(たとえば、ネットワークを介したリモートサーバ)から読み取ることができ、次いで、2つの部分を結合して(たとえば、各部分のビットの排他的論理和を取る)この部分を生成することができる。

#### 【0106】

トラステッドコア146を安全な場所に格納すること、および/または、安全な方法においてメモリ110にロードすることが必要ないことに留意されたい。トラステッドコア146を、公にアクセス可能な(または、半ば公にアクセス可能な)いかなる領域にも格納することができ、これは、大容量記憶デバイス118、ネットワークアダプタ128を介してアクセスされるリモートサーバなどである。むしろ、トラステッドコア146の暗号化措置(cryptographic measure)を、メモリ110にロードした後に(かつ、これが、信用されていないコードによるさらなる修正が可能でないように保護された後に)検証することができる。暗号化措置は、幅広い種類の従来の方法のいずれにおいても生成することができ、トラステッドコアにおけるいかなる変更も暗号化措置において反映されるように設計される。たとえば、不当なユーザが、トラステッドコアの安全性をくつがえすための試みにおいて、命令を削除あるいは修正すること、または、新しい命令を追加することによって、トラステッドコアを改変しようと試みた場合、この改変が暗号化措置において反映される(そのため、後に生成されたいかなる暗号化措置も、先に生成された暗号化措置に合致しないようになり、これは命令における変更による)。一実施態様では、暗号化措置は、トラステッドコアのダイジェスト値を、よく知られているSHA, SHA-1, MD5(メッセージダイジェスト5)などのアルゴリズムに従うなどして生成することによって得られる。10

#### 【0107】

この暗号化措置は、本明細書に記載された安全な初期化プロセス中に生成され、後に挑戦者(challenger)(たとえば、銀行、IT管理者、スマートカードなど)により使用可能となる。ダイジェストの解釈は、いくつかの方法において行うことができる。これは、企業がそのトラステッドコアの予想値をそのwebサイト上で公開するなど、「よく知られた(well known)」値にすることができる。他の実施形態として、企業が、それが書き込む、各トラステッドコアのための証明書を生成し、これを、トラステッドコアと共に出荷する(あるいは、webサイト上で使用可能にする)ことができる。これにより、挑戦者がダイジェストを見て、ダイジェストを「命名する(name)」証明書を求める(あるいは、探す)ことができる。証明書がダイジェストを命名するので、この証明書をコア自体に入れるべきではないことに留意されたい。20

#### 【0108】

本明細書に記載された初期化プロセス(initialization process)は、ユーザが「トラステッドコア」として動作するように試みることができるものを限定するものではなく、ユーザが、実質的にいかなる命令のセットも、トラステッドコアとして動作するように試みることができることに留意されたい。しかし、トラステッドコアが不正に変更された場合、「トラステッドコア」として動作しようと試みている命令(トラステッドコアを不正に変更したもの)は、他の関係者から信用されなくなり、これは、トラステッドコアを不正に変更したものが、異なる暗号化措置を有するようになり、トラステッドコアを不正に変更しないものにアクセス可能である鍵にアクセスできなくなるからである。30

#### 【0109】

本明細書に記載された初期化プロセスにより、当然かつ容易に、コンピュータが、異なるトラステッドコアを逐次、任意の回数で、システムをリブート(re-boot)することなく動作できることにも留意されたい。たとえば、ユーザは、トラステッドコアxの実行を開始し、次いで、トラステッドコアy(これを、トラステッドコアxの異なるバージョン、または、まったく異なるトラステッドコアにすることができる)の実行に切り替え、次いで、トラステッドコアzに切り替える(あるいは、トラステッドコアxに戻る)ことなどができる。

#### 【0110】

50

メモリコントローラ 106 は、トラステッドコア 146 がメモリ 110 にロードされた後、これを、コンピュータ 100 のいかなる先の状態もが初期化プロセスの保全性を損なうことのないような方法において、初期化し、実行を開始できることを保証するように動作する。メモリコントローラ 106 が、トラステッドコアを初期化することができる安全な環境を提供するように動作することに留意されたい。しかし、初期化プロセスが完了した後、トラステッドコア 146 が、それ自体の安全性の責任を負う。加えて、メモリコントローラ 106 は、トラステッドコア 146 によって提供された信用可能性または安全性に関するいかなる保証または確信も生成しない。

#### 【0111】

トラステッドコア 146 の初期化は、トラステッドコア 146 の実行を開始することを指す。この初期化は一般的には、トラステッドコア 146 が全体としてメモリ 110 にロードされた後に起こるが、代替実施態様では、コード 146 のいくつかの部分を、初期化プロセスが起こった後にメモリにロードできるようにすることができます。初期化プロセスは、トラステッドコア初期化命令のセットによって実行され、これは、トラステッドコア 146 の一部である（また、場合によっては、1つまたは複数の部分 148、150 および 152 の一部である）。初期化プロセスによって実行される厳密な動作は、トラステッドコアが動作する特定の方法、ならびに、コンピュータ 100 の特定のハードウェア（たとえば、CPU アーキテクチャ）に基づいて変わる可能性があるが、一般に、トラステッドコアによって提供された保護を確立すること（たとえば、トラステッド空間をセットアップすること）、および、CPU を初期化してこの保護を使用するようにすることを含む。「初期化コード(initialization code)」が行わなければならないことの1つが「リセットベクトル(reset vector)」を提供することであり、これは適所に残され、常に、リセット、開始(initiate)，ホットプラグ追加(hot-plug add)などが行われるいかなるプロセッサをも処理する準備ができている。これを行うことにより、トラステッドコアが、その継続された保全性を、マシンの CPU 構成における深い変更（たとえば、新しいものがオンラインで追加される）に対して保証する。

10

20

#### 【0112】

トラステッドコア 146 の初期化は、CPU 102, 104 のうちの1つによって発行された「トラステッドコア初期化(trusted core initialization)」コマンドに応答して開始する。トラステッドコア初期化コマンドは一般に、コンピュータ 100 のブート中に発行されるが、コンピュータ 100 が完全にブートされている間あるいはその後のいかなるときにも起こる可能性がある。トラステッドコア初期化コマンドは、トラステッドコア初期化をトリガるように設計されており、幅広い種類の方法のいずれにおいても実施することができる。たとえば、このコマンドを、特定のポートへの書き込み、特定のアドレスへの書き込みなどにすることができるが、ポートまたはアドレスは、トラステッドコアが、コアが制御を獲得した後にハードウェアが提供する保護手段がどんなものであれ、それを使用してポートまたはアドレスを保護することができるという特性を有するべきである。これは、トラステッドコアが動作中になった後、信用されていないいかなるコードもこれをメモリから除去したり置き換えることができる、単純なサービス拒絶攻撃に対して、脆弱ではないことを保証するものである。他の実施形態として、このような保護が提供されなかった（たとえば、トラステッドコア初期化コマンドを、ある保護不可能なポートによって呼び出さなければならない）場合、これを「一回実行(run once)」の動作にすることができ、これは、システムがリブートされるまで、その機能を再度実行することを拒絶するものである。しかし、このようなマシンは、トラステッドコアを停止かつ開始するか、あるいは、ブートにつき複数のトラステッドコアを使用するための能力を失う。

30

40

#### 【0113】

一実施態様では、トラステッドコア初期化コマンドが3つのパラメータ、すなわち、開始、コード長およびメモリ長を含む。開始パラメータは、メモリ 110 においてトラステッドコア 146 が開始する場所を指す（たとえば、プラットフォームトラステッドコア部 148 の最初の命令のメモリアドレス）。他の実施形態として、特に、トラステッドコア 1

50

4 6 が物理的に隣接したメモリに位置しない実施形態では、メモリ記述子リスト（ M D L ）を開始パラメータとして識別することができ、メモリコントローラ 1 0 6 に対してどのメモリページがトラステッドコアを含むかを識別する。コード長パラメータは、トラステッドコア 1 4 6 のコードの長さ（たとえば、バイト数）を指す（たとえば、部分 1 4 8 および 1 5 0 の結合であるが、トラステッドコアデータ部 1 5 2 を除く）。メモリ長パラメータは、トラステッドコアの長さ（たとえば、バイト数）を指す（たとえば、すべての 3 つの部分 1 4 8 , 1 5 0 および 1 5 2 の結合）。これらのパラメータが、トラステッドコア初期化コマンドの前に（あるいは、その一部として）、メモリコントローラ 1 0 6 に渡される。一実施態様では、3 つのパラメータが、 C P U 1 0 2 , 1 0 4 のうちの 1 つによって、トラステッドコア初期化コマンドの発行の前に、メモリコントローラ 1 0 6 のパラメータレジスタ 1 5 3 にロードされる。

10

#### 【 0 1 1 4 】

トラステッドコア初期化コマンドを受信すると、メモリコントローラ 1 0 6 がメモリ 1 1 0 を、すべての C P U 1 0 2 , 1 0 4 およびコンピュータ 1 0 0 における他のいかなるバスマスター (bus master) からも保護する。 C P U 1 0 2 , 1 0 4 、ならびに、コンピュータ 1 0 0 における他のいかなるバスマスターも、メモリ 1 1 0 に直接アクセスできず、むしろメモリコントローラ 1 0 6 を介してメモリ 1 1 0 にアクセスしなければならないことを考えると、メモリコントローラ 1 0 6 が容易にメモリ 1 1 0 を C P U およびバスマスターから保護することができる。メモリ 1 1 0 を保護することによって、メモリコントローラ 1 0 6 は、他のコード（たとえば、 C P U によって実行中であるか、あるいは別のバスマスターを制御しているもの）が、トラステッドコア初期化プロセスを干渉しないことを保証する。メモリ 1 1 0 の保護において、メモリコントローラ 1 0 6 は最初に、メモリ 1 1 0 へのアクセスを、メモリリフレッシュコントローラ（図示せず）からのメモリリフレッシュ信号のみにすることができる、これは、 D R A M をリフレッシュさせ、その状態を維持することができる。

20

#### 【 0 1 1 5 】

要素化されたメモリ (factored memory)、つまり、多数のメモリコントローラを有する多数のメモリのブロックを有するマシンでは、多数の異なる手法を使用することができる。1 つの手法では、多数のメモリコントローラが互いに調整して、トラステッドコア初期化オペレータをすべてのメモリに渡って適用する。もう 1 つの手法では、トラステッドコア初期化を行うために選択されたメモリコントローラ / メモリが、そのすべてを行い（そのため、トラステッドコア全体が 1 つの「バンク」にロードされる）、他のメモリコントローラがこれを無視する。すべてのトラステッドコアが単一の保護メモリバンクにあるので、他の動作は重要ではない。選択されたメモリコントローラがなお、すべての C P U の挙動を強制し、そのため、プラットフォームのハードウェアが、これを行うことができるようセットアップされる。

30

#### 【 0 1 1 6 】

メモリコントローラ 1 0 6 における制御ロジック 1 3 6 も、トラステッドコア初期化ビット 1 5 4 を、メモリコントローラ 1 0 6 の安全部分 1 5 6 内に設定する。この安全部分 1 5 6 は、制御ロジック 1 3 6 のみが安全部分 1 5 6 内のレジスタおよび / またはメモリにアクセスできることにおいて安全である。安全部分 1 5 6 は、メモリコントローラ 1 0 6 の外部のコンピュータ 1 0 0 における他の構成要素に対して可視にすることはできず、あるいは、他の実施形態として、制御ロジック 1 3 6 が単に、安全部分 1 5 6 内のいかなるレジスタまたはメモリにもアクセスしようと試みる、メモリコントローラ 1 0 6 で受信されたいかなるコマンドも、無視（あるいは、拒絶）することができる。トラステッドコア初期化ビット 1 5 4 により、制御ロジック 1 3 6 は、トラステッドコア初期化プロセスが進行中であるかどうかを知ることができ、ビット 1 5 4 の使用については以下でより詳細に論じる。

40

#### 【 0 1 1 7 】

メモリコントローラ 1 0 6 は、様々な異なる方法においてメモリ 1 1 0 を保護することが

50

できる。一実施態様では、メモリコントローラ106は、CPU102, 104が読み取りまたは書き込み要求をプロセッサバス112上に発行するのを防止し、それにより、CPU102, 104がメモリ110にアクセスするのを防止する。CPU102, 104をバスから離しておく方法は、CPU102, 104およびプロセッサバス112のアーキテクチャに基づいて変わる（たとえば、あるIntelアーキテクチャの実施では、CPUが読み取りおよび書き込み要求をバス上に発行するのを防止することができ、これは、BNR#(Block Next Request)信号をプロセッサバス112上にアサートすることによって、あるいは、各CPUがリセットされるまでその動作を停止する停止（たとえば、HLT）コマンドをCPUに発行することによって行われる）。CPU102, 104は最終的に、再度読み取りおよび書き込み要求をプロセッサバス112上に発行することができるようになるので、制御ロジック136も、メモリコントローラ106がCPU102, 104からメモリ110におけるトラステッドコア146のアドレス範囲に受信するすべての要求を比較し、メモリコントローラ106がCPU102, 104からこのトラステッドコア初期化プロセス中に受信する（たとえば、ビット154セットによる）、このアドレス範囲内であるいかなる要求も、従来の方法において受け入れられ、応答されるが、このアドレス範囲内でないか、あるいはCPU102, 104以外の構成要素からのいかなる要求も拒絶される（たとえば、メモリコントローラ106が、要求を確認することを拒絶することができる、要求を否定することができる、など）。他の実施形態として、このアドレス範囲内でなく受信された要求を許可することができるが、このようなメモリの領域が保護されていないことを理解することを伴う。

10

20

#### 【0118】

メモリコントローラ106は、I/Oバス114上の他のバスマスターがメモリ110にアクセスすることも防止する。加えて、メモリコントローラ106は、I/Oバス114上の他のバスマスターが（たとえば、CPU内あるいはバス112上の）キャッシュメモリに影響を与えることを、このようないかなるトランザクションをもバス112上に発行しないことなどによって、防止することができる。たとえば、メモリコントローラ106が、I/Oコントローラ108に信号をI/Oバス114上にアサートさせることができ、これにより、いかなるバスマスターもが読み取りおよび書き込み要求をバス114上に発行するのを防止する。もう1つの例として、メモリコントローラ106が単に、I/Oコントローラ108から受信するいかなるメモリアクセス要求も無視することができ、これは、I/Oインターフェース134にこのような要求を否定させ、このような要求の受け入れまたは確認を拒絶されることなどによって行う。メモリ110へのアクセスを防止することは、CPUのアクセスおよびI/Oバスマスターのアクセスのための類似の様式において実施することができるが、初期化プロセス中に、CPUのアクセスが可能とされても、I/Oバスマスターのアクセスが可能とされないことに留意されたい。

30

#### 【0119】

メモリコントローラ106は、トラステッドコア初期化コマンドを受信すると、即時にメモリ110を保護することができ、あるいは、他の実施形態として、メモリ110を保護する前に、ある期間、あるいは、ある他の動作が発生するまで待機することができる。たとえば、特定のバスマスターが、トラステッドコア初期化コマンドが受信されたときに、長いDMA転送の処理中である可能性があり、メモリコントローラ106が、DMA転送を完了させることを選択することができる。メモリ110の保護を即時に行なうことはできないが、トラステッドコア初期化プロセスはメモリ110が保護されるまで進行しない。

40

#### 【0120】

メモリ110が保護された後、制御ロジック136が、トラステッドコア146に基づいてダイジェスト値を生成する。他の実施形態として、専用の暗号化プロセッサなど、もう1つの構成要素（図示せず）が、ダイジェスト値を生成するために一時的にメモリ110にアクセスできるようにすることができる（あるいは、ダイジェストを暗号化プロセッサにおいて保持することができ、これは、暗号化プロセッサが私的にメモリコントローラと共に作業して、ダイジェスト操作を、CPUが初期化プロセスを実行中である（かつ、暗

50

号化プロセッサのこの要求を行う、信用されていないソフトウェアによってだますことができない)ときにはのみ実行する限りである)。しかし、このアクセスは、暗号化プロセッサがメモリ110からしか読み取ることができないようにするなど、限定することができる。このダイジェストは、上述したような同じ暗号化機構を使用して生成される。次いで、制御ロジック136が、生成されたダイジェスト値をダイジェスト138として、メモリコントローラ106の安全部分156に格納する。次いで、ダイジェスト138を、トラステッドコア146による後続の証明および/または認証のために使用することができる。

#### 【0121】

次いで、制御ロジック136が、リセットベクトルを新しいリセットベクトルにマップし、これは初期化ベクトルと呼ばれ、メモリコントローラ106がプロセッサバス112上の特定のアドレス(たとえば、FFFFFFF0<sub>16</sub>)のための次の読み取り要求に、初期化ベクトルにより応答するようにする。CPUが常に、(リセットベクトル取り出し手順によって供給された間接化技法を使用するのではなく)分かっている場所から実行を開始する状況では、制御ロジック136が命令を、メモリサブシステムから取り出された命令の最初のものまたは少数のものとして発行するように構成し、これにより、CPUに、トラステッドコア(たとえば、JUMP動作)の開始時に命令の実行を開始させるか、あるいは、他の実施形態として、トラステッドコアを再マップさせて、固定プロセッサリセットベクトルに現れるようにする。この初期化ベクトルは、トラステッドコア146の最初のアドレスである。一実施態様では、このマッピングが、制御ロジック136によって実施され、トラステッドコア146の開始場所(たとえば、トラステッドコア初期化コマンドのパラメータとして受信されたもの)をリセットベクトル140として書き込む。メモリコントローラ106が、プロセッサバス112上の特定のアドレス(たとえば、FFFFFFF0<sub>16</sub>)のための読み取り要求を受信するときは、制御ロジック136が安全部分156のビット154をチェックする。このビットが設定された場合、マップされたリセットベクトル140が、要求側のCPUに、リセットベクトルとして返される。しかし、このビットが設定されていなかった場合、最初のBIOSブートブロックアドレスが要求側のCPUに返される。

#### 【0122】

次いで、制御ロジック136が、リセット信号をプロセッサバス112上のCPUにアサートする。多数のCPUがプロセッサバス112上にある状況では、リセット信号がすべてのCPUにアサートされる(他の実施形態として、リセット信号を单一のCPUに向けて送ることができる)。リセット信号がアサートされる方法(および、リセット信号自体の特性)は、CPU102, 104およびプロセッサバス112のアーキテクチャに基づいて変わる可能性がある(たとえば、あるIntelアーキテクチャの実施では、プロセッサバス112上のすべてのCPUを、RESET#信号をプロセッサバス112上にアサートすることによってリセットすることができる)。

#### 【0123】

他の実施形態として、他の機構を使用して、プロセッサバス112上のCPUをリセットすることができる。CPUをリセットする目的は、CPUのその状態(たとえば、CPUのレジスタ、キャッシュ、バッファなどの内に存在する可能性のある、すべての命令およびデータ)をクリアして、その以前の状態がトラステッドコア初期化プロセスの実行保全性を損なう可能性のないようにすることである。たとえば、CPUのキャッシュに格納されている不当なアプリケーションの命令は、トラステッドコア初期化プロセスの保全性を損なうことができない。

#### 【0124】

プロセッサバス112上のCPUをリセットすることに加えて、プロセッサバス112上でメモリを含む、他のいかなるキャッシュメモリまたは他のデバイスもリセットされる。たとえば、追加のL3キャッシュ(図示せず)もプロセッサバス112に結合することができ、この場合、制御ロジック136がL3キャッシュならびにCPUをリセットする。

10

20

30

40

50

プロセッサバス 112 上のこれらの追加のキャッシュメモリまたは他のデバイスは、様々な方法のいずれにおいてもリセットすることができ、これらは、ランダム値をメモリに書き込むこと、ゼロまたは 1 の文字列をメモリに書き込むこと、電力をメモリから除去すること（たとえば、一時的に DRAM をリフレッシュしないこと）、特定のバストランザクション (specific bus transaction) を発行してキャッシュ全体または特定のキャッシュ線エントリ (specific cache-line entry) を無効にすることなどである。

#### 【0125】

CPU102, 104（および、プロセッサバス 112 上の他のいかなるキャッシュまたはデバイス（メモリコントローラ 106 を除く））をリセットした後、メモリコントローラ 106 により、プロセッサバス 112 上の CPU の 1 つがメモリ 110 にアクセスできるようになる。例示された例では、CPU102, 104 のいずれもが、最初にメモリ 110 にアクセスできるようになることができる（が、ただ 1 つのみが可能とされる）。メモリコントローラ 106 は、多数のプロセッサのうちのどれがメモリ 110 にアクセスできるようになるかを、様々な方法のうちのいずれにおいても決定することができ、これらは、ある所定の設定、ランダム決定、ある外部の（あるいは、CPU 内部の）バスアービトレーション機構が決定できるようにすることなどである。

#### 【0126】

考察のため、メモリコントローラ 106 が、CPU102 がメモリ 110 にアクセスできるようになると仮定する。次いで、メモリコントローラ 106 は、CPU102 がプロセッサバス 112 にアクセスできるようになると（他のすべての CPU104 はなお、プロセッサバス 112 にアクセスするのを防止される）。CPU がリセットされた後、CPU は、そのいかなるキャッシュまたはバッファにおいても命令を有していない（あるいは、少なくとも、CPU が読み取る命令またはデータがない）ようになる。したがって、CPU102 は、実行するための命令を、プロセッサバス 112 上で特定のアドレス（たとえば、FFF FFFF 0<sub>16</sub>）をアサートすることによって要求する。メモリコントローラ 106 がこの要求を受信し、制御ロジック 136 が、トラステッドコア初期化プロセスピット 154 が設定されていることを決定し、そのため、メモリコントローラ 106 がリセットベクトル 140 を CPU102 に返す。特定のアドレス（たとえば、FFF FFFF 0<sub>16</sub>）を受信すると、制御ロジックが追加のプロセッサ毎のベクトルビット 158 を設定する。このビット 158 により、制御ロジック 136 が、別の特定のアドレス（たとえば、FFF FFFF 0<sub>16</sub>）が受信された場合に、リセットベクトル 140 がすでに別のプロセッサに返されていることを知ることができる。ビット 158 の使用については以下でより詳細に論じる。

#### 【0127】

リセットベクトル 140 を受信すると、CPU102 は、プロセッサバス 112 上に、リセットベクトル 140 におけるメモリアドレスのための読み取り要求を発行し、これはトラステッドコア 146 における最初の命令である（また、トラステッドコア初期化プロセスにおける最初の命令である）。したがって、CPU102 が、トラステッドコアコード 146 の実行を開始する。CPU102 がリセットされたので、先に CPU102 にロードされた命令（たとえば、不当なコード）が、トラステッドコア 146 のその実行に影響を与えることはできない。加えて、他のすべてのバスマスターがメモリ 110 にアクセスすることが防止されるので、これらが、CPU102 によってメモリ 110 から取り込みかつ実行中のコード 146 を改変することはできない。

#### 【0128】

CPU102 は、トラステッドコアコード 146 の取り込みおよび実行を継続し、これにより、コンピュータ 100 においてトラステッドコアを初期化する。上述のように、トラステッドコアが初期化される厳密な方法は、コンピュータ 100 のアーキテクチャ、CPU102, 104、実施中のトラステッドコアのタイプなどに基づいて変わる可能性がある。この初期化プロセスの一部として、トラステッドコア 146 が多数のプロセッサをサポートする場合、追加の CPU 開始ベクトルがリセットベクトル 142 としてロードされ

10

20

30

40

50

る。この追加の C P U 開始ベクトルは、コード 1 4 6 において、追加のプロセッサが命令の実行を開始した場合に追加の命令が取り込まれるメモリアドレスを識別する。この第 2 のリセットベクトルを使用して、たとえば、追加のプロセッサに、トラステッドコアにおいて、トラステッドコア 1 4 6 の開始ではない他のところ（たとえば、コード 1 4 6 のトラステッドコア初期化部分の開始以外）で命令の実行を開始させることができる。しかし、他の C P U は、「初期化の終了(end of initialization)」まで動作することができないので、1 4 2 のベクトルは「初期化の終了」後まで使用されない。

#### 【 0 1 2 9 】

最終的に、トラステッドコア初期化プロセスが完了し、「初期化の終了」コマンドが C P U 1 0 2 によって発行される。初期化の終了コマンドを、上述のトラステッドコア初期化コマンドに類似した、様々な方法のいずれにおいてもアサートすることができる。初期化の終了コマンドを受信すると、メモリコントローラ 1 0 6 により、プロセッサバス 1 1 2 上のすべての残りの C P U 1 0 4 がメモリ 1 1 0 にアクセスできるようになる。これらの各 C P U 1 0 4 はリセットされており、それらのキャッシュまたはバッファのいずれにおいても命令を有していない（あるいは、少なくとも、有効な命令がない）ようになる。したがって、各 C P U 1 0 4 は、命令を実行するように、プロセッサバス 1 1 2 上で特定のアドレス（たとえば、F F F F F F F 0<sub>16</sub>）をアサートすることによって要求する。メモリコントローラ 1 0 6 がこれらの要求を受信し、制御ロジック 1 3 6 が、追加のプロセッサベクトルビット 1 5 8 が設定されていることを決定し、そのため、メモリコントローラ 1 0 6 がリセットベクトル 1 4 2 を各 C P U 1 0 4 に返す。10

#### 【 0 1 3 0 】

次いで、制御ロジック 1 3 6 は、トラステッドコア初期化プロセスが完了したときトラステッドコア初期化ビット 1 5 4 をクリアする。メモリコントローラ 1 0 6 は、他のバスマスターがメモリ 1 1 0 にアクセスするのを防止することもやめる。したがって、別のバスマスターからの不当なコードに対するいかなる追加の保護も、メモリコントローラ 1 0 6 ではなくトラステッドコア 1 4 6 の実行によって防止されるものである。20

#### 【 0 1 3 1 】

各 C P U 1 0 4 は、リセットベクトル 1 4 2 を受信すると、プロセッサバス 1 1 2 上に、リセットベクトル 1 4 2 におけるメモリアドレスのための読み取り要求を発行し、これは、トラステッドコア 1 4 6 における命令である。したがって、各 C P U 1 0 4 は、トラステッドコアコード 1 4 6 における命令の実行を開始する。各 C P U 1 0 4 がリセットされると、先に C P U 1 0 4 にロードされた命令（たとえば、不当なコード）は、トラステッドコア 1 4 6 のその実行に影響を与えることはできない。30

#### 【 0 1 3 2 】

一実施態様では、1つまたは複数の C P U 1 0 2 , 1 0 4 が、正しく機能するために、マイクロコードがそれにロードされることを必要とする可能性がある。このマイクロコードは、たとえば、C P U におけるエラーまたは他のバグを修正し、C P U の固有の命令セットとは異なる命令セットを露出することができます。このマイクロコードを、トラステッドコア 1 4 6 に（たとえば、トラステッドコアデータ部 1 5 2 において）含めることができ、命令を、トラステッドコア初期化プロセスに含めて、マイクロコードを適切な C P U にロードすることができる。加えて、マイクロコードが本物であることを検証することができ、これは、ダイジェストを計算し、これをマイクロコード内で証明されたダイジェスト（たとえば、マイクロコードの作成者または配布者によってそこに配置されたもの）に対して比較して、このマイクロコードが、マイクロコードの配布者によって署名された以後に改変されていないことを保証することなどによる。40

#### 【 0 1 3 3 】

一実施態様では、メモリコントローラ 1 0 6 は、トラステッドコア初期化コマンドに応答して、以下の保証を提供する。

- ・メモリに対するすべての I / O アクセスが停止する。リフレッシュコントローラおよび C P U （リセットされた後）を除き、どの構成要素もメモリにアクセスできない。

1020304050

- ・トラステッドコアの暗号化措置は、メモリに対するI/Oアクセスが停止した後に計算される。

- ・どのCPUも、リセットされた後まで再起動できず、メモリにアクセスできない。

- ・すべてのCPUは、トラステッドコアコードにおける2つの場所のうちの一方で命令の実行を開始し、これらの場所が、トラステッドコアコードから設定される。

- ・CPUのうちの1つのみが、2つの場所のうちの一方で命令の実行を開始し、他のものはすべて、トラステッドコア初期化プロセスの終了まで待機し、2つの場所のうちの他方で命令の実行を開始する。

- ・メモリに対するI/Oアクセスは、トラステッドコア初期化プロセスが完了するまで可能にされない。

10

#### 【0134】

加えて、メモリコントローラ106は、いかなる割り込みもインターフェーストかつ禁ずるように動作することもできる。たとえば、メモリコントローラ106は、コンピュータ100のための割り込みコントローラを含むか、あるいは他の実施形態としてそれと通信することができる。トラステッドコア初期化プロセス中に受信されたいかなる割り込みも禁ずることができる。他の実施形態として、メモリコントローラ106が割り込みに関与することができない（たとえば、CPU102, 104がリセットされ、メモリコントローラ106およびトラステッドコア146によって、命令を得るためのそれらの能力が制限されるため）。

#### 【0135】

加えて、ある実施形態では、トラステッドコア初期化プロセスが、トラステッドコアの保護あるいはカーテニングされた空間内である、メモリのある領域（実および／または仮想領域のいずれか）を確立する。トラステッドコアの動作中に、トラステッドコアは、その保護された空間内で実行中のトラステッドアプリケーションのみが、その保護された空間内の他のメモリアドレスにアクセスできることを保証するように動作する。これらの実施形態では、メモリコントローラ106のすべての制御（たとえば、パラメータレジスタ153など、コントローラ106のアドレス指定可能な部分）は、保護された空間内に含まれる。加えて、トラステッドコア初期化コマンドが発行される機構（たとえば、特定のレジスタアドレス、特定のポートなど）も保護された空間に含まれ、信用できないコードがトラステッドコア初期化コマンドを再発行するのを防止する。

20

#### 【0136】

ある実施態様では、CPU102, 104が2つの動作モード、すなわち、実モード(ready mode)および保護モード(protected mode)をサポートする。実モードは、前のCPU（たとえば、Intel 8086プロセッサ）のプログラミング環境を提供することを指し、保護モードは、CPUのすべての命令およびアーキテクチャの特徴を使用可能にする。これらの実施態様では、CPU102, 104が、電源が入れられたときに（かつ、RESET#信号に応答して）、実モードに初期化される。トラステッドコア初期化プロセスが開始し、これは、各CPUについて、そのCPUを保護モードに移行し、次いでメモリページングをオンにすることによって行う（メモリページングは、仮想メモリを指し、メモリの「ページ」をCPUによって参照することができ、メモリ110と別の記憶デバイス（たとえば、デバイス118）の間で必要とされたときにスワップすることができる）。したがって、トラステッドコア初期化プロセスにおいて、リセットされ、メモリへのアクセスが許可される追加のCPUについて（最初のCPUの後）、これらが実モードにおいて、保護モードおよびオンにされたページングに移行されるために十分長く動作することができることに配慮するべきである。これは、たとえば、追加のプロセッサ開始ベクトル（リセットベクトル142）の選択における配慮によって実施することができる。

30

#### 【0137】

また、トラステッドコアの外部のコードが、強制のプロセッサリセットを構成した場合（これはしばしばプログラムにより可能であり、一般的にはPCクラスのマシンで可能である）、プロセッサは、動作中のコアを潜在的にくつがえす可能性のあるコードではなく、

40

50

トラステッドコアを実行することによって起動することにも留意されたい。この場合、そのコアは、これを例外条件として処理することを選択し、すべての既存の内部状態を破棄する（メモリをクリアする）ことができ、あるいは、実行を継続するための動作を取ることができる（たとえば、プロセッサのリセット前に実施されていたCPU保護プロファイルを再ロードする）。

#### 【0138】

トラステッドコア初期化プロセスには、プロセッサバス112においていかなる追加のバストランザクションも必要ではなく、CPU102, 104における追加のピン、または、CPU102, 104への他のこのような修正も必要ではないことに留意されたい。むしろ、初期化プロセスがメモリコントローラにおいて（たとえば、チップセットにおいて）実施され、それによりCPUへのいかなる修正の必要性も防止される。10

#### 【0139】

本明細書では、主としてコンピュータのブート中に実行されるものとして論じたが、トラステッドコア初期化プロセスを異なる時点で実行することができる。たとえば、トラステッドコアが動作することを必要とするアプリケーションが実行される（たとえば、ユーザが、保護される必要のあるマルチメディアコンテンツをダウンロードしようとする）まで、トラステッドコアをメモリ110にロードすることができず、トラステッドコア初期化コマンドを発行することができない。加えて、トラステッドコア初期化プロセスを、多くの回数繰り返すことができる。例として、トラステッドコアコードは、トラステッドコアの実行を終了する「トラステッドコアを終了させる(terminate trusted core)」コマンドを有している可能性がある。しかし、トラステッドコアを、後の時点で再度メモリ110にロードすることができ（それが実際に実行終了の一部として除去されたかのように）、トラステッドコア初期化プロセスを、トラステッドコアコードが再度実行を開始するため繰り返すことができる。また、多数の異なるトラステッドコアを、一度に1つずつ、交互に動作することができる。20

#### 【0140】

加えて、トラステッドコア初期化プロセスが完了し、他のCPUがメモリにアクセスできるようにされた後、これらの追加のCPUが、トラステッドコア初期化プロセスが開始するときにコンピュータにおいて存在している必要がないことに留意されたい。例として、コンピュータは、CPUを「ホットプラグ(hot-plug)」する（コンピュータの動作中にCPUをコンピュータに追加する）ための能力をサポートすることができる。このような新たに追加されたいかなるCPUもメモリにアクセスすることができ、命令の実行を追加のプロセッサリセットベクトルで開始する。30

#### 【0141】

図1は、単一のメモリコントローラ106がメモリ110へのアクセスを制御する例示的アーキテクチャを例示する。他の実施形態として、トラステッドコア初期化プロセスを、多数のメモリコントローラがあるアーキテクチャにおいて実施することができる。

#### 【0142】

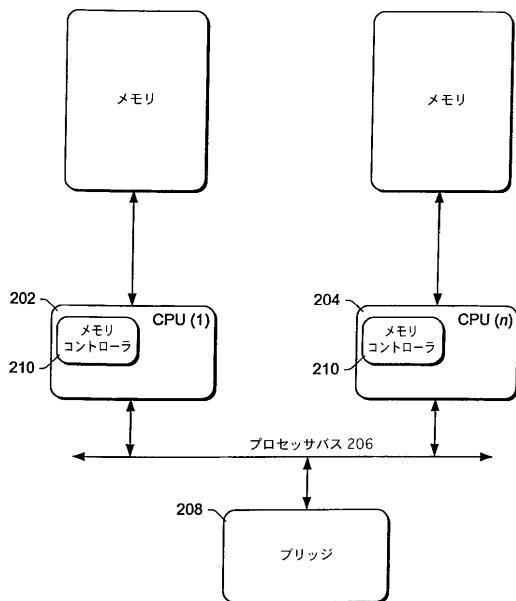

図4は、本発明のある実施形態による、分散メモリコントローラを使用した例示的コンピュータアーキテクチャを例示する。コンピュータ200は、プロセッサバス206に結合された多数( $m$ )のCPU202, 204を含むように例示される。CPU202, 204は、様々なI/O構成要素（図示せず）と、ブリッジ208を介して通信する。加えて、各CPU202, 204はメモリコントローラ210を含む。個別のメモリコントローラ210は、分散メモリコントローラアーキテクチャを実施し、これは、図1のメモリコントローラ106に類似した機能を実行する。ただし、個別のコントローラ210は多数のCPUに渡って分散している。分散メモリコントローラアーキテクチャは、幅広い種類の従来の方法のいずれにおいても実施することができ、追加の結合部（図示せず）を個別のメモリコントローラ210の間に含めて、通信をメモリコントローラ210の間で渡すことができるようになることができる（たとえば、個別のメモリコントローラ210の同期化のため）。4050

**【 0 1 4 3 】**

図4の例では、各CPUは、それ自体の直接接続されたメモリを含む。コンピュータ200に含まれたバスロジックおよびプロトコルは、各CPUによる全体のメモリサブシステムのビューがコヒーレントの状態であることを保証する。このようなメモリアーキテクチャはしばしば、キャッシュコヒーレント不均等メモリアクセスシステム(CC-NUMA)と呼ばれる。他の実施形態として、それ自体の接続されたメモリを有する各CPUではなく、メモリコントローラを多数のCPUの間に分散させて、単一の共有システムメモリにアクセスすることができる。

**【 0 1 4 4 】**

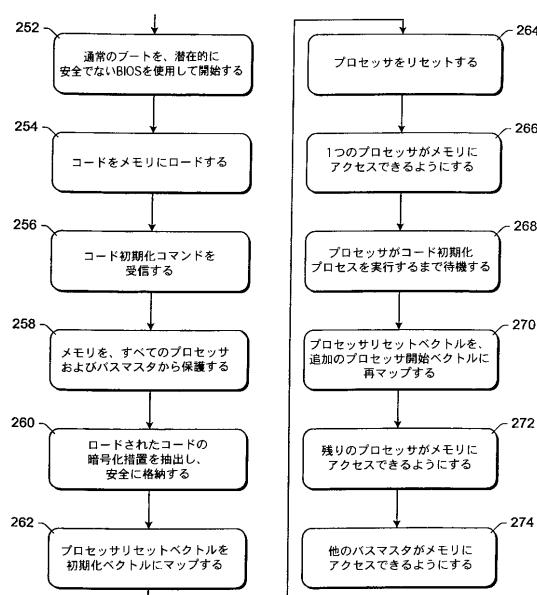

図5は、本発明のある実施形態による、コード初期化プロセスのための例示的処理を例示する流れ図である。図5の処理は、図1のコンピュータ100または図4のコンピュータ200など、コンピュータによって実施され、ソフトウェアにおいて実施することができる。図5の処理を、トラステッドコア初期化プロセス、または、他の実施形態として、他のコードのための初期化プロセスのために使用することができる。

10

**【 0 1 4 5 】**

最初に、コンピュータのための通常のブート処理が、必ずしも安全ではないBIOSを使用して開始される(動作252)。最終的に、コードがメモリにロードされ(動作254)、コード初期化コマンドが受信される(動作256)。コード初期化コマンドに応答して、メモリがすべてのプロセッサおよびバスマスターから保護される(動作258)。次いで、メモリにおけるコードの暗号化措置が抽出され、安全な場所に格納される(動作260)。次いで、プロセッサリセットベクトルが、メモリにおけるコードの開始など、初期化ベクトルにマップされる(動作262)。

20

**【 0 1 4 6 】**

プロセッサリセットベクトルが初期化ベクトルにマップされた後、すべてのプロセッサはリセットされ(動作264)、プロセッサのうちの1つがメモリにアクセスできるようになる(動作266)。次いで、処理は、メモリにアクセスできるようにされたプロセッサがメモリからコード初期化プロセスを実行するまで待機する(動作268)。コード初期化プロセスの終了が信号により通知され、これは、たとえば、コード初期化プロセスを実行するプロセッサから発行されたコマンドによる。コード初期化プロセスが終了した後、プロセッサリセットベクトルは追加のプロセッサ開始ベクトルに再マップされる(動作270)。次いで、コンピュータにおける他のいかなるプロセッサもメモリにアクセスできるようになり(動作272)、コンピュータにおける他のいかなるバスマスターもメモリにアクセスできるようになる(動作274)。

30

**【 0 1 4 7 】**

本明細書の考察では、本発明の実施形態を、1つまたは複数の従来のプロセッサまたはコントローラ(たとえば、図1の制御ロジック136)によって実行されるプログラムモジュールまたはコードなど、一般にプロセッサ実行可能命令に関して記載してある。一般に、プログラムモジュールまたはコードは、ルーチン、プログラム、オブジェクト、コンポーネント、データ構造などを含み、これらが特定のタスクを実行し、あるいは、特定の抽象データ型を実施する。分散環境(distributed environment)では、プログラムモジュールまたはコードは、多数のメモリ記憶デバイスに位置することができる。

40

**【 0 1 4 8 】**

他の実施形態として、本発明の実施形態を、ハードウェア、または、ハードウェア、ソフトウェアおよび/またはファームウェアの組み合わせにおいて実施することができる。たとえば、本発明のすべてまたは一部を、1つまたは複数の特定用途向け集積回路(ASSIC)またはプログラマブルロジックデバイス(PLD)において実施することができる。

**【 0 1 4 9 】**

コンピューティングデバイス(図1のデバイス100または図4のデバイス200など)は、一般的には、少なくともある形式のコンピュータ可読媒体を含む。コンピュータ可読媒体は、コンピューティングデバイスによってアクセスすることができる、いかなる使用

50

可能な媒体にすることもできる。例として、限定ではなく、コンピュータ可読媒体は、コンピュータ記憶媒体および通信媒体を含むことができる。コンピュータ記憶媒体は、揮発性および不揮発性、取外し可能および取外し不能な媒体であって、情報の格納のためのいずれかの方法または技術において実施されたものを含む。これら情報は、コンピュータ可読命令、データ構造、プログラムモジュールまたは他のデータなどである。コンピュータ記憶媒体には、RAM、ROM、EEPROM、フラッシュメモリまたは他のメモリ技術、CD-ROM、デジタル多用途ディスク(DVD)または他の光学記憶装置、磁気カセット、磁気テープ、磁気ディスク記憶装置または他の磁気記憶デバイス、または、所望の情報を格納するために使用することができ、コンピューティングデバイスによってアクセスすることができる、他のいかなる媒体もが含まれるが、これらに限定されるものではない。通信媒体は、一般的には、コンピュータ可読命令、データ構造、プログラムモジュールまたは他のデータを、搬送波などの変調データ信号または他の移送機構において実施し、いかなる情報送達媒体をも含む。「変調データ信号(modulate data signal)」という用語は、1つまたは複数のその特性セットを有するか、あるいは、信号において情報を符号化するような方法において変更された信号を意味する。例として、限定ではなく、通信媒体には、有線ネットワークまたは直接有線接続などの有線媒体、および、音波、RF、赤外線および他の無線媒体などの無線媒体が含まれる。上記のいかなるものの組み合わせもコンピュータ可読媒体の範囲内に含まれるべきである。

## 【0150】

例示のため、オペレーティングシステムなど、プログラムおよび他の実行可能プログラム構成要素は、本明細書において離散的ブロック(discrete block)として例示したが、このようなプログラムおよび構成要素が様々な時点でコンピュータの異なる記憶構成要素において存在し、コンピュータのデータプロセッサによって実行されることを理解されたい。

## 【0151】

(むすび)

上記の説明は、構造上の特徴および/または方法上の動作に特有である言語を使用したが、付属の特許請求の範囲において定義された本発明については、記載された特定の特徴または動作に限定されないことを理解されたい。むしろ、特定の特徴および動作は、本発明を実施する例示的形式として開示したものである。

## 【図面の簡単な説明】

【図1】本発明の一実施形態によるコンピュータを示すブロック図である。

【図2】トラステッドコアを実現する手法を示す図である。

【図3】トラステッドコアを実現する手法を示す図である。

【図4】本発明の一実施形態による、分散メモリコントローラを使用したコンピュータアーキテクチャを示す図である。

【図5】本発明の一実施形態による、コード初期化プロセスを示す流れ図である。

## 【符号の説明】

102, 104, 202, 204 C P U

106, 210 メモリコントローラ

110 メモリ

112, 206 プロセッサバス

114 I/Oバス

118 大容量記憶デバイス

120 ROM

122 BIOS

124 オプションのROM/BIOS拡張

130 プロセッサバスインターフェース

132 メモリインターフェース

136 制御ロジック

138 ダイジェスト

10

20

30

40

50

140, 142 リセットベクトル

145 初期化ビット

146, 160, 170 トラステッドコア

158 ベクトルビット

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 ブライアン ウィルマン

アメリカ合衆国 98034 ワシントン州 カークランド 80 プレイス ノースイースト

10901

合議体

審判長 赤川 誠一

審判官 宮司 卓佳

審判官 鈴木 匡明