(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-54069

(P2019-54069A)

(43) 公開日 平成31年4月4日(2019.4.4)

(51) Int.Cl.

H01L 25/07 (2006.01)

H01L 25/18 (2006.01)

H01L 23/36 (2006.01)

F 1

H01L 25/04

H01L 23/36

C C

テーマコード(参考)

5 F 1 3 6

審査請求 未請求 請求項の数 10 O L (全 11 頁)

(21) 出願番号

(22) 出願日

特願2017-176262 (P2017-176262)

平成29年9月14日 (2017.9.14)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

317011920

(71) 出願人 東芝デバイス&ストレージ株式会社

東京都港区芝浦一丁目1番1号

100119035

(74) 代理人 弁理士 池上 徹真

100141036

(74) 代理人 弁理士 須藤 章

100088487

(74) 代理人 弁理士 松山 允之

刀櫛館 達郎

(72) 発明者 東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】放熱性の向上を可能とする半導体装置を提供する。

【解決手段】実施形態の半導体装置は、半導体チップと、金属板と、半導体チップと金属板との間に設けられ、第1の金属層と、第2の金属層と、第1の金属層と第2の金属層との間の絶縁層を有し、第2の金属層が、第1の膜厚を有する第1の領域と、第2の膜厚を有する第2の領域と、第1の膜厚及び第2の膜厚よりも厚い第3の膜厚を有する第3の領域を有し、第3の領域は第1の領域と第2の領域との間に位置する絶縁基板と、第2の金属層と金属板との間に設けられたはんだ層と、を備える。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

半導体チップと、

金属板と、

前記半導体チップと前記金属板との間に設けられ、第1の金属層と、第2の金属層と、前記第1の金属層と前記第2の金属層との間の絶縁層を有し、前記第2の金属層が、第1の膜厚を有する第1の領域と、第2の膜厚を有する第2の領域と、前記第1の膜厚及び前記第2の膜厚よりも厚い第3の膜厚を有する第3の領域を有し、前記第3の領域は前記第1の領域と前記第2の領域との間に位置する絶縁基板と、

前記第2の金属層と前記金属板との間に設けられたはんだ層と、

を備える半導体装置。 10

**【請求項 2】**

前記第1の膜厚及び前記第2の膜厚は、前記第3の膜厚の0.4倍以上0.9倍以下である請求項1記載の半導体装置。

**【請求項 3】**

前記半導体チップの第1の端部と、前記第1の領域と前記第3の領域との境界部とを仮想的に結ぶ第1の線分と、前記第2の金属層と前記絶縁層との界面との間の角度が45度以下であり、

前記半導体チップの第2の端部と、前記第1の領域と前記第3の領域との境界部とを仮想的に結ぶ第2の線分と、前記第2の金属層と前記絶縁層との界面との間の角度が45度以下である請求項1又は請求項2記載の半導体装置。 20

**【請求項 4】**

前記金属板は、前記絶縁基板に対向する面の反対の面が凸形状となるよう湾曲している請求項1ないし請求項3いずれか一項記載の半導体装置。

**【請求項 5】**

前記半導体チップと前記第1の金属層との間に設けられた接着層を、更に備える請求項1ないし請求項4いずれか一項記載の半導体装置。

**【請求項 6】**

前記絶縁層は、酸化アルミニウム、窒化シリコン、又は、窒化アルミニウムである請求項1ないし請求項5いずれか一項記載の半導体装置。 30

**【請求項 7】**

前記金属板は、銅(Cu)を含む請求項1ないし請求項6いずれか一項記載の半導体装置。

**【請求項 8】**

前記第1の金属層、及び、前記第2の金属層は銅(Cu)を含む請求項1ないし請求項7いずれか一項記載の半導体装置。

**【請求項 9】**

前記はんだ層がアンチモン(Sb)を含む請求項1ないし請求項8いずれか一項記載の半導体装置。

**【請求項 10】**

前記絶縁基板の周囲を囲む枠体と、前記金属板との間に前記絶縁基板を挟む蓋と、前記絶縁基板と前記枠体との間、及び、前記絶縁基板と前記蓋との間に設けられた封止材を、更に備える請求項1ないし請求項9いずれか一項記載の半導体装置。 40

**【技術分野】****【0001】**

本発明の実施形態は、半導体装置に関する。

**【背景技術】****【0002】**

パワー半導体モジュールでは、例えば、金属ベース板の上に、絶縁基板を間に挟んでパワー半導体チップが実装される。パワー半導体チップは、例えば、IGBT (Insulated Gate Bipolar Transistor)、MOSFET (Metal Oxide Field Effect Transistor)、又は、ダイオードである。

10

**【0003】**

パワー半導体チップは、高電圧で高電流を流すため、発熱量が大きい。パワー半導体モジュールの放熱性が低いと、パワー半導体チップの発熱に起因して、ボンディングワイヤのオーブン不良等の信頼性不良が生じる。このため、パワー半導体モジュールでは、放熱性を向上させることが要求される。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2013-16525号公報

20

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

本発明が解決しようとする課題は、放熱性の向上を可能とする半導体装置を提供することにある。

**【課題を解決するための手段】****【0006】**

本発明の一態様の半導体装置は、半導体チップと、金属板と、前記半導体チップと前記金属板との間に設けられ、第1の金属層と、第2の金属層と、前記第1の金属層と前記第2の金属層との間の絶縁層を有し、前記第2の金属層が、第1の膜厚を有する第1の領域と、第2の膜厚を有する第2の領域と、前記第1の膜厚及び前記第2の膜厚よりも厚い第3の膜厚を有する第3の領域を有し、前記第3の領域は前記第1の領域と前記第2の領域との間に位置する絶縁基板と、前記第2の金属層と前記金属板との間に設けられたはんだ層と、を備える。

30

**【図面の簡単な説明】****【0007】**

【図1】実施形態の半導体装置の模式断面図。

【図2】実施形態の一部の拡大模式断面図。

【図3】比較形態の半導体装置の模式断面図。

【図4】比較形態の半導体装置の問題点の説明図。

【図5】実施形態の半導体装置の作用及び効果の説明図。

40

**【発明を実施するための形態】****【0008】**

本明細書中、同一又は類似する部材については、同一の符号を付し、重複する説明を省略する場合がある。

**【0009】**

本明細書中、部品等の位置関係を示すために、図面の上方向を「上」、図面の下方向を「下」と記述する場合がある。本明細書中、「上」、「下」の概念は、必ずしも重力の向きとの関係を示す用語ではない。

**【0010】**

実施形態の半導体装置は、半導体チップと、金属板と、半導体チップと金属板との間に

50

設けられ、第1の金属層と、第2の金属層と、第1の金属層と第2の金属層との間の絶縁層を有し、第2の金属層が、第1の膜厚を有する第1の領域と、第2の膜厚を有する第2の領域と、第1の膜厚及び第2の膜厚よりも厚い第3の膜厚を有する第3の領域を有し、第3の領域は第1の領域と第2の領域との間に位置し、第3の領域は半導体チップと金属板との間に位置する絶縁基板と、第2の金属層と金属板との間に設けられたはんだ層と、を備える。

#### 【0011】

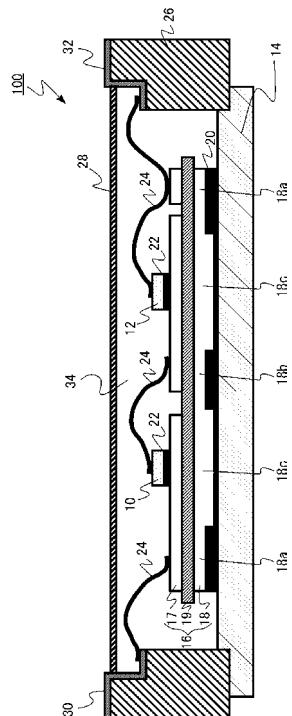

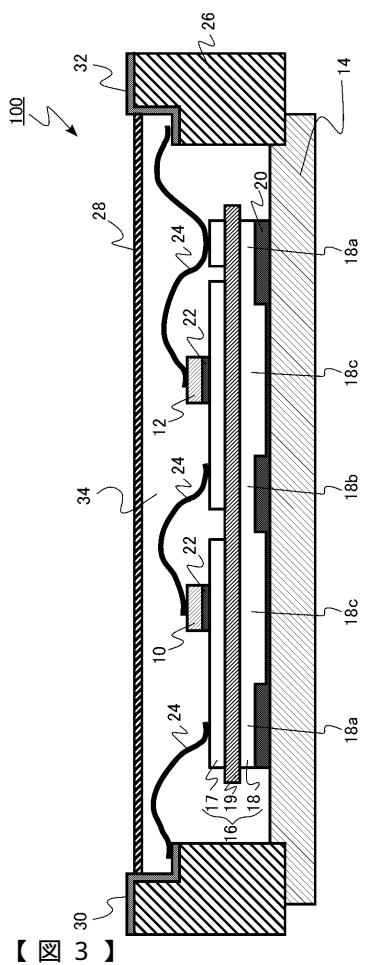

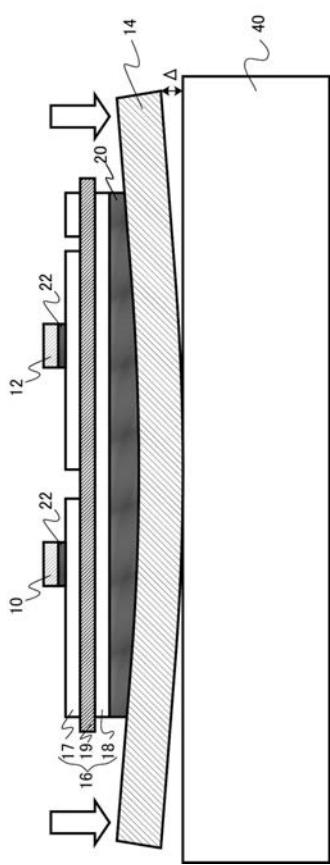

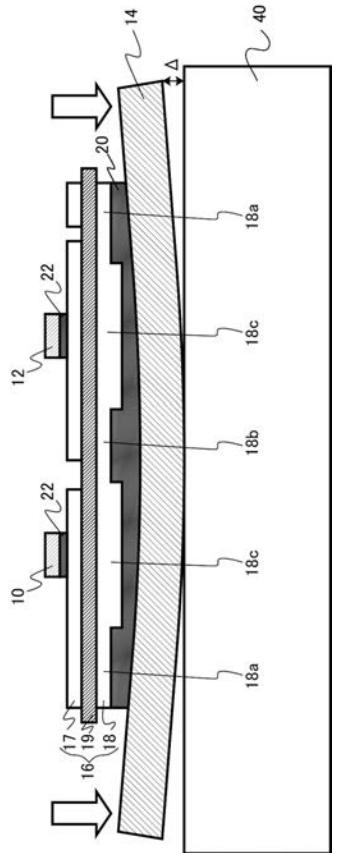

図1は、実施形態の半導体装置の模式断面図である。図2は、実施形態の一部の拡大模式断面図である。実施形態の半導体装置は、パワー半導体モジュール100である。

#### 【0012】

実施形態のパワー半導体モジュール100は、MOSFET10(半導体チップ)、MOSFET12、金属ベース板14(金属板)、絶縁回路基板16(絶縁基板)、第1のはんだ層20(はんだ層)、第2のはんだ層22(接着層)、ボンディングワイヤ24、樹脂ケース26(枠体)、蓋28、第1の電力端子30、第2の電力端子32、シリコーンゲル34(封止剤)を備える。絶縁回路基板16は、第1の金属層17、第2の金属層18、セラミック層19(絶縁層)を有する。第2の金属層18は、第1の凹領域18a(第1の領域)、第2の凹領域18b(第2の領域)、凸領域18c(第3の領域)を有する。

#### 【0013】

MOSFET10、及び、MOSFET12は、絶縁回路基板16の上に設けられる。MOSFET10、及び、MOSFET12は、高耐圧のパワーMOSFETである。MOSFET10及び、MOSFET12は、第2のはんだ層22によって第1の金属層17に固定される。MOSFET10、及び、MOSFET12は、例えば、シリコン、又は、炭化珪素を用いた縦型MOSFETである。

#### 【0014】

MOSFET10、及び、MOSFET12は、はんだに代えて、例えば、銀ペーストを用いた焼結接合により、第1の金属層17に固定されても構わない。

#### 【0015】

金属ベース板14は、例えば、銅を含む。金属ベース板14は、例えば、純銅又は銅合金である。金属ベース板14は、アルミニウムであっても構わない。

#### 【0016】

例えば、パワー半導体モジュール100を製品に実装する際、金属ベース板14の裏面には、図示しない放熱板が接続される。例えば、パワー半導体モジュール100の四方と放熱板をネジ止めすることにより、金属ベース板14と放熱板は固定される。金属ベース板14と放熱板との間には、例えば、サーマルグリースが挟まれる。

#### 【0017】

金属ベース板14は、例えば、絶縁回路基板16に対向する面の反対の面が、凸形状となるように湾曲している。言い換えれば、金属ベース板14の裏面は、端部に対し中央部が突出するような反り形状を有する。

#### 【0018】

絶縁回路基板16は、MOSFET10と金属ベース板14との間、及び、MOSFET12と金属ベース板14との間に設けられる。絶縁回路基板16は、MOSFET10と金属ベース板14との間、及び、MOSFET12と金属ベース板14との間の電気的絶縁を確保する機能を有する。金属ベース板14と絶縁回路基板16との間には、第1のはんだ層20が設けられる。

#### 【0019】

絶縁回路基板16は、第1の金属層17、第2の金属層18、セラミック層19(絶縁層)を有する。第1の金属層17、及び、第2の金属層18は、例えば、銅を含む。第1の金属層17、及び、第2の金属層18は、例えば、純銅である。セラミック層19は、例えば、酸化アルミニウム、窒化シリコン、又は、窒化アルミニウムである

10

20

30

40

50

## 【0020】

第2の金属層18は、第1の凹領域18a、第2の凹領域18b、凸領域18c（第3の領域）を有する。凸領域18cは、第1の凹領域18aと第2の凹領域18bとの間に位置する。

## 【0021】

第1の凹領域18aは第1の膜厚（図2中のt1）を有する。第2の凹領域18bは第2の膜厚（図2中のt2）を有する。凸領域18cは第3の膜厚（図2中のt3）を有する。第3の膜厚t3は、第1の膜厚t1及び第2の膜厚t2よりも厚い。第1の膜厚t1及び第2の膜厚t2は、第3の膜厚t3の0.4倍以上0.9倍以下である。

## 【0022】

第1の膜厚t1、第2の膜厚t2、及び、第3の膜厚t3の膜厚の関係は、例えば、顕微鏡写真の画像上で、それぞれの膜厚を比較することで、判定することが可能である。

## 【0023】

第1の膜厚t1及び第2の膜厚t2は、例えば、0.16mm以上0.76mm以下である。また、第3の膜厚t3は、例えば、0.4mm以上0.8mm以下である。

## 【0024】

凸領域18cは、MOSFET10と金属ベース板14との間、及び、MOSFET12と金属ベース板14との間に位置する。凸領域18cは、MOSFET10の直下に位置する。また、凸領域18cは、MOSFET12の直下に位置する。

## 【0025】

MOSFET10の第1の端部（図2中のE1）と、第1の凹領域18aと凸領域18cの境界部とを仮想的に結ぶ第1の線分（図2中のL1）と、第2の金属層18とセラミック層19との界面（図2中のI1）との間の角度（図2中の1）は、例えば、45度以下である。また、MOSFET10の第2の端部（図2中のE2）と、第2の凹領域18bと凸領域18cの境界部とを仮想的に結ぶ第2の線分（図2中のL2）と、第2の金属層18とセラミック層19との界面（図2中のI2）との間の角度（図2中の2）は、例えば、45度以下である。

## 【0026】

第1の凹領域18a、第2の凹領域18b、凸領域18cは、例えば、平板形状の金属層をエッチング加工することにより形成することが可能である。

## 【0027】

第1のはんだ層20は、第2の金属層18と金属ベース板14との間に設けられる。第1のはんだ層20は、金属ベース板14に絶縁回路基板16を固定する。第1のはんだ層20の主成分は、例えば、スズ(Sn) - 鉛(Pb)合金、スズ(Sn) - 銀(Ag)合金、スズ(Sn) - ビスマス(Bi)合金、スズ(Sn) - 銅(Cu)合金、又は、スズ(Sn) - インジウム(Indium)合金である。また、例えば、アンチモン(Sb)を含むスズ(Sn) - アンチモン(Sb)合金である。

## 【0028】

樹脂ケース26は、絶縁回路基板16の周囲を囲んで設けられる。樹脂ケース26の上には樹脂の蓋28が設けられる。蓋28は、金属ベース板14との間に絶縁回路基板16を挟む。

## 【0029】

また、パワー半導体モジュール100の内部には、封止材としてシリコーンゲル34が充填されている。樹脂ケース26、金属ベース板14、蓋28、及び、シリコーンゲル34は、半導体モジュール100内の部材を保護又は絶縁する機能を有する。

## 【0030】

樹脂ケース26の上部には、第1の電力端子30、及び、第2の電力端子32が設けられる。樹脂ケース26の上部に、例えば、図示しないAC出力端子、及び、ゲート端子が設けられる。第1の電力端子30、及び、第2の電力端子32により、パワー半導体モジュール100と外部との電気的接続が行われる。

10

20

30

40

50

## 【0031】

第1の電力端子30は、ボンディングワイヤ24を用いて、第1の金属層17に電気的に接続される。MOSFET10は、ボンディングワイヤ24を用いて、第1の金属層17に電気的に接続されるMOSFET12は、ボンディングワイヤ24を用いて、第1の金属層17に電気的に接続される。第1の金属層17は、ボンディングワイヤ24を用いて、第2の電力端子32に電気的に接続される。ボンディングワイヤ24は、例えば、アルミワイヤである。

## 【0032】

次に、実施形態の半導体装置の作用及び効果について説明する。

## 【0033】

10

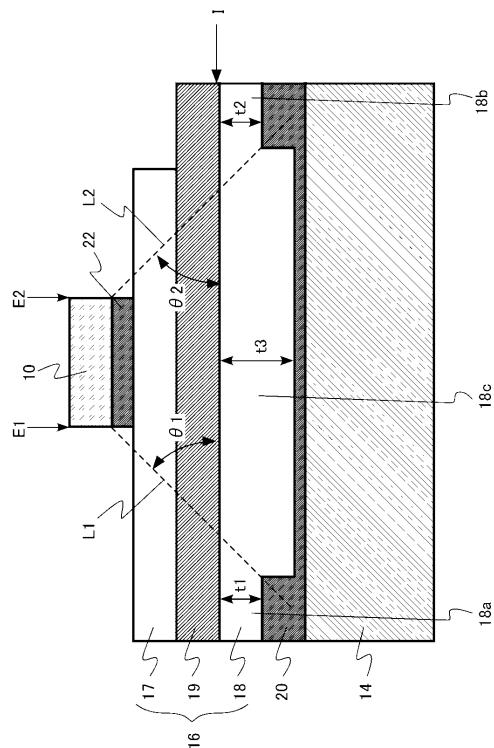

図3は、比較形態の半導体装置の模式断面図である。比較形態の半導体装置は、パワー半導体モジュール900である。

## 【0034】

比較形態のパワー半導体モジュール900は、絶縁回路基板16の第2の金属層18に、凸領域18cが設けられない点で実施形態のパワー半導体モジュール100と異なっている。すなわち、パワー半導体モジュール900の第2の金属層18は平板形状である。

## 【0035】

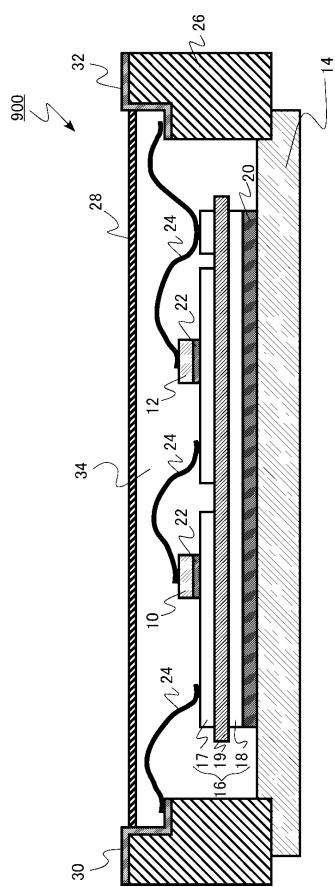

図4は、比較形態の半導体装置の問題点の説明図である。図4は、パワー半導体モジュール900の一部、及び、放熱板を図示している。

## 【0036】

20

パワー半導体モジュール900を製品に実装する際、金属ベース板14の裏面には、放熱板40が接続される。例えば、パワー半導体モジュール900の四方と放熱板40をネジ止めして、金属ベース板14を押さえつけることにより、金属ベース板14と放熱板40は密着して固定される。金属ベース板14と放熱板40との間には、例えば、図示しないサーマルグリースが挟まれる。

## 【0037】

金属ベース板14の裏面は、端部に対し中央部が突出するような反り形状を有する。金属ベース板14の表面は、端部に対し中央部が窪むような反り形状を有する。金属ベース板14の反り量(図4中の )は、例えば、0mm以上1mm以下である。また、例えば、0mmより大きく1mm以下である。また、例えば、0.1mmより大きく1mm以下である。なお、図4では、説明のために、反り量を強調して図示している。

30

## 【0038】

仮に、金属ベース板14の裏面が反り形状を有しない場合、ネジ止めの際に、金属ベース板14の裏面の中央部と放熱板40の表面との間に隙間ができるおそれがある。そして、その隙間に熱伝導率の低いサーマルグリースが溜ったり、熱伝導率の低い空隙が出来たりして、熱抵抗が上がり放熱性が低下するおそれがある。

## 【0039】

40

金属ベース板14が反り形状を有する場合、絶縁回路基板16の中央部と金属ベース板14の間の、第1のはんだ層20の厚さが、絶縁回路基板16の端部と金属ベース板14の間の厚さと比較して厚くなる。はんだの熱伝導率は、例えば、第2の金属層18や金属ベース板14の熱伝導率と比較して格段に低い。また、はんだが厚くなると、はんだよりも更に熱伝導率の低いボイドの発生確率が高くなる。

## 【0040】

したがって、第1のはんだ層20の厚さが厚くなると熱抵抗が上がり、放熱性が低下するため好ましくない。特に、発熱量の大きいMOSFET10の直下、及び、MOSFET12の直下の第1のはんだ層20の厚さが厚くなることは好ましくない。

## 【0041】

図5は、実施形態の半導体装置の作用及び効果の説明図である。図5は、パワー半導体モジュール100の一部、及び、放熱板を図示している。

## 【0042】

50

実施形態では、パワー半導体モジュール100の第2の金属層18に、凸領域18cが設けられる。凸領域18cは、発熱量の大きいMOSFET10の直下、及び、MOSFET12の直下に設けられる。凸領域18cが設けられることで、比較形態に比べ、MOSFET10の下の第1のはんだ層20の厚さ、及び、MOSFET12の下の第1のはんだ層20の厚さが薄くなる。したがって、比較形態に比べて熱抵抗が下がり、放熱性が向上する。

#### 【0043】

第1の凹領域18aの第1の膜厚t1、及び、第2の凹領域18bの第2の膜厚t2は、凸領域18cの第3の膜厚t3の0.4倍以上0.9倍以下であることが好ましい。10 上記範囲を下回ると、加工が困難になるおそれがある。また、上記範囲を下回ると、第1の凹領域18aと凸領域18cとの境界部、第2の凹領域18bと凸領域18cとの境界部で、第1のはんだ層20のはんだ量の変化が大きくなり、クラック発生の要因となるおそれがある。また、上記範囲を下回ると、第1のはんだ層20との間の合金形成が不十分となり、絶縁回路基板16と金属ベース板14との接着性が低下するおそれがある。また、上記範囲を上回ると、第1のはんだ層20の厚さが厚くなりすぎ、放熱性の向上が不十分となるおそれがある。

#### 【0044】

MOSFET10の第1の端部(図2中のE1)と、第1の凹領域18aと凸領域18cの境界部とを仮想的に結ぶ第1の線分(図2中のL1)と、第2の金属層18とセラミック層19との界面(図2中のI)との間の角度(図2中の1)は、例えば、45度以下であることが好ましい。また、MOSFET10の第2の端部(図2中のE2)と、第2の凹領域18bと凸領域18cとの境界部とを仮想的に結ぶ第2の線分(図2中のL2)と、第2の金属層18とセラミック層19との界面(図2中のI)との間の角度(図2中の2)は、例えば、45度以下であることが好ましい。20

#### 【0045】

上記構成により、MOSFET10の下で、第1のはんだ層20の厚さが薄い領域が広がり、放熱性を向上させることが可能である。

#### 【0046】

第1のはんだ層20の主成分が、アンチモン(Sb)を含むスズ(Sn)-アンチモン(Sb)合金である場合に、実施形態は特に有効に作用する。30 スズ(Sn)-アンチモン(Sb)合金は、高い耐熱性を備える一方、熱伝導率が比較的低い。実施形態のパワー半導体モジュール100の第1のはんだ層20に、スズ(Sn)-アンチモン(Sb)合金を適用することで、高い耐熱性と高い放熱性を両立させることが可能となる。

#### 【0047】

以上、実施形態の半導体モジュール100によれば、半導体チップ直下の絶縁回路基板16と金属ベース板14との間の第1のはんだ層20の厚さを薄くすることが可能となる。したがって、半導体モジュール100の放熱性の向上が可能となる。

#### 【0048】

実施形態では、半導体チップとしてMOSFETを例に説明したが、半導体チップは、IGBTであっても、ダイオードであっても構わない。また、例えば、MOSFETとダイオード、あるいは、IGBTとダイオードの組み合わせであっても構わない。40

#### 【0049】

また、1枚の絶縁回路基板16の上に実装される半導体チップの数は、2個に限定されず、1個であっても、3個以上であっても構わない。また、半導体モジュール100には、2枚以上の絶縁回路基板16が含まれていても構わない。

#### 【0050】

実施形態では、封止材としてシリコーンゲル34を用いる場合を例に説明したが、シリコーンゲル34に代えて、例えば、エポキシ樹脂など、その他の樹脂材料を用いることも可能である。

#### 【0051】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。例えば、一実施形態の構成要素を他の実施形態の構成要素と置き換え又は変更してもよい。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

## 【符号の説明】

## 【0052】

|      |                 |    |

|------|-----------------|----|

| 10   | MOSFET (半導体チップ) | 10 |

| 14   | 金属ベース板 (金属板)    |    |

| 16   | 絶縁回路基板 (絶縁基板)   |    |

| 17   | 第1の金属層          |    |

| 18   | 第2の金属層          |    |

| 18 a | 第1の凹領域 (第1の領域)  |    |

| 18 b | 第2の凹領域 (第2の領域)  |    |

| 18 c | 凸領域 (第3の領域)     |    |

| 20   | 第1のはんだ層 (はんだ層)  |    |

| 22   | 第2のはんだ層 (接着層)   |    |

| 19   | セラミック層 (絶縁層)    | 20 |

| 26   | 樹脂ケース (枠体)      |    |

| 28   | 蓋               |    |

| 34   | シリコーンゲル (封止剤)   |    |

| 100  | パワー半導体モジュール     |    |

| E1   | 第1の端部           |    |

| E2   | 第2の端部           |    |

| I    | 界面              |    |

| L1   | 第1の線分           |    |

| L2   | 第2の線分           |    |

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

F ターム(参考) 5F136 BB05 DA27 DA28 EA02 EA13 FA02 FA03 FA12 FA52 FA53