(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0062695

(43) 공개일자 2012년06월14일

- (51) 국제특허분류(Int. C1.)

*H03M 1/10* (2006.01) *H03M 1/44* (2006.01)

*H03M 1/16* (2006.01) *H03M 1/36* (2006.01)

- (21) 출원번호 10-2012-7002931

- (22) 출원일자(국제) 2010년07월08일

심사청구일자 없음

- (85) 번역문제출일자 2012년02월02일

- (86) 국제출원번호 PCT/EP2010/059821

- (87) 국제공개번호 WO 2011/003978

국제공개일자 2011년01월13일

- (30) 우선권주장

10151660.7 2010년01월26일

유럽특허청(EPO)(EP)

61/224,519 2009년07월10일 미국(US)

- (71) 출원인

브리제 유니버시티브 브루셀

벨기에, 비-1050 플루셀, 블레인란 2

아이엠이씨

벨기에 비-3001 루벤 카펠드리프 75

- (72) 발명자

베르브루겐, 밥

벨기에, 케셀-로 비-3010, 티엔세스틴베그

289/0001

- (74) 대리인

강명구

전체 청구항 수 : 총 10 항

(54) 발명의 명칭 인터리브된 파이프라인형 이진 검색 A/D 변환기

### (57) 요 약

본 발명은 아날로그 입력 신호를 디지털 신호로 변환하기 위한 파이프라인형 아날로그-디지털 변환기, ADC에 관한 것이며, 상기 변환기는 입력 신호와 비교되기 위한 튜닝 가능한 임계치를 갖는 복수의 비교기 수단(이때, 지정 임계치 중 둘 이상은 서로 상이함)과, 복수의 증폭 회로를 포함하며, 상기 복수의 비교 수단은 계층적 트리 구조를 형성하도록 구성되고, 상기 계층적 트리 구조는 복수의 계층적 레벨을 가지며, 상기 복수의 계층적 레벨 중 하나 이상이 상기 복수의 증폭 회로 중 최소한 하나의 증폭 회로와 연계되고, 상기 하나 이상의 증폭 회로가 다음 번 계층 레벨에 있는 하나 이상의 비교 수단의 입력을 발생시키고, 상기 복수의 계층적 레벨은, 수행하는 계층 레벨의 비선형 왜곡(non-linear distortion)이 제거되도록, 이전 계층 레벨의 출력에 따라 튜닝 가능한 임계치를 설정하기 위한 수단을 포함한다.

**대 표 도** - 도1

## 특허청구의 범위

### 청구항 1

아날로그 입력 신호를 디지털 신호로 변환하기 위한 파이프라인형 아날로그-디지털 변환기(ADC)에 있어서, 상기 변환기는

- 입력 신호와 비교되기 위한 튜닝 가능한 임계치를 갖는 복수의 비교 수단으로서, 지정 임계치들 중 둘 이상은 서로 상이한, 상기 복수의 비교 수단, 및

- 복수의 증폭 회로

를 포함하며,

상기 복수의 비교 수단은 계층적 트리 구조를 형성하도록 구성되고, 상기 계층적 트리 구조는 복수의 계층적 레벨을 가지며, 상기 복수의 계층적 레벨 중 하나 이상이 상기 복수의 증폭 회로 중 최소한 하나의 증폭 회로와 연계되고, 상기 하나 이상의 증폭 회로가 다음 번 계층 레벨에 있는 하나 이상의 비교 수단의 입력을 발생시키고,

상기 복수의 계층 레벨은, 선행하는 계층 레벨의 비선형 왜곡(non-linear distortion)이 제거되도록, 이전 계층 레벨의 출력에 따라 튜닝 가능한 임계치를 설정하기 위한 수단을 포함하는 것을 특징으로 하는 파이프라인형 아날로그-디지털 변환기.

### 청구항 2

제 1 항에 있어서, 상기 튜닝 가능한 임계치를 설정하기 위한 수단은 가변 커패시터를 포함하는 것을 특징으로 하는 파이프라인형 아날로그-디지털 변환기.

### 청구항 3

제 2 항에 있어서, 상기 가변 커패시터는 상기 비교 수단과 연계된 제 1 가변 커패시터와 상기 증폭 회로와 연계된 제 2 가변 커패시터를 포함하는 것을 특징으로 하는 파이프라인형 아날로그-디지털 변환기.

### 청구항 4

제 1 항 내지 제 3 항 중 어느 한 항에 있어서, 상기 증폭 회로는 비선형 디지털-아날로그 변환기인 것을 특징으로 하는 파이프라인형 아날로그-디지털 변환기.

### 청구항 5

제 1 항 내지 제 4 항 중 어느 한 항에 있어서, 상기 복수의 비교 수단 각각은, 하나씩의 증폭 회로와 함께, 비교기/트랙 앤 홀드 증폭 회로로 구현되는 것을 특징으로 하는 파이프라인형 아날로그-디지털 변환기.

### 청구항 6

제 1 항 내지 제 5 항 중 어느 한 항에 있어서, m-비트 폴딩 ADC 프론트-엔드(m-bit folding ADC front-end)를 더 포함하는 것을 특징으로 하는 파이프라인형 아날로그-디지털 변환기.

### 청구항 7

제 1 항 내지 제 6 항 중 어느 한 항에 있어서, n-비트 플래시 아날로그-디지털 변환기를 더 포함하는 것을 특징으로 하는 파이프라인형 아날로그-디지털 변환기.

### 청구항 8

파이프라인형 아날로그-디지털 변환기에서 아날로그 입력 신호를 디지털 출력으로 변환하기 위한 방법에 있어서, 상기 파이프라인형 아날로그-디지털 변환기는

입력 신호와 비교되기 위한 튜닝 가능한 임계치를 갖는 복수의 비교 수단으로서, 지정 임계치들 중 둘 이상은 서로 상이한, 상기 복수의 비교 수단, 및

## 복수의 증폭 회로

를 포함하고, 상기 복수의 비교 수단은 계층적 트리 구조를 형성하도록 구성되고, 상기 계층적 트리 구조는 복수의 계층 레벨을 가지며, 상기 복수의 계층 레벨 중 하나 이상은 상기 복수의 증폭 회로 중 하나 이상의 증폭 회로와 연계되고, 상기 하나 이상의 증폭 회로는 다음 계층 레벨에 있는 하나 이상의 비교 수단의 입력을 발생하도록 배열되고, 상기 방법은

- 상기 아날로그 입력 신호를 상기 계층적 트리 구조의 제 1 계층 레벨로 인가하는 단계,

- 상기 제 1 계층 레벨의 제 1 비교 수단을 통해 상기 입력 신호를 각각의 임계치 신호와 비교하여, 비교 신호를 발생하고, 이 비교 신호를 다음 번 계층 레벨의 입력 신호로서 제공하는 단계, 및

- 이전 단계의 비교 결과를 기초로, 제 2 계층 레벨의 다음 번 비교 수단 및 이와 연계된 증폭 회로를 선택하는 단계

를 포함하는 것을 특징으로 하는 아날로그 입력 신호를 디지털 출력으로 변환하기 위한 방법.

## 청구항 9

제 8 항에 있어서, 교정 단계가 선행되는 것을 특징으로 하는 아날로그 입력 신호를 디지털 출력으로 변환하기 위한 방법.

## 청구항 10

제 9 항에 있어서, 상기 교정 단계는, 가변 커패시턴스를 이용해 계층 레벨 중 하나 이상과 연계된 하나 이상의 증폭 회로를 투닝하는 단계를 포함하는 것을 특징으로 하는 아날로그 입력 신호를 디지털 출력으로 변환하기 위한 방법.

## 명세서

### 기술 분야

[0001]

본 발명은 이진 검색(binary search)이 사용되는 아날로그-디지털 변환기에 관한 것이다.

### 배경 기술

[0002]

일부 적용예, 가령, 하드 디스크 판독 채널, 또는 광대역 무선 표준은 낮은 분해능(가령, 약 6비트) 및 고속(가령, 초당 1기가 샘플(GS/s) 이상)의 아날로그-디지털 변환기(ADC)를 필요로 한다.

[0003]

전통적으로, 낮은 분해능 및 고속 ADC를 위한 두 가지 아키텍처(즉, 시간 인터리브형 연속 근사 레지스터(SAR) 변환기와 플래시 변환기)가 있다. 단일 채널 SAR 변환기는 초당 수백 메가 샘플(MS/s)(예를 들어, 약 300MS/s)의 샘플링 주파수에서 동작하는 것이 일반적이다. 그 결과로 큰 입력 용량을 산출하면서 복수의 채널이 인터리브될 필요가 있다. 선택된 방식에 따라, 동일한 세부사항에 대해 시간-인터리브형 SAR 아키텍처가 파이프라인형 이진 검색 ADC보다 10-20배 더 큰 입력 용량을 가질 수 있다. 한편, 낮은 잡음/오프셋에서 각각의 변환에 대해 63회 비교(6비트)가 이뤄져야 하기 때문에, 플래시 변환기는 양자화된 파워(quantized power)에 의해 심하게 제한될 것이다. 교정된 플래시 변환기를 이용한 유사한 세부사항에 대한 파워 요구치는 파이프라인형 이진 검색 ADC에서 소비되는 파워보다 10배 더 클 것이다.

[0004]

파이프라인형 아날로그-디지털 변환기는 초당 수 메가샘플 내지 초당 100 메가샘플의 샘플링 레이트로 알려져 있다. 동적 파이프라인형 변환에 의해, 낮은 입력 용량으로 고속의 낮은 파워 양자화가 가능해진다. 그러나 교정이 필요하다.

[0005]

미국 특허 출원 US2005/0062635는 비선형 스케일(non-linear scale)을 따르고, 2GHz 이상의 주파수에서의 동작을 가능하게 하는 파이프라인형 아날로그-디지털 변환기를 소개한다. 파이프라인형 ADC는 복수의 비교기 스테이지를 포함하여, 상기 복수의 비교기 스테이지에서, 이전 스테이지에서의 디지털 변환 결과에 따라 비교기 스테이지의 임계치가 조정된다. 요약하자면, 본원에서, 파이프라인형 ADC에 프로그래밍 가능한 특성을 제공하

기 위한 아키텍처와 방법이 제안되며, 이에 따라 비선형 스케일도 구현될 수 있다. 선형 증폭기를 이용하여, 출력 신호가 선형 신호 프로세싱(linear signal processing)을 통해 처리된다.

## 발명의 내용

### 해결하려는 과제

[0006]

본 발명은 전력 소비량이 감소되는(저-분해능 및 고속의) 아날로그-디지털 변환기를 제공하는 것을 목적으로 삼는다.

### 과제의 해결 수단

[0007]

아날로그 입력 신호를 디지털 신호로 변환하기 위한 파이프라인형 아날로그-디지털 변환기가 제공된다. 상기 파이프라인형 아날로그-디지털 변환기는, 입력 신호와 비교되기 위한 튜닝 가능한 임계치를 갖는 복수의 비교 수단(이때, 상기 주어진 임계치들 중 적어도 둘은 서로 상이함)과, 복수의 증폭 회로를 포함한다. 복수의 비교 수단은 복수의 계층적 레벨을 갖는 계층적 트리 구조를 형성하도록 구성된다. 계층 레벨들 중 하나 이상은 복수의 증폭 회로 중 하나 이상의 증폭 회로와 연계된다. 하나 이상의 증폭 회로는 다음 번 계층 레벨의 하나 이상의 비교 수단의 입력을 발생한다. 복수의 계층 레벨은, 선행하는 계층 레벨의 비선형 왜곡을 제거하도록 이전 계층 레벨의 출력에 따라 튜닝 가능한 임계치를 설정하기 위한 수단을 포함한다. 하나의 실시예에서, 튜닝 가능한 임계치를 설정하기 위한 수단은 가변 커페시터를 포함한다. 일례에서 상기 가변 커페시터는 비교 수단과 연계되는 제 1 가변 커페시터와 증폭 회로와 연계되는 제 2 가변 커페시터를 포함한다.

[0008]

선행하는 계층 레벨의 비선형 왜곡을 상쇄시키도록, 원하는 입력 임계치가 인가될 때 임계치는 이전 레벨의 출력으로 튜닝되는 것이 바람직하다.

[0009]

하나의 실시예에서, 증폭 회로는 비선형 멀티플라잉 디지털-아날로그 변환기(NLMDAC: non-linear multiplying digital to analog converter)이다.

[0010]

하나의 실시예에서, 파이프라인형 ADC가 제공되며, 여기서 복수의 비교 수단 각각은 하나씩의 증폭 회로와 함께, 비교기/트랙 앤 홀드 증폭 회로로 구현된다. 이러한 비교기/트랙 앤 홀드 증폭 회로는 동적 증폭기와 래치를 포함한다. 복수의 비교기/트랙 앤 홀드 증폭 회로 각각은 뒤 이은 레벨의 2개의 비교기/트랙 앤 홀드 증폭 회로에 대한 입력 신호를 발생시킨다.

[0011]

하나의 실시예에서, 비교기/트랙 앤 홀드 증폭 회로는 튜닝 가능한 임계치를 가진다. 예를 들어, 비교기/트랙 및 홀드 증폭 회로는 가변 커페시터를 포함한다. 가변 커페시터를 설정함으로써, 지정 임계치가 제공된다. 선행하는 비교기/트랙 앤 홀드 증폭 회로의 비선형 왜곡을 상쇄시키기 위해, 임계치는, 원하는 입력 임계치가 인가될 때의 이전 레벨의 출력으로 튜닝되는 것이 바람직하다.

[0012]

또 다른 하나의 실시예에서, 앞서 언급된 실시예들 중 하나에 따르는 파이프라인형 아날로그-디지털 변환기를 이용해 아날로그 입력 신호를 디지털 출력으로 변환하기 위한 방법이 제공된다. 상기 방법은 a) 아날로그 입력 신호를 계층적 트리 구조의 제 1 계층 레벨로 인가하는 단계와, b) 제 1 계층 레벨의 제 1 비교 수단을 통해 상기 입력 신호를 각각의 임계치 신호와 비교하여, 비교 신호를 발생시키고, 이 비교 신호를 다음 번 계층 레벨로의 입력 신호로서 공급하는 단계와, c) 이전 단계의 비교 결과를 기초로, 제 2 계층 레벨의 다음 번 비교 수단( 및 이와 연계된 증폭 회로도)을 선택하는 단계를 포함한다.

[0013]

상기 방법은 이진 검색 알고리즘을 이행하는 것이 바람직하다. 병렬 검색 대신, 이진 검색을 이용함으로써, 작동되는 비교기의 수가 감소되고, 따라서 전력 소비량이 감소된다.

[0014]

비교 수단의 결정을 기초로, 이 레벨 또는 그 다음 번 레벨에서의 증폭 회로는 입력 신호로부터 결정의 가중치에 따른 값을 더하거나 뺀다. 제 1 계층 레벨(부모 계층 레벨)의 비교 수단이 다음 번 계층 레벨(자식 계층 레벨)의 비교 수단을 제어하거나 트리거한다.

[0015]

하나의 실시예에서, 아날로그 입력 신호를 디지털 출력으로 변환하기 위한 방법에 앞서, 교정 단계가 존재한다. 교정 주기 동안 하나 이상의 비교 수단의 임계치가 튜닝되고, 그 시점부터 쭉 비교기는 지정 임계치를 가진다. 교정 단계는 가변 커페시터스를 이용해, 계층 레벨들 중 하나 이상과 연계된 하나 이상의 증폭 회로를

튜닝하는 단계를 포함하는 것이 바람직하다.

[0016] 또 다른 하나의 실시예에서, 비교 단계는 증폭 회로/DAC로 공급되는 출력 신호를 도출하여, 연속 근사 프로세스를 구현한다. 이진 코드가 결정된다.

### 도면의 간단한 설명

[0017] 본 발명은 다음의 상세한 설명과 첨부된 도면을 통해 더 명확해질 것이다.

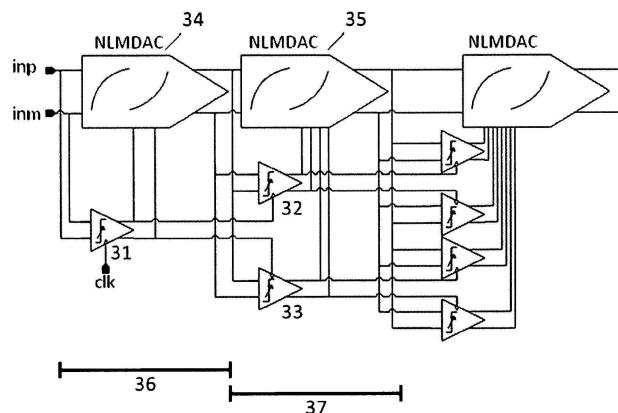

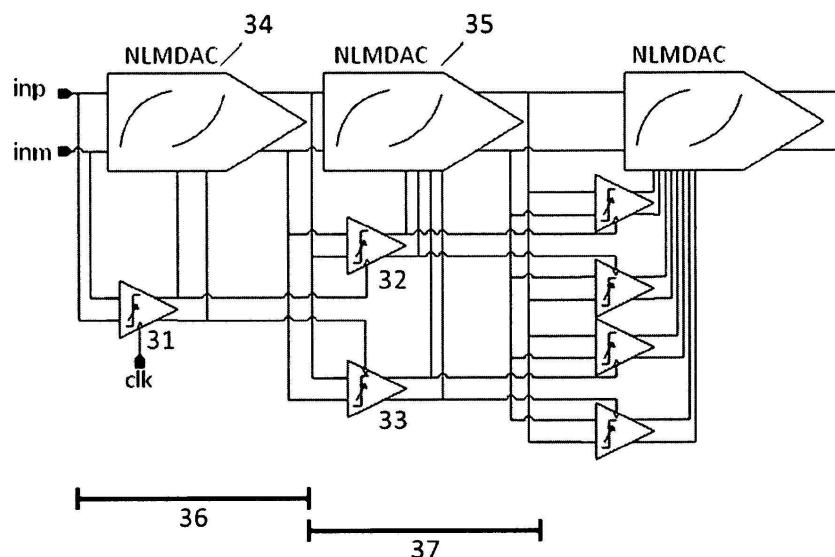

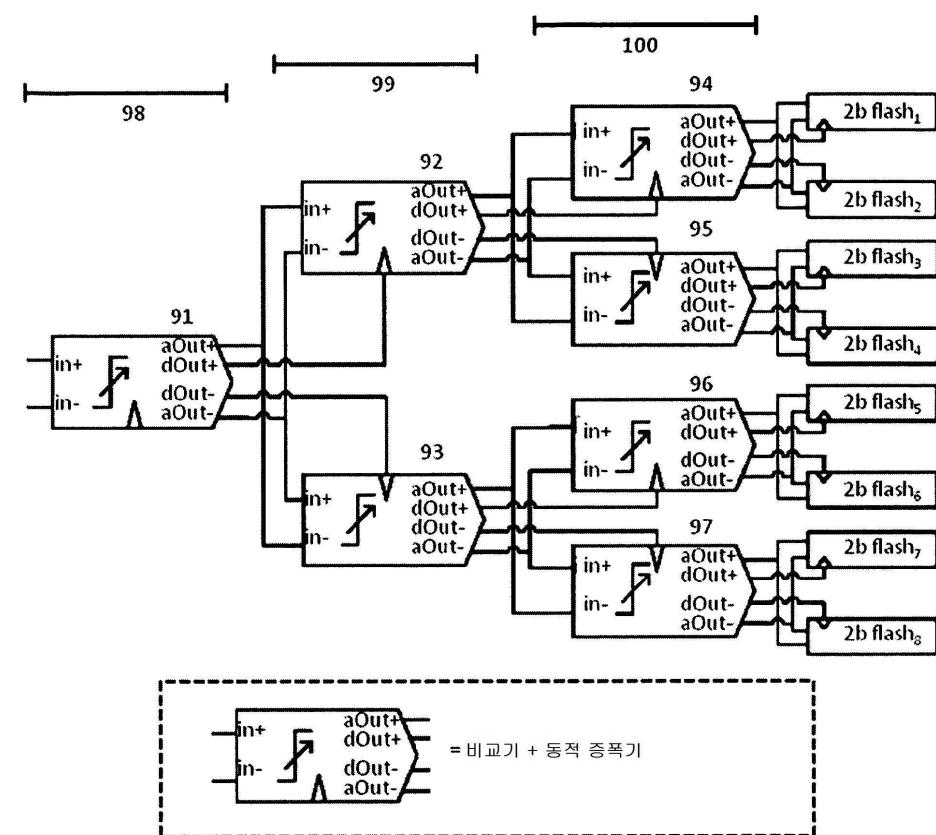

도 1은 스테이지당 1비트 파이프라인형 A/D 변환기의 3비트에 대한 블록도이다.

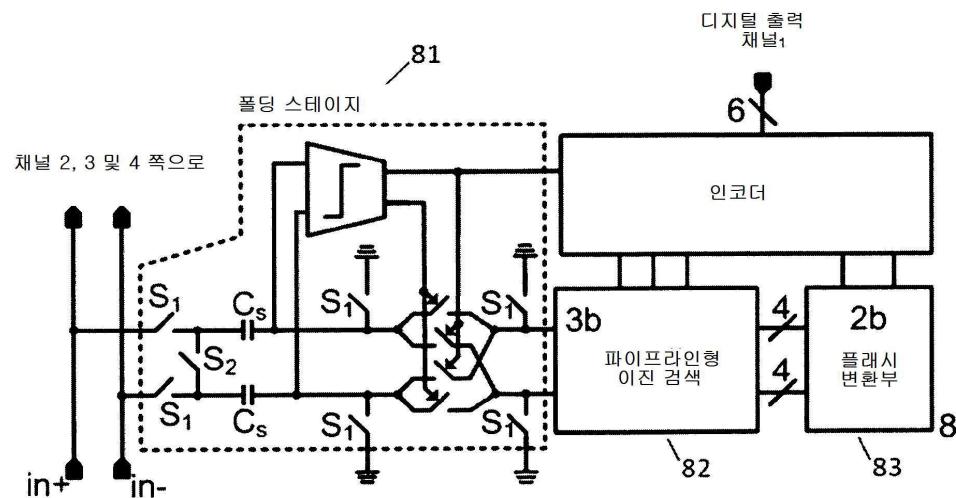

도 2는 하이브리드 ADC의 일례를 도시한다.

도 3은 파이프라인형 이진 검색 방법의 개략도이다.

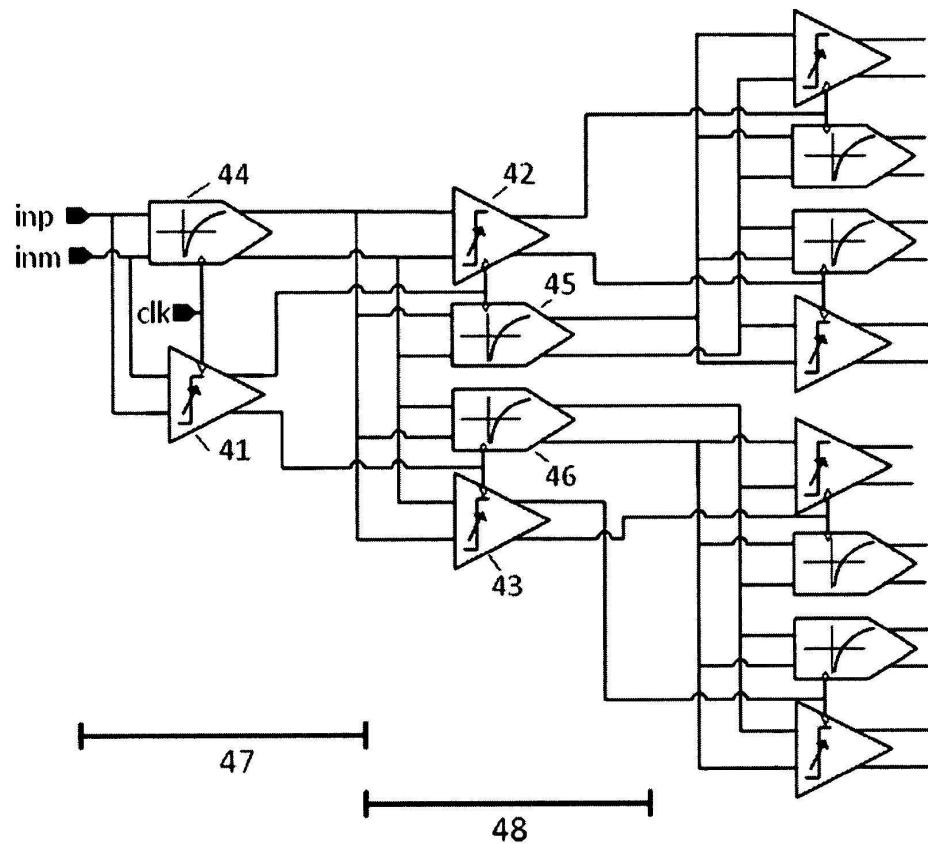

도 4는 스테이지당 1비트 파이프라인형 ADC 변환기의 3비트에 대한 블록도이다.

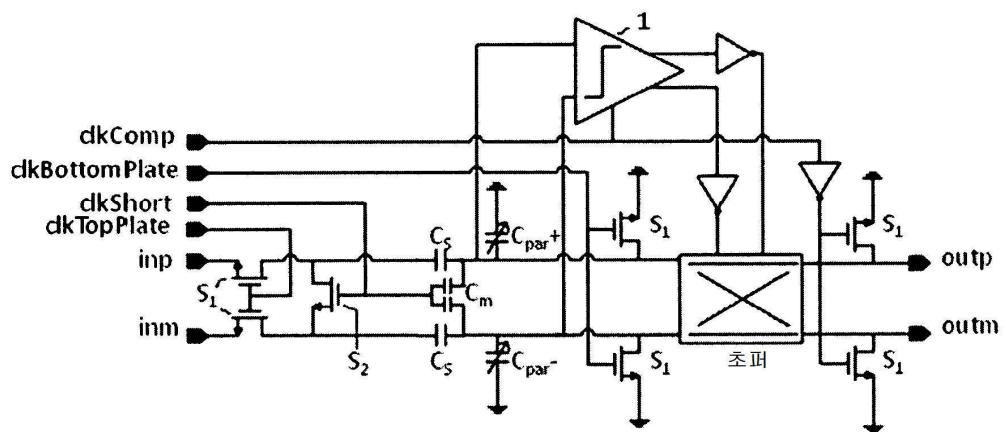

도 5는 폴딩 프론트-엔드 스테이지의 개략도이다.

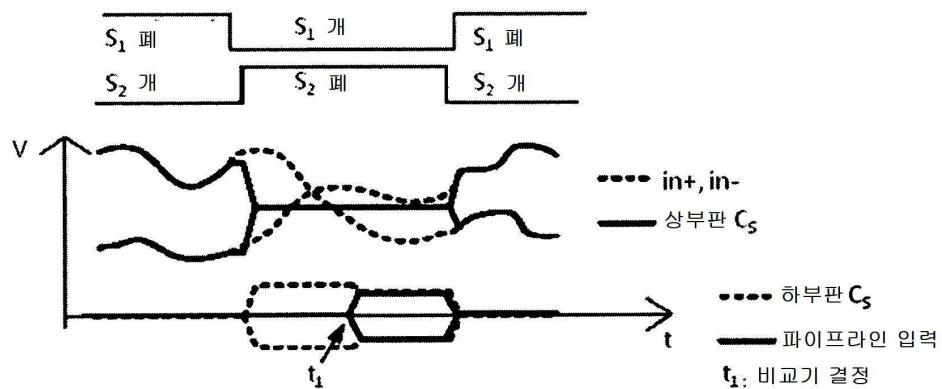

도 6은 폴딩 프론트-엔드 스테이지의 파형이다.

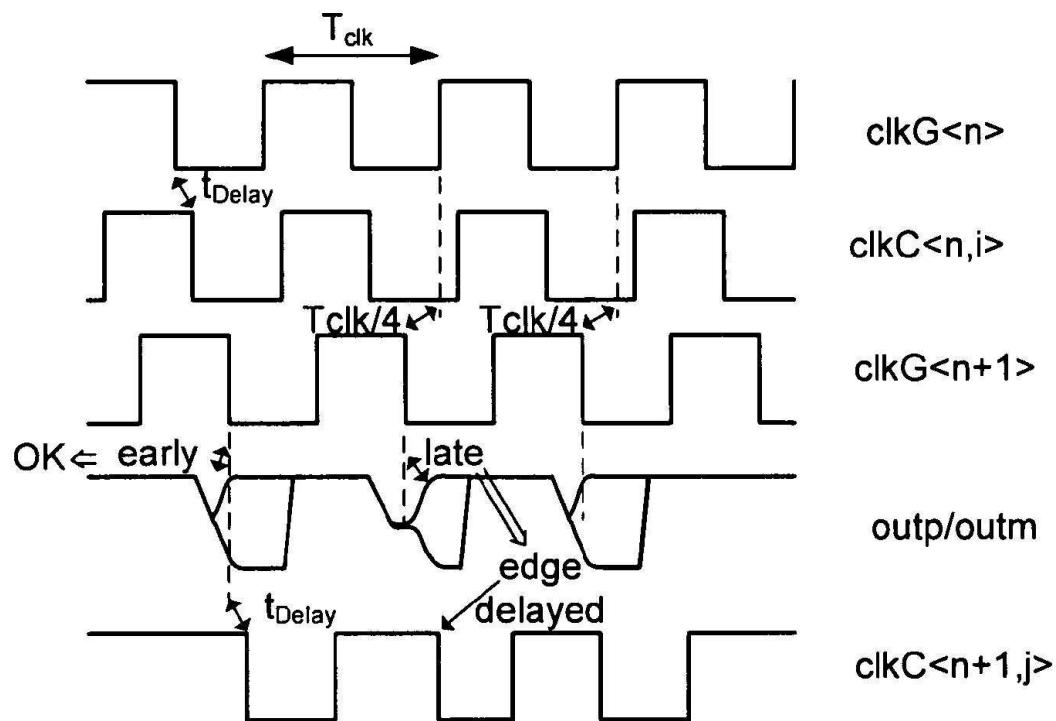

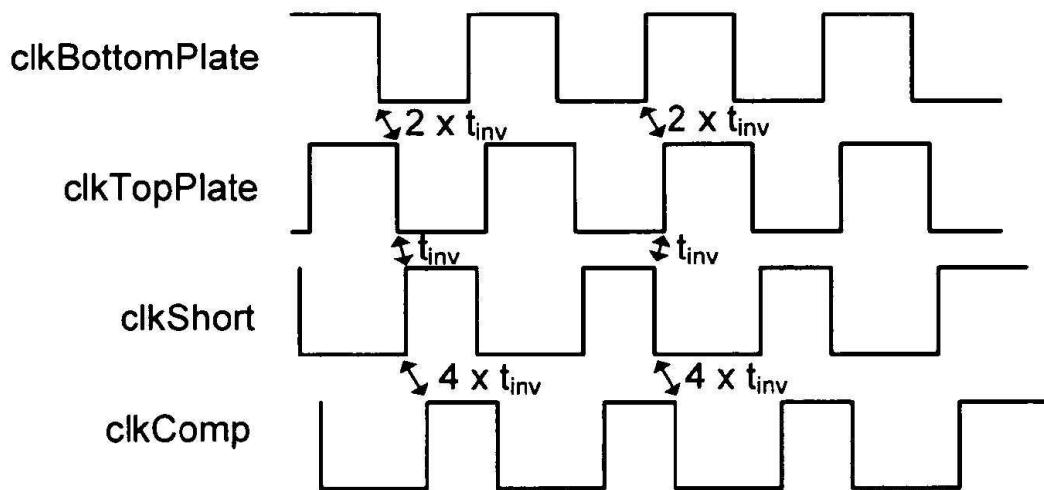

도 7은 폴딩 스테이지의 클럭 신호의 타이밍을 나타낸다.

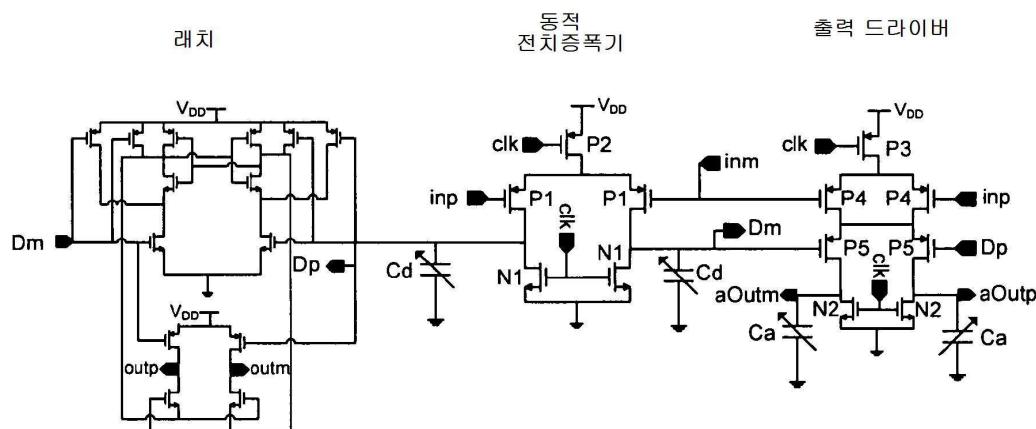

도 8은 가능한 비교기-T/H 회로의 일례를 도시한다.

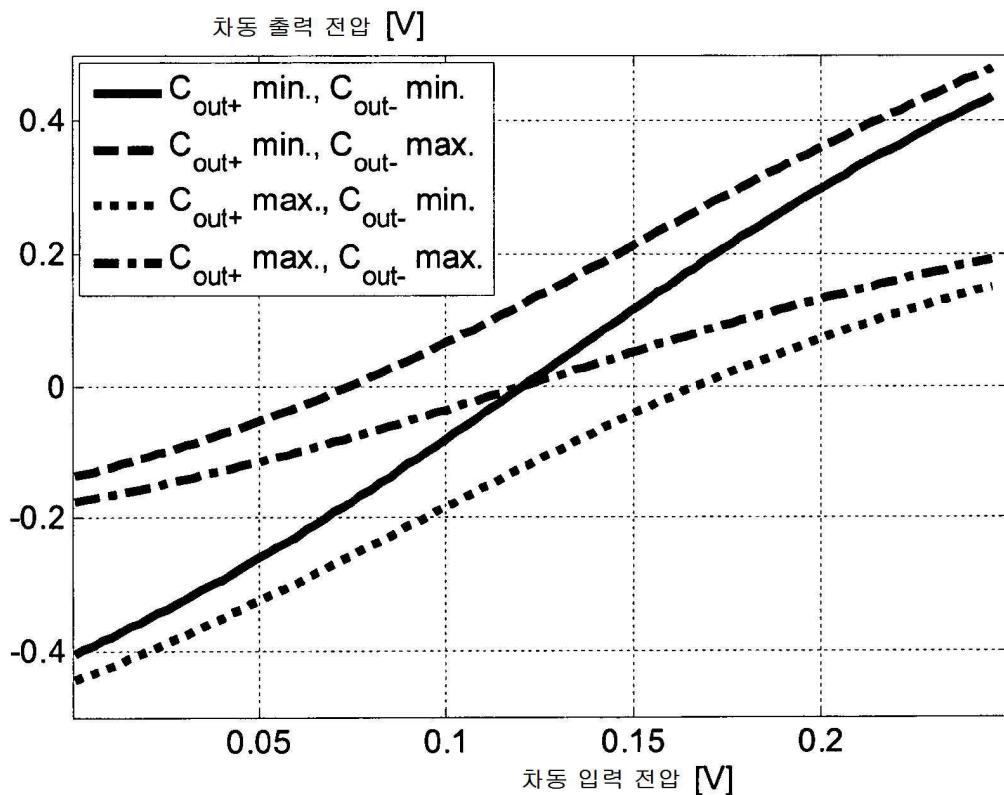

도 9는 동적 증폭기의 시뮬레이트된 입력-출력 특성의 도표를 도시한다.

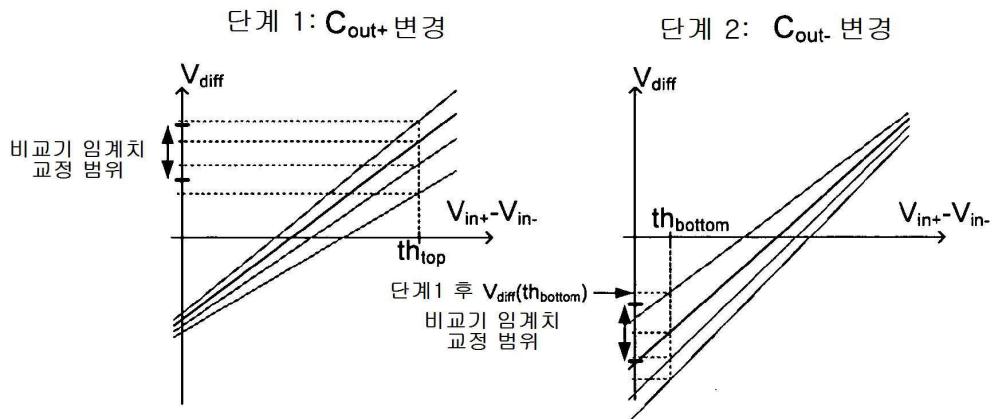

도 10은 Ca를 교정하기 위한 상이한 교정 단계들의 도표를 도시한다.

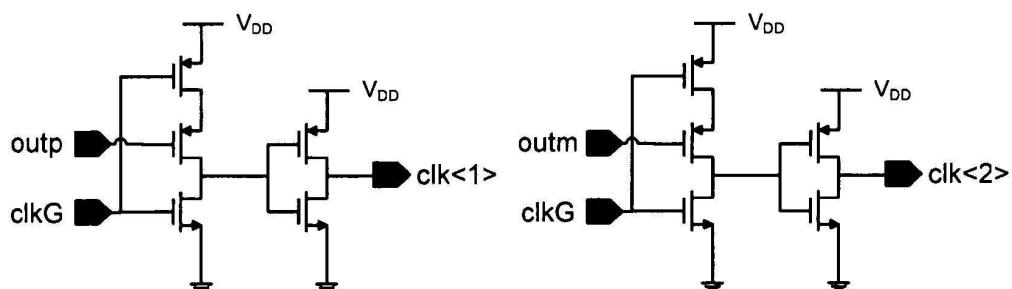

도 11은 각각의 행에 대한 클럭을 게이트-제어하도록 사용되는 회로의 개략도이다.

도 12는 비교기/트랙&홀드 증폭기 트리에서의 여러 다른 클럭 신호의 타이밍을 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0018] 본 발명은 특정 실시예 및 특정 도면에 관련하여 기재될 것이지만 본 발명이 이렇게 한정되는 것은 아니다.

도시된 도면은 단지 개념도에 불과하고 이렇게 한정되는 것은 아니다. 도면에서, 설명을 목적으로, 일부 요소들의 크기가 과장된 것일 수 있으며, 비례대로 그려지지 않았다. 치수 및 상대적 치수가 반드시 본 발명의 실시로의 실질적인 축소에 대응하는 것은 아니다.

[0019] 덧붙이자면, 본원에서 제 1, 제 2, 제 3, 등의 용어는 유사한 요소들을 구별하기 위해 사용되며, 반드시 순차 또는 연대 순서를 설명하는 것은 아니다. 용어들은 적정한 경우에서 상호교환적이고, 본 발명의 실시예들은 본원에서 기재되거나 설명된 것과 다른 순서로 동작할 수 있다.

[0020] 덧붙이자면, 본원에서 상부, 하부, 위에, 아래에, 등의 용어는 설명 목적으로 사용되며, 반드시 상대적 위치를 기술하는 것은 아니다. 이렇게 사용되는 용어들은 경우에 따라 상호 교환되고, 본원에서 기재되는 본 발명의 실시예들은 본원의 기재 또는 도시와 다른 배향으로 동작할 수 있다.

[0021] 용어 "포함하는"은 그 앞에 나열되는 수단들에 한정되는 것으로 해석되어서는 안된다. 그 밖의 다른 요소나 단계들을 제외하지 않는다. 언급된 특징, 정수, 단계, 구성요소의 제공을 특정하는 것으로 해석될 필요가 있지만, 하나 이상의 그 밖의 다른 특징, 정수, 단계, 구성요소, 또는 이들의 그룹의 존재 또는 추가를 또는 이들의 그룹 중 하나 이상을 배제하지 않는다. 따라서 "수단 A 및 B를 포함하는 장치"라는 표현은 구성요소 A와 B만으로 구성된 장치로 국한되지 않는다. 본 발명과 관련해 장치에서 관련 있는 구성요소가 A와 B임을 의미한다.

[0022] 종래의 파이프라인형 ADC는 순차 변환의 원리를 기초로 한다. 변환될 아날로그 신호는 먼저 샘플링되고, 제 1 스테이지 비교기에서 임계치와 비교된다. 그 후 신호는 증폭 배율 2로 증폭되고, 여기서 제 1 스테이지의 비트 값이 빠져서 나머지 신호(residue signal)가 도출된다. 이 나머지 신호는 제 2 스테이지의 입력 신호이다. 또 다시, 나머지 신호가 샘플링되고 제 2 스테이지 비교기에 의해 비교된다. 이 프로세스는, 필요한 비트 분해능까지, 다음 번 스테이지로 계속된다.

[0023] 본원에서 (나머지 발생 및 증폭에 해당하는) 비선형 신호 프로세싱을 이용하는 파이프라인형 아날로그-디지털

변환기가 제공되며, 여기서 각각의 ADC 임계치가 서로 다르게 교정된 비교기를 이용해 구현된다. 그 후 이러한 교정이 장치 오정합으로 인한 비선형성(nonlinearity)과 랜덤 오프셋(random offset)에 대해 보상될 수 있다. 덧붙여, 이진 검색을 위해 필요한 비교기 및 증폭기만 활성화되고, 이로써 낮은 전력 소비가 달성된다.

[0024] 파이프라인형 변환기는 폴딩(folding) 프론트-엔드를 더 포함하는 것이 바람직하다.

[0025] 파이프라인형 변환기는 n-비트 플래시 아날로그-디지털 변환기를 더 포함하는 것이 바람직하다.

[0026] 본 발명의 일 양태에 따르면, 도 1에 도시된 바와 같이, 아날로그 입력 신호를 디지털 신호로 변환하기 위한 파이프라인형 아날로그-디지털 변환기(PL ADC)가 제공된다. PL ADC는 입력 신호와 비교되기 위한 튜닝 가능한 임계치(이로써, 상기 지정 임계치들 중 둘 이상이 상이함)를 갖는 복수의 비교 수단(31), (32), (33)을 포함한다. 임계치는 교정 주기 동안 튜닝되고, 상기 포인트로부터 각각의 비교기가 지정 임계치를 가진다. PL ADC는 복수의 증폭 회로(34), (35)를 더 포함한다. 상기 복수의 비교 수단은 복수의 계층 레벨(36), (37)을 갖는 계층 트리 구조를 형성하도록 구성되고, 여기서 상기 계층 레벨들 중 하나 이상이 복수의 증폭 회로들 중 하나 이상의 증폭 회로와 연계된다. 복수의 계층 레벨은, 선행 계층 레벨의 비-선형 왜곡이 제거되도록 이전 계층 레벨의 출력(비교 결과)에 따라 튜닝 가능한 임계치를 설정하기 위한 수단을 포함한다.

[0027] 하나의 실시예에서, 인터리브형 구조를 포함하는 인터리브형 폴딩-파이프라인-플래시 ADC(또는 하이브리드 ADC)가 제공되고, 이 구조는 폴딩 프론트-엔드, PL ADC, 및 플래시 ADC를 포함한다. 아키텍처는 샘플링 주파수에 비례하는 전력 소비량을 제시한다. 일례에서, 4x 인터리브형 6비트 ADC가 제공된다. 도 2에 도시된 바와 같이, 각각의 변환 채널이 1비트 폴딩 프론트-엔드(81), 3비트의 파이프라인형 변환부(82), 및 2비트의 플래시 변환부(83)를 포함한다. 폴딩 프론트-엔드는 입력 신호를 샘플링하고, 입력 신호의 공통-모드 성분을 제거하며, 입력 신호의 극성을 결정하면서 입력의 차동 신호를 정류(rectify)한다. 예를 들어, PL ADC는 도 3에 도시된 3개의 계층 레벨(98), (99), (100)을 포함하는 계층 트리로 배열되는 7개의 비교 수단(91 내지 97)을 포함한다. 도시된 예에서, 각각의 비교 수단은 증폭 수단으로 연결된다.

[0028] 본원에서 아날로그 입력 신호를 디지털 출력으로 변환하기 위한 방법이 더 제공된다. 상기 방법은 이진 검색 알고리즘을 이행하는 것이 바람직하다. 병렬 검색보다 이진 검색을 이용함으로써, 능동 비교기의 개수가 감소되고, 이에 따라 전력 소비량이 감소된다. 제 1 계층 레벨의 하나 이상의 비교 수단이, 다음 번 계층 레벨의 하나 이상의 그 밖의 다른 비교 수단을 제어하도록 더 구성된다. 제어는, 비교 수단이 이전 단계의 비교 결과를 기초로 구조 내 경로를 선택하도록 배열되며, 복수의 비교 수단에 의해 구조가 형성된다. 이 경로는 도 2에 도시되어 있다. PL ADC는 변환의 3비트를 결정하고, 4개의 출력((94), (95), (96) 또는 (97)의 출력) 중 단 하나에서 나머지를 생성한다.

[0029] 일반적으로, 플래시 변환기에서는, 전력을 많이 소비하는 비교기를 필요로 하는 병렬 검색을 통해 비트가 결정된다. 병렬 검색 대신, 이진 검색을 이용함으로써, 능동 비교기의 개수가 감소되고, 따라서 전력 소비량이 감소된다.

[0030] 이러한 PL ADC는 저전력 및 고속의 동적 비선형 증폭기를 이용한다. 각각의 ADC 임계치에 대해 서로 다른 동적 비교기를 활성화시키고, 대응하는 비교기 임계치를 바람직한 입력으로 지정되는 값에 교정하며, 비선형 신호 프로세싱과 비교기 내 오프셋으로 인한 오류 모두 상쇄시킴으로써, 이를 증폭기에서 선형성(linearity) 요건이 피해진다. 이는, 각각 개별적으로 교정되는 증폭 회로와 조합되는 비교기 트리에 의해 얻어진다. 임계치 교정값은 증폭기와 비교기 결합에 대해 보정된다. 트리의 각각의 스테이지가 하나씩의 증폭 회로와 결합되거나(도 1 참조), 하나의 스테이지의 각각의 비교기가 하나씩의 증폭 회로와 결합될 수 있다(도 4 참조). 덧붙이자면, 이를 증폭 회로는 내장된 트랙 앤 홀드 증폭기일 수 있다(비교기/트랙 앤 홀드 증폭이 하나로 됨). 종래의 파이프라인에서는 "변환될" 신호가 체인(또는 캐스케이드)을 통해 전송된다. 본원에서 제공되는 것과 같은 신호 종속적 라우팅, 또는 경로 선택은 없다.

### 아키텍처

[0031] 일례에서, 4개의 인터리브형 아날로그-디지털 변환(ADC) 채널, 클럭 발생부 및 신호 재조합부(signal recombination)를 포함하는 하이브리드 ADC가 도시된다(도 2). 상기 클럭 발생부는  $F_8$  입력 신호를 가지며, 이로부터, 모두 주파수  $F_s/4$ 를 갖는 4개의 차동 쿼터 클럭 신호 및 4개의 저-스퀴(low-skew) 및 저-지터(low-jitter) 샘플링 신호를 발생한다. 예를 들어, PL ADC는 60GHz의 무선 장치에서 사용될 수 있다. 이러한 적용예

를 위한 아날로그-디지털 변환기는 최대 4GS/s의 샘플링 주파수를 필요로 한다. 각각의 ADC 채널은 1비트 폴딩 프론트 엔드, 3비트 파이프라인형 이진 검색 변환부, 2비트 플래시를 포함하여, 총 6비트 공칭 변환이다. 신호 재조합부는, 2-입력 멀티플렉서의 2개의 스테이지로 구성되고, 여러 다른 인터리브된 채널 출력을 6개의 전속 비트 스트림(full-speed bit stream)으로 조합한다. 임계치 교정을 이용하여 완화된 선형성 및 정합 제약을 갖는 정적 선형성(static linearity)이 개선되지만, 복잡도 때문에 타이밍 교정이 피해진다.

### [0033] 클럭 발생부

[0034] 클럭 발생부는 두 세트의 클럭 신호를 발생하는데, 둘 모두, 샘플링 주파수의 4분의 1로 동작한다. 제 1 신호 세트는, ADC에서 비-핵심적(non-critical) 타이밍 인스턴스를 제어하고, 서로 다른 채널들을 서로에 대해 동기화시키기 위해 사용된다. 이를 신호는 큰 팬-아웃(fan-out)을 가지며, 따라서 큰 구동 세기(drive strength)를 가진다.

[0035] 제 2 신호 세트는, 하부판 샘플링 스위치를 직접 구동하기 위해 사용되는 높은 정확도의 샘플링 신호이다. 이들 신호의 타이밍 스케일 확산은 수 피코초(picosecond) 수준일 필요가 있고, 낮은 지터가, 바람직하다(일부 예에서는 요구된다). 이러한 속성을 얻기 위해, 공용 인버터가 사용되어 샘플링 신호를 구동시키는데, 이때 통과 게이트(pass gate)를 이용해 인버터의 출력이 실제 샘플링 스위치에게로 게이트-제어된다. 인버터 출력의 하강 에지(falling edge) 또는 상승 에지(rising edge) 바로 전, 적합한 때에 통과 게이트가 활성화된다. 그 후 샘플링 신호의 하강 에지의 타이밍 확산은 통과 게이트의 온-저항과, 각각의 샘플링 스위치 및 그 기생 소자(parasitics)에 의해 제공되는 정확한 부하에 따라서만 달라진다. 이러한 확산은 중간 장치 크기를 이용할 때라도 낮게 만들어질 수 있다: (NMOS와 PMOS 둘 모두에 대해) 2마이크로미터 장치를 이용해 시뮬레이트된 표준 편차 500fs가 획득되었다. 샘플링 스위치 기생 소자들 간 오정합(mismatch)이 측정치들 간 이러한 정합을 열화시킬 수 있다. 클럭 입력에서 샘플링 신호까지 짧은 경로를 유지함으로써, 이들 신호에 대한 낮은 지터가 얻어질 수 있다.

### [0036] 1비트 폴딩 프론트-엔드

[0037] 폴딩 프론트-엔드는 입력 신호를 샘플링하고, 우선 공통 모드(common-mode) 성분을 제거한다. 결과적 차동 신호의 극성은 비교기(1)에 의해 판단되고, 이 비교기(1)에 의해 제어되는 초퍼(chopper)를 이용해 뒤 이은 ADC의 범위내이도록 신호가 정류된다. 완전한 변환기(하이브리드 ADC)에서 폴딩 스테이지가 구현되는 주 이유는 교정 복잡도(calibration complexity)를 낮추기 위함이다. 폴딩 스테이지의 개념도가 도 5에 도시되어 있다.

[0038] 상이한 클럭 신호들의 타이밍이 도 7에 나타나 있다. "clkBottomPlate"이 로우(low)가 될 때, 하부판(bottom plate)의 스위치가 비활성화되고, 샘플링 커페시턴스  $C_s$  대부분이 부유 커페시턴스로 유지된다(일부 기생 커페시턴스가 하부판에 존재). 또한 2 인버터 딜레이( $2 \times t_{inv}$ ) 후에 "clkTopPlate"이 또한 로우(low)가 되고, 상부판 스위치가 불능이 된다. 1 인버터 딜레이( $t_{inv}$ ) 후에 "clkShort"가 하이(high)가 되고 샘플링 커페시턴스  $C_s$ 의 2개의 상부판이 단락된다. 그 후 샘플링된 입력 전압이  $C_s$ 의 상부판에서 하부판으로 이동될 것이고, 거기서 차동 전압(differential voltage)이 발생된다.

$$\frac{C_s}{C_s + C_{par}}$$

[0039] 전하 주입이 없는 경우, 하부판 노드가 0의 공통 모드 전압과, 비  $\frac{C_s}{C_s + C_{par}}$  (여기서,  $C_{par}$ 는 하부판 노드의 총 기생 용량)에 따라 달라지는 차동 전압을 가질 것이다. 하부판 노드들 중 하나가 접지 전위 아래가 되는 것을 막기 위해, 하부판의 공통 모드 전압은, "clkShort"에 의해 제어되는 두 커페시턴스  $C_{cm}$ 만큼 증가된다.

[0040] 2개의 하부판 노드의 기생 커페시턴스들이 정확히 정합되지 않는 경우, 동일한 크기의 반대 부호를 갖는 입력 전압에 의해 발생되는 두 전압이 하부판 노드에 동일한 전압을 야기하지 않을 것이다. 이는, 뒤 이은 ADC의 임계치에 무관하게, 정류 동작이 수행되는 경우 오류를 초래할 것이다. 2개의 하부판 노드의 커페시턴스의 충분한 정합을 보장하기 위해, 디지털 방식으로 제어 가능한 교정 커페시터(calibration capacitor)의 두 뱅크가 하부판 노드에 추가된다.

[0041] "clkShort"의 상승 에지로부터 4 인버터 딜레이( $4 \times t_{inv}$ ) 후에, "clkComp"의 상승 에지에 의해 비교기가 활성

화된다. 이 상승 에지에서 1 인버터 딜레이 후에, 노드  $out_m$  및  $out_p$ 를 클램핑하는 스위치가 꺼진다. 비교기의 결정이,  $C_s$ 의 하부판의 전압을 출력 노드들과 공유하는 초퍼 스위치의 2개의 세트 중 하나를 비동기식으로 활성화시키며, 폴딩 프론트-엔드의 동작을 완료한다.

[0042] 다음의 절차를 바탕으로  $C_{par}$  커패시터가 교정된다. 다음 번 스테이지의 제 1 임계치가 ADC 범위의 양의 절반과 음의 절반에서 교정된다. 이들 2개의 값은 비교되고, 중앙값이 "올바른 것"으로 가정되고 설정된다. 그 후, 이 임계치를 기초로,  $C_{par}$  값이 적응(adapt)될 수 있다.

[0043] 도 5는 폴딩 프론트-엔드의 단순화된 개략도를 도시하고, 도 6은 폴딩 프론트-엔드의 과정을 도시한다. 입력 신호의 공통 모드를 제거하면서 입력 신호를 샘플링하고 정류한다.  $S_1$  스위치가 폐쇄될 때, 입력 전압이  $C_s$  양 단에서 추적된다. 하강  $\Phi_1$  에지에서  $C_s$ 에 있는 전하가 고정된다. 하부판은 접지, 상부 판은 샘플링된 입력 전압을 가지며, 전하 주입은 무시한다.  $S_2$  폐쇄가 상부판을 단락시키고, 하부판에서 차동 전압을 발생시키고, 이때 누설 커패시턴스로 인해 약간의 손실이 있다. 그 후, 폴딩 스테이지 비교기가 활성화되며, 자신의 결정에 따라, ( $t_1$ 에서) 초퍼에서 하나의 스위치 세트를 폐쇄하고, 하부판의 전하를 다음 번 스테이지와 공유하여, 차동 출력 전압이 항상 양(positive)이도록 한다. 공통 모드 출력은 공통 모드 입력과 무관하며, 이는 ADC 백-엔드에 대한 공통 모드 전압을 고정시키고, 공통 모드 입력 범위를 상당히 증가시킨다. 덧붙이자면, 인가된 공통 모드 전압은 교정 동작과 보통 동작에서 상이할 수 있다.

#### [0044] 파일라인 이진 검색

#### [0045] 일반 원리

[0046] 일반적으로 파일라인 이진 검색(PLBS: pipelined binary search) 변환기는, 스테이지당 1비트 PLBS의 3비트에 대해 도 1에 도시되어 있는 바와 같이, 비선형 멀티플라잉 디지털-아날로그 변환기(NLMDAC: non-linear multiplying digital to analog converter)의 캐스케이드 및 비교기의 트리로 구성된다. NLMDAC의 목적은 자신의 입력 신호를 샘플링하고, 이를 증폭하고, 출력에서 임의의 값을 빼거나/더해서 0에 가깝게 하는 것이다. 종래의 파일라인형 변환기에서, 제 1 스테이지 MDAC에 대한 선형성 요구가 바람직한 전체 선형성과 동일하다. 본원에서, 각각의 PL ADC 임계치에 대해 튜닝 가능한 임계치를 갖는 상이한 비교기를 이용함으로써, 상당한 비선형성이 허용된다. 시작 교정 또는 배경 교정 동안, 비교기 임계치가 튜닝되어, 원하는 ADC 임계치에 대해 선행하는 NLMDAC의 캐스케이드의 비선형 효과를 상쇄시킨다. NLMDAC에 대한 유일한 요구는 NLMDAC가 모노토닉(monotonic)하다는 것이기 때문에, 전력 절약이 가능하다.

#### [0047] 구현 예

[0048] 이진 검색을 이용하는 PL ADC의 입력이 폴딩 프론트-엔드의 출력이다. 여기서 선택된 접근법은 도 3에 도시된 바와 같은 일반적인 PLBS 원리를 수정하는 것이다. 선택된 구현 예와 일반 원리 간에 3가지 중요한 차이가 있다.

[0049] 첫째, 각각의 NLMDAC의 랠셉 기능이 현재 스테이지 NLMDAC에서 다음 번 스테이지 NLMDAC로 이동된다. 랠셉을 다음 번 스테이지로 이동시킴으로써, NLMDAC 출력 노드에서의 스윙 전압이 증가하지만, NLMDAC 출력 노드의 낮은 스윙 전압 및 선형성 요구가 가정되면, 이는 문제가 되지 않는다.

[0050] 둘째, NLMDAC가 두 번째와 그 이후 스테이지로 분할될 수 있어서, 이들 스테이지 각각에 2개의 비교기와 2개의 분할된 NLMDAC에 의해 부하가 실린다. 동적으로 만들어지고, 필요할 때만 클러킹된다면, 각각의 NLMDAC의 부하가 파일라인 전체에 걸쳐 일정하게 유지되면서, 이렇게 하는 것과 연계된 어떠한 파워 페널티(power penalty)도 없다. 그 후 이전 스테이지로부터의 랠셉 기능이 이들 NLMDAC 내에 하드웨어링될 수 있다. 이전 스테이지 비교기의 결정이, 이들 중 어느 것이 활성화될지를 결정한다. 도 3에 스테이지 2의 2개의 동일한 NLMDAC의 입력과 출력이 스위칭된 극성으로 연결되어 있으며, 따라서 하나의 NLMDAC가 자신의 입력에서 전압을 뺀다면, 다른 NLMDAC가 동일한 값을 더한다.

[0051] 셋째, 이 변환기의 입력 범위는 0V 차동 전압을 중심으로 대칭인 것은 아니다. 이전 스테이지(폴딩 프론트 엔드 스테이지)에서 입력 신호가 정류되기 때문에, 양의 차동 신호만 변환되어야 한다. 제 1 스테이지의 입력

신호에서 입력 범위의 절반을 뺏으로써, 뒤 이은 스테이지가 대략 0에서 차동이 될 수 있다.

#### [0052] 회로 블록

도 4에서 도시된 바와 같이, 선택된 구현예에서 각각의 NLMDAC(44)이 튜닝 가능한 임계치를 갖는 비교기와 병렬연결된다. 이에 따라 비교기/트랙 앤 홀드 증폭기(CTHA)라고 불리는 하나의 단일 구조로 병합되었다. 끝에서 두 번째 스테이지(penultimate stage)에 있는 CTHA를 제외한 모든 CTHA는 2개의 CTHA의 부하를 가지는데, 이때, 이전 스테이지의 CTHA는 "부모"라고 일컬어지고, 뒤 이은 스테이지의 CTHA는 "자식"이라고 일컬어진다. 끝에서 두 번째 스테이지의 CTHA는 단지, 각각 마지막 스테이지에 있는 2개의 비교기에 의한 부하를 받는다.

비교기/트랙 앤 홀드 증폭기(CTHA)가 도 8에 개략적으로 도시되어 있으며, P1, P4 및 P5의 소스 상의 NMOS 리셋 스위치는 명료함을 위해 생략되었다. 회로는 3개의 부분(동적 전치증폭기, 래치, 및 출력 드라이버)으로 구성된다. 동적 전치증폭기와 래치는 조합되어 비교기가 된다.

동적 전치증폭기와 출력 드라이버는 조합되어 트랙 및 홀드 증폭기를 형성할 수 있다. 클럭 신호가 로우(low)가 될 때, 트랜지스터 쌍 N1 및 N2이 꺼지고, P2 및 P3은 켜진다. 노드 Dm 및 Dp는 입력 전압에 따라 달라지는 속도로 접지에서 Vdd까지로 풀업된다. 이러한 충전 상태 동안 트랜지스터 P5는 켜지고(on), 노드 aOutp 및 aOutm를 충전한다. Dp 및 Dm에서의 전압이 충분히 높을 때, P5 쌍이 꺼지고(off), 회로에 더 이상 전류가 흐르지 않아서, aOutp 및 aOutm에서의 전압이 이들 노드에 추가되는 전하량에 의해 고정된다.

따라서 입력 전압이 시간(P5 쌍이 켜져 있는 시간)으로 변환되고, 다시 전압(출력 커패시터에 추가되는 전하)으로 변환된다. 출력 전압이 입력 전압에 따라 달라지기 때문에, 트랙 앤 홀드 기능이 탈성된다.

트랜지스터 P4는 다음의 경우에 공통 모드(CM) 안정화를 이룬다: CM 레벨이 하락하고, P5가 더 짧은 시간 동안 활성상태이지만, P4의 증가된 오버드라이브(overdrive)로 인해 이들이 출력 커패시터로부터 인출하는 전류가 증가되는 경우. PVT(프로세스, 전압, 온도) 변동을 통해 CTHA의 임계치 및 이득을 제어하기 위해, 그리고 뒤 이은 스테이지에 가장 잘 맞도록 입력-출력 특성을 개별적으로 변경시킴으로써 입력-출력 특성의 내재적 비선형성에 대처하기 위해 가변 커패시턴스가 P5의 게이트 노드와 드레인 노드 모두에 추가된다.

이 CTHA가 차동적으로 균형을 이루고, 어떠한 오정합도 존재하지 않는다면, 비교기 임계치는 0이고, 입력 출력 관계는  $out \approx in \times gain$ 로 주어지며, 여기서 gain(이득)은 트랜지스터 크기와 Cd 및 Ca의 선택된 값에 의해 결정된다. 동적 전치증폭기 회로가 어떤 식으로든 균형을 이루지 않는 경우, 비교기 임계치가 값  $V_{offset}$ 으로 변경될 것이고, 입력 출력 관계는  $out \approx (in - V_{offset}) \times gain$ 로 변경된다. 즉, 비교기가 자신의 임계치에 있을 때 출력이 거의 0이다(비교기는 래치와 동적 전치증폭기를 결합함으로써 형성된다).

이 속성은 특정 구현예의 경우 매우 편리하다. PLBS 변환기가 0 내지  $V_{IR}$ 의 입력 범위를 가진다고 가정될 때, 제 1 비교기는  $V_{IR}/2$ 의 임계치를 가져야 하고, 제 1 MDAC는 입력에서  $V_{IR}/2$ 를 빼야 하는데, 이 두 가지 모두는, P1 쌍의 폭의 의도적인 불균형을 지니는 CTHA를 이용함으로써 명쾌하게 이뤄질 수 있다. 이득이 2이도록 선택된 경우, 다음 번 PLBS 스테이지가  $-V_{IR}$  내지  $+V_{IR}$ 의 전압을 처리해야 한다. 다음 번 스테이지가 교환되는 차동 입력을 갖는 2개의 CTHA를 갖기 때문에, 트리 내 모든 CTHA가 동일한 불균일성을 공유할 수 있도록 각각의 CTHA는 0 내지  $V_{IR}$ 의 신호를 처리해야 한다.

실제로, 비교기 임계치가 선행하는 증폭기의 비선형성을 올바르게 상쇄시키도록, CTHA 트리의 모든 레벨에서 교정을 필요로 한다. 먼저, 부모 임계치를 설정하도록 Cd 커패시터가 변경된다(이로써, 가장 높은 계층 레벨의 비교기 임계치의 교정이 이뤄짐). 도 4에 도시된 바와 같이, 부모 임계치는 제 1 레벨의 CTHA(41), (44)의 임계치이다. 그 후, Ca 커패시터가 사용되어, 두 자식 CTHA 모두에 대한 대략적인 임계치 튜닝을 한다. 제 1 자식 CTHA는 도 4에 도시되어 있으며 (42)와 (45)의 조합이고, 제 2 자식 CTHA는 (43)과 (46)의 조합이다. Ca 커패시터가 사용되어, 대응하는 ADC 임계치가 인가될 때 증폭기 출력을 다음 레벨의 교정되지 않은 비교기 임계치에 가깝도록 설정할 수 있다.

도 9는 Ca 커패시턴스의 최댓값과 최솟값에 대한 시뮬레이트된 입력-출력 특성을 도시한다. 높은 입력 전압에서 출력 전압은 노드 aOutm에서의 Ca(또는  $C_{out+}$ )보다 노드 aOutp에서의 Ca(또는  $C_{out+}$ )에 훨씬 더 감응하며(도

8 참조), 낮은 입력 전압에서는 그 반대이다. 이는 직관적인 것에 부합한다: 양의 출력 전압이 높을 때, 많은 전하가 이 노드에 쌓이고, 커패시턴스 값의 변화가 높은 전압 변화를 초래한다. 제안되는 교정 절차에서 이러한 입력-종속적 감도가 활용된다.

[0062] CTHA를 위해 제안된 교정 절차는 다음과 같다:

[0063] 1. 부모 CTHA의 원하는 ADC 임계치를 적용하고 ADC 출력을 관찰하기.

[0064] 2. Cd 커패시터를 변경하고, CTHA 판정이 가능한 50%의 양, 50%의 음에 가깝도록 정합될 때까지 부모 CTHA 임계치를 이동시키기

[0065] 3. 첫 번째(가장 높은 전압) 자식 CTHA의 원하는 ADC 임계치를 적용하고 ADC 출력을 관찰하기

[0066] 4. 첫 번째 자식 CTHA의 임계치가 이러한 Ca에 대한 연속적인 설정치에 대한 부모 CTHA 출력들 사이에 있도록, 부모 CTHA의 aOutp에서의 커패시터 Ca(또는 Cout+)를 변경하기

[0067] 5. 두 번째 자식 CTHA의 원하는 ADC 임계치를 적용하고 ADC 출력을 관찰하기

[0068] 6. 두 번째 자식 CTHA의 임계치가 이 Ca에 대한 연속적인 설정치에 대한 부모 CTHA 출력들 사이에 있도록, aOutm에서의 커패시터 Ca(또는 Cout-)를 변경하기

[0069] 7. 두 자식 CTHA 모두에 대해 단계 1부터 반복하기

[0070] 교정 프로세스의 결과는 도 10에 도시되어 있다. 제 1 단계에서, 다음 스테이지의 최고 임계치( $th_{top}$ )가 적용되고, 증폭기 출력이, 이 임계치를 이행하는 비교기의 교정 범위 내에 속하도록 노드 aOutp에서의 Ca가 변경된다. 그 후, 다음 스테이지의 최저 임계치( $th_{bottom}$ )가 적용되고, 노드 aOutm에서의 Ca가 마찬가지로 변경된다. 그 후, 동일한 프로세스(먼저 비교기 임계치를 교정하고, 그 다음에 Ca 커패시턴스를 교정)를 이용해 다음 PLBS 스테이지가 교정될 수 있다. 이는 이하에 나열된 것을 가정한다:

[0071] \* 출력 전압이 양(positive)일 때, aOutm 펀에서의 Ca 커패시터 값에 대한 아날로그 출력 전압의 감도는 낮다(따라서 어떠한 반복도 필요하지 않다).

[0072] \* Ca 커패시터의 교정 스텝이 자식 Cd 커패시턴스의 교정에 의해 가능한 임계치 범위보다 작다.

[0073] "공통 모드" Cd 커패시턴스가 하나의 행의 이득을 변화시켜, 다음 번 행이 교정될 수 없을 경우 상이한 공통 모드 커패시턴스를 이용해 한 행을 개정하는 것이 필요할 수 있음에 주목하는 것이 중요하다.

#### 클럭킹

[0075] 도 11의 회로를 이용해 각각의 자식 CTHA의 클럭킹이 이뤄진다. 부모 CTHA가 적절하게 재생된 경우, outm 또는 outp 노드가 접지까지로 방전될 것이다. clkG가 로우(low)가 될 때, 내부 노드가 Vdd까지로 상승되고 적정 클럭 신호가 로우(outm 또는 outp)가 된다. clkG 신호가 하이(high)가 될 때, 모든 클럭 신호(outm 및 outp)가 하이가 되고 다음 행의 CTHA는 재설정(reset)된다.

[0076] 상이한 클럭 신호들의 타이밍의 일례가 도 12에 도시되어 있다. 여기서  $clkG_{n}$ 는 n번째 행의 모든 CTHA에 의해 공유되는 전역 클럭(global clock)이다. 신호  $clkG_{n+1}$ 는 항상,  $clkG_n$ 에 대해  $T_{clk}/4$ 만큼 지연된다. 결과적으로, 각각의 비교기가 동일한 재생 시간을 가짐을 보장하기 위해, 비교기는  $T_{clk}/4 - t_{Delay}$  내에 결정해야 한다. 도시된 그래프에서, 중앙 재생은 느린다. 따라서 다음 비교기를 위한 결정 시간이 더 짧아진다. 그러나 이 비교기는 더 큰 입력 신호를 가질 것이고, 따라서 더 빠르게 결정할 것이다.

[0077] 일반적으로, PLBS 트리가 적절하게 동작하기 위해, 각각의 비교기는  $T_{clk}/2 - t_{Delay} - t_{Aperture}$  내에 결정해야 하고, 임의의 연속하는 2개 비교기는  $3 \cdot T_{clk}/4 - 2 \cdot t_{Delay} - t_{Aperture}$  내에 결정해야 하며, 임의의 연속하는 3개의 비교기는  $T_{clk} - 3 \cdot t_{Delay} - t_{Aperture}$  내에 결정해야 하며, 그 이상의 경우에서도 마찬가지이다. 여기서,  $t_{Delay}$ 는 도 11의 회로로부터의 게이트 딜레이이고,  $t_{Aperture}$ 는 다음 CTHA의 개구 시간(aperture time)이다.

[0078] 변환기의 폭에 걸쳐 단 2개의 clkG 신호만 분산되며 필요한 경우 반전(invert)된다. 이들은 앞서 기재된 클럭 발생부에서 발생되는 더 낮은 정확도의 높은 구동 세기의 신호이다.

[0079]

인코더

[0080]

인코더(84)는 비교기 결정을 3비트 그레이 코드로 변환한다. 인코더는 각각의 행에서의 clkC 출력에 의해 제어되는 프리차지/디스차지 ROM 라인으로 구성된다. 행들 중 하나에서 준안정적 상태(metastability)가 발생하는 경우, 이 행에서 시작하는 모든 비트가 0이 될 것이다.

[0081]

플래시 변환기

[0082]

플래시 변환기(83)는 PLBS 변환의 3개의 스테이지의 출력을 변환하며, 이는 구조적으로 비선형 왜곡을 추가할 것이다. 이러한 비선형 왜곡에 대처하기 위해, 재설정 가능한 임계치를 갖는 8개의 상이한 플래시 변환기가 필요하다. 그 후, PLBS 트리의 마지막 레이어 내 각각의 CTHA는, 서로 반전된 입력을 갖는 2개의 동일한 플래시 변환기에 의해 부하를 받는다. 그 후, 이들 2개의 플래시 변환기 중 어느 것이 활성화되는지는 비교기의 결정에 달렸다. 교정 단계 중에, 각각의 플래시 변환기 임계치가 적응되거나 조절되어, 선행하는 CTHA 스테이지의 비선형성 및 오정합을 상쇄시킬 수 있다.

**도면****도면1**

## 도면2

## 도면3

도면4

도면5

## 도면6

## 도면7

## 도면8

도면9

도면10

도면11

도면12