(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5998521号

(P5998521)

(45) 発行日 平成28年9月28日(2016.9.28)

(24) 登録日 平成28年9月9日(2016.9.9)

(51) Int.Cl.

F 1

HO1L 21/336 (2006.01)

HO1L 29/788 (2006.01)

HO1L 29/792 (2006.01)

HO1L 21/8247 (2006.01)

HO1L 27/115 (2006.01)

HO1L 29/78

HO1L 27/10 434

請求項の数 6 (全 14 頁)

(21) 出願番号 特願2012-41221 (P2012-41221)

(22) 出願日 平成24年2月28日 (2012.2.28)

(65) 公開番号 特開2013-179122 (P2013-179122A)

(43) 公開日 平成25年9月9日 (2013.9.9)

審査請求日 平成27年2月13日 (2015.2.13)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100116665

弁理士 渡辺 和昭

(74) 代理人 100164633

弁理士 西田 圭介

(74) 代理人 100179475

弁理士 仲井 智至

(74) 代理人 100107261

弁理士 須澤 修

(72) 発明者 福本 洋平

山形県酒田市十里塚166番地3 東北エプソン株式会社内

最終頁に続く

(54) 【発明の名称】不揮発性半導体メモリー及び不揮発性半導体メモリーの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

不揮発性半導体メモリーであつて、

シリコン基板と、

第1のシリコン酸化膜と、

第2のシリコン酸化膜と、

第3のシリコン酸化膜と、

第1のシリコン窒化膜と、

第2のシリコン窒化膜と、を含み、

前記第1のシリコン酸化膜および前記第3のシリコン酸化膜は、前記シリコン基板上に積層され、

前記第1のシリコン窒化膜は、前記第1のシリコン酸化膜上に積層され、

前記第2のシリコン酸化膜は、前記第1のシリコン窒化膜上に積層され、

前記第3のシリコン酸化膜の厚さは、前記第1のシリコン酸化膜の厚さよりも薄く、

前記第2のシリコン窒化膜は、第1の部分が前記第1のシリコン酸化膜に接すると共に第2の部分が前記第3のシリコン酸化膜に接しており、

前記第3のシリコン酸化膜は、厚さが0より大きく22以下であることを特徴とする不揮発性半導体メモリー。

## 【請求項 2】

更に、前記シリコン基板内にシリサイド領域を含み、

前記シリサイド領域は、前記第3のシリコン酸化膜に接することを特徴する請求項1に記載の不揮発性半導体メモリー。

【請求項3】

更に、前記第2のシリコン酸化膜上に第1の電極を有し、

前記第2のシリコン窒化膜の第3の部分が前記第1の電極に接していることを特徴とする請求項1又は2に記載の不揮発性半導体メモリー。

【請求項4】

前記第2のシリコン窒化膜は、厚さが45以上であることを特徴とする請求項1乃至3のいずれか一項に記載の不揮発性半導体メモリー。

【請求項5】

不揮発性半導体メモリーの製造方法であって、

シリコン基板上に、第1のシリコン酸化膜を成膜する第1の工程と、

前記第1のシリコン酸化膜上に、第1のシリコン窒化膜を成膜する第2の工程と、

前記第1のシリコン窒化膜上に、第2のシリコン酸化膜を成膜する第3の工程と、

前記第1のシリコン酸化膜、前記第1のシリコン窒化膜及び第2のシリコン酸化膜を所定の形状にパターニングする第4の工程と、

前記第4の工程の後に第2のシリコン窒化膜を成膜する第5の工程と、を含み、

前記第4の工程において、前記第1のシリコン窒化膜及び前記シリコン基板が露出され、

前記第4の工程と前記第5の工程の間の第6の工程において、前記シリコン基板が露出された領域に前記第1のシリコン酸化膜より膜厚が薄い第3のシリコン酸化膜が形成され、

前記第3のシリコン酸化膜は、厚さが0より大きく22以下であり、

前記第5の工程において、前記第1のシリコン窒化膜と前記第2のシリコン窒化膜とが接することを特徴とする不揮発性半導体メモリーの製造方法。

【請求項6】

不揮発性半導体メモリーの製造方法であって、

シリコン基板上に、第1のシリコン酸化膜を成膜する第1の工程と、

前記第1のシリコン酸化膜上に、第1のシリコン窒化膜を成膜する第2の工程と、

前記第1のシリコン窒化膜上に、第2のシリコン酸化膜を成膜する第3の工程と、

前記第1のシリコン酸化膜、前記第1のシリコン窒化膜及び第2のシリコン酸化膜を所定の形状にパターニングする第4の工程と、

前記第4の工程の後に第2のシリコン窒化膜を成膜する第5の工程と、を含み、

前記第4の工程において、前記第1のシリコン窒化膜が露出され、前記第1のシリコン酸化膜をエッチングすることで前記第1のシリコン酸化膜より膜厚が薄い第3のシリコン酸化膜が形成され、

前記第3のシリコン酸化膜は、厚さが0より大きく22以下であり、

前記第5の工程において、前記第1のシリコン窒化膜と前記第2のシリコン窒化膜とが接することを特徴とする不揮発性半導体メモリーの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、シリコン酸化膜-シリコン窒化膜-シリコン酸化膜の積層構造を有する不揮発性半導体メモリー、及び、該不揮発性半導体メモリーの製造方法に関する。

【背景技術】

【0002】

従来、読み出し及び書き込みを繰り返し行うことが可能な、EEPROMと呼ばれる半導体メモリーが存在する。EEPROMは電源を切っても記憶したデータが消滅しない不揮発性半導体メモリーであり、特にデータの書換えが一部又は全部に対して一括して行うことができるものをフラッシュメモリーと呼ぶ。

10

20

30

40

50

## 【0003】

フラッシュメモリーは、NAND型及びNOR型と呼ばれるタイプがあるが、いずれの場合においてもメモリセル自体は類似の構造を有し、該メモリセルの構造には、フローティングゲート型と呼ばれるものとチャージトラップ型とよばれるものがある。フローティングゲート型及びチャージトラップ型のいずれもMIS型トランジスターの構造を有する。フローティングゲート型は、ゲート絶縁膜内にフローティングゲート電極を設け、該フローティングゲート電極に電荷を保持することでデータの記憶を行うものである。これに対し、チャージトラップ型は、ゲート絶縁膜がシリコン酸化膜 - シリコン窒化膜 - シリコン酸化膜の積層構造(ONO構造)を有し、シリコン窒化膜とシリコン基板側のシリコン酸化膜との界面近傍に存在する離散トラップに電荷を蓄積することによりトランジスターの閾値が変化することでデータが保持されるものである。チャージトラップ型には、SONOS(Silicon Oxide Nitride Oxide Semiconductor)型やMONOS(Metal Oxide Nitride Oxide Semiconductor)型と呼ばれるものがある。尚、フローティングゲート型及びチャージトラップ型のいずれにおいても、シリコン基板側の酸化膜がトンネル酸化膜と呼ばれる。

10

## 【0004】

以前はフローティングゲート型が主流であったが、近年はチャージトラップ型が採用される例が増える傾向にある。その理由としては、フローティングゲート型の場合はフローティングゲート層に電荷を捕獲させるためにトンネル酸化膜に対して高い絶縁性が要求されるが、チャージトラップ型の場合には、絶縁膜であるシリコン窒化膜の離散トラップに電荷を捕獲させることから、フローティングゲート型に比較してトンネル酸化膜の一部の絶縁性が多少低下しても問題とならない場合が多いという利点をもつことが挙げられる。また、トンネル酸化膜自体の厚さもチャージトラップ型の方が薄くすることが可能であることから、チャージトラップ型の方がデータの書き込み電圧を低くすることができることも大きな利点である。

20

## 【0005】

上述した理由などによりチャージトラップ型が好まれるようになってきているが、データの保持特性、書き込み / 消去の繰り返し耐性をより向上させたいという要求がある。該要求に対応するために、特許文献1には、トラップの形成層として、原子層化学的気相成長法により成膜された、 $SiO_2$ と $Si_3N_4$ の中間組成の $SiO_xNy$ 薄膜を設けることが記載されている。トラップ層をこのようにすることで、トラップを高密度で制御性よく、所望の深さに形成することができ、データの保持特性、書き込み / 消去の繰り返し耐性を向上させることができること、メモリー効果としての閾値電圧の差を大きくとることができるので、多値化にも有利となることが記載されている。

30

## 【先行技術文献】

## 【特許文献】

## 【0006】

## 【特許文献1】特開2002-222876号公報

## 【発明の概要】

40

## 【発明が解決しようとする課題】

## 【0007】

しかしながら、閾値電圧の差を大きく取ることが可能なトラップ層を設けたとしても、製造工程においてトラップ層に電荷が捕獲され、該電荷が捕獲されたまま製造工程が終了すると、該電荷が捕獲されていない状態と比較して閾値電圧が変動するという問題がある。

## 【課題を解決するための手段】

## 【0008】

本発明は、上述した問題若しくは課題の少なくともひとつを解決するためになされたものであり、以下の適用例若しくは実施形態として実現することが可能である。

50

## 【0009】

## [適用例1]

本適用例にかかる不揮発性半導体メモリーは、シリコン基板と、第1のシリコン酸化膜と、第2のシリコン酸化膜と、第1のシリコン窒化膜と、第2のシリコン窒化膜と、を含み、前記第1のシリコン酸化膜は、前記シリコン基板上に積層され、前記第1のシリコン窒化膜は、前記第1のシリコン酸化膜上に積層され、前記第2のシリコン酸化膜は、前記第1のシリコン窒化膜上に積層され、前記第2のシリコン窒化膜は、第1の部分が前記第1のシリコン窒化膜に接すると共に第2の部分が前記シリコン基板に接するように積層されていることを特徴とする。

## 【0010】

10

この構成によれば、不揮発性半導体メモリーの電荷の保持部が、シリコン基板上に積層された第1のシリコン酸化膜、第1のシリコン窒化膜及び第2のシリコン酸化膜により構成され(ONO構造)、第2のシリコン窒化膜が第1のシリコン窒化膜及びシリコン基板に接している構成を有することで、製造時における所定の工程においてONO構造に捕獲された余分な電荷を他の所定の工程において第2のシリコン窒化膜を介してシリコン基板に拡散することができ、該余分な電荷の閾値電圧に対する影響を低減することができる。これにより、メモリーの動作の高速化・低電圧化を図ることができる。

## 【0011】

ONO構造は、その製造過程において、第1のシリコン窒化膜が電荷を捕獲した状態となり、電荷を捕獲した状態が維持されたまま製造が終了される場合がある。この場合、第1のシリコン窒化膜に捕獲されたままとなる電荷の量が、不揮発性半導体メモリーとしての動作に影響を与える可能性がある。第1のシリコン窒化膜に捕獲されたままの電荷がより多いと、メモリーとしての書き込み動作における閾値電圧がより高くなる。閾値電圧がより高くなると、不揮発性半導体メモリーとして書き込み動作を行った場合に、第1のシリコン窒化膜に新たに捕獲される電荷の量がより少なくなることが考えられる。これは、メモリーとしての読み出し動作のときに流れる電流の量に影響し、メモリーのデータ出力に所定の変化を起こさせるのにより時間を要することになる。このため、第1のシリコン窒化膜により多くの電荷が捕獲されたまま製造工程の終了した不揮発性半導体メモリーは、高速・低電圧動作に不向きな不揮発性半導体メモリーとなる。また、メモリーの閾値電圧が設計値から変動するため、閾値電圧の変動を伴うチャネル部の不純物濃度の変更・調整に制限がある。

20

## 【0012】

本適用例にあるように、第2のシリコン窒化膜の第1の部分が第1のシリコン窒化膜に接し、第2のシリコン窒化膜の第2の部分がシリコン基板に接することにより、所定の工程において第1のシリコン窒化膜に捕獲された電荷を、該所定の工程の後の他の所定の工程において第2のシリコン窒化膜を介してシリコン基板に拡散させることができるとなる。これにより第1のシリコン窒化膜に捕獲されたままとなる電荷の量の低減化を図ることができ、不揮発性半導体メモリーの動作を高速化・低電圧化することができる。

30

## 【0013】

## [適用例2]

40

本適用例にかかる不揮発性半導体メモリーは、シリコン基板と、第1のシリコン酸化膜と、第2のシリコン酸化膜と、第3のシリコン酸化膜と、第1のシリコン窒化膜と、第2のシリコン窒化膜と、を含み、前記第1のシリコン酸化膜は、前記シリコン基板上に積層され、前記第1のシリコン窒化膜は、前記第1のシリコン酸化膜上に積層され、前記第2のシリコン酸化膜は、前記第1のシリコン窒化膜上に積層され、前記第3のシリコン酸化膜の厚さは、前記第1のシリコン酸化膜の厚さよりも薄く、前記第2のシリコン窒化膜は、第1の部分が前記第1のシリコン窒化膜に接すると共に第2の部分が前記第3のシリコン酸化膜を介して前記シリコン基板に接していることを特徴とする。

## 【0014】

この構成によれば、不揮発性半導体メモリーの電荷の保持部が、シリコン基板上に積層

50

された第1のシリコン酸化膜、第1のシリコン窒化膜及び第2のシリコン酸化膜により構成され(ONO構造)、第2のシリコン窒化膜が第1のシリコン窒化膜に接すると共に第3のシリコン酸化膜を介してシリコン基板に接している構成を有することで、製造時における所定の工程においてONO構造に捕獲された余分な電荷を他の所定の工程において第2のシリコン窒化膜及び第3のシリコン酸化膜を介して拡散することができ、該余分な電荷の閾値電圧に対する影響を低減することができる。これによりメモリーの動作の高速化・低電圧化を図ることができる。

#### 【0015】

上述したように、製造過程において第1のシリコン窒化膜に捕獲された電荷をより少なくすることが、不揮発性半導体メモリーの動作を高速化・低電圧化する効果を有する。第3のシリコン酸化膜の膜厚が第1のシリコン酸化膜の膜厚よりも薄いことから、第2のシリコン窒化膜及び第3のシリコン酸化膜を介するほうが第1のシリコン酸化膜を介するほうよりも容易に第1のシリコン窒化膜に捕獲された電荷を拡散させることができある。

10

#### 【0016】

##### [適用例3]

上記適用例にかかる不揮発性半導体メモリーにおいて、更に、前記シリコン基板内にシリサイド領域を含み、前記シリサイド領域は、前記第2のシリコン窒化膜の第2の部分に接することが好ましい。

#### 【0017】

この構成によれば、第2のシリコン窒化膜がシリサイド領域に接していることにより、第2のシリコン窒化膜からの電荷をより効率よくシリコン基板に拡散させることができる。尚、該シリサイド領域は、第3のシリコン酸化膜を介して第2のシリコン窒化膜に接していてもよい。

20

#### 【0018】

##### [適用例4]

上記適用例にかかる不揮発性半導体メモリーにおいて、更に、前記第2のシリコン酸化膜上に第1の電極を有し、前記第2のシリコン窒化膜の第3の部分が前記第1の電極に接していることが好ましい。

#### 【0019】

この構成によれば、第1の電極に第2のシリコン窒化膜が接していることにより、製造過程において第1のシリコン窒化膜に捕獲された電荷を、第2のシリコン窒化膜を介して第1の電極に拡散させることができる。これにより、シリコン基板に電荷を拡散させると共に第1の電極に電荷を拡散させることができ、より効率よく第1のシリコン窒化膜に捕獲された電荷を拡散することができる。

30

#### 【0020】

##### [適用例5]

上記適用例にかかる不揮発性半導体メモリーにおいて、前記第3のシリコン酸化膜は、厚さが22以下であることが好ましい。

#### 【0021】

この構成によれば、第3のシリコン酸化膜の厚さを22以下とすることにより、第2のシリコン窒化膜からの電荷をより効率よくシリコン基板に拡散することができる。

40

#### 【0022】

##### [適用例6]

上記適用例にかかる不揮発性半導体メモリーにおいて、前記第2のシリコン窒化膜は、厚さが45以上であることが好ましい。

#### 【0023】

この構成によれば、第2のシリコン窒化膜を45以上とすることにより、第1のシリコン窒化膜の電荷の第2のシリコン窒化膜への伝搬をより効率よく行うことができる。

#### 【0024】

##### [適用例7]

50

本適用例にかかる不揮発性半導体メモリーの製造方法は、シリコン基板上に、第1のシリコン酸化膜を成膜する第1の工程と、前記第1のシリコン酸化膜上に、第1のシリコン窒化膜を成膜する第2の工程と、前記第1のシリコン窒化膜上に、第2のシリコン酸化膜を成膜する第3の工程と、前記第1のシリコン酸化膜、前記第1のシリコン窒化膜及び第2のシリコン酸化膜を所定の形状にパターニングする第4の工程と、前記第4の工程の後に第2のシリコン窒化膜を成膜する第5の工程と、を含み、前記第4の工程において、前記第1のシリコン窒化膜及び前記シリコン基板が露出され、前記第5の工程において、前記第1のシリコン窒化膜と前記第2のシリコン窒化膜とが接することを特徴とする。

【0025】

この方法によれば、第4の工程におけるパターニングで第1のシリコン窒化膜及びシリコン基板が露出し、第4の工程の後の第5の工程において第2のシリコン窒化膜を成膜することで、第2のシリコン窒化膜を第1のシリコン窒化膜に接するようにすることができると共にシリコン基板に接するようにすることができる。これにより、第5の工程より後の工程において、第1のシリコン窒化膜に捕獲された電荷を第2のシリコン窒化膜を介してシリコン基板に拡散することが可能となる。

【0026】

[適用例8]

上記適用例にかかる不揮発性半導体メモリーの製造方法において、前記第4の工程と前記第5の工程の間の第6の工程において、前記シリコン基板が露出された領域に第3のシリコン酸化膜が形成されていてもよい。

【0027】

この方法によれば、第5の工程において第2のシリコン窒化膜を成膜することで、第2のシリコン窒化膜を第1のシリコン窒化膜に接するようにすることができると共に、シリコン基板には第3のシリコン酸化膜を介して接するようにすることができる。第3のシリコン酸化膜は酸素雰囲気下で加熱することで形成してもよいが、大気にさらされことなどによりシリコン基板が酸化して形成される自然発生的なシリコン酸化膜を第3のシリコン酸化膜とすることでもよい。

【0028】

[適用例9]

本適用例にかかる不揮発性半導体メモリーの製造方法は、シリコン基板上に、第1のシリコン酸化膜を成膜する第1の工程と、前記第1のシリコン酸化膜上に、第1のシリコン窒化膜を成膜する第2の工程と、前記第1のシリコン窒化膜上に、第2のシリコン酸化膜を成膜する第3の工程と、前記第1のシリコン酸化膜、前記第1のシリコン窒化膜及び第2のシリコン酸化膜を所定の形状にパターニングする第4の工程と、前記第4の工程の後に第2のシリコン窒化膜を成膜する第5の工程と、を含み、前記第4の工程において、前記第1のシリコン窒化膜が露出され、前記第1のシリコン酸化膜をエッチングすることで前記第1のシリコン酸化膜より膜厚が薄い第3のシリコン酸化膜が形成され、前記第5の工程において、前記第1のシリコン窒化膜と前記第2のシリコン窒化膜とが接することを特徴とする。

【0029】

この方法によれば、第5の工程において第2のシリコン窒化膜を成膜することで、第2のシリコン窒化膜を第1のシリコン窒化膜に接するようにすることができると共に、シリコン基板には第3のシリコン酸化膜を介して接するようにすることができる。

【図面の簡単な説明】

【0030】

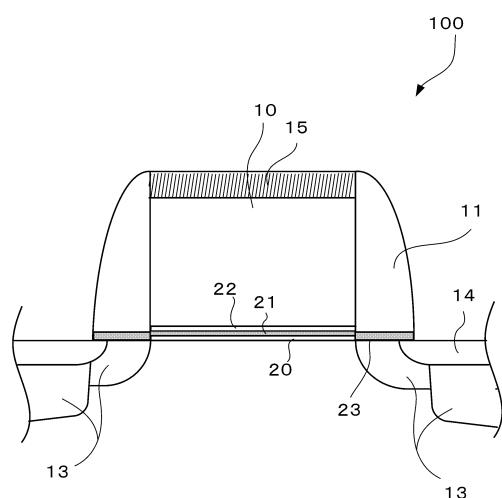

【図1】第1実施形態における不揮発性半導体メモリーの概略断面図。

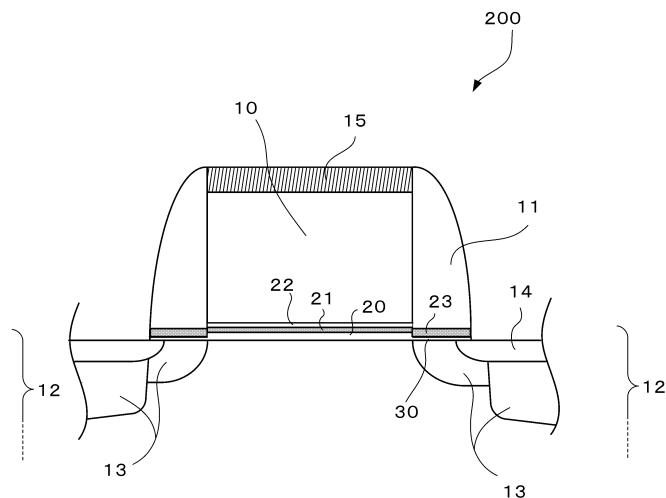

【図2】第2実施形態における不揮発性半導体メモリーの概略断面図。

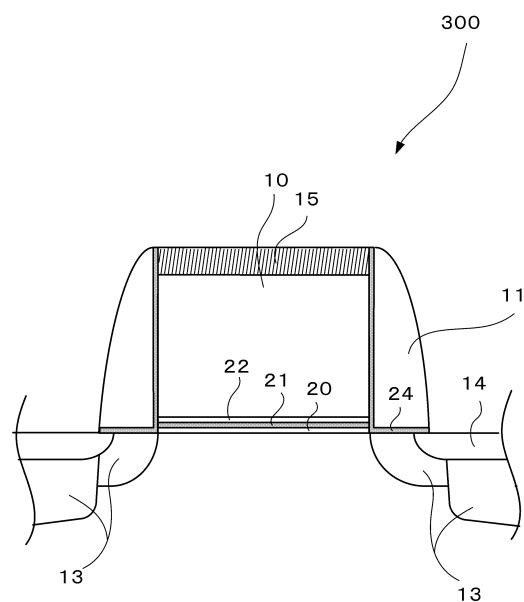

【図3】第3実施形態における不揮発性半導体メモリーの概略断面図。

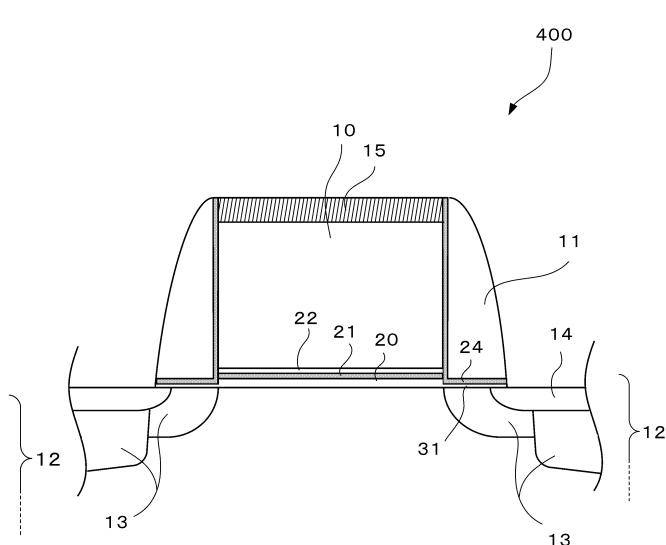

【図4】第4実施形態における不揮発性半導体メモリーの概略断面図。

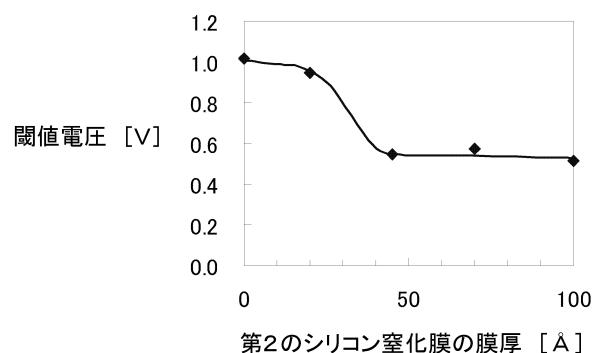

【図5】第2シリコン窒化膜の特性を示したグラフ。

10

20

30

40

50

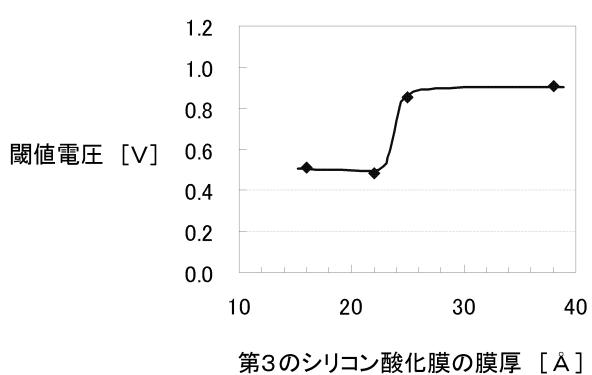

【図6】第3シリコン酸化膜の特性を示したグラフ。

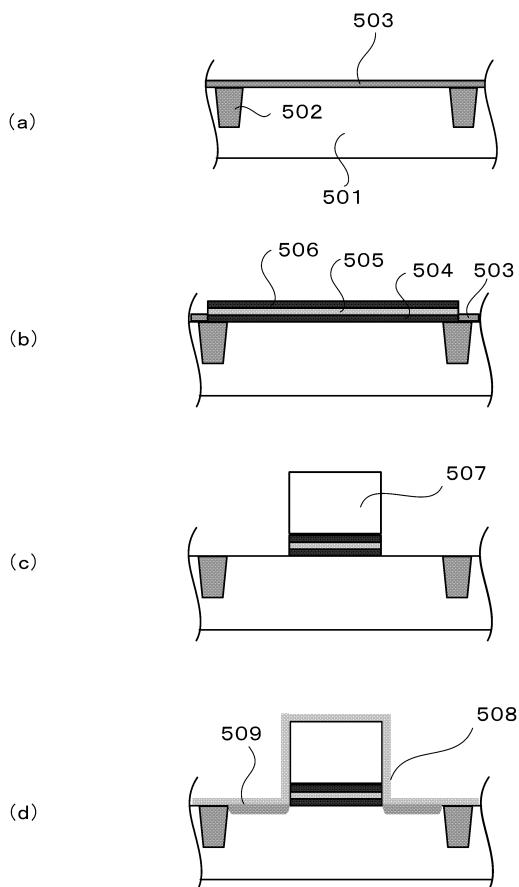

【図7】製造工程の一部を示す模式図。

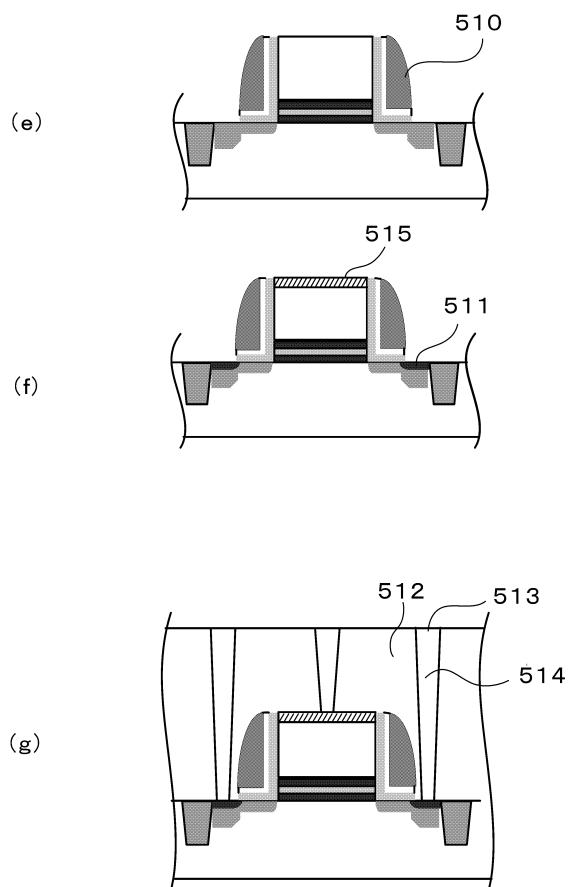

【図8】製造工程の一部を示す模式図。

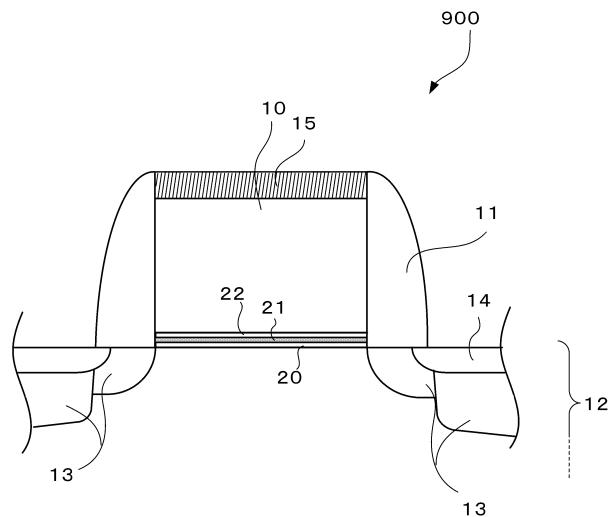

【図9】従来の不揮発性半導体メモリーの概略断面図。

【発明を実施するための形態】

【0031】

以下、図を用いて本発明の実施形態について説明する。尚、以下の説明に用いる図は、主に説明に必要な部分を記載した便宜上の概略図である。このため、デフォルメがなされており、形状の異なる部分や大きさの比率が異なる部分などがある。

【0032】

(第1実施形態)

図1に本願発明を適用した不揮発性半導体メモリー100の断面図を示す。不揮発性半導体メモリー100は、シリコン基板12を用いて形成され、第1電極10、サイドウォール11、ソース領域/ドレイン領域13、シリサイド領域14、シリサイド層15、第1シリコン酸化膜20、第1シリコン窒化膜21、第2シリコン酸化膜22及び第2シリコン窒化膜23を有する。第1電極10としては、例えばポリシリコン膜、サイドウォール11としては、例えばシリコン酸化膜が用いられる。ソース領域/ドレイン領域13及びシリサイド領域14は、シリコン基板12内に形成された領域である。シリサイドは、例えばコバルトシリサイドやチタンシリサイドが用いられる。また、メモリー機能のためのトラップ層は、第1シリコン酸化膜20、第1シリコン窒化膜21及び第2シリコン酸化膜22から構成されるONO構造である。第2シリコン窒化膜23は、第1シリコン窒化膜21及びシリコン基板12に接している。以後、特に断りがない限り、シリコン基板12は、ソース領域/ドレイン領域13及びシリサイド領域14を含む意味で記載する。

【0033】

比較のため、図9に、従来の不揮発性半導体メモリー900の断面図を示す。不揮発性半導体メモリー900は、第2シリコン窒化膜23が無い点で、本願発明を適用した不揮発性半導体メモリー100と異なる。不揮発性半導体メモリー900においては、サイドウォール11として、シリコン酸化膜が用いられるのが一般的であり、その場合、第1シリコン窒化膜の側面は、シリコン酸化膜に覆われる。

【0034】

不揮発性半導体メモリー100及び900の製造過程においては、エッチングやスパッタリング等のプラズマを用いる処理を多用するが、その際に第1シリコン酸化膜20、第1シリコン窒化膜21及び第2シリコン酸化膜22から構成されるONO構造(トラップ層)にプラズマ由來の電荷が注入され、保持される。このような現象を本願ではプロセスチャージと呼ぶ。プロセスチャージが発生した場合、従来の不揮発性半導体メモリー900においては、シリコン酸化膜の絶縁性が高いために、プロセスチャージによる電荷を拡散させることができない。そのため、トラップ層に多くの電荷が捕獲されたまま製造工程が終了し、高速・低電圧動作に不向きな不揮発性半導体メモリーとなる場合がある。また、メモリーの閾値電圧が設計値から変動するため、閾値電圧の変動を伴うチャネル部の不純物濃度の変更・調整に制限がある。

【0035】

本願発明を適用した不揮発性半導体メモリー100(図1)においては、従来の不揮発性半導体メモリー900に対して、新たに第2シリコン窒化膜23を設けた。第2シリコン窒化膜23は、第1シリコン窒化膜21の側面と、シリコン基板12に接している。シリコン窒化膜は、シリコン酸化膜に比べて絶縁性が低い。そこで、トラップ層に保持されたプロセスチャージによる電荷を、第2シリコン窒化膜23を介してシリコン基板12に拡散させることができとなる。電荷の拡散は、加熱処理を行うことで、加速される。加熱処理は、不純物の活性化やシリサイド化等、メモリーの製造過程で従来から行われる加熱処理を用いてもよいし、専用の工程を設けてもよい。第2シリコン窒化膜23は、シリコン酸化膜より絶縁性の低い絶縁膜であればよい。例えばシリコン酸窒化膜でもよい。

10

20

30

40

50

## 【0036】

図5には、第2シリコン窒化膜の膜厚と、不揮発性半導体メモリー100及び900の閾値電圧の関係を表すグラフを示した。ここではプロセスチャージによって、電子がトラップ層に蓄積され、閾値電圧が上昇する。第2シリコン窒化膜が0すなわち不揮発性半導体メモリー900の場合、閾値電圧は1.0Vである。一方、第2シリコン窒化膜の膜厚が0より大きい不揮発性半導体メモリー100の場合、第2シリコン窒化膜の膜厚が大きくなるにつれて、トラップ層に蓄積された電子が拡散され、閾値電圧が低下する。第2シリコン窒化膜の膜厚が45以上の場合、閾値電圧が0.6V付近に低下して安定するようになるので、特に好ましい。この閾値電圧の膜厚依存性は、後述の第2～第4実施形態でも同じである。

10

## 【0037】

## (第2実施形態)

本実施形態も含め、以降に記載する実施形態の説明において、第1実施形態と同様の構成要素については同じ番号を付与し、その説明を省略する。

## 【0038】

図2に本願発明を適用した不揮発性半導体メモリー200の断面図を示す。不揮発性半導体メモリー200は、不揮発性半導体メモリー100の構成要素に第3シリコン酸化膜30を付加したものである。第2シリコン窒化膜23は、第3シリコン酸化膜30を介してシリコン基板12に接している。第3シリコン酸化膜30の厚さは、第1シリコン酸化膜20の厚さよりも薄く形成されている。これにより、第1シリコン酸化膜20が第1シリコン窒化膜21の電荷を拡散することに対する障壁となっていても、第3シリコン酸化膜30を介して該電荷を拡散することができる。

20

## 【0039】

図6には、第3シリコン酸化膜の膜厚と、不揮発性半導体メモリー200の閾値電圧の関係を表すグラフを示した。ここではプロセスチャージによって電子が、トラップ層に蓄積され、閾値電圧が上昇する。不揮発性半導体メモリー200においては、第3シリコン酸化膜の膜厚が小さくなるにつれて、トラップ層に蓄積された電子が拡散され、閾値電圧が低下する。第3シリコン酸化膜の膜厚が22以下の場合、閾値電圧が0.5V付近に低下して安定するようになるので、特に好ましい。この閾値電圧の膜厚依存性は、後述の第4実施形態でも同じである。

30

## 【0040】

尚、第3シリコン酸化膜30は、意図的に形成されるものでもよく、第2シリコン窒化膜23が形成される前の工程で自然発生的に形成されるものでもよい。

## 【0041】

## (第3実施形態)

図3に本願発明を適用した不揮発性半導体メモリー300の断面図を示す。不揮発性半導体メモリー300は、シリコン基板12及び第1電極10に接する第2シリコン窒化膜24を有する。サイドウォール11は、第2シリコン窒化膜24を覆うように形成されている。上記した第2シリコン窒化膜23と同様に、第2シリコン窒化膜24の厚さは45以上であることが好ましい。

40

## 【0042】

第1シリコン窒化膜21に捕獲された電荷は、第2シリコン窒化膜24を介して第1電極10及びシリコン基板12に拡散されることになり、シリコン基板12のみに拡散させる場合よりも効率がよくなる。これにより、加熱処理の温度の設定及び時間の設定に対する自由度を上げることができる。

## 【0043】

## (第4実施形態)

図4に本願発明を適用した不揮発性半導体メモリー400の断面図を示す。不揮発性半導体メモリー400は、不揮発性半導体メモリー300の構成要素に第3シリコン酸化膜31を付加したものである。第2シリコン窒化膜24は、第3シリコン酸化膜31を介し

50

てシリコン基板 1 2 に接している。第 3 シリコン酸化膜 3 1 の厚さは、第 1 シリコン酸化膜 2 0 の厚さよりも薄く形成されている。これにより、第 1 シリコン酸化膜 2 0 が第 1 シリコン窒化膜 2 1 の電荷を拡散させることに対する障壁となつても、第 3 シリコン酸化膜 3 1 を介して該電荷を拡散させることができる。上記した第 3 シリコン酸化膜 3 0 と同様に、第 3 シリコン酸化膜 3 1 の厚さは 2 2 以下であることが好ましい。

#### 【 0 0 4 4 】

第 3 シリコン酸化膜 3 1 は、意図的に形成されるものでもよく、第 2 シリコン窒化膜 2 4 が形成される前の工程で自然発生的に形成されるものでもよい。

#### 【 0 0 4 5 】

上記した不揮発性半導体メモリー 1 0 0 、 2 0 0 、 3 0 0 及び 4 0 0 のいずれもシリコン基板 1 2 内にシリサイド領域 1 4 が形成されている。シリサイド領域 1 4 はシリコン基板 1 2 の他の部分に比較して電気抵抗が低いことから、シリサイド領域 1 4 を設けることがプロセスチャージの電荷を基板に拡散させる工程の効率を上げることに繋がり好ましい。

10

#### 【 0 0 4 6 】

##### ( 第 5 実施形態 )

本実施形態は、本発明にかかる O N O 構造を有する不揮発性半導体メモリーの製造方法の 1 例を説明するものである。具体的には、上述した不揮発性半導体メモリー 3 0 0 若しくは 4 0 0 の製造方法となる。図 7 及び図 8 に、製造過程における素子の断面図の模式図を示す。尚、図に示しているのは、不揮発性半導体メモリーの部分のみであり、他の種類の素子の形成も同時に行われている。また、該不揮発性半導体メモリーを形成する領域を O N O 領域と呼ぶことにする。

20

#### 【 0 0 4 7 】

図 7 - ( a ) は、シリコン基板 5 0 1 に S T I ( S h a l l o w T r e n c h I s o l a t i o n ) 5 0 2 形成後に、ダミー酸化膜 5 0 3 を形成した状態を示す。ダミー酸化膜 5 0 3 は、 O N O 構造を形成するときの O N O 領域以外の領域に対する O N O 除去時の基板への影響を無くすためのものである。その後、 O N O 領域におけるダミー酸化膜 5 0 3 は除去され、 O N O 構造が積層される。図 7 - ( b ) は、 O N O 構造が積層された後、ダミー酸化膜 5 0 3 上に形成された O N O 構造を除去した状態を示したものである。その後、残っていたダミー酸化膜 5 0 3 が除去され、 O N O 領域以外のトランジスターのゲート酸化膜が形成される。 O N O 領域における O N O 構造は、第 1 シリコン酸化膜 5 0 4 、第 1 シリコン窒化膜 5 0 5 及び第 2 シリコン酸化膜 5 0 6 から構成される。

30

#### 【 0 0 4 8 】

次に、ポリシリコンが全面に成膜され、ドライエッチングにより所定の形状の第 1 ゲート電極 5 0 7 が形成される(図 7 - ( c ) )。該ドライエッチングの工程が、プロセスチャージが引き起こす工程となる(以下、電荷蓄積工程と称する)。その後、デバイスに応じたイオン注入が行われ不純物領域 5 0 9 が形成され、その後第 2 シリコン窒化膜 5 0 8 が成膜される(図 7 - ( d ) )。

#### 【 0 0 4 9 】

次に、サイドウォールを形成するためにシリコン酸化膜を成膜し、異方性エッチングによりサイドウォール 5 1 0 が形成される。この異方性エッチングも電荷蓄積工程である。シリコン窒化膜はストレスの大きい膜なので、シリコン窒化膜のみでサイドウォールを形成すると、ストレスによる不具合が発生する場合がある。したがって、サイドウォール 5 1 0 をシリコン窒化膜だけでなく、シリコン酸化膜との積層構造とすることが好ましい。続いて、ソース領域 / ドレイン領域を形成するためのイオンを注入し、活性化アニールが行われる。(図 8 - ( e ) )。該活性化アニールは、プロセスチャージを拡散する工程となる(以下、電荷拡散工程と称する)。第 1 シリコン窒化膜 5 0 5 及び第 2 シリコン窒化膜 5 0 8 に蓄積された電荷が、該活性化アニールにより、シリコン基板 5 0 1 及び第 1 ゲート電極 5 0 7 に拡散する。

40

#### 【 0 0 5 0 】

次に、Co(コバルト)をスパッタリングしアニールすることで、コバルトシリサイド領域511およびコバルトシリサイド層515が形成される。この工程においては、該スパッタリングが電荷蓄積工程となり、該アニールが電荷拡散工程となる。(図8-(f))。

#### 【0051】

次に、層間絶縁膜512を形成し、ドライエッチングによりコンタクトホール513を形成する。該ドライエッチングが電荷蓄積工程となるが、この後のタングステン等を成膜しアニールし配線514を形成する工程が電荷拡散工程となる(図8-(g))。

#### 【0052】

以降、必要な層数の層間絶縁膜の形成、コンタクトホールの形成及び配線の形成を行うために、所定のスパッタリング、所定のエッチング及び所定のアニールが行われ、電荷蓄積工程と電荷拡散工程が繰り返される。電荷蓄積工程で第1シリコン酸化膜504、第1シリコン窒化膜505及び第2シリコン酸化膜506から構成されるONO構造(トラップ層)に蓄積された電荷が、電荷拡散工程でシリコン基板501及び第1ゲート電極507に拡散させることができる。製造に必要な工程のすべてが終了する時点で、トラップ層に電荷が捕獲されたままにならぬようにするには、最終の電荷蓄積工程より後に、電荷拡散工程を設けることが好ましい。最終工程が電荷拡散工程であることがさらに好ましい。これにより、プロセスチャージによる弊害をなくした不揮発性半導体メモリーを製造することが可能となる。

#### 【0053】

また、上記の製造工程において、第2シリコン窒化膜508が成膜される前に第3シリコン酸化膜を形成する工程を付加してもよい。例えば、ドライエッチングにより所定の形状の第1ゲート電極507が形成される際に、前記シリコン基板を露出させない様にシリコン酸化膜を残すように加工する事で、第3シリコン酸化膜を意図的に形成してもよい。尚或いは、製造過程の中でシリコン基板と第2シリコン窒化膜との間に自然発生的に形成されるシリコン酸化膜を、第3シリコン酸化膜として利用することを考慮して製造工程を構成してもよい。

#### 【0054】

本実施形態として、不揮発性半導体メモリー300若しくは400の場合の製造方法の説明を行ったが、不揮発性半導体メモリー100若しくは200の場合は第2シリコン窒化膜の形状が異なることから製造工程が異なってくる。しかしながら、電荷蓄積工程の後に電荷拡散工程が存在するようにして、本実施形態で説明した製造方法における効果と同様の効果を得ることができる。

#### 【0055】

以上、本発明にかかる適用例及び実施形態について記載したが、本発明は上述した記載に限定されるものではない。本発明は、趣旨を逸脱しない範囲において広く適用が可能である。

#### 【符号の説明】

#### 【0056】

10...第1電極、11...サイドウォール、12...シリコン基板、13...ソース/ドレイン領域、14...シリサイド領域、15...シリサイド層、20...第1シリコン酸化膜、21...第1シリコン窒化膜、22...第2シリコン酸化膜、23...第2シリコン窒化膜、24...第2シリコン窒化膜、30...第3シリコン酸化膜、31...第3シリコン酸化膜、100...不揮発性半導体メモリー、200...不揮発性半導体メモリー、300...不揮発性半導体メモリー、400...不揮発性半導体メモリー、501...シリコン基板、502...STI、503...ダミー酸化膜、504...第1シリコン酸化膜、505...第1シリコン窒化膜、506...第2シリコン酸化膜、507...第1ゲート電極、508...第2シリコン窒化膜、509...不純物領域、510...サイドウォール、511...コバルトシリサイド領域、512...層間絶縁膜、513...コンタクトホール、514...配線、515...コバルトシリサイド層、900...不揮発性半導体メモリー。

10

20

30

40

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 佐々木 隆興

山形県酒田市十里塚166番地3 東北エプソン株式会社内

審査官 佐藤 靖史

(56)参考文献 特開2007-005699 (JP, A)

国際公開第2006/080081 (WO, A1)

特開2001-326288 (JP, A)

特開2009-071325 (JP, A)

特開2004-165553 (JP, A)

特開2006-269697 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8229

21/8242 - 21/8247

27/10 - 27/115

27/28

29/788 - 29/792

51/05