(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 602 00 498 T2 2005.06.02

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 256 960 B1

(51) Int Cl.<sup>7</sup>: G11C 16/04

(21) Deutsches Aktenzeichen: 602 00 498.5

(96) Europäisches Aktenzeichen: 02 002 973.2

(96) Europäischer Anmeldetag: 11.02.2002

(97) Erstveröffentlichung durch das EPA: 13.11.2002

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 19.05.2004

(47) Veröffentlichungstag im Patentblatt: 02.06.2005

(30) Unionspriorität:

2001137165 08.05.2001 JP

(84) Benannte Vertragsstaaten:

AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT,

LI, LU, MC, NL, PT, SE, TR

(73) Patentinhaber:

Seiko Epson Corp., Tokio/Tokyo, JP

(72) Erfinder:

Kanai, Masahiro, Suwa-shi, Nagano-ken 392-8502,

JP; Kamei, Teruhiko, Suwa-shi, Nagano-ken

392-8502, JP

(74) Vertreter:

Hoffmann, E., Dipl.-Ing., Pat.-Anw., 82166

Gräfelfing

(54) Bezeichnung: Programmierverfahren für einen nichtflüchtigen Halbleiterspeicher

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****TECHNISCHES GEBIET**

**[0001]** Die vorliegende Erfindung bezieht sich auf ein Programmierverfahren für einen nichtflüchtigen Halbleiterbaustein, der aus Doppelspeicherzellen gebildet ist, die je mit einem Wort-Gate und zwei von zwei Steuer-Gates gesteuerten, nichtflüchtigen Speicherelementen ausgestattet sind.

**HINTERGRUND**

**[0002]** Es ist ein nichtflüchtiger Halbleiterbaustein vom Metalloxid-Nitridoxid-Substrat- (MONOS)-Typ bekannt, bei dem eine dielektrische Gate-Schicht zwischen einem Kanal und einem Gate aus einem Stapel gebildet ist, der eine Siliziumoxidschicht, eine Siliziumnitridschicht und eine Siliziumoxidschicht umfaßt und bei dem Ladung in der Siliziumnitridschicht eingefangen ist.

**[0003]** Ein nichtflüchtiger Halbleiterbaustein des MONOS-Typs ist in einer Veröffentlichung von Y. Hayashi et al. 2000 Symposium on VLSI Technology, Digest of Technical Papers, S. 122 – S. 123 beschrieben. In der Veröffentlichung wird eine blitzartig wirkende Doppelspeicherzelle des MONOS-Typs beschrieben, die mit einem Wort-Gate und zwei nichtflüchtigen Speicherelementen (MONOS-Speicherelementen oder Zellen) versehen ist, die von zwei Steuer-Gates gesteuert werden. Anders ausgedrückt, eine Blitzspeicherzelle umfaßt zwei Ladungsfallenstellen. Eine Vielzahl MONOS-Blitzdoppelspeicherzellen, die alle den oben beschriebenen Aufbau haben, sind in Reihenrichtung und in Spaltenrichtung in einer Vielzahl von Reihen und Spalten angeordnet, so daß sie einen Speicherzellenmatrixbereich bilden.

**[0004]** Zum Treiben einer MONOS-Blitzspeicherzelle sind zwei Bitleitungen, eine Wortleitung sowie zwei Steuer-Gateleitungen erforderlich. Wenn aber eine Vielzahl von Doppelspeicherzellen angesteuert wird, können diese Leitungen für verschiedene Steuer-Gates gemeinsam verbunden werden, falls sie auf das gleiche Potential gesetzt sind.

**[0005]** Zu den Aufgaben dieser Art von Blitzspeicher gehört das Löschen, Programmieren und Lesen von Daten. Normalerweise wird die Datenprogrammierung oder das Datenlesen an ausgewählten Zellen (ausgewählte nichtflüchtige Speicherelemente) in Einheiten von 8 Bits oder 16 Bits gleichzeitig durchgeführt.

**[0006]** Es sei darauf hingewiesen, daß im MONOS-Blitzspeicher eine Vielzahl nicht gegeneinander isolierter MONOS-Blitzdoppelspeicherzellen an eine einzige Wortleitung angeschlossen ist. Zum Programmieren von Daten an einer spezifizierten, ausgewählten Zelle muß nicht nur die Spannung eines MONOS-Blitzdoppelspeichers, der die ausgewählte Zelle umfaßt, zweckentsprechend gesetzt werden, sondern es muß auch die Spannung einer benachbarten MONOS-Blitzdoppelspeicherzelle zweckentsprechend gesetzt werden.

**[0007]** Es sei darauf hingewiesen, daß es bei dem vorstehend beschriebenen Typ eines nichtflüchtigen Speichers ein Problem mit Datenstörung gibt. Datenstörung bedeutet hier eine Störung von Daten an einer nicht ausgewählten Zelle (nicht ausgewähltes nichtflüchtiges Speicherelement). Wenn eine ausgewählte Zelle durch Anlegen einer hohen Spannung an die Steuer-Gateleitung und die Bitleitung für die ausgewählte Zelle programmiert wird, wird die hohe Spannung auch an die nicht ausgewählte Zelle angelegt, weil sie sich die Verdrahtung teilen. Wenn diese Situation für jedes Programmieren wiederholt wird, entsteht eine Datenstörung. Anders ausgedrückt, die nicht ausgewählte Zelle wird programmiert, oder ihre Daten werden gelöscht.

**[0008]** Ein Verfahren gemäß dem Oberbegriff von Anspruch 1 ist aus EP 1 215 681 A bekannt (Stand der Technik gemäß Art. 54(3) EPÜ).

**ZUSAMMENFASSUNG**

**[0009]** Es ist eine Aufgabe der vorliegenden Erfindung, ein Programmierverfahren für einen nichtflüchtigen Halbleiterbaustein zu schaffen, in dem bei einer Datenprogrammierung an einer ausgewählten Zelle Spannungen für eine Doppelspeicherzelle, die die ausgewählte Zelle umfaßt, und eine benachbarte Doppelspeicherzelle zweckentsprechend gesetzt werden, um dadurch eine Störung an nicht ausgewählten Zellen zu verhindern.

**[0010]** Dieses Ziel wird mit einem Verfahren gemäß Anspruch 1 erreicht. Bevorzugte Ausführungsbeispiele der Erfindung sind der Gegenstand der abhängigen Ansprüche.

[0011] Ein Potentialunterschied zwischen Source und Drain (Bitleitungen) einer nicht ausgewählten Doppelspeicherzelle, die einer ausgewählten Zelle (ausgewähltes nichtflüchtiges Speicherelement) benachbart ist, in der Daten programmiert werden, wird kleiner gemacht, wodurch ein Durchgreiffekt des Stroms an der nicht ausgewählten Doppelspeicherzelle vermieden wird, so daß eine Störung an der nicht ausgewählten Zelle (nicht ausgewähltes nichtflüchtiges Speicherelement) verhindert werden kann.

[0012] Es kann auch eine an der Bitleitung gesetzte, höhere Spannung als 0 Volt vorzugsweise der Programmierwortleitungsauswahlspannung gleich oder größer sein als diese. Folglich kann ein Transistorabschnitt, der das Wort-Gate in einer nicht ausgewählten Doppelspeicherzelle umfaßt, die einer ausgewählten Zelle benachbart ist, nur schwer eingeschaltet werden, womit der Fluß von Durchgriffstrom verhindert wird. Folglich wird auch hierdurch verhindert, daß an der der ausgewählten Zelle benachbarten, nicht ausgewählten Zelle eine Störung auftritt.

[0013] Strom, der während des Programmierens in der Bitleitung fließt, ist außerdem durch die Konstantstromquelle begrenzt, so daß der Strom für die Bitleitung ordnungsgemäß gesetzt und der Programmievorgang sicher durchgeführt werden kann.

[0014] Es sei erwähnt, daß die Programmierwortleitungsauswahlspannung vorzugsweise auf eine Spannung gesetzt werden kann, die ausreichend hoch ist, damit zwischen Source und Drain der ausgewählten Doppelspeicherzelle ein Strom fließen kann, der größer ist als der von der Konstantstromquelle bereitgestellte Strom. Folglich ist auch der während des Programmierens in der Bitleitung fließende Strom von der Konstantstromquelle auf ein gleichbleibendes Niveau beschränkt, so daß die Spannung für die Bitleitung ordnungsgemäß gesetzt und der Programmievorgang sicher durchgeführt werden kann.

[0015] Wenn die Programmierwortleitungsauswahlspannung auf ein hohes Niveau gesetzt wird, kommt es ohne weiteres, wie schon gesagt, zu einer Störung an einer nicht ausgewählten Zelle. Aber ein Potentialunterschied zwischen Source und Drain einer nicht ausgewählten Zelle wird, wie oben erwähnt, reduziert, und damit kann eine Störung an der nicht ausgewählten Zelle verhindert werden.

[0016] Sowohl das erste als auch das zweite nichtflüchtige Speicherelement kann eine ONO-Schicht umfassen, die aus einem Oxidfilm (O), einem Nitridfilm (N) und einem Oxidfilm (O) gebildet ist und als Ladungsfallenstelle benutzt werden kann. Ohne auf den beschriebenen Aufbau beschränkt zu sein, können die Elemente jeden beliebigen anderen Aufbau haben.

#### KURZBESCHREIBUNG DER ZEICHNUNGEN

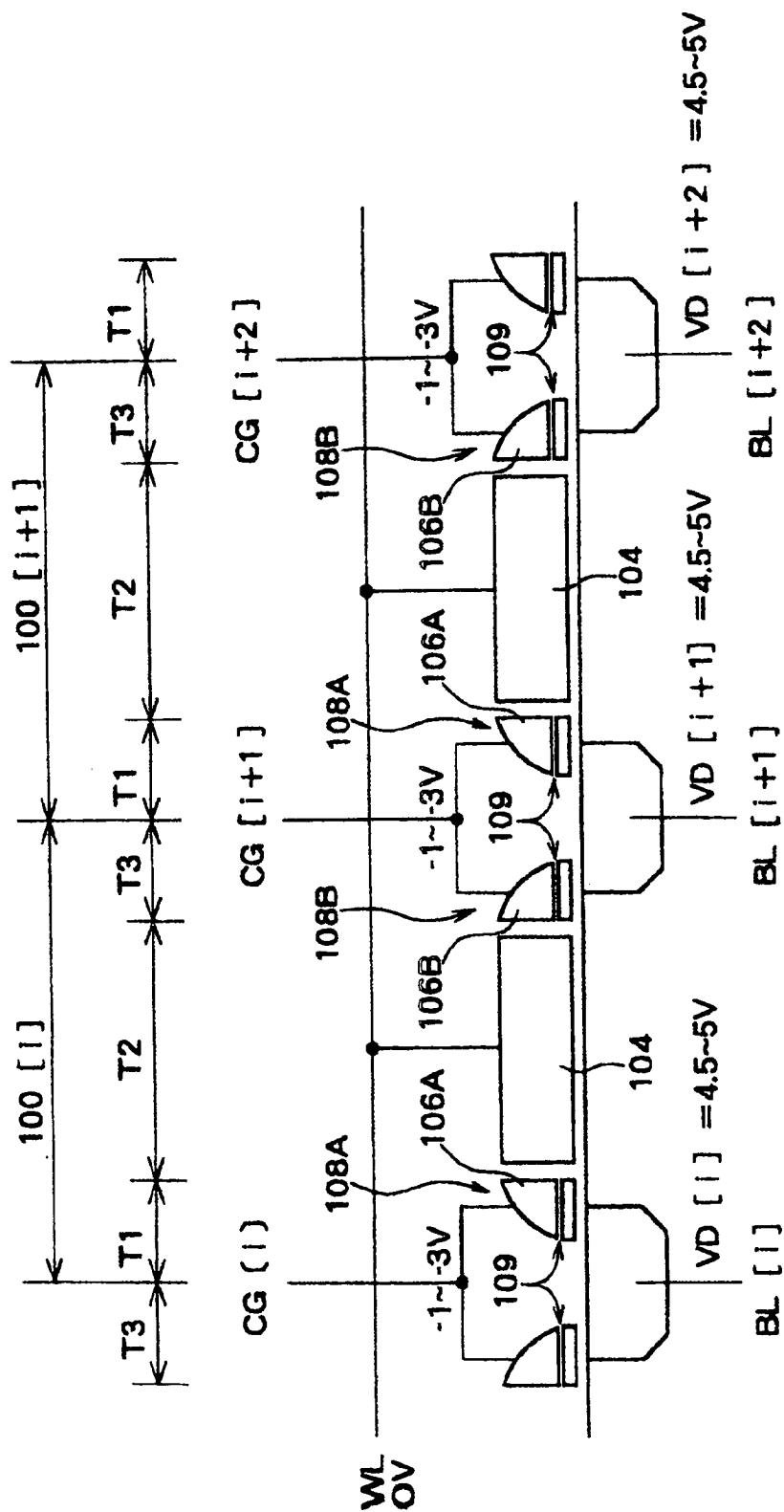

[0017] [Fig. 1](#) zeigt einen Querschnitt durch einen nichtflüchtigen HalbleiterSpeicherbaustein gemäß einem Ausführungsbeispiel der vorliegenden Erfindung.

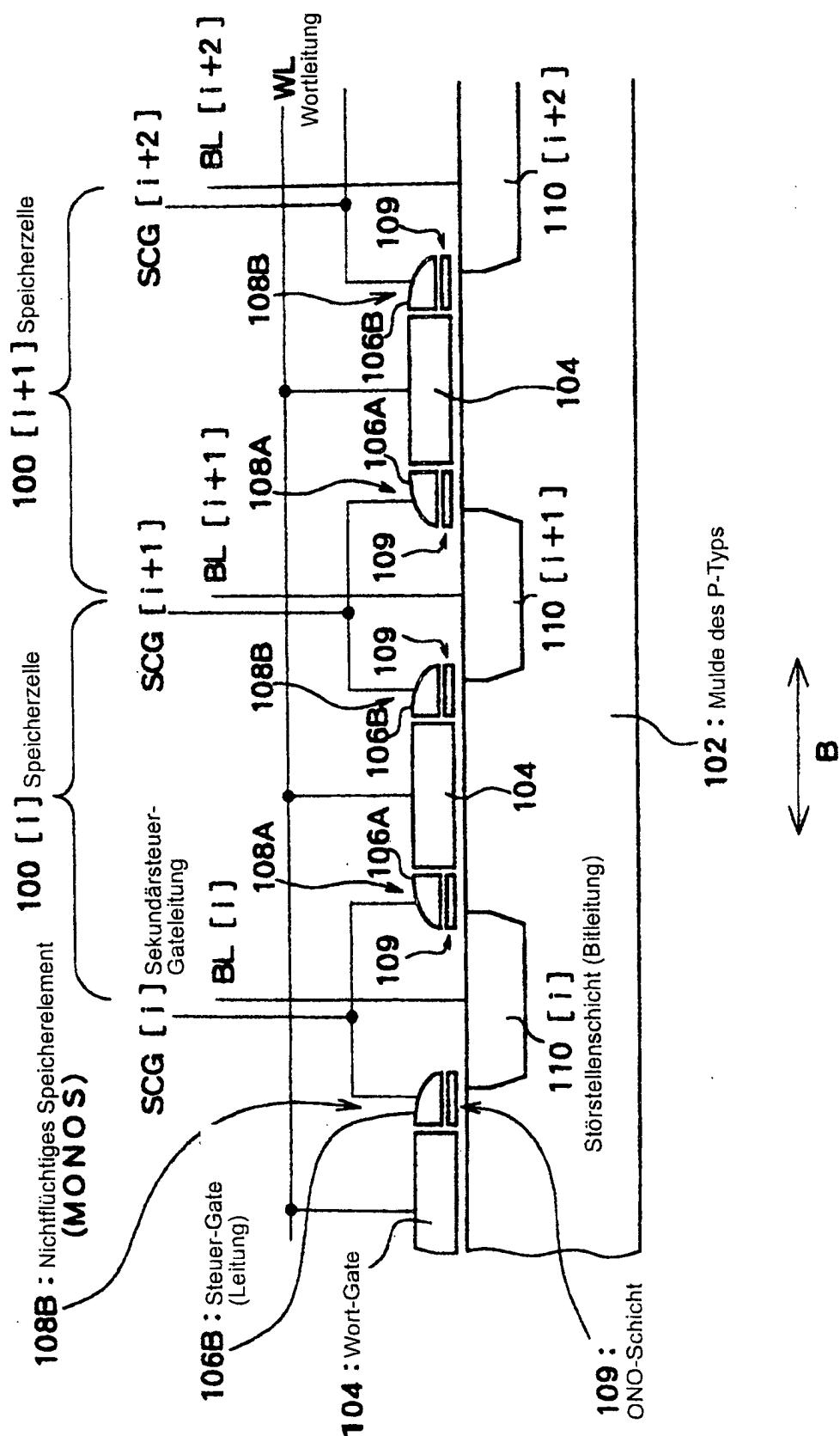

[0018] [Fig. 2A](#) zeigt einen Grundrißplan des in [Fig. 1](#) gezeigten, nichtflüchtigen HalbleiterSpeicherbausteins.

[0019] [Fig. 2B](#) zeigt einen Grundriß von zwei Sektorbereichen in [Fig. 2A](#).

[0020] [Fig. 2C](#) zeigt einen Grundriß eines Speicherblocks in [Fig. 2B](#).

[0021] [Fig. 2D](#) zeigt einen Grundriß eines großen Blocks in [Fig. 2C](#).

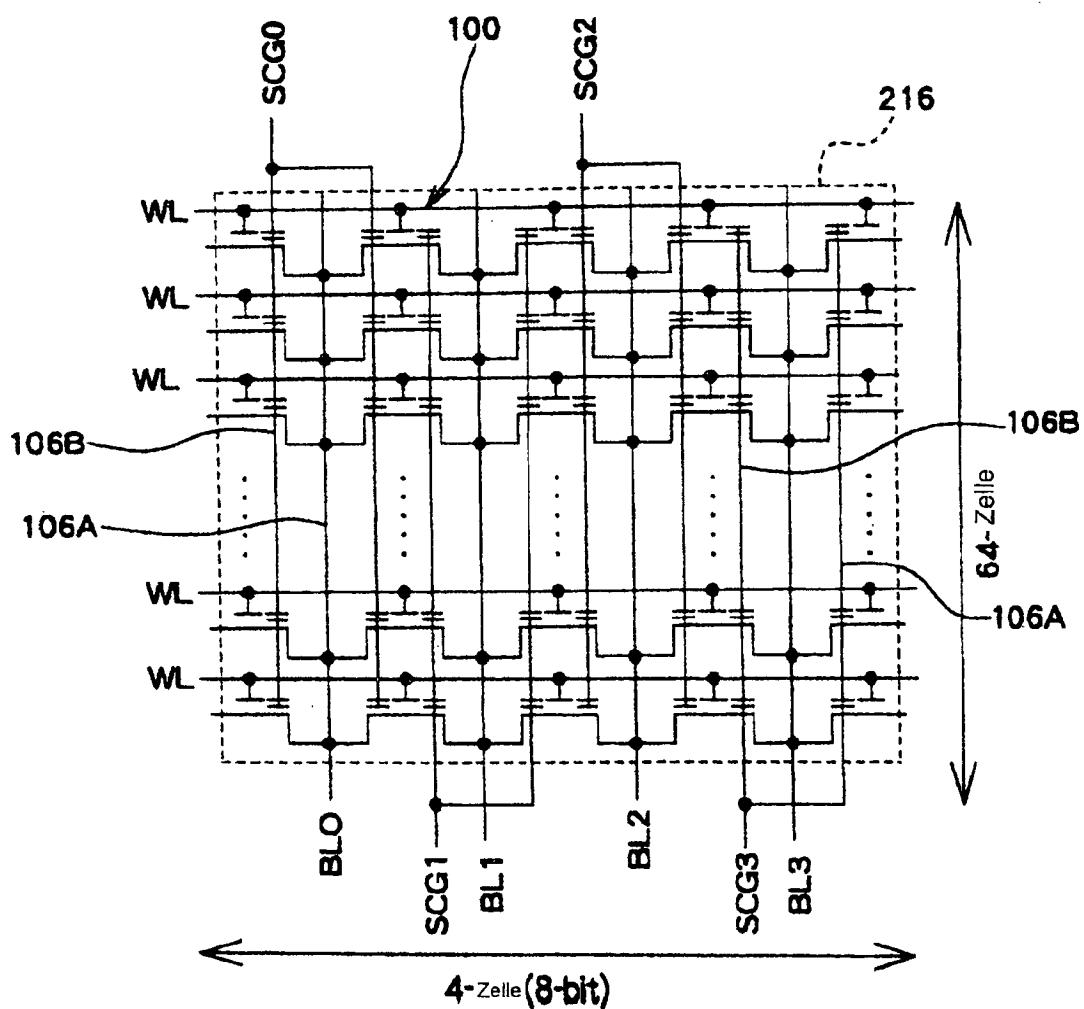

[0022] [Fig. 2E](#) zeigt einen Grundriß eines kleinen Blocks in [Fig. 2D](#).

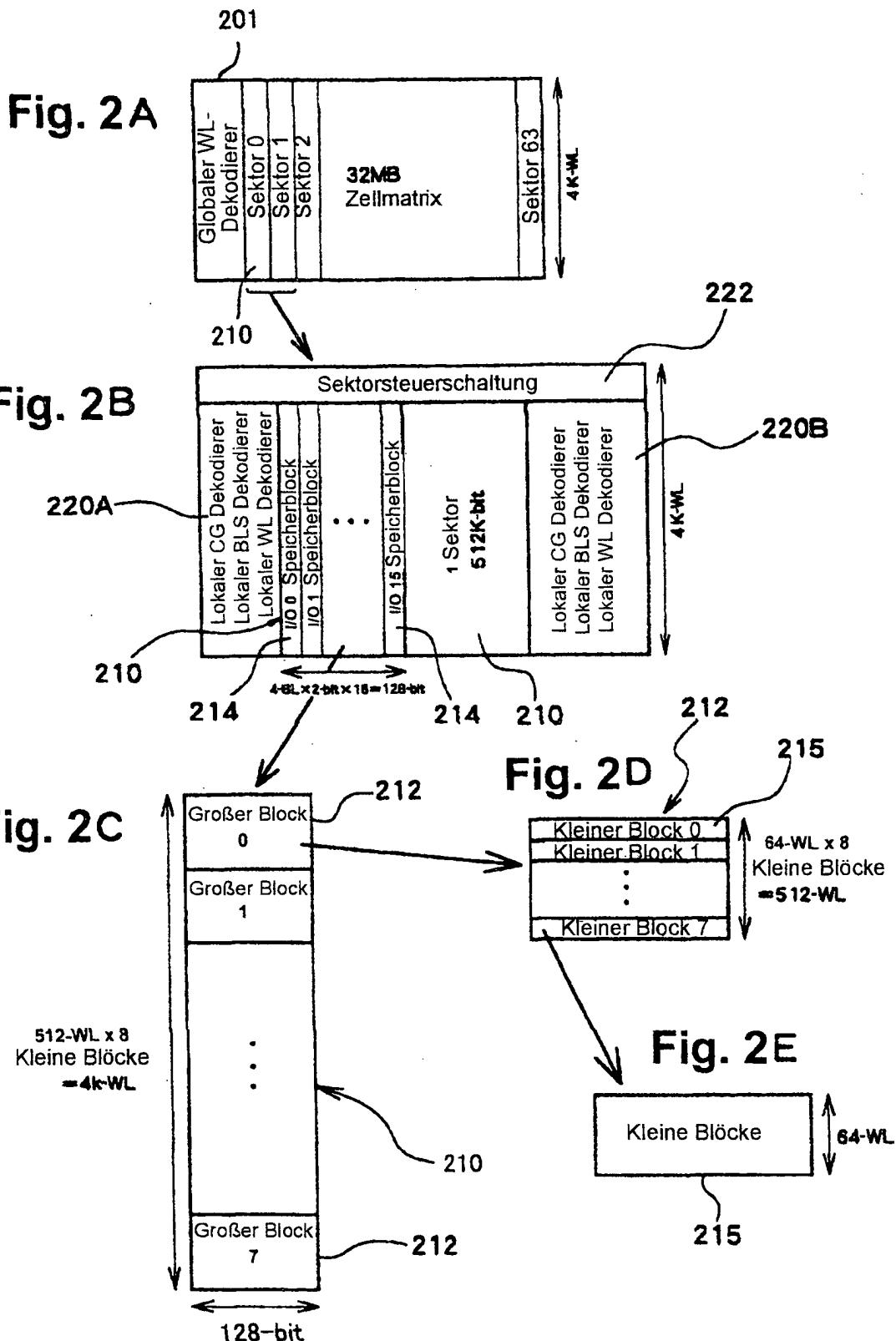

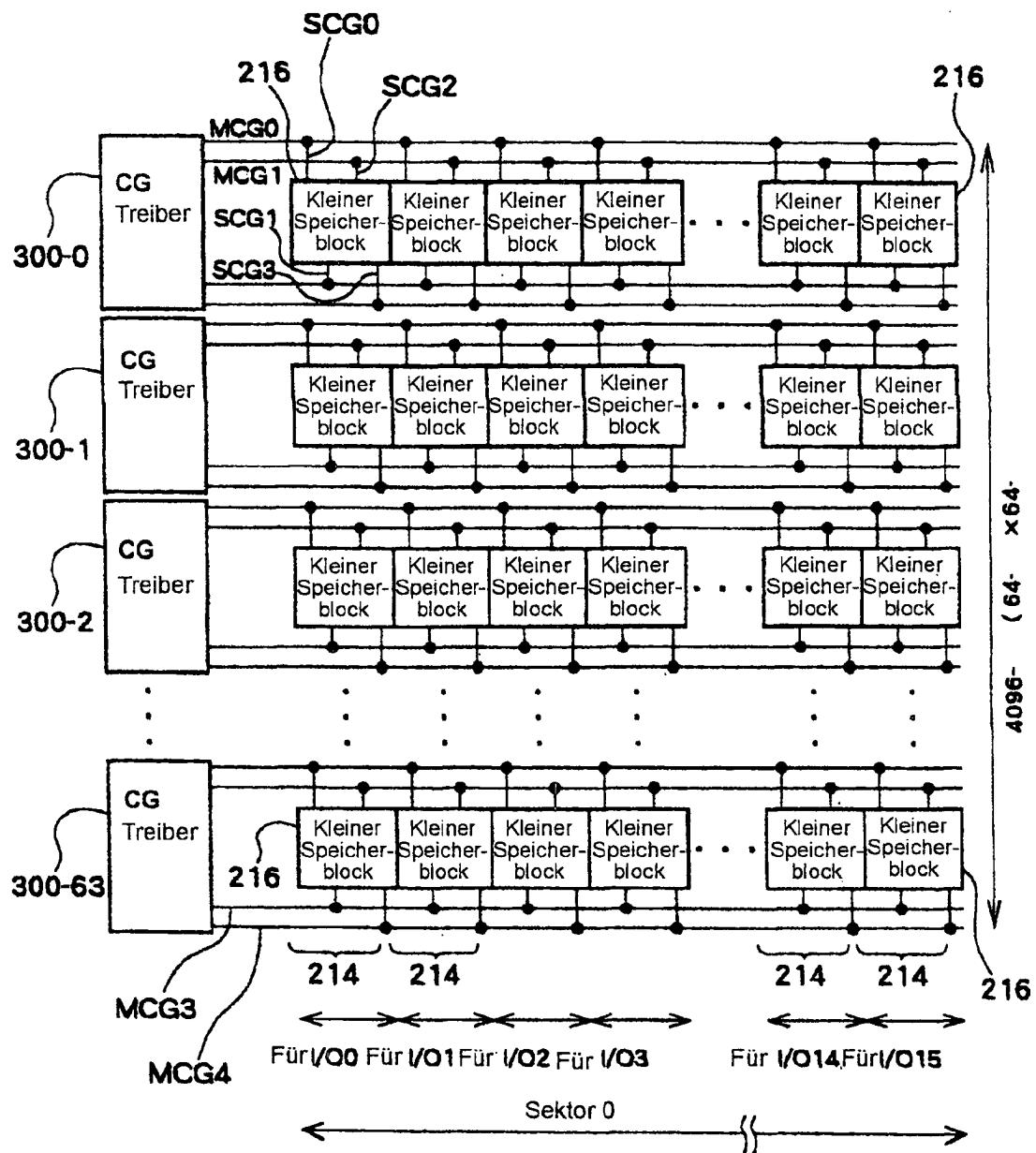

[0023] [Fig. 3](#) ist eine schematische Darstellung zur Beschreibung vieler kleiner Speicherblöcke und ihrer Verdrahtungen in einem in [Fig. 2B](#) gezeigten Sektorbereich.

[0024] [Fig. 4](#) zeigt ein Schaltkreisdiagramm eines in [Fig. 3](#) gezeigten, kleinen Speicherblocks.

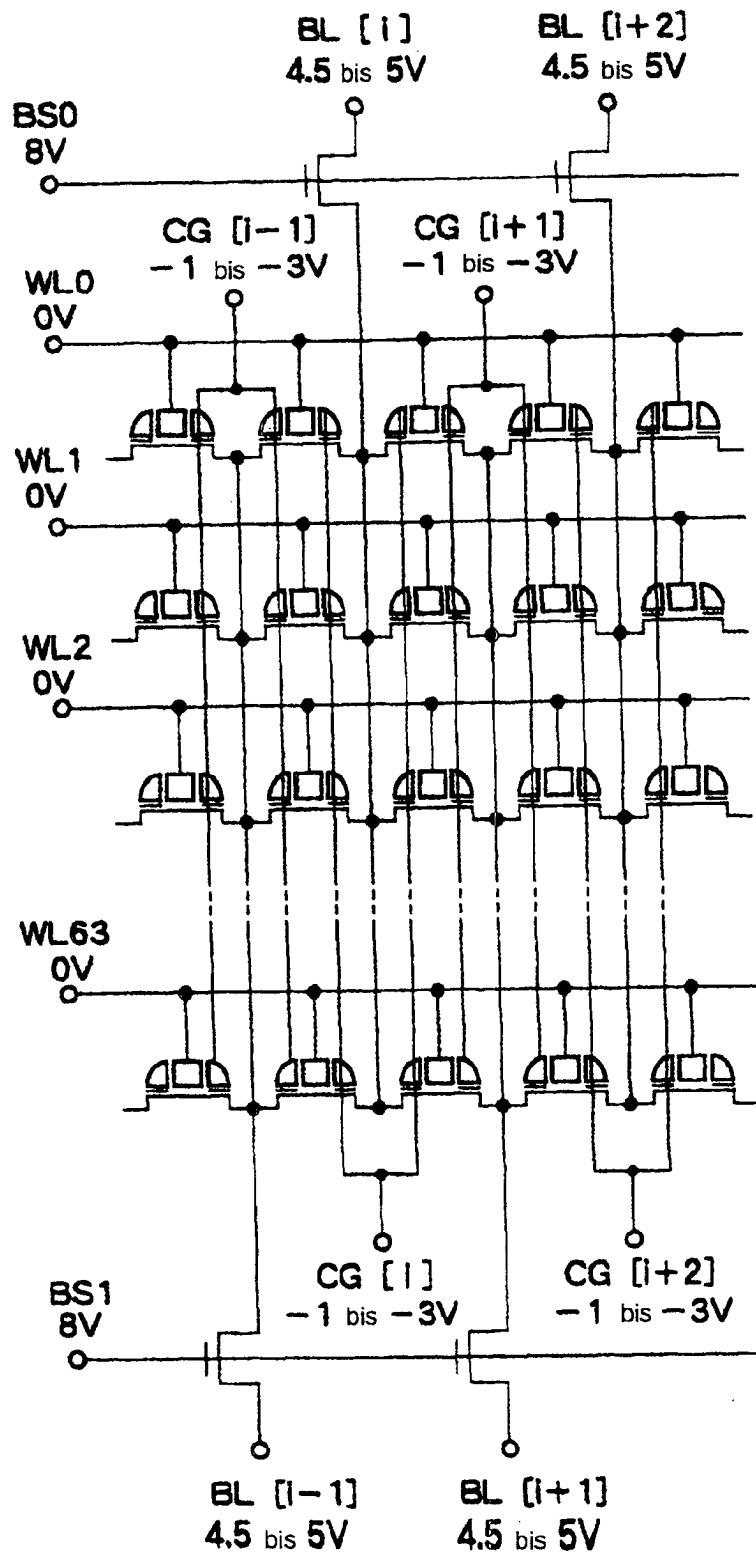

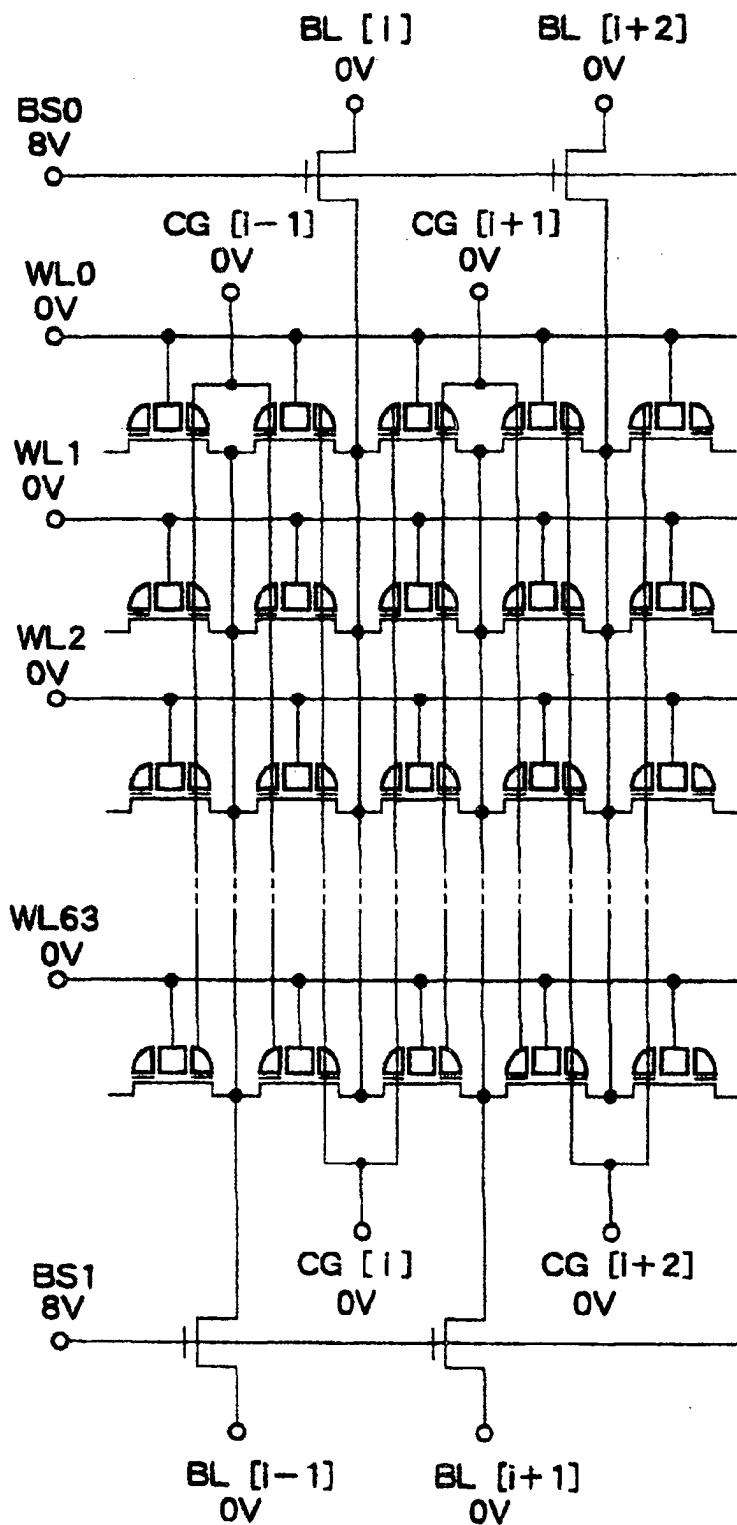

[0025] [Fig. 5](#) zeigt ein Schaltkreisdiagramm zur Darstellung des Verhältnisses zwischen kleinen Speicherblöcken und Steuer-Gatetreibern, die in [Fig. 3](#) gezeigt sind.

[0026] [Fig. 6](#) ist eine schematische Darstellung zur Beschreibung des Verhältnisses zwischen zwei Speicherblöcken und lokalen Treibern in zwei einander benachbarten Sektoren.

[0027] [Fig. 7](#) ist eine schematische Darstellung zur Beschreibung eines ausgewählten Blocks, eines diesem gegenüberliegenden, nicht ausgewählten Gegenblocks und weiterer nicht ausgewählter Blöcke.

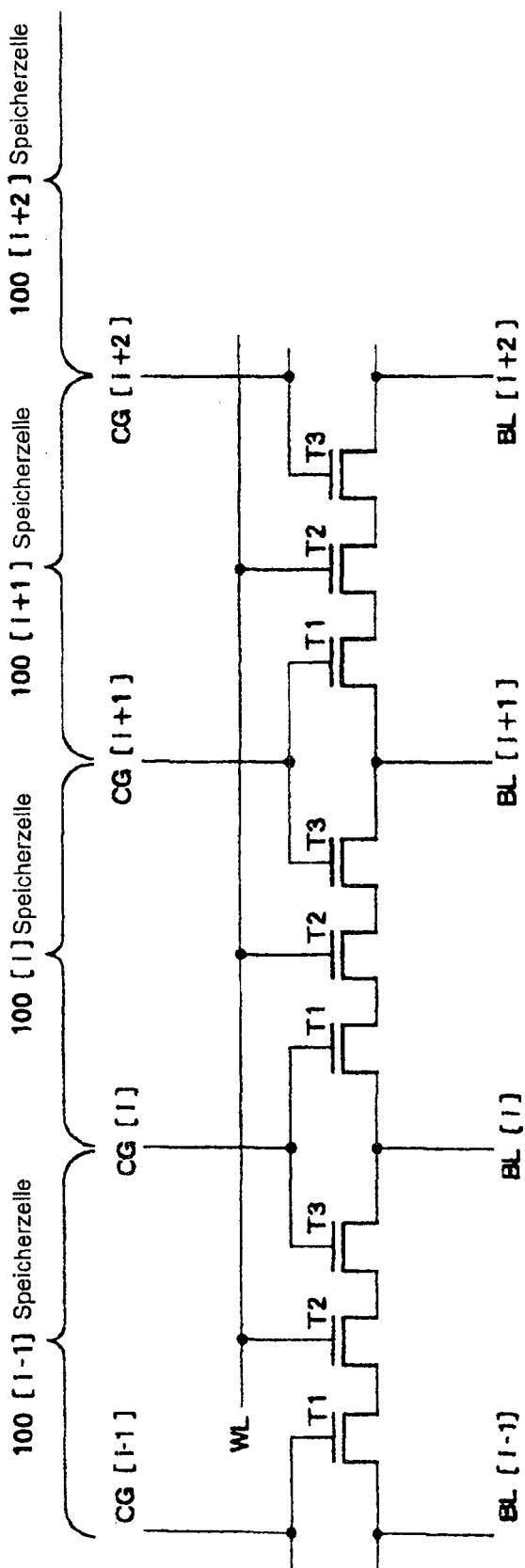

[0028] [Fig. 8](#) ist ein Ersatzschaltbild der in [Fig. 1](#) gezeigten Speicherzellen.

[0029] [Fig. 9](#) ist eine schematische Darstellung zur Beschreibung eines Datenlesevorgangs in dem in [Fig. 1](#) gezeigten nichtflüchtigen Halbleiterspeicherbaustein.

[0030] [Fig. 10](#) ist eine schematische Darstellung zur Beschreibung von Spannungen, die während des Datenlesens in einem ausgewählten Block gesetzt sind.

[0031] [Fig. 11](#) zeigt Kurvenprofile der Beziehung zwischen Steuer-Gatespannungen VCG und Source-Drain-Strom Ids in der in [Fig. 1](#) gezeigten Speicherzelle.

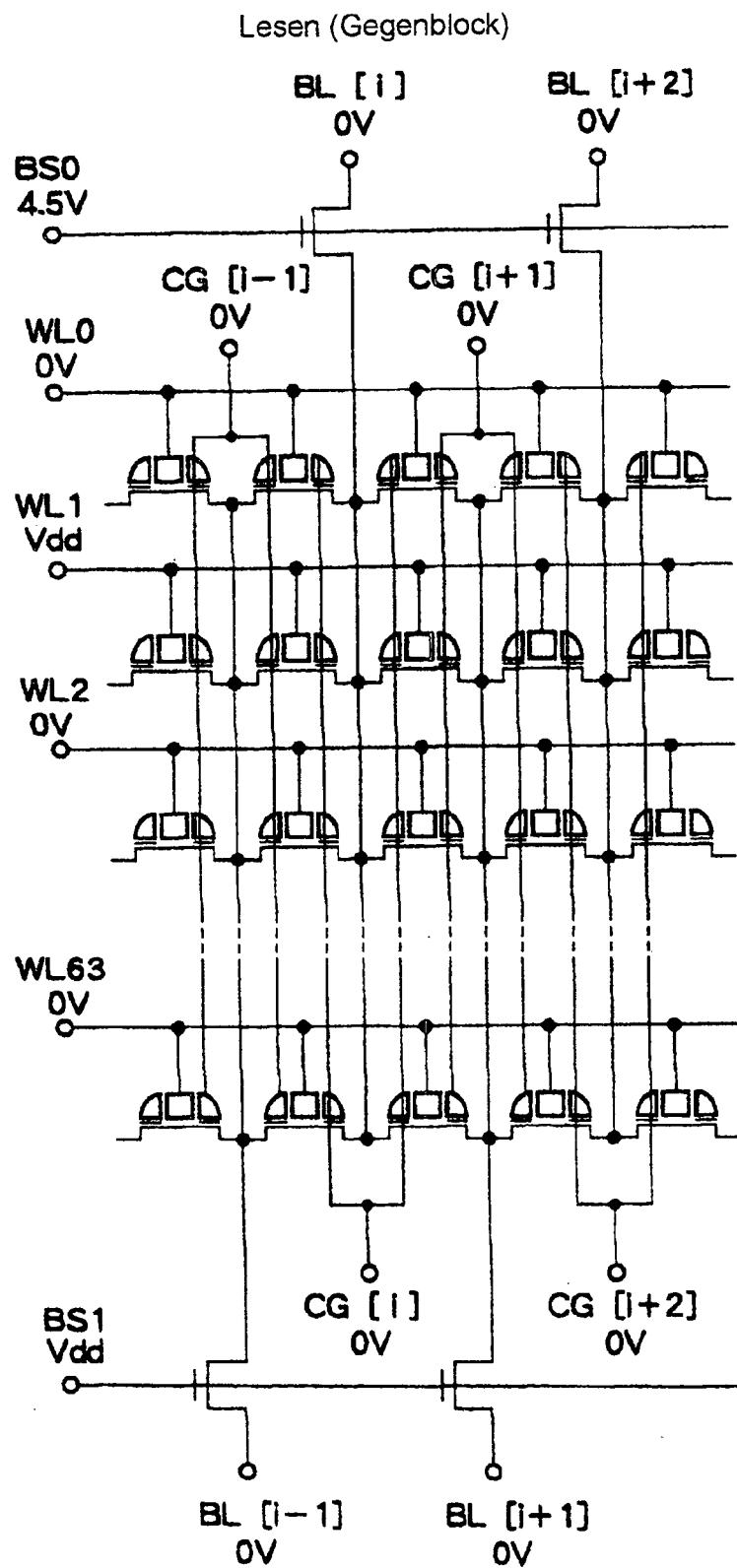

[0032] [Fig. 12](#) ist eine schematische Darstellung zur Beschreibung von Spannungen, die während des Datenlesens in einem nicht ausgewählten Gegenblock gesetzt sind.

[0033] [Fig. 13](#) ist eine schematische Darstellung zur Beschreibung von Spannungen, die während des Datenlesens in anderen nicht ausgewählten Blöcken als dem Gegenblock gesetzt sind.

[0034] [Fig. 14](#) ist eine schematische Darstellung zur Beschreibung eines Datenschreibvorganges (Programmieren) in dem in [Fig. 1](#) gezeigten nichtflüchtigen Halbleiterspeicherbaustein.

[0035] [Fig. 15](#) ist eine schematische Darstellung zur Beschreibung von Spannungen, die während des Datenprogrammierens in einem ausgewählten Block gesetzt sind.

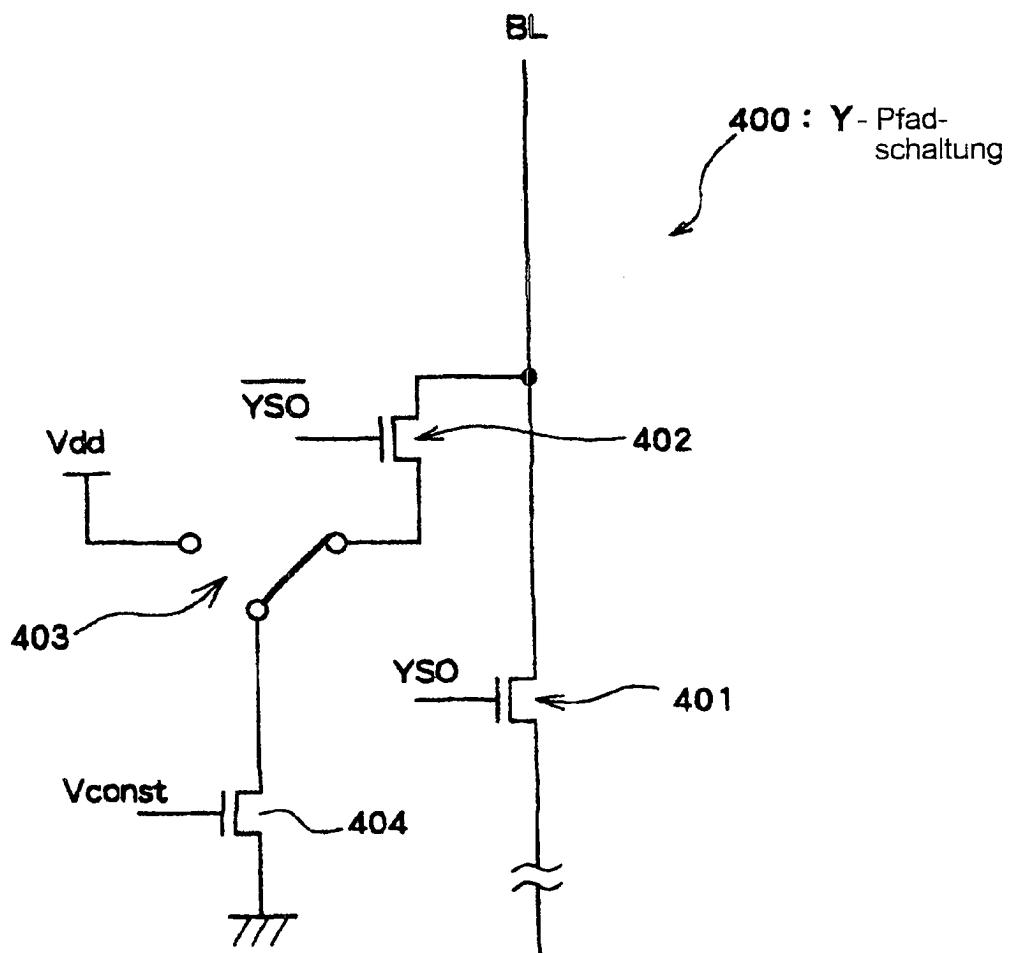

[0036] [Fig. 16](#) zeigt schematisch eine Y-Pfadsschaltung, die mit der Bitleitung verbunden ist.

[0037] [Fig. 17](#) ist eine schematische Darstellung zur Beschreibung von Spannungen, die während der Datenprogrammierung in einem nicht ausgewählten Gegenblock gesetzt sind.

[0038] [Fig. 18](#) ist eine schematische Darstellung zur Beschreibung von Spannungen, die während der Datenprogrammierung in anderen nicht ausgewählten Blöcken als dem Gegenblock gesetzt sind.

[0039] [Fig. 19](#) ist eine schematische Darstellung zur Beschreibung von Spannungen, die während der Datenprogrammierung in einem ausgewählten Block gesetzt sind, in Bezug auf Speicherelemente an der ausgewählten Seite, die sich von den in [Fig. 15](#) gezeigten unterscheiden.

[0040] [Fig. 20](#) ist eine schematische Darstellung zur Beschreibung eines Datenlöschvorgangs in dem in [Fig. 1](#) gezeigten nichtflüchtigen Halbleiterspeicherbaustein.

[0041] [Fig. 21](#) ist eine schematische Darstellung zur Beschreibung von Spannungen, die im Zeitpunkt der Datenlöschung in einem ausgewählten Block gesetzt sind.

[0042] [Fig. 22](#) ist eine schematische Darstellung zur Beschreibung von Spannungen, die im Zeitpunkt der Datenlöschung in einem nicht ausgewählten Gegenblock gesetzt sind.

[0043] [Fig. 23](#) ist eine schematische Darstellung zur Beschreibung von Spannungen, die im Zeitpunkt der Datenlöschung in anderen nicht ausgewählten Blöcken als dem Gegenblock gesetzt sind.

#### DETAILLIERTE BESCHREIBUNG

[0044] Ausführungsbeispiele der vorliegenden Erfindung werden unter Hinweis auf die beigefügten Zeichnungen beschrieben.

##### Aufbau einer Doppelspeicherzelle

[0045] [Fig. 1](#) zeigt einen Querschnitt durch einen nichtflüchtigen Halbleiterspeicherbaustein. In [Fig. 1](#) gehört zu einer einzigen Doppelspeicherzelle **100** ein Wort-Gate **104** aus einem Material unter Einschluß von beispielsweise polykristallinem Silizium und eine Mulde **102** des P-Typs mit einer Gate-Oxidschicht dazwischen,

ein erstes und ein zweites Steuer-Gate **106A** und **106B** sowie ein erstes und ein zweites Speicherelement **108A** und **108B** (MONOS-Speicherelemente).

**[0046]** Das erste und das zweite Steuer-Gate **106A** und **106B** sind an zwei Wänden des Wort-Gates **104** ausgebildet und gegenüber dem Wort-Gate **104** elektrisch isoliert.

**[0047]** Sowohl das erste als auch das zweite Speicherelement **108A** und **108B** besteht aus einem Schichtstapel aus einer Oxidschicht (O), einer Nitridschicht (N) und einer Oxidschicht (O) zwischen dem ersten oder zweiten Steuer-Gate **106A** und **106B**, aus polykristallinem Silizium entsprechend dem M (Metall) von MONOS und der Mulde **102** des P-Typs. Es sei erwähnt, daß das erste und zweite Steuer-Gate **106A** und **106B** aus einem leitfähigen Werkstoff, beispielsweise Silizid, gebildet sein kann.

**[0048]** Auf diese Weise sind in einer Doppelspeicherzelle **100** das erste und zweite MONOS-Speicherelement **108A** und **108B** mit geteilten Gates versehen (erstes und zweites Steuer-Gate **106A** und **106B**), und das erste und zweite MONOS-Speicherelement **108A** und **108B** nutzen gemeinsam ein Wort-Gate **104**.

**[0049]** Sowohl das erste als auch das zweite MONOS-Speicherelement **108A** und **108B** wirkt als Ladungsfallenstelle. Sowohl das erste als auch das zweite MONOS-Speicherelement **108A** und **108B** kann auf der ONO-Schicht **109** Ladung einfangen.

**[0050]** Wie [Fig. 1](#) zeigt, ist eine Vielzahl von Wort-Gates **104** in Intervallen in Reihenrichtung (eine zweite Richtung B in [Fig. 1](#)) angeordnet und gemeinsam mit einer einzigen Wortleitung WL verbunden, die aus Polygid gebildet ist., Auch die in [Fig. 1](#) gezeigten Steuer-Gates **106A** und **106B** erstrecken sich in Spaltenrichtung (eine erste Richtung A senkrecht zur Zeichnungsebene der [Fig. 1](#)) und werden gemeinsam von einer Vielzahl der Doppelspeicherzellen **100** benutzt, die in der Spaltenrichtung angeordnet sind. Folglich kann man die Elemente **106A** und **106B** auch als Steuer-Gateleitungen bezeichnen.

**[0051]** Hier ist das Steuer-Gate **106B** der [i]ten Doppelspeicherzelle **100[i]** und das Steuer-Gate **106A** der [i+1]ten Doppelspeicherzelle **100[i+1]** an eine Sekundärsteuer-Gateleitung SCG [i+1] angeschlossen, die aus einer Metallschicht gebildet ist, die beispielsweise oberhalb des Wort-Gate, der Steuer-Gates und der Wortleitungen vorgesehen ist.

**[0052]** In der Mulde **102** des P-Typs ist eine [i+1]te Störstellenschicht **110[i+1]** vorgesehen, die gemeinsam genutzt wird von dem MONOS-Speicherelement **108B** der [i]ten Doppelspeicherzelle **100[i]** und dem MONOS-Speicherelement **108A** der [i+1]ten Doppelspeicherzelle **100[i+1]**.

**[0053]** Die Störstellenschichten **110[i]**, **[i+1]** und **[i+2]** sind beispielsweise N-leitende Störstellen, die in einer P-leitenden Mulde ausgebildet sind, sich in Spaltenrichtung erstrecken (in der ersten Richtung A senkrecht zur Zeichnungsfläche der [Fig. 1](#)) und als Bitleitungen wirken, die von der Vielzahl der Doppelspeicherzellen **100** gemeinsam genutzt werden, welche in der Spaltenrichtung angeordnet sind. Dementsprechend werden die Elemente **100[i]**, **[i+1]** und **[i+2]** auch als Bitleitungen BL[i], **[i+1]** und **[i+2]** bezeichnet.

#### Gesamtaufbau des nichtflüchtigen HalbleiterSpeicherbausteins

**[0054]** Der Gesamtaufbau eines nichtflüchtigen HalbleiterSpeicherbausteins, der mit Hilfe der oben beschriebenen Doppelspeicherzellen **100** gebildet ist, wird unter Hinweis auf die [Fig. 2A](#) bis [Fig. 2E](#) beschrieben.

**[0055]** [Fig. 2A](#) zeigt einen Grundrißplan eines nichtflüchtigen HalbleiterSpeicherbausteins in Form eines einzigen Chips, der einen Speicherzellenmatrixbereich **200** und einen globalen Wortleitungsdekodierer **201** umfaßt. Der Speicherzellenmatrixbereich **200** umfaßt zum Beispiel insgesamt 64 Sektorbereiche **210**, nämlich einen 0<sup>ten</sup> bis 63<sup>ten</sup> Sektorbereich.

**[0056]** Die 64 Sektorbereiche **210** sind durch Teilen des Speicherzellenmatrixbereichs **200** in der zweiten Richtung (Reihenrichtung) B erhalten, wie in [Fig. 2A](#) gezeigt. Jeder der Sektorbereiche **210** hat eine langgestreckte, rechteckige Gestalt, deren Längsrichtung in der ersten Richtung (Spaltenrichtung) A verläuft. Die Mindesteinheit zum Löschen von Daten ist der Sektorbereich **210**, und in diesem Sektorbereich **210** gespeicherte Daten werden auf einmal oder mit einer Zeiteinteilung gelöscht.

**[0057]** Der Speicherzellenmatrixbereich **200** umfaßt zum Beispiel 4K Wortleitungen WL und 4K Bitleitungen BL. Bei dem vorliegenden Ausführungsbeispiel sind zwei MONOS-Speicherelemente **108A** und **108B** mit einer

Bitleitung BL verbunden. Deshalb bedeutet 4K Bitleitungen BL eine Speicherkapazität von 8K Bits. Jeder der Sektorbereiche **210** hat eine Speicherkapazität, die ein Vierundsechzigstel (1/64) der Speicherkapazität des gesamten Speichers und eine Speicherkapazität, bestimmt durch (4K Wortleitungen WL)  $\times$  (64 Bitleitungen BL)  $\times$  2, ist.

**[0058]** [Fig. 2B](#) zeigt im einzelnen zwei benachbarte ( $0^{\text{ten}}$  und  $1^{\text{sten}}$ ) der Sektorbereiche **210** in dem in [Fig. 2A](#) gezeigten nichtflüchtigen Halbleiter-speicherbaustein. Wie aus [Fig. 2B](#) hervorgeht, sind zu beiden Seiten der beiden Sektoren **210** lokale Treiber **220A** und **220B** angeordnet (die jeder einen lokalen Steuer-Gatetreiber, einen lokalen Bitleitungsauswahltreiber und einen lokalen Wortleitungstreiber umfassen). Auch eine Bereichssteuerschaltung **222** ist zum Beispiel an einer Oberseite der bei den Sektoren **210** und der beiden lokalen Treiber **220A** und **220B** vorgesehen.

**[0059]** Jeder der Sektorbereiche **210** ist in der zweiten Richtung aufgeteilt, so daß jeder sechzehn Speicherblöcke (Speicherblöcke entsprechen input/output Bits) für I/O0 bis I/O15 hat, die es ermöglichen, 16 Bits Daten zu lesen und zu schreiben. Jeder der Speicherblöcke hat 4K (4096) Wortleitungen WL, wie in [Fig. 2B](#) gezeigt.

**[0060]** Wie [Fig. 2C](#) zeigt, ist jeder der in [Fig. 2B](#) gezeigten Sektorbereiche **210** in der ersten Richtung A in acht große Blöcke **212** unterteilt. Jeder der großen Blöcke **212** ist in der ersten Richtung A in acht kleine Blöcke **215** unterteilt, wie in [Fig. 2D](#) gezeigt.

**[0061]** Jeder der kleinen Blöcke **215** hat 64 Wortleitungen WL, wie in [Fig. 2E](#) gezeigt.

#### Einzelheiten eines Sektorbereichs

**[0062]** [Fig. 3](#) zeigt den in [Fig. 2A](#) dargestellten Sektorbereich 0 im einzelnen. Wie [Fig. 4](#) zeigt, umfaßt der in [Fig. 3](#) gezeigte kleine Speicherblock **216** die Doppelspeicherzellen **100**, die in einer Matrix von zum Beispiel 64 in Spaltenrichtung und zum Beispiel 4 in Reihenrichtung angeordnet sind. Jeder der kleinen Speicherblöcke **216** ist zum Beispiel an 4 Sekundärsteuer-Gateleitungen SCG0 bis SCG3, 4 Bitleitungen BL0 bis BL3, bei denen es sich um Dateneingabe- und Ausgabeleitungen handelt, sowie 64 Wortleitungen WL angeschlossen.

**[0063]** Die geradzahligen Sekundärsteuer-Gateleitungen SCG0 und SCG2 sind zusammen an die zweiten Steuer-Gates **106B** der Vielzahl der Doppelspeicherzellen in einer geradzahligen Spalte (0<sup>te</sup> Spalte oder 2<sup>te</sup> Spalte) bzw. an die ersten Steuer-Gates **106A** der Vielzahl Doppelspeicherzellen in einer ungeradzahligen Spalte (die 1<sup>te</sup> Spalte oder die 3<sup>te</sup> Spalte) angeschlossen. Ähnlich sind die ungeradzahligen Sekundärsteuer-Gateleitungen SCG1 und SCG3 zusammen an die zweiten Steuer-Gates **106B** der Vielzahl Doppelspeicherzellen in einer ungeradzahligen Spalte (die 1<sup>te</sup> Spalte oder die 3<sup>te</sup> Spalte) bzw. die ersten Steuer-Gates **106A** der Vielzahl Doppelspeicherzellen in einer ungeradzahligen Spalte (die 2<sup>te</sup> Spalte oder die 4<sup>te</sup> Spalte) angeschlossen.

**[0064]** Wie aus [Fig. 3](#) hervorgeht, sind 64 kleine Speicherblöcke **216** in Spaltenrichtung in jedem der Speicherblöcke **214** angeordnet, und 16 Speicherblöcke **214** entsprechend 16 I/O0 bis I/O15 sind in Reihenrichtung zum Eingeben und Ausgeben von 16 Bits angeordnet.

**[0065]** 16 Sekundärsteuer-Gateleitungen SCG0 der 16 kleinen Speicherblöcke **216**, die in Reihenrichtung angeordnet sind, sind gemeinsam in Reihenrichtung an eine Hauptsteuer-Gateleitung MCG0 angeschlossen. Ähnlich sind 16 Sekundärsteuer-Gateleitungen SCG1 gemeinsam an eine Hauptsteuer-Gateleitung MCG1 angeschlossen, 16 Sekundärsteuer-Gateleitungen SCG2 sind gemeinsam an eine Hauptsteuer-Gateleitung MCG2 angeschlossen, und 16 Sekundärsteuer-Gateleitungen SCG3 sind gemeinsam an eine Hauptsteuer-Gateleitung MCG3 angeschlossen.

**[0066]** Es sind CG-Treiber **300-0** bis **300-63** vorgesehen, die als Steuer-Gateabschnitte für den Sektorbereich 0 dienen. Die CG-Treiber **300** sind mit den 4 Hauptsteuer-Gateleitungen MCG0 bis MCG3 verbunden, welche sich in Reihenrichtung erstrecken.

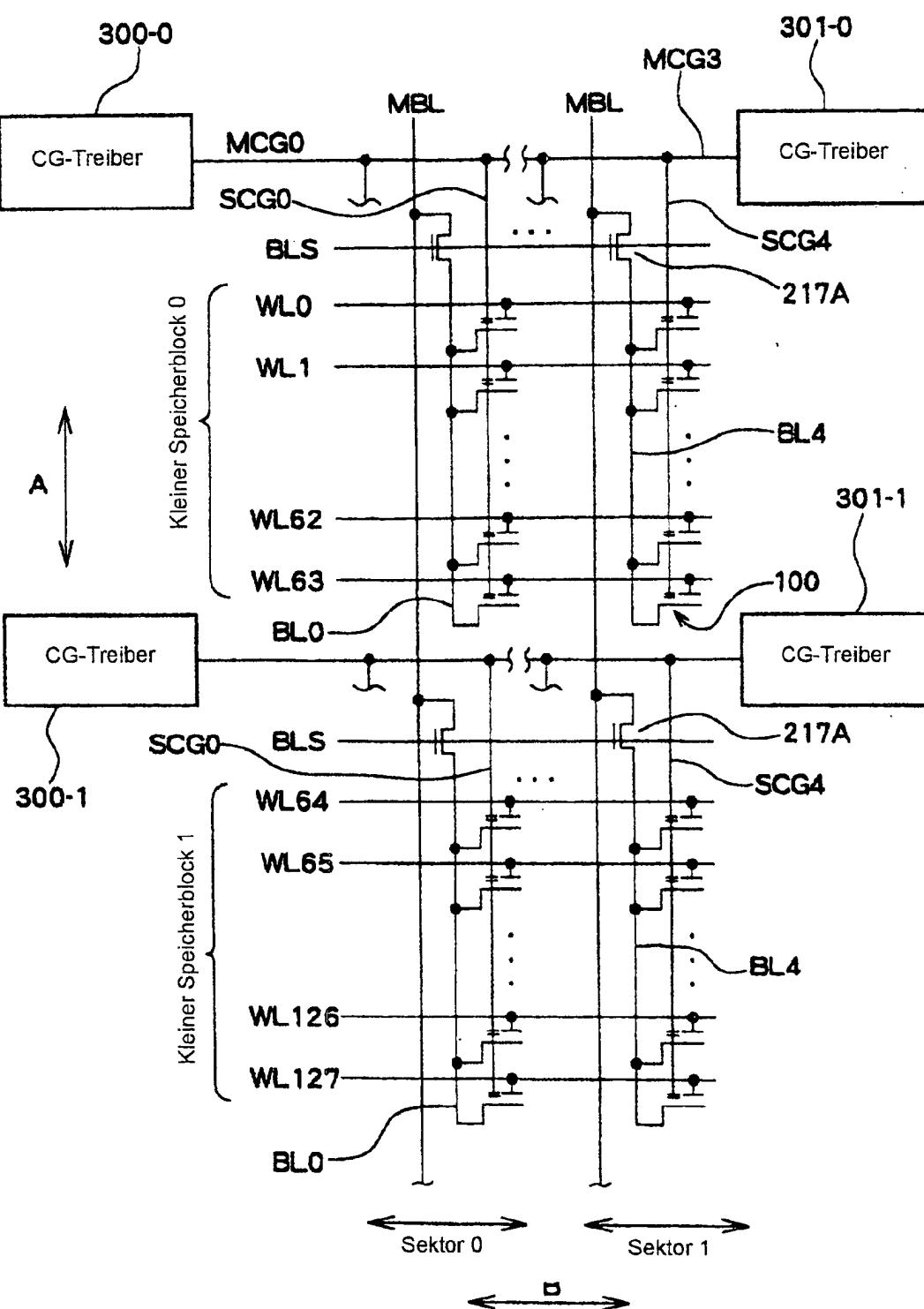

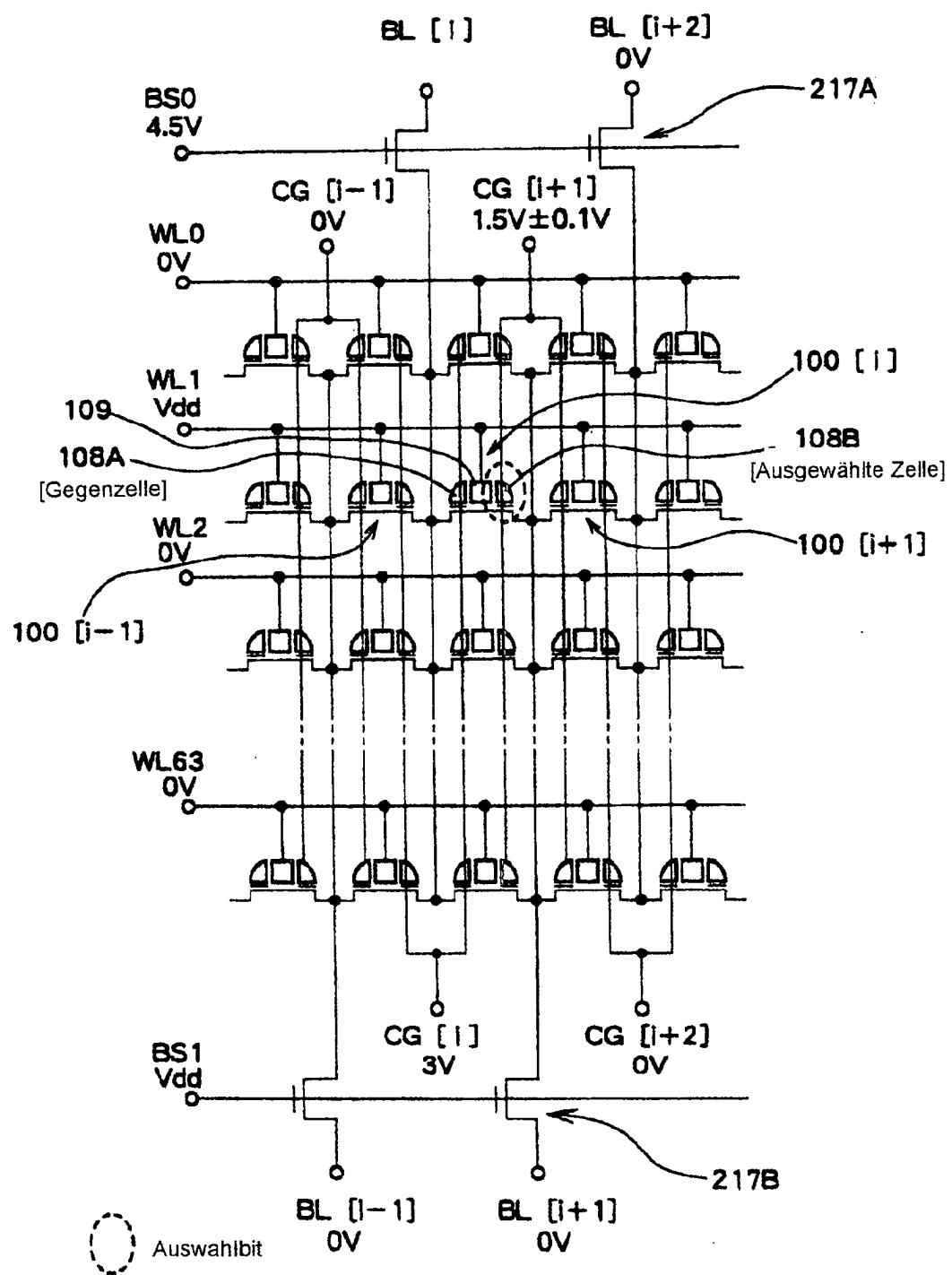

**[0067]** [Fig. 5](#) zeigt das Verhältnis zwischen den einander benachbarten Sektorbereichen 0 und 1. Der Sektorbereich 0 und der Sektorbereich 1 benutzen gemeinsam die Wortleitung WL, sind aber mit der Hauptsteuer-Gateleitung MCG und der Hauptbitleitung MBL unabhängig voneinander versehen. Im einzelnen zeigt [Fig. 5](#) die dem Sektorbereich 0 entsprechenden CG-Treiber **300-0** und **300-1** sowie die dem Sektorbereich 1 entsprechenden CG-Treiber **301-0** und **301-1**, wobei die CG-Treiber für jeden der Sektorbereiche unabhängig vorgesehen sind.

**[0068]** Jede der für jeden der kleinen Speicherblöcke **216** vorgesehenen Bitleitungen BL0 (eine Störstellen-schicht) ist zusammen an die Hauptbitleitung MBL angeschlossen, bei der es sich um eine Metallverdrahtung handelt. Die Hauptbitleitung MBL wird von den kleinen Speicherblöcken gemeinsam benutzt, die in Spaltenrichtung angeordnet sind. Ein Bitleitungsauswahlgate **217A** ist in einem Weg von der Hauptbitleitung MBL zu jeder Bitleitung BL0 in jedem der kleinen Speicherblöcke vorgesehen. Es sei darauf hingewiesen, daß die Bitleitungsauswahlgates **217A** mit den entsprechenden geradzahligen Bitleitungen BL0, BL2, BL4,... verbunden sind, während die Bitleitungsauswahlgates **217B**, auch wenn sie in [Fig. 5](#) nicht gezeigt sind, mit den ungeradzahligen Bitleitungen BL1, BL3, BL5, ... verbunden sind (siehe [Fig. 10](#) und [Fig. 15](#)).

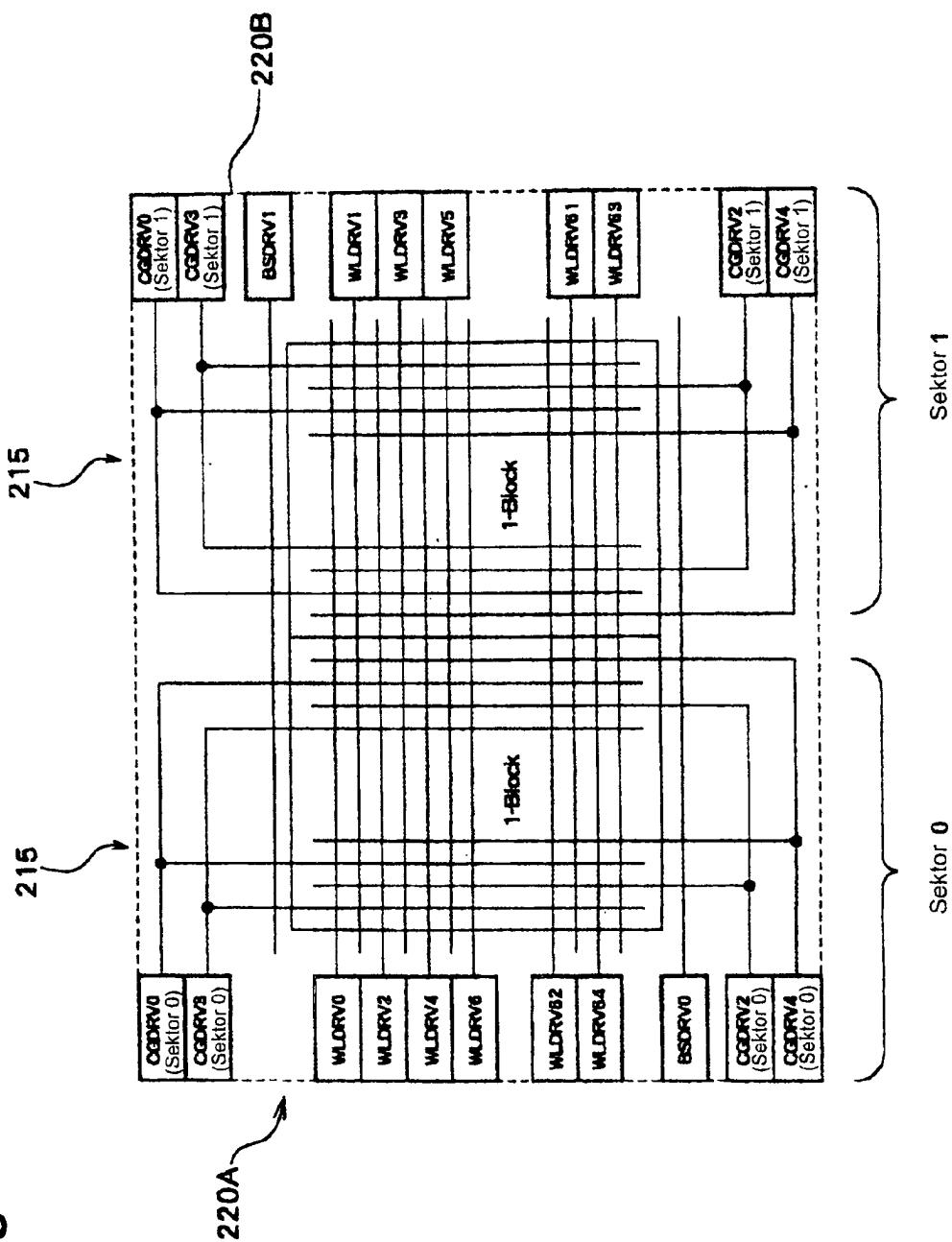

**[0069]** Zwei kleine Blöcke **215** in dem 0<sup>ten</sup> und 1<sup>ten</sup> Sektorbereich **210** sind einander benachbart, und die lokalen Treiber **220A** und **220B** an deren beiden Seiten sind im einzelnen in [Fig. 6](#) gezeigt. Wie aus [Fig. 6](#) hervorgeht, sind in dem lokalen Treiber **220** an der linken Seite vier lokale Steuer-Gateleitungstreiber CGDRV0 bis CGDRV3 entsprechend den CG-Treibern **300** gemäß [Fig. 3](#) und [Fig. 5](#) vorgesehen. Ähnlich sind vier lokale Steuer-Gateleitungstreiber CGDRV0 bis CGDRV3 entsprechend den in [Fig. 5](#) gezeigten CG-Treibern **301** im lokalen Treiber **220B** an der rechten Seite vorgesehen.

**[0070]** In dem lokalen Treiber **220A** auf der linken Seite sind auch lokale Wortleitungstreiber WLDRV0, WLDRV2,... WLDRV62 zum Ansteuern geradzahliger Wortleitungen WL0, 2,... 62 in den Sektoren 0 und 1 sowie WLDRV0 zum Ansteuern einer redundanten Wortleitung im Sektor 0 angeordnet. In dem lokalen Treiber **220A** auf der rechten Seite sind lokale Wortleitungstreiber WLDRV1, WLDRV3, ... WLDRV63 zum Ansteuern ungeradzahliger Wortleitungen WL1, 3,... 63 in den Sektoren 0 und 1 sowie WLDRV0 zum Ansteuern einer redundanten Wortleitung im Sektor 1 angeordnet.

**[0071]** Darüber hinaus ist ein lokaler Bitleitungstreiber BSRV0 zum Ansteuern des Bitleitungsauswahlgate **217A**, welches beispielsweise mit den geradzahligen Bitleitungen BL0 und BL2 in den Sektoren 0 und 1 verbunden ist, im lokalen Treiber **220A** an der linken Seite vorgesehen. Ein lokaler Bitleitungstreiber BSRV1 zum Ansteuern des Bitleitungsauswahlgate **217B**, welches zum Beispiel mit den ungeradzahligen Bitleitungen BL1 und BL3 in den Sektoren 0 und 1 verbunden ist, ist im lokalen Treiber **220B** auf der rechten Seite vorgesehen.

#### Beschreibung des Betriebs

**[0072]** Nachfolgend werden Vorgänge des Datenlesens, Datenprogrammierens und Datenlöschens in einem nichtflüchtigen Halbleiterspeicherbaustein gemäß einem Ausführungsbeispiel der vorliegenden Erfindung beschrieben.

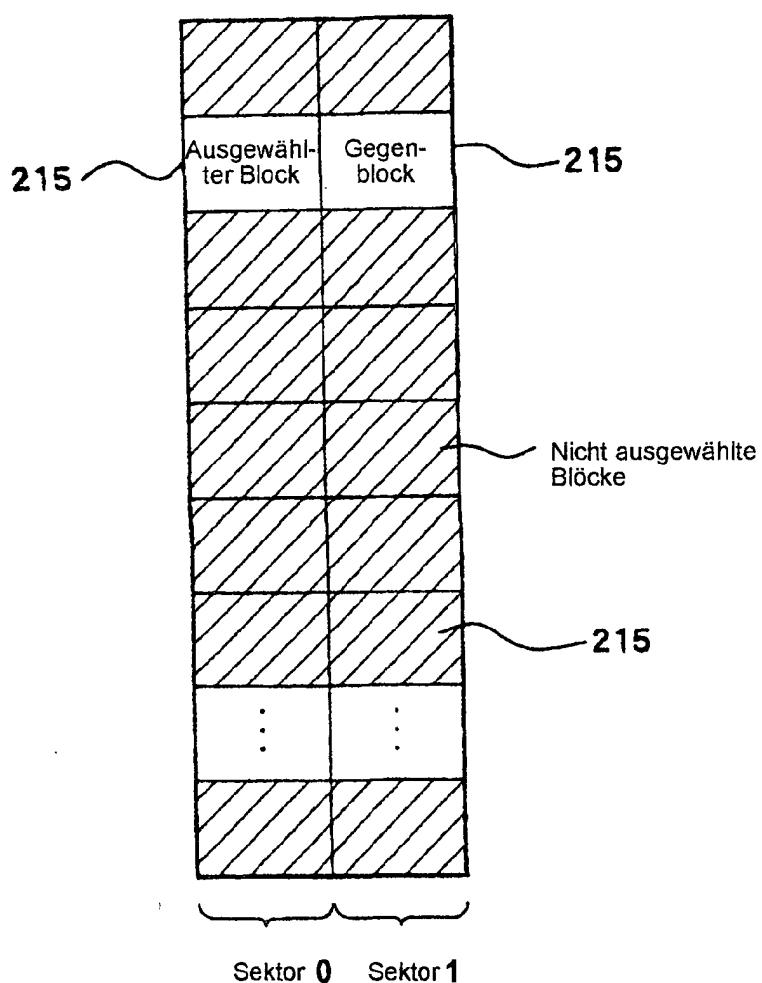

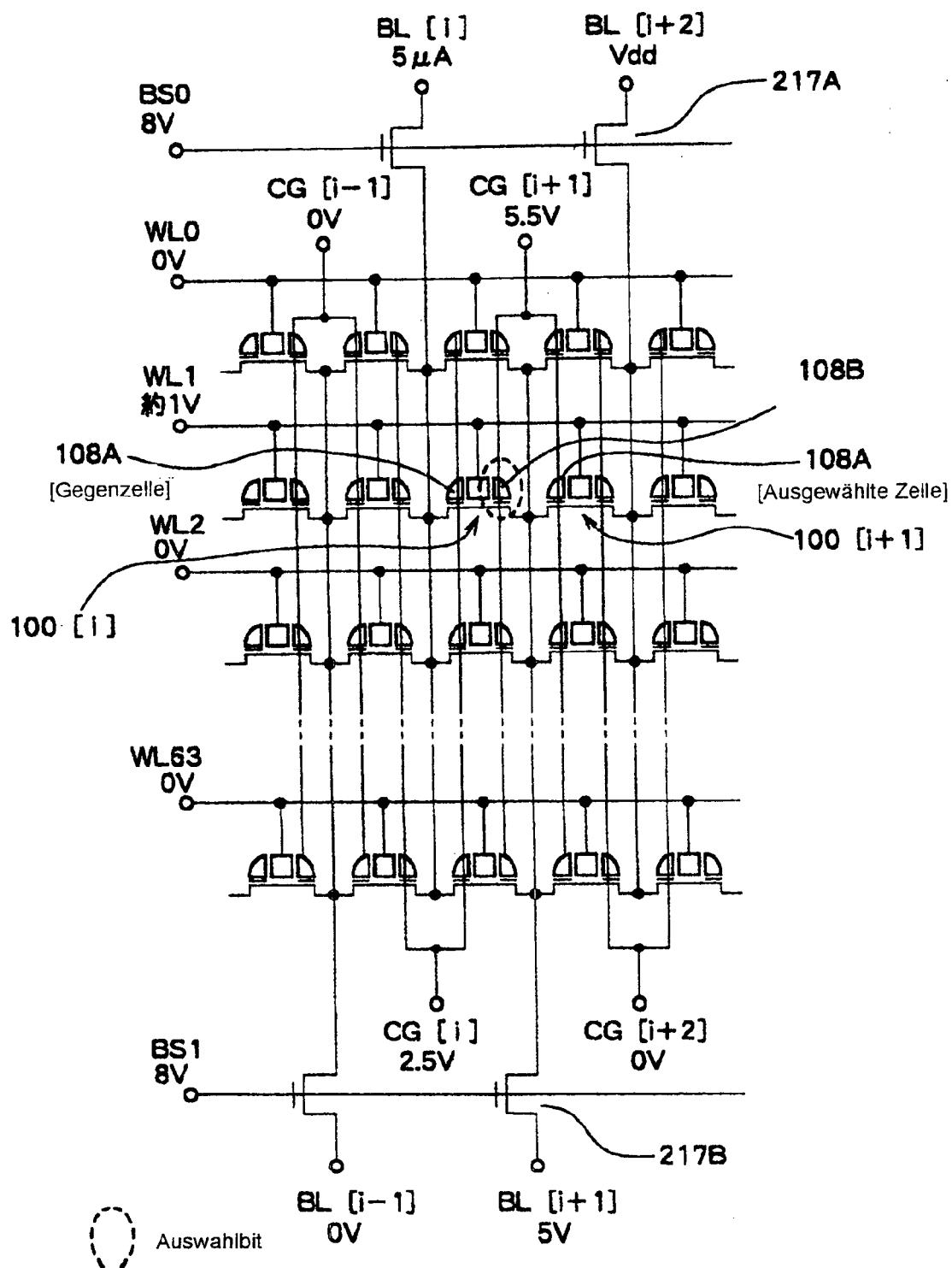

**[0073]** In der folgenden Beschreibung werden Ausdrücke, wie ausgewählter Block (Ausgewählter Block), nicht ausgewählter Gegenblock (Gegenblock) und nicht ausgewählter Block (Nicht ausgewählter Block) benutzt. Sie beziehen sich auf die kleinen Blöcke **215** mit verschiedenen Namen. Wie zum Beispiel in [Fig. 7](#) gezeigt, bedeutet der ausgewählte Block in einem Paar der Sektoren 0 und 1 zum Beispiel einen kleinen Block **215**, der im Sektor 0 ausgewählt ist. Der nicht ausgewählte Gegenblock ist ein kleiner Block **215** im Sektor 1 neben dem Sektor 0 und bedeutet einen kleinen Block **215**, der dem ausgewählten Block benachbart ist. Der nicht ausgewählte Block bedeutet sämtliche kleinen Blöcke **215** mit Ausnahme des ausgewählten Blocks und des Gegenblocks in den Sektoren 0 und 1 (einschließlich der Sektoren 2 bis 63).

**[0074]** Und beim Lesen oder Programmieren gibt es ausgewählte Zellen (Ausgewählte Zelle: ausgewählte Doppelspeicherzelle **100**) und nicht ausgewählte Zellen (Nicht ausgewählte Zelle: nicht ausgewählte Doppelspeicherzelle **100**), die in einem ausgewählten Block vorhanden sind. Ferner gibt es ein Speicherelement **108A** oder **108B** auf einer ausgewählten Seite (Ausgewählte Seite) und ein Speicherelement **108A** oder **108B** an einer gegenüberliegenden Seite (Gegenseite) in einer ausgewählten Zelle.

**[0075]** Ausgehend von den obigen Definitionen sind in den folgenden Tabellen 1 und 2 Potentiale an der Steuer-Gateleitung CG, Bitleitung BL und Wortleitung WL im Zeitpunkt des Lesens, Programmierens und Löschens gezeigt.

[Tabelle 1]

| Modus    | BS                                                      | Ausgewählter Block |                               |                      |                                     |                      |                                     |                                            |                                               |

|----------|---------------------------------------------------------|--------------------|-------------------------------|----------------------|-------------------------------------|----------------------|-------------------------------------|--------------------------------------------|-----------------------------------------------|

|          |                                                         | WL                 | Ausgewählte MONOS-Doppelzelle |                      |                                     |                      | Nicht ausgewählte MONOS-Doppelzelle |                                            |                                               |

|          |                                                         |                    | BL                            | CG                   | BL                                  | CG                   | WL                                  | BL                                         | CG                                            |

| Lesen    | 4.5V<br>(Gegen-<br>seite)<br>Vdd<br>(ausgew.<br>.Seite) | Vdd                | 0V                            | 1.5V<br>±<br>0.1V    | Lesen                               | 3V                   | Vdd<br>oder<br>0V                   | Lesen<br>oder 0V                           | 3V<br>oder<br>1.5V<br>±<br>0.1V<br>oder<br>0V |

| Programm | 8V                                                      | Etwa<br>1V         | 5V                            | 5.5V                 | I <sub>PRG</sub> =5μA<br>(0 bis 1V) | 2.5V                 | About<br>1V<br>oder<br>0V           | 5V<br>oder<br>Vdd<br>oder<br>(0 bis<br>1V) | 5.5V<br>oder<br>2.5V<br>oder<br>0V            |

| Löschen  | 8V                                                      | 0V                 | 4.5<br>to<br>5V               | -1<br>bis<br>-<br>3V | 4.5 bis 5V                          | -1<br>bis<br>-<br>3V |                                     |                                            |                                               |

[Table 2]

| Modus    | Gegenblock                                              |                    |    |    | Nicht ausgewählter Block |    |    |    |

|----------|---------------------------------------------------------|--------------------|----|----|--------------------------|----|----|----|

|          | BS                                                      | WL                 | BL | CG | BS                       | WL | BL | CG |

| Lesen    | 4.5V<br>(Gegen-<br>seite)<br>Vdd<br>(ausgew.<br>.Seite) | Vdd<br>oder<br>0V  | 0V | 0V | 0V                       | 0V | F  | 0V |

| Programm | 8V                                                      | Etwa 1V<br>oder 0V | 0V | 0V | 0V                       | 0V | F  | 0V |

| Löschen  | 8V                                                      | 0V                 | 0V | 0V | 0V                       | 0V | F  | 0V |

[0076] Ausgehend von Tabelle 1 und Tabelle 2 wird der Betrieb im jeweiligen Modus nachfolgend beschrieben.

Daten aus der Speicherzelle lesen

[0077] Eine Doppelspeicherzelle **100** kann, wie [Fig. 8](#) zeigt, als ein Typ bezeichnet werden, der einen Transistor T2, angesteuert vom Wort-Gate **104** sowie Transistoren T1 und T3 aufweist, die vom ersten bzw. zweiten Steuer-Gate **106A** bzw. **106B** angesteuert werden und miteinander in Reihe geschaltet sind.

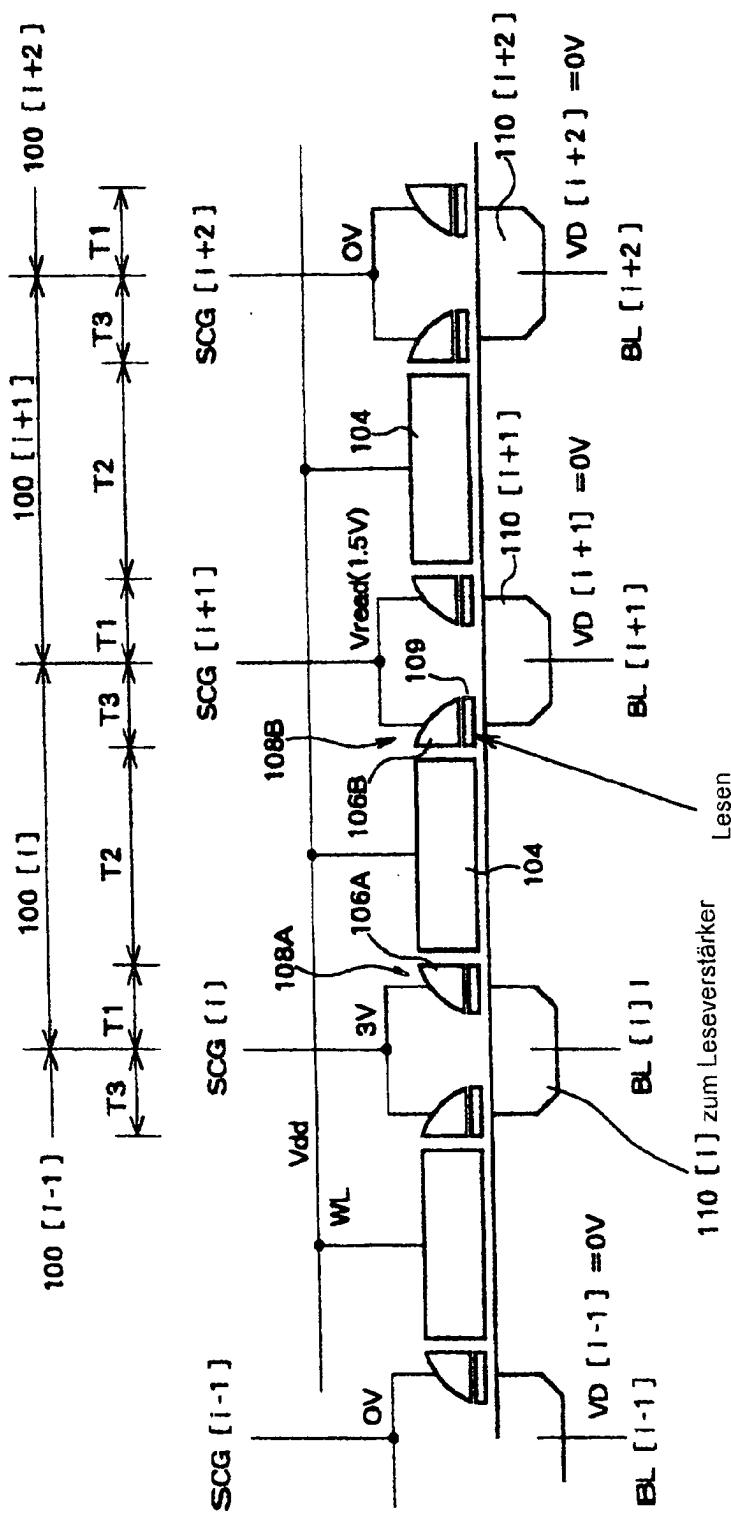

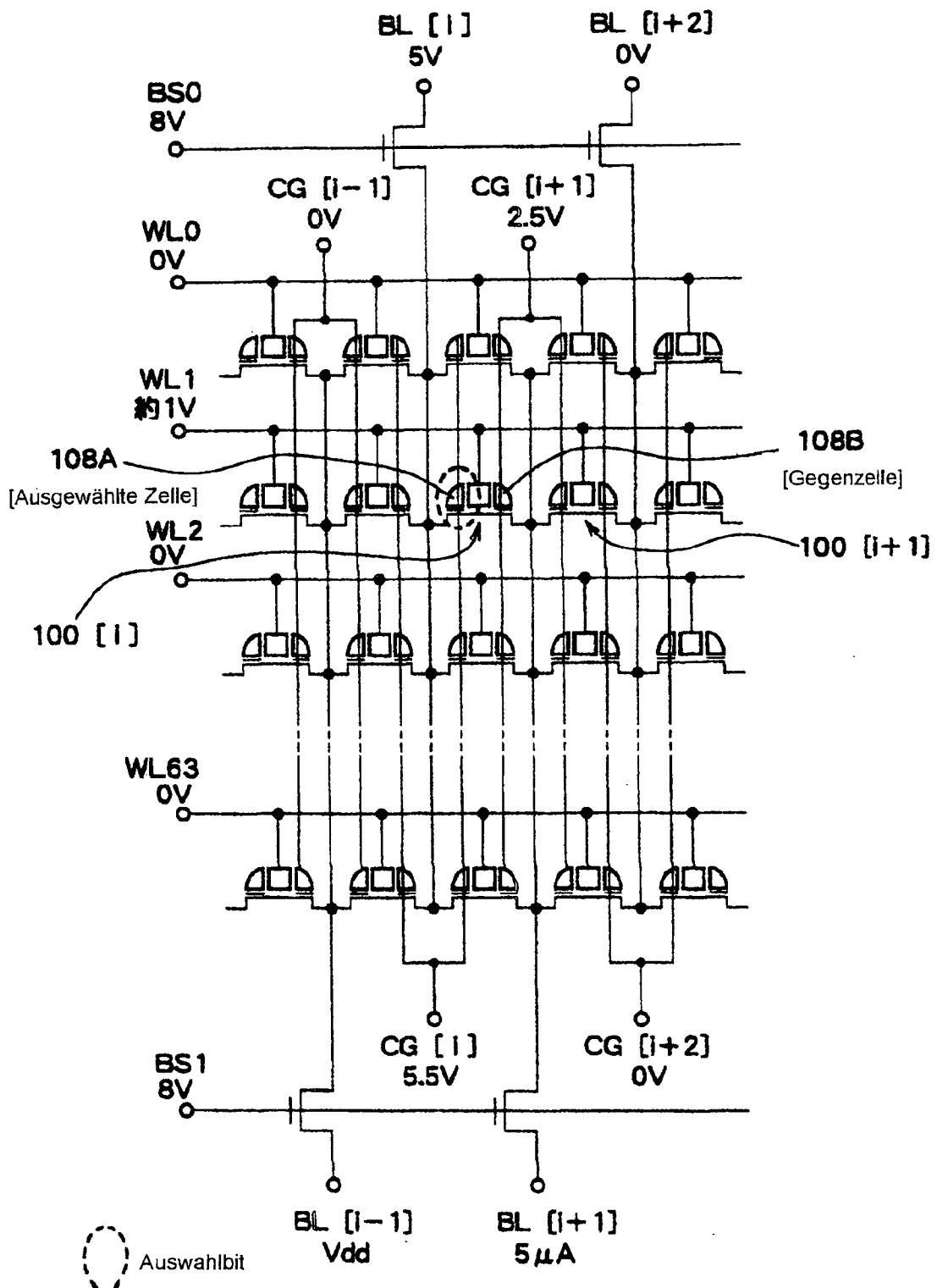

**[0078]** Vor der Beschreibung des Betriebs der Doppelspeicherzelle **100** wird zunächst das Setzen von Potentialen in bestimmten Abschnitten von drei einander benachbarten Doppelspeicherzellen **100[i-1]**, **[i]**, **[i+1]** und **[i+2]** in einem ausgewählten Block (einem ausgewählten kleinen Block **215**) beispielsweise im Sektor 0 beschrieben. Die Darstellung in [Fig. 9](#) kann benutzt werden, um das Lesen von Daten im Umkehrmodus aus dem MONOS-Speicherelement **108B** (ausgewählte Zelle) auf der rechten Seite des Wort-Gate **104** der Doppelspeicherzelle **100[i]** zu beschreiben, welches mit der Wortleitung WL1 verbunden ist. [Fig. 10](#) zeigt Spannungen, die in diesem Zeitpunkt am ausgewählten Block gesetzt sind.

**[0079]** Hierbei liegt eine Lesewortleitungsauswahlspannung Vdd (zum Beispiel 1,8 V) am Wort-Gate WL1 an, das in der gleichen Reihe wie die Doppelspeicherzelle **100[i]** vorhanden ist, um hierdurch die Transistoren T2 dieser Reihe durchzusteuern. Außerdem wird eine Übersteuerungsspannung (override voltage) (zum Beispiel 3 V) über die Sekundärsteuer-Gateleitung SCG[i] an das Steuer-Gate **106A** auf der linken Seite (einer Gegenzelle) der Doppelspeicherzelle **100[i]** angelegt, um dadurch den Transistor T1 durchzusteuern, der dem MONOS-Speicherelement **108A** entspricht. Eine Lesespannung Vread (zum Beispiel 1,5 V) wird als Spannung VCG an das Steuer-Gate **106B** auf der rechten Seite der Doppelspeicherzelle **100[i]** angelegt.

**[0080]** In diesem Moment arbeitet der dem MONOS-Speicherelement **108B** entsprechende Transistor T3 unterschiedlich, je nach dem, ob im MONOS-Speicherelement **108B** (ausgewählte Zelle) an der rechten Seite des Wort-Gate **104** Ladung gespeichert ist oder nicht.

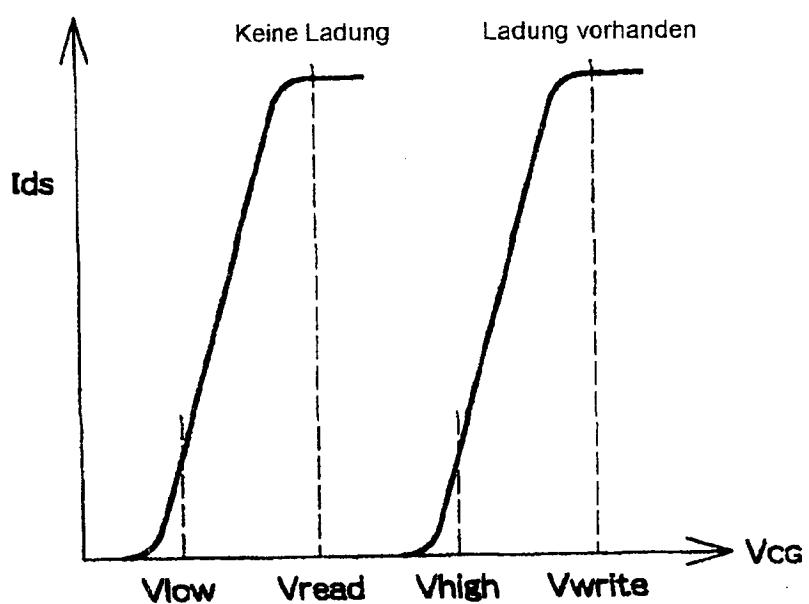

**[0081]** [Fig. 11](#) zeigt das Verhältnis zwischen Spannungen, die am Steuer-Gate **106B** an der rechten Seite (der ausgewählten Zellenseite) der Doppelspeicherzelle **100[i]** anliegen, und Strömen Ids, die zwischen Source und Drain des Transistors T3 fließen, der dem von den anliegenden Spannungen gesteuerten MONOS-Speicherelement **108B** (ausgewählte Zelle) entspricht.

**[0082]** Aus [Fig. 11](#) ist zu entnehmen, daß für den Fall, daß im MONOS-Speicherelement **108B** (ausgewählte Zelle) keine Ladung gespeichert ist, der Strom Ids zu fließen beginnt, wenn die Steuer-Gatespannung VCG eine niedrige Schwellenspannung Vlow übersteigt. Wenn andererseits im MONOS-Speicherelement **108B** (ausgewählte Zelle) Ladung gespeichert ist, beginnt der Strom Ids erst zu fließen, wenn das Steuer-Gatepotential VCG an der ausgewählten Seite eine hohe Schwellenspannung Vhigh übersteigt.

**[0083]** Es sei darauf hingewiesen, daß die Spannung Vread, die am Steuer-Gate **106B** an der ausgewählten Seite anliegt, wenn Daten gelesen werden, im wesentlichen auf eine Spannung gesetzt ist, die zwischen den beiden Schwellenspannungen Vlow und Vhigh liegt.

**[0084]** Folglich fließt Strom Ids, wenn im MONOS-Speicherelement **108B** (ausgewählte Zelle) keine Ladung gespeichert ist, und wenn Ladung im MONOS-Speicherelement **108B** (ausgewählte Zelle) gespeichert ist, fließt der Strom Ids nicht.

**[0085]** Wenn Daten gelesen werden, ist, wie [Fig. 10](#) zeigt, die Bitleitung BL[i] (Störstellenschicht **110[i]**), die mit der Gegenzelle verbunden ist, an einen Leseverstärker angeschlossen, und Potentiale VD [i-1], **[i+1]** und **[i+2]** auf den anderen Bitleitungen BL [i-1], **[i+1]** und **[i+2]** sind auf 0 V gesetzt. Aufgrunddessen fließt der Strom Ids, wenn im MONOS-Speicherelement **108B** (ausgewählte Zelle) keine Ladung gespeichert ist, und aus diesem Grund fließt auf der Gegenseite z. B. ein Strom von 25 µA oder mehr in der Bitleitung BL[i] durch die Transistoren T1 und T2, die sich in eingeschaltetem Zustand befinden. Hingegen fließt kein Strom Ids, wenn Ladung im MONOS-Speicherelement **108B** (ausgewählte Zelle) gespeichert ist. Selbst wenn die Transistoren T1 und T2 sich in eingeschaltetem Zustand befinden, ist also in der Bitleitung BL[i] auf der Gegenseite fließender Strom kleiner als 10 nA. Durch Erfassen des in der Bitleitung BL[i] auf der Gegenseite fließenden Stroms mit Hilfe des Leseverstärkers können also Daten aus dem MONOS-Speicherelement **108B** (ausgewählte Zelle) der Doppelspeicherzelle **100[i]** gelesen werden.

**[0086]** Bei diesem Ausführungsbeispiel sind, wie [Fig. 10](#) zeigt, die Bitleitung BL[i] und **[i+2]** mit dem Bitleitungsauswahltransistor **217A** (N-leitender MOS-Transistor) und die Bitleitungen BL[i-1] und **[i+1]** mit dem Bitleitungsauswahltransistor **217B** verbunden.

**[0087]** Es ist schwer, für die Auswahltransistoren **217A** und **217B**, angesichts ihrer Größe, eine hohe Stromansteuerbarkeit sicherzustellen. Sie haben beispielsweise eine Kanalbreite W = 0,9 µm und eine Kanallänge L = 0,8 µm beim vorliegenden Ausführungsbeispiel.

**[0088]** Da die an den Leseverstärker anzuschließende Bitleitung BL[i] den vorstehend erwähnten Strom ga-

rantieren muß, wird die Gate-Spannung des Bitleitungsauswahltransistors **217A** über einen nicht gezeigten Aufwärtsschaltkreis geliefert, so daß die Bitleitung BL[i] beispielsweise mit einer Spannung von 4,5 V versorgt wird.

**[0089]** Andererseits gelangt die Spannung an der Source-Seite des MONOS-Speicherelements **108A** auf der ausgewählten Seite in die Nähe von 0 V (etwa einige -zig bis einhundert mV). Der Einfluß auf das hintere Gate des Bitleitungsauswahltransistors **217B** ist also gering, und daher wird die Gate-Spannung auf Vdd gesetzt. Dieses Gate muß nicht mit 4,5 V versorgt werden, so daß die Last auf dem oben genannten Aufwärtsschaltkreis (Ladepumpe) verringert werden kann.

**[0090]** Es sei erwähnt, daß die in Tabelle 1 gezeigten Spannungen für die nicht ausgewählten Zellen im ausgewählten Block gesetzt sind.

**[0091]** Als nächstes werden die Spannungen gemäß Tabelle 2 für den Gegenblock (kleiner Block **215**) im Sektor 1 gesetzt, der dem ausgewählten Block im Sektor 0 gegenüberliegt; dessen Zustand in [Fig. 12](#) gezeigt ist. Wie aus [Fig. 12](#) hervorgeht, wird die Spannung jeder der Wortleitungen WL und die Gate-Spannung des Bitleitungsauswahltransistors von den Sektoren 0 und 1 gemeinsam benutzt, so daß sie genauso gesetzt sind wie im ausgewählten Block gemäß [Fig. 10](#). Alle Bitleitungen sind auf 0 V gesetzt.

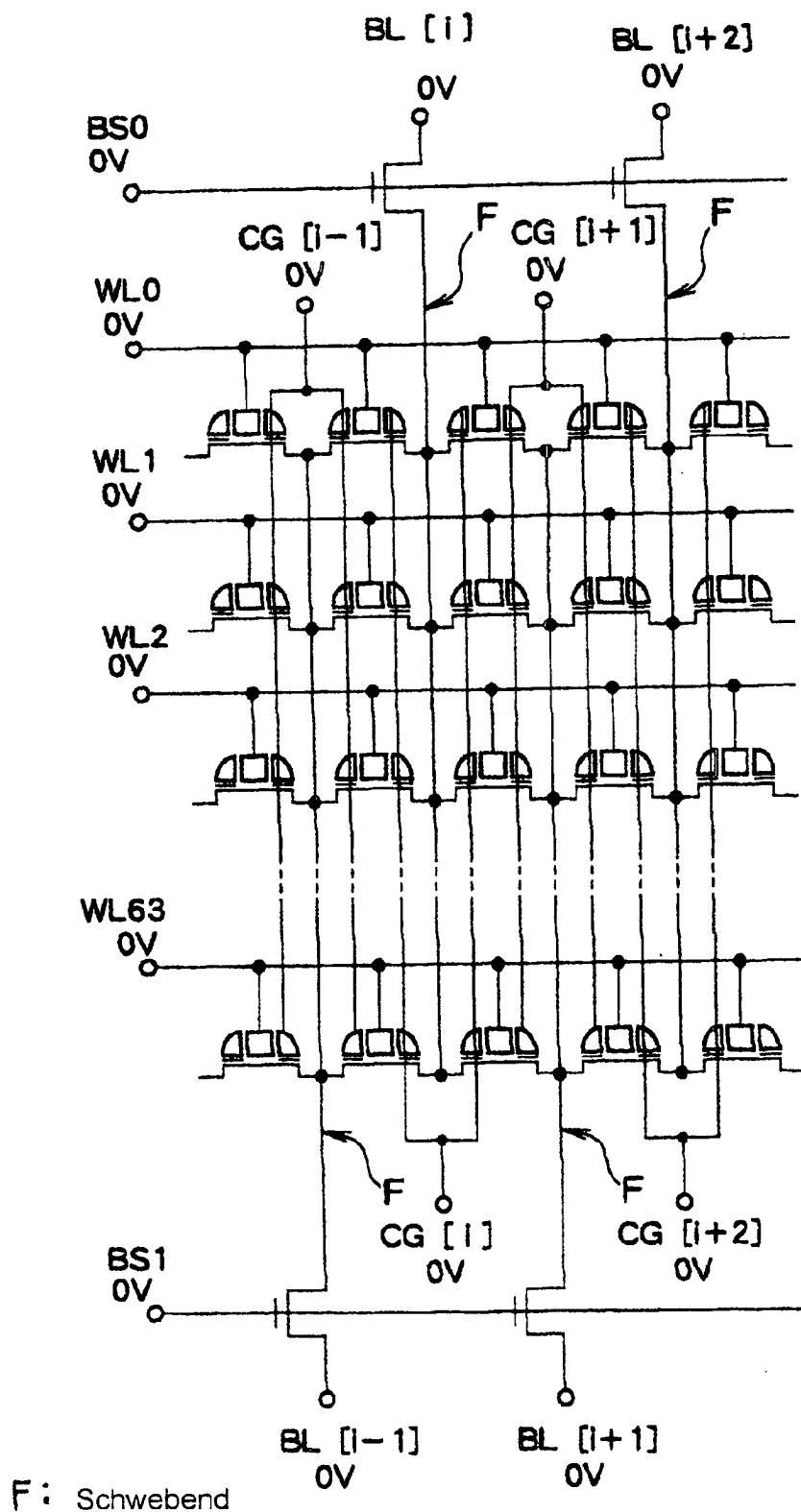

**[0092]** Spannungen entsprechend der vorstehenden Tabelle 2 werden für die nicht ausgewählten Blöcke (kleine Blöcke **215**) gesetzt, die in den Sektoren 0 bis 63 vorhanden sind, mit Ausnahme des ausgewählten Blocks und des Gegenblocks, deren Zustand in [Fig. 13](#) dargestellt ist.

**[0093]** In den nicht ausgewählten Blöcken ist die Gate-Spannung der Bitleitungsauswahltransistoren **217A** und **217B**, der Wortleitungen WL und der Steuer-Gateleitungen CG überall auf 0 V gesetzt. Da die Bitleitungsauswahltransistoren **217A** und **217B** ausgeschaltet sind, befinden sich die Bitleitungen BL in einem Schwebezustand.

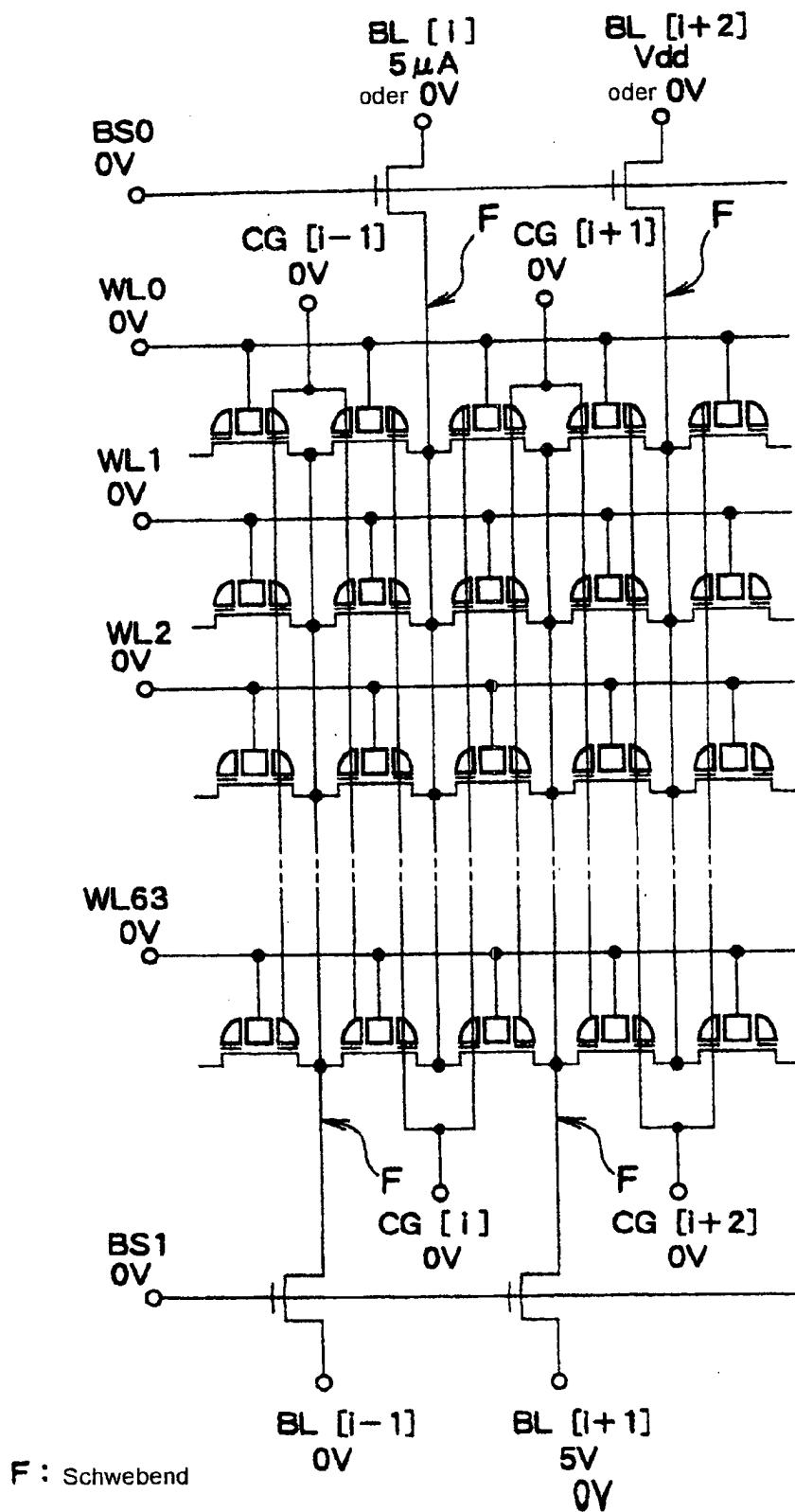

#### Programmieren der Speicherzelle

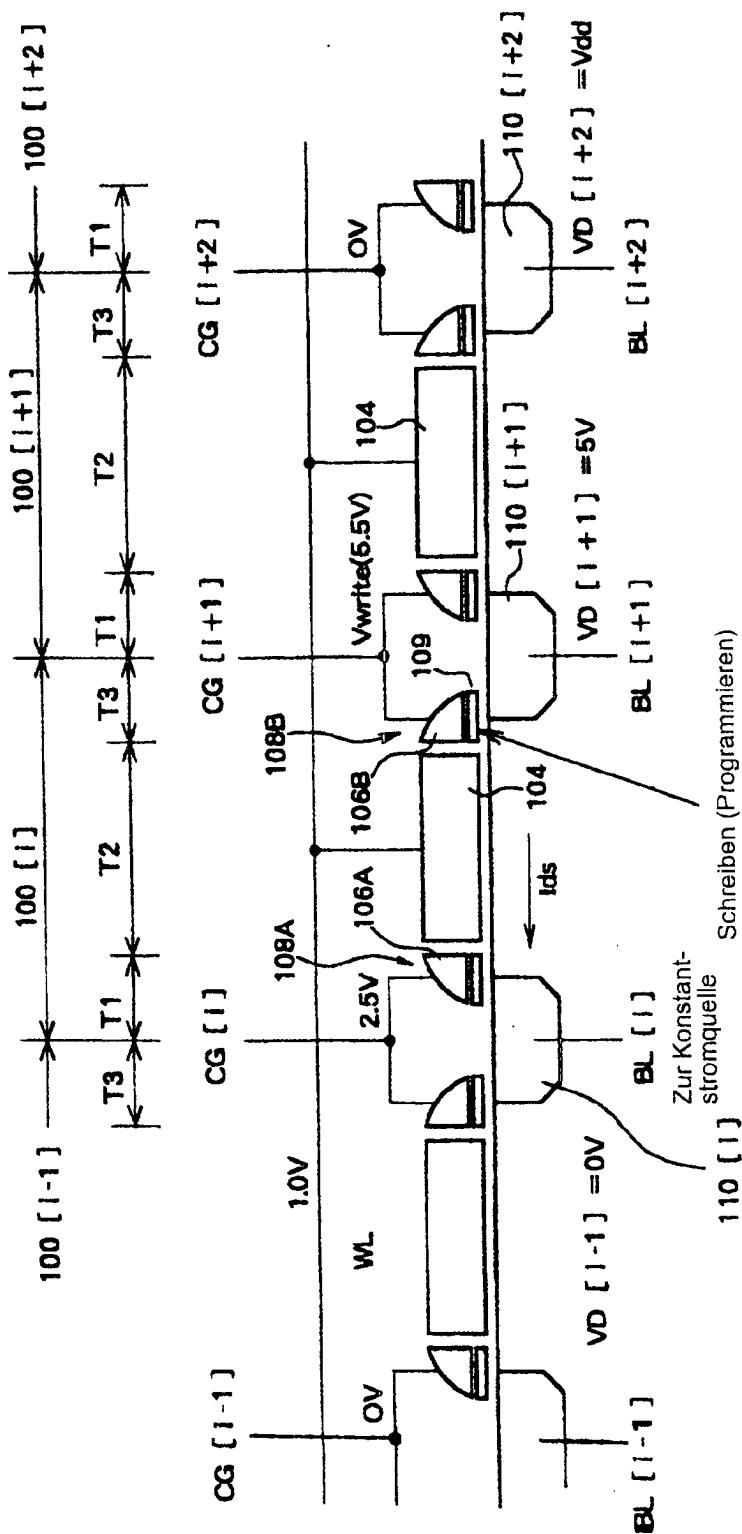

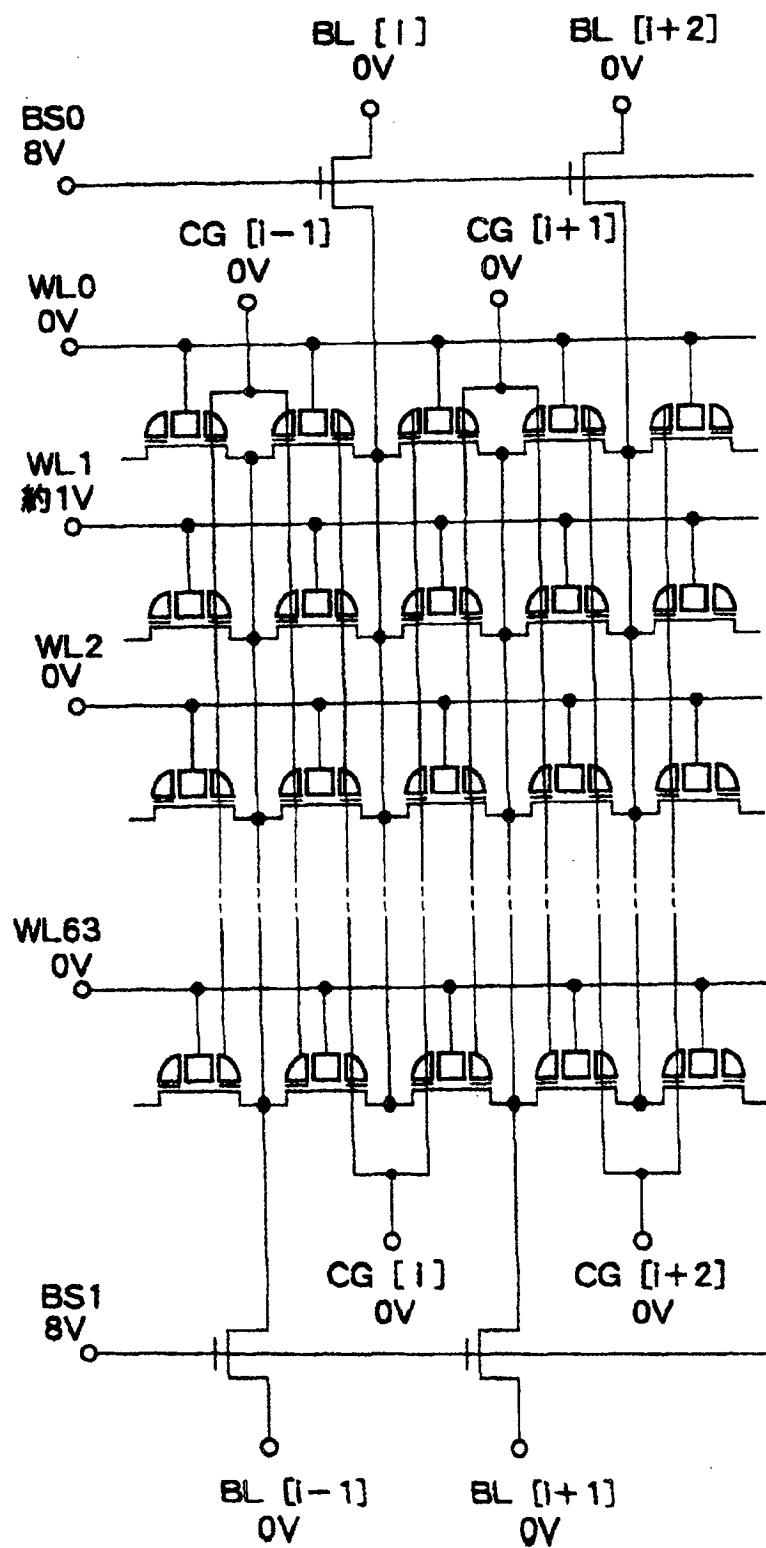

**[0094]** [Fig. 14](#) ist eine Darstellung zum Beschreiben der Datenprogrammierung für das MONOS-Speicherelement **108B** (ausgewählte Zelle) an der rechten Seite des Wort-Gate **104** der Doppelspeicherzelle **100[i]**, das mit der Wortleitung WL1 verbunden ist. [Fig. 15](#) zeigt in dem ausgewählten Block gesetzte Spannungen. Vor der Datenprogrammierung wird ein nachfolgend beschriebener Datenlöschvorgang durchgeführt.

**[0095]** Unter Hinweis auf [Fig. 14](#) handelt es sich bei einem Potential an der Sekundärsteuer-Gateleitung SCG[i] um ein Aufschaltepotential (zum Beispiel 2,5 V), ebenso wie das in [Fig. 9](#) gezeigte, und Potentiale an den Sekundärsteuer-Gateleitungen SCG[i-1] und [i+2] liegen auf 0 V. Es sei angemerkt, daß das "Aufschaltepotential" ein Potential ist, welches zum Einschalten des Transistors T1 entsprechend dem MONOS-Speicherelement **108A** erforderlich ist, damit ein Programmstrom fließt, gleichgültig ob ein Programmieren des MONOS-Speicherelements **108A** (Element an der dem Element auf der ausgewählten Seite gegenüberliegenden Seite) auf der linken Seite der Doppelspeicherzelle **100[i]** anwesend oder abwesend ist. Von der Wortleitung WL1 wird auch ein Potential an jedem der Wort-Gates **104** in [Fig. 15](#) auf eine Programmierwortleitungsauswahlspannung von zum Beispiel etwa 1,0 V gesetzt, was niedriger ist als die Speisespannung Vdd. Ferner wird durch die Sekundärsteuer-Gateleitung SCG [i+1] ein Potential am Steuer-Gate **108B** (ausgewählte Zelle) auf der rechten Seite der Doppelspeicherzelle **100[i+1]** auf eine in [Fig. 4](#) gezeigte Schreibspannung Vwrite (zum Beispiel 5,5 V) gesetzt, bei der es sich um eine Programmiersteuerergatespannung handelt.

**[0096]** Als nächstes wird unter Hinweis auf [Fig. 16](#) das Setzen von Spannungen auf der Bitleitung BL beschrieben. [Fig. 16](#) zeigt schematisch das Innere einer Y-Pfadschaltung **400**, die mit der Bitleitung BL verbunden ist. In der Y-Pfadschaltung **400** ist ein erster Transistor **401** zum Verbinden der Bitleitung BL mit einem Leseverstärker oder einem Bitleitungstreiber und ein zweiter Transistor **402** zum Verbinden der Bitleitung BL mit einem anderen als dem obigen Pfad vorgesehen.

**[0097]** Entgegengesetzte Signale YS0 und /YS0 werden jeweils in das Gate des ersten bzw. zweiten Transistors **401** und **402** eingegeben. Eine Speisespannung Vdd (1,8V) und eine Konstantstromquelle **404**, die einen gleichbleibenden Strom von beispielsweise 5  $\mu$ A liefert, stehen für die Source des zweiten Transistors **402** über einen Schalter **403** zur Verfügung.

**[0098]** Beim Programmieren wird die Spannung VD[i+1] auf der Bitleitung BL[i+1], in [Fig. 14](#) und [Fig. 15](#) ge-

zeigt, über den in [Fig. 16](#) gezeigten Transistor **401** an den Bitleitungstreiber angeschlossen, so daß er auf eine Programmierbitleitungsspannung von zum Beispiel 5 V gesetzt wird. Außerdem wird die Bitleitung BL[i+2] über den Transistor **402** und den Schalter **403**, gezeigt in [Fig. 16](#), auf Vdd gesetzt, Beide Bitleitungen BL[i-1] und [i] sind über den zweiten Transistor **401** und den Schalter **403** mit der Konstantstromquelle **404** verbunden, wie in [Fig. 16](#) gezeigt. Aber die MONOS-Zelle, die mit der Bitleitung BL[i-1] verbunden ist, deren Steuer-Gateleitung CG[i-1] auf 0 V liegt und sich folglich in einem ausgeschalteten Zustand befindet, bei dem kein Strom fließt, wird über die Konstantstromquelle **404** auf 0 V gesetzt.

**[0099]** Infolgedessen werden die Transistoren T1 und T2 der Doppelspeicherzelle **100[i]** eingeschaltet, so daß der Strom Ids zur Bitleitung BL[i] fließt und andererseits heiße Kanalelektronen (channel hot electrons – CHE) in der ONO-Schicht **109** des MONOS-Speicherelements **108B** eingefangen werden. Auf diese Weise wird ein Programmervorgang für das MONOS-Speicherelement **108B** durchgeführt, mit dem Ergebnis, daß Daten "0" oder "1" geschrieben werden.

**[0100]** Gemäß einem alternativen Verfahren kann die Programmierwortleitungsauswahlspannung statt auf etwa 1 V auf etwa 0,77 V gesetzt werden, um die Bitleitung BL[i] auf 0 V zu setzen. Obwohl die Programmierwortleitungsauswahlspannung bei diesem Ausführungsbeispiel auf etwa 1 V angehoben wird, um den Source-Drain-Strom zu erhöhen, wird der Strom, der während des Programmierens in der Bitleitung BL[i] fließen kann, von der Konstantstromquelle **404** begrenzt. Infolgedessen kann die Spannung auf der Bitleitung BL[i] optimal gesetzt werden (in einem Bereich von 0 bis 1 V, und bei diesem Ausführungsbeispiel auf etwa 0,7 V), und der Programmervorgang kann optimal durchgeführt werden.

**[0101]** Als Folge des vorstehend beschriebenen Vorgangs wird eine Spannung von 5,5 V auch an das Steuer-Gate des nichtflüchtigen Speicherelements **108A** auf der rechten Seite der nicht ausgewählten Doppelspeicherzelle **100[i+1]** angelegt. Da das Steuer-Gate CG[i+2] auf der rechten Seite der Doppelspeicherzelle **100[i+1]** in diesem Zeitpunkt auf 0 V liegt, fließt nicht schon an sich Strom zwischen Source und Drain der Doppelspeicherzelle **100[i+1]** (zwischen den Bitleitungen). Da aber eine Spannung von 5 V an den Bitleitungen BL[i+1] anliegt, fließt ein Durchgriffstrom, und es kommt zu einer Schreibstörung, wenn zwischen Source und Drain (zwischen den Bitleitungen) der Doppelspeicherzelle **100[i+1]** ein hohes elektrisches Feld angelegt wird. Dementsprechend wird die Spannung auf der Bitleitung BL[i+2] beispielsweise auf Vdd gesetzt statt auf 0 V, um hierdurch den Potentialunterschied zwischen Source und Drain zu verringern, damit es nicht zu einer Schreibstörung kommt. Auch kann die Spannung auf der Bitleitung BL[i+2] auf einen Wert oberhalb 0 V gesetzt werden, und kann vorzugsweise so gesetzt werden, daß sie der Wortleitungsauswahlspannung während des Programmierens gleicht oder größer ist als diese. Infolgedessen ist das Einschalten des Transistors T2 der Speicherzelle [i+1] schwierig, so daß auch eine Störung verhindert wird.

**[0102]** Da die Bitleitung BL[i+1] mit einer Spannung von 5 V versorgt werden muß, wird eine Spannung von 8 V an das Gate des Bitleitungsauswahltransistors **217B** angelegt. In der Zwischenzeit wird eine Spannung von 8 V auch an das Gate des Bitleitungsauswahltransistors **217B** angelegt. Da die Bitleitung BL[i+2] aus den oben genannten Gründen auf Vdd gesetzt werden muß und aus diesem Grund eine hohe Spannung, höher als Vdd, auch an das Gate des Transistors **217A** angelegt werden muß, wird eine Spannung von 8 V benutzt, die die gleiche ist wie die Gate-Spannung des Transistors **217B**. Es sei darauf hingewiesen, daß eine Gate-Spannung des Bitleitungsauswahltransistors **217A** oberhalb von Vdd + Vth ausreichend sein kann.

**[0103]** Es sei angemerkt, daß Spannungen entsprechend der Tabelle 1 für die nicht ausgewählten Zellen in dem ausgewählten Block gesetzt werden.

**[0104]** Als nächstes werden Spannungen entsprechend der obigen Tabelle 2 für den Gegenblock (kleiner Block **215**) im Sektor 1 gegenüber dem ausgewählten Block im Sektor 0 gesetzt, dessen Zustand in [Fig. 17](#) gezeigt ist. Unter Hinweis auf [Fig. 17](#) wird die Spannung jeder der Wortleitungen WL und die Gate-Spannung des Bitleitungsauswahltransistors von den Sektoren 0 und 1 gemeinsam benutzt, so daß sie die gleichen Einstellungen haben wie in dem in [Fig. 14](#) gezeigten, ausgewählten Block. Alle Bitleitungen sind auf 0 V gesetzt.

**[0105]** Spannungen entsprechend der obigen Tabelle 2 werden für die nicht ausgewählten Blöcke (kleine Blöcke **215**) gesetzt, die in den Sektoren 0 bis 63 vorhanden sind, mit Ausnahme des ausgewählten Blocks und des Gegenblocks; deren Zustand ist in [Fig. 18](#) gezeigt.

**[0106]** In den nicht ausgewählten Blöcken ist die Gate-Spannung der Bitleitungsauswahltransistoren **217A** und **217B**, der Wortleitungen WL und der Steuer-Gateleitungen CG überall auf 0 V gesetzt. Da die Bitleitungsauswahltransistoren **217A** und **217B** ausgeschaltet sind, befinden sich die Bitleitungen BL in einem Schweb-

zustand.

**[0107]** Um das MONOS-Speicherelement **108A** an der linken Seite der Doppelspeicherzelle **100[i]** zu programmieren, können Potentiale an gewissen Abschnitten der Doppelspeicherzellen **100[i-1]**, **[i]** und **[i+1]** so gesetzt werden, wie in [Fig. 19](#) gezeigt.

#### Löschen von Daten in der Speicherzelle

**[0108]** [Fig. 20](#) ist eine schematische Darstellung zum Beschreiben der Löschung von Daten in sämtlichen Speicherzellen im Sektor D auf einmal, und [Fig. 21](#) zeigt den Zustand gesetzter Spannungen für Speicherzellen in einem Teil des Sektors 0.

**[0109]** Unter Hinweis auf [Fig. 20](#) wird das Potential jedes der Wort-Gates **104** mittels der Wortleitung WL auf 0 V gesetzt, und das Potential der Steuer-Gates **106A** und **106B** wird mittels der Sekundärsteuer-Gateleitungen SCG[i-1], **[i]**, **[i+1]** und **[i+2]** auf eine Löschsteuergateleitungsspannung gesetzt, die zum Beispiel etwa -1 bis -3 V beträgt. Ferner wird ein Potential jeder der Bitleitungen BL[i-1], **[i]**, **[i+1]** sowie **[i+2]** durch die Bitleitungsauswahltransistoren **217A** und **217B** und den Bitleitungstreiber auf eine Löschbitleitungsspannung gesetzt, die zum Beispiel 4,5 V bis 5 V beträgt.

**[0110]** Hierdurch werden in der ONO-Schicht **109** jedes der MONOS-Speicherelemente **108a** und **108B** eingefangene Elektronen durch den Tunneleffekt extrahiert und die an den Steuer-Gates anliegende Löschsteuergateleitungsspannung sowie die an den Bitleitungen anliegende Löschbitleitungsspannung gelöscht. Auf diese Weise können Daten in der Vielzahl der Doppelspeicherzellen gleichzeitig gelöscht werden. Es sei noch erwähnt, daß gemäß einem anderen Löschvorgang, der sich von dem oben beschriebenen unterscheidet, in der Band-Band-Durchtunnelung an der Oberfläche der Störstellenschicht, die Bits bestimmt, Heißlöcher ausgebildet werden können, um auf diese Weise die gespeicherten Elektronen zu löschen.

**[0111]** Das Löschen von Daten ist nicht darauf beschränkt, daß Daten in einem Sektor auf einmal gelöscht werden; Daten können auch in Zeiteinteilung gelöscht werden.

**[0112]** Als nächstes werden Spannungen entsprechend der obigen Tabelle 2 für den Gegenblock (kleiner Block **215**) im Sektor 1 gesetzt, der dem ausgewählten Block im Sektor 0 gegenüberliegt; dessen Zustand ist in [Fig. 22](#) gezeigt. Unter Hinweis auf [Fig. 22](#) wird die Spannung jeder der Wortleitungen WL und die Gate-Spannung der Bitleitungsauswahltransistoren von den Sektoren 0 und 1 gemeinsam benutzt, so daß sie die gleichen Einstellungen haben wie in dem ausgewählten Block gemäß [Fig. 18](#). Alle Bitleitungen sind auf 0 V gesetzt. In jeder der Zellen des Gegenblocks liegen sowohl die Steuer-Gateleitungen CG als auch die Bitleitungen BL alle auf 0 V, und infolgedessen tritt keine Störung auf.

**[0113]** Spannungen gemäß der obigen Tabelle 2 werden für die nicht ausgewählten Blöcke (kleine Blöcke **215**) gesetzt, die in den Sektoren 0 bis 63 vorhanden sind, mit Ausnahme des ausgewählten Blocks und des Gegenblocks; der Zustand ist in [Fig. 23](#) gezeigt.

**[0114]** In den nicht ausgewählten Blöcken ist die Gate-Spannung der Bitleitungsauswahltransistoren **217A** und **217B**, der Wortleitungen WL und der Steuer-Gateleitungen CG überall auf 0 V gesetzt. Da die Bitleitungsauswahltransistoren **217A** und **217B** ausgeschaltet sind, befinden sich die Bitleitungen BL in einem Schwebezustand. Da aber die Spannung auf den Bitleitungen BL eine Spannung ist, die sehr nahe bei 0 V liegt und fast 0 V ist, gibt es in den Zellen in den nicht ausgewählten Blöcken keine Störung.

**[0115]** Es sei noch erwähnt, daß die vorliegende Erfindung nicht auf die oben beschriebenen Ausführungsbeispiele beschränkt ist und daß viele Abwandlungen innerhalb des Umfangs des Gegenstandes der vorliegenden Erfindung vorgenommen werden können.

**[0116]** Zum Beispiel ist der Aufbau der nichtflüchtigen Speicherelemente **108A** und **108B** nicht auf die MONOS-Struktur begrenzt. Die vorliegende Erfindung ist auch auf einen nichtflüchtigen Halbleiter-speicherbaustein anwendbar, der mit anderen Arten von Doppelspeicherzellen arbeitet, in denen mit Hilfe eines Wort-Gate **104** und eines ersten und zweiten Steuer-Gates **106A** und **106B** Ladungen unabhängig an zwei Orten eingefangen werden können.

**[0117]** Auch ist bei dem vorstehend beschriebenen Ausführungsbeispiel hinsichtlich der Anzahl der Unterteilungen von Sektorbereichen, der Anzahl der Unterteilungen großer Blöcke und kleiner Blöcke sowie der Anzahl

Speicherzellen in jedem kleinen Speicherblock nur ein Beispiel gegeben, und es können viele Abwandlungen gemacht werden. Es sei erwähnt, daß die Anzahl der Unterteilungen der großen Blöcke deshalb acht ist, weil der Metallverdrahtungsabstand Einschränkungen auferlegt. Wenn der Metallverdrahtungsabstand kleiner gemacht werden kann, läßt sich die Anzahl Unterteilungen noch weiter erhöhen. Wird zum Beispiel eine Unterteilung in sechzehn Blöcke vorgenommen, so wird der Ladekondensator (Gate-Kondensator) jeder der Steuer-Gateleitungen noch weiter verkleinert, und es kann eine höhere Ansteuergeschwindigkeit erzielt werden. Allerdings ist zu erwähnen, daß bei einer Unterteilung in sechzehn Blöcke die Zahl der Hauptsteuer-Gateleitungen zunimmt. Dementsprechend müssen die Leitungen und Zwischenräume schmäler gemacht oder die Fläche vergrößert werden. Außerdem nimmt die Anzahl Steuer-Gatetreiber zu, und dementsprechend wird die Fläche größer.

### Patentansprüche

1. Verfahren zum Programmieren eines nichtflüchtigen Halbleiter-Speicherbausteins, in dem eine Vielzahl Doppelspeicherzellen (**100**) angeordnet sind, die je ein Wort-Gate (**104**) und ein erstes und ein zweites nichtflüchtiges Speicherelement (**108A, 108B**) haben, welche von einem ersten und einem zweiten Steuer-Gate (**106A, 106B**) gesteuert sind, wobei das Verfahren zum Programmieren von Daten für das n-te nichtflüchtige Speicherelement der Doppelspeicherzelle i unter drei benachbarten Doppelspeicherzellen i-1, i und i+1, deren Wort-Gates mit einer Wortleitung (LW) verbunden sind, wobei n = 1 oder 2, folgendes aufweist:

Setzen der Wortleitung (WL) auf eine Programmierwortleitungsauswahlspannung;

Setzen des zweiten Steuer-Gates (**106B**) der Doppelspeicherzelle i+n-2 und des ersten Steuer-Gates (**106A**) der Doppelspeicherzelle i+n-1 auf eine Programmiersteuerungsspannung;

Setzen des zweiten Steuer-Gates (**106B**) der Doppelspeicherzelle i+(n-2)·(-1)n-1 und des ersten Steuer-Gates (**106A**) der Doppelspeicherzelle i+(n-2)·(-1)n auf eine Übersteuerungsspannung;

Setzen einer Bitleitung (BL), die mit dem zweiten nichtflüchtigen Speicherelement (**108B**) der Doppelspeicherzelle i+n-2 und dem ersten nichtflüchtigen Speicherelement (**108A**) der Doppelspeicherzelle i+n-1 gemeinsam verbunden ist, auf eine Programmierbitleitungsspannung; und

Setzen einer Bitleitung (BL), die mit dem zweiten nichtflüchtigen Speicherelement (**108B**) der Doppelspeicherzelle i+(-1)<sup>n</sup> verbunden ist, auf eine höhere Spannung als 0 V,

**dadurch gekennzeichnet**, daß die gemeinschaftlich mit dem zweiten nichtflüchtigen Speicherelement (**108B**) der Doppelspeicherzelle i+(n-2)·(-1)n-1 und dem ersten nichtflüchtigen Speicherelement (**108A**) der Doppelspeicherzellen i+(n-2)·(-1)n verbundene Bitleitung (BL) an eine Konstantstromquelle angeschlossen ist.

2. Verfahren nach Anspruch 1, bei dem, wenn n=2, die mit dem zweiten nichtflüchtigen Speicherelement (**108B**) der Doppelspeicherzelle i+1 verbundene Bitleitung (BL) auf eine Spannung gesetzt wird, die der Programmierwortleitungsauswahlspannung gleich oder größer ist als diese.

3. Verfahren nach Anspruch 1, bei dem, wenn n=1, die mit dem ersten nichtflüchtigen Speicherelement (**108A**) der Doppelspeicherzelle i-1 verbundene Bitleitung auf eine Spannung gesetzt wird, die der Programmierwortleitungsauswahlspannung gleich oder größer ist als diese.

4. Verfahren nach Anspruch 1, bei dem die Programmierwortleitungsauswahlspannung auf eine Spannung gesetzt wird, die hoch genug ist, um zu veranlassen, daß ein Strom, der größer ist als ein von der Konstantstromquelle gelieferter Strom zwischen Source und Drain der Doppelspeicherzelle fließt, die das zu programmierende, nichtflüchtige Speicherelement umfaßt.

5. Verfahren nach einem der Ansprüche 1 bis 4, bei dem jedes der ersten und zweiten nichtflüchtigen Speicherelemente (**108A, 108B**) eine aus einer Oxidschicht (O), einer Nitridschicht (N) und einer Oxidschicht (O) zusammengesetzte ONO-Schicht als Ladungsfallenstelle umfaßt, wobei Daten an der Fallenstelle programmiert werden.

Es folgen 23 Blatt Zeichnungen

**Fig. 1**

Fig. 3

**Fig. 4**

Fig. 5

**Fig. 6**

Fig. 7

**Fig. 8**

Fig. 9

**Fig. 10**

Lesen (Ausgewählter Block)

Fig. 11

**Fig. 12**

Fig. 13

Lesen (Gegenblock)

F: Schwebend

Fig. 14

**Fig. 15**

Programmieren (Ausgewählter Block)

Fig. 16

Zum Leseverstärker, Bitleitungstreiber

**Fig. 17**

Programmieren (Gegenblock)

**Fig. 18**

Programmieren (nicht ausgewählter Block)

**Fig. 19**

Programmieren (Ausgewählter Block)

Fig. 20

**Fig. 21**

Löschen (Ausgewählter Block)

**Fig. 22**

Löschen (Gegenblock)

**Fig. 23**

Löschen (nicht ausgewählter Block)