(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7635153号**

**(P7635153)**

(45)発行日 令和7年2月25日(2025.2.25)

(24)登録日 令和7年2月14日(2025.2.14)

(51)国際特許分類

F I

|         |                 |         |              |

|---------|-----------------|---------|--------------|

| G 0 9 G | 3/36 (2006.01)  | G 0 9 G | 3/36         |

| G 0 9 G | 3/20 (2006.01)  | G 0 9 G | 3/20 6 2 4 B |

| G 0 2 F | 1/1368(2006.01) | G 0 9 G | 3/20 6 2 2 D |

|         |                 | G 0 9 G | 3/20 6 2 1 M |

|         |                 | G 0 9 G | 3/20 6 2 2 C |

請求項の数 15 (全12頁) 最終頁に続く

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2021-566502(P2021-566502) |

| (86)(22)出願日       | 令和3年11月4日(2021.11.4)        |

| (65)公表番号          | 特表2023-550848(P2023-550848) |

| A)                |                             |

| (43)公表日           | 令和5年12月6日(2023.12.6)        |

| (86)国際出願番号        | PCT/CN2021/128761           |

| (87)国際公開番号        | WO2023/070720               |

| (87)国際公開日         | 令和5年5月4日(2023.5.4)          |

| 審査請求日             | 令和5年11月27日(2023.11.27)      |

| (31)優先権主張番号       | 202111263202.1              |

| (32)優先日           | 令和3年10月28日(2021.10.28)      |

| (33)優先権主張国・地域又は機関 | 中国(CN)                      |

|          |                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 515203228<br>ティーシーエル チャイナスター オプト<br>エレクトロニクス テクノロジー カンパ<br>ニー リミテッド<br>T C L C h i n a S t a r O p t o<br>e l e c t r o n i c s T e c h n o<br>l o g y C o . , L t d .<br>中華人民共和国廣東省深 せん 市光明<br>新區塘明大道9-2號518132<br>No. 9 - 2 , T a n g m i n g R d<br>, G u a n g m i n g N e w D i s t<br>r i c t , S h e n z h e n , G u a n<br>g d o n g , C h i n a 5 1 8 1 3 2<br>110002181<br>弁理士法人 I P - F O C U S |

| (74)代理人  | 最終頁に続く                                                                                                                                                                                                                                                                                                                                                                                                     |

(54)【発明の名称】 画素回路及び表示装置

**(57)【特許請求の範囲】****【請求項1】**

複数の画素駆動モジュールを含む画素回路であって、

前記画素駆動モジュールは、

主スイッチ及び主画素電極を含む主画素制御群であって、前記主スイッチは、データ線のデータ信号を前記主画素電極に伝達するように本段走査線の走査信号によって制御されるように構成される主画素制御群と、

次スイッチ及び次画素電極を含む次画素制御群であって、前記次スイッチは、前記データ線のデータ信号を前記次画素電極に伝達するように前記本段走査線の走査信号によって制御されるように構成される次画素制御群と、

前記次画素電極の電位が低くなるように共有走査線の共有走査信号によって制御されるように構成される共有スイッチと、を含み、

前記本段走査線及び前記共有走査線は、互いに絶縁され、前記本段走査線の走査信号は、第1正レベルパルスを有するように構成され、前記共有走査線の共有走査信号は、前記第1正レベルパルスよりも遅い第2正レベルパルスを有するように構成され、前記第1正レベルパルスと前記第2正レベルパルスとの間に間隔時間を有し、

前記本段走査線及び前記共有走査線は、二つの金属材料層にそれぞれ設けられ、二つの前記金属材料層の間に絶縁層が設けられる、

画素回路。

**【請求項2】**

前記主スイッチ、前記次スイッチ及び前記共有スイッチは、それぞれ、制御端、第1端及び第2端を含むトランジスタスイッチであり、前記主スイッチの制御端及び前記次スイッチの制御端は、前記本段走査線に電気的に接続され、前記共有スイッチの制御端は、前記共有走査線に電気的に接続される。

請求項1に記載の画素回路。

**【請求項3】**

前記共有スイッチは、第1端が前記次画素電極及び前記次スイッチの第2端に電気的に接続され、第2端が共通電極に電気的に接続される。

請求項2に記載の画素回路。

**【請求項4】**

前記主画素電極及び前記次画素電極は、それぞれ、液晶コンデンサ及び蓄積コンデンサを含み、前記次画素電極は、液晶コンデンサが前記次スイッチの第2端及び第1共通電極に電気的に接続され、蓄積コンデンサが前記次スイッチの第2端及び第2共通電極に電気的に接続され、前記共有スイッチの第2端は、前記第2共通電極に電気的に接続される、請求項3に記載の画素回路。

**【請求項5】**

前記共有スイッチは、前記次画素電極の電位が低くなるように、オンにされるように構成される。

請求項1に記載の画素回路。

**【請求項6】**

前記画素駆動モジュールは、青色サブ画素、赤色サブ画素、又は青色及び赤色サブ画素用に構成される。

請求項1に記載の画素回路。

**【請求項7】**

複数の画素駆動モジュールを含む画素回路であって、

前記画素駆動モジュールは、

主スイッチ及び主画素電極を含む主画素制御群であって、前記主スイッチは、データ線のデータ信号を前記主画素電極に伝達するように本段走査線の走査信号によって制御されるように構成される主画素制御群と、

次スイッチ及び次画素電極を含む次画素制御群であって、前記次スイッチは、前記データ線のデータ信号を前記次画素電極に伝達するように前記本段走査線の走査信号によって制御されるように構成される次画素制御群と、

前記次画素電極の電位が低くなるように共有走査線の共有走査信号によって制御されるように構成される共有スイッチと、を含み、

前記本段走査線及び前記共有走査線は、二つの金属材料層にそれぞれ設けられ、二つの前記金属材料層の間に絶縁層が設けられる、

画素回路。

**【請求項8】**

前記主スイッチ、前記次スイッチ及び前記共有スイッチは、それぞれ、制御端、第1端及び第2端を含むトランジスタスイッチであり、前記主スイッチの制御端及び前記次スイッチの制御端は、前記本段走査線に電気的に接続され、前記共有スイッチの制御端は、前記共有走査線に電気的に接続される。

請求項7に記載の画素回路。

**【請求項9】**

前記共有スイッチは、第1端が前記次画素電極及び前記次スイッチの第2端に電気的に接続され、第2端が共通電極に電気的に接続される。

請求項8に記載の画素回路。

**【請求項10】**

前記主画素電極及び前記次画素電極は、それぞれ、液晶コンデンサ及び蓄積コンデンサを含み、前記次画素電極は、液晶コンデンサが前記次スイッチの第2端及び第1共通電極

10

20

30

40

50

に電気的に接続され、蓄積コンデンサが前記次スイッチの第2端及び第2共通電極に電気的に接続され、前記共有スイッチの第2端は、前記第2共通電極に電気的に接続される、請求項9に記載の画素回路。

**【請求項11】**

前記本段走査線及び前記共有走査線は、互いに絶縁される、

請求項7に記載の画素回路。

**【請求項12】**

前記共有スイッチは、前記次画素電極の電位が低くなるように、オンにされるように構成される、

請求項7に記載の画素回路。

10

**【請求項13】**

前記本段走査線の走査信号は、第1正レベルパルスを有するように構成され、前記共有走査線の共有走査信号は、前記第1正レベルパルスよりも遅い第2正レベルパルスを有するように構成され、前記第1正レベルパルスと前記第2正レベルパルスとの間に間隔時間を有する、

請求項7に記載の画素回路。

**【請求項14】**

前記画素駆動モジュールは、青色サブ画素、赤色サブ画素、又は青色及び赤色サブ画素用に構成される、

請求項7に記載の画素回路。

20

**【請求項15】**

請求項7～14のいずれか一項に記載の画素回路を含む、

表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、表示技術分野に関し、具体的には、画素回路及び表示装置に関する。

**【背景技術】**

**【0002】**

液晶表示装置において、垂直配列型液晶表示装置の大視野角色ずれ現象を改善するため、例えば、各サブ画素ユニットを主画素電極と次画素電極とに分割するなど、画素ユニットの低色ずれ(*low color shift*, LCS)設計を行うことができる。表示中において、まず主画素電極及び次画素電極に同じ電位を充電し、次に主画素電極と次画素電極の電位が異なるように次画素電極の電位を低くする。

30

**【0003】**

例えば、主画素電極のスイッチ、次画素電極のスイッチ及び共有信号スイッチは、同じ信号線によって制御され、LCS曲線は、下降傾向となり、LCS特徴パラメータが低い場合、視野角が悪くなり、LCS特徴パラメータが高い場合、透過性が悪くなる。この状況を改善するために、例えば、共有信号スイッチの制御方式を変更するなど、他の技術が提案されているが、LCS特性曲線は、調整可能な範囲が限られており、視野角及び透過率要求を同時に満たすことができず、依然として改善する必要がある。

40

**【発明の概要】**

**【0004】**

本発明によれば、従来技術の低色ずれ曲線の調整可能な範囲を改善するための画素回路及び表示装置が提供される。

**【0005】**

上記問題を解決するために、本発明の第1態様によれば、複数の画素駆動モジュールを含む画素回路であって、

前記画素駆動モジュールは、

主スイッチ及び主画素電極を含む主画素制御群であって、前記主スイッチは、データ線

50

のデータ信号を前記主画素電極に伝達するように本段走査線の走査信号によって制御されるように構成される主画素制御群と、

次スイッチ及び次画素電極を含む次画素制御群であって、前記次スイッチは、前記データ線のデータ信号を前記次画素電極に伝達するように前記本段走査線の走査信号によって制御されるように構成される次画素制御群と、

前記次画素電極の電位が低くなるように共有走査線の共有走査信号によって制御されるように構成される共有スイッチと、を含み、

前記本段走査線及び前記共有走査線は、互いに絶縁され、前記本段走査線の走査信号は、第1正レベルパルスを有するように構成され、前記共有走査線の共有走査信号は、前記第1正レベルパルスよりも遅い第2正レベルパルスを有するように構成され、前記第1正レベルパルスと前記第2正レベルパルスとの間に間隔時間是有する画素回路が提供される。

#### 【0006】

本発明の一実施例によれば、前記主スイッチ、前記次スイッチ及び前記共有スイッチは、それぞれ、制御端、第1端及び第2端を含むトランジスタスイッチであり、前記主スイッチの制御端及び前記次スイッチの制御端は、前記本段走査線に電気的に接続され、前記共有スイッチの制御端は、前記共有走査線に電気的に接続される。

#### 【0007】

本発明の一実施例によれば、前記共有スイッチは、第1端が前記次画素電極及び前記次スイッチの第2端に電気的に接続され、第2端が共通電極に電気的に接続される。

#### 【0008】

本発明の一実施例によれば、前記主画素電極及び前記次画素電極は、それぞれ、液晶コンデンサ及び蓄積コンデンサを含み、前記次画素電極は、液晶コンデンサが前記次スイッチの第2端及び第1共通電極に電気的に接続され、蓄積コンデンサが前記次スイッチの第2端及び第2共通電極に電気的に接続され、前記共有スイッチの第2端は、前記第2共通電極に電気的に接続される。

#### 【0009】

本発明の一実施例によれば、前記本段走査線及び前記共有走査線は、二つの金属材料層にそれぞれ設けられ、二つの前記金属材料層の間に絶縁層が設けられる。

#### 【0010】

本発明の一実施例によれば、前記共有スイッチは、前記次画素電極の電位が低くなるように、オンにされるように構成される。

#### 【0011】

本発明の一実施例によれば、前記画素駆動モジュールは、青色サブ画素、赤色サブ画素、又は青色及び赤色サブ画素用に構成される。

#### 【0012】

上記問題を解決するために、本発明の第2態様によれば、複数の画素駆動モジュールを含む画素回路であって、

前記画素駆動モジュールは、

主スイッチ及び主画素電極を含む主画素制御群であって、前記主スイッチは、データ線のデータ信号を前記主画素電極に伝達するように本段走査線の走査信号によって制御されるように構成される主画素制御群と、

次スイッチ及び次画素電極を含む次画素制御群であって、前記次スイッチは、前記データ線のデータ信号を前記次画素電極に伝達するように前記本段走査線の走査信号によって制御されるように構成される次画素制御群と、

前記次画素電極の電位が低くなるように共有走査線の共有走査信号によって制御されるように構成される共有スイッチと、を含む画素回路が提供される。

#### 【0013】

本発明の一実施例によれば、前記主スイッチ、前記次スイッチ及び前記共有スイッチは、それぞれ、制御端、第1端及び第2端を含むトランジスタスイッチであり、前記主スイッチの制御端及び前記次スイッチの制御端は、前記本段走査線に電気的に接続され、前記

10

20

30

40

50

共有スイッチの制御端は、前記共有走査線に電気的に接続される。

**【0014】**

本発明の一実施例によれば、前記共有スイッチは、第1端が前記次画素電極及び前記次スイッチの第2端に電気的に接続され、第2端が共通電極に電気的に接続される。

**【0015】**

本発明の一実施例によれば、前記主画素電極及び前記次画素電極は、それぞれ、液晶コンデンサ及び蓄積コンデンサを含み、前記次画素電極は、液晶コンデンサが前記次スイッチの第2端及び第1共通電極に電気的に接続され、蓄積コンデンサが前記次スイッチの第2端及び第2共通電極に電気的に接続され、前記共有スイッチは、第2端が前記第2共通電極に電気的に接続される。

10

**【0016】**

本発明の一実施例によれば、前記本段走査線及び前記共有走査線は、互いに絶縁される。

**【0017】**

本発明の一実施例によれば、前記本段走査線及び前記共有走査線は、二つの金属材料層にそれぞれ設けられ、二つの前記金属材料層の間に絶縁層が設けられる。

**【0018】**

本発明の一実施例によれば、前記共有スイッチは、前記次画素電極の電位が低くなるように、オンにされるように構成される。

**【0019】**

本発明の一実施例によれば、前記本段走査線の走査信号は、第1正レベルパルスを有するように構成され、前記共有走査線の共有走査信号は、前記第1正レベルパルスよりも遅い第2正レベルパルスを有するように構成され、前記第1正レベルパルスと前記第2正レベルパルスとの間に間隔時間がある。

20

**【0020】**

本発明の一実施例によれば、前記画素駆動モジュールは、青色サブ画素、赤色サブ画素、又は青色及び赤色サブ画素用に構成される。

**【0021】**

上記問題を解決するために、本発明の第3態様によれば、上述したような画素回路を含む表示装置が提供される。

**【発明の効果】**

30

**【0022】**

本発明の画素回路及び表示装置によれば、前記主スイッチがデータ線のデータ信号を前記主画素電極に伝達するように本段走査線の走査信号によって制御されるように構成され、前記次スイッチが前記データ線のデータ信号を前記次画素電極に伝達するように前記本段走査線の走査信号によって制御されるように構成され、前記共有スイッチが前記次画素電極の電位が低くなるように共有走査線の共有走査信号によって制御されるように構成されることにより、前記主画素電極の電位と前記次画素電極の電位とが異なるようになり、LCS曲線の調整可能な範囲を大幅に増加させ、液晶偏向角度の差別化が適切に制御されるように表示装置の低階調視野角及び高階調透過要求を同時に満たすことができ、視野角を改善し、液晶表示装置の大視野角色ずれ現象を改善することができる。

40

**【図面の簡単な説明】**

**【0023】**

本発明の実施例における技術的手段をより明確に説明するために、以下では、実施例の説明において使用する必要がある図面を簡単に説明する。明らかに、以下の説明における図面は、本発明のいくつかの実施例にすぎず、当業者にとって、創造的な労力を払わずにこれらの図面に基づいて他の図面を得ることができる。

**【0024】**

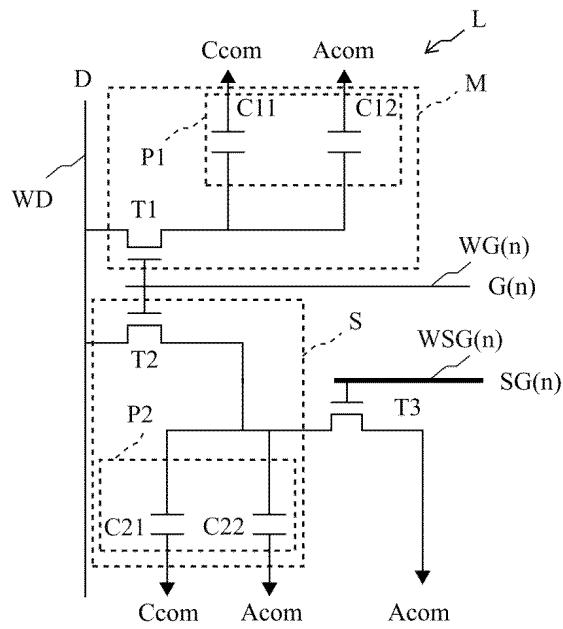

**【図1】**本発明の実施例に係る画素回路の回路を示す概略図である。

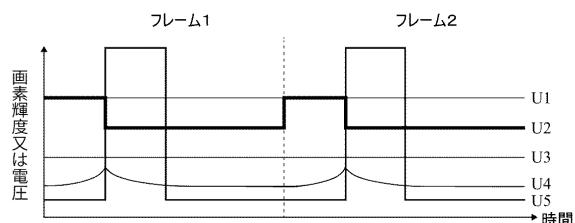

**【図2】**本発明の実施例に係る共有スイッチが主スイッチ及び次スイッチよりも1/4フレーム時間遅延してオンにされる画素輝度変化を示す概略図である。

50

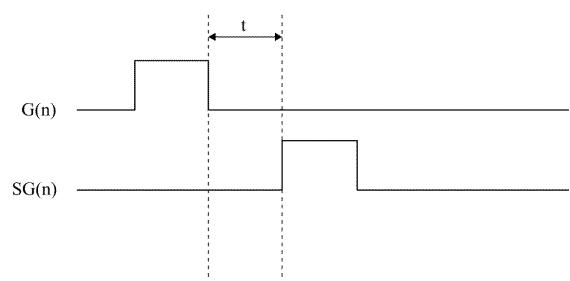

【図3】本発明の実施例に係る走査信号と共有走査信号との間隔時間を示す概略図である。

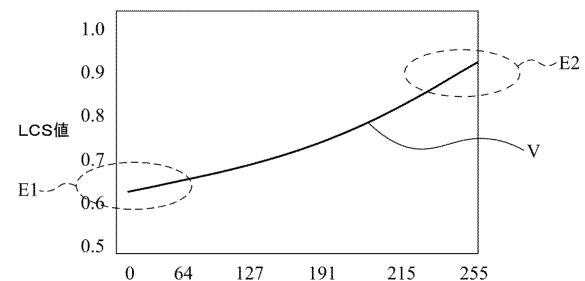

【図4】本発明の実施例に係るLCS曲線を示す概略図である。

【発明を実施するための形態】

【0025】

以下、本発明の実施例における図面を参照しながら本発明の実施例における技術的手段について明確かつ完全に説明する。明らかに、説明される実施例は、本発明の一部の実施例にすぎず、すべての実施例ではない。本発明の実施例に基づいて、当業者は、創造的な労働を払わないことを前提に得られる他のすべての実施例は、いずれも本発明の保護範囲に属する。

【0026】

なお、本明細書の説明において、「中心」、「縦方向」、「横方向」、「長さ」、「幅」、「厚さ」、「上」、「下」、「前」、「後」、「左」、「右」、「垂直」、「水平」、「頂」、「底」、「内」、「外」、「時計回り」、「反時計回り」などの用語で示す方位又は位置関係は、図面に示す方位又は位置関係に基づくものであり、本発明の説明の便宜及び説明の簡略化のためであり、示される装置又は要素が特定の方位を有し、特定の方位で構成及び動作することを示し、又は暗示するものではないため、本発明を限定するものとして理解することができない。

【0027】

なお、本明細書の説明において、「第1」と「第2」という用語は、説明のみを目的としており、相対的な重要性を示し若しくは暗示し、又は示される技術的特徴の数を暗黙的に示すものとして理解することができない。したがって、「第1」と「第2」に限定される特徴は、一つ又はより多くの前記特徴を明示的又は暗黙的に含むことができる。本発明の説明において、「複数」とは、特に限定されない限り二つ又は二つ以上を意味する。

【0028】

本明細書では、本発明の異なる構造を実現するために多くの異なる実施形態又は例を提供する。本発明の開示内容を簡略化するために、以下、特定の実施例の構成要素及び設定について説明する。もちろん、それらは一例にすぎず、本発明を限定するものではない。また、本発明では、異なる例において符号及び/又は参照文字を繰り返すことができるが、このような繰り返しは、簡略化及び明確化の目的で、それ自体が議論される種々の実施形態及び/又は設定の間の関係を示すものではない。また、本明細書に提供される様々な特定のプロセス及び材料の例は、当業者であれば、他のプロセスの適用及び/又は他の材料の使用を認識することができる。

【0029】

液晶表示パネルにおいて、液晶表示装置（例えば垂直配列型など）の大視野角色ずれ現象を改善するために、画素ユニットの低色ずれ（low color shift, LCS）設計を行うことができる。

【0030】

例えば、本発明の第1態様によれば、例えば、マルチドメイン（例えば、4ドメイン又は8ドメイン）アーキテクチャの液晶表示装置などの低色ずれ設計の液晶表示装置に適用可能な画素回路が提供されるが、これらに限定されない。

【0031】

図1に示すように、前記画素回路は、複数のサブ画素（例えば、赤、緑、青のサブ画素）を駆動するための複数の画素駆動モジュールLを含む。例えば、前記画素駆動モジュールLは、主画素制御群M及び次画素制御群Sを含む。例えば、前記主画素制御群M及び次画素制御群S w含む画素駆動モジュールLは、表示効果の最適化に有利となるように、青色サブ画素、赤色サブ画素、又は青色及び赤色サブ画素用に構成されてもよいが、これらに限定されない。

【0032】

図1に示すように、前記主画素制御群Mは、主スイッチT1及び主画素電極P1を含んでもよい。前記主スイッチT1は、データ線WDのデータ信号Dを前記主画素電極P1に

10

20

30

40

50

伝達するように本段走査線 W G ( n ) の走査信号 G ( n ) によって制御されるように構成されてもよく、 n は、正の整数であり、多段走査アーキテクチャにおける特定の一段走査構成を示す。

#### 【 0 0 3 3 】

図 1 に示すように、前記次画素制御群 S は、次スイッチ T 2 及び次画素電極 P 2 を含んでもよい。前記次スイッチ T 2 は、前記データ線 W D のデータ信号 D を前記次画素電極 P 2 に伝達するように前記本段走査線 W G ( n ) の走査信号 G ( n ) によって制御されるように構成されてもよい。

#### 【 0 0 3 4 】

図 1 に示すように、前記画素駆動モジュールは、共有スイッチ T 3 をさらに含んでもよい。前記共有スイッチ T 3 は、前記次画素電極 P 2 の電位が低くなるように、共有走査線 W S G ( n ) の共有走査信号 S G ( n ) によって制御されるように構成されてもよい。

10

#### 【 0 0 3 5 】

以下、前記画素回路の実施例を例示するが、これらに限定されない。

#### 【 0 0 3 6 】

例えば、図 1 に示すように、前記主スイッチ T 1 、次スイッチ T 2 及び共有スイッチ T 3 は、それぞれ、トランジスタスイッチである。前記トランジスタスイッチは、制御端、第 1 端及び第 2 端、例えば、薄膜トランジスタ ( TFT ) のゲート、ドレイン及びソースを含むが、これらに限定されない。前記制御端は、前記第 1 端の信号が前記第 2 端に伝達されるように電気信号により前記第 1 端と前記第 2 端との間のオン状態を制御することができる。

20

#### 【 0 0 3 7 】

図 1 に示すように、前記主スイッチ T 1 は、制御端が前記走査線 W G ( n ) に電気的に接続され、第 1 端が前記データ線 W D に電気的に接続され、第 2 端が前記主画素電極 P 1 に電気的に接続される。例えば、前記主画素電極 P 1 は、液晶コンデンサ C 1 1 及び蓄積コンデンサ C 1 2 を含む。前記液晶コンデンサ C 1 1 は、前記主スイッチ T 1 の第 2 端と第 1 共通電極 C com との間に電気的に接続され、前記蓄積コンデンサ C 1 2 は、前記主スイッチ T 1 の第 2 端と第 2 共通電極 A com との間に電気的に接続される。

#### 【 0 0 3 8 】

図 1 に示すように、前記次スイッチ T 2 は、制御端が前記走査線 W G ( n ) に電気的に接続され、第 1 端が前記データ線 W D に電気的に接続され、第 2 端が前記次画素電極 P 2 に電気的に接続される。例えば、前記次画素電極 P 2 は、液晶コンデンサ C 2 1 及び蓄積コンデンサ C 2 2 を含む。前記液晶コンデンサ C 2 1 は、前記次スイッチ T 2 の第 2 端と前記第 1 共通電極 C com との間に電気的に接続され、前記蓄積コンデンサ C 2 2 は、前記次スイッチ T 2 の第 2 端と前記第 2 共通電極 A com との間に電気的に接続される。

30

#### 【 0 0 3 9 】

図 1 に示すように、前記共有スイッチ T 3 は、制御端が前記共有走査線 W S G ( n ) に電気的に接続され、第 1 端が前記次画素電極 P 2 ( 例えば、前記液晶コンデンサ C 2 1 及び前記蓄積コンデンサ C 2 2 ) 及び前記次スイッチ T 2 の第 2 端に電気的に接続され、第 2 端が前記第 2 共通電極 A com に電気的に接続される。

40

#### 【 0 0 4 0 】

図 1 に示すように、表示中において、前記本段走査線 W G ( n ) の走査信号 G ( n ) により、前記主スイッチ T 1 及び前記次スイッチ T 2 がオン ( ON ) にされるように制御されると同時に、前記共有走査線 W S G ( n ) の共有走査信号 S G ( n ) により、前記共有スイッチ T 3 がオフ ( OFF ) にされるように制御されることで、前記データ線 W D のデータ信号 D を前記主画素電極 P 1 及び前記次画素電極 P 2 に伝達することができるため、前記主画素電極 P 1 ( 例えば、前記液晶コンデンサ C 1 1 及び前記蓄積コンデンサ C 1 2 ) 及び前記次画素電極 P 2 ( 例えば、前記液晶コンデンサ C 2 1 及び前記蓄積コンデンサ C 2 2 ) は、同じ電位 ( 例えば高電位 ) に充電され、次に、前記本段走査線 W G ( n ) の走査信号 G ( n ) により、前記主スイッチ T 1 及び前記次スイッチ T 2 がオフにされるよ

50

うに制御されると同時に、前記共有走査線 W S G ( n ) の共有走査信号 S G ( n ) により、前記共有スイッチ T 3 がオンにされるように制御されることで、前記主画素電極 P 1 と前記次画素電極 P 2 の電位が異なるようになり、例えば、前記次画素電極 P 2 は、前記共有スイッチ T 3 を介して前記第 2 共通電極 A c o m に放電されるため、前記次画素電極 P 2 の電位が前記主画素電極 P 1 の電位よりも低くなる。

#### 【 0 0 4 1 】

任意選択的に、一実施例において、図 1 に示すように、前記主スイッチ T 1 、前記次スイッチ T 2 及び前記共有スイッチ T 3 は、それぞれ、制御端、第 1 端及び第 2 端を含むトランジスタスイッチである。前記主スイッチ T 1 の制御端及び前記次スイッチ T 2 の制御端は、前記走査線 W G ( n ) に電気的に接続され、前記共有スイッチ T 3 の制御端は、前記共有走査線 W S G ( n ) に電気的に接続される。これにより、前記共有スイッチの制御端は、前記主画素電極と前記次画素電極との輝度比が制御されるように前記主スイッチの制御端及び前記次スイッチの制御端とは独立して制御することができる。

#### 【 0 0 4 2 】

任意選択的に、一実施例において、図 1 に示すように、前記共有スイッチ T 3 は、第 1 端が前記次画素電極 P 2 及び前記次スイッチ T 2 の第 2 端に電気的に接続され、第 2 端が共通電極に電気的に接続される。これにより、前記次画素電極は、前記共有スイッチを介して放電されるため、前記次画素電極の電位が前記主画素電極の電位よりも低くなり、視野角の改善に有利となる。

#### 【 0 0 4 3 】

任意選択的に、一実施例において、図 1 に示すように、前記主画素電極 P 1 及び次画素電極 P 2 は、それぞれ液晶コンデンサ（例えば、C 1 1、C 2 1）及び蓄積コンデンサ（例えば、C 1 2、C 2 2）を含む。前記次画素電極 P 2 は、液晶コンデンサ C 2 1 が前記次スイッチ T 2 の第 2 端及び第 1 共通電極 C c o m に電気的に接続され、蓄積コンデンサ C 2 2 が前記次スイッチ T 2 の第 2 端及び第 2 共通電極 A c o m に電気的に接続され、前記共有スイッチ T 3 の第 2 端は、前記第 2 共通電極 A c o m に電気的に接続される。これにより、前記次画素電極は、前記共有スイッチを介して前記第 2 共通電極に放電されるため、前記主画素電極の電位と前記次画素電極の電位とが異なるようになり、液晶の偏向角度の差別化が適切に制御される。

#### 【 0 0 4 4 】

任意選択的に、一実施例において、図 1 に示すように、前記共有スイッチ T 3 は、前記次画素電極 P 2 の電位が低くなるように、オンにされるように構成される。これにより、前記次画素電極の電位が前記主画素電極の電位よりも低くなるため、前記主画素電極の電位と前記次画素電極の電位とが異なるようになり、液晶表示装置の大視野角ずれ現象を改善することができる。

#### 【 0 0 4 5 】

任意選択的に、一実施例において、図 1 に示すように、前記本段走査線 W G ( n ) 及び前記共有走査線 W S G ( n ) は、互いに絶縁される。例えば、前記本段走査線 W G ( n ) 及び前記共有走査線 W S G ( n ) は、二つの金属材料層にそれぞれ設けられ、二つの前記金属材料層の間には、制御信号が互いに干渉しないように絶縁層が設けられる。これにより、前記本段走査線の走査信号及び前記共有走査線の共有走査信号は、互いに独立することができ、前記共有走査信号は、前記走査信号間で時間分割により時間長を調整することができ、前記次画素電極及び前記主画素電極の電位及び輝度比の柔軟な調整に有利となる。

#### 【 0 0 4 6 】

なお、前記次画素電極の電位が高電位及び低電位にある時間長は、低色ずれ ( L C S ) 特徴パラメータ（例えば、次画素電極の輝度と主画素電極の輝度との比）が柔軟に調整できるように調整可能（時間分割）である。

#### 【 0 0 4 7 】

例えば、前記共有スイッチが前記主スイッチ及び前記次スイッチよりも 1 / 4 フレーム ( f r a m e ) 時間遅延してオンにされる画素輝度を例として、図 2 は、共有スイッチが

10

20

30

40

50

主スイッチ及び次スイッチよりも 1 / 4 フレーム時間遅延してオンにされる画素輝度変化を示す概略図である。ここで、縦軸に示される画素輝度又は電圧は、正の相関をなし、横軸に示されるのは、時間である。図 2において、二フレームの時間長を例として、ここで、U 1 は、前記主スイッチがオンにされることにより、前記主画素電極がハイレベル（例えば、14 ボルト）を維持するときに高階調主画素電極の輝度ラインが生成されることを示し、U 2 は、前記次スイッチがオン及びオフにされることにより、前記次画素電極がハイレベルパルスを備えるときに高階調次画素電極の輝度ラインが生成されることを示し、U 3 は、前記主スイッチがオンにされることにより、前記主画素電極がロー・レベル（例えば、0.2 ボルト）を維持するときに低階調主画素電極の輝度ラインが生成されることを示し、U 4 は、前記次スイッチがオン及びオフにされることにより、前記次画素電極の充放電中に低階調次画素電極の輝度ラインが生成されることを示し、U 5 は、前記共有スイッチが前記主スイッチ及び前記次スイッチよりも 1 / 4 フレーム時間遅延してオンにされる電圧ラインを示す。

#### 【0048】

図 2において、ライン U 1 に示すように、前記主画素電極は、高階調時に高輝度を維持し、ライン U 3 に示すように、前記主画素電極は、低階調時に低輝度を維持する。

#### 【0049】

図 2において、ライン U 2 及びライン U 5 に示すように、前記次スイッチがオンにされ（ライン U 2 に示すハイレベル）、かつ、前記共有スイッチがオフにされる（ライン U 5 に示すロー・レベル）とき、前記次画素電極は、高階調時に高輝度（ライン U 2 に示すように）を維持し、前記次スイッチがオフにされ（ライン U 2 に示すロー・レベル）、かつ、前記共有スイッチがオンにされる（ライン U 5 に示すハイレベル）とき、前記次画素電極は、輝度が前記主画素電極の輝度と異なるように、高階調時に低輝度（ライン U 2 に示すように）を維持する。

#### 【0050】

なお、前記共有スイッチがオンにされた後、前記次画素電極の電圧が低下して明暗変化が生じるが、輝度変化周波数は、表示パネルのリフレッシュ周波数と一致し、決してフリック（flicker）画面の輝度変化周波数が表示パネルのリフレッシュ周波数の 2 倍のようなものではないため、前記共有スイッチがオンにされた後の明暗変化は、顕著なフリックを引き起こすことはない。

#### 【0051】

図 2において、ライン U 4 及びライン U 5 に示すように、前記共有スイッチがオンにされた後、別のフレーム（例えば、図 2におけるフレーム 2）において、前記次スイッチがオンにされ（ライン U 2 に示すハイレベル）、かつ、前記共有スイッチがオフにされる（ライン U 5 に示すロー・レベル）とき、低階調における液晶の反応が遅いため、前記次画素電極の低階調時の輝度が徐々に上昇し（ライン U 4 に示す）、前記次画素電極の輝度がまだ前記主画素電極の輝度に達していないときに、前記次スイッチがオフにされ、かつ、前記共有スイッチがオンにされる（ライン U 5 に示すハイレベル）ことにより、前記次画素電極が放電を開始し、前記次画素電極の低階調時の輝度が徐々に低下し（ライン U 4 に示す）、これにより、前記次画素電極の低階調時の輝度がより低くなるため、低階調の L C S 特徴パラメータが高階調の L C S 特徴パラメータよりも低くなり、L C S 特性曲線が上昇傾向となる。

#### 【0052】

図 2において、ライン U 2、ライン U 4 及びライン U 5 に示すように、前記共有スイッチがオンにされた後、前記次画素電極の電圧が低下するため、前記次画素電極の輝度が低下する。L C S 特徴パラメータは、次画素電極の輝度と主画素電極の輝度との比であるため、前記共有スイッチがオンにされる時間を調整することにより、前記次画素電極の輝度を調整することができ、ひいては L C S 特徴パラメータを調整することができる。

#### 【0053】

なお、図 1 に示すように、前記本段走査線 W G (n) 及び前記共有走査線 W S G (n)

は、互いに絶縁され、前記本段走査線WG(n)の走査信号G(n)及び前記共有走査線WSG(n)の共有走査信号SG(n)は、別々に配信されるため、前記共有スイッチT3のオン時間は、個別に制御することができる。

#### 【0054】

例えば、図1及び図3に示すように、前記本段走査線WG(n)の走査信号G(n)のパルスがハイレベルからローレベルに遷移した後、一定の間隔時間tが経過し、前記共有走査線WSG(n)の共有走査信号SG(n)のパルスがローレベルからハイレベルに遷移するため、前記次画素電極P2が高電位を維持するとき、前記間隔時間tが経過した後に前記次画素電極P2を電位が低下するように制御し、前記次画素電極P2の電位が前記主画素電極P1の電位よりも低くなるため、前記主画素電極P1の電位と前記次画素電極P2の電位とが異なるようになり、液晶の偏向角度の差別化が適切に制御されることにより、視野角を改善し、液晶表示装置の大視野角ずれ現象を改善することができる。10

#### 【0055】

任意選択的に、一実施例において、図1及び図3に示すように、前記走査線WG(n)の走査信号G(n)は、第1正レベルパルスを有するように構成され、前記共有走査線WSG(n)の共有走査信号SG(n)は、前記第1正レベルパルスよりも遅い第2正レベルパルスを有するように構成され、前記第1正レベルパルスと前記第2正レベルパルスとの間に間隔時間を有する。これにより、前記間隔時間を調整することにより、前記主画素電極と前記次画素電極との間の電位及び輝度割合を調節することができる。20

#### 【0056】

また、本発明の第2態様によれば、例えば、低色ずれアーキテクチャを備える液晶表示装置など、上述した画素回路を含む表示装置が提供され、その実施の詳細は、上述した実施例を参照することができるが、その説明を省略する。20

#### 【0057】

なお、本発明の上記実施例の画素回路及び表示装置によれば、前記共有スイッチのオン及びオフ時間を個別に制御することにより、サブ画素の表示過程に時間分割効果を有するようになる。図4に示すように、LCS曲線Vが上昇傾向となる調整可能な範囲を大幅に増加させることができ、低階調範囲(範囲E1に示す)におけるLCS特徴パラメータが低いほど、視野角効果がよくなり、高階調範囲(範囲E2に示す)におけるLCS特徴パラメータが高いほど、透過効果がよくなり、表示装置の低階調視野角及び高階調透過要求を同時に満たすことができる。これにより、本発明の上記実施例に係る画素回路及び表示装置によれば、例えば、視野角及び透過率が制限される場合など、従来技術のLCS曲線が下降傾向となることや、調整可能な範囲が限られていることから生じる問題を改善することができる。30

#### 【0058】

本発明の上記実施例に係る画素回路及び表示装置によれば、前記主スイッチがデータ線のデータ信号を前記主画素電極に伝達するように本段走査線の走査信号によって制御されるように構成され、前記次スイッチが前記データ線のデータ信号を前記次画素電極に伝達するように前記本段走査線の走査信号によって制御されるように構成され、前記共有スイッチが前記次画素電極の電位が低くなるように共有走査線の共有走査信号によって制御されるように構成されることにより、前記主画素電極の電位と前記次画素電極の電位とが異なるようになり、LCS曲線の調整可能な範囲を大幅に増加させ、液晶偏向角度の差別化が適切に制御されるように表示装置の低階調視野角及び高階調透過要求を同時に満たすことができ、視野角を改善し、液晶表示装置の大視野角ずれ現象を改善することができる。40

#### 【0059】

以上、本発明の実施例について詳細に説明したが、本明細書では、具体例を適用して本発明の原理及び実施形態を説明した。以上の実施例の説明は、本発明の技術的手段及びそのコア思想の理解を助けるためだけであり、当業者は、依然として前記各実施例に記載された技術的手段を変更したり、その技術的特徴の一部を同等に置き換えたりすることができ、これらの修正又は置換は、本発明の各実施例の技術的手段の範囲から対応する技術的50

手段の本質を逸脱させるものではないことを理解すべきである。

【図面】

【図 1】

図 1

【図 2】

図 2

10

20

【図 3】

図 3

【図 4】

図 4

30

40

50

---

フロントページの続き

(51)国際特許分類

F I

G 0 2 F      1/1368

(72)発明者 嚴 允晟

中華人民共和国広東省深 せん 市光明新区塘明大道9 - 2号518132

(72)発明者 劉 菁

中華人民共和国広東省深 せん 市光明新区塘明大道9 - 2号518132

(72)発明者 張 き

中華人民共和国広東省深 せん 市光明新区塘明大道9 - 2号518132

(72)発明者 曲 凱莉

中華人民共和国広東省深 せん 市光明新区塘明大道9 - 2号518132

(72)発明者 梁 楚尉

中華人民共和国広東省深 せん 市光明新区塘明大道9 - 2号518132

審査官 西島 篤宏

(56)参考文献 国際公開第2016/207982 (WO, A1)

国際公開第2017/033341 (WO, A1)

国際公開第2016/078180 (WO, A1)

米国特許出願公開第2016/0246140 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

G 0 9 G      3 / 3 6

G 0 9 G      3 / 2 0

G 0 2 F      1 / 1 3 6 8