(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7353765号**

**(P7353765)**

(45)発行日 令和5年10月2日(2023.10.2)

(24)登録日 令和5年9月22日(2023.9.22)

(51)国際特許分類

|        |                  |        |        |   |

|--------|------------------|--------|--------|---|

| H 01 L | 27/146 (2006.01) | H 01 L | 27/146 | A |

| G 01 J | 1/02 (2006.01)   | H 01 L | 27/146 | D |

| G 01 J | 1/42 (2006.01)   | G 01 J | 1/02   | Q |

| H 01 L | 31/107 (2006.01) | G 01 J | 1/42   | H |

| H 01 L | 31/10 (2006.01)  | H 01 L | 31/10  | B |

請求項の数 12 (全28頁) 最終頁に続く

(21)出願番号 特願2019-22355(P2019-22355)

(22)出願日 平成31年2月12日(2019.2.12)

(65)公開番号 特開2019-192903(P2019-192903)

A)

(43)公開日 令和1年10月31日(2019.10.31)

審査請求日 令和4年2月2日(2022.2.2)

(31)優先権主張番号 特願2018-82796(P2018-82796)

(32)優先日 平成30年4月24日(2018.4.24)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100094112

弁理士 岡部 譲

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100106183

弁理士 吉澤 弘司

(74)代理人 100136799

弁理士 本田 亜希

(72)発明者 岩田 旬史

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

宮本 博司

最終頁に続く

(54)【発明の名称】 光検出装置、光検出システム及び移動体

**(57)【特許請求の範囲】****【請求項1】**

複数のアバランシェダイオードと、

前記複数のアバランシェダイオードにおけるアバランシェ増倍を抑制するクエンチ素子と、

前記複数のアバランシェダイオードのそれぞれから出力される信号を加算して得られた信号を処理する画素信号処理部と、

前記複数のアバランシェダイオードの各々に対応する複数のスイッチ素子と、

を有し、

1つの前記クエンチ素子が、前記複数のアバランシェダイオードに対して直列に接続されており、

前記複数のアバランシェダイオード及び前記クエンチ素子は、同一の基板に形成されており、

前記クエンチ素子は、前記基板に垂直な方向からの平面視において、前記複数のアバランシェダイオードのうちの2つのアバランシェダイオードの間に配されており、

前記複数のスイッチ素子の各々は、対応するアバランシェダイオードと前記クエンチ素子との間に接続されており、

前記複数のスイッチ素子が互いに異なるタイミングでオン状態になることにより、前記複数のアバランシェダイオードは、互いに異なるタイミングで前記画素信号処理部に信号を出力する

ことを特徴とする光検出装置。

**【請求項 2】**

1つの前記クエンチ素子と、前記1つの前記クエンチ素子に対して直列に接続された2つのアバランシェダイオードと、を含む領域が、前記基板に複数個、配列されていることを特徴とする請求項1に記載の光検出装置。

**【請求項 3】**

複数のアバランシェダイオードと、

前記複数のアバランシェダイオードにおけるアバランシェ増倍を抑制するクエンチ素子と、

前記複数のアバランシェダイオードのそれぞれから出力される信号を加算して得られた信号を処理する画素信号処理部と、

前記複数のアバランシェダイオードの各々に対応する複数のスイッチ素子と、

を有し、

1つの前記クエンチ素子が、前記複数のアバランシェダイオードに対して直列に接続されており、

前記複数のアバランシェダイオード及び前記クエンチ素子は、同一の基板に形成されており、

前記複数のアバランシェダイオードのうちの1つを含む第1の領域と、前記クエンチ素子を含む第2の領域とが、前記基板に複数の行及び複数の列をなす行列状に配列されており、

前記複数のスイッチ素子の各々は、対応するアバランシェダイオードと前記クエンチ素子との間に接続されており、

前記複数のスイッチ素子が互いに異なるタイミングでオン状態になることにより、前記複数のアバランシェダイオードは、互いに異なるタイミングで前記画素信号処理部に信号を出力する

ことを特徴とする光検出装置。

**【請求項 4】**

複数のアバランシェダイオードと、

前記複数のアバランシェダイオードにおけるアバランシェ増倍を抑制するクエンチ素子と、前記複数のアバランシェダイオードのそれぞれから出力される信号を加算して得られた信号を処理する画素信号処理部と、

を有し、

1つの前記クエンチ素子が、前記複数のアバランシェダイオードに対して直列に接続されており、

前記複数のアバランシェダイオード及び前記クエンチ素子は、同一の基板に形成されており、

前記複数のアバランシェダイオードのうちの1つを含む第1の領域と、前記クエンチ素子を含む第2の領域とが、前記基板に複数の行及び複数の列をなす行列状に配列されており、

前記第2の領域は、前記第1の領域に含まれるアバランシェダイオードの面積よりも小さい面積を有するアバランシェダイオードを更に含む

ことを特徴とする光検出装置。

**【請求項 5】**

複数のアバランシェダイオードと、

前記複数のアバランシェダイオードにおけるアバランシェ増倍を抑制するクエンチ素子と、前記複数のアバランシェダイオードのそれぞれから出力される信号を加算して得られた信号を処理する画素信号処理部と、

を有し、

1つの前記クエンチ素子が、前記複数のアバランシェダイオードに対して直列に接続されており、

前記複数のアバランシェダイオード及び前記クエンチ素子は、同一の基板に形成されてお

10

20

30

40

50

10、

前記複数のアバランシェダイオードのうちの1つを含む第1の領域と、前記クエンチ素子を含む第2の領域とが、前記基板に複数の行及び複数の列をなす行列状に配列されており、前記第2の領域は、アバランシェダイオードを含まないことを特徴とする光検出装置。

【請求項6】

複数のアバランシェダイオードと、

前記複数のアバランシェダイオードにおけるアバランシェ増倍を抑制するクエンチ素子と、

前記複数のアバランシェダイオードのそれぞれから出力される信号を加算して得られた信号を処理する画素信号処理部と、

前記複数のアバランシェダイオードの各々に対応する複数のスイッチ素子と、

を有し、

1つの前記クエンチ素子が、前記複数のアバランシェダイオードに対して直列に接続されており、

前記複数のアバランシェダイオードは、第1の基板に形成されており、

前記クエンチ素子は、前記第1の基板とは異なる第2の基板に形成されており、

前記複数のスイッチ素子の各々は、対応するアバランシェダイオードと前記クエンチ素子との間に接続されており、

前記複数のスイッチ素子が互いに異なるタイミングでオン状態になることにより、前記複数のアバランシェダイオードは、互いに異なるタイミングで前記画素信号処理部に信号を出力する

ことを特徴とする光検出装置。

【請求項7】

前記複数のアバランシェダイオードは、互いに並列に接続されている

ことを特徴とする請求項1乃至6のいずれか1項に記載の光検出装置。

【請求項8】

前記クエンチ素子は、前記アバランシェダイオードに供給される電位を変化させることにより前記アバランシェ増倍を抑制する能動クエンチ回路を含む

ことを特徴とする請求項1乃至7のいずれか1項に記載の光検出装置。

【請求項9】

請求項1乃至8のいずれか1項に記載の光検出装置と、

前記光検出装置から出力される信号を処理する信号処理手段と

を有することを特徴とする光検出システム。

【請求項10】

第1波長帯の光を前記第1波長帯と異なる第2波長帯の光に変換する波長変換部と、

前記波長変換部により変換された前記第2波長帯の光が入射されるよう構成された、請求項1乃至8のいずれか1項に記載の複数の光検出装置と、

前記複数の光検出装置により取得された複数の信号に基づく複数の画像の合成処理を行う信号処理手段と、

を有することを特徴とする光検出システム。

【請求項11】

光を照射する発光部と、

前記光を検出するよう構成された、請求項1乃至8のいずれか1項に記載の光検出装置と、

前記光検出装置により検出された前記光に基づく信号を用いて距離算出を行う距離算出手段と、

を有することを特徴とする光検出システム。

【請求項12】

移動体であって、

10

20

30

40

50

請求項 1 乃至 8 のいずれか 1 項に記載の光検出装置と、

前記光検出装置からの信号に基づく視差画像から、対象物までの距離情報を取得する距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と、

を有することを特徴とする移動体。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、光検出装置、光検出システム及び移動体に関する。

【背景技術】

【0002】

従来、アバランシェ（電子なだれ）増倍を利用し、単一光子レベルの微弱光を検出可能な光検出装置が知られている。特許文献 1 には、アバランシェフォトダイオードを含む画素が二次元状にアレイ化された受光部を有する光電変換素子が開示されている。各画素からの出力電流は一括して収集され、フォトンカウンティングが行われる。これにより、特許文献 1 の光電変換素子は、微弱な入射光量の測定を行うことができる。特許文献 1 の光電変換素子においては、1 つのアバランシェフォトダイオードに対して、1 つのクエンチ素子が直列に接続されている。

【先行技術文献】

【特許文献】

【0003】

【文献】特開 2017 - 117835 公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献 1 に記載されているような構造において、一部のクエンチ素子の性能が他のクエンチ素子と大きく異なる場合、出力信号の精度が不十分になることがある。そこで、本発明は、出力信号の精度が向上された光検出装置を提供することを目的とする。

【課題を解決するための手段】

【0005】

本発明の一観点によれば、複数のアバランシェダイオードと、前記複数のアバランシェダイオードにおけるアバランシェ増倍を抑制するクエンチ素子と、前記複数のアバランシェダイオードのそれぞれから出力される信号を加算して得られた信号を処理する画素信号処理部と、前記複数のアバランシェダイオードの各々に対応する複数のスイッチ素子と、を有し、1 つの前記クエンチ素子が、前記複数のアバランシェダイオードに対して直列に接続されており、前記複数のアバランシェダイオード及び前記クエンチ素子は、同一の基板に形成されており、前記クエンチ素子は、前記基板に垂直な方向からの平面視において、前記複数のアバランシェダイオードのうちの 2 つのアバランシェダイオードの間に配されており、前記複数のスイッチ素子の各々は、対応するアバランシェダイオードと前記クエンチ素子との間に接続されており、前記複数のスイッチ素子が互いに異なるタイミングでオン状態になることにより、前記複数のアバランシェダイオードは、互いに異なるタイミングで前記画素信号処理部に信号を出力することを特徴とする光検出装置が提供される。

本発明の他の一観点によれば、複数のアバランシェダイオードと、前記複数のアバランシェダイオードにおけるアバランシェ増倍を抑制するクエンチ素子と、前記複数のアバランシェダイオードのそれぞれから出力される信号を加算して得られた信号を処理する画素信号処理部と、前記複数のアバランシェダイオードの各々に対応する複数のスイッチ素子と、を有し、1 つの前記クエンチ素子が、前記複数のアバランシェダイオードに対して直列に接続されており、前記複数のアバランシェダイオード及び前記クエンチ素子は、同一の基板に形成されており、前記複数のアバランシェダイオードのうちの 1 つを含む第 1 の領域と、前記クエンチ素子を含む第 2 の領域とが、前記基板に複数の行及び複数の列をな

10

20

30

40

50

す行列状に配列されており、前記複数のスイッチ素子の各々は、対応するアバランシェダイオードと前記クエンチ素子との間に接続されており、前記複数のスイッチ素子が互いに異なるタイミングでオン状態になることにより、前記複数のアバランシェダイオードは、互いに異なるタイミングで前記画素信号処理部に信号を出力することを特徴とする光検出装置が提供される。

本発明の他の一観点によれば、複数のアバランシェダイオードと、前記複数のアバランシェダイオードにおけるアバランシェ増倍を抑制するクエンチ素子と、前記複数のアバランシェダイオードのそれぞれから出力される信号を加算して得られた信号を処理する画素信号処理部と、を有し、1つの前記クエンチ素子が、前記複数のアバランシェダイオードに対して直列に接続されており、前記複数のアバランシェダイオード及び前記クエンチ素子は、同一の基板に形成されており、前記複数のアバランシェダイオードのうちの1つを含む第1の領域と、前記クエンチ素子を含む第2の領域とが、前記基板に複数の行及び複数の列をなす行列状に配列されており、前記第2の領域は、前記第1の領域に含まれるアバランシェダイオードの面積よりも小さい面積を有するアバランシェダイオードを更に含むことを特徴とする光検出装置が提供される。

本発明の他の一観点によれば、複数のアバランシェダイオードと、前記複数のアバランシェダイオードにおけるアバランシェ増倍を抑制するクエンチ素子と、前記複数のアバランシェダイオードのそれぞれから出力される信号を加算して得られた信号を処理する画素信号処理部と、を有し、1つの前記クエンチ素子が、前記複数のアバランシェダイオードに対して直列に接続されており、前記複数のアバランシェダイオード及び前記クエンチ素子は、同一の基板に形成されており、前記複数のアバランシェダイオードのうちの1つを含む第1の領域と、前記クエンチ素子を含む第2の領域とが、前記基板に複数の行及び複数の列をなす行列状に配列されており、前記第2の領域は、アバランシェダイオードを含まないことを特徴とする光検出装置が提供される。

本発明の他の一観点によれば、複数のアバランシェダイオードと、前記複数のアバランシェダイオードにおけるアバランシェ増倍を抑制するクエンチ素子と、前記複数のアバランシェダイオードのそれぞれから出力される信号を加算して得られた信号を処理する画素信号処理部と、前記複数のアバランシェダイオードの各々に対応する複数のスイッチ素子と、を有し、1つの前記クエンチ素子が、前記複数のアバランシェダイオードに対して直列に接続されており、前記複数のアバランシェダイオードは、第1の基板に形成されており、前記クエンチ素子は、前記第1の基板とは異なる第2の基板に形成されており、前記複数のスイッチ素子の各々は、対応するアバランシェダイオードと前記クエンチ素子との間に接続されており、前記複数のスイッチ素子が互いに異なるタイミングでオン状態になることにより、前記複数のアバランシェダイオードは、互いに異なるタイミングで前記画素信号処理部に信号を出力することを特徴とする光検出装置が提供される。

#### 【発明の効果】

#### 【0006】

出力信号の精度が向上された光検出装置を提供することができる。

#### 【図面の簡単な説明】

#### 【0007】

【図1】第1実施形態に係る光検出装置の概略構成を示すブロック図である。

【図2】第1実施形態に係る画素の構成例を示す回路図である。

【図3】第1実施形態に係るクエンチ素子の構成例を説明する回路図である。

【図4】第1実施形態に係る光電変換素子の構成例を示す図である。

【図5】第1実施形態の比較例に係る光電変換素子の構成例を示す図である。

【図6】第1実施形態の比較例における各ノードの電位を示すグラフである。

【図7】第1実施形態の比較例における各ノードの電位を示すグラフである。

【図8】第1実施形態における各ノードの電位を示すグラフである。

【図9】第2実施形態に係る画素の構成例を示す模式図である。

【図10】第3実施形態に係る画素の構成例を示す模式図である。

10

20

30

40

50

- 【図11】第4実施形態に係る画素の構成例を示す模式図である。

- 【図12】第5実施形態に係る画素の構成例を示す模式図である。

- 【図13】第6実施形態に係る光電変換部の概略断面図である。

- 【図14】第6実施形態に係る光電変換部のポテンシャル図である。

- 【図15】第6実施形態に係る光電変換素子の構成例を示す図である。

- 【図16】第6実施形態に係る光電変換素子の駆動方法を示すタイミングチャートである。

- 【図17】第7実施形態に係る光検出システムのブロック図である。

- 【図18】第8実施形態に係る光検出システムのブロック図である。

- 【図19】第8実施形態に係る光検出システム及び移動体の構成例を示す図である。

**【発明を実施するための形態】**

**【0008】**

以下に、本発明の好ましい実施形態を、添付の図面を参照しつつ説明する。複数の図面にわたって対応する要素には共通の符号を付し、その説明を省略又は簡略化することがある。

**【0009】**

**[第1実施形態]**

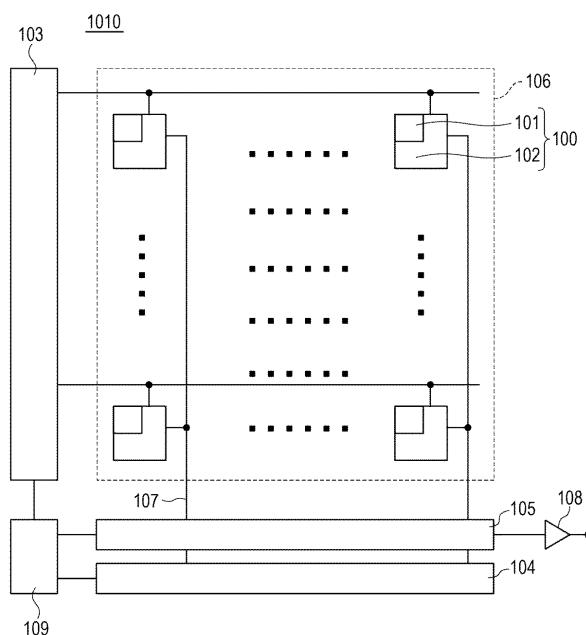

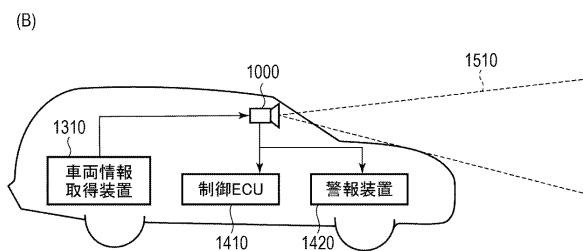

第1実施形態に係る光検出装置について、図1乃至図8を参照しつつ説明する。図1は、本実施形態に係る光検出装置1010の概略構成を示すブロック図である。光検出装置1010は、垂直走査回路部103、水平走査回路部104、列回路105、画素部106、信号線107、出力回路108及び制御パルス生成部109を有している。

**【0010】**

画素部106は、行列状に配された複数の画素100を有している。画素100は、光電変換素子101及び画素信号処理部102を含む。光電変換素子101は入射された光を光電変換して電気信号に変換する。画素信号処理部102は、変換された電気信号を列回路105に出力する。

**【0011】**

なお、本明細書において、「光」とはあらゆる波長の電磁波を含み得る。すなわち、「光」は、可視光に限定されるものではなく、赤外線、紫外線、X線、ガンマ線等の不可視光を含み得る。

**【0012】**

制御パルス生成部109は、垂直走査回路部103、水平走査回路部104及び列回路105を駆動する制御パルスを生成し、これらの各部に供給する。これにより、制御パルス生成部109は、各部の駆動タイミング等の制御を行う。

**【0013】**

垂直走査回路部103は、制御パルス生成部109から供給された制御パルスに基づいて、複数の画素100の各々に制御パルスを供給する。図1に示されているように、垂直走査回路部103は、画素部106の行ごとに設けられている駆動線を介して各画素100に対して行ごとに制御パルスを供給する。垂直走査回路部103にはシフトレジスタ、アドレスデコーダ等の論理回路が用いられ得る。

**【0014】**

画素部106の列ごとに設けられている信号線107は、垂直走査回路部103により選択された行の画素100から出力された信号を電位信号として画素100の後段の列回路105に伝送する。列回路105は、信号線107を介して入力された各画素100の信号に対して所定の処理を行う。所定の処理とは、例えば、入力された信号のノイズ除去、増幅、出力形式の変換等の処理である。これらの機能を実現するため、列回路105は、パラレル・シリアル変換回路等を有し得る。

**【0015】**

水平走査回路部104は、制御パルス生成部109から供給された制御パルスに基づいて、所定の処理が行われた信号を出力回路108へ順次出力するための制御パルスを列回路105に供給する。出力回路108は、バッファアンプ、差動増幅器等を含み、列回路

10

20

30

40

50

105から出力された信号を光検出装置1010の外部の記録部又は信号処理部に出力する。

#### 【0016】

図1において、画素部106内における画素100の配列は一次元状であってもよく、画素100が1つのみであってもよい。画素部106内における画素100がいくつかのブロックに分割されている場合には、垂直走査回路部103、水平走査回路部104及び列回路105は、各ブロックに対応して複数個配置されていてもよい。また、水平走査回路部104及び列回路105は、列ごとに配置されていてもよい。

#### 【0017】

画素信号処理部102が、すべての画素100に1つずつ設けられていることは必須ではない。例えば、複数の画素100によって1つの画素信号処理部102が共有されてもよい。この場合、画素信号処理部102は、各光電変換素子101から出力された信号を順次処理することにより、各画素に対して信号処理の機能を提供する。

10

#### 【0018】

また、画素信号処理部102は、光電変換素子101が設けられている半導体基板とは異なる半導体基板に設けられていてもよい。この場合、光電変換素子101の受光可能な面積の割合（開口率）を向上させることにより、感度を向上させることができる。この場合、光電変換素子101と画素信号処理部102とは、画素100ごとに設けられた接続配線を介して電気的に接続される。更に、垂直走査回路部103、水平走査回路部104、列回路105及び信号線107も画素信号処理部102と同様に、光電変換素子101が設けられている半導体基板とは異なる半導体基板に設けられていてもよい。

20

#### 【0019】

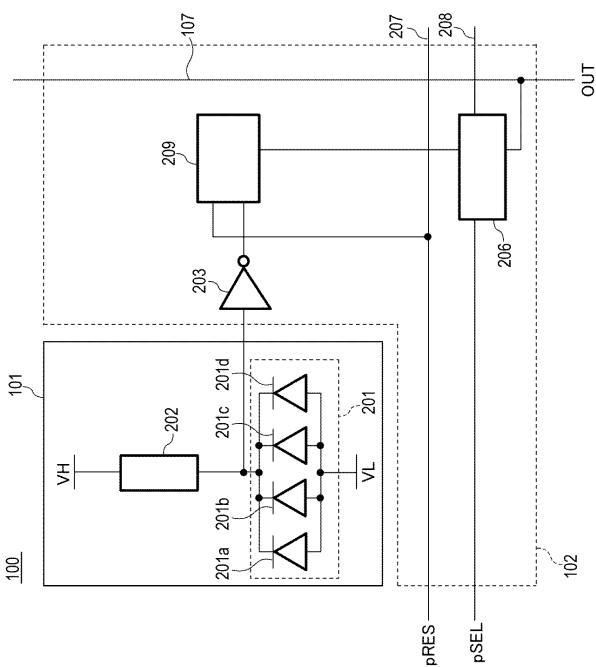

図2は、本実施形態に係る画素100の構成例を示す回路図である。画素100は光電変換素子101及び画素信号処理部102を有する。光電変換素子101は、4個の光電変換部201a、201b、201c、201dとクエンチ素子202とを有する。4個の光電変換部201a、201b、201c、201dは、互いに並列に接続されている。なお、1つの画素100に含まれる光電変換部の個数は4個に限定されるものではなく、複数であればよい。また、以下の説明において、4個の光電変換部201a、201b、201c、201dをまとめて光電変換部201と呼称することもある。

30

#### 【0020】

光電変換部201a～201dは、光電変換により入射光に応じた電荷対を生成する。光電変換部201a～201dには、アバランシェダイオードが用いられる。光電変換部201a～201dのアノードには電位VLが供給される。光電変換部201a～201dのカソードはクエンチ素子202の一端に接続されている。クエンチ素子202の他端には、電位VLよりも高い電位VHが供給される。

#### 【0021】

ここで、光電変換部201a～201dのアノードとカソードには、光電変換部201a～201dに生じた電荷がアバランシェ増倍を起こしうるような逆バイアスの電位が供給される。このような逆バイアスの電位差を供給した状態で、入射光によって生じた電荷がアバランシェ増倍領域を通過すると、アバランシェ電流が発生する。

40

#### 【0022】

なお、逆バイアスの電位差が供給される場合において、アノードとカソードとの間の電位差がアバランシェダイオードの降伏電圧より大きいときには、アバランシェダイオードはガイガーモードで動作する。ガイガーモードにおいて単一光子レベルの微弱信号を高速検出するフォトダイオードはSPADと呼ばれる。

#### 【0023】

また、光電変換部201a～201dのアノードとカソードとの間の電位差が、光電変換部201a～201dに生じた電荷がアバランシェ増倍を起こす電位差以上かつ降伏電圧以下である場合には、アバランシェダイオードは線形モードで動作する。線形モードにおいて光検出を行うアバランシェダイオードはアバランシェフォトダイオード(APD)

50

と呼ばれる。本実施形態においては、光電変換部 201a～201d は、SPAD と APD のどちらのアバランシェダイオードとして動作してもよい。

#### 【0024】

クエンチ素子 202 は、光電変換部 201a～201d で生じたアバランシェ電流の変化を電圧信号に置き換える機能を有する。更に、クエンチ素子 202 は、アバランシェ増倍による信号增幅時に負荷回路（クエンチ回路）として機能し、光電変換部 201a～201d に供給する電圧を抑制することで、アバランシェ増倍を抑制する機能を有する（クエンチ動作）。クエンチ素子 202 を構成する回路素子の具体例としては、抵抗素子又は能動クエンチ回路が挙げられる。能動クエンチ回路は、アバランシェ電流の増加を検出してフィードバック制御を行うことによりアバランシェ増倍を能動的に抑制する。

10

#### 【0025】

画素信号処理部 102 は、波形整形部 203、選択回路 206 及びカウンタ回路 209 を有する。波形整形部 203 は、光電変換素子 101 から単一光子レベルの信号電圧が入力されたときに、電圧変化を整形して、パルス信号を出力する。波形整形部 203 を構成する回路素子の具体例としては、インバータ回路が挙げられる。図 2 には、波形整形部 203 として、1 つのインバータ回路が設けられている回路構成が示されているが、波形整形効果があればその他の回路を用いてもよい。例えば、波形整形部 203 は、複数のインバータ回路を直列接続した回路であってもよい。

#### 【0026】

カウンタ回路 209 は、波形整形部 203 から出力されたパルス信号のパルスの個数をカウントする。カウンタ回路 209 は、例えば、N-bit カウンタ（N：正の整数）であり得る。この場合、カウンタ回路 209 はパルスの個数を最大で約 2 の N 乗個までカウントすることが可能である。カウント数は、検出信号としてカウンタ回路 209 に保持される。また、カウンタ回路 209 には、図 1 に示されている垂直走査回路部 103 から駆動線 207 を介して制御パルス pRES が供給され得る。制御パルス pRES がカウンタ回路 209 に供給されると、保持されているカウント数がリセットされる。

20

#### 【0027】

選択回路 206 は、カウンタ回路 209 と信号線 107 との間の電気的な接続・非接続を切り替える。選択回路 206 には、図 1 に示されている垂直走査回路部 103 から駆動線 208 を介して制御パルス pSEL が供給される。制御パルス pSEL が選択回路 206 に供給されると、制御パルス pSEL のレベルに応じてカウンタ回路 209 と信号線 107 との間の電気的な接続・非接続が切り替わる。選択回路 206 には、例えば、トランジスタ、画素 100 の外部に信号を出力するためのバッファ回路等が含まれ得る。カウンタ回路 209 と信号線 107 との間が電気的に接続されると、カウンタ回路 209 に保持されている検出信号のカウント値を示すデジタル信号が信号線 107 に伝達される。

30

#### 【0028】

なお、選択回路 206 に代えて、クエンチ素子 202 と光電変換部 201a～201d との間、光電変換素子 101 と画素信号処理部 102 との間等のノードにトランジスタ等のスイッチが設けられていてもよい。この場合も、スイッチの接続・非接続を切り替えることにより、選択回路 206 と同様の機能が実現され得る。同様に、クエンチ素子 202 又は光電変換素子 101 に供給される電位の供給の有無をトランジスタ等のスイッチを用いて切り替えることによっても、選択回路 206 と同様の機能が実現され得る。

40

#### 【0029】

画素部 106 の各画素 100 は、ローリングシャッタ動作又はグローバル電子シャッタ動作により駆動され得る。各画素 100 から取得された信号は、画素部 106 への入射光に基づく画像の生成に用いられ得る。

#### 【0030】

ローリングシャッタ動作とは、カウンタ回路 209 におけるカウント値のリセットとカウンタ回路 209 からの信号の出力とを行ごとに異なるタイミングで順次行う動作である。グローバル電子シャッタ動作とは、すべての行のカウンタ回路 209 におけるカウント

50

のリセットを同時に行い、その後、カウンタ回路 209 に保持された信号を行ごとに順次出力する動作である。

#### 【0031】

なお、グローバル電子シャッタ動作を行う場合には、パルスのカウントを行う時間を各行で同一にするため、カウンタ回路 209 のカウントを実行するか否かを切り替える手段を更に追加することが好ましい。カウントを実行するか否かを切り替える手段は、例えば、トランジスタ等のスイッチであり得る。

#### 【0032】

また、カウンタ回路 209 に代えて時間・デジタル変換回路 (Time to Digital Converter: 以下、TDC と呼称する) 及びメモリが設けられていてもよい。この場合、光検出装置 1010 は、パルスを検出したタイミングを取得することができる。

10

#### 【0033】

この変形例において、波形整形部 203 から出力されたパルス信号の発生タイミングは、TDC によってデジタル信号に変換される。TDC には、パルス信号のタイミングの測定に用いる参照信号として、垂直走査回路部 103 から駆動線を介して、制御パルス pREF が供給される。TDC は、制御パルス pREF を時刻の基準として、波形整形部 203 からのパルスの入力時刻に相当するデジタル信号を取得する。

#### 【0034】

TDC の回路には、例えば、バッファ回路を直列接続した Delay Line を用いて遅延回路を形成する Delay Line 方式、Delay Line をループ状に繋いだ回路を用いる Looped TDC 方式等が用いられ得る。TDC の回路には、その他の方式を用いてもよいが、十分な時間分解能を確保するため、光電変換部 201a ~ 201d の時間分解能と同等以上の時間分解能を達成できる方式であることが好ましい。

20

#### 【0035】

TDC により取得されたデジタル信号は、1つ又は複数のメモリに保持される。メモリの個数が複数である場合には、選択回路 206 に複数の制御パルス pSEL を供給することにより、複数のメモリのいずれかから信号線 107 に選択的に信号を出力させることが可能である。

#### 【0036】

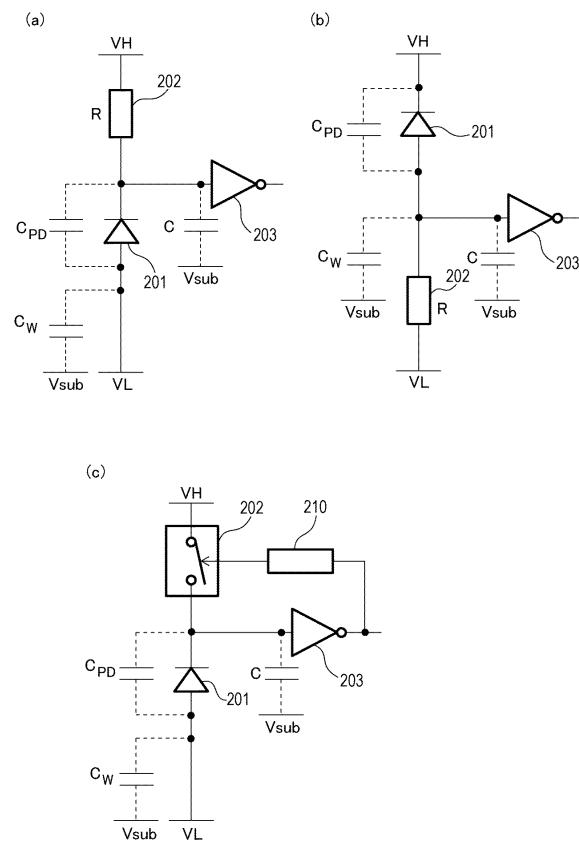

図 3 (a)、図 3 (b) 及び図 3 (c) は、クエンチ素子 202 のいくつかの構成例を説明する回路図である。図 3 (a) は、光電変換部 201 のカソード側にクエンチ素子 202 として抵抗値 R を有する抵抗素子が配される構成例を示す回路図である。光電変換部 201、クエンチ素子 202 及び波形整形部 203 の接続関係は図 2 と同様であるため説明を省略する。また、図 3 (a) には、光電変換部 201 の PN 接合容量 C<sub>PD</sub>、光電変換部 201 のウエル容量 C<sub>w</sub> 及び配線及び拡散層の寄生容量 C が図示されている。図 3 (a) に示されている V<sub>sub</sub>b は基板電位を示している。

30

#### 【0037】

光電変換部 201 の PN 接合容量 C<sub>PD</sub> は、アバランシェ増倍を生じさせるために強電界が誘起される検出領域の容量である。そのため、PN 接合容量 C<sub>PD</sub> は、検出領域の面積に比例する。

40

#### 【0038】

図 3 (a) の構成において、アバランシェ電流により波形整形部 203 の入力電位が変化してから、クエンチ素子 202 による電圧降下によって光電変換部 201 のバイアスが初期状態に復帰するまでには一定の時間が必要である。光電変換素子 101 が一度電荷を検出してから、次に電荷を検出することが可能な状態に戻るまでの時間は、デッドタイム (Dead time) と呼ばれる。このデッドタイムが短いほど、単位時間にカウントできる電荷の個数が増加し、光検出装置 1010 のダイナミックレンジが大きくなる。

#### 【0039】

図 3 (a) の構成例における光電変換素子 101 のデッドタイム  $t_d$  は、以下の式 (1)

50

)により求められる。

【数1】

$$\tau_d = R(C_{pd} + C) \quad (1)$$

【0040】

図3(b)は、光電変換部201のアノード側にクエンチ素子202として抵抗値Rを有する抵抗素子が配される構成例を示す回路図である。本例においては、光電変換部201のカソードには電位VHが供給される。光電変換部201のアノードはクエンチ素子202の一端に接続されている。クエンチ素子202の他端には、電位VLよりも低い電位VLが供給される。

10

【0041】

図3(b)の構成例における光電変換素子101のデッドタイム $\tau_d$ は、以下の式(2)により求められる。

【数2】

$$\tau_d = R(C_{pd} + C_w + C) \quad (2)$$

【0042】

図3(c)は、光電変換部201のカソード側にクエンチ素子202としてスイッチが配される構成例を示す回路図である。クエンチ素子202は、クエンチ素子制御部210によりオン状態又はオフ状態に制御されるように構成されている。クエンチ素子制御部210は、波形整形部203から出力されたパルスを遅延させて出力する。これにより、クエンチ素子制御部210は、アバランシェ増倍が発生した直後にクエンチ素子202をオフ状態に制御するように構成されている。本構成例によれば、クエンチ動作が能動的に行われることにより、クエンチ素子202に受動素子を用いた場合と比べてデッドタイムを短縮することができる。

20

【0043】

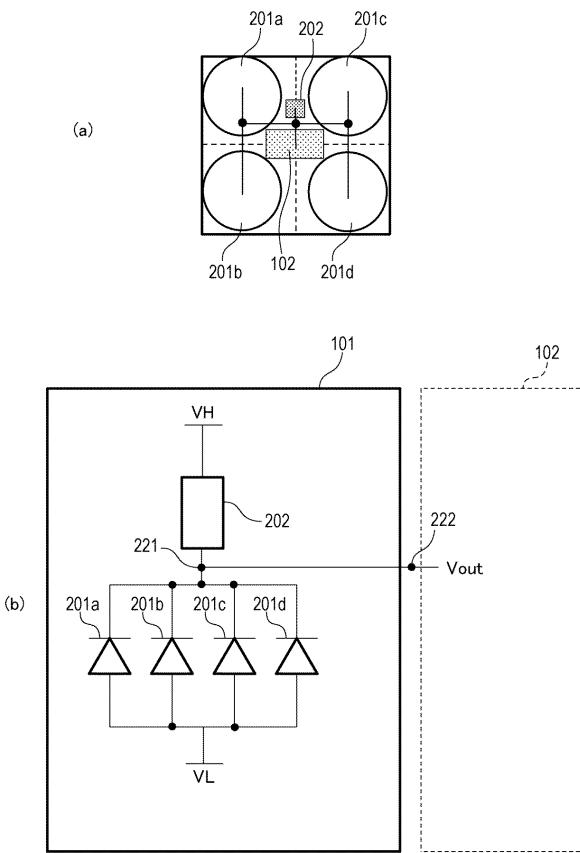

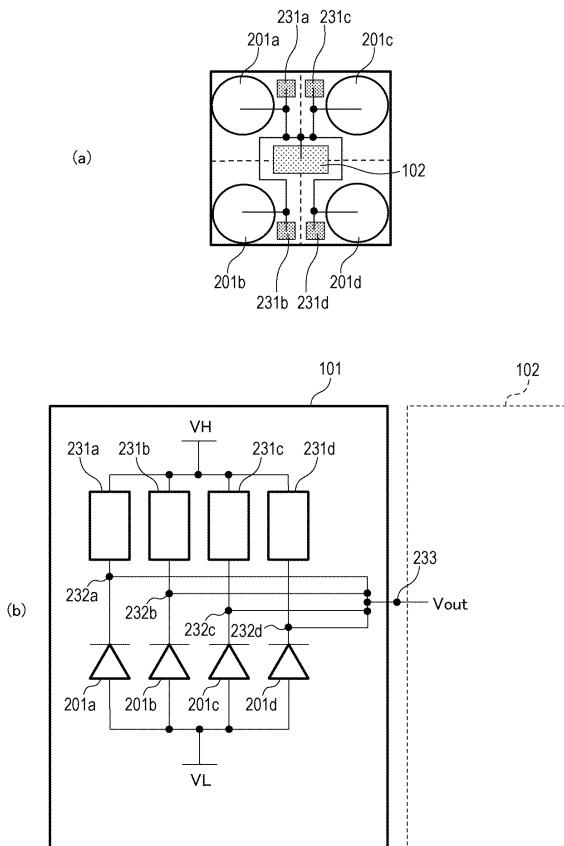

図4(a)及び図4(b)は、本実施形態に係る光電変換素子101の構成例を示す図である。図4(a)は、光電変換素子101及び画素信号処理部102が形成されている半導体基板に対して垂直な方向からの平面視による模式図である。図4(b)は、光電変換素子101の回路図である。

30

【0044】

図4(a)に示されるように、1つの画素100には4つの光電変換部201a、201b、201c、201dが設けられている。4つの光電変換部201a、201b、201c、201dは、2行及び2列をなす行列状に配されている。画素信号処理部102は、4つの光電変換部201a、201b、201c、201dの中心付近に配されている。クエンチ素子202は2つの光電変換部201a、201cの間に配されている。

40

【0045】

このように、本実施形態では、4つの光電変換部201a、201b、201c、201dと、画素信号処理部102と、クエンチ素子202とが同一の半導体基板の同一の面に形成されている。これにより、これらを別の基板に形成する場合と比較して製造コストを低減させることができる。この面積低減効果は、クエンチ素子202が抵抗素子等の受動素子である場合よりも、図3(c)のような能動クエンチ回路である場合の方が大きい。一般的に、能動クエンチ回路の方が受動素子よりも素子面積が大きいためである。

【0046】

図4(b)に示されるように、1つのクエンチ素子202が、4つの光電変換部201a、201b、201c、201dに対して直列に接続されている。クエンチ素子202と光電変換部201a、201b、201c、201dとが接続されるノード221において、4つの光電変換部201a、201b、201c、201dのカソードから伸びる配線は1つに束ねられている。

【0047】

50

図5(a)及び図5(b)は、本実施形態の比較例に係る光電変換素子101の構成例を示す図である。図5(a)は、光電変換素子101及び画素信号処理部102が形成されている半導体基板に対して垂直な方向からの平面視による模式図である。図5(b)は、光電変換素子101の回路図である。

#### 【0048】

図5(a)及び図5(b)に示される比較例において図4(a)及び図4(b)と相違する点は、4つのクエンチ素子231a、231b、231c、231dが設けられている点である。4つのクエンチ素子231a、231b、231c、231dは、4つの光電変換部201a、201b、201c、201dにそれぞれ対応して設けられている。4つのクエンチ素子231a、231b、231c、231dは、それぞれ、4つの光電変換部201a、201b、201c、201dに対して直列に接続されている。

10

#### 【0049】

図4(a)及び図4(b)に示されている本実施形態の構成では、4つの光電変換部201a、201b、201c、201dに直列接続されるクエンチ素子202が1つに共通化されている。これにより、図5(a)及び図5(b)に示される比較例において生じ得るクエンチ素子231a、231b、231c、231dの性能のばらつきに起因する出力信号の精度への影響を低下させることができる。この効果について、図6(a)、図6(b)、図7(a)、図7(b)、図8(a)及び図8(b)を参照してより詳細に説明する。

20

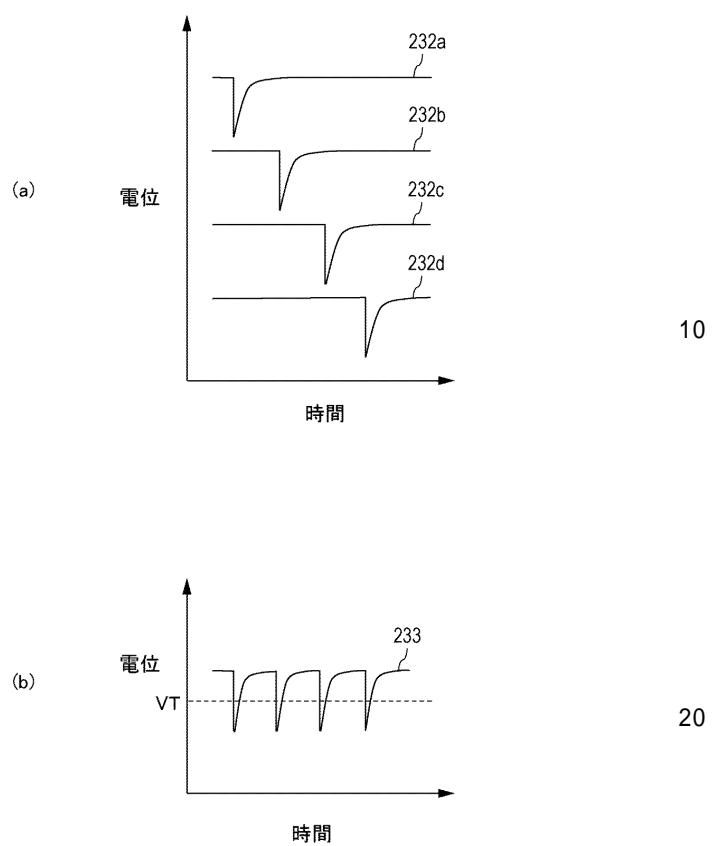

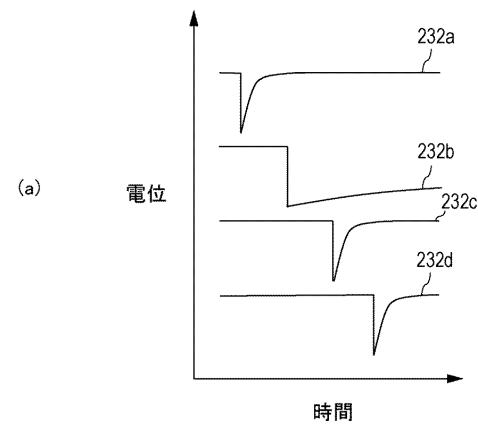

#### 【0050】

図6(a)及び図6(b)は、本実施形態の比較例における各ノードの電位を示すグラフである。各グラフの横軸は時間を、縦軸は電位をそれぞれ示している。なお、本明細書において、各グラフの軸の単位は任意であり、グラフ間でスケールは一致していない。図6(a)は、4つの光電変換部201a、201b、201c、201dのそれぞれに異なるタイミングで1個の光子が入射した際の、ノード232a、232b、232c、232dの電位の変化を示すグラフである。ノード232a、232b、232c、232dの各グラフは重ならないように縦方向にずらして図示されている。図6(a)は、各光電変換部に光子が入射したタイミングで、各ノードの電位が低下し、その後所定の時間(デッドタイム)が経過するとクエンチ動作により元の電位に戻ることを示している。

30

#### 【0051】

図6(b)は、図6(a)に示すタイミングで4つの光電変換部201a、201b、201c、201dに光子が入射した際の、ノード233の電位の変化を示すグラフである。4つの光電変換部201a、201b、201c、201dのそれぞれに1個ずつ光子が入射されているため、これらを加算平均した電位であるノード233の電位は4回下降している。

30

#### 【0052】

図6(b)の破線は、画素信号処理部102において、電位変化をカウントする際の論理判定閾値VTの電位レベルを示している。カウンタ回路209は、電位が論理判定閾値VTよりも高い状態から論理判定閾値VTをまたいで論理判定閾値VTよりも低い状態に変化した回数をカウントする。ノード233の電位が論理判定閾値VTを下回る回数は4回であるため、カウンタ回路209によりカウントされるカウント数は4である。このカウント数は入射された光子の個数の合計と一致しており、画素信号処理部102からは適切な値が出力される。

40

#### 【0053】

しかしながら、クエンチ素子231a、231b、231c、231dのうちの、いずれか1つでも理想的な動作を行えない場合、ノード233における電位の波形は、図6(b)に示すものとは異なる波形となる。図7(a)及び図7(b)には、クエンチ素子231bの実効的な抵抗値が、他のクエンチ素子231a、231c、231dよりも大きい場合の各ノードの電位を示すグラフが示されている。図7(a)及び図7(b)において、4つの光電変換部201a、201b、201c、201dへの光子の入射タイミングは

50

図6(a)及び図6(b)の場合と同様である。

**【0054】**

図7(a)において、ノード232a、232c、232dの電位の変化は図6(a)に示されているものと同様である。しかしながら、ノード232bについては、電位が低下してから、元に戻るまでの時間が長くなっている。この理由は、クエンチ素子231bの実効的な抵抗値が大きいため回路の時定数が大きくなり、上述の式(1)又は式(2)に示されているデッドタイム<sub>d</sub>が大きくなるためである。

**【0055】**

この場合において、ノード233の電位は、図7(b)に示されるものとなる。ノード233の電位が論理判定閾値VTをまたいで下回る回数は2回である。そのため、カウンタ回路209によりカウントされるカウント数は2である。このように、比較例では、ノード232bでの電位の低下が戻る時間が長くなっている影響により、光電変換部201c、201dに光子が入射した時刻における電位降下量はカウントされない。このように、比較例においては、カウント数が入射された光子の個数の合計と一致せず、画素信号処理部102から出力される値の精度が低下する場合がある。

10

**【0056】**

図4(a)及び図4(b)に示されている本実施形態の構成では、4つの光電変換部201a、201b、201c、201dは、1つのクエンチ素子202に直列接続されている。この場合、クエンチ素子202が1つであるため、異なるクエンチ素子間の性能ばらつきに起因する精度劣化は生じない。この場合における各ノードの電位が図8(a)及び図8(b)に示されている。図8(a)及び図8(b)において、4つの光電変換部201a、201b、201c、201dへの光子の入射タイミングは図6(a)及び図6(b)の場合と同様である。

20

**【0057】**

図8(a)は、図4(a)のノード221における電位の変化を示すグラフである。4つの光電変換部201a、201b、201c、201dは、出力電位が配線上で加算平均された状態でクエンチ素子202に接続されている。そのため、電位が降下する回数は、光電変換部201a、201b、201c、201dに入射される光子の個数と一致する。

30

**【0058】**

図8(b)は、図4(a)のノード222における電位の変化を示すグラフである。本構成では、ノード222は、ノード221と同電位であるため、図8(b)は、図8(a)と同様の波形である。そのため、ノード222の電位が論理判定閾値VTを下回る回数は4回であり、カウンタ回路209によりカウントされるカウント数は4である。このカウント数は入射された光子の個数の合計と一致しており、画素信号処理部102からは適切な値が出力される。

40

**【0059】**

以上のように、本実施形態においては、4つの光電変換部201a、201b、201c、201dは1つのクエンチ素子202に直列接続されている。そのため、異なるクエンチ素子間の性能ばらつきに起因する精度劣化は生じない。したがって、本実施形態によれば、出力信号の精度が向上された光検出装置1010が提供される。

40

**【0060】**

また、本実施形態では、4つの光電変換部201a、201b、201c、201dに対して、1つのクエンチ素子202を設ける構成であるため、光電変換部ごとにクエンチ素子を設ける構成に比べてクエンチ素子の素子数を少なくすることができる。そのため、クエンチ素子の配置に要する素子面積を低減することができ、その分の素子面積を光電変換部の面積に割り当てるにより、光検出装置1010の検出感度を向上させることができる。

**【0061】**

[第2実施形態]

50

第1実施形態では、図4(a)に示されるように、4つの光電変換部201a、201b、201c、201dと、画素信号処理部102と、クエンチ素子202とが同一の半導体基板の同一の面に形成されている。これに対し、本実施形態では、4つの光電変換部201a、201b、201c、201dが第1の基板500に形成され、画素信号処理部102とクエンチ素子202とが第1の基板500とは異なる第2の基板600に形成される例を説明する。

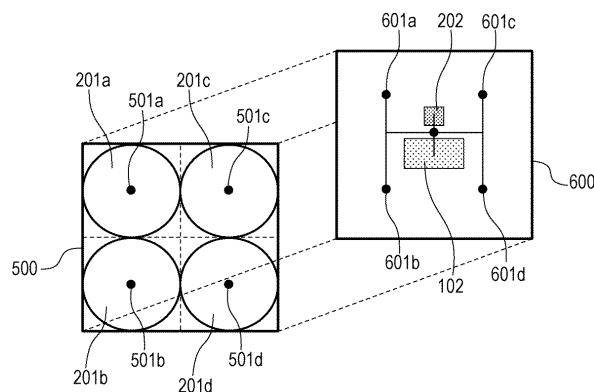

#### 【0062】

図9は、本実施形態に係る画素100の構成例を示す模式図である。図9に示されるように、本実施形態の光検出装置1010は、第1の基板500と第2の基板600を有する。4つの光電変換部201a、201b、201c、201dは、第1の基板500上に形成される。画素信号処理部102及びクエンチ素子202は、第2の基板600に形成される。

10

#### 【0063】

第1の基板500は、電極501a～501dを有し、第2の基板600は、電極601a～601dを有する。電極501a～501dと電極601a～601dとは、それぞれ相互に電気的に接続される。これにより、第1実施形態と同様の回路構成が実現される。

#### 【0064】

本実施形態においても、第1実施形態と同様に出力信号の精度が向上された光検出装置1010が提供される。更に、画素信号処理部102及びクエンチ素子202を光電変換部201a、201b、201c、201dを別の基板に形成することにより、光電変換部201a、201b、201c、201dの面積を大きくすることができる。これにより、受光面積が広くなるため、光検出装置1010の検出感度を向上させることができる。

20

#### 【0065】

一方、本実施形態では、第1実施形態の場合と比べて、基板の枚数が増加する等の理由により製造コストが増加する。したがって、コスト低減が優先される場合には、第1実施形態の構成の方が望ましい場合もある。

#### 【0066】

##### [第3実施形態]

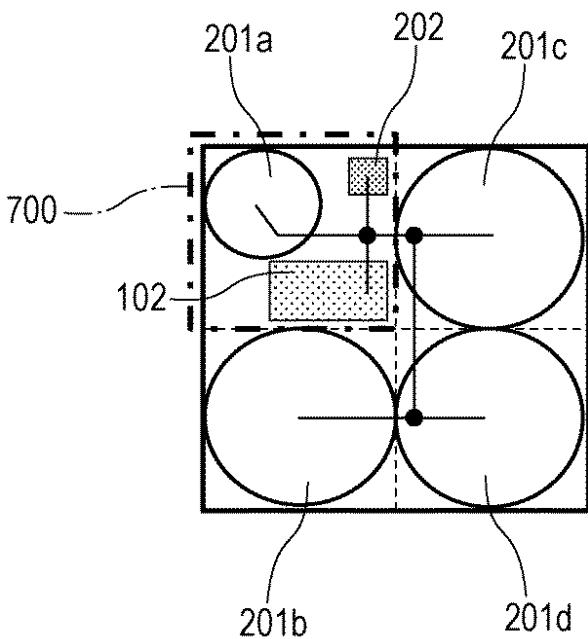

第1実施形態では、図4(a)に示されるように、4つの光電変換部201a、201b、201c、201dの面積が同一である。これに対し、本実施形態では、光電変換部201aの面積が、光電変換部201b、201c、201dよりも小さい例を説明する。

30

#### 【0067】

図10は、本実施形態に係る画素100の構成例を示す模式図である。本実施形態では、光電変換部201aの面積が、光電変換部201b、201c、201dよりも小さい。光電変換部201b、201c、201dのうちのいずれかが配されている領域を第1の領域、光電変換部201aが配されている領域を第2の領域700とすると、第1の領域と第2の領域700とは、行列状に配列されている。第2の領域700内には、光電変換部201aと、クエンチ素子202と、画素信号処理部102とが配置される。この構成により、第1実施形態の場合と比べて光電変換部201b、201c、201dの面積を大きくすることが可能となり、光検出装置1010の検出感度を向上させることができる。

40

#### 【0068】

なお、光電変換部201aについては、第1実施形態の場合と比べて面積が小さくなり得る。しかしながら、光電変換部201a上に設けられるマイクロレンズ等の光学系の設計を最適化して、入射光を光電変換部201aの受光領域に集光させることで、面積の縮小に起因する感度低下を補償することができる。

#### 【0069】

##### [第4実施形態]

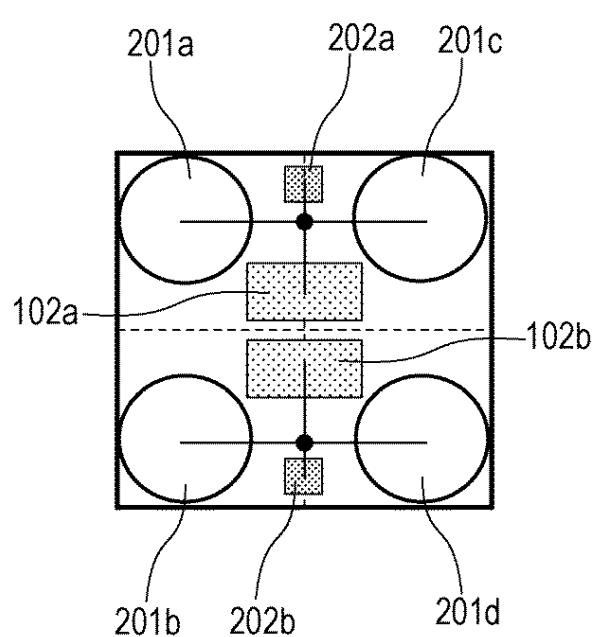

第1実施形態では、図4(a)に示されるように、4つの光電変換部201a、201b、201c、201d

50

b、201c、201dに対して1つのクエンチ素子202が接続されている。これに対し、本実施形態では、4つの光電変換部201a、201b、201c、201dに対して2つのクエンチ素子202a、202bが接続される例を説明する。

#### 【0070】

図11は、本実施形態に係る画素100の構成例を示す模式図である。本実施形態の画素100は、2つのクエンチ素子202a、202bと、2つの画素信号処理部102a、102bとを有する。2つの光電変換部201a、201cは、1つのクエンチ素子202a及び画素信号処理部102aに接続される。2つの光電変換部201b、201dは、1つのクエンチ素子202b及び画素信号処理部102bに接続される。このように、本実施形態では、1つのクエンチ素子と、2つの光電変換部と、1つの画素信号処理部とが組となって1つの領域に配されており、この領域が半導体基板上に複数個配列されている。

10

#### 【0071】

第1実施形態では、4つの光電変換部で得られた信号を加算して検出する構成であるのに対し、本実施形態では、2つの光電変換部で得られた信号を加算して検出する構成である。これにより、本実施形態では1つの画素100から2つの信号が得られる。そのため、第1実施形態の構成に比べ、光検出装置1010により取得される画像の空間分解能が向上する。

#### 【0072】

なお、本実施形態の光電変換部201a、201b、201c、201dは、第1実施形態のそれらと比べて面積が小さくなり得る。しかしながら、第3実施形態と同様に、マイクロレンズ等の光学系の設計を最適化して、入射光を受光領域に集光させることで、面積の縮小に起因する感度低下を補償することができる。

20

#### 【0073】

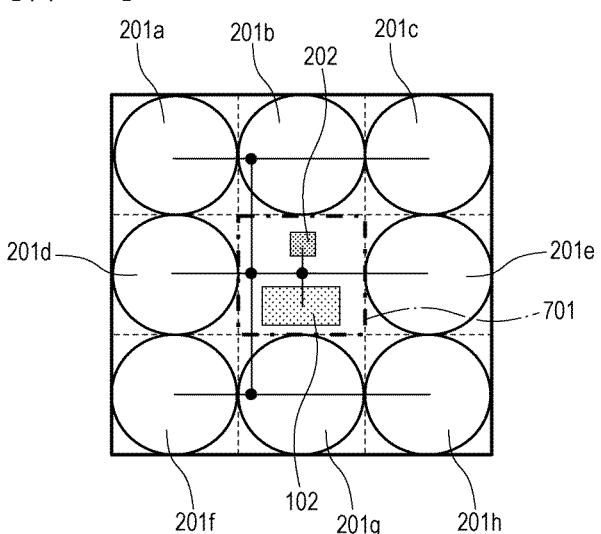

##### [第5実施形態]

第1実施形態では、図4(a)に示されるように、2つの光電変換部201a、201cの間に1つのクエンチ素子202が配置されている。これに対し、本実施形態では、8つの光電変換部201a～201hの各々が配されている第1の領域の中央の第2の領域701に1つのクエンチ素子202が配置される例を説明する。

30

#### 【0074】

図12は、本実施形態に係る画素100の構成例を示す模式図である。本実施形態の画素100は、8つの光電変換部201a～201hを有する。8つの光電変換部201a～201hの各々が配されている第1の領域の中央は、光電変換部が設けられていない第2の領域701である。第1の領域及び第2の領域701は、3行及び3列をなす行列状に配されている。第2の領域701には、画素信号処理部102及びクエンチ素子202が配置されている。

#### 【0075】

第1実施形態の構成において、光電変換部の面積が小さい場合には、画素100内に光電変換部、クエンチ素子202及び画素信号処理部102を1つの領域に収めて行列状に配列することが困難になる。本実施形態では、第2の領域701内に、光電変換部を配置せずに、クエンチ素子202と画素信号処理部102のみを配置する構成として、レイアウト設計が容易になる。

40

#### 【0076】

##### [第6実施形態]

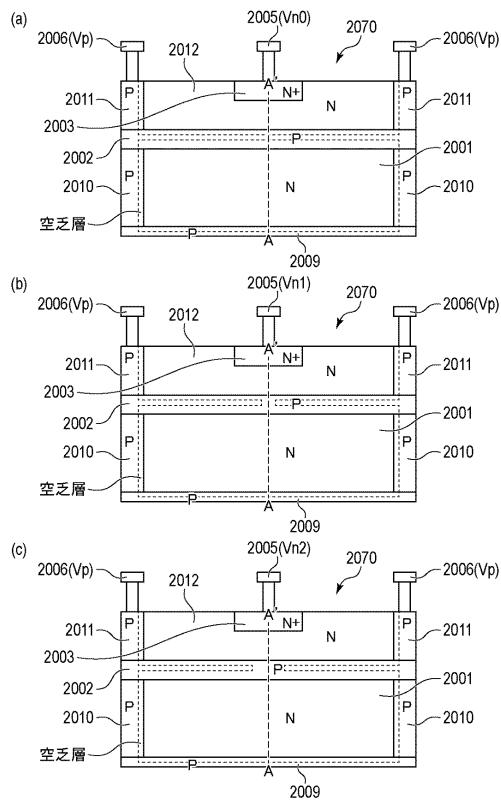

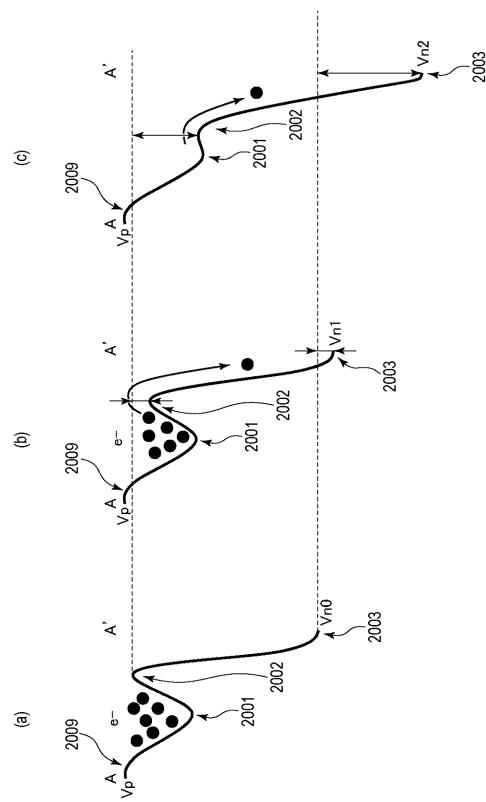

図13(a)、図13(b)及び図13(c)は、光電変換部2070の断面構造を模式的に示す図である。図13(a)、図13(b)及び図13(c)に示すように、光電変換部2070は、半導体基板に形成されたN型半導体領域2001、P型半導体領域2002、N型半導体領域2003、及びN型半導体領域2012を含む。N型半導体領域2001とP型半導体領域2002とは、光を信号電荷に変換して蓄積するPD(フォトダイオード)を構成する。P型半導体領域2002と、N型半導体領域2003と、N型

50

半導体領域 2012 と、は A D (アバランシェダイオード) を構成する。後述するが、光電変換部 2070 の動作期間は、信号電荷が P D に蓄積される蓄積期間と、P D に蓄積した信号電荷が A D に転送される読出期間とに大別される。読出期間のうちの少なくとも一部の期間には、転送される信号電荷により A D においてアバランシェ増倍が生じる。

#### 【0077】

光電変換部 2070 は、N型半導体領域 2001 の下方に形成される P型半導体領域 2009 と、N型半導体領域 2001、2012 の側方に形成される P型半導体領域 2010、2011 とを更に含む。P型半導体領域 2010、2011 は、隣接する光電変換部 2070 同士を分離する。

#### 【0078】

これらの半導体領域の断面構造における配置は、図 13 (a) 等に示される通りである。特に、N型半導体領域 2001 は、P型半導体領域 2002、2009、2010 によって囲まれている。また、N型半導体領域 2001 と N型半導体領域 2003との間には、少なくとも部分的に、P型半導体領域 2002 が配される。N型半導体領域 2012 は、N型半導体領域 2003 よりも低い不純物濃度を有し、かつ、P型半導体領域 2002 と N型半導体領域 2003との間に配されている。N型半導体領域 2012 の少なくとも一部はアバランシェ増倍部を形成する。なお、図 13 (a)、図 13 (b) 及び図 13 (c)において、入射光は図中の上側から入射されるものとする。

#### 【0079】

N型半導体領域 2003 には、電位制御部 2005 が接続されている。電位制御部 2005 は、N型半導体領域 2003 に電位 Vn を印加している。P型半導体領域 2011 には、電位制御部 2006 が接続されている。電位制御部 2006 は、P型半導体領域 2011 に電位 Vp を印加している。電位 Vp は、P型半導体領域 2011 を介して、P型半導体領域 2002、2009、2010 にも供給され得る。図 13 (a) に示す状態では、N型半導体領域 2001 は電気的にフローティングとなっている。

#### 【0080】

半導体基板の内部のポテンシャル分布は、上述の各半導体領域の配置、各半導体領域の不純物濃度分布、電位制御部 2005 及び電位制御部 2006 に印加される電位によって決定される。したがって、電位制御部 2005 及び電位制御部 2006 に印加される電位を制御することにより、上述の蓄積期間状態と読出期間状態とを切り替えることができる。また、信号電荷転送時においてアバランシェ増倍を生じさせる等の所定のポテンシャルの状態を実現するために、上述の各半導体領域の配置、及び、各半導体領域の不純物濃度分布が、光検出装置の設計時に調整され得る。

#### 【0081】

図 13 (a)、図 13 (b)、図 13 (c) は、N型半導体領域 2003 に印加する電位 Vn の値を Vn0、Vn1、Vn2 と変化させた例を示している。また、図 14 (a)、図 14 (b)、図 14 (c) は、図 13 (a)、図 13 (b)、図 13 (c) のそれに対応する A - A' におけるポテンシャルを示す図である。この 3 つの例では、N型半導体領域 2001 と N型半導体領域 2003との間に生じるポテンシャル障壁の高さが互いに異なる。これにより、N型半導体領域 2001 に信号電荷を蓄積する期間と、N型半導体領域 2001 から N型半導体領域 2003 に信号電荷を読み出す期間とが制御される。説明の単純化のために、図 13 (a)、図 13 (b)、図 13 (c) では、P型半導体領域 2002 に固定の電位 Vp が印加されているものとしているが、P型半導体領域 2002 に印加される電位が互いに異なっていてもよい。なお、図 13 (a)、図 13 (b) 及び図 13 (c) の破線は、空乏層の端部を示している。

#### 【0082】

図 13 (a) は、N型半導体領域 2001 に信号電荷が蓄積される状態の光電変換部 2070 を示す図であり、図 14 (a) は図 13 (a) の A - A' におけるポテンシャルを示す図である。電位制御部 2005 に印加される電位 Vn0 は、電位制御部 2006 に印加される電位 Vp よりも高い。すなわち、PN 接合には逆バイアスが印加されており、PN

10

20

30

40

50

接合面の付近には空乏層が広がっている。図13(a)に示されるように、P型半導体領域2002の一部には中性領域が存在している。P型半導体領域2002の中性領域には、P型半導体領域の多数キャリアであるホールが多数存在している。そのため、P型半導体領域2002の中性領域の電位は、電位制御部2006の電位V<sub>p</sub>とほぼ同じである。なお、P型半導体領域2011、2010、2009にも、それぞれ中性領域が存在しているものとする。

#### 【0083】

暗状態、すなわち信号電荷が無い場合において、図13(a)の状態では、N型半導体領域2001の全体に空乏層が広がっている。このとき、P型半導体領域2002の中性領域（及び周囲にある他のP型半導体領域の中性領域）とN型半導体領域2001との間には、いわゆる「空乏化電圧」と呼ばれる逆バイアス電圧が少なくとも生じている。換言すると、N型半導体領域2001に存在する信号電荷（電子）に対しては、PN接合間のビルトインポテンシャルに空乏化電圧を加えた電圧に相当するポテンシャル障壁がN型半導体領域2001の周囲に生じている。したがって、A-A'に沿ったポテンシャル分布において、図14(a)に示すように、N型半導体領域2001とN型半導体領域2003との間に、N型半導体領域2001の電子に対するポテンシャル障壁が生じている。なお上述のPDの空乏化電圧は、典型的には、CMOSセンサ、CCDセンサ等のイメージセンサにおけるPDの空乏化電圧と同レベルであり、すなわち1V~2V程度である。

10

#### 【0084】

図13(a)では、N型半導体領域2003に印加される電位V<sub>n0</sub>は、電位制御部2006に印加される電位V<sub>p</sub>よりも高い。したがって、P型半導体領域2002、2011と、N型半導体領域2003、2012との間のPN接合には、電位V<sub>n0</sub>と電位V<sub>p</sub>との差分に相当する逆バイアスが印加される。また、当該逆バイアスに応じた空乏層が、P型半導体領域2002及びP型半導体領域2011に広がっている。この図13(a)の状態において、P型半導体領域2002とN型半導体領域2003、2012とで形成されるADのPN接合では基本的にはアバランシェ増倍が起こらないように電位V<sub>n0</sub>が設定される。また、光入射により発生した信号電荷はN型半導体領域2001に蓄積される。

20

#### 【0085】

図13(b)は、N型半導体領域2003に印加される電位V<sub>n</sub>が、V<sub>n0</sub>から、V<sub>n</sub>0よりも高いV<sub>n1</sub>に変化した状態を示す図である。V<sub>n1</sub>はV<sub>n0</sub>より高い電位であり、一方で、V<sub>p</sub>は固定である。そのため、P型半導体領域2002、2011と、N型半導体領域2003、2012との間のPN接合には、図13(a)の場合と比べて大きな逆バイアスが印加される。また、それに応じて、P型半導体領域2002の空乏層が図13(a)の場合に比べて広がる。その結果、電位V<sub>n</sub>がV<sub>n1</sub>の時に、N型半導体領域2001の周囲のP型半導体領域2002の空乏層と、N型半導体領域2003の周囲のP型半導体領域2002の空乏層とがつながる。換言すると、N型半導体領域2001からN型半導体領域2003まで、空乏層が連続的に延びた状態となる。

30

#### 【0086】

P型半導体領域2002のうち、空乏化している部分のポテンシャルは、P型半導体領域2002の中性領域のポテンシャル（ほぼV<sub>p</sub>と同じ）よりも低い。これは、N型半導体領域2003に印加される電位V<sub>n</sub>の影響を受けるためである。したがって、図13(b)のA-A'に沿ったポテンシャル分布においては、図14(b)が示す通り、N型半導体領域2001とN型半導体領域2003との間のポテンシャル障壁の高さが、図13(a)の場合に比べて低くなる。

40

#### 【0087】

このとき、N型半導体領域2001の周囲のほとんどをP型半導体領域2002、2009、2010の中性領域が取り囲んでいる。そして、電位制御部2006の電位V<sub>p</sub>は固定である。そのため、N型半導体領域2001の中心のポテンシャルはほとんど変化しない。したがって、上述の通り、N型半導体領域2001に対するポテンシャル障壁の高

50

さを、局的に下げることができる。

#### 【0088】

図13(b)において、N型半導体領域2001に信号電荷が蓄積されている場合は、ポテンシャル障壁を超えて信号電荷がN型半導体領域2003に転送され始める。このとき、N型半導体領域2003とP型半導体領域2002との間には、アバランシェ増倍が起こる程度の逆バイアス電圧が生じている状態となっていることが好ましい。

#### 【0089】

連続的な空乏層が形成された後、N型半導体領域2003に印加される電位 $V_n$ が $V_n$ 1から $V_n$ 1よりも高い電位 $V_n$ 2へ変化する。これに応じて、ポテンシャル障壁が徐々に低下する。また、電位 $V_n$ の変化に応じて、P型半導体領域2002に生じる空乏層の幅も変化する。

10

#### 【0090】

図13(c)は、N型半導体領域2001とN型半導体領域2003との間のポテンシャル障壁がほぼなくなった状態を示す図である。また、図14(c)は、図13(c)のA-A'のポテンシャルを示す図である。このとき、N型半導体領域2003には電位 $V_n$ 2が印加されている。図14(c)の状態では、N型半導体領域2001に蓄積された信号電荷がN型半導体領域2003にすべて転送される。すなわち、完全空乏化転送が可能となる。

#### 【0091】

このような完全空乏化転送に必要な電圧は、P型半導体領域2002の不純物濃度が低いほど低くなり、逆に、P型半導体領域2002の不純物濃度が高いほど高くなる。前述のように信号電荷が転送されている期間の少なくとも一部で、P型半導体領域2002とN型半導体領域2003との間にアバランシェ増倍が生じる逆バイアスが生じるように、P型半導体領域2002やN型半導体領域2012の不純物濃度が設定される。

20

#### 【0092】

なお、暗状態において、電位 $V_n$ が図13(b)の状態から図13(c)の状態に変化するときに、N型半導体領域2001のポテンシャルが多少変化することが考えられる。しかしながら、N型半導体領域2001よりもP型半導体領域2002の方が、電位 $V_n$ の供給されるN型半導体領域2003に近いため、P型半導体領域2002の方が電位 $V_n$ の変化の影響をより強く受ける。したがって、P型半導体領域2002の空乏化した部分のポテンシャルの方がN型半導体領域2001のポテンシャルよりも変化しやすい。結果として、N型半導体領域2001とN型半導体領域2003との間のポテンシャルバリアを無くすことができる。

30

#### 【0093】

本実施形態では、図13(c)において、P型半導体領域2009及びP型半導体領域2010には中性領域が残った状態である。この構成によれば、N型半導体領域2001の周囲の大部分に電位 $V_p$ を供給できるため、図14(b)及び図14(c)の状態において、N型半導体領域2001のポテンシャルの変化を小さく抑えることができる。したがって、電位 $V_n$ の変化量がさほど大きくななくても、電荷の完全転送が可能である。ただし、電位 $V_n$ が $V_n$ 0から $V_n$ 2に変化する過程で、P型半導体領域2009又はP型半導体領域2010の全体が空乏化することもあり得る。

40

#### 【0094】

以上に説明した通り、本実施形態の光電変換部2070は、電位 $V_n$ が制御されることにより、N型半導体領域2001とN型半導体領域2003との間のポテンシャル障壁の高さを制御することができる。したがって、本実施形態の光電変換部2070を備える光検出装置は、N型半導体領域2001に信号電荷を蓄積する動作と、N型半導体領域2001からN型半導体領域2003に信号電荷を読み出す動作と、を選択的に実施することができる。

#### 【0095】

ここで、図13(b)において信号電荷が転送されたときに、アバランシェ増倍が生じ

50

ることが好ましいと説明した。しかしながら、電位  $V_n$  が  $V_{n0}$  から  $V_{n2}$  に変化する間に、アバランシェ増倍が起きる大きさの逆バイアスが印加されるタイミングと、空乏層がつながるタイミング（すなわち、ポテンシャル障壁が下がり始めるタイミング）とがずれていてもよい。アバランシェ増倍が起きる大きさの逆バイアスが印加されるタイミングと P 型半導体領域 2002において空乏層がつながるタイミングとは、どちらが先であってもよい。N 型半導体領域 2001における飽和電荷量は、アバランシェ増倍によって信号検出が開始できるようなバイアス電圧が印加されるときのポテンシャル障壁で決まる。

#### 【0096】

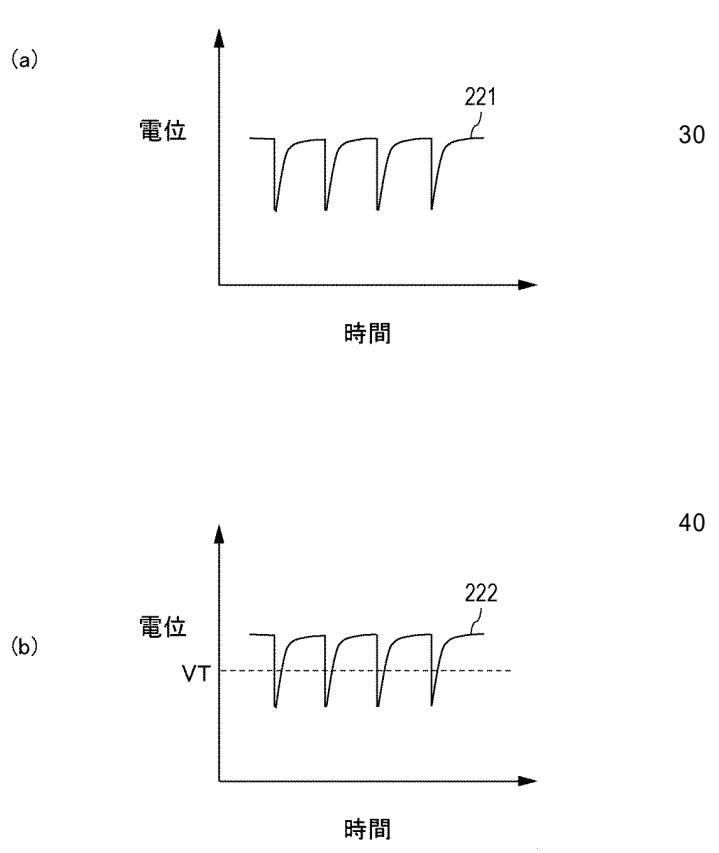

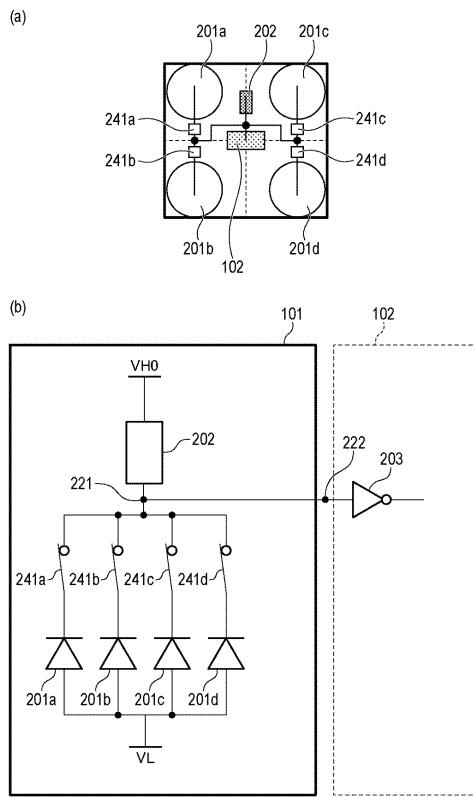

上述の構成の光電変換部 2070 を備える光電変換素子 101 の構成例を説明する。図 15(a) 及び図 15(b) は、本実施形態に係る光電変換素子 101 の構成例を示す図である。図 15(a) 及び図 15(b)において、図 4(a) 及び図 4(b)との差異点は、光電変換部 201a、201b、201c、201d のそれぞれに対して、スイッチ素子 241a、241b、241c、241d が追加されている点である。ここで、光電変換部 201a、201b、201c、201d は、いずれも上述の光電変換部 2070 と同様の構成を有しているものとする。光電変換部 201a は、スイッチ素子 241a を間に介してクエンチ素子 202 との接続ノードであるノード 221 に接続されている。光電変換部 201b は、スイッチ素子 241b を間に介してノード 221 に接続されている。光電変換部 201c は、スイッチ素子 241c を間に介してノード 221 に接続されている。光電変換部 201d は、スイッチ素子 241d を間に介してノード 221 に接続されている。

10

#### 【0097】

図 15(b) に示すように、初期状態において、スイッチ素子 241a、241b、241c、241d は、全てオン状態であり、電位  $V_{H0}$  が光電変換部 201a、201b、201c、201d に供給されている。その後、例えば、スイッチ素子 241a だけをオン状態とし、その他のスイッチ素子 241b、241c、241d はオフ状態にすると、光電変換部 201a だけに電位  $V_{H0}$  が供給される状態となる。

20

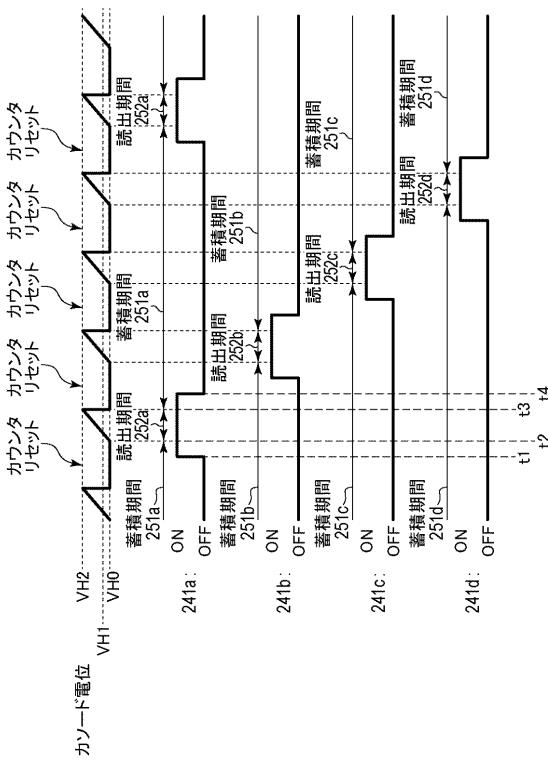

#### 【0098】

図 16 に示すタイミングチャートを用いて、光電変換素子 101 の駆動方法を説明する。図中の「カソード電位」は、電位制御部 2005 に印加される電位を示しており、図中の「241a」、「241b」、「241c」、「241d」は、対応するスイッチ素子のオン状態又はオフ状態を示している。

30

#### 【0099】

上述の初期状態の後、スイッチ素子 241a、241b、241c、241d はオフ状態になり、光電変換部 201a、201b、201c、201d は電荷が蓄積される蓄積状態となる。時刻  $t_1$ において、スイッチ素子 241a のみがオン状態になる。この時点において、他のスイッチ素子 241b、241c、241d はオフ状態のままに維持されている。時刻  $t_2$  以前の時点において、光電変換部 201a のカソード電位は  $V_{H0}$  である。このとき、光電変換部 201a には、アバランシェ増倍が起きるのに必要なバイアス電圧は印加されておらず、光電変換部 201a は、ポテンシャル障壁が下がり始める前の状態である。したがって、光電変換部 201a に蓄積された電荷は電位制御部 2005 から読み出されない。言い換えると、時刻  $t_2$  以前の期間は蓄積期間 251a である。このときの図 13(a) の A - A' のポテンシャルが図 14(a) である。図 14(a) に示されるように、N 型半導体領域 2001 に蓄積された電荷は P 型半導体領域 2002 のポテンシャル障壁により、N 型半導体領域 2003 に到達していない。

40

#### 【0100】

時刻  $t_2$  において、光電変換部 201a のカソード電位が  $V_{H0}$  から遷移を開始する。カソード電位が  $V_{H1}$  になった時点から、光電変換部 201a には、アバランシェ増倍が起きるのに必要なバイアスが印加され始める。これにより、ポテンシャル障壁が下がり、蓄積電荷が徐々に読み出され始める。このときの図 13(b) の A - A' のポテンシャルが図 14(b) である。図 14(b) に示されるように、P 型半導体領域 2002 のポテン

50

シャル障壁が下がることにより、N型半導体領域2001に蓄積された電荷のうちの一部がN型半導体領域2003に到達する。

#### 【0101】

時刻t2から時刻t3の期間にわたって光電変換部201aのカソード電位がVH0からVH2に徐々に遷移する。時刻t3付近において、光電変換部201aにはアバランシェ増倍が起きるのに十分なバイアスが印加され、蓄積された信号電荷はすべて転送され完全空乏化転送が実現する。このときの図13(c)のA-A'のポテンシャルが図14(c)である。図14(c)に示されるように、P型半導体領域2002のポテンシャル障壁が下がることにより、N型半導体領域2001に蓄積された電荷のすべてが、N型半導体領域2003に到達する。このようにして、光電変換部201aに蓄積された電荷が読み出される。言い換えると、時刻t2から時刻t3までの期間は読み出し期間252aである。10

#### 【0102】

その後、時刻t3において光電変換部201aのカソード電位がVH2からVH0に遷移する。これにより、光電変換部201aには、アバランシェ増倍が起きるのに必要なバイアスが印加されない状態となり、ポテンシャル障壁が時刻t2以前と同じ状態に戻る。言い換えると、時刻t3以降の期間は蓄積期間251aである。なお、読み出し期間252aの後には、光電変換部201aから転送された電荷のカウント数がリセットされる。

#### 【0103】

上述の光電変換部201aからの読み出しと同様の処理が光電変換部201b、201c、201dに対しても、順次行われる。これにより、光電変換部201a、201b、201c、201dに蓄積された電荷が、順次読み出される。20

#### 【0104】

上述の第1実施形態では、出力された信号が4つの光電変換部201a、201b、201c、201dのうちのいずれで発生した電荷によるものであるかを区別できない回路構成となっている。これに対し、本実施形態では、光電変換部201a、201b、201c、201dのそれぞれに対して個別に読み出しを行うよう制御することが可能である。したがって、本実施形態によれば、出力された信号が4つの光電変換部201a、201b、201c、201dのうちのいずれで発生した電荷によるものであるかを区別することが可能な光検出装置1010が提供される。なお、本実施形態において、信号電荷は正孔であってもよく、その場合、各半導体領域のN型とP型は反対になる。30

#### 【0105】

##### [第7実施形態]

本実施形態では、図17を参照しつつ、第1乃至第6実施形態の光検出装置1010を用いた光検出システムの一例を説明する。本実施形態の光検出システムは、不可視光である波長帯の光を検出する不可視光検出システムであり、PET(Positron Emission Tomography)等の医療診断システムに用いられる。なお、本実施形態の画素100は、図2のカウンタ回路209に代えてTDC204及びメモリ205を有する。

#### 【0106】

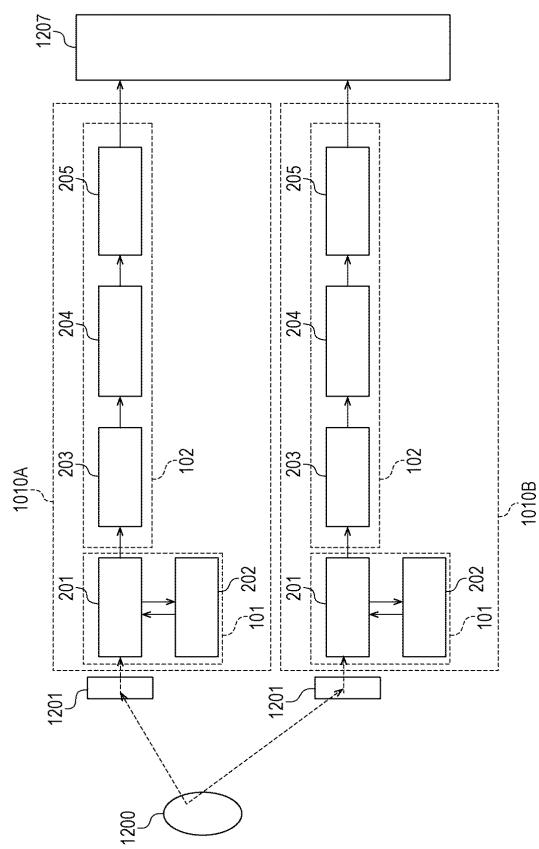

図17は、不可視光検出システムのブロック図である。不可視光検出システムは、複数の光検出装置1010A、1010B、波長変換部1201及びデータ処理部1207を有している。複数の光検出装置1010A、1010Bの各々は、カウンタ回路209に代えてTDC204及びメモリ205を有している点を除いては、第1乃至第6実施形態の光検出装置1010と同様である。40

#### 【0107】

照射物1200は、不可視光である波長帯(第1波長帯)の光を照射する。波長変換部1201は、照射物1200から照射された不可視光を受光し、可視光である波長帯(第2波長帯)の光を照射する。波長変換部1201から照射された可視光は光電変換部201に入射される。光電変換部201は、入射光を光電変換して電気信号に変換する。この電気信号は、クエンチ素子202、波形整形部203、TDC204を介して、デジタル

信号としてメモリ 205 に保持される。複数の光検出装置 1010A、1010B は、1 つの装置として構成されていてもよく、複数の装置として構成されていてもよい。

#### 【0108】

複数の光検出装置 1010A、1010B のメモリ 205 に保持された複数のデジタル信号は、データ処理部 1207 により読み出され、信号処理が行われる。データ処理部 1207 は、複数のデジタル信号から得られた複数の画像の合成処理を行う信号処理手段として機能する。

#### 【0109】

次に、不可視光検出システムの具体的な例として PET 等の医療診断システムの構成について説明する。照射物 1200 である被験者は、生体内からガンマ線等の放射線対を放出する。波長変換部 1201 は、シンチレータを含み、シンチレータは、被験者から放出された放射線対が入射すると可視光を照射する。

10

#### 【0110】

シンチレータから照射された可視光は、光検出装置 1010A、1010B に入射し、入射光に基づくデジタル信号がメモリ 205 に保持される。これにより、光検出装置 1010A、1010B は、被験者から放出された放射線対のそれぞれの到達時間を検出することができる。

#### 【0111】

複数の光検出装置 1010A、1010B のメモリ 205 に保持された複数のデジタル信号は、データ処理部 1207 により読み出され、信号処理が行われる。データ処理部 1207 は、複数のデジタル信号から得られた複数の画像を用いて画像再構成等の合成処理を行い、被験者の生体内の画像を生成する。

20

#### 【0112】

本実施形態によれば、検出性能が向上された光検出装置 1010A、1010B を用いることにより、より高精度な不可視光検出システム、医療診断システム等の光検出システムを提供することができる。

#### 【0113】

##### 〔第 8 実施形態〕

本実施形態では、図 18 及び図 19 を参照しつつ、第 1 乃至第 6 実施形態の光検出装置 1010 を用いた光検出システムの他の一例を説明する。

30

#### 【0114】

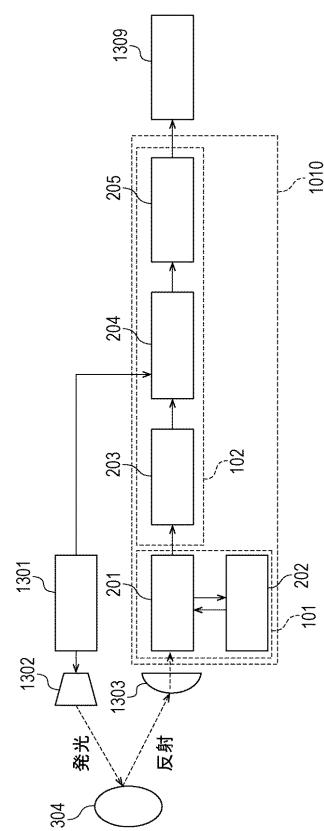

まず、図 18 を参照して光検出システムの一例である距離検出システムについて説明する。なお、本実施形態の画素 100 は、図 2 のカウンタ回路 209 に代えて TDC 204 及びメモリ 205 を有する。

#### 【0115】

図 18 は、距離検出システムのプロック図である。距離検出システムは、光源制御部 1301、発光部 1302、光学部材 1303、光検出装置 1010 及び距離算出部 1309 を有している。

#### 【0116】

光源制御部 1301 は発光部 1302 の駆動を制御する。発光部 1302 は、光源制御部 1301 からの信号に応じて、撮影方向に対して短パルス(列)の光を照射する発光装置である。

40

#### 【0117】

発光部 1302 から照射された光は、被写体 1304 において反射される。反射光は、レンズなどの光学部材 1303 を通して、光検出装置 1010 の光電変換部 201 で受光される。光電変換部 201 は、入射光に基づく信号を出力し、当該信号は、波形整形部 203 を介して TDC 204 に入力される。

#### 【0118】

TDC 204 は、光源制御部 1301 から発光部 1302 からの光照射のタイミングを示す信号を取得する。TDC 204 は、光源制御部 1301 から取得した信号と、波形整

50

形部 203 から入力された信号とを比較する。これにより、TDC204 は、発光部 1302 がパルス光を発光してから被写体 1304 で反射された反射光を受光するまでの時間をデジタル信号として出力する。TDC204 から出力されたデジタル信号は、メモリ 205 に保持される。この処理は複数回繰り返し行われ、メモリ 205 が複数回分のデジタル信号を保持することができる。

#### 【0119】

距離算出部 1309 は、メモリ 205 に保持された複数のデジタル信号に基づいて、光検出装置 1010 から被写体 1304 までの距離を算出する。この距離検出システムは例えば、車載用の距離検出装置に適用することができる。なお、距離算出部 1309 で行われる処理はデジタル信号の処理であることから、より一般的に信号処理手段と呼ばれることがある。

10

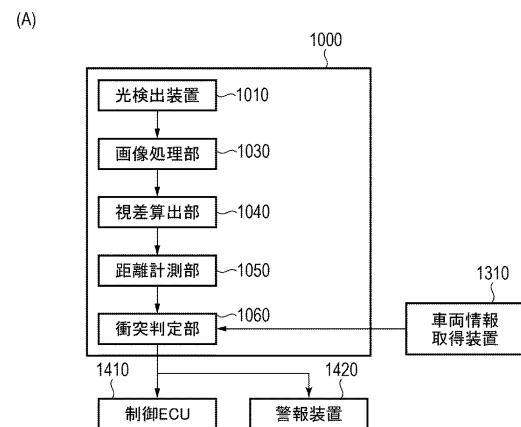

#### 【0120】

次に、図 19(A) 及び図 19(B) を参照して、光検出装置 1010 を車載カメラとして用いた光検出システムについて説明する。図 19(A) 及び図 19(B) は、本実施形態による光検出システム 1000 及び移動体の構成を示す図である。

#### 【0121】

図 19(A) は、車載カメラに関する光検出システム 1000 の一例を示したブロック図である。光検出システム 1000 は、第 1 実施形態に係る光検出装置 1010 を有する。光検出システム 1000 は、光検出装置 1010 により取得された複数のデジタル信号に対し、画像処理を行う画像処理部 1030 を有する。更に、光検出システム 1000 は、画像処理部 1030 により取得された複数の画像データから視差（視差画像の位相差）の算出を行う視差算出部 1040 を有する。

20

#### 【0122】

また、光検出システム 1000 は、算出された視差に基づいて対象物までの距離を算出する距離計測部 1050 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 1060 と、を有する。ここで、視差算出部 1040 及び距離計測部 1050 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。

#### 【0123】

衝突判定部 1060 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよいし、これらの組合せによって実現されてもよい。また、FPGA (Field Programmable Gate Array)、ASIC (Application Specific Integrated Circuit) 等によって実現されてもよい。更に、これらの組合せによって実現されてもよい。

30

#### 【0124】

光検出システム 1000 は車両情報取得装置 1310 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、光検出システム 1000 は、衝突判定部 1060 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 ECU1410 と接続されている。

40

#### 【0125】

また、光検出システム 1000 は、衝突判定部 1060 での判定結果に基づいて、ドライバーへ警報を発する警報装置 1420 とも接続されている。例えば、衝突判定部 1060 の判定結果として衝突可能性が高い場合、制御 ECU1410 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置 1420 は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

#### 【0126】

50

本実施形態では、車両の周囲、例えば前方又は後方を光検出システム 1000 で撮像する。図 19 (B) に、車両前方 (撮像範囲 1510) を撮像する場合の光検出システム 1000 を示した。車両情報取得装置 1310 は、所定の動作を行うように光検出システム 1000 又は光検出装置 1010 に指示を送る。このような構成により、測距の精度をより向上させることができる。

#### 【0127】

上述の例では他の車両と衝突しない制御を説明したが、光検出システム 1000 は、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。更に、光検出システム 1000 は、車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体 (移動装置) に適用することができる。加えて、移動体に限らず、高度道路交通システム (ITS) 等、広く物体認識を利用する機器に適用することができる。

#### 【0128】

本実施形態によれば、検出性能が向上された光検出装置 1010 を用いることにより、より高性能な光検出システム及び移動体を提供することができる。

#### 【0129】

##### 〔変形実施形態〕

本発明は、上述の実施形態に限らず種々の変形が可能である。例えば、いずれかの実施形態の一部の構成を他の実施形態に追加した例や、他の実施形態の一部の構成と置換した例も、本発明の実施形態である。

#### 【0130】

また、第 7 及び第 8 実施形態に示したシステムは、本発明の光検出装置を適用しうるシステムの構成例を示したものであり、本発明の光検出装置を適用可能なシステムは 17 乃至図 19 に示した構成に限定されるものではない。

#### 【0131】

本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける 1 つ以上のプロセッサがプログラムを読み出し実行する処理でも実現可能である。また、1 以上の機能を実現する回路 (例えば、ASIC) によっても実現可能である。

#### 【0132】

なお、上述の実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【符号の説明】

#### 【0133】

|      |         |

|------|---------|

| 102  | 画素信号処理部 |

| 201  | 光電変換部   |

| 202  | クエンチ素子  |

| 1010 | 光検出装置   |

10

20

30

40

50

【四面】

【 四 1 】

【 図 2 】

【図3】

【図4】

10

20

30

40

50

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

10

20

【図 11】

【図 12】

30

40

50

【図 1 3】

【図 1 4】

10

20

30

40

【図 1 5】

【図 1 6】

50

【図17】

【図18】

10

20

【図19】

30

40

50

---

フロントページの続き

(51)国際特許分類

H 0 4 N 25/70 (2023.01)

F I

H 0 1 L 31/10

H 0 4 N 25/70

G

(56)参考文献

特表 2 0 1 0 - 5 3 6 1 6 5 ( J P , A )

国際公開第 2 0 1 7 / 0 0 4 6 6 3 ( WO , A 1 )

国際公開第 2 0 1 6 / 1 6 6 0 0 2 ( WO , A 1 )

特開 2 0 1 8 - 0 6 4 0 8 6 ( J P , A )

(58)調査した分野 (Int.Cl. , DB名)

H 0 1 L 2 7 / 1 4 6

H 0 4 N 2 5 / 7 0

H 0 1 L 3 1 / 1 0 7

H 0 1 L 3 1 / 1 0

G 0 1 J 1 / 4 2

G 0 1 J 1 / 0 2