(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3811532号

(P3811532)

(45) 発行日 平成18年8月23日(2006.8.23)

(24) 登録日 平成18年6月2日(2006.6.2)

(51) Int.C1.

F 1

B23K 9/073 (2006.01)

H02M 9/00 (2006.01)B23K 9/073 560

H02M 9/00 B

請求項の数 2 (全 13 頁)

(21) 出願番号 特願平8-352657

(22) 出願日 平成8年12月13日(1996.12.13)

(65) 公開番号 特開平10-175070

(43) 公開日 平成10年6月30日(1998.6.30)

審査請求日 平成15年12月8日(2003.12.8)

(73) 特許権者 000000262

株式会社ダイヘン

大阪府大阪市淀川区田川2丁目1番11号

(72) 発明者 寺山 喜久夫

大阪市淀川区田川2丁目1番11号 株式

会社ダイヘン内

(72) 発明者 森本 慶樹

大阪市淀川区田川2丁目1番11号 株式

会社ダイヘン内

(72) 発明者 山口 悟

大阪市淀川区田川2丁目1番11号 株式

会社ダイヘン内

審査官 福島 和幸

最終頁に続く

(54) 【発明の名称】アーク加工用電源装置

## (57) 【特許請求の範囲】

## 【請求項 1】

相対向する辺を形成する一方の対をなす第1および第2の2個のスイッチング素子と相対向する辺を形成する他方の対をなす第3および第4の2組のスイッチング素子とによってブリッジ回路を形成し、前記ブリッジ回路の直流接続用端子に直流電源を接続するとともに、前記ブリッジ回路の交流接続用端子に出力変圧器の一次巻線を接続して、前記出力変圧器の二次巻線の出力を整流して直流を出力するか、前記整流した直流を導通方向が異なる2組のスイッチング素子を交互に導通・遮断を繰り返す極性切替回路によって所定の正・負比率の交流を出力するか、直流および交流を各出力端子から同時に出力するか、または予め定めた周期で切り替えて出力するアーク加工用電源装置において、

出力設定器の出力設定信号  $S_r$  と出力検出器の出力検出信号  $S_f$  とを入力とし両入力信号の比較信号  $S = S_r - S_f$  を出力する比較器と、

前記第1ないし第4のスイッチング素子からなるインバータ回路の動作周波数を決定する動作周波数基準信号を出力する基準信号発振器と、

前記動作周波数基準信号と前記比較信号  $S$  が加算された第2の入力信号との位相差に応じた位相差電圧信号を出力する位相比較器と、

前記第2の入力信号が前記位相差電圧信号であって、前記位相差電圧信号と前記比較信号  $S$  との和の加算信号  $S = S_i + S$  によって前記インバータ回路の出力電圧に対応した周波数のインバータ出力対応周波数信号を出力する電圧制御発振器と、

前記動作周波数基準信号を反転して第1の極性反転信号を出力する第1の極性反転回路

10

20

と、

前記インバータ出力対応周波数信号を反転して第2の極性反転信号を出力する第2の極性反転回路とを備えて、

前記動作周波数基準信号を前記第1のスイッチング素子の駆動信号とし、前記第2の極性反転信号を前記第2のスイッチング素子の駆動信号とし、前記インバータ出力対応周波数信号を前記第3のスイッチング素子の駆動信号とし、前記第1の極性反転信号を前記第4のスイッチング素子の駆動信号として前記第1および第2のスイッチング素子と前記第3および第4のスイッチング素子との導通期間を制御したアーク加工用電源装置。

**【請求項2】**

相対向する辺を形成する一方の対をなす第1および第2の2個のスイッチング素子と相対向する辺を形成する他方の対をなす第3および第4の2組のスイッチング素子とによってブリッジ回路を形成し、前記ブリッジ回路の直流接続用端子に直流電源を接続するとともに、前記ブリッジ回路の交流接続用端子に出力変圧器の一次巻線を接続して、前記出力変圧器の二次巻線の出力を整流して直流を出力するか、前記整流した直流を導通方向が異なる2組のスイッチング素子を交互に導通・遮断を繰り返す極性切替回路によって所定の正・負比率の交流を出力するか、直流および交流を各出力端子から同時に出力するか、または予め定めた周期で切り替えて出力するアーク加工用電源装置において、

出力設定器の出力設定信号  $S_r$  と出力検出器の出力検出信号  $S_f$  とを入力とし両入力信号の差の比較信号  $S = S_r - S_f$  を出力する比較器と、

前記第1ないし第4のスイッチング素子からなるインバータ回路の動作周波数を決定する動作周波数基準信号を出力する基準信号発振器と、

前記動作周波数基準信号と前記比較信号  $S$  が加算された第2の入力信号との位相差に応じた位相差電圧信号を出力する位相比較器と、

前記第2の入力信号が前記位相差電圧信号であって、前記位相差電圧信号と前記比較信号  $S$  との和の加算信号  $S = S_i + S$  によって前記インバータ回路の出力電圧に対応した周波数のインバータ出力対応周波数信号を出力する電圧制御発振器と、

前記動作周波数基準信号を反転して第1の極性反転信号を出力する第1の極性反転回路と、

前記インバータ出力対応周波数信号を反転して第2の極性反転信号を出力する第2の極性反転回路と、

矩形波の信号を入力して一定時間だけ遅れて立上りかつ前記矩形波の信号の立下りと同時に立上り遅延信号を出力する遅延回路とを備えて、

前記電圧制御発振器と前記第1のスイッチング素子との間または前記第1の極性反転回路と前記第4のスイッチング素子との間および前記電圧制御発振器と前記第3のスイッチング素子との間または前記第2の極性反転回路と前記第2のスイッチング素子との間に直列に前記遅延回路を挿入して、

第1のスイッチング素子および第4のスイッチング素子の一方のスイッチング素子の駆動信号を一定時間だけ遅れて立上る前記立上り遅延信号とするとともに、第3のスイッチング素子および第2のスイッチング素子のうちの前記一方のスイッチング素子の導通期間と同一方向に遅延する立上り遅延信号にして前記第1および第2のスイッチング素子と前記第3および第4のスイッチング素子との導通期間を制御したアーク加工用電源装置。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は直流電源をインバータ回路によって高周波交流に変換した後に再度整流して直流とする方式のアーク溶接、切断、プラズマアーク加工等に用いるアーク加工用電源装置の改良に関するものである。

**【0002】**

**【従来の技術】**

従来、アーク加工用電源として直流電源をインバータ回路により数KHzないし数10KHz

10

20

30

40

50

の高周波交流に変換した後に再度整流して直流出力を得る方式のものが小形、軽量化および高精度の出力制御を目的として製作されている。

#### 【0003】

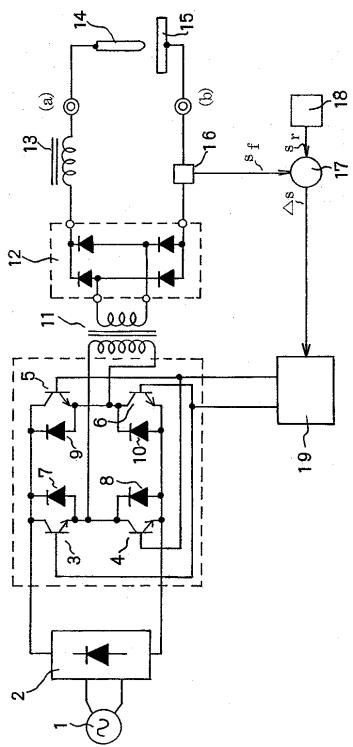

図8は上記のようにした直流出力のアーク加工用電源装置の例を示す接続図である。同図において、1は交流電源であり、単相商用交流または3相商用交流の電源が用いられる。2は交流電源1からの電力を整流して直流に変換する一次整流回路であり、簡単な平滑回路を含むこともある。3ないし6はブリッジ接続されたスイッチング素子であり、後述するPWM制御回路19からの駆動信号によって、ブリッジ回路の相対向する辺を構成するスイッチング素子3と6、またはスイッチング素子4と5がそれぞれ1対となり、これらの各対をなす2個のスイッチング素子が交互に導通と遮断とをくりかえして一次整流回路2の出力を高周波の交流に変換するインバータ回路を構成している。7ないし10はスイッチング素子3ないし6にそれぞれ逆極性で並列に接続されたダイオードであり、スイッチング素子3ないし6に逆方向の電圧が印加されるのを防止するために設けられている。11は出力変圧器であり、スイッチング素子3ないし6にて構成されるインバータ回路の出力電圧をアーク加工に適した電圧に変換する。12は出力変圧器11の出力を再度整流して直流とする二次整流回路、13は二次整流回路12と出力端子(a)との間に直列に接続された直流リアクトル、14は出力端子(a)に接続されたアーク加工用電極、15は出力端子(b)に接続された被加工物である。16は出力検出器、17は出力設定器18の出力信号Srと出力検出器16の出力信号Sfとを比較して差信号S=Sr-Sfを出力する比較器、19は比較器17の出力信号Sに応じてデューティサイクルが決定されるPWM制御回路であり、スイッチング素子3、6およびスイッチング素子4、5を交互に所定の時間幅で導通させる駆動信号を出力する。

#### 【0004】

図8の従来装置においては、交流電源1からの電力は一次整流回路2にて整流・平滑されて直流となり、スイッチング素子3ないし6にて構成されるインバータ回路にて高周波交流に変換された後に出力変圧器11にて所定の電圧となる。出力変圧器11の出力電圧は二次整流回路12にて再び直流に変換されて直流リアクトル13を経て出力端子(a)(b)からアーク加工用電極14および被加工物15に供給され、これによって両者間に加工用アークが発生する。この出力は出力検出器16にて検出されて出力設定器18の設定値と比較され、差信号Sが演算される。PWM制御回路19はこの差信号Sを入力として入力信号が減少する方向に出力パルスの導通時間率即ちデューティサイクルを調整してインバータ回路を駆動する。この結果、出力は設定値に対応した一定値に保たれる。

#### 【0005】

##### 【発明が解決しようとする課題】

上記の従来装置においては、出力設定器の設定値を変化させることによって出力電流または出力電圧を変化させるものであるが、その構造上出力設定値を小さくしてゆくときに小出力域において出力変化に跳躍点が生じ、スムーズに変化しない部分が現われる。

#### 【0006】

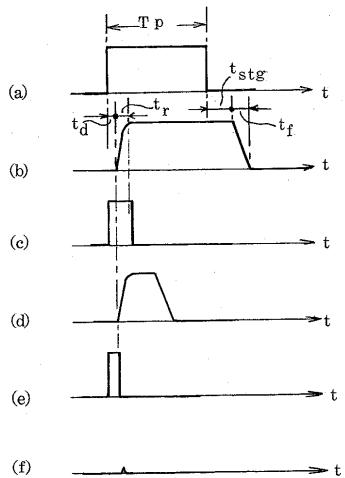

図9はこの現象を説明するための線図であり、同図(a)、(c)および(e)はPWM制御回路19からの出力信号を示し、同図(b)、(d)および(f)はこれによって導通するスイッチング素子を流れる電流の時間的变化の様子を示す。

#### 【0007】

図9に示すように、スイッチング素子は駆動信号が供給されると導通遅延時間tdの後に電流が流れ始め次第に増加して上昇時間trの後に最大電流に達する。次に駆動信号が遮断されると蓄積時間t<sub>sg</sub>の後に電流が減少を始め、さらに下降時間tfの後に完全遮断となる。これらの遅れ時間td、tr、t<sub>sg</sub>、tfはスイッチング素子に対する駆動信号の波形を工夫することによりある程度は改善することができるが完全には零にはできない。このために出力電流設定器18の設定値が大きく駆動信号の幅が図9(a)に示すようにこれらの遅れ時間に較べて広いときはあまり影響しないが、出力電流設定器の設定値を小さくしていったときに図9(c)に示すように駆動信号の幅がこれらの遅れ時間の幅

10

20

20

30

40

50

に近くなると無視できなくなる。

【0008】

即ち、この駆動信号の幅が図9(c)のような( $t_d + t_r$ )よりも若干大となるときは同図(d)に示すようにスイッチング素子の導通期間が( $t_r + t_{stg} + t_f$ )であるが図9(e)に示すように駆動信号の幅が( $t_d + t_r$ )よりも狭くなると図9(f)に示すように零へと急変することになる。

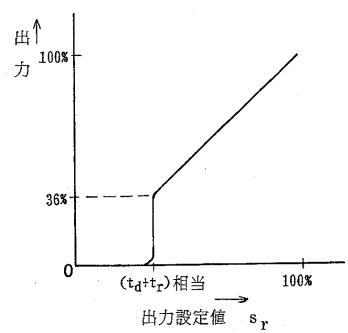

図10に出力設定の最小値近辺における設定値と出力との関係を示す。同図に示すように出力設定値が零から( $t_d + t_r$ )までは出力も零であり、( $t_d + t_r$ )を越えると急に( $t_r + t_{stg} + t_f$ )に相当する出力となる。

【0009】

ここで、インバータ回路の出力波形の半周期を考えてみると、この半周期の長さはインバータ回路の動作周波数が10KHzのときには50μs、20KHzでは25μs、40KHzでは12.5μsである。これに対して、スイッチング素子としてスイッチング用パワートランジスタを用いるときには、例えば定格容量が300A、1200Vのもので遮断時にベース電流を逆方向に流して高速化を図ったとしても

$t_d + t_r = 3 \mu s$ 、 $t_{stg} = 15 \mu s$ 、 $t_f = 3 \mu s$ 程度の値となっており、 $t_r$ を無視しても $t_{stg} + t_f = 18 \mu s$ となる。

【0010】

したがって、このようなパワートランジスタを用いるときはインバータ回路の周波数が10KHzであっても $18/50 = 0.36$ 、即ち最大出力の36%が最小出力となり、それよりも出力電流を低下させようとすると図10に示すように出力は急速に零となってしまう。このために出力調整範囲は100%~36%の範囲となり、ほとんど実用にならない範囲となる。

【0011】

この出力調整範囲は、蓄積時間 $t_{stg}$ の短いものを採用すれば広くすることが可能であるが、一般に電流容量の大きな素子ほどこの $t_{stg}$ は長くなる傾向にある。このために $t_{stg}$ の短い小容量の素子を並列にして使用することが必要となるが、並列接続のための多くの製作工数が必要となるばかりでなく、素子の合計価格も合計容量と同容量の1個の素子を使用するときに比べて高くなり、また装置も大型化してしまうことになる。

【0012】

さらに、インバータ回路の動作周波数が人間の可聴周波数内(20KHz以下)であるとインバータ回路の動作音が強烈な雑音となって作業環境を悪化させることから、インバータ回路の動作周波数は20KHz以上、望ましくは40KHz程度にまで高くすることが要求されている。このためにインバータ回路に用いるスイッチング素子としては蓄積時間 $t_{stg}$ が数桁小さいMOS・FETの比較的小容量のものを複数個並列に接続して用いなければならず、高価な高速MOS・FETが必要となるばかりでなく、並列接続のために大形化が避けられないものであった。

【0013】

【課題を解決するための手段】

本発明は上記従来装置の課題を解決するために、インバータ回路を構成する4個のスイッチング素子のうち相対向する辺を構成して各1対となって駆動されるスイッチング素子の片方を他方に対して出力設定値に対応した位相差を持って導通させるようにして、インバータ回路の出力を出力変圧器にて取り出し、スイッチング素子そのものは一定のデュエイサイクルと周波数で動作させたまま、位相差を変化させることによって出力を零から100%まで跳躍点なく連続的に変化させ得るようにしたアーケ加工用電源装置を提案したものである。

【0014】

【作用】

本発明の装置においては、導通位相が異なるブリッジ回路の相対向する辺を構成する2個のスイッチング素子が共に導通状態にあるときのみ出力が二次整流回路に現われるので、

10

20

30

40

50

インバータ回路の動作周期をスイッチング素子の各動作遅れ時間の和に等しい長さ近くまで短かく設定しても出力を 100% から 0% まで連続的に調整可能となる。このために比較的遅いスイッチング素子を用いても高い周波数で動作させることが可能となる。

#### 【0015】

##### 【発明の実施の形態】

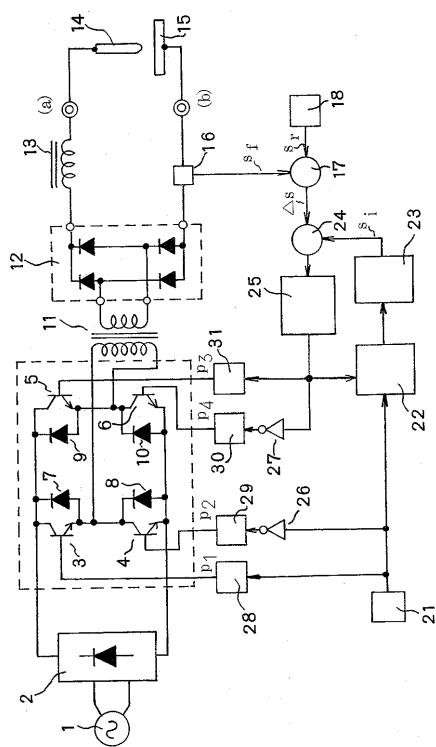

図 1 は本発明の実施の形態の例を示す接続図である。同図において、21 は基準信号発振器であり、導通時間率 (ON デューティ) が約 50% の矩形波を出力し、スイッチング素子 3 ないし 6 からなるインバータ回路の動作周波数を決定する。22 は位相比較器であり 10 2 つの入力信号の位相差に応じた電圧信号を出力する公知の乗算器形、ディジタル形、位相周波数比較器などの位相比較器が用いられる。23 はローパスフィルタであり、位相比較器 22 の出力のうち高周波成分を除去する。24 は加算器、25 は電圧制御発振器、26, 27 は入力信号のローレベルをハイレベルにまたハイレベルをローレベルにそれぞれ反転する極性反転回路、28 ないし 31 は入力信号を必要に応じて増幅して各スイッチング素子を駆動する増幅器である。その他は図 9 に示した従来装置と同機能のものに同符号を付してある。

#### 【0016】

基準信号発振器 21 の出力は直接増幅器 28 に入力されてブリッジ回路の相対向する辺を構成する一方の対となるスイッチング素子 3 と 6 とのうち一方の素子 3 を駆動し、同時に極性反転回路 26 にて極性反転されて増幅器 29 に入力されてブリッジ回路の相対向する辺を構成する他方の対となるスイッチング素子 4 と 5 とのうちの一方の素子 4 を駆動する。さらに基準信号発振器 21 の出力はまた電圧制御発振器 25 の出力信号と位相比較器 22 にて比較されて両入力信号の位相差に相当する電圧が演算される。この位相比較器 22 の出力はローパスフィルタ 23 にて高周波成分が除去されて加算器 24 の一方の入力となる。一方、出力設定器 18 の設定値  $S_r$  は出力検出器 16 の出力信号  $S_f$  と比較器 17 にて比較されて差信号  $S = S_r - S_f$  となり、加算器 24 の他方の入力となる。加算器 24 において、ローパスフィルタ 23 の出力と比較器 17 の出力とが加算されて電圧制御発振器 25 に入力され、電圧制御発振器 25 は入力電圧に対応した周波数でかつ ON デューティが約 50% の矩形波状のパルス信号を出力する。この電圧制御発振器 25 の出力信号は直接増幅器 31 に入力されてスイッチング素子 4 に対向する辺をなす他方のスイッチング素子 5 を駆動すると同時に極性反転回路 27 にて極性が反転された後に増幅器 30 に入力されてスイッチング素子 3 に対向する辺をなす他方のスイッチング素子 6 を駆動する。また電圧制御発振器 25 の出力は位相比較器 22 にフィードバックされる。

#### 【0017】

上記において、出力検出器 16、比較器 17、出力設定器 18、基準信号発振器 21、位相比較器 22、ローパスフィルタ 23、加算器 24、電圧制御発振器 25、極性反転回路 26 および 27 は位相制御回路を構成している。

#### 【0018】

次に図 1 の位相制御回路の動作について説明する。図 1 において、電圧制御発振器 25 の発振周波数  $f$  が基準信号発信器 21 の出力信号と比較されて両信号の位相の差に応じた電圧が位相比較器 22 とローパスフィルタ 23 とによって算出される。いま仮に電圧制御発信器 25 がある周波数で発信していたとしてこの発信周波数  $f$  が基準信号発信器 21 の出力信号  $f^{ref}$  よりも低いかまたは位相が遅れていたときは、この差に相当するだけローパスフィルタ 23 の出力信号  $S_i$  が増加する。この信号  $S_i$  は誤差信号  $S$  と加算器 24 で加算されて和の信号  $S + S_i$  となりこの信号の増加分に相当するだけ電圧制御発信器 25 の発信周波数が高くなる。この高くなった電圧制御発信器 25 の出力信号が基準信号発信器 21 の発信周波数よりもまだ低いか位相が遅れているときは、同様の経過により電圧制御発信器 25 の発信周波数をより高くするように動作を続ける。一方、逆に電圧制御発信器 25 の発信周波数が基準信号発信器 21 の発信周波数よりも高いかまたは位相が進んでいるときは、その差が位相差検出器 22 にて算出されて、その差に相当する電圧がローパスフィルタ 23 を介して信号  $S_i$  となり、加算器 24 にて誤差信号  $S$  と加算され 40 50

る結果、電圧制御発信器 25 に入力される信号  $S + Si$  は低くなり、電圧制御発信器 25 の発信周波数はその分だけ低下する。このようにして、電圧制御発信器 25 の出力信号が基準信号発信器 21 の出力信号  $f$ 。に対して  $S$  だけ変化した位相となった時に安定し、23 の出力はその時点の出力状態に落ち着くことになる。

#### 【0019】

上記の結果、電圧制御発振器 25 は基準信号発振器 21 の出力周波数と同一の周波数でかつ差信号  $S$  に相当する分だけ位相がずれた信号を出力することになり、この差信号  $S$  は基準信号発振器 21 の出力信号  $S_r$  と出力検出器 16 の出力信号  $S_f$  との差であるから、結局この信号と基準信号発振器 21 の出力信号とによって增幅器 28 ないし 31 を介してスイッチング素子 3 ないし 6 を駆動すると出力変圧器 11 には出力設定器 21 の設定値  $S_r$  に対応した出力が現われることになる。

#### 【0020】

図 2 は図 1 の装置の動作を説明するための線図である。同図において (a) は基準信号発振器 21 の出力、(b) はこれを極性反転回路 26 によって反転した出力、(c) は電圧制御発振器 25 の出力信号、(d) はこれを極性反転回路 27 によって反転した出力、(e) は增幅器 28 の出力、(f) は增幅器 29 の出力、(g) は增幅器 30 の出力、(h) は增幅器 31 の出力、(i) は出力変圧器 11 の出力をそれぞれ時間の経過とともに示したものである。

#### 【0021】

図 1 および図 2 に示すように、スイッチング素子駆動信号  $P_1, P_2$  と  $P_3, P_4$  とは出力設定器 18 の設定値  $S_r$  に対応した位相 だけずれた信号となる。この信号  $P_1$  ないし  $P_4$  にて導通期間が制御されるブリッジ接続されたスイッチング素子 3 ないし 6 はブリッジ回路を構成する相対向する辺を構成する各 1 対のスイッチング素子 3 と 6 または 4 と 5 とがそれ共に導通している期間のみ出力変圧器に電力が供給されて、2 次整流回路 12 に出力が現われ、これが整流されて直流リアクトル 13 にて平滑されて出力端子 (a) 、(b) 間に現われることになる。また図 1 の装置の場合、2 次整流回路 12 がブリッジ接続されたダイオードからなる両波整流回路であるのでこのブリッジ接続されたダイオードがフライホイールダイオードを兼ねて、リアクトル 13 とともに断続する出力変圧器の出力を平滑する役割を果している。

#### 【0022】

また上記から判るようにインバータ回路を構成するスイッチング素子 3 ないし 6 それぞれの ON デューティと総合出力とは無関係であり、総合出力はブリッジ回路の相対向する辺を構成するスイッチング素子の導通する位相差のみによって決定される。それ故、各スイッチング素子の ON デューティは常に最大となるように基準信号発振器 21 の出力波形も ON デューティを約 50 % にしてある。このためにスイッチング素子 3 と 6 および 4 と 6 に供給する駆動信号も単に極性反転回路 26, 27 によって極性反転させるだけでよいので、従来のような 2 相分離回路が不要となり、回路が簡単となる。この結果、総合出力として最大出力を指定したときには各スイッチング素子に実際に電流が流れる期間も 50 % (即ち、導通期間の全域に等しい期間) に達し、スイッチング素子の電流容量を有效地に利用できる。

#### 【0023】

また、図 1 に示した実施の形態の例において、出力検出器として出力電流を検出してこれを設定値と比較するときは、出力電流を設定値に保つ定電流特性のアーク加工用電源装置が得られ、また出力検出器として出力電圧を検出するものを用いてこれを設定値と比較すれば、出力電圧を設定値に保つ定電圧特性のアーク加工用電源装置が得られる。さらには出力電流、出力電圧ともに検出してそれぞれ設定値と比較し、両方の差信号に所定の係数を乗じて加算した信号によってスイッチング素子を導通する位相差を制御するときは所定の出力電圧・電流特性を有するアーク加工用電源装置が得られる。

#### 【0024】

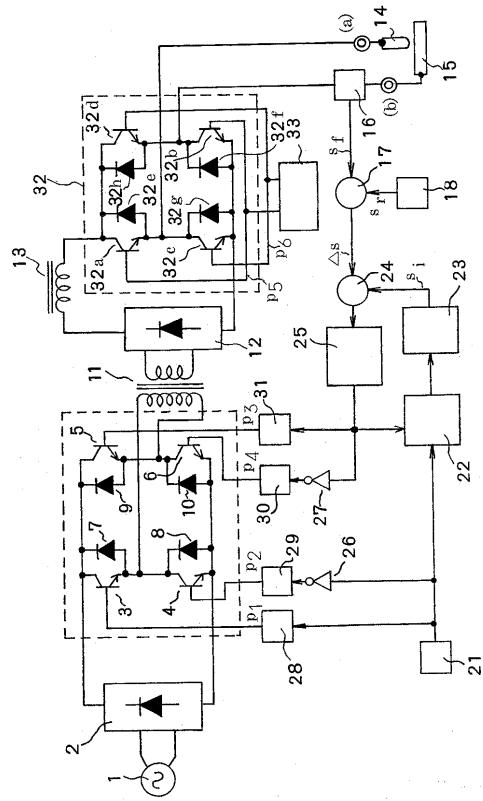

図 3 は本発明の別の実施の形態の例を示す接続図である。同図の実施例においては図 1 に

10

20

30

40

50

示した実施例に加えて、直流リアクトルと出力端子との間に出力極性を切りかえるためのブリッジ接続されたスイッチング素子からなる極性切替回路32および極性切替制御回路33を設けたものである。ここで極性切替回路32は極性切替制御回路33が信号P<sub>5</sub>のみを出力するときはスイッチング素子32a、32bのみが導通し、出力端子(a)側が正の極性の直流出力となり、信号P<sub>6</sub>のみを出力するときはスイッチング素子32c、32dのみが導通して、出力端子(b)側が正の極性の直流出力となる。さらに信号P<sub>5</sub>とP<sub>6</sub>とを所定のくりかえし周期とデューティサイクルとによって交互に出力するときはスイッチング素子32a、32bまたはスイッチング素子32c、32dが交互に導通・遮断をくりかえし、所定の正・負比率の交流出力が得られることになる。この場合、直流出力、交流出力にかかわらず、導通期間の一部にスイッチング素子が不完全飽和となる期間を設ければ、その期間を低電流または低電圧出力期間とし、完全飽和期間を高電流または高電圧出力期間としたパルス波形を得ることができる。

#### 【0025】

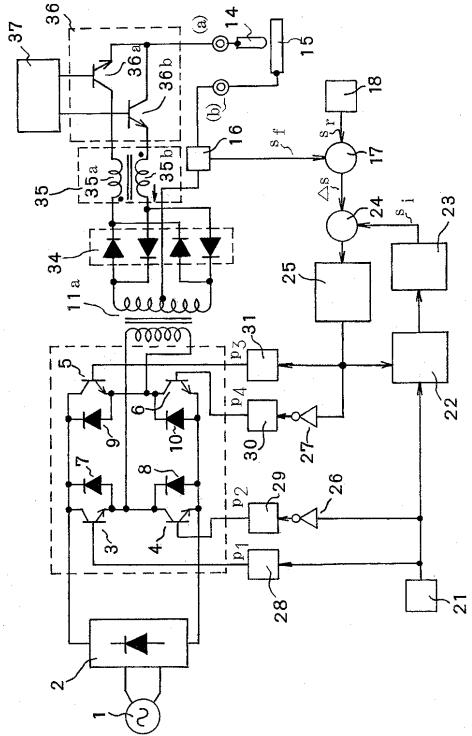

図4は図3に示した装置の変形例に相当する実施の形態の例であり、出力変圧器11aとしてセンタータップ付の2次巻線を用意し、このセンタータップを出力端子(b)に接続してある。34は二次整流回路であり、直列接続された出力変圧器の両端にそれぞれ正・負両出力を得るためのセンタータップ式両波整流回路である。35は直流リアクトルであり、2つの巻線35a、35bが共通の鉄心に巻かれており、かつ両巻線は図中に・印で示すようにそれぞれに流れる2次整流回路34の出力電流によって共有する鉄心に同一方向の磁束を生ずる極性にその巻方向が定められている。36は極性切替回路であり、互いに逆方向に電流を流す極性に定められたスイッチング素子36aと36bとからなる。37は極性切替制御回路であり、図3に示した実施例の極性切替制御回路33と同機能のものである。

#### 【0026】

図4の装置においては、出力変圧器11aの出力は二次整流回路34にて両波整流されてかつ正・負両極性の直流出力となってリアクトル巻線35a、35bを経て極性切替回路36のスイッチング素子36a、36bに供給される。いま極性切替回路36のスイッチング素子36aが導通していると出力端子(a)側、即ち電極14が正となる極性の出力が発生し、電流はリアクトル35の巻線35a、極性切替回路36のスイッチング素子36a、出力端子(a)、電極14、加工アーク、被加工物15、出力端子(b)、出力変圧器11aの2次巻線のセンタータップの経路を流れる。次にスイッチング素子36aが遮断すると同時にスイッチング素子36bを導通させると、それまでリアクトル巻線35aに流れていた電流は急減しようとするが電磁誘導により共通鉄心に巻かれているリアクトル巻線35bはこの電流の急減を防げる方向の電圧を図中に矢印で示す極性に発生する。この誘起電圧の極性は新たに導通し始めるスイッチング素子36bの導通によって流れ始める電流の極性と同じ極性である。このために、スイッチング素子36aを遮断し同時にスイッチング素子36bを導通させると、回路にはこの切替の直前に流れていた電流と同じ値の電流が先とは逆の極性の被加工物15から電極14に向う方向に流れ始める。この結果電極14から被加工物15に向って流れていた電流は急峻にその極性が反転して被加工物15から電極14に向って流れることになる。スイッチング素子36bが導通している状態から遮断し、スイッチング素子36aが導通するときも同様に出力電流はその絶対値が同じで極性のみ反転した電流に急峻に変化することになる。この結果、出力電流の極性反転に際してアークが一旦消滅した後の再点弧が容易となり、交流アーク加工が安定に継続できるものである。

#### 【0027】

なお、上記説明においては電極と被加工物のみを対象として出力するアーク加工用電源装置に本発明を適用する場合についてのみ説明したが、出力電圧の一部をパイロットアーク用電極に導いて加工用アークの起動に先立ち電極との間にパイロットアークを発生させ、このパイロットアークを被加工物に移行させて加工を行うプラズマアーク加工用電源にも本発明が適用できるのはもちろんである。

## 【0028】

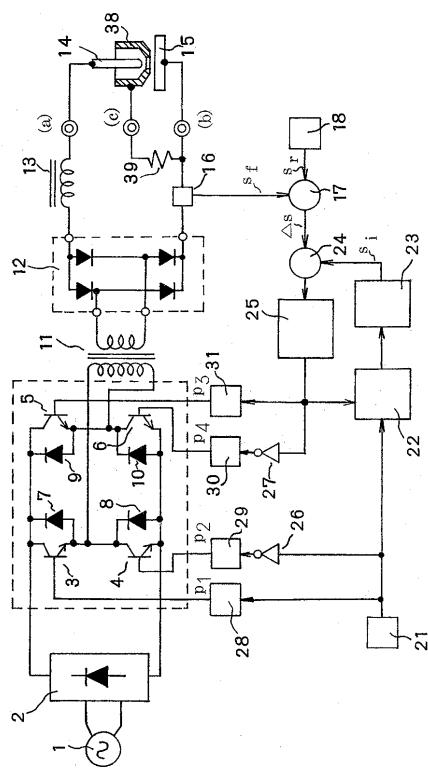

図5は、プラズマアーク加工用電源装置に本発明を適用したときの実施の形態の例を示す接続図である。同図において39はパイロットアーク電流制限用抵抗器であり、二次整流回路12の正出力端子とパイロットアーク出力用端子(c)との間に接続されている。38はパイロットアーク用電極であり、加工用電極14の周囲にプラズマ生成ガスを供給し、先端の狭い開口部からアークによってプラズマ化されたガスを高速で噴出させるためのノズルを共用しているので一般にノズル電極と呼ばれている。その他の構成要素は図1に示した装置と同機能のものに同符号を付してあるので説明は省略する。

## 【0029】

図5の装置において、図示を省略した高周波点弧手段により加工用電極14とパイロットアーク用電極(ノズル電極)38との間に抵抗器39によって制限された小電流のアーク(パイロットアーク)を点弧し、同時にノズル内にプラズマ生成ガスを供給すると、このプラズマ生成ガスがパイロットアークによって電離してイオン化され、このイオン化されたガスが加工用電極14とノズル電極38とを被加工物15に接近させることによって被加工物に接触すると加工用電極14と被加工物15との間の絶縁が低下するためにアークが発生する。このアークは出力電流設定器18にて設定された値にまで増加し、プラズマアーク加工が行なわれる。

## 【0030】

上記各実施例においては、各スイッチング素子3ないし6には各增幅器28ないし31が入力信号を全く遅れなく伝達するものとして説明した。しかし、通常スイッチング素子は導通遅れ時間よりも遮断遅れ時間の方が長い。このために、例えばスイッチング素子3に対する導通駆動信号を遮断すると同時にスイッチング素子4に導通駆動信号を与えると、遮断遅れ時間が長い分だけ両スイッチング素子が共に導通する期間が発生する可能性があり、もしこのような事態が発生すると直流電源の出力がこれらによって完全短絡されることになり、スイッチング素子が破壊されるのみならず、直流電源にも大きな負担をかけて、障害発生の原因となる。これを防止するためには、直流電源2とブリッジ回路との間に直流リクトルを追加挿入することにより短絡電流を抑制する方法を採用するか、またはスイッチング素子の遮断遅れ時間だけ次のスイッチング素子に対する導通駆動信号の立ち上がりを遅らせる方法を採用すればよい。このうち、直流リクトルを挿入する方法は例をあげるまでもなく、容易に理解できるので説明を省略し、駆動信号の立ち上がりを遅らせるものについて説明する。

## 【0031】

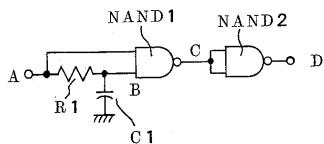

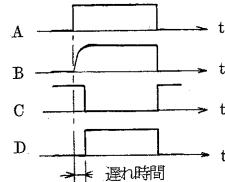

図6は、増幅器28ないし31の入力側または出力側に直列に入れて、伝達する信号の立ち上がり時間のみを遅らせる遅延回路の例を示す接続図である。同図においてAは入力端子、Dは出力端子であり、R1は抵抗器、C1はコンデンサ、NAND1, NAND2はそれぞれNANDゲートである。同図の遅延回路の動作を図7の線図と共に説明する。図7において(A)は図6の入力端子(A)の信号変化を示し、(B)は図6の(B)点の、(C)は(C)点の、(D)は出力信号のそれぞれ変化を示す。

## 【0032】

図6および図7において、矩形状の入力信号が立ち上ると、NANDゲートNAND1の一方の入力端子の信号レベルは直ちに立ちあがるが他方の入力端子の信号レベルは抵抗器R1およびコンデンサC1によって定まる時定数に従って図7(B)のように上昇してゆく。この(B)点の信号レベルがNANDゲートNAND1のしきい値に達するまではNANDゲートNAND1の出力はハイレベルのままであり、これを入力とするNANDゲートNAND2の出力はローレベルを保っている。コンデンサC1の充電が進行して(B)点の信号レベルがNANDゲートNAND1のしきい値を超えるとNANDゲートNAND1の出力は反転してローレベルとなり、これに伴ってNANDゲートNAND2の出力はハイレベルとなる。一方、入力端子の信号レベルが立ち下ったときはNANDゲートNAND1の一方の入力信号が直ちに立下るので(B)点のレベルにかかわらずNANDゲートNAND1の出力は直ちにハイレベルとなり、出力端子Dの出力レベルも直ちにローレ

10

20

30

40

50

ベルとなる。この結果、入力信号の立上りから抵抗器 R 1 とコンデンサ C 1 によって定まる一定時間だけ遅れて立上りかつ入力信号の立下りと同時に立下る出力信号が得られる。この立上り遅れ時間を各実施例に示したスイッチング素子 3 ないし 6 の遮断遅れ時間と導通遅れ時間の差の時間より若干長く設定しておけば、スイッチング素子 3 と 4 またはスイッチング素子 5 と 6 とが同時に導通してしまうことが防止できる。

【0033】

【発明の効果】

上記の通り、本発明のアーカ加工用電源装置は、ブリッジ接続された 4 個のスイッチング素子のうち対をなす 2 個の各スイッチング素子をお互いに出力設定値に対応した位相差をもって ON - OFF 制御することによって出力調整を実現するものであり、スイッチング素子の導通遮断遅れ時間に無関係に出力が決定されるので、比較的動作速度の遅い大容量のスイッチング素子を用いても出力調整の範囲を 0 ~ 100 % まで連続的に変化させることができるとなる。しかも各スイッチング素子の ON デューティは常に一定の約 50 % であるのでスイッチング素子の電流容量を最大限に利用できるものである。さらにまた動作速度の遅いスイッチング素子は大容量のものでも安価であるので多数を並列運転する必要がなく、安価でかつ小形の装置を得ることができる。

10

【図面の簡単な説明】

【図 1】 本発明の装置の実施の形態の例を示す接続図である。

【図 2】 図 1 の装置の動作を説明するための線図である。

【図 3】 本発明の装置の別の実施の形態の例を示す接続図である。

20

【図 4】 本発明の装置の別の実施の形態の例を示す接続図である。

【図 5】 本発明の装置の別の実施の形態の例を示す接続図である。

【図 6】 本発明の装置に用いるスイッチング素子駆動パルスの立上り遅延回路の例を示す接続図である。

【図 7】 図 6 の遅延回路の動作を説明するための線図である。

【図 8】 従来の装置の例を示す接続図である。

【図 9】 図 8 の従来装置における現象を説明するための線図である。

【図 10】 図 8 の従来装置の出力設定を 0 から 100 % の間で変化させたときの設定値と出力との関係を示す線図である。

【符号の説明】

30

1 交流電源

2 一次整流回路

3 スイッチング素子

4 スイッチング素子

5 スイッチング素子

6 スイッチング素子

7 ないし 10 ダイオード

32e ないし 32h ダイオード

11、11a 出力変圧器

12、34 二次整流回路

40

13、35 直流リアクトル

14 加工用電極

15 被加工物

16 出力検出器

17 比較器

18 出力設定器

19 PWM 制御回路

20 インバータ制御回路

21 基準信号発振器

22 位相比較器

50

- 2 3 ローパスフィルタ

2 4 加算器

2 5 電圧制御発振器

2 6、2 7 極性反転回路

2 8ないし3 1 増幅器

3 2、3 6 極性切替回路

3 2 aないし3 2 d 極性切替用スイッチング素子

3 6 a、3 6 b 極性切替用スイッチング素子

3 3、3 7 極性切替制御回路

3 8 パイロットアーク用電極（ノズル電極）

3 9 電流制限用抵抗器

- N A N D 1、N A N D 2 N A N D ゲート 10

N A N D 1、N A N D 2 N A N D ゲート

【図1】

【図3】

【図4】

【図5】

【図6】

【図7】

【 図 8 】

【 図 9 】

【 図 1 0 】

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

B23K 9/073

H02M 9/00

H02M 7/42 ~ 7/98