(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6164722号

(P6164722)

(45) 発行日 平成29年7月19日(2017.7.19)

(24) 登録日 平成29年6月30日(2017.6.30)

|                         |                    |

|-------------------------|--------------------|

| (51) Int.Cl.            | F 1                |

| HO 1 L 23/12 (2006.01)  | HO 1 L 23/12 301 C |

| HO 1 L 25/00 (2006.01)  | HO 1 L 25/00 B     |

| HO 1 L 21/822 (2006.01) | HO 1 L 27/04 E     |

| HO 1 L 27/04 (2006.01)  | HO 3 F 3/24        |

| HO 3 F 3/24 (2006.01)   |                    |

請求項の数 9 (全 11 頁)

(21) 出願番号 特願2012-273958 (P2012-273958)

(22) 出願日 平成24年12月14日 (2012.12.14)

(65) 公開番号 特開2014-120582 (P2014-120582A)

(43) 公開日 平成26年6月30日 (2014.6.30)

審査請求日 平成27年12月11日 (2015.12.11)

(73) 特許権者 000154325

住友電工デバイス・イノベーション株式会

社

神奈川県横浜市栄区金井町1番地

(74) 代理人 100087480

弁理士 片山 修平

(72) 発明者 井上 真吾

神奈川県横浜市栄区金井町1番地 住友電

工デバイス・イノベーション株式会社内

審査官 梅本 章子

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

入力端子と、

出力端子と、

前記入力端子と前記出力端子との間の領域に配置された実装基板と、

前記実装基板上の前記入力端子と前記出力端子との間の領域に配置された半導体チップと、

前記実装基板上の前記入力端子と前記半導体チップとの間の領域に配置されるとともに

、前記入力端子と前記半導体チップとに電気的に接続されてなる回路部品と、

一端が前記半導体チップの上面に設けられた出力パッドに接続され、他端が前記出力端

子に接続された第1ボンディングワイヤと、を具備し、

前記半導体チップと前記出力端子との距離は、前記入力端子と前記半導体チップとの距

離以上であり、かつ前記実装基板上の前記半導体チップと前記出力端子の間の領域は、回

路部品が搭載されない領域であることを特徴とする半導体装置。

## 【請求項 2】

複数の前記半導体チップが、前記実装基板上に配置されていることを特徴とする請求項

1記載の半導体装置。

## 【請求項 3】

前記出力端子は、前記半導体装置の外部の整合回路と接続されることを特徴とする請求

項1又は2記載の半導体装置。

10

20

**【請求項 4】**

前記実装基板は金属により形成されていることを特徴とする請求項 1 から 3 いずれか一項記載の半導体装置。

**【請求項 5】**

前記第 1 ボンディングワイヤの長さは 1.5 mm 以上であることを特徴とする請求項 1 から 4 いずれか一項記載の半導体装置。

**【請求項 6】**

前記実装基板の一辺の長さは 3 mm 以上であることを特徴とする請求項 1 から 5 いずれか一項記載の半導体装置。

**【請求項 7】**

前記回路部品は整合回路部品であることを特徴とする請求項 1 に記載の半導体装置。 10

**【請求項 8】**

前記半導体チップと前記出力端子との距離は、前記入力端子と前記半導体チップとの距離より大きい請求項 1 に記載の半導体装置。

**【請求項 9】**

前記実装基板の前記半導体チップ、前記回路部品、前記第 1 ボンディングワイヤおよび前記回路部品が搭載されていない領域は樹脂封止されてなる請求項 1 に記載の半導体装置。

。

**【発明の詳細な説明】**

20

**【技術分野】****【0001】**

本発明は半導体装置に関する。

**【背景技術】****【0002】**

近年、携帯電話などの無線通信システムにおいて電力の高出力化が望まれている。これに伴い、例えば基地局の電力増幅器などの電子装置に使用される半導体装置にはより高出力化が要求されている。従来から、LDMOS (Laterally Diffused MOS) が使用されていた。半導体装置の小型化のため窒化物半導体を含む半導体装置も使用されている。良好な特性を得るために、入力インピーダンス及び出力インピーダンスの整合を行うことが求められる。また半導体装置の動作に伴う発熱により温度が上昇する。温度上昇により半導体装置の特性が劣化するため、放熱性も重要である。電子装置には低コスト化及び小型化が求められる。特許文献 1 には、入力回路基板及び出力回路基板を備える発明が記載されている。 30

**【先行技術文献】****【特許文献】****【0003】**

【特許文献 1】特開 2010-186965 号公報

**【発明の概要】****【発明が解決しようとする課題】**

40

**【0004】**

しかし、インピーダンス整合のための整合回路が大型化及び複雑化することがある。この結果、電子装置の低コスト化及び小型化が困難となる。本願発明は、上記課題に鑑み、良好な特性及び放熱性を得ることができ、低コスト化及び小型化可能な半導体装置を提供することを目的とする。

**【課題を解決するための手段】****【0005】**

本発明は、入力端子と、出力端子と、前記入力端子と前記出力端子との間の領域に配置された実装基板と、前記実装基板上の前記入力端子と前記出力端子との間の領域に配置された半導体チップと、前記入力端子と前記半導体チップとの間の領域に配置されるととも

50

に、前記入力端子と前記半導体チップとに電気的に接続されてなる回路部品と、前記半導体チップの出力パッドと、前記出力端子とを直接に接続する第1ボンディングワイヤと、を具備し、前記半導体チップと前記出力端子との距離は、前記入力端子と前記半導体チップとの距離以上であり、かつ前記実装基板上の前記半導体チップと前記出力端子の間の領域は、回路部品が搭載されない領域である。

【0006】

上記構成において、複数の前記半導体チップが、前記実装基板上に配置されている構成とすることができます。

【0007】

上記構成において、前記出力端子は、前記半導体装置の外部の整合回路と接続される構成とすることができます。

【0008】

上記構成において、前記実装基板は金属により形成されている構成とすることができます。

【0009】

上記構成において、前記出力端子は、前記半導体装置の外部の整合回路と接続される構成とすることができます。

【0010】

上記構成において、前記第1ボンディングワイヤの長さは1.5mm以上である構成とすることができます。

【0011】

上記構成において、前記実装基板の一辺の長さは3mm以上である構成とすることができます。

【発明の効果】

【0012】

本発明によれば、良好な特性及び放熱性を得ることができ、低コスト化及び小型化可能な半導体装置を提供することが可能となる。

【図面の簡単な説明】

【0013】

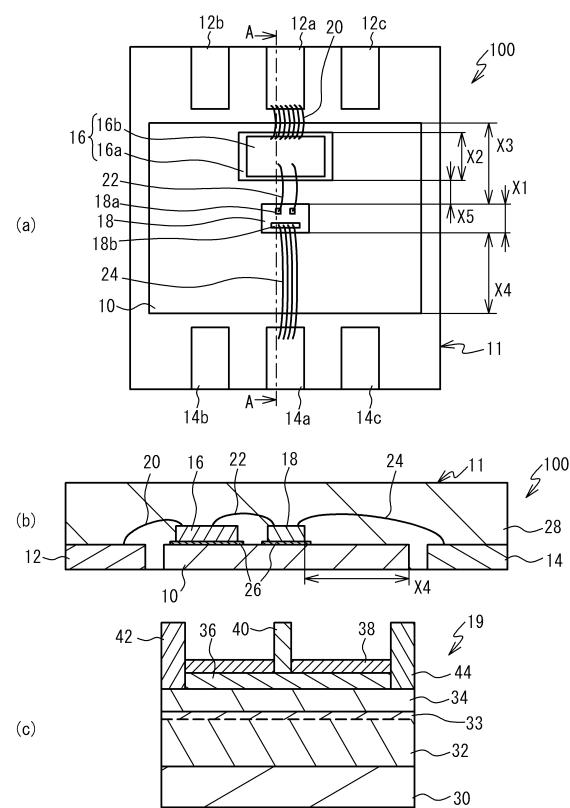

【図1】図1(a)は実施例1に係る半導体装置を例示する平面図である。図1(b)は半導体装置を例示する断面図である。図1(c)はHEMTを例示する断面図である。

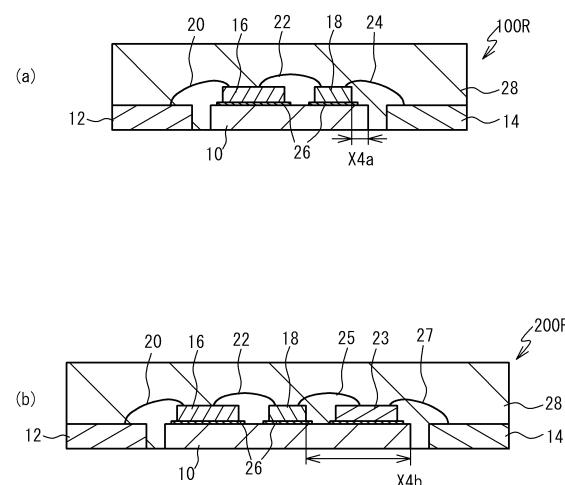

【図2】図2(a)は比較例1に係る半導体装置を例示する断面図である。図2(b)は比較例2に係る半導体装置を例示する断面図である。

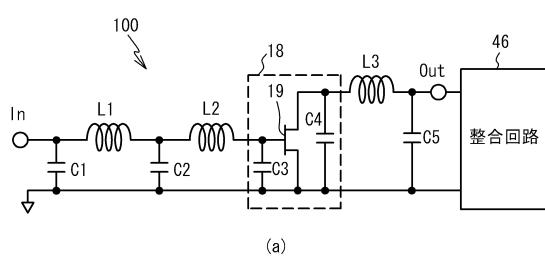

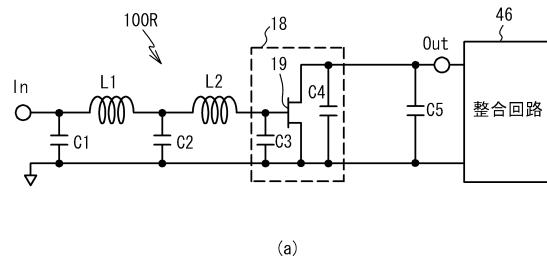

【図3】図3(a)は半導体装置の等価回路を例示する回路図である。図3(b)は実施例1における出力インピーダンスの整合を例示するスミスチャートである。

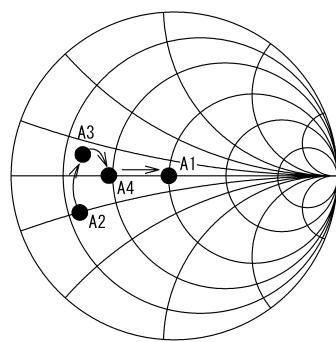

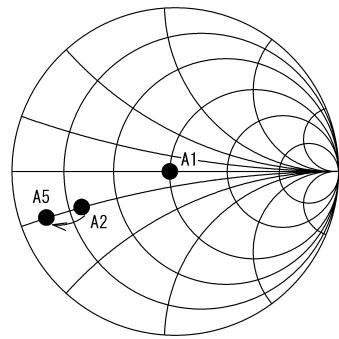

【図4】図4(a)は半導体装置の等価回路を例示する回路図である。図4(b)は比較例1における出力インピーダンスの整合を例示するスミスチャートである。

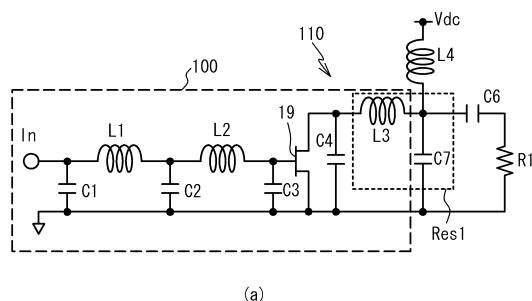

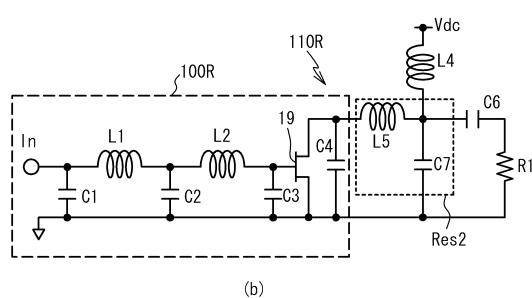

【図5】図5(a)及び図5(b)は半導体装置を用いたE級パワーアンプを例示する回路図である。

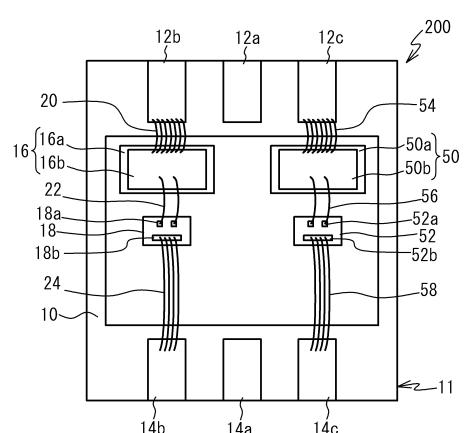

【図6】図6は実施例2に係る半導体装置を例示する平面図である。

【発明を実施するための形態】

【0014】

本発明の実施例について説明する。

【実施例1】

【0015】

実施例1は出力側のボンディングワイヤを長くする例である。図1(a)は実施例1に係る半導体装置100を例示する平面図である。図1(b)は半導体装置100を例示する断面図であり、図1(a)の線A-Aに沿った断面を図示している。

【0016】

図1(a)及び図1(b)に示すように、半導体装置100は、パッケージ11、整合

10

20

30

40

50

回路部品 16 及び半導体チップ 18 を有する。パッケージ 11 は、ダイパッド 10 (実装基板)、入力端子 12a ~ 12c、及び出力端子 14a ~ 14c を含む。半導体チップ 18 は、入力端子 12a に入力される高周波信号を増幅するアンプとして機能する。増幅された高周波信号は出力端子 14a から出力される。

【 0017 】

ダイパッド 10 は入力端子 12a と出力端子 14a との間に設けられている。整合回路部品 16 及び半導体チップ 18 は、導電性を有する接着剤 26 によりダイパッド 10 の上面に搭載されている。整合回路部品 16 は、入力端子 12a と半導体チップ 18 との間に位置する。図 1 (b) に示すように、整合回路部品 16 は、基板 16a、基板 16a の上面に設けられた電極のパターン 16b、及び図示しない裏面電極パターンを備え、キャパシタとして機能する。基板 16a は例えばアルミナ ( $Al_2O_3$ ) などの絶縁体により形成されている。パターン 16b は例えば金 (Au) などの金属により形成されている。整合回路部品 16 は、その表面にインダクタのパターンを備える構造でもよい。このような整合回路部品 16 は、基板 16a のような平面部材が採用され、半導体装置 100 の内部において所定の面積を占有する。半導体チップ 18 は、入力パッド 18a 及び出力パッド 18b を含む。また半導体チップ 18 には後述する H E M T (High Electron Mobility Transistor: 高電子移動度トランジスタ) が形成されている。入力端子 12b 及び 12c は入力端子 12a の両側に設けられている。出力端子 14b 及び 14c は出力端子 14a の両側に設けられている。入力端子 12b 及び 12c、出力端子 14b 及び 14c については後述する。

10

20

【 0018 】

入力端子 12a とパターン 16b とはボンディングワイヤ (第 2 ボンディングワイヤ) 20 により、電気的に接続されている。パターン 16b と入力パッド 18a とはボンディングワイヤ 22 により電気的に接続されている。出力パッド 18b と出力端子 14a とはボンディングワイヤ 24 (第 1 ボンディングワイヤ) により電気的に接続されている。半導体チップ 18 の下面に設けられた不図示の接地パッドは、ダイパッド 10 と接続されている。ボンディングワイヤ 20、22 及び 24 は例えば Au などの金属により形成されている。封止部 28 は整合回路部品 16 及び半導体チップ 18 を封止する。ダイパッド 10、入力端子 12a 及び出力端子 14a は、例えば銅 (Cu) とモリブデン (Mo) との積層構造、及び Cu を主成分とする合金など、金属により形成されている。接着剤 26 は例えば銀 (Ag) などの導電体を主成分とする。封止部 28 は例えばエポキシ樹脂などの樹脂により形成されている。整合回路部品 16 及びボンディングワイヤ 20 は入力インピーダンスを整合する。

30

【 0019 】

入力端子 12a と出力端子 14a とが並ぶ方向 (図 1 (a) の上下方向) における、半導体チップ 18 の長さ X1 は例えば 0.5 mm である。半導体チップ 18 の図 1 (a) における横方向の一辺は例えば 0.8 mm である。整合回路部品 16 の長さ X2 は例えば 0.85 mm である。ダイパッド 10 の入力端子 12a 側の端部から、半導体チップ 18 の入力端子 12a 側の端部までの距離 X3 は例えば 1.5 mm である。半導体チップ 18 の出力端子 14a 側の端部から、ダイパッド 10 の出力端子 14a 側の端部までの距離 X4 は例えば 1.6 mm である。半導体チップ 18 から整合回路部品 16 までの距離 X5 は例えば 0.3 mm である。ダイパッド 10 の他の一辺は例えば 5.3 mm である。ダイパッド 10 の面積は、例えば半導体チップ 18 の面積に対し 10 倍以上である。ボンディングワイヤ 20 の長さは例えば 1 mm である。ボンディングワイヤ 22 の長さは例えば 1 mm である。ボンディングワイヤ 24 の長さは例えば 2 mm である。1 本のボンディングワイヤの直径は例えば 25  $\mu m$  である。

40

【 0020 】

図 1 (c) は H E M T 19 を例示する断面図である。図 1 (c) に示すように、H E M T 19 では、下から順に基板 30、チャネル層 32、電子供給層 34、キャップ層 36、及び絶縁層 38 が積層されている。キャップ層 36 の上面にゲート電極 40 が設けられて

50

いる。電子供給層 3 4 の上面にソース電極 4 2 及びドレイン電極 4 4 が設けられている。HEMT 1 9 は半導体チップ 1 8 に含まれる。ゲート電極 4 0 は不図示の配線により入力パッド 1 8 a と電気的に接続されている。ソース電極 4 2 は不図示のビア配線などにより、ダイパッド 1 0 と電気的に接続されている。ドレイン電極 4 4 は出力パッド 1 8 b と電気的に接続されている。基板 3 0 は例えば炭化シリコン (SiC) 、チャネル層 3 2 及びキャップ層 3 6 は例えば窒化ガリウム (GaN) 、電子供給層 3 4 は例えば窒化アルミニウムガリウム (AlGaN) 、絶縁層 3 8 は例えば窒化シリコン (SiN) により形成されている。ソース電極 4 2 及びドレイン電極 4 4 は、電子供給層 3 4 に近い方からチタン層及びアルミニウム層 (Ti / Al) を積層したオーミック電極である。ゲート電極 4 0 は、キャップ層 3 6 に近い方から例えばニッケル層及び金層 (Ni / Au) を積層した電極である。チャネル層 3 2 と電子供給層 3 4 との界面には二次元電子ガス 3 3 が発生する。HEMT 1 9 を含む半導体チップ 1 8 の動作電力は例えば 20W である。

#### 【0021】

実施例 1 によれば、距離 X 3 と同等又は X 3 以上の距離 X 4 を確保することにより、ダイパッド 1 0 が大きくなる。距離 X 4 の領域は、整合回路部品 1 6 が搭載される距離 X 3 の領域以上の大きさを有し、かつキャパシタなどの整合回路部品が搭載されていない。つまり距離 X 4 の領域は整合回路が搭載されないスペースとなる。このように、図 1 (a) ではダイパッド 1 0 を大きくすることで、放熱経路が大きくなり、放熱性が高まる。熱の発生による半導体装置 1 0 0 の特性の劣化は抑制される。さらに、ボンディングワイヤ 2 4 を長くすることができるため、ボンディングワイヤ 2 4 のインダクタンス成分が大きくなる。ボンディングワイヤ 2 4 が出力インピーダンスの整合に寄与することができる。従って、半導体装置 1 0 0 を含む電子部品の低コスト化・小型化が可能となり、かつ特性が改善する。以下、比較例と比較し説明する。

#### 【0022】

図 2 (a) は比較例 1 に係る半導体装置 1 0 0 R を例示する断面図である。図 2 (a) に示すように、半導体チップ 1 8 の出力端子 1 4 a 側の端部と、ダイパッド 1 0 の出力端子 1 4 a 側の端部との距離 X 4 a は、実施例 1 における対応する距離 X 4 より小さい。つまり、実施例 1 と比較して、比較例 1 におけるダイパッド 1 0 は小さい。このため、放熱性が悪化する。半導体チップ 1 8 の動作に伴う発熱により、半導体装置 1 0 0 R の特性が悪化する。またダイパッド 1 0 が小さいため、ボンディングワイヤ 2 4 は実施例 1 と比べ短くなる。従って出力インピーダンスを整合するために半導体装置 1 0 0 R の外部に整合回路を接続する。整合回路は大型かつ高価であるため、半導体装置 1 0 0 R を含む電子部品が大型化及び高コスト化する。

#### 【0023】

図 2 (b) は比較例 2 に係る半導体装置 2 0 0 R を例示する断面図である。図 2 (b) に示すように、半導体チップ 1 8 と出力端子 1 4 a との間に整合回路部品 2 3 が設けられている。比較例 2 における半導体チップ 1 8 の出力端子 1 4 a 側の端部と、ダイパッド 1 0 の出力端子 1 4 a 側の端部との距離 X 4 b は、距離 X 4 と同程度である。このため比較例 2 における放熱性は実施例 1 と同程度である。半導体チップ 1 8 の出力パッド 1 8 b (図 2 (b) では不図示) と整合回路部品 2 3 が備えるパターン (不図示) とは、ボンディングワイヤ 2 5 により電気的に接続されている。整合回路部品 2 3 のパターンと、出力端子 1 4 a とは、ボンディングワイヤ 2 7 により電気的に接続されている。整合回路部品 1 9 によりインピーダンス整合が可能である。しかし、整合回路部品 2 3 は高価であるため、半導体装置 2 0 0 R は半導体装置 1 0 0 に比べ高コストである。

#### 【0024】

実施例 1 と比較例 1 について等価回路を用いて説明する。図 3 (a) は半導体装置 1 0 0 の等価回路を例示する回路図である。

#### 【0025】

図 3 (a) に示すように、入力端子 In と HEMT 1 9 のゲート電極との間に、入力端子 In に近い側からインダクタ L 1 及び L 2 が直列に接続されている。HEMT 1 9 のド

10

20

30

40

50

レイン電極と出力端子 Out との間にインダクタ L 3 が直列に接続されている。In ~ L 1 間にキャパシタ C 1 の一端、L 1 ~ L 2 間にキャパシタ C 2 の一端、L 2 ~ HEMT 1 9 間にキャパシタ C 3 の一端が接続されている。HEMT 1 9 ~ L 3 間にキャパシタ C 4 の一端、L 3 ~ Out 間にキャパシタ C 5 の一端が接続されている。HEMT 1 9 のソース電極、及びキャパシタ C 1 ~ C 5 の他端は接地されている。出力端子 Out には整合回路 4 6 が接続されている。

【0026】

入力端子 In は図 1 (a) 及び図 1 (b) に示した入力端子 12a に対応する。キャパシタ C 1 は入力端子 12a の寄生容量である。キャパシタ C 2 は整合回路部品 16 により生成される。インダクタ L 1 はボンディングワイヤ 20、インダクタ L 2 はボンディングワイヤ 22 により生成される。キャパシタ C 3 は半導体チップ 18 のゲート電極の寄生容量であり、キャパシタ C 4 はドレイン電極の寄生容量である。つまり HEMT 1 9、キャパシタ C 3 及び C 4 は半導体チップ 18 に含まれる。インダクタ L 3 はボンディングワイヤ 24 により生成される。出力端子 Out は出力端子 14a に対応し、キャパシタ C 5 は出力端子 14a の寄生容量である。

【0027】

図 3 (b) は実施例 1 における出力インピーダンスの整合を例示するスミスチャートである。黒丸 A 1 は所望する出力インピーダンス (例えば 50 ) を表す。黒丸 A 2 は HEMT 1 9 の出力端 (図 1 (a) 及び図 1 (b) の出力パッド 18b)、黒丸 A 3 はインダクタ L 3 (ボンディングワイヤ 24) の出力端子 Out 側、黒丸 A 4 は出力端子 Out 、それそれぞれにおける出力インピーダンスを表す。

【0028】

図 3 (b) に示すように、出力インピーダンスは、インダクタ L 3 により A 2 から A 3 、キャパシタ C 5 により A 3 から A 4 にシフトする。つまり出力インピーダンスは A 1 が表す所望の値に近付く。整合回路 4 6 は出力インピーダンスを A 2 から A 1 にシフトさせる機能を有していればよい。これにより所望の出力インピーダンスが得られ、良好な特性が得られる。整合回路 4 6 の構成は簡単になり、かつ小型化可能である。また整合回路 4 6 における信号の損失は抑制される。

【0029】

図 4 (a) は半導体装置 100R の等価回路を例示する回路図である。図 4 (a) に示すように、HEMT 1 9 ~ Out 間にインダクタ L 3 が接続されていない。これは、図 2 (a) に示すようにボンディングワイヤ 24 が短いため、インダクタンス成分をほとんど有しないことによる。

【0030】

図 4 (b) は比較例 1 における出力インピーダンスの整合を例示するスミスチャートである。黒丸 A 5 は出力端子 Out における出力インピーダンスを表す。図 4 (b) に示すように、出力インピーダンスは、キャパシタ C 5 により A 2 から A 5 にシフトする。つまり出力インピーダンスは A 1 が表す所望の値から遠ざかる。整合回路 4 6 は出力インピーダンスを A 5 から A 1 にシフトさせる。従って、整合回路 4 6 の構成は複雑になり、かつ大型化する。このため整合回路 4 6 における信号の損失は増大する。

【0031】

次に半導体装置 100 を E 級パワーアンプに用いる例を説明する。図 5 (a) は半導体装置 100 を用いた E 級パワーアンプ 110 を例示する回路図である。

【0032】

図 5 (a) においても、図 3 (a) と同様に HEMT 1 9 のドレイン電極にインダクタ L 3 及びキャパシタ C 4 が接続されている。HEMT 1 9、インダクタ L 1 ~ L 3 及びキャパシタ C 1 ~ C 4 は半導体装置 100 に含まれる。キャパシタ C 6 及び C 7、インダクタ L 4 及び抵抗 R 1 は半導体装置 100 の外部から接続される。HEMT 1 9 のドレイン電極と抵抗 R 1 の一端との間に、インダクタ L 3 及びキャパシタ C 6 が直列に接続されている。L 3 ~ C 6 間にはインダクタ L 4 の一端、及びキャパシタ C 7 の一端が接続されて 50

いる。インダクタ L 4 の他端は電源 V d c に接続されている。キャパシタ C 7 の他端は H E M T 1 9 のソース電極と抵抗 R 1 の他端との間に接続されている。インダクタ L 3 とキャパシタ C 7 とは共振回路 R e s 1 を形成する。キャパシタ C 6 は信号の D C (Direct Current: 直流) 成分をカットする。ボンディングワイヤ 2 4 がインダクタ L 3 として機能するため、寄生容量を抑制し、かつ E 級パワーアンプ 1 1 0 を小型化することができる。またインダクタ L 3 は高い Q を有するため、共振回路 R e s 1 の共振特性が改善する。従って、小型で高効率な E 級パワーアンプ 1 1 0 を得ることができる。

#### 【 0 0 3 3 】

図 5 ( b ) は半導体装置 1 0 0 R を用いた E 級パワーアンプ 1 1 0 R を例示する回路図である。図 5 ( b ) に示すように、インダクタ L 5 は半導体装置 1 0 0 R の外部に接続される。例えばチップインダクタをインダクタ L 5 とすることができます。このため、インダクタ L 5 による寄生容量が大きくなる。またインダクタ L 5 は、インダクタ L 4 より Q が低い。このため、共振特性が悪化する。インダクタ L 5 として Q の高い空芯インダクタを用いることができる。しかし、空芯インダクタは不要な電磁波を発生させる。このため E 級パワーアンプ 1 1 0 R の受信感度が低下し、周辺の回路に影響を及ぼす。

10

#### 【 0 0 3 4 】

ボンディングワイヤ 2 4 は、出力パッド 1 8 b と出力端子 1 4 a とを直接に接続する。つまり出力パッド 1 8 b と出力端子 1 4 a との間には部品が接続されない。このためボンディングワイヤ 2 4 が長くなり、ボンディングワイヤ 2 4 のインダクタンス成分を高くすることができる。例えば整合回路部品 1 6 を半導体装置 1 0 0 の外部に出してもよい。しかし、入力端子 1 2 a と半導体チップ 1 8 とを接続するボンディングワイヤが長くなり、インダクタンス成分が大きくなる。この結果、インピーダンス整合を適切にとることが難しく、半導体装置 1 0 0 の特性が劣化する。整合回路部品 1 6 は半導体装置 1 0 0 に含まれることが好ましい。

20

#### 【 0 0 3 5 】

ボンディングワイヤに大きな電流が流れると、ジュール熱が増大し、ボンディングワイヤが溶断することがある。特に、長いボンディングワイヤは大きなジュール熱が発生し溶断しやすい。例えば半導体チップ 1 8 は L D M O S ( Lateral Diffused MOS: 横方向拡散 M O S ) を備えてもよい。L D M O S を用いる場合、例えば V d s = 2 8 V とする。出力電力を高めるために、ゲート幅を大きくし電流を増大させる。しかし電流の増大によりジュール熱が大きくなり、溶断が起こりやすくなる。図 1 ( c ) のように、半導体チップ 1 8 が H E M T 1 9 ( G a N - H E M T ) を備えてもよい。例えば G a N - H E M T は L D M O S と比較して耐圧が高いため、例えば V d s = 5 0 V とすることができます。このため、例えば L D M O S の場合と同じ出力電力を得る場合、電流を小さくすることができる。従ってジュール熱が小さくなり、溶断が抑制される。実施例 1 のようにダイパッド 1 0 を大きくすることで放熱性が高まる。従って、溶断はより効果的に抑制される。

30

#### 【 0 0 3 6 】

ボンディングワイヤ 2 2 の本数は、入力パッド 1 8 a の数に応じて定まる。入力パッド 1 8 a は半導体チップ 1 8 のゲート幅に応じて定めればよい。例えばゲート幅を大きくすることにより、半導体チップ 1 8 の出力電力を高めることができる。ボンディングワイヤ 2 4 の本数は、出力パッド 1 8 b の数及び出力電流に応じて定めることができる。

40

#### 【 0 0 3 7 】

寸法は変更可能である。長さ X 2 は長さ X 1 より大きければよい。距離 X 4 は距離 X 3 以上で、長さ X 1 及び X 2 より大きく、かつ X 4 > X 2 + X 5 であればよい。放熱性を高めかつインピーダンス整合を適切にとるためである。出力インピーダンスを整合させるためには、ボンディングワイヤ 2 4 は十分な長さを有することが好ましい。ボンディングワイヤ 2 4 はボンディングワイヤ 2 2 より長く、例えば 1 . 5 m m 以上 3 m m 以下である。ボンディングワイヤ 2 4 の長さは例えば、1 m m 以上、1 . 3 m m 以上、1 . 7 m m 以上又は 2 m m 以上でもよい。放熱性を高めるためには、ダイパッド 1 0 が大きいことが好ましい。ダイパッド 1 0 の一辺の長さ ( 図 1 ( a ) の X 1 + X 3 + X 4 ) は例えば 3 m m 以

50

上 5 mm 以下である。ダイパッド 10 の一边の長さは例えば 2 mm 以上、2.5 mm 以上、3.5 mm 以上、又は 4 mm 以上でもよい。

【0038】

放熱性を高めるために、ダイパッド 10 は金属により形成されていることが好ましい。また放熱性及びソース電極 42 とダイパッド 10 との接続を確保するため、接着剤 26 は金属を含有していることが好ましい。

【実施例 2】

【0039】

実施例 2 は複数の半導体チップ 18 及び 52 を備える例である。図 6 は実施例 2 に係る半導体装置 200 を例示する平面図である。

10

【0040】

図 6 に示すように、ダイパッド 10 上に、整合回路部品 16 及び 50、並びに半導体チップ 18 及び 52 が搭載されている。パターン 16b は入力端子 12b と接続され、半導体チップ 18 は出力端子 14b と接続されている。整合回路部品 50 はベース部 50a 及びパターン 50b を有する。半導体チップ 52 には HEMT が形成されており、入力パッド 52a 及び出力パッド 52b を有する。入力端子 12c とパターン 50b とは、ボンディングワイヤ 54 により接続されている。パターン 50b と入力パッド 52a とは、ボンディングワイヤ 56 により接続されている。出力パッド 52b と出力端子 14c とはボンディングワイヤ 58 により接続されている。

【0041】

20

半導体装置 200 における寸法及び距離は、半導体装置 100 と同じである。従って、ボンディングワイヤ 24 及び 58 のインダクタンス成分が大きく、出力インピーダンスの整合が可能である。ダイパッド 10 が大きいため、放熱性が高くなる。半導体装置 200 は 2 つの半導体チップ 18 及び 52 を有する。従って、半導体装置 200 を差動プッシュプルアンプ及びドハティアンプとして用いることができる。また半導体装置 200 における半導体チップ 18 及び 52、整合回路部品 16 及び 50 における各寸法及び各距離は異なっていてもよい。また、どちらか一方のみが実施例 1 及び 2 に示したような構成を採ることもできる。半導体チップは 3 つ以上でもよい。

【0042】

30

半導体チップ 18 は HEMT 以外のトランジスタを含んでもよい。上述のように、溶断を抑制し高出力を得るために半導体チップ 18 は HEMT を含むことが好ましい。HEMT 19 は図 1 (c) に示した以外の窒化物半導体を含んでもよい。窒化物半導体とは窒素 (N) を含む半導体であり、例えば窒化アルミニウム (AlN)、窒化インジウム (InN)、窒化インジウムガリウム (InGaN)、窒化インジウムアルミニウム (InAlN)、及び窒化アルミニウムインジウムガリウム (AlInGaN) などである。HEMT 19 は窒化物半導体以外に、ガリウム砒素 (GaAs) など砒素系の半導体を含んでもよい。

【0043】

以上、本発明の実施例について詳述したが、本発明はかかる特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

40

【符号の説明】

【0044】

|                 |        |

|-----------------|--------|

| 10              | ダイパッド  |

| 11              | パッケージ  |

| 12a、12b、12c、In  | 入力端子   |

| 14a、14b、14c、Out | 出力端子   |

| 16、50           | 整合回路部品 |

| 18、52           | 半導体チップ |

| 18a、52a         | 入力パッド  |

50

1 8 b、5 2 b

1 9

2 0、2 2、2 4、5 4、5 6、5 8

4 6

出力パッド

H E M T

ボンディングワイヤ

整合回路

【図 1】

【図 2】

【図3】

(a)

(b)

【図4】

(a)

(b)

【図5】

(a)

(b)

【図6】

---

フロントページの続き

(56)参考文献 特開昭59-124745(JP,A)

特開2001-230640(JP,A)

特開平02-028350(JP,A)

特開平01-296702(JP,A)

特開昭61-073352(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/00 - 23/15

H01L 25/00 - 25/18

H01L 21/822

H01L 27/04

H03F 3/24