(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第6999565号

(P6999565)

(45)発行日 令和4年1月18日(2022.1.18)

(24)登録日 令和3年12月24日(2021.12.24)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| G 0 6 F | 13/12 (2006.01) | F I | G 0 6 F | 13/12 | 3 3 0 A |

| G 0 6 F | 12/00 (2006.01) |     | G 0 6 F | 12/00 | 5 5 0 E |

| G 0 6 F | 12/02 (2006.01) |     | G 0 6 F | 12/02 | 5 8 0 J |

| G 0 6 F | 13/16 (2006.01) |     | G 0 6 F | 13/16 | 5 2 0 B |

| G 0 6 F | 13/36 (2006.01) |     | G 0 6 F | 13/36 | 5 3 0 B |

請求項の数 14 (全24頁) 最終頁に続く

(21)出願番号 特願2018-544830(P2018-544830)

(86)(22)出願日 平成29年3月3日(2017.3.3)

(65)公表番号 特表2019-507436(P2019-507436)

A)

(43)公表日 平成31年3月14日(2019.3.14)

(86)国際出願番号 PCT/US2017/020582

(87)国際公開番号 WO2017/152005

(87)国際公開日 平成29年9月8日(2017.9.8)

審査請求日 令和2年2月7日(2020.2.7)

(31)優先権主張番号 62/302,891

(32)優先日 平成28年3月3日(2016.3.3)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 15/448,327

(32)優先日 平成29年3月2日(2017.3.2)

最終頁に続く

(73)特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 9 2 1

2 1 サン デイエゴ モアハウス ドライ

ブ 5 7 7 5

(74)代理人 100108453

弁理士 村山 靖彦

(74)代理人 100163522

弁理士 黒田 晋平

(72)発明者 ジュンウォン・スー

アメリカ合衆国・カリフォルニア・ 9 2

1 2 1 ・サン・ディエゴ・モアハウス・

ドライブ・ 5 7 7 5

(72)発明者 デクスター・タミオ・チュン

アメリカ合衆国・カリフォルニア・ 9 2

最終頁に続く

(54)【発明の名称】 メモリシステムのための省電力化技法

## (57)【特許請求の範囲】

## 【請求項1】

メモリバスの複数のデータレーンに結合されるように構成された物理層(PHY)インターフェースと、

読み取りレジスタと、

前記PHYインターフェースに結合されたメモリコントローラであって、データパターンチェックカーリン理回路を備え、

前記データパターンチェックカーリン理回路を使用して、前記メモリバスを介してメモリ要素に書き込むべきデータに繰り返し可能なデータのパターンが存在するかどうかを判定することと、

前記データをより少ないレーン内に統合し、列アドレス選択(CAS)コマンドによって修正される書き込みコマンドを使用して前記データを前記メモリバスの前記複数のデータレーンのうちのいくつかのデータレーンのみを介して送ることと、

前記PHYインターフェースを介して前記メモリ要素からデータを受信することと、

前記メモリ要素から受信された情報に基づいて前記読み取りレジスタ内のデータを複製することと

をするように構成された、メモリコントローラと

を備える、ホストプロセッサ。

## 【請求項2】

前記メモリコントローラは、ルックアップテーブルをさらに備え、前記メモリコントロ

ラは、前記メモリ要素に書き込まれるデータに関するアドレス情報を前記ルックアップテーブルに書き込む、請求項1に記載のホストプロセッサ。

【請求項3】

前記メモリコントローラは、前記ルックアップテーブルを使用して、統合された読み取りコマンドが使用されてもよいように、前記メモリ要素から読み取られるデータが繰り返し可能なデータの前記パターンを有するかどうかを判定するように構成される、請求項2に記載のホストプロセッサ。

【請求項4】

前記メモリコントローラは、8つのレーンのそれぞれを使用して前記書き込むべきデータを送信する代わりに、前記書き込むべきデータを1つのデータレーン上に統合するように構成される、請求項1に記載のホストプロセッサ。

10

【請求項5】

前記メモリコントローラは、8つのレーンのそれぞれを使用して前記書き込むべきデータを送信する代わりに、前記書き込むべきデータを2つまたは4つのデータレーン上に統合するように構成される、請求項1に記載のホストプロセッサ。

【請求項6】

前記PHYインターフェースはバックチャネルレーンを備える、請求項1に記載のホストプロセッサ。

【請求項7】

前記メモリコントローラは、前記メモリ要素からのデータが統合されたデータであることを示すバックチャネルコマンドを受信するように構成される、請求項6に記載のホストプロセッサ。

20

【請求項8】

集積回路(IC)に組み込まれた、請求項1に記載のホストプロセッサ。

【請求項9】

メモリシステムであって、

メモリバスに結合されるように構成された入出力(IO)ブロックと、

メモリ要素を備えたメモリバンクであって、前記IOブロックに通信可能に結合された、メモリバンクと、

前記IOブロックを介して前記メモリバスからデータを受信し、ホストプロセッサからの列アドレス選択(CAS)コマンドによって修正される書き込みコマンドに応じた回数だけ前記データを複製するように動作可能な書き込みレジスタであって、前記CASコマンドは、どのように前記データを複製するかを前記メモリシステムに通知する、書き込みレジスタとを備える、メモリシステム。

30

【請求項10】

前記メモリバンクは、前記メモリ要素内に、前記書き込みレジスタからの前記複製されたデータを記憶するように構成される、請求項9に記載のメモリシステム。

【請求項11】

前記メモリバンクに結合されたデータパターンチェッカー論理回路をさらに備える、請求項9に記載のメモリシステム。

40

【請求項12】

前記データパターンチェッカー論理回路は、前記メモリ要素から読み取られたデータに繰り返し可能なデータのパターンが存在するかどうかを判定し、前記データをより少ないレーン内に統合し、前記メモリバスの複数のデータレーンのうちのいくつかのデータレーンのみを介して前記データを送るように構成される、請求項11に記載のメモリシステム。

【請求項13】

バックチャネルレーン出力をさらに含む、請求項9に記載のメモリシステム。

【請求項14】

前記メモリシステムは、複製されたデータの表示をバックチャネルレーンを介して前記バックチャネルレーン出力によって前記ホストプロセッサに送るように構成される、請求項

50

13に記載のメモリシステム。

【発明の詳細な説明】

【技術分野】

【0001】

優先権主張

本出願は、参照により内容全体が本明細書に組み込まれる、2016年3月3日出願の「POWER SAVING TECHNIQUES FOR MEMORY SYSTEMS」と題する米国仮特許出願第62/302,891号の優先権を主張する。

【0002】

本出願は、参照により内容全体が本明細書に組み込まれる、2017年3月2日出願の「POWER SAVING TECHNIQUES FOR MEMORY SYSTEMS」と題する米国特許出願第15/448,327号の優先権も主張する。

10

【0003】

本開示の技術は概して、コンピューティングデバイスにおけるメモリシステムに関し、詳細には、メモリシステムのための省電力化技法に関する。

【背景技術】

【0004】

コンピューティングデバイスが現在の社会において一般的になっている。特にモバイルコンピューティングデバイスは、日常生活の多くの局面にわたって普及している。そのようなモバイルコンピューティングデバイスは、周期的に再充電されるバッテリーによって電力を供給される。バッテリー技術の進歩によって、バッテリーを再充電することが必要になるまでの時間が延びているが、そのような進歩は、モバイルコンピューティングデバイスの機能が増大することによって相殺されている。すなわち、追加の機能によってバッテリーの使用量が増し、それによって、より頻繁に充電を行う必要が生じる。したがって、依然として、モバイルコンピューティングデバイス全体における電力消費量を削減することが強く求められている。

20

【0005】

ほぼすべてのコンピューティングデバイスが何らかの種類のメモリ要素を動作させる必要があることを諒解されたい。メモリ電力消費量は、低電力ダブルデータレート(LPDDR)メモリ規格を連続的に反復することによる電圧スケーリングによって削減されているが(たとえば、LPDDR1は1.8ボルトに設定され、LPDDR2およびLPDDR3は1.2ボルトに設定され、LPDDR4は1.1ボルトに設定された)、現在の技術制約を考慮すると電圧スケーリングは頭打ちになったように思われる。特に、リフレッシュ制限およびその他の回路性能問題によってLPDDR4では1.1ボルトが必要になっている。現在、低電力メモリの次の世代(すなわち、LPDDR5)が検討されており、LPDDR5では、電圧を1.05ボルトまで低下させることが考えられているが、この削減は、限界的な省電力化にすぎない。

30

【0006】

省電力化は特にモバイルコンピューティングデバイスにおいて関心の対象となり得るが、モバイルデバイス以外も電力消費量を削減して廃熱の発生を低減させることから利益を得る場合がある。したがって、様々な種類のコンピューティングデバイスが、電力消費量を削減したメモリシステムから利益を得る場合がある。

40

【発明の概要】

【課題を解決するための手段】

【0007】

詳細な説明において開示される態様は、メモリシステムのための省電力化技法を含む。詳細には、本開示の例示的な態様では、メモリ要素内に存在する場合があるパターンを利用し、重複したデータ転送をなくすことを企図している。具体的には、データが繰り返されている場合、同じデータを繰り返し送るのではなく、データを受信端において複製させてデータの元の反復状態に復元させる命令とともにデータを1回のみ送ってもよい。ホストとメモリ要素との間で転送されるデータの量を減らすことによって、電力消費量が削減さ

50

れる。

【 0 0 0 8 】

この点に関して、一態様では、ホストプロセッサが開示される。ホストプロセッサは、メモリバスの複数のデータレーンに結合されるように構成された物理層(PHY)インターフェースを含む。ホストプロセッサは、PHYインターフェースに結合されたメモリコントローラも含む。メモリコントローラは、データパターンチェッカー論理回路を含む。メモリコントローラは、データパターンチェッカー論理回路を使用して、メモリバスを介してメモリ要素に書き込むべきデータに繰り返し可能なデータのパターンが存在するかどうかを判定するように構成される。メモリコントローラはまた、データをより少ないレーン内に統合し、メモリバスの複数のデータレーンのうちのいくつかのデータレーンのみを介してデータを送るように構成される。

10

【 0 0 0 9 】

別の態様では、メモリシステムが開示される。メモリシステムは、メモリバスに結合されるように構成された入出力(IO)ブロックを含む。メモリシステムは、メモリ要素を含むメモリバンクも含む。メモリバンクは、IOブロックに通信可能に結合される。メモリシステムは、IOブロックを介してメモリバスからデータを受信し、ホストプロセッサからのコマンドに応じた回数だけデータを複製するように動作可能な書き込みレジスタも含む。

【 0 0 1 0 】

別の態様では、ホストプロセッサが開示される。ホストプロセッサは、メモリバスの複数のデータレーンに結合されるように構成されたPHYインターフェースを含む。ホストプロセッサは、読み取りレジスタも含む。ホストプロセッサは、PHYインターフェースに結合されたメモリコントローラも含む。メモリコントローラは、PHYインターフェースを介してメモリシステムからデータを受信するように構成される。メモリコントローラはまた、メモリシステムから受信された情報に基づいて読み取りレジスタ内のデータを複製するように構成される。

20

【 0 0 1 1 】

別の態様では、メモリシステムが開示される。メモリシステムは、メモリバスに結合されるように構成されたIOブロックを含む。メモリシステムは、メモリ要素を含むメモリバンクも含む。メモリバンクは、IOブロックに通信可能に結合される。メモリバンクは、統合されたデータをメモリバスを介してホストプロセッサに送ることによって読み取りコマンドに応答するように構成される。

30

【 0 0 1 2 】

別の態様では、装置が開示される。この装置は、メモリコントローラとPHYインターフェースとを含むホストプロセッサを含む。この装置は、メモリシステムも含む。この装置は、メモリバスも含む。ホストプロセッサは、メモリシステムに書き込むべきデータをPHYインターフェースおよびメモリバスを介して送る。メモリコントローラは、データパターンチェッカー論理回路を含む。メモリコントローラは、データパターンチェッカー論理回路を使用して、メモリバスを介してメモリ要素に書き込むべきデータに繰り返し可能なデータのパターンが存在するかどうかを判定するように動作可能である。メモリコントローラはまた、データを統合して、メモリバスを介して送られるデータを減らすように動作可能である。

40

【 0 0 1 3 】

別の態様では、装置が開示される。この装置は、メモリコントローラとPHYインターフェースとを含むホストプロセッサを含む。この装置は、メモリシステムも含む。この装置は、メモリバスも含む。ホストプロセッサは、メモリシステムから読み取られたデータをPHYインターフェースおよびメモリバスを介して受信する。メモリシステムは、メモリシステムから読み取られているデータに繰り返し可能なデータのパターンが存在するかどうかを判定し、ホストプロセッサからの読み取りコマンドに応答してデータを統合して、メモリバスを介して送られるデータを減らすように動作可能である。

【図面の簡単な説明】

50

## 【0014】

【図1】ホストプロセッサとメモリシステムとを有する例示的な従来のコンピューティングデバイスの簡略ブロック図である。

【図2A】メモリ要素内に記憶されたコードの例示的な画像である。

【図2B】メモリ要素内に記憶された未圧縮データの例示的な画像である。

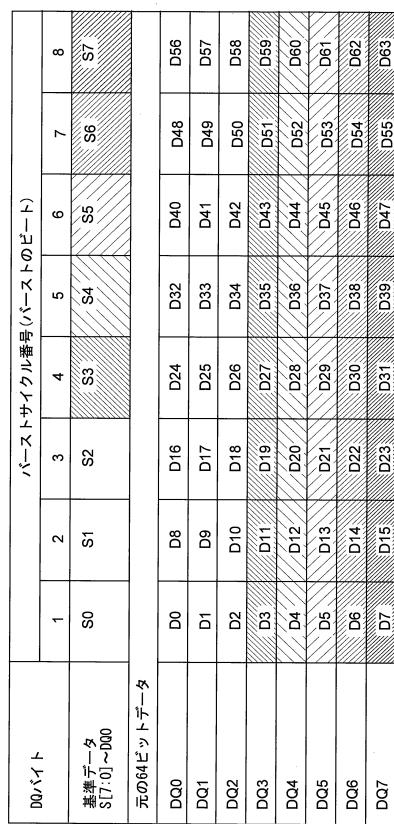

【図3A】本開示の利点を有さない、ホストプロセッサとメモリシステムとの間の8つのデータレーンを介した例示的なデータフローを示す図である。

【図3B】本開示の例示的な態様によるホストプロセッサとメモリシステムとの間の例示的なデータフローを示す図である。

【図3C】本開示の例示的な態様によるホストプロセッサとメモリシステムとの間の例示的なデータフローを示す図である。

【図3D】本開示の例示的な態様によるホストプロセッサとメモリシステムとの間の例示的なデータフローを示す図である。

【図4】本開示の例示的な態様による、ホストプロセッサとメモリシステムとを有する例示的なコンピューティングデバイスの簡略ブロック図である。

【図5】本開示の第2の例示的な態様による、ホストプロセッサとメモリシステムとを有する例示的なコンピューティングデバイスの簡略ブロック図である。

【図6】本開示の第3の例示的な態様による、ホストプロセッサとメモリシステムとを有する例示的なコンピューティングデバイスの簡略ブロック図である。

【図7】本開示の例示的な態様による書き込みプロセスを示すフローチャートである。

【図8】本開示の例示的な態様による読み取りプロセスを示すフローチャートである。

【図9】メモリシステムにおける書き込みバス回路の簡略ブロック図である。

【図10】メモリコントローラにおけるデータパターンチェック器論理回路の簡略ブロック図である。

【図11】読み取りコマンドおよび書き込みコマンドをバス上のクロックに対するタイミングとともに示す図である。

【図12】例示的な書き込みおよび読み取りコマンド真理値表を示す図である。

【図13】データレーンの間でデータを統合するための代替方法を示すデータフローの図である。

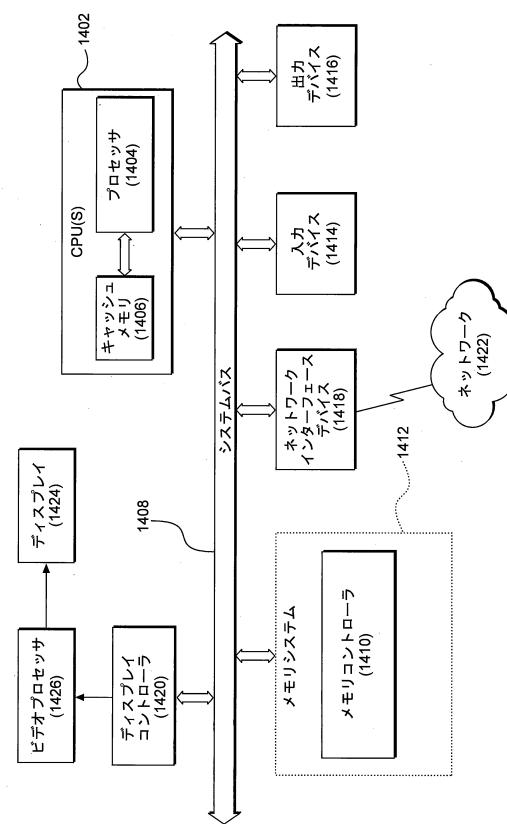

【図14】図4～図6のホストプロセッサとメモリシステムとを含むことができる例示的なプロセッサベースのシステムを示すブロック図である。

## 【発明を実施するための形態】

## 【0015】

次に図面を参照して、本開示のいくつかの例示的な態様について説明する。「例示的」という単語は、本明細書では「例、事例、または例示としての働きをすること」を意味するために使用される。本明細書で「例示的」と記載されている任意の態様は、必ずしも他の態様よりも好ましいまたは有利であると解釈されるべきではない。

## 【0016】

詳細な説明において開示される態様は、メモリシステムのための省電力化技法を含む。詳細には、本開示の例示的な態様では、メモリ要素内に存在する場合があるパターンを利用し、重複したデータ転送を排除することを企図している。具体的には、データが繰り返されている場合、同じデータを繰り返し送るのではなく、データを受信端において複製させてデータの元の反復状態に復元させる命令とともにデータを1回のみ送ってもよい。ホストとメモリ要素との間で転送されるデータの量を減らすことによって、電力消費量が削減される。

## 【0017】

本開示の特定の態様について説明する前に、ホストプロセッサとメモリシステムとを有する従来のコンピューティングデバイスについて、図1～図3Aに示されている繰り返しデータおよびその電力消費量に対する影響について説明しながら概略的に説明する。以下に、本開示の例示的な態様についての説明を図3Bを参照しながら開始する。

10

20

30

40

50

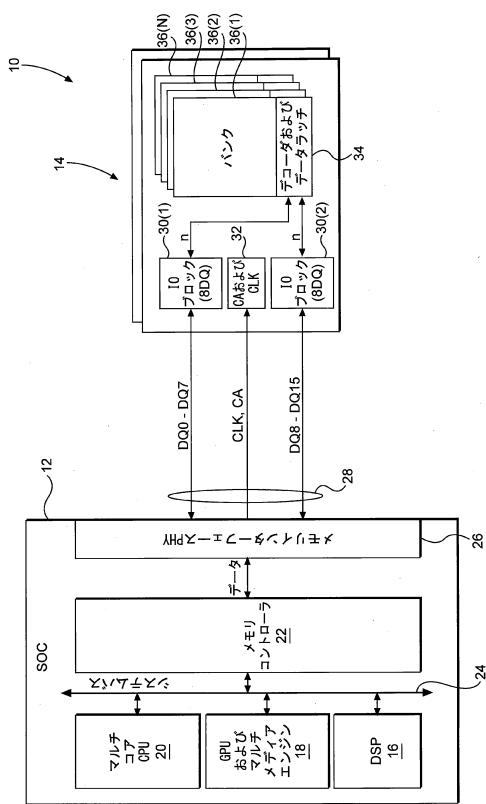

## 【0018】

この点に関して、図1は、ホストプロセッサ12とメモリシステム14とを有する従来のコンピューティングデバイス10の簡略ブロック図である。ホストプロセッサ12は、同じ機能を実現するためのシステムオンチップ(SoC)または集積回路(IC)の組合せであってもよい。詳細には、ホストプロセッサ12は、デジタル信号プロセッサ(DSP)16と、グラフィック処理ユニット(GPU)およびマルチメディアエンジン18と、マルチコア中央処理ユニット(CPU)20と、メモリコントローラ22とを含んでもよい。DSP16、GPUおよびマルチメディアエンジン18、マルチコアCPU20、ならびにメモリコントローラ22は、システムバス24を介して互いに通信してもよい。メモリコントローラ22は、メモリインターフェース物理層(PHY)26と協働してメモリバス28に結合する。メモリバス28は、メモリシステム14にも結合される。例示的な態様では、メモリバス28は、第1の8つのデータレーン(DQ0～DQ7と呼ばれることがある)と、クロック(図面ではCLKと参照されている)、コマンド、およびアドレスレーン(コマンドレーンおよびアドレスレーンはCAと示されることがある)と、第2の8つのデータレーン(DQ8～DQ15と呼ばれることがある)とを含む。クロック、コマンド、およびアドレスレーンが必要または所望に応じて3つの別々のレーンであってもよく、2つのレーンであってもよく(たとえば、一方のレーンがクロックで他方のレーンがコマンドおよびアドレス)、または単一のレーンであってもよいことに留意されたい。本明細書で使用するレーンは物理的導体(たとえば、ワイヤトレース)である。一般に、各レーンは、ホストプロセッサ12上のメモリインターフェースPHY26に関連するレーン自体のピンと、メモリシステム14用のそれぞれのピンとを有する。

10

20

## 【0019】

引き続き図1を参照するとわかるように、メモリシステム14は、データレーンIOブロック30(1)～30(2)などの1つまたは複数のデータレーン入出力(IO)ブロックと、コマンド/アドレス/クロック(図面ではCA&CLKと参照されている)ブロック32とを含んでもよい。さらに、メモリシステム14は、メモリバンク36(1)～36(N)(4つが図示されている)のメモリバンクごとにデコーダおよびデータラッ奇34を含んでもよい。よく理解されるように、「ブロック」という用語が使用されるときに、この文脈におけるブロックが論理回路または他のハードウェア要素であることを諒解されたい。

## 【0020】

同じくよく理解されるように、ホストプロセッサ12は、メモリシステム14に対して読み取りおよび書き込みを行う。多くの例では、読み取り/書き込み活動はデータに関係するが、いくつかの例では、読み取り/書き込み活動はコードに関係する。いずれの場合も、メモリバンク36(1)～36(N)内に記憶されたコンテンツはしばしば重複する。コードは、一般にメモリバンク36(1)～36(N)のうちの約10%を占めるにすぎないが、しばしば重複する。例示的なコードスニペット200が図2Aに示されている。すでに明らかのように、コードスニペット200は、この例では「00」である繰り返されるコンテンツを含む(コードスニペット200内の領域202および204を概略参照されたい)。同様に、このデータは、メモリバンク36(1)～36(N)の残りの部分を消費する場合があるが、同じくしばしば重複する。例示的なデータブロック210が図2Bに示されている。すでに明らかのように、データブロック210は、繰り返される「00」(たとえば、領域212を参照されたい)および繰り返される「FF」(たとえば、領域214を参照されたい)を含む。データとコードが概念的に異なるとき、「データ」は、メモリバンク36(1)～36(N)内に存在し、メモリバンク36(1)～36(N)に書き込まれ、メモリバンク36(1)～36(N)から読み取られるコンテンツを指す。同様に、例示的な繰り返されるコンテンツが「00」または「FF」であるとき、実際のデータが、他の繰り返されるコンテンツを含み、および/または繰り返しの頻度を変化させる場合があることを諒解されたい。

30

40

## 【0021】

図1のコンピューティングデバイス10などの従来のシステムでは、読み取りコマンドまたは書き込みコマンドが実行されるときに、読み取りコマンドまたは書き込みコマンドのデータがデータレーン(すなわち、DQ0～DQ15)を介して分散され、受信エンティティ(すなわち、読み

50

取りコマンドの場合のホストプロセッサ12または書き込みコマンドの場合のメモリシステム14)に送られる。この構成は図3Aに示されており、図3Aにはデータバースト300が示されている。データバースト300は、図2Aのコンテンツに対応し、第1の8つのデータレーンDQ0～DQ7におけるスロット(D0～D127)の各々に対応するデータが存在する(D39までのみ示されている)。容易に明らかのように、多くの例では、スロットD0～D127内のデータの多くが重複する。メモリバス28を介した電力消費量がデータ速度およびデータの量の関数であることを諒解されたい。したがって、メモリバス28を介して重複するデータを送ると電力が消費される。

#### 【0022】

本開示の例示的な態様は、読み取りコマンドおよび書き込みコマンドにおけるデータの重複を利用して、複数のデータレーンを介して複数のコピーを送るのではなく、重複するデータを単一のデータレーン上に統合し、その後重複するデータの単一のコピーのみをメモリバス28を介して送る。本開示の例示的な態様は、メモリバス28を介して送られるデータの量を減らすことによって、さらなる電圧スケーリングを実行することができなくても省電力化を可能にする。この省電力化によってモバイルコンピューティングデバイス用のバッテリー寿命が伸び得るが、モバイルデバイス以外において発生する廃熱が少くなり得、本開示からあらゆるコンピューティングデバイスが利益を得る場合がある。

10

#### 【0023】

この点に関して、図3Bは、データブロック310内のデータが8つのスロットグループにわたって同じである第1の態様を示す。たとえば、スロットD0～D7に入るデータ(312を全体的に参照されたい)はすべて「00」であり、スロットD16～D23に入るデータ(314を全体的に参照されたい)はすべて「01」であり、スロットD24～D31に入るデータ(316を全体的に参照されたい)はすべて「FF」である。しかし、同じデータを8回送る(各データレーンDQ0～DQ7を介して1回)のではなく、データはデータレーンDQ0上でのみ送られ、データレーンDQ1～DQ7はオフにされる。すなわち、たとえば、データレーンDQ0～DQ7上のスロットD8～D15において「00」を送るのではなく、データレーンDQ1～DQ7に関するデータがスロットD8と同じであるという指示とともに、データレーンDQ0のみがスロットD8を送る。受信端において、レシーバがデータレーンDQ0からスロットを受信し、データを複製して複製したデータを再構成する。

20

#### 【0024】

あらゆるデータの集合が同じデータを有する8つのスロットを有するとは限らないことを諒解されたい。このことに関して、図3Cは、データブロック320が同じ4つのスロットを有する状況を示している。たとえば、スロットD0～D3に対応するグループ322内のデータは同じであり、スロットD4～D7に対応するグループ324内のデータは、同じであるが、グループ322内のデータと同じではない。したがって、データレーンDQ0およびDQ4上でデータが送られ、重複するデータレーンDQ1～DQ3およびDQ5～DQ7はオフにされる。2つのアクティブレーンを有すると、1つのアクティブレーンを有するよりも多くの電力が消費されるが、それでも、2つのアクティブレーンを有する場合、8つのアクティブレーンを有する場合よりも電力消費量が少ない。

30

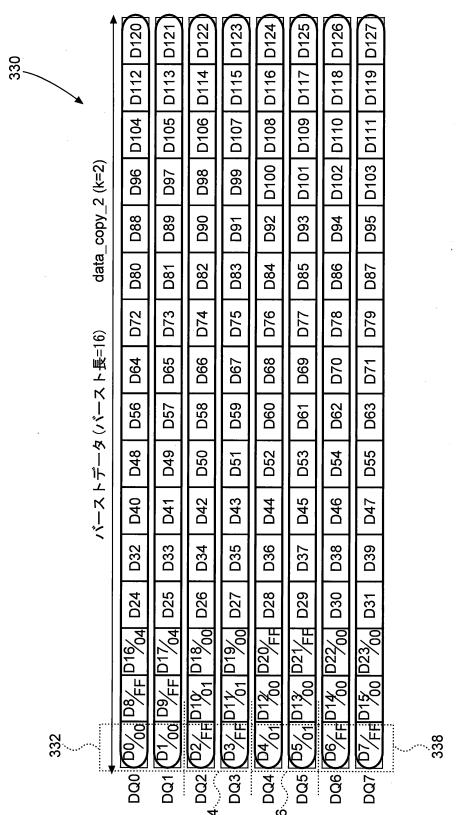

#### 【0025】

同様に、図3Dは、データブロック330が同じ2つのスロットを有する状況を示す。たとえば、スロットD0～D1に対応するグループ332内のデータは同じであり、スロットD2～D3に対応するグループ334内のデータは同じであり、スロットD4～D5に対応するグループ336内のデータは同じであり、スロットD6～D7に対応するグループ338内のデータは同じである。したがって、データレーンDQ0、DQ2、DQ4、およびDQ6上でデータが送られ、データレーンDQ1、DQ3、DQ5、およびDQ7はオフにされる。この場合も、4つのアクティブレーンを有すると、1つまたは2つのアクティブレーンを有するよりも多くの電力が消費されるが、それでも、4つのアクティブレーンを有する場合、8つのアクティブレーンを有する場合よりも電力消費量が少ない。データレーンDQ8～DQ15を介して送られるデータについて別個のパターン検査を使用することができる。

40

50

## 【 0 0 2 6 】

本開示の重複データ技法が使用されることを伝えるには、修正された読み取りコマンドおよび書き込みコマンドが使用されてもよい。たとえば、7つの重複に対して1つのデータレーンのみが使用される場合、コマンドはRD\_X1およびWR\_X1であってもよい。2つのデータレーンが使用され、データレーンごとに3つの重複が使用される場合、コマンドはRD\_X2およびWR\_X2であってもよい。同様に、4つのデータレーンが使用され、レーンごとに1つの重複が使用される場合、コマンドはRD\_X4およびWR\_X4であってもよい。上記の符号が任意のものであり、説明のために使用されていることを諒解されたい。実際には、読み取りコマンドおよび書き込みコマンドは列アドレス選択(CAS)コマンドによって修正されることがある。CASコマンド内のデータは、読み取りコマンドまたは書き込みコマンドがどのように修正されるか(たとえば、読み取りコマンドをRD\_X1、RD\_X2、またはRD\_X4に修正する)を符号化することができる。読み取りコマンドまたは書き込みコマンドに対するCASコマンドについて、図11を参照しながら以下でさらに詳細に検討する。CASコマンドを使用することは修正された読み取りコマンドおよび書き込みコマンドを知らせる1つの方法であるが、本開示の範囲から逸脱せずに他の技法が使用されてもよい。

10

## 【 0 0 2 7 】

重複するデータレーンの統合を実行するには、重複するデータを検出することと、非アクティブデータレーンが存在していたスロットに重複するデータをコピーすることを可能にする何らかの修正を図1のコンピューティングデバイス10に施さなければならない。図4～図6は、これらの修正が実施される場合がある例示的な代替方法を示す。この点に関して、図4は、ホストプロセッサ402とメモリシステム404とを有する例示的なコンピューティングデバイス400を示す。ホストプロセッサ402は、同じ機能を実現するためのロバストなSoCまたはICの組合せであってもよい。詳細には、ホストプロセッサ402は、DSP406と、GPUおよびマルチメディアエンジン408と、マルチコアCPU410と、メモリコントローラ412とを含んでもよい。DSP406、GPUおよびマルチメディアエンジン408、マルチコアCPU410、ならびにメモリコントローラ412は、システムバス414を介して互いに通信してもよい。メモリコントローラ412は、メモリインターフェースPHY416と協働してメモリバス418に結合し、メモリバス418はメモリシステム404にも結合する。例示的な態様では、メモリバス418は、第1の8つのデータレーン(DQ0～DQ7と呼ばれることがある)と、クロック(CLKと呼ばれることがある)、コマンド、およびアドレスレーン(CAと呼ばれることがある)と、第2の8つのデータレーン(DQ8～DQ15と呼ばれることがある)とを含む。クロック、コマンド、およびアドレスレーンが必要または所望に応じて3つの別々のレーンであってもよく、2つのレーンであってもよく(たとえば、一方のレーンがクロックで他方のレーンがコマンドおよびアドレス)、または単一のレーンであってもよいことに留意されたい。さらに、さらなるバックチャネルレーンが存在してもよい(具体的には図示されていない)。上述のように、各レーンは一般に、それ自体の物理的ピンに結合され、かつ物理的導体である。

20

## 【 0 0 2 8 】

引き続き図4を参照するとわかるように、メモリシステム404は、データレーンIOブロック420(1)～420(2)などの1つまたは複数のデータレーンIOブロックと、コマンド/アドレス/クロックブロック422とを含んでもよい。さらに、メモリシステム404は、メモリバンク426(1)～426(N)(4つが図示されている)のメモリバンクごとにデコーダおよびデータラッ奇424を含んでもよい。

30

## 【 0 0 2 9 】

引き続き図4を参照するとわかるように、メモリコントローラ412は、データパターンチエッカー論理回路430とメモリアドレスルックアップテーブル432とを含んでもよい。同様に、メモリインターフェースPHY416は、1つまたは複数の読み取りデータコピーレジスタ434を含んでもよい。1つまたは複数の読み取りデータコピーレジスタ434のうちの1つがデータレーンの各バンドル(DQ0～DQ7またはDQ8～DQ15)に結合されてもよい。メモリシステム404は、それぞれのデータレーンIOブロック420(1)～420(2)に結合された書き込み

40

50

みデータコピーレジスタ436(1)～436(2)を含む。書き込みデータコピーレジスタ436(1)～436(2)の各々にコマンド/アドレス/クロックブロック422からの出力が与えられる。受信されたコマンド(たとえば、WR\_X1、WR\_X2、またはWR\_X4)に基づいて、このコマンドが、書き込みデータコピーレジスタ436(1)～436(2)に渡され、書き込みデータコピーレジスタ436(1)～436(2)に、データセット全体をメモリバンク426(1)～426(N)に書き込むために各デコーダおよびデータラッチ424に渡す前にデータを複製させる。

#### 【 0 0 3 0 】

メモリシステム404にデータが書き込まれるとき、データパターンチェック論理回路430は、データが特定のパターンで繰り返されているかどうかを確認し、繰り返されている場合、重複するデータをすべての8つのデータレーンを介して送るのではなく、適切な書き込みコマンド(たとえば、WR\_X1、WR\_X2、またはWR\_X4)によってデータをより少ないレーン上で束ねさせてもよい。同時に、重複するデータの表示は、メモリアドレスルックアップテーブル432に記憶される。メモリシステム404において、書き込みデータコピーレジスタ436(1)～436(2)は、受信されたデータを得て複製し、データの元の8つのスロットを再作成し、それによって、再作成されたデータは、コマンド/アドレス/クロックブロック422から受信されたコマンドに基づいて適切な数のメモリスロットを消費する。拡張されたデータは、メモリバンク426(1)～426(N)に書き込まれる。

10

#### 【 0 0 3 1 】

読み取りコマンドが生成されると、ホストプロセッサ402はメモリアドレスルックアップテーブル432を参照して重複するデータがあるかどうかを確認してもよい。重複するデータがある場合、メモリシステム404に適切な読み取りコマンド(たとえば、RD\_X1、RD\_X2、またはRD\_X4)が送られる。メモリシステム404は次いで、束ねられたデータのみをメモリバス418上のアクティブレーンを介して送る。次いで、1つまたは複数の読み取りデータコピーレジスタ434は、束ねられたデータを得て適切な回数だけ複製し、元のデータを再作成する。

20

#### 【 0 0 3 2 】

なお、本開示の態様を使用しない場合、図1のメモリコントローラ22は、 $2^*n$ ビットのデータを生成してもよい。データレーンの各バンドル(DQ0～DQ7およびDQ8～DQ15)は、nビットのデータを受信し、ビート長(BL)が完成するまでnビットのデータをデータレーンを介して順次拡散させる。したがって、 $8DQ*BL=n$ である。データレーンIOブロック30(1)～30(2)の各々は、nビットのデータをメモリバンク36(1)～36(N)に記憶できるようにデコーダおよびデータラッチ34に送る。これに対して、図4のコンピューティングデバイス400では、同じ $2^*n$ 個のデータがメモリインターフェースPHY416に渡されてもよいが、(書き込みコマンドとしてWR\_X1が使用されるか、WR\_X2が使用されるか、それともWR\_X4が使用されるかに応じて) $n/8$ ビット、 $n/4$ ビット、または $n/2$ ビットのデータがデータレーンの特定のグループを介して送られる。書き込みデータコピーレジスタ436(1)～436(2)は、コマンド/アドレス/クロックブロック422からのコマンド(data\_copy\_k、ここでkは統合の逆数である(すなわち、WR\_X1の場合kは8であり、WR\_X2の場合kは4であり、WR\_X4の場合kは2である))に基づいて、統合されたデータを拡張してnビットのデータに戻し、次にnビットをデコーダおよびデータラッチ424に渡す。(たとえば、データが反復的ではないという理由で)コンピューティングデバイス400においてデータ統合が行われない場合でも、コンピューティングデバイス400が、8つのレーン全部を介して $2^*n$ 個のデータを送ることによってコンピューティングデバイス10と同様に機能する場合があることに留意されたい。

30

#### 【 0 0 3 3 】

書き込みデータコピーレジスタ436(1)～436(2)をデータレーンIOブロック420(1)～420(2)とともに配置するのではなく、1つの書き込みデータコピーレジスタをコンピューティングデバイスのメモリシステムの各デコーダおよびデータラッチ内に配置してもよい。この例示的な態様が図5に示されている。具体的には、図4のホストプロセッサ402と同一のホストプロセッサ502を有する例示的なコンピューティングデバイス500が示されている。

40

50

同様に、ホストプロセッサ502は、メモリバス418に結合される。コンピューティングデバイス500は、メモリシステム404の代わりにメモリシステム504を含む。

#### 【 0 0 3 4 】

引き続き図5を参照するとわかるように、メモリシステム504は、データレーンIOブロック520(1)～520(2)などの1つまたは複数のデータレーンIOブロックと、コマンド/アドレス/クロックブロック522とを含んでもよい。さらに、メモリシステム504は、メモリバンク526(1)～526(N)(4つが図示されている)のメモリバンクごとにデコーダおよびデータラッチ524を含んでもよい。

#### 【 0 0 3 5 】

コマンド/アドレス/クロックブロック522は、書き込みデータコピーレジスタ528にコマンドを与える。データレーンIOブロック520(1)～520(2)と各デコーダおよびデータラッチ524との間で伝達されるデータが少なくなる( $n/k$ ビットのデータ)ので、この様態が、さらなる省電力化を可能にする場合があることに留意されたい。これらの内部バスを介して伝達されるデータが少なくなるので、消費される電力が少なくなる。したがって、図4のメモリシステム404とは対照的に、メモリシステム504は、メモリバンク526(1)～526(N)に $n/k$ ビットのデータを伝達するにすぎず、各内部書き込みデータコピーレジスタ528は、data\_copy\_kコマンドを受信し、データを拡張して元の $2^n$ ビットのデータに戻す。

10

#### 【 0 0 3 6 】

メモリアドレスルックアップテーブル432は、実際のシリコン実装形態を考慮すると、比較的高価なハードウェアであり、アドレス空間が限定されることを諒解されたい。したがって、さらなる例示的な態様として、図6に示す例示的なコンピューティングデバイス600では、メモリアドレスルックアップテーブル432をなくし、各デコーダおよびデータラッチ内に読み取りデータパターンチェッカー論理回路を配置するとともに、メモリシステム内に書き込みデータコピーレジスタを配置する。この点に関して、図6は、ホストプロセッサ602とメモリシステム604とを有するコンピューティングデバイス600を示す。ホストプロセッサ602は、同じ機能を実現するためのロバストなSoCまたはICの組合せであってもよい。詳細には、ホストプロセッサ602は、DSP606と、GPUおよびマルチメディアエンジン608と、マルチコアCPU610と、メモリコントローラ612とを含んでもよい。DSP606、GPUおよびマルチメディアエンジン608、マルチコアCPU610、ならびにメモリコントローラ612は、システムバス614を介して互いに通信してもよい。メモリコントローラ612は、メモリインターフェースPHY616と協働してメモリバス618に結合し、メモリバス618はメモリシステム604にも結合する。例示的な態様では、メモリバス618は、第1の8つのデータレーン(DQ0～DQ7と呼ばれることがある)と、クロック(CLKと呼ばれることがある)、コマンド、およびアドレスレーン(CAと呼ばれることがある)と、第2の8つのデータレーン(DQ8～DQ15と呼ばれることがある)とを含む。クロック、コマンド、およびアドレスレーンが必要または所望に応じて3つの別々のレーンであってもよく、2つのレーンであってもよく(たとえば、一方のレーンがクロックで他方のレーンがコマンドおよびアドレス)、または単一のレーンであってもよいことに留意されたい。さらに、さらなるバックチャネルレーン634が存在してもよい。上述のように、各レーンは一般に、それ自身の物理的ピンに結合され、かつ物理的導体である。

20

30

40

#### 【 0 0 3 7 】

引き続き図6を参照するとわかるように、メモリシステム604は、データレーンIOブロック620(1)～620(2)などの1つまたは複数のデータレーンIOブロックと、コマンド/アドレス/クロックブロック622とを含んでもよい。さらに、メモリシステム604は、メモリバンク626(1)～626(N)(4つが図示されている)のメモリバンクごとにデコーダおよびデータラッチ624を含んでもよい。

#### 【 0 0 3 8 】

メモリシステム604にデータが書き込まれるとき、メモリコントローラ612内のデータパターンチェッカー論理回路630は、データが特定のパターンで繰り返されているかどうかを確認し、繰り返されている場合、重複するデータをすべての8つのデータレーンを介し

50

て送るのではなく、適切な書込みコマンド(たとえば、WR\_X1、WR\_X2、またはWR\_X4)によってデータをより少ないレーン上に束ねさせてもよい。書込みデータコピーレジスタ628は、data\_copy\_kコマンドを受信し、データを拡張して元の $2^n$ ビットのデータに戻す。

#### 【0039】

この例示的な態様では、メモリアドレスルックアップテーブルがないので、ホストプロセッサ602は、パターンをメモリアドレスルックアップテーブルには記憶しない。しかし、書込みコマンド(WR\_X1、WR\_X2、WR\_X4)は前述のように発行される。読み取りコマンドは常に、重複するデータを束ねるかまたは統合するための要求なしに通常の読み取りコマンドとして開始する。しかし、メモリシステム604は、読み取りコマンドを受信すると、読み取りデータパターンチェック論理回路632を使用して、上述のように統合できる重複するデータのインスタンスがあるかどうかを確認する。重複するデータのインスタンスがある場合、読み取りデータパターンチェック論理回路632は、コマンド/アドレス/クロックブロック622に通知し、コマンド/アドレス/クロックブロック622は、読み取りコマンドに対する応答が統合されたデータの形になることを、メモリバス618上のバックチャネルレーン634を介して示す。したがって、メモリシステム604は、統合されたデータに関する情報をホストプロセッサ602に送るのを可能にするバックチャネル出力(標示されていない)を含む。ホストプロセッサ602、および特に1つまたは複数の読み取りデータコピーレジスタ636は次いで、受信されたデータを複製して元のデータを再作成する。

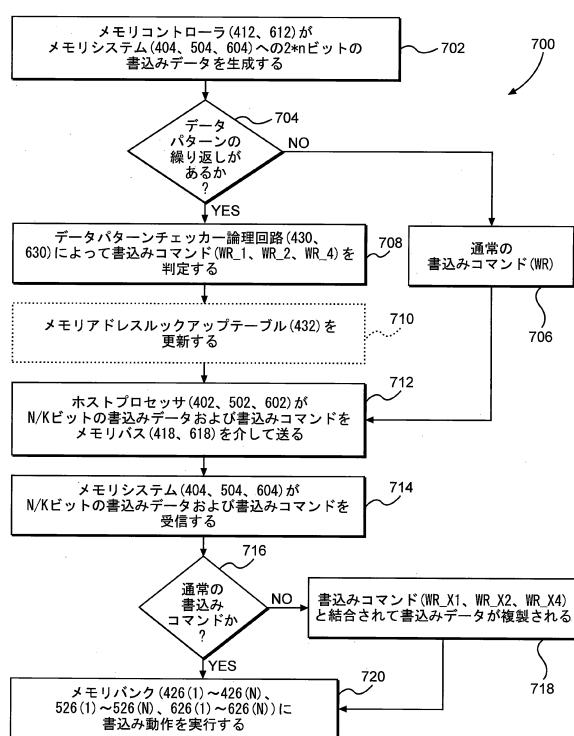

#### 【0040】

図4～図6を参照しながら上記で説明したハードウェアに基づいて、図7および図8は、本開示の例示的な態様を実施する例示的なプロセスのフローチャートを提示する。この点に関して、図7は、本開示の例示的な態様による書込み動作プロセス700のフローチャートである。書込み動作プロセス700は、メモリコントローラ412または612がメモリシステム404、504、または604に書き込むべき $2^n$ ビットの書込みデータを生成することによって開始する(ブロック702)。データパターンチェック論理回路430または630は、データパターンの繰り返しがあるかどうかを確認する(ブロック704)。ブロック704に対する応答がnoである場合、データパターンの繰り返しはなく、メモリコントローラ412または612は、通常の書込みコマンドを発行する(ブロック706)。

#### 【0041】

引き続き図7を参照するとわかるように、ブロック704に対する応答がyesである場合、データパターンの繰り返しがあり、データパターンチェック論理回路430または630は、検出されたパターンに鑑みてどの書込みコマンドが適切であるか(たとえば、WR\_X1、WR\_X2、またはWR\_X4)を判定する(ブロック708)。メモリアドレスルックアップテーブル432が存在する場合、メモリコントローラ412はメモリアドレスルックアップテーブル432を更新する(ブロック710)。ホストプロセッサ402、502、または602は次いで、メモリバス418または618を介してn/kビットの書込みデータおよび適切な書込みコマンド(WR\_X1、WR\_X2、またはWR\_X4、その場合、kはそれぞれ8、4、または2である)を送る(ブロック712)。したがって、本開示の例示的な態様は、データをメモリバス418または618のデータレーンのうちのいくつかのみを介して送るのを可能にする。本明細書で使用する「いくつかのデータレーン」が1つのデータレーンのみを使用することを含むことを諒解されたい。通常の書込みコマンドが使用される場合、kは1に等しい(すなわち、nビットの書込みデータが送られる)ことに留意されたい。メモリシステム404、504、または604は、n/kビットの書込みデータおよび書込みコマンドを受信する(ブロック714)。コマンド/アドレス/クロックブロック422、522、または622は、書込みコマンドが通常の書込みコマンドであるかどうかを判定する(ブロック716)。ブロック716に対する応答がnoである場合、書込みデータコピーレジスタ436(1)～436(2)、528、または628は、元のデータが復元されるまで書込みデータを複製する(ブロック718)。しかし、ブロック716において通常の書込みコマンドが判定された場合(またはブロック718の複製の後)、メモリシステム404、504、または604は、メモリバンク426(1)～426(N)、526(1)～526(N)、ま

10

20

30

40

50

たは626(1)～626(N)への書き込み動作を実行する。

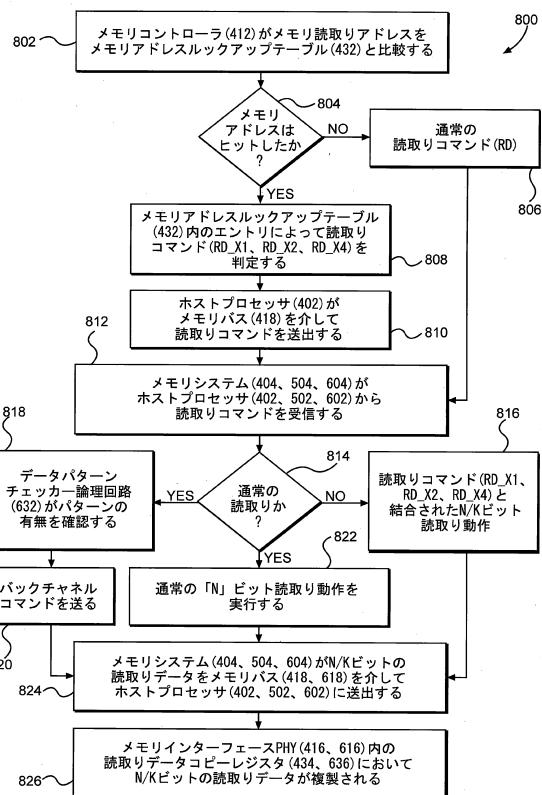

【0042】

同様に、図8は読み取り動作プロセス800のフローチャートを示す。読み取り動作プロセス800は、メモリコントローラ412(または612)が、メモリシステム404または504におけるデータが必要であると判定することによって開始する。メモリコントローラ412は、メモリ読み取りアドレスをメモリアドレスルックアップテーブル432と比較して(ブロック802)、メモリアドレスヒットがあるかどうかを確認する(ブロック804)。ブロック804においてヒットがない場合、通常の読み取りコマンドが送られる(ブロック806)。コンピューティングデバイス600では、メモリアドレスルックアップテーブル432がない場合、ブロック806において通常の読み取りコマンドが送られることに留意されたい。しかし、ブロック804においてメモリアドレスヒットがあった(すなわち、メモリ読み取りアドレスに対応するエントリがメモリアドレスルックアップテーブル432内にある)場合、メモリアドレスルックアップテーブル432内のエントリに基づいて、メモリコントローラ412は適切な読み取りコマンド(すなわち、RD\_X1、RD\_X2、またはRD\_X4)を判定する(ブロック808)。ホストプロセッサ402は次いで、メモリバス418を介して適切な読み取りコマンドを送出する(ブロック810)。メモリシステム404、504、または604は、ホストプロセッサ402、502、または602から読み取りコマンドを受信する(ブロック812)。

10

【0043】

引き続き図8を参照するとわかるように、読み取りコマンドが受信された後、コマンド/アドレス/クロックブロック422、522、または622は、読み取りコマンドが通常の読み取りコマンドであるかどうかを判定する(ブロック814)。ブロック814に対する応答がnoである場合、読み取りコマンドは通常の読み取りコマンドではなく(すなわち、RD\_X1、RD\_X2、またはRD\_X4)、その場合、デコーダおよびデータラッシュ424または524は、メモリバンク426(1)～426(N)または526(1)～526(N)からn/kビットを取り出す(ブロック816)。コンピューティングデバイス600の場合、ブロック814に対する応答がyesである場合でも、読み取りデータパターンチェックカーリ論理回路632は、パターンの有無を確認し(ブロック818)、どの程度の統合が可能であるかを判定することに留意されたい。メモリシステム604は、統合された読み取りデータセットがホストプロセッサ602に送られることを示すバックチャネルコマンドをバックチャネルレーン634を介して送る(ブロック820)。通常ならば、読み取りコマンドが通常の読み取りコマンドである場合、デコーダおよびデータラッシュ424、524、または624は通常のnビット読み取り動作を実行する(ブロック822)。ブロック816、820、または822の後で、メモリシステム404、504、または604は、メモリバス418または618を介してホストプロセッサ402、502、または602にn/kビットの読み取りデータを送出する(ブロック824)。n/kビットの読み取りデータは次いで、必要に応じてメモリインターフェースPHY416または616内の1つまたは複数の読み取りデータコピーレジスタ434または636によって複製され(ブロック826)、必要に応じて使用される。

20

【0044】

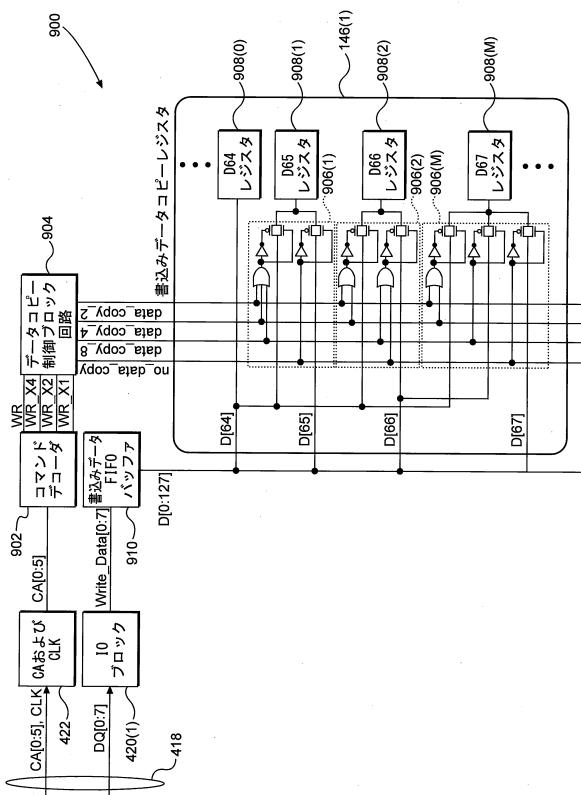

図9は、図4のメモリシステム404、図5のメモリシステム504、または図6のメモリシステム604内の例示的な書き込みデータバス900を示す。しかし、例示を目的として、書き込みデータバス900がメモリシステム404内に存在すると仮定する。したがって、データレーンDQ0～DQ7およびCAレーンは、メモリバス418を介して達する。図示されていないが、メモリバス418にはデータレーンDQ8～DQ15も存在してもよい。CAレーンは、コマンド/アドレス/クロックブロック422に達し、一方、データレーンDQ0～DQ7はデータレーンIOブロック420(1)に結合される。CAレーン内の命令およびコマンドはコマンドデコーダ902に渡され、コマンドデコーダ902は、ホストプロセッサ402によって通常の書き込みコマンドが発行されたかそれともWR\_X1、WR\_X2、またはWR\_X4が発行されたかを判定する。コマンドデコーダ902は、受信されたコマンドに基づいて、データコピー制御ブロック回路904に命令する。データコピー制御ブロック回路904は、書き込みデータコピー・レジスタ436(1)内のレジスタ908(1)～908(M)に結合されたゲーティング論理回路906(1)～906(M)を制御する。同時に、書き込みデータ先入れ先出し(FIFO)バッファ910が、n

30

40

50

ビットのデータを書込みデータコピー・レジスタ436(1)へのデータ入力として与える。

【0045】

図9に示すように、nビットのデータは通常、レジスタ908(1)～908(M)のうちのM個のレジスタに送られる。データコピー制御ブロック回路904がno\_data\_copyをアサートすると、レジスタ908(1)～908(M)のうちの1つに1データビットが送られる。しかし、データコピー制御ブロック回路904がdata\_copy\_8線、data\_copy\_4線、またはdata\_copy\_2線のうちの1つをアサートすると、ゲーティング論理回路906(1)～906(M)は、データをレジスタ908(1)～908(M)のうちのそれぞれの数のレジスタにコピーさせるように動作する。本開示の範囲から逸脱せずに書込みデータバス900に他の構造が使用されてもよいことを諒解されたい。

10

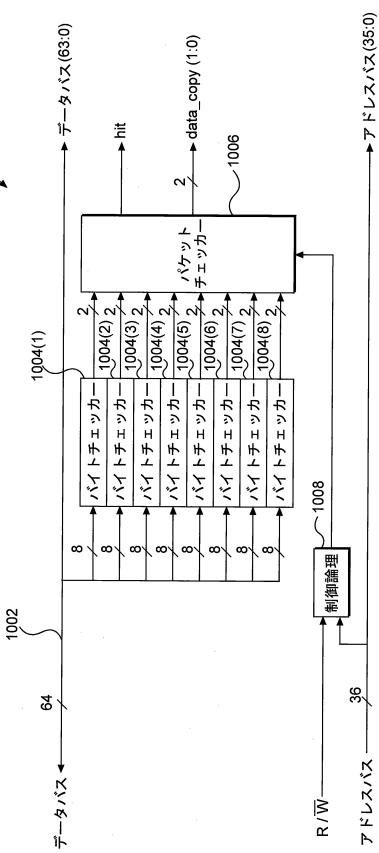

【0046】

図10は、図4または図6のデータパターン・チェック・カーランゲィング回路430または630に対応するデータパターン・チェック・カーランゲィング回路1000の例示的なブロック図を示す。データパターン・チェック・カーランゲィング回路1000は、たとえば64ビットのデータを伝達するデータバス1002を含む。これらの64ビットのデータはバイト・チェック・カーランゲィング(1)～(8)に与えられる。図示のように、データレーンDQ0～DQ7の各々についての1ビットに対応する8ビットがバイト・チェック・カーランゲィング(1)～(8)の各々に与えられる。バイト・チェック・カーランゲィング(1)～(8)は、たとえば、通常の書込み、WR\_X4、WR\_X2、またはWR\_X1にそれぞれ対応する0ビット、2ビット、4ビット、または8ビットの一一致を示す2ビットコードを出力する。これらの2ビットコードはパケット・チェック・カーランゲィング1006に与えられる。パケット・チェック・カーランゲィング1006は、パケット全体に関するすべての出力を比較して、伝播すべきデータの最小値を判定する。最小値が一致しない場合、データが統合されないことを意味する偽の結果が返される。肯定的結果が返された場合、トランザクション開始アドレスが存在する場合、図4のメモリアドレス・ルックアップ・テーブル432に記憶される。制御論理1008は、トランザクションの開始および終了を記録する。パケット・チェック・カーランゲィング1006は、ヒット信号およびdata\_copy(1:0)をメモリ・インターフェースPHY416または616に出力する。これらの信号は、メモリ・インターフェースPHY416または616内のコマンドおよびアドレス・符号化・ブロック(図示せず)に送られる。アドレスバス(35:0)もコマンドおよびアドレス・符号化・ブロックに送られる。コマンドおよびアドレス・符号化・ブロックは、これらの信号を使用して、メモリバス418または618を介してメモリ・システム404、504、または604に送るべき適切なアドレスを有する適切なコマンドを構成する。データバス63:0は、メモリ・インターフェースPHY416または616に送られ、メモリ・システム404、504、または604に送られる前に適宜統合される(または統合されない)データである。

20

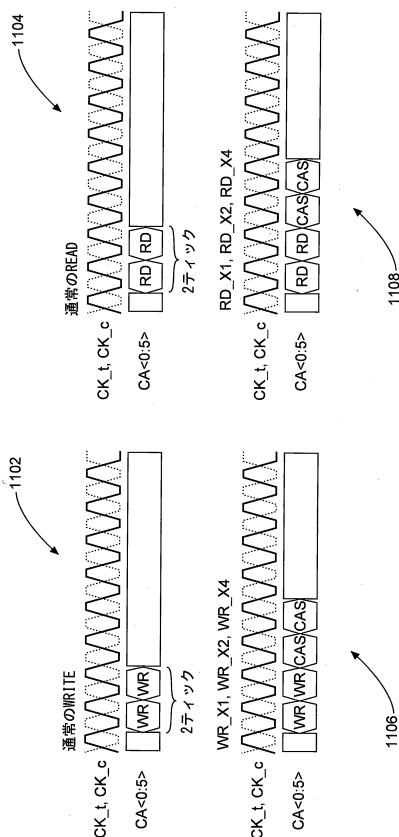

【0047】

図11は、例示的な書込みおよび読み取りコマンドアドレス・バストライミングを示す。すでに明らかのように、通常の書込みコマンド1102および通常の読み取りコマンド1104には2クロック・ティック必要である。本開示の修正されたコマンドは、読み取りコマンドおよび書込みコマンドをCASコマンドによって修正する。2ビットのCASコマンドおよび2ビットの読み取りコマンドまたは書込みコマンドを得るには合計で4ティック必要である。したがって、図示のように、修正された書込みコマンド1106はWR、WR、CAS、CASとして提示され、修正された読み取りコマンド1108はRD、RD、CAS、CASとして提示される。しかし、メモリバス418を介して送られるデータの純減によって、コマンドがわずかに多くのビットを使用するにもかかわらず、電力が削減される。修正された書込みコマンド1106および修正された読み取りコマンド1108が例示的なものであり、代替コマンドが使用されてもよいことを諒解されたい。同様に、CASコマンドは、本開示の範囲から逸脱せずに書込みコマンドまたは読み取りコマンドの前に位置させることができる。さらに、修正された読み取りコマンドを使用する代わりに、ホスト・プロセッサ602が通常の読み取りコマンドを送ってもよく、メモリ・システム604が、バック・チャネル・レーン634を使用して、統合されたデータがホスト・プロセッサ602に送られることをホスト・プロセッサ602に対して示すことに留意されたい。バック・チャネル・レーン634はコマンド/アドレス/クロック・ブロック622から延

30

40

50

びるよう示されているが、他のバックチャネルを使用できることを諒解されたい。たとえば、バックチャネルはデータレーンIOブロック(たとえば、データレーンIOブロック620(1)または620(2))からの追加のDQレーンであってもよい。

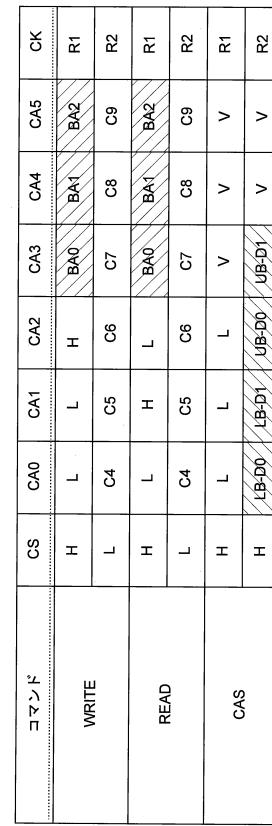

#### 【0048】

図12は、例示的な書込みおよび読み取りコマンド真理値表である。コマンドバスは、チップセレクト(CS)とコマンドアドレスバスの6つのレーン(CA0～CA5)とからなる。通常の書込みおよび読み取りコマンドプロトコル(コマンドコード、バンクアドレス(BA)、列アドレス(C4～C9))が2クロックティックにわたって転送される。低減IOレーン書込みおよび読み取りの場合、書込みコマンドおよび読み取りコマンドは、図11に示す修正されたコマンド1106および1108のような低減IOレーンコマンド(書込みコマンドの場合はWR\_X1またはWR\_X2またはWR\_X4、読み取りコマンドの場合はRD\_X1またはRD\_X2またはRD\_X4)の種類を通知するためにCASコマンドによって修正されてもよい。CASコマンドは、コマンドコードと、DQバイト当たりの低減IO(下位DQバイト(DQ0～DQ7)の場合はLB-D0、LB-D1、上位DQバイト(DQ8～DQ15)の場合はUB-D0、UB-D1)とを含む。たとえば、書込みコマンドおよびCASコマンドに関して(LB-D0, LB-D1)=00および(UB-D0, UB-D1)=10であるとき、メモリシステムは、下位DQバイトの場合は通常の書込みを行い、上位DQバイトの場合は低減IOレーン書込み(たとえば、WR\_X1)を行う。本開示の例示的な態様を実行するようにさらに他の真理値表が構成されてもよい。

10

#### 【0049】

さらに、それぞれに異なる書込みコマンド間の差を示す代わりに(またはそれぞれに異なる書込みコマンド間の差を示すことに加えて)、CASコマンドを使用して、より大きい書込みコマンドからどのくらいの長さのデータ統合が行われるかを示すことができることに留意されたい。たとえば、データ統合は、16BLの第1または第2の8つのビートあるいは32BLの第1、第2、第3、または第4の8つのビートに対して行われる。

20

#### 【0050】

同様に、バックチャネルレーン634を使用すると、修正された読み取りコマンド1108をなくすことが可能になる場合があることを諒解されたい。例示的な態様では、バックチャネルレーン634はデータマスク(DM)レーンであってもよい。DMレーンは、データレーンIOブロック620(1)および620(2)に結合されてもよい。通常、DMビートが「H」である場合、対応するDQバイトはメモリアレイに書き込まれないが、従来、DMレーンは書込みコマンドの間にのみ使用される。したがって、DMレーンは、読み取りコマンドに対する応答の間使用できるようにオープンされる。そのような場合、特定のDMレーンがアサートされると、そのことは、読み取りコマンドに応答してデータ統合が行われることを示す。

30

#### 【0051】

上記の説明は転送中のデータ内の垂直繰り返しに基づくデータ統合を企図しているが、本開示がそのように限定されないことに留意されたい。この点に関して、図13は、8ビットごとに繰り返される状況を示す。データ統合はそのような場合でも行われてもよく、第1の繰り返しビットがD0、D8、D16、D24などにマップされ、第2の繰り返しビットがD1、D9、D17、D25などにマップされ、以下同様である。しかし、繰り返しビットはデータレーンDQ0上でのみ送られ、上記で略述したように電力が節約される。

40

#### 【0052】

本明細書で開示する態様による、メモリシステムのための省電力化技法は、任意のプロセッサベースのデバイス内に設けられるか、またはその中に組み込まれてもよい。例には、限定はしないが、セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、全地球測位システム(GPS)デバイス、モバイルフォン、セルラーフォン、スマートフォン、セッション開始プロトコル(SIP)フォン、タブレット、ファブレット、サーバ、コンピュータ、ポータブルコンピュータ、モバイルコンピューティングデバイス、装着型コンピューティングデバイス(たとえば、スマートウォッチ、ヘルスまたはフィットネストラッカー、アイウェアなど)、デスクトップコンピュータ、携帯情報端末(PDA)、モ

50

ニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、ポータブルデジタルビデオプレーヤ、自動車、車両構成要素、アビオニクスシステム、ドローン、およびマルチコプターが含まれる。

#### 【0053】

これに関して、図14は、図4～図6に示すホストプロセッサ402、502、および602、ならびにメモリシステム404、504、および604を使用することができるプロセッサベースのシステム1400の一例を示す。この例では、プロセッサベースのシステム1400は、ホストプロセッサ402、502、または602であってもよい1つまたは複数のプロセッサ1404を各々が含む1つまたは複数のCPU1402を含む。CPU1402は、一時的に記憶されているデータに迅速にアクセスするために、プロセッサ1404に結合されたキャッシュメモリ1406を有してもよい。CPU1402は、プロセッサベースのシステム1400内に含まれるデバイスを相互結合することができるシステムバス1408に結合される。システムバス1408は、システムバス414または614であってもよい。よく知られているように、CPU1402は、システムバス1408を介してアドレス情報、制御情報、およびデータ情報を交換することによって、これらの他のデバイスと通信する。たとえば、CPU1402は、メモリコントローラ412または612であってもよいメモリコントローラ1410にバストランザクション要求を伝達することができる。図14には示していないが、複数のシステムバス1408を設けることができる。

#### 【0054】

他のデバイスをシステムバス1408に接続することができる。図14に示すように、これらのデバイスは、例として、メモリシステム404、504、または604であってもよいメモリシステム1412と、1つまたは複数の入力デバイス1414と、1つまたは複数の出力デバイス1416と、1つまたは複数のネットワークインターフェースデバイス1418と、1つまたは複数のディスプレイコントローラ1420とを含むことができる。入力デバイス1414は、入力キー、スイッチ、音声プロセッサなどを含むが、これらに限定されない、任意のタイプの入力デバイスを含むことができる。出力デバイス1416は、限定はしないが、オーディオ、ビデオ、他の視覚的インジケータなどを含む任意のタイプの出力デバイスを含むことができる。ネットワークインターフェースデバイス1418は、ネットワーク1422との間のデータの交換を可能にするように構成される任意のデバイスとすることができます。ネットワーク1422は、限定はしないが、有線ネットワークまたはワイヤレスネットワーク、プライベートネットワークまたは公衆ネットワーク、ローカルエリアネットワーク(LAN)、ワイヤレスローカルエリアネットワーク(WLAN)、ワイドエリアネットワーク(WAN)、BLUETOOTH(登録商標)ネットワーク、およびインターネットを含む、任意のタイプのネットワークであってよい。ネットワークインターフェースデバイス1418は、所望の任意のタイプの通信プロトコルをサポートするように構成することができます。

#### 【0055】

CPU1402はまた、1つまたは複数のディスプレイ1424に送信される情報を制御するために、システムバス1408を介してディスプレイコントローラ1420にアクセスするように構成されてもよい。ディスプレイコントローラ1420は、1つまたは複数のビデオプロセッサ1426を介して表示されるように情報をディスプレイ1424へ送り、ビデオプロセッサ1426は、表示すべき情報を処理してディスプレイ1424に適したフォーマットにする。ディスプレイ1424は、限定はしないが、陰極線管(CRT)、液晶ディスプレイ(LCD)、プラズマディスプレイ、発光ダイオード(LED)ディスプレイなどを含む、任意のタイプのディスプレイを含むことができる。

#### 【0056】

本明細書で開示する態様に関して説明した様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムが、電子ハードウェア、メモリの中もしくは別のコンピュータ可読媒体の中に記憶されるとともにプロセッサもしくは他の処理デバイスによって実行される命令、または両方の組合せとして実装されてもよいことを、当業者はさらに諒解されよ

う。本明細書で説明するデバイスは、例として、回路、ハードウェア構成要素、IC、またはICチップにおいて利用されてもよい。本明細書で開示されるメモリは、任意のタイプおよびサイズのメモリであってもよく、所望の任意のタイプの情報を記憶するように構成されてもよい。この互換性を明確に示すために、様々な例示的な構成要素、ロック、モジュール、回路、およびステップについて、概してそれらの機能に関して上記において説明した。そのような機能がどのように実装されるのかは、特定の適用例、設計選択、およびまたはシステム全体に課される設計制約によって決まる。当業者は、特定の適用例ごとに様々な方式で記載の機能を実装してもよいが、そのような実装の決定が、本開示の範囲からの逸脱を引き起こすと解釈されるべきではない。

#### 【 0 0 5 7 】

本明細書で開示される態様とともに説明した様々な例示的論理ブロック、モジュール、および回路は、プロセッサ、DSP、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブル論理デバイス、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書で説明した機能を実施するように設計されたそれらの任意の組合せとともに実装または実施されてもよい。プロセッサは、マイクロプロセッサであってもよいが、代替として、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンであってもよい。プロセッサはまた、コンピューティングデバイスの組合せ(たとえば、DSPとマイクロプロセッサとの組合せ、複数のマイクロプロセッサ、DSPコアと連携した1つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成)としても実装されてもよい。

#### 【 0 0 5 8 】

本明細書で開示する態様は、ハードウェアにおいて具現化されてもよく、かつハードウェアに記憶され、たとえば、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、電気的プログラマブルROM(EPROM)、電気的消去可能プログラマブルROM(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野において知られている任意の他の形態のコンピュータ可読媒体の中に存在してもよい命令において具現化されてもよい。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り記憶媒体に情報を書き込むことができるようプロセッサに結合される。代替形態において、記憶媒体は、プロセッサと一体化してもよい。プロセッサおよび記憶媒体は、ASICの中に存在する場合がある。ASICは、リモート局の中に存在する場合がある。代替形態において、プロセッサおよび記憶媒体は、個別構成要素としてリモート局、基地局、またはサーバ内に存在する場合がある。

#### 【 0 0 5 9 】

本明細書の例示的な態様のいずれかにおいて説明する動作ステップが、例示および説明のために記載されていることにも留意されたい。説明する動作は、図示のシーケンス以外の数多くの異なるシーケンスにおいて実行される場合がある。さらに、単一の動作ステップにおいて説明する動作は、実際にはいくつかの異なるステップにおいて実行される場合がある。さらに、例示的な態様において説明する1つまたは複数の動作ステップは組み合わせられる場合がある。当業者には容易に明らかになるように、流れ図に示される動作ステップが数多くの異なる変更を受ける場合があることを理解されたい。情報および信号が様々な異なる技術および技法のいずれかを使用して表される場合があることも当業者は理解されよう。たとえば、上記の説明全体にわたって参照される場合があるデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁気粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表されてもよい。

#### 【 0 0 6 0 】

本開示のこれまでの説明は、任意の当業者が本開示を作製または使用できるようにするために提供される。本開示の様々な変更が当業者に容易に明らかになり、本明細書で定義する一般原理は、本開示の趣旨または範囲から逸脱することなく他の変形形態に適用されてもよい。したがって、本開示は、本明細書で説明した例および設計に限定されるものでな

10

20

30

40

50

く、本明細書で開示する原理および新規の特徴と一致する最も広い範囲を与えるべきである。

【符号の説明】

【0061】

|                 |                    |

|-----------------|--------------------|

| 10              | 従来のコンピューティングデバイス   |

| 12              | ホストプロセッサ           |

| 14              | メモリシステム            |

| 16              | デジタル信号プロセッサ(DSP)   |

| 18              | マルチメディアエンジン        |

| 20              | マルチコア中央処理ユニット(CPU) |

| 22              | メモリコントローラ          |

| 24              | システムバス             |

| 26              | メモリインターフェース物理層     |

| 28              | メモリバス              |

| 30(1) ~ 30(2)   | データレーンIOブロック       |

| 32              | コマンド/アドレス/クロックブロック |

| 34              | デコーダおよびデータラッ奇      |

| 36(1) ~ 36(N)   | メモリバンク             |

| 200             | コードスニペット           |

| 202、204         | 領域                 |

| 210             | データブロック            |

| 212、214         | 領域                 |

| 300             | データバースト            |

| 310             | データブロック            |

| 312             | スロットD0 ~ D7        |

| 314             | スロットD16 ~ D23      |

| 316             | スロットD24 ~ D31      |

| 322、324         | グループ               |

| 330             | データブロック            |

| 332、334、336、338 | グループ               |

| 30              | コンピューティングデバイス      |

| 400             | コンピューティングデバイス      |

| 402             | ホストプロセッサ           |

| 404             | メモリシステム            |

| 406             | DSP                |

| 408             | GPUおよびマルチメディアエンジン  |

| 410             | マルチコアCPU           |

| 412             | メモリコントローラ          |

| 414             | システムバス             |

| 416             | メモリインターフェースPHY     |

| 418             | メモリバス              |

| 40              | データレーンIOブロック       |

| 420(1) ~ 420(2) | データレーンIOブロック       |

| 422             | コマンド/アドレス/クロックブロック |

| 424             | デコーダおよびデータラッ奇      |

| 426(1) ~ 426(N) | メモリバンク             |

| 430             | データパターンチェック論理回路    |

| 432             | メモリアドレスルックアップテーブル  |

| 434             | 読み取りデータコピーレジスタ     |

| 436(1) ~ 436(2) | 書き込みデータコピーレジスタ     |

| 500             | コンピューティングデバイス      |

| 502             | ホストプロセッサ           |

|                             |    |

|-----------------------------|----|

| 504 メモリシステム                 |    |

| 520(1)~520(2) データレーンI/Oブロック |    |

| 522 コマンド/アドレス/クロックブロック      |    |

| 524 デコーダおよびデータラッチ           |    |

| 526(1)~526(N) メモリバンク        |    |

| 528 内部書き込みデータコピー・レジスタ       |    |

| 600 コンピューティングデバイス           |    |

| 602 ホストプロセッサ                |    |

| 604 メモリシステム                 |    |

| 606 DSP                     | 10 |

| 608 GPUおよびマルチメディアエンジン       |    |

| 610 マルチコアCPU                |    |

| 612 メモリコントローラ               |    |

| 614 システムバス                  |    |

| 616 メモリインターフェースPHY          |    |

| 618 メモリバス                   |    |

| 620(1)~620(2) データレーンI/Oブロック |    |

| 622 コマンド/アドレス/クロックブロック      |    |

| 624 デコーダおよびデータラッチ           |    |

| 626(1)~626(N) メモリバンク        | 20 |

| 628 書き込みデータコピー・レジスタ         |    |

| 630 データパターンチェック・論理回路        |    |

| 632 読取りデータパターンチェック・論理回路     |    |

| 634 バックチャネルレーン              |    |

| 636 読取りデータコピー・レジスタ          |    |

| 700 書き込み動作プロセス              |    |

| 800 読取り動作プロセス               |    |

| 900 書き込みデータバス               |    |

| 902 コマンドデコーダ                |    |

| 904 データコピー制御ブロック回路          | 30 |

| 906(1)~906(M) ゲーティング論理回路    |    |

| 908(1)~908(M) レジスタ          |    |

| 910 書き込みデータ先入れ先出し(FIFO)バッファ |    |

| 1000 データパターンチェック・論理回路       |    |

| 1002 データバス                  |    |

| 1004(1)~1004(8) バイトチェック     |    |

| 1006 パケットチェック               |    |

| 1008 制御論理                   |    |

| 1102 通常の書き込みコマンド            |    |

| 1104 通常の読み取りコマンド            |    |

| 1106 修正された書き込みコマンド          | 40 |

| 1108 修正された読み取りコマンド          |    |

| 1400 プロセッサベースのシステム          |    |

| 1402 CPU                    |    |

| 1404 プロセッサ                  |    |

| 1406 キャッシュメモリ               |    |

| 1408 システムバス                 |    |

| 1410 メモリコントローラ              |    |

| 1412 メモリシステム                |    |

| 1414 入力デバイス                 | 50 |

1416 出力デバイス

1418 ネットワークインターフェースデバイス

1420 ディスプレイコントローラ

1422 ネットワーク

1424 ディスプレイ

1426 ビデオプロセッサ

C4 ~ C9 列アドレス

CA0 ~ CA5 レーン

D0 ~ D127 スロット

DQ0 ~ DQ15 データレーン

【図面】

【図1】

【図2 A】

| ELF           |             |             |

|---------------|-------------|-------------|

| D0            | D1          | D2 D3       |

| 7F 45 4C 46   | 01 01 01 00 | 00 00 00 00 |

| 03 00 28 00   | 01 00 00 00 | 00 00 00 00 |

| 5C 31 00 [00] | 00 00 00 05 | 34 00 20 00 |

| 16 00 15 00   | 06 00 00 00 | 34 00 00 00 |

| 34 00 [00]    | 00 01 00 00 | 00 01 00 00 |

| 04 00 [00]    | 03 00 00 00 | 34 01 00 00 |

| 34 01 [00]    | 13 00 00 00 | 04 00 00 00 |

| 01 00 [00]    | 01 00 00 00 | 00 00 00 00 |

| 00 00 [00]    | B7 23 00 00 | 05 00 00 00 |

| 00 10 [00]    | 01 00 00 00 | 98 2E 00 00 |

| 98 3E [00]    | 6C 01 00 00 | 70 01 00 00 |

| 00 10 [00]    | 02 00 00 00 | A4 2E 00 00 |

| A4 3E [00]    | 08 01 00 00 | 08 01 00 00 |

| 04 00 [00]    | 51 E5 00 00 | 00 00 00 00 |

FIG. 2A

10

20

30

40

50

【図2B】

### 【図3A】

| バーストデータ(バースト長=16) |       |        |        |        |        |     |     |     |     |     |     | no_data_copy |      |      |      |      |

|-------------------|-------|--------|--------|--------|--------|-----|-----|-----|-----|-----|-----|--------------|------|------|------|------|

| Q0                | D0~F  | D8~5C  | D16~34 | D24~34 | D32~00 | D40 | D48 | D56 | D64 | D72 | D80 | D88          | D96  | D104 | D112 | D120 |

| Q1                | D1~45 | D9~31  | D17~00 | D25~01 | D33~00 | D41 | D49 | D57 | D65 | D73 | D81 | D89          | D97  | D105 | D113 | D121 |

| Q2                | D2~4C | D10~00 | D18~00 | D26~00 | D34~00 | D42 | D50 | D58 | D66 | D74 | D82 | D90          | D98  | D106 | D114 | D122 |

| Q3                | D3~46 | D11~00 | D19~00 | D27~00 | D35~00 | D43 | D51 | D59 | D67 | D75 | D83 | D91          | D99  | D107 | D115 | D123 |

| Q4                | D4~63 | D12~00 | D20~04 | D28~01 | D36~00 | D44 | D52 | D60 | D68 | D76 | D84 | D92          | D100 | D108 | D116 | D124 |

| Q5                | D5~60 | D13~00 | D21~00 | D29~00 | D37~10 | D45 | D53 | D61 | D69 | D77 | D85 | D93          | D101 | D109 | D117 | D125 |

| Q6                | D6~28 | D14~15 | D22~00 | D30~00 | D38~00 | D46 | D54 | D62 | D70 | D78 | D86 | D94          | D102 | D110 | D118 | D126 |

| Q7                | D7~00 | D15~00 | D23~00 | D31~00 | D39~00 | D47 | D55 | D63 | D71 | D79 | D87 | D95          | D103 | D111 | D119 | D127 |

【図3B】

| バーストデータ(バースト長=6) |        |        |        |        |     |     |     |     |     |     |     | data_copy_B (k=8) |      |      |      |      |      |      |      |      |      |      |      |      |

|------------------|--------|--------|--------|--------|-----|-----|-----|-----|-----|-----|-----|-------------------|------|------|------|------|------|------|------|------|------|------|------|------|

| 0                | D00/00 | D8/00  | D16/01 | D24/FF | D32 | D40 | D48 | D56 | D64 | D72 | D80 | D88               | D96  | D104 | D112 | D120 | D128 | D136 | D144 | D152 | D160 | D168 | D176 |      |

| 1                | D11/00 | D9/00  | D17/01 | D25/FF | D33 | D41 | D49 | D57 | D65 | D73 | D81 | D89               | D97  | D105 | D113 | D121 | D129 | D137 | D145 | D153 | D161 | D169 | D177 | D185 |

| 2                | D22/00 | D10/00 | D18/01 | D26/FF | D34 | D42 | D50 | D58 | D66 | D74 | D82 | D90               | D98  | D106 | D114 | D122 | D130 | D138 | D146 | D154 | D162 | D170 | D178 | D186 |

| 3                | D33/00 | D11/00 | D19/01 | D27/FF | D35 | D43 | D51 | D59 | D67 | D75 | D83 | D91               | D99  | D107 | D115 | D123 | D131 | D139 | D147 | D155 | D163 | D171 | D179 | D187 |

| 4                | D44/00 | D12/00 | D20/01 | D28/FF | D36 | D44 | D52 | D60 | D68 | D76 | D84 | D92               | D100 | D108 | D116 | D124 | D132 | D140 | D148 | D156 | D164 | D172 | D180 | D188 |

| 5                | D55/00 | D13/00 | D21/01 | D29/FF | D37 | D45 | D53 | D61 | D69 | D77 | D85 | D93               | D101 | D109 | D117 | D125 | D133 | D141 | D149 | D157 | D165 | D173 | D181 | D189 |

| 6                | D66/00 | D14/00 | D22/01 | D30/FF | D38 | D46 | D54 | D62 | D70 | D78 | D86 | D94               | D102 | D110 | D118 | D126 | D134 | D142 | D150 | D158 | D166 | D174 | D182 | D190 |

| 7                | D77/00 | D15/00 | D23/01 | D31/FF | D39 | D47 | D55 | D63 | D71 | D79 | D87 | D95               | D103 | D111 | D119 | D127 | D135 | D143 | D151 | D159 | D167 | D175 | D183 | D191 |

【図3C】

【図 3 D】

【図 7】

【図 8】

【図 9】

【図 10】

10

20

30

40

50

【図 1-1】

【図 1-2】

【図 1-3】

【図 1-4】

## フロントページの続き

(51)国際特許分類 F I

G 0 6 F 13/38 (2006.01) G 0 6 F 13/38 3 3 0 Z

## (33)優先権主張国・地域又は機関

米国(US)

1 2 1 · サン・ディエゴ・モアハウス・ドライブ · 5 7 7 5

(72)発明者 マイケル・ハウゼン・ロ

アメリカ合衆国・カリフォルニア · 9 2 1 2 1 · サン・ディエゴ・モアハウス・ドライブ · 5 7 7

5

審査官 打出 義尚

(56)参考文献 国際公開第 2 0 1 5 / 0 4 2 4 6 9 (WO, A 1)

米国特許出願公開第 2 0 1 5 / 0 1 8 6 2 8 2 (US, A 1)

米国特許第 0 7 6 3 1 2 0 7 (US, B 1)

特開平 1 0 - 0 1 1 3 6 0 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

G 0 6 F 1 3 / 1 2

G 0 6 F 1 2 / 0 0

G 0 6 F 1 2 / 0 2

G 0 6 F 1 3 / 1 6

G 0 6 F 1 3 / 3 6

G 0 6 F 1 3 / 3 8