### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

# (10) International Publication Number WO 2011/159581 A2

- (43) International Publication Date 22 December 2011 (22.12.2011)

- (51) International Patent Classification: H01L 45/00 (2006.01) H01L 27/24 (2006.01)

- (21) International Application Number:

PCT/US2011/040103

(22) International Filing Date:

10 June 2011 (10.06.2011)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

61/356,327 18 June 2010 (18.06.2010) US 61/467,936 25 March 2011 (25.03.2011) US 13/157,191 9 June 2011 (09.06.2011) US

- (71) Applicant (for all designated States except US): SAN-DISK 3D LLC [US/US]; 601 Mccarthy Boulevard, Milpitas, CA 95035 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): KREUPL, Franz [DE/DE]; 601 McCarthy Boulevard, Milpitas, CA 95035 (US). COSTA, Xiying [US/US]; 601 McCarthy Boulevard, Milpitas, CA 95035 (US). KAI, James [US/US]; 601 McCarthy Boulevard, Milpitas, CA 95035 (US). MAKALA, Raghuveer, S. [IN/US]; 601 McCarthy Boulevard, Milpitas, CA 95035 (US).

- (74) Agent: MAGEN, Burt; Vierra Magen Marcus & DeNiro, LLP, 575 Market Street, Suite 2500, San Francisco, CA 94105 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report (Rule 48.2(g))

(54) Title: MEMORY CELL WITH RESISTANCE-SWITCHING LAYERS

Fig. 6C

(57) Abstract: A memory device in a 3-D read and write memory includes memory cells. Each memory cell includes a resistance-switching memory element (RSME) in series with a steering element. The RSME has first and second resistance-switching layers on either side of a conductive intermediate layer, and first and second electrodes at either end of the RSME. The first and second resistance-switching layers can both have a bipolar or unipolar switching characteristic. In a set or reset operation of the memory cell, an electric field is applied across the first and second electrodes. An ionic current flows in the resistance-switching layers, contributing to a switching mechanism. An electron flow, which does not contribute to the switching mechanism, is reduced due to scattering by the conductive intermediate layer, to avoid damage to the steering element. Particular materials and combinations of materials for the different layers of the RSME are provided.

-1-

# MEMORY CELL WITH RESISTANCE-SWITCHING LAYERS

### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the benefit of U.S. provisional pat. app. no. 61/356,327, filed June 18, 2010, (docket no.: SAND-01478US0), and U.S. provisional pat. app. no. 61/467,936, filed March 25, 2011 (docket no.: SAND-01478US1), both of which are incorporated herein by reference.

#### **BACKGROUND**

[0002] The present technology relates to data storage.

[0003] A variety of materials show reversible resistance-change or resistance-switching behavior in which the resistance of the material is a function of the history of the current through, and/or voltage across, the material. These materials include chalcogenides, carbon polymers, perovskites, and certain metal oxides (MeOx) and metal nitrides (MeN). Specifically, there are metal oxides and nitrides which include only one metal and exhibit reliable resistance switching behavior. This group includes, for example, Nickel Oxide (NiO), Niobium Oxide (Nb2O5), Titanium Dioxide (TiO2), Hafnium Oxide (HfO2) Aluminum Oxide (Al2O3), Magnesium Oxide (MgOx), Chromium Dioxide (CrO2), Vanadium Oxide (VO), Boron Nitride (BN), and Aluminum Nitride (AlN), as described by Pagnia and Sotnick in "Bistable Switching in Electroformed Metal-Insulator-Metal Device," Phys. Stat. Sol. (A) 108, 11-65 (1988). A resistance-switching layer (RSL) of one of these materials may be formed in an initial state, for example, a relatively low-resistance state. Upon application of sufficient voltage, the material switches to a stable high-resistance state which is maintained even after the voltage is removed. This resistance switching is reversible such that subsequent application of an appropriate current or voltage can serve to return the RSL to a stable low-resistance state which is maintained even after the voltage or current is removed. This conversion can be repeated many times. For some materials, the initial state is highresistance rather than low-resistance. A set process may refer to switching the material from high to low resistance, while a reset process may refer to switching the material from low to

high resistance. A resistance-switching memory element (RSME) can include a RSL positioned between first and second electrodes.

[0004] These reversible resistance-change materials are of interest for use in nonvolatile memory arrays. One resistance state may correspond to a data "0," for example, while the other resistance state corresponds to a data "1." Some of these materials may have more than two stable resistance states. Moreover, in a memory cell, the RSME can be in series with a steering element such as a diode, which selectively limits the voltage across, and/or the current flow through, the RSME. For example, a diode can allow current to flow in only one direction of the RSME while essentially preventing a current flow in the opposite direction. Such a steering element itself is not typically a resistance-change material. Instead, the steering element allows a memory cell to be written to, and/or read from, without affecting the state of other memory cells in an array.

[0005] Non-volatile memories that have storage elements or cells formed from resistance-change materials are known. For example, U.S. Patent Application Publication No. 2006/0250836, titled "Rewriteable Memory Cell Comprising A Diode And A Resistance-Switching Material," incorporated herein by reference, describes a rewriteable non-volatile memory cell that includes a diode coupled in series with a resistance-change material such as a MeOx or MeN.

[0006] However, there is a continuing need for technologies which allow memory cells to be scaled down in size.

# BRIEF DESCRIPTION OF THE DRAWINGS

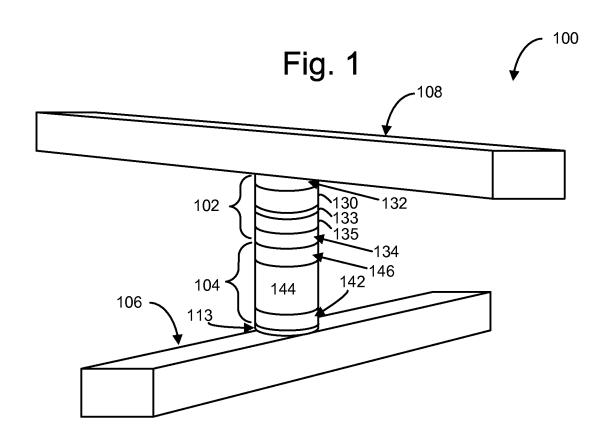

[0007] FIG. 1 is a simplified perspective view of one embodiment of a memory cell which includes a RSME in series with a steering element.

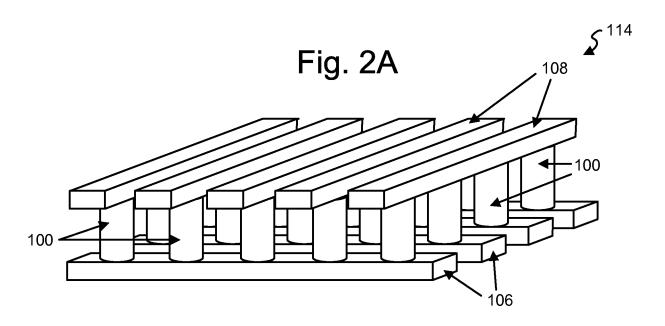

[0008] FIG. 2A is a simplified perspective view of a portion of a first memory level formed from a plurality of the memory cells of FIG. 1.

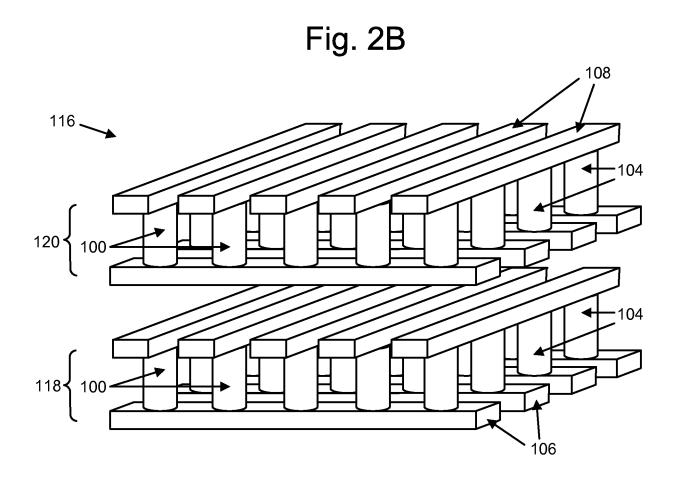

[0009] FIG. 2B is a simplified perspective view of a portion of a three-dimensional memory array formed from a plurality of the memory cells of FIG. 1.

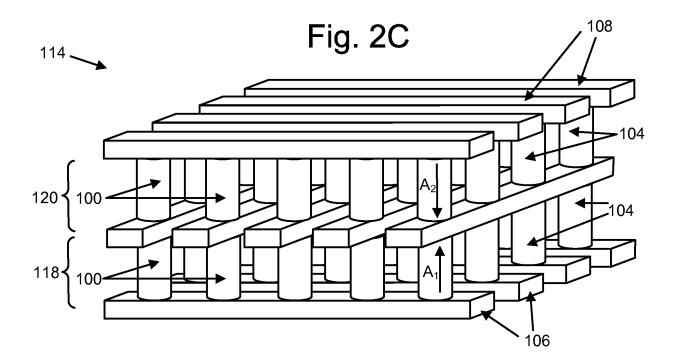

[0010] FIG. 2C is a simplified perspective view of a portion of a three-dimensional memory array formed from a plurality of the memory cells of FIG. 1.

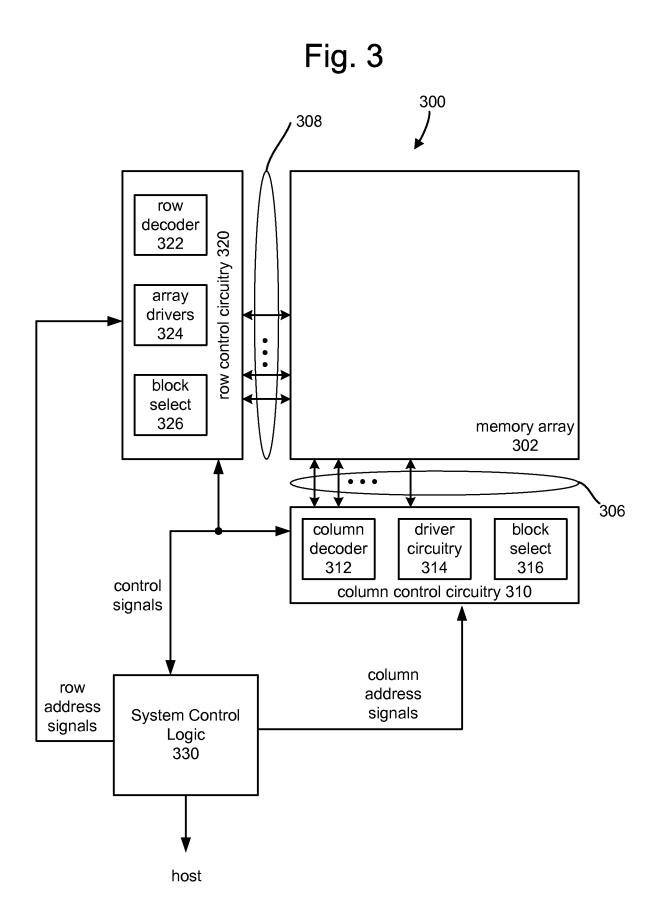

[0011] FIG. 3 is a block diagram of one embodiment of a memory system.

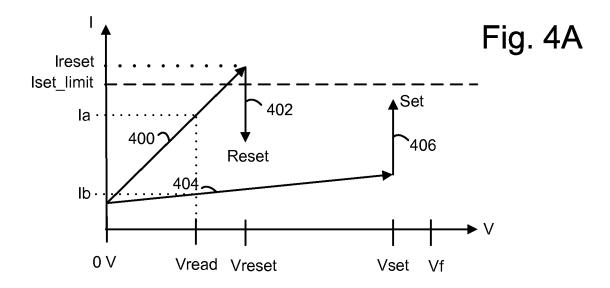

[0012] FIG. 4A is a graph depicting I-V characteristics of an example unipolar RSL.

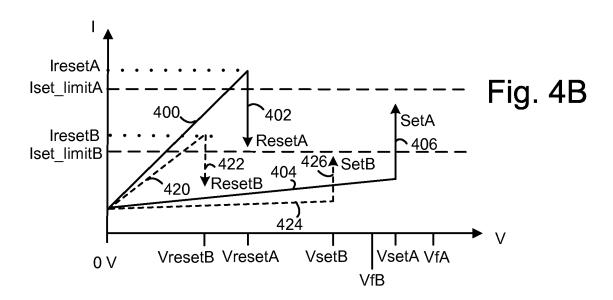

[0013] FIG. 4B is a graph depicting different I-V characteristics of two example unipolar

RSLs.

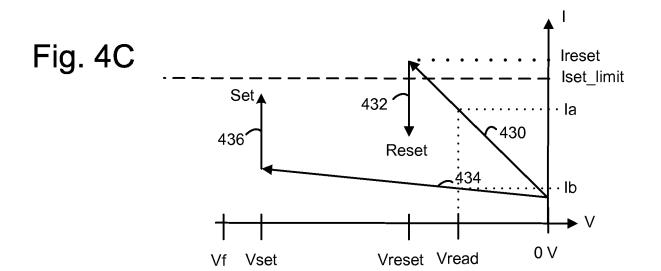

- [0014] FIG. 4C is a graph depicting I-V characteristics of another example unipolar RSL.

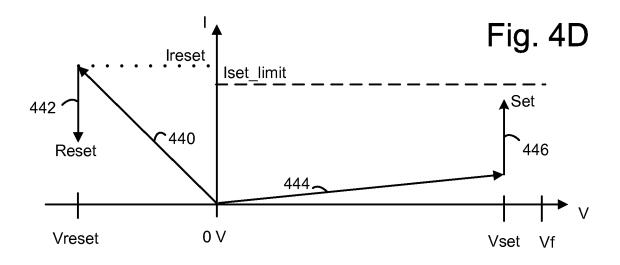

- [0015] FIG. 4D is a graph depicting I-V characteristics of an example bipolar RSL.

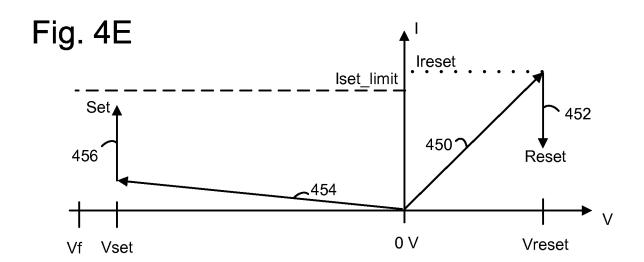

- [0016] FIG. 4E is a graph depicting I-V characteristics of another example bipolar RSL.

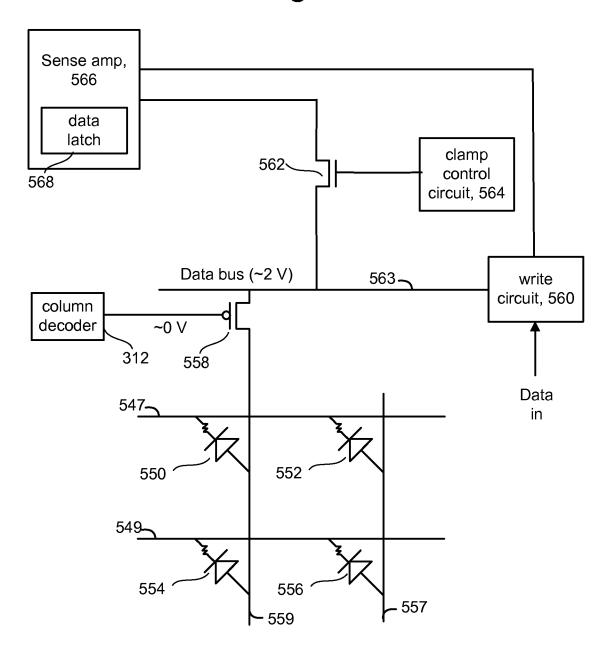

- [0017] FIG. 5 depicts an embodiment of a circuit for reading the state of a memory cell.

- [0018] FIG. 6A depicts an example memory cell having a RSME and a steering element (SE) below the RSME.

- [0019] FIG. 6B depicts an alternative configuration of a memory cell having a RSME, where the steering element (SE) is above the RSME.

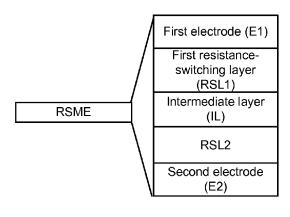

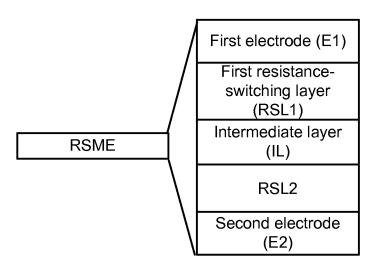

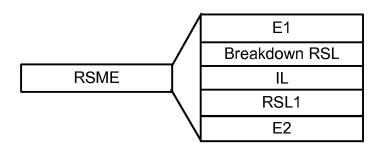

- [0020] FIG. 6C depicts an example implementation of the RSME of FIG. 6A as a mirror resistive switch (MRS) in a vertical stack.

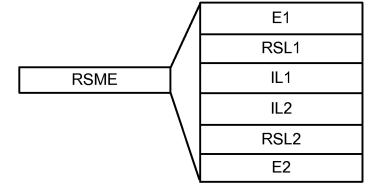

- [0021] FIG. 6D depicts an example implementation of the RSME of FIG. 6A using multiple intermediate layers (ILs) between RSLs.

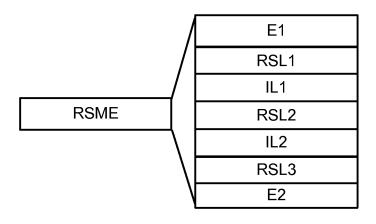

- [0022] FIG. 6E depicts an example implementation of the RSME of FIG. 6A using a repeating RSL/IL pattern.

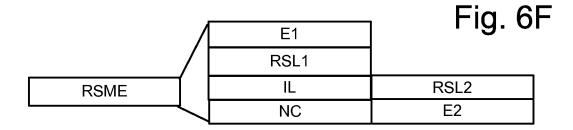

- [0023] FIG. 6F depicts an example implementation of the RSME of FIG. 6A where each layer of the RSME extends horizontally and one or more of the layers are arranged end-to-end.

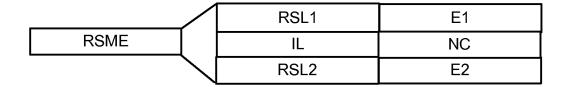

- [0024] FIG. 6G depicts another example implementation of the RSME of FIG. 6A where each layer of the RSME extends horizontally and one or more of the layers are arranged end-to-end.

- [0025] FIG. 6H depicts another example implementation of the RSME of FIG. 6A where each layer of the RSME extends vertically.

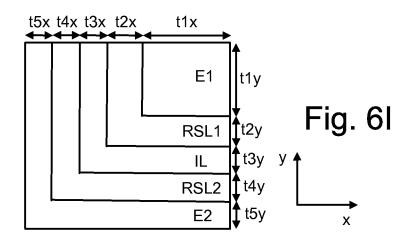

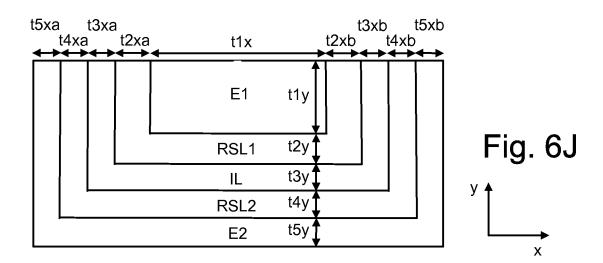

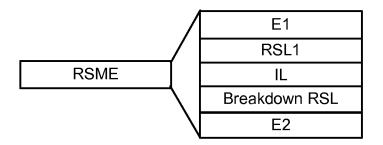

- [0026] FIG. 6I depicts another example implementation of the RSME of FIG. 6A which includes L-shaped portions for RSL1, IL, RSL2 and E2.

- [0027] FIG. 6J depicts another example implementation of the RSME of FIG. 6A which includes U-shaped portions for RSL1, IL, RSL2 and E2.

- [0028] FIG. 6K1 depicts an example implementation of the RSME of FIG. 6A which uses one RSL and one breakdown layer, below the RSL.

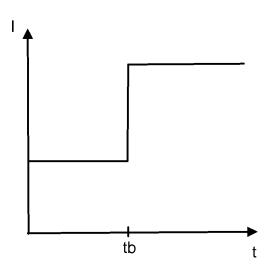

[0029] FIG. 6K2 is a graph showing a transition from an initial state to a breakdown state for a breakdown layer.

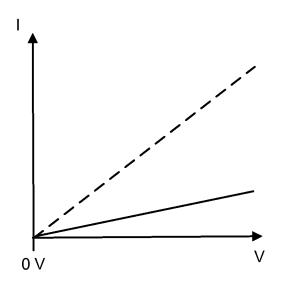

[0030] FIG. 6K3 is a graph showing an I-V characteristic of a breakdown layer in an initial state (solid line) and in a breakdown state (dashed line).

[0031] FIG. 6L depicts an example implementation of the RSME of FIG. 6A which uses one RSL and one breakdown layer, above the RSL.

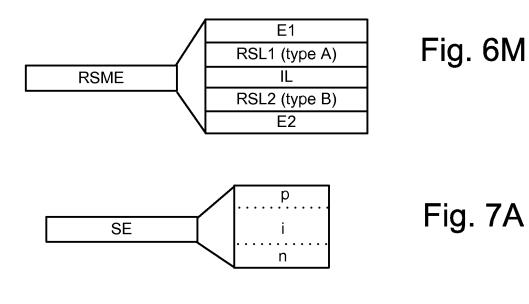

[0032] FIG. 6M depicts an example implementation of the RSME of FIG. 6A, in which the RSLs are of different types.

[0033] FIG. 7A depicts an example implementation of the steering element (SE) of the memory cell FIG. 6A as an Si diode.

[0034] FIG. 7B depicts an example implementation of the steering element (SE) of the memory cell of FIG. 6A as a punch-through diode.

[0035] FIG. 8 depicts an example implementation of the memory cell of FIG. 6A connected between a bit line and a word line.

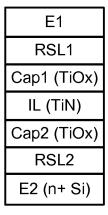

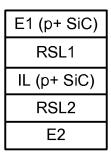

[0036] FIG. 9A depicts an embodiment of the RSME of FIG. 6C in which E1 is made of Co, CoSi, n+ Si, p+ Si or p+ SiC, and E2 is made of n+ Si.

[0037] FIG. 9B depicts an embodiment of the RSME of FIG. 6C in which E1 and the IL are made of p+ SiC, and E2 is made of n+ Si, n+ SiC or p+ SiC.

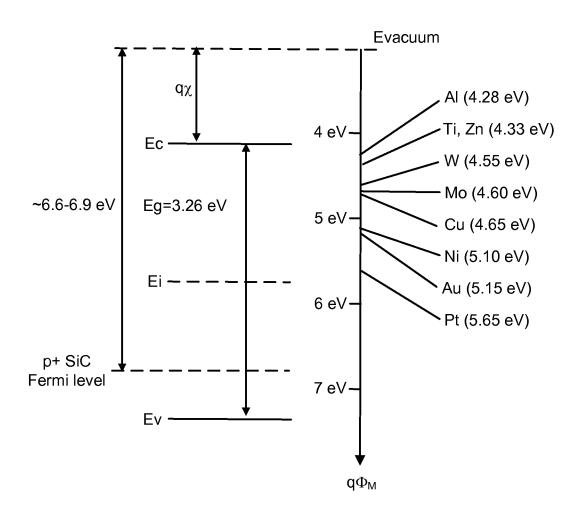

[0038] FIG. 9C is a diagram depicting the Fermi level of p+ SiC relative to other materials.

[0039] FIG. 10A depicts an embodiment of the RSME of FIG. 6C describing alternative IL materials.

[0040] FIG. 10B depicts an embodiment of the RSME of FIG. 6C in an inverted, mirror stack configuration.

[0041] FIG. 10C depicts an embodiment of the RSME of FIG. 6C in an asymmetric, upright stack configuration.

[0042] FIG. 10D depicts an embodiment of the RSME of FIG. 6A in an asymmetric, inverted stack configuration.

[0043] FIG. 11A depicts an embodiment of the RSME of FIG. 6C showing the growth of SiOx when E2 is n+ Si.

[0044] FIG. 11B depicts an embodiment of the RSME of FIG. 6C showing the growth of a low band gap material such as TiOx when E2 is TiN.

[0045] FIG. 11C depicts an embodiment of the RSME of FIG. 6C in which the RSLs are made of a doped metal oxide to reduce operating voltage.

[0046] FIG. 11D depicts an embodiment of the RSME of FIG. 11C in which E2 is TiN instead of n+ Si.

[0047] FIG. 11E depicts an embodiment of the RSME of FIG. 6C in an asymmetric mirror cell configuration, where the RSLs are made of different materials.

[0048] FIG. 11F depicts an embodiment of the RSME of FIG. 6C in an asymmetric mirror cell configuration which is SiOx-free.

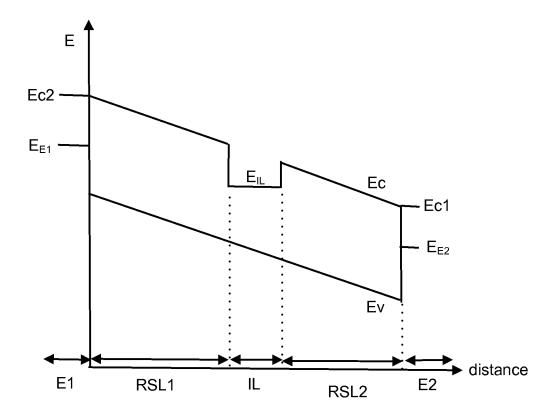

[0049] FIG. 12 depicts an energy diagram of the RSME of FIG. 6C.

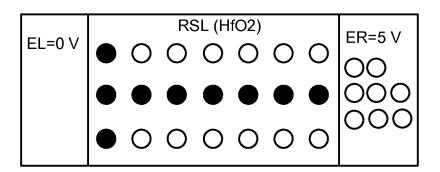

[0050] FIG. 13 depicts application of a high electric field in a set process of a RSL.

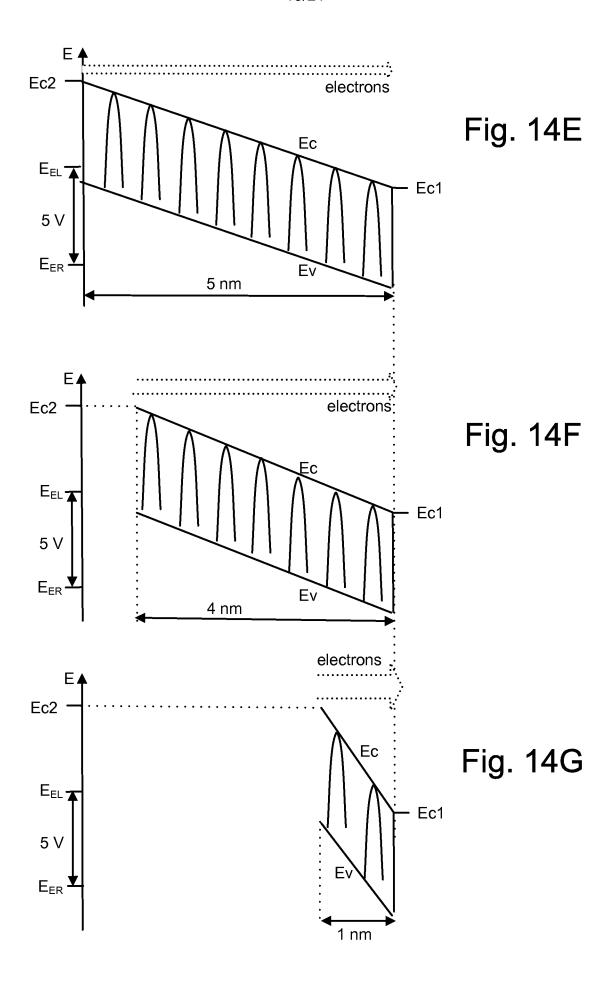

[0051] FIGs. 14A-14D depict different stages in the formation of a conductive filament in a set process of a RSL.

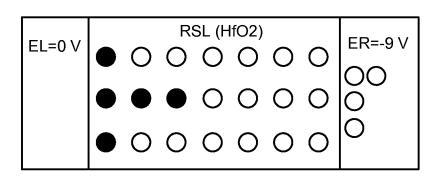

[0052] FIGs. 14E, 14F and 14G are energy diagrams which describe the set process stages of FIGs. 14A, 14B and 14D, respectively.

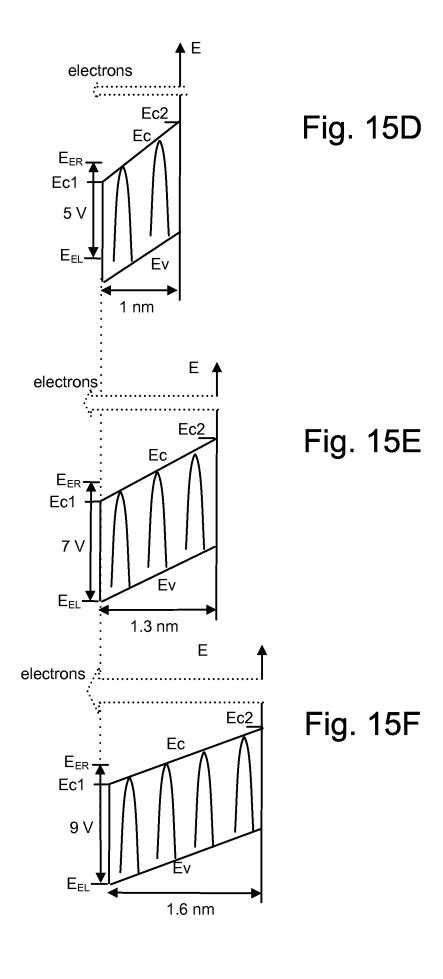

[0053] FIGs. 15A-15C depict different stages in the removal of a conductive filament in a reset process of a RSL.

[0054] FIGs. 15D, 15E and 15F are energy diagrams which describe the reset process stages of FIG. 15A, 15B and 15C, respectively.

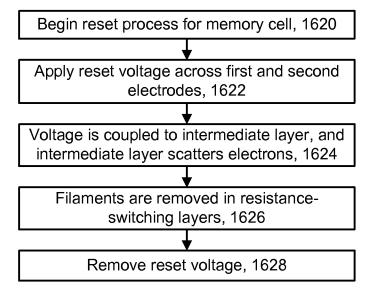

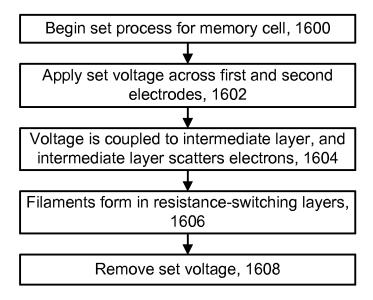

[0055] FIG. 16A depicts a set process for the RSME of FIG. 6A.

[0056] FIG. 16B depicts a reset process for the RSME of FIG. 6A.

## **DETAILED DESCRIPTION**

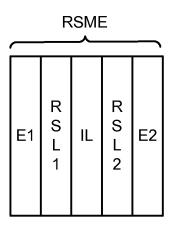

[0057] A memory system is provided that includes reversible resistivity-switching memory elements (RSME) having two or more resistance-switching layers (RSLs). In an example implementation, the RSME includes, in series, a first electrode (E1), a first resistance-switching layer (RSL1), an intermediate layer (IL), which is considered to be a scattering layer or coupling electrode, a second RSL (RSL2) and a second electrode (E2). In one approach, the RSME has a mirror configuration, in which the RSME configuration is symmetrical on either side of the IL. However, such a mirror configuration is not required.

-6-

[0058] Generally, as RSME-based memory devices are scaled down in size, a disadvantage is that a ballistic current flow during a set or reset process of the RSME can damage an associated steering element which is in series with the RSME or even prevent the operation of the memory cell at very reduced dimensions. Also generally, a plethora of RSL-based memory devices need a forming step during which the initially insulating properties of the RSL are broken down. This forming step is usually associated with a very short and very high discharge current peak, which can set the on-resistance level of the RSL for subsequent switching events. If the on-resistance level is very low (e.g.,  $100 - 30 \text{ k}\Omega$ ), the associated switching currents are also very high and as a consequence, the memory cell would not be operable at very small technology nodes. A set or reset process is a type of resistance-switching operation for a RSL and RSME. To solve this problem, an RSME is provided which includes separate RSLs on either side of a conductive IL.

[0059] In particular, a memory cell which includes a RSME as provided herein can limit ballistic current overshoot by actively reducing the operating currents. A thin IL such as TiN can prevent the current overshoot and can limit the current flow, whereby it is easier to create a large electric field across the individual RSL. Due to the reduced current, the likelihood of damaging a steering element of the cell is reduced, and a thinner steering element can be used, facilitating the scaling down of the memory device and possibly reducing power consumption. The switching ability of the cell is maintained as an ionic current is still allowed.

[0060] The RSME is based on a qualitative model for an individual RSL which describes a number of findings, including: a switching current based on electron/hole and ion conduction, exponential E-field dependence of the ionic current, and the measured current is a ballistic current without use for the switching mechanism. Specifically, the qualitative model describes: (i) an avalanche-type set-current increase, (ii) why it is difficult to limit the set state to a high on-resistance state, (iii) sensitivity of cycling yield to the set process, (iv) why reset voltage can be higher than set voltage, (v) why higher reset voltage is needed for deeper reset, and (vi) why reset current is higher for deeper reset. The model of ballistic current may also be applicable to any other "thin" storage material/ionic memories such as TiSi, CBRAM (conductive-bridge RAM). For a RSL of MeOx, the findings also indicate that the electron/hole current does not contribute to the switching effect, but travels

-7-

ballistically in the MeOx, delivering heat only to the contacts, and that this is different than thicker carbon or phase change materials, where this current generates heat in the memory cell, if the cell is long enough.

[0061] FIG. 1 is a simplified perspective view of one embodiment of a resistance-switching memory cell (RSMC) 100 which includes a RSME 102 coupled in series with a steering element 104 between a first conductor 106 and a second conductor 108.

[0062] The RSME 102 includes RSLs 130 and 135 on either side of a conductive intermediate layer (IL) 133. As mentioned, a RSL has a resistivity that may be reversibly switched between two or more states. For example, a RSL may be in an initial highresistivity (high resistance) state upon fabrication that is switchable to a low-resistivity state upon application of a first voltage and/or current. Application of a second voltage and/or current may return the RSL to the high-resistivity state. Alternatively, the RSL may be in an initial low-resistance state upon fabrication that is reversibly switchable to a high-resistance state upon application of the appropriate voltage(s) and/or current(s). When used in a memory cell, one resistance state for each RSL (and a corresponding resistance state of the RSME) may represent a binary "0" of the RSME while another resistance state for each RSL (and a corresponding resistance state of the RSME) may represent a binary "1" of the RSME. However, more than two data/resistance states may be used. Numerous reversible resistancechange materials and operation of memory cells employing reversible resistance-change materials are described, for example, in the above-mentioned U.S. Patent Application Publication No. 2006/0250836.

[0063] In one embodiment, the process of switching the RSME from the high-resistivity state (representing, e.g., binary data "0") to the low-resistivity state (representing, e.g., binary data "1") is referred to as setting or forming, and the process of switching the RSME from the low-resistivity state to the high-resistivity state is referred to as resetting. In other embodiments, setting and resetting and/or the data encoding can be reversed. The set or reset process can be performed for a memory cell to program it to a desired state to represent binary data.

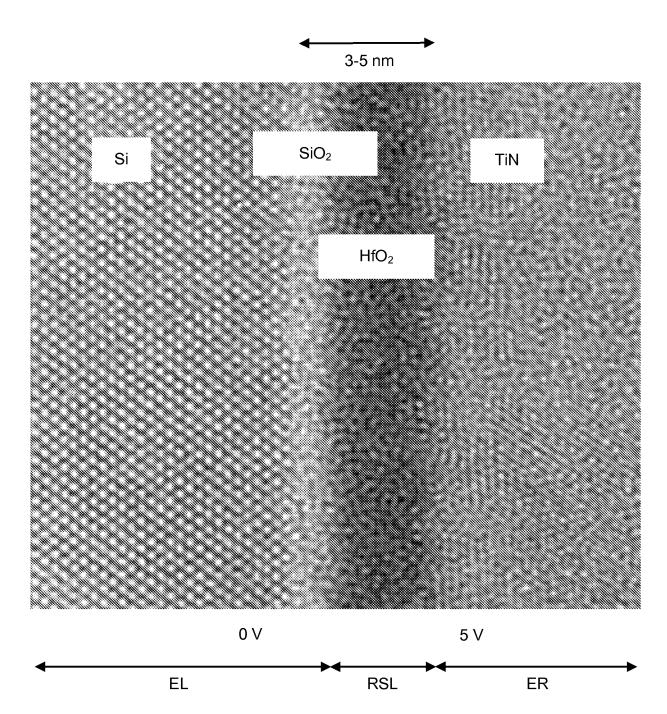

[0064] In some embodiments, the RSLs 130 and 135 may be formed from metal oxide (MeOx), one example of which is HfO2.

-8-

[0065] More information about fabricating a memory cell using reversible resistance-change material can be found in US 2009/0001343, published January 1, 2009, titled "Memory Cell That Employs a Selectively Deposited Reversible Resistance Switching Element and Methods of Forming The Same," and incorporated herein by reference.

[0066] The RSME 102 includes electrodes 132 and 134. Electrode 132 is positioned between the RSL 130 and a conductor 108 such as a bit line or word line (control line). In one embodiment, electrode 132 is made of titanium (Ti) or titanium nitride (TiN). Electrode 134 is positioned between the RSL 133 and a steering element 104. In one embodiment, electrode 134 is made of Titanium Nitride (TiN), and serves as an adhesion and barrier layer.

[0067] Steering element 104 can be a diode, or other suitable steering element that exhibits non-ohmic conduction by selectively limiting the voltage across and/or the current flow through the RSME 102. In one approach, the steering element allows current to flow through the RSME in only one direction, e.g., from the bit line to the word line. In another approach, a steering element such as a punch-through diode allows current to flow through the RSME in either direction.

[0068] The steering element acts as a one-way valve, conducting current more easily in one direction than in the other. Below a critical "turn-on" voltage in the forward direction, the diode conducts little or no current. By use of appropriate biasing schemes, when an individual RSME is selected for programming, the diodes of neighboring RSMEs can serve to electrically isolate the neighboring RSMEs and thus prevent inadvertent resistance switching, so long as the voltage across the neighboring RSMEs does not exceed the turn-on voltage of the diode when applied in the forward direction, or the reverse breakdown voltage when applied in the reverse direction. neighboring RSMEs.

[0069] Specifically, in a large cross-point array of RSMEs, when relatively large voltage or current is required, there is a danger that RSMEs that share the top or the bottom conductor (e.g., word line or bit line) with the RSME to be addressed will be exposed to sufficient voltage or current to cause undesired resistance switching. Depending on the biasing scheme used, excessive leakage current across unselected cells may also be a concern. The use of a diode or other steering element can overcome this danger.

[0070] In this manner, the memory cell 100 may be used as part of a two- or three-dimensional memory array and data may be written to and/or read from the memory cell 100

-9-

without affecting the state of other memory cells in the array. Steering element 104 may include any suitable diode such as a vertical polycrystalline p-n or p-i-n diode, whether upward pointing with an n-region above a p-region of the diode or downward pointing with a p-region above an n-region of the diode. Or, even a punch-through diode or a Zener diode, which are operable in both directions, can be used. The steering element and the RSME together can be in the shape of a vertical pillar. In other approaches, portions of the RSME are arranged laterally of one another, as discussed further below.

[0071] In some embodiments, steering element 104 may be formed from a polycrystalline semiconductor material such as polysilicon, a polycrystalline silicon-germanium alloy, polygermanium or any other suitable material. For example, the steering element 104 may include a heavily doped n+ polysilicon region 142, a lightly doped or an intrinsic (unintentionally doped) polysilicon region 144 above the n+ polysilicon region 142, and a heavily doped p+ polysilicon region 146 above the intrinsic region 144. In some embodiments, a thin (e.g., a few hundred angstroms or less) germanium and/or silicon-germanium alloy layer (not shown), with about 10% or more of germanium when using a silicon-germanium alloy layer, may be formed on the n+ polysilicon region 142 to prevent and/or reduce dopant migration from the n+ polysilicon region 142 into the intrinsic region 144, as described, for example, in U.S. Patent Application Publication No. 2006/0087005, titled "Deposited Semiconductor Structure To Minimize N-Type Dopant Diffusion And Method Of Making," incorporated herein by reference. It will be understood that the locations of the n+ and p+ regions may be reversed.

[0072] When steering element 104 is fabricated from deposited silicon (e.g., amorphous or polycrystalline), a silicide layer may be formed on the diode to place the deposited silicon in a low resistivity state, as fabricated. Such a low resistivity state allows for easier programming of the memory cell as a large voltage is not required to switch the deposited silicon to a low resistivity state.

[0073] As described in U.S. Patent No. 7,176,064, "Memory Cell Comprising a Semiconductor Junction Diode Crystallized Adjacent to a Silicide," incorporated herein by reference, silicide-forming materials such as titanium and/or cobalt react with deposited silicon during annealing to form a silicide layer. The lattice spacing of titanium silicide and cobalt silicide are close to that of silicon, and it appears that such silicide layers may serve as

"crystallization templates" or "seeds" for adjacent deposited silicon as the deposited silicon crystallizes (e.g., the silicide layer enhances the crystalline structure of the silicon diode during annealing). Lower resistivity silicon thereby is provided. Similar results may be achieved for silicon-germanium alloy and/or germanium diodes.

[0074] Conductors 106 and 108 include any suitable conductive material such as tungsten, any appropriate metal, heavily doped semiconductor material, a conductive silicide, a conductive silicide-germanide, a conductive germanide, or the like. In the embodiment of FIG. 1, conductors 106 and 108 are rail-shaped and extend in different directions (e.g., substantially perpendicular to one another). Other conductor shapes and/or configurations may be used. In some embodiments, barrier layers, adhesion layers, antireflection coatings and/or the like (not shown) may be used with conductors 106 and 108 to improve device performance and/or aid in device fabrication. The conductors 106 may be a word line while the conductor 108 is a bit line, or vice-versa.

[0075] While the RSME 102 is shown as being positioned above the steering element 104 in FIG. 1, it will be understood that in alternative embodiments, the RSME 102 may be positioned below the steering element 104. Various other configurations are possible as well. An RSL can exhibit unipolar or bipolar resistance-switching characteristics. With a unipolar resistance-switching characteristic, the voltages used for both set and reset processes are of the same polarity, i.e., either both positive or both negative. In contrast, with a bipolar resistance-switching characteristic, opposite polarity voltages are used for the set and reset processes. Specifically, the voltage used for the set process can be positive while the voltage used for the reset process is negative, or the voltage used for the set process can be negative while the voltage used for the reset process is positive.

[0076] FIG. 2A is a simplified perspective view of a portion of a first memory level 114 formed from a plurality of the memory cells 100 of FIG. 1. For simplicity, the RSME 102, the steering element 104, and barrier layer 113 are not separately shown. The memory array 114 is a "cross-point" array including a plurality of bit lines (second conductors 108) and word lines (first conductors 106) to which multiple memory cells are coupled (as shown). Other memory array configurations may be used, as may multiple levels of memory.

[0077] FIG. 2B is a simplified perspective view of a portion of a monolithic threedimensional array 116 that includes a first memory level 118 positioned below a second

-11-

memory level 120. In the embodiment of FIG. 3, each memory level 118 and 120 includes a plurality of memory cells 100 in a cross-point array. It will be understood that additional layers (e.g., an inter-level dielectric) may be present between the first and second memory levels 118 and 120, but are not shown in FIG. 2B for simplicity. Other memory array configurations may be used, as may additional levels of memory. In the embodiment of FIG. 2B, all diodes may "point" in the same direction, such as upward or downward depending on whether p-i-n diodes having a p-doped region on the bottom or top of the diode are employed, simplifying diode fabrication.

[0078] In some embodiments, the memory levels may be formed as described in U.S. Patent No. 6,952,030, "High-Density Three-Dimensional Memory Cell," incorporated herein by reference. For instance, the upper conductors of a first memory level may be used as the lower conductors of a second memory level that is positioned above the first memory level as shown in FIG. 2C. In such embodiments, the diodes on adjacent memory levels preferably point in opposite directions, as described in U.S. Patent 7,586,773, titled "Large Array Of Upward Pointing P-I-N Diodes Having Large And Uniform Current," incorporated herein by reference. For example, the diodes of the first memory level 118 may be upward pointing diodes as indicated by arrow A1 (e.g., with p regions at the bottom of the diodes), while the diodes of the second memory level 120 may be downward pointing diodes as indicated by arrow A2 (e.g., with n regions at the bottom of the diodes), or vice versa.

[0079] A monolithic three-dimensional memory array is one in which multiple memory levels are formed above a single substrate, such as a wafer, with no intervening substrates. The layers forming one memory level are deposited or grown directly over the layers of an existing level or levels. In contrast, stacked memories have been constructed by forming memory levels on separate substrates and adhering the memory levels atop each other, as in Leedy, U.S. Patent No. 5,915,167, "Three Dimensional Structure Memory," incorporated herein by reference. The substrates may be thinned or removed from the memory levels before bonding, but as the memory levels are initially formed over separate substrates, such memories are not true monolithic three-dimensional memory arrays.

[0080] The above examples show memory cells in a cylindrical or pillar shape and conductors in the shapes of rails according to the disclosed arrangements. However, the technology described herein is not limited to any one specific structure for a memory cell.

Other structures can also be used to form memory cells that include RSMEs. For example, U.S. Patents 6,952,043, 6,951,780, 6,034,882, 6,420,215, 6,525,953 and 7,081,377, each of which is incorporated herein by reference, provide examples of structures of memory cells that can be adapted to use RSMEs. Additionally, other types of memory cells can also be used with the techniques described herein.

[0081] FIG. 3 is a block diagram that depicts one example of a memory system 300 that can implement the technology described herein. Memory system 300 includes a memory array 302 that can be a two- or three-dimensional array of memory cells as described above. In one embodiment, memory array 302 is a monolithic three-dimensional memory array. The array terminal lines of memory array 302 include the various layer(s) of word lines organized as rows, and the various layer(s) of bit lines organized as columns. However, other orientations can also be implemented.

[0082] Memory system 300 includes row control circuitry 320, whose outputs 308 are connected to respective word lines of the memory array 302. Row control circuitry 320 receives a group of M row address signals and one or more various control signals from system control logic circuit 330, and typically may include such circuits as row decoders 322, array terminal drivers 324, and block select circuitry 326 for both read and programming (e.g., set and reset) operations. Memory system 300 also includes column control circuitry 310 whose input/outputs 306 are connected to respective bit lines of the memory array 302. Column control circuitry 306 receives a group of N column address signals and one or more various control signals from system control logic 330, and typically may include such circuits as column decoders 312, array terminal receivers or drivers 314, block select circuitry 316, as well as read/write circuitry, including sense amps 318, and I/O multiplexers. System control logic 330 receives data and commands from a host and provides output data to the host. In other embodiments, system control logic 330 receives data and commands from a separate controller circuit and provides output data to that controller circuit, with the controller circuit communicating with the host. System control logic 330 may include one or more state machines, registers and other control logic for controlling the operation of memory system 300. For example, write circuitry 460, read circuitry 461 and clamp control circuitry 464, discussed further below, may be provided.

-13-

[0083] In one embodiment, all of the components depicted in FIG. 3 are arranged on a single integrated circuit. For example, system control logic 330, column control circuitry 310 and row control circuitry 320 can be formed on the surface of a substrate and memory array 302 in a monolithic three-dimensional memory array formed above the substrate (and, therefore, above system control logic 330, column control circuitry 310 and row control circuitry 320). In some cases, a portion of the control circuitry can be formed on the same layers as some of the memory array.

Integrated circuits incorporating a memory array usually subdivide the array into a number of sub-arrays or blocks. Blocks can be further grouped together into bays that contain, for example, 16, 32, or a different number of blocks. As frequently used, a sub-array is a contiguous group of memory cells having contiguous word and bit lines generally unbroken by decoders, drivers, sense amplifiers, and input/output circuits. This is done for any of a variety of reasons. For example, the signal delays traversing down word lines and bit lines which arise from the resistance and the capacitance of such lines (i.e., the RC delays) may be very significant in a large array. These RC delays may be reduced by subdividing a larger array into a group of smaller sub-arrays so that the length of each word line and/or each bit line is reduced. As another example, the power associated with accessing a group of memory cells may dictate an upper limit to the number of memory cells which may be accessed simultaneously during a given memory cycle. Consequently, a large memory array is frequently subdivided into smaller sub-arrays to decrease the number of memory cells which are simultaneously accessed. Nonetheless, for ease of description, an array may also be used synonymously with sub-array to refer to a contiguous group of memory cells having contiguous word and bit lines generally unbroken by decoders, drivers, sense amplifiers, and input/output circuits. An integrated circuit may include one or more than one memory array.

[0085] As described above, RSME 102 may be reversibly switched between two or more states by reversibly switching each of its RSLs. For example, the RSME may be in an initial, high-resistivity state upon fabrication that is switchable to a low-resistivity state upon application of a first voltage and/or current. Application of a second voltage and/or current may return the RSME to a high-resistivity state. The memory system 300 can used with any RSME described herein.

-14-

[0086] FIG. 4A is a graph of voltage versus current for an example embodiment of a unipolar RSL. The x-axis depicts an absolute value of voltage, the y-axis depicts current and the lines are adjusted to meet at the origin of the graph. In the set process, line 404 represents the I-V characteristic of the RSL when in the high-resistivity, reset state, and line 406 represents a transition to the low-resistivity, set state at Vset. In the reset process, line 400 represents the I-V characteristic of the RSL when in the low-resistivity, set state, and line 402 represents a transition to the high-resistivity, reset state at Vreset. The example shows a unipolar operation mode where the polarity of the voltage is the same for the both the set and reset switching.

[0087] To determine the RSL's state, a voltage can be applied across the RSL and the resulting current is measured. A higher or lower measured current indicates that the RSL is in the low- or high-resistivity state, respectively. In some cases, the high resistivity state is substantially higher, e.g., two or three orders of magnitude (100-1,000) times higher than the low resistivity state. Note that other variations of a RSL having different I-V characteristics can also be used with the technology herein.

[0088] When in the reset state, the RSME exhibits the resistance characteristics shown by line 404 in response an applied voltage between 0 and Vset. When in the set state, however, the RSME exhibits the resistance characteristics shown by line 400 in response an applied voltage between 0 and Vreset, where Vreset<Vset. Thus, the RSME thus exhibits different resistance characteristics in response to the same voltages in the same voltage range (e.g., between 0 and Vreset) depending on the resistance state of the RSME. In a read operation, a fixed voltage Vread<Vreset can be applied, in response to which the sensed current is Ia in the set state or Ib in the reset state. The state of an RSL or RSME can thus be sensed by identifying at least one point of its I-V characteristic.

[0089] The RSME can include multiple RSLs which each exhibit a substantially similar unipolar switching characteristic, in one approach.

[0090] FIG. 4B is a graph depicting different I-V characteristics of two example unipolar RSLs. For two or more unipolar RSLs, the I-V (current-voltage) characteristics can be substantially the same, so that I increases with V at a common rate, and the set and/or reset levels can be substantially the same, for instance. Or, the I-V characteristics of the RSLs can differ such that, e.g., I increases with V more quickly for one of the RSLs, or the set and/or

-15-

reset levels can be different. In this example, "A" denotes a first type of RSL and "B" denotes a second type of RSL, where the RSLs have different unipolar resistance-switching characteristics. The x-axis depicts voltage (V) and the y-axis depicts current (I). For the type "A" RSL, lines 400, 402, 404 and 406 are the same as in FIG. 4A. Also for the type "A" RSL, VsetA is the set voltage, VresetA is the reset voltage, IresetA is the reset current and Iset\_limitA is the current set limit. For the type "B" RSL, lines 420, 422, 424 and 426 correspond to lines 400, 402, 404 and 406, respectively. Also for the type "B" RSL, VsetB is the set voltage, VresetB is the reset voltage, IresetB is the reset current and Iset\_limitB is the current set limit. In the approach shown here, VsetA>VsetB, VresetA>VresetB, IresetA>IresetB and Iset\_limitA>Iset\_limitB, but this is only an example and other, alternative relations may apply.

[0091] When two or more RSLs are in the same RSME, the switching characteristic of the RSME will be a function of the switching characteristic of each of the RSLs. During a set process, for example, as V is increased, the type "B" RSL could switch before the type "A" RSL, if the voltage was split equally across each RSL. Similarly, during a reset process, for example, as V is increased, the type "B" RSL could switch before the type "A" RSL, assuming the same voltage is applied in each RSL.

[0092] It is alternatively possible for the type "A" and "B" RSLs to have different I-V characteristics of opposite polarity. For example, we could have VsetA>0 V and VresetA>0 V, while VsetB<0 V and VresetB<0 V. As an example, the characteristic of the type "A" RSL can be as described in FIG. 4A while the characteristic of the type "B" RSL can be as described in FIG. 4C, below. It is also possible, in theory, for one RSL in a RSME to have a unipolar characteristic while another RSL in the RSME has a bipolar characteristic. However, using only one kind of switching characteristic (unipolar or bipolar) among all RSLs in a RSME can allow for a simplified control scheme.

[0093] In some cases, a read out of an RSME switches the data state of one of the RSLs. For example, with a first RSL in the low resistance state and a second RSL in the high resistance state, a read operation would detect essentially no current, assuming the high resistance state was orders of magnitude higher than the low resistance state. That is, the resistance of the RSME, equal to the sum of the resistance of each RSL, would be very high, so the current would be very low or essentially zero. A read operation could switch the

-16-

second RSL to the low resistance state, so that the resistance of the RSME was low, and the current through it is relatively high and detectable. A write back operation could be performed next to switch the second RSL back to the high resistance state.

[0094] When a voltage is applied across the electrodes of an RSME, it will be divided across each RSL according in proportion to each RSL's resistance. When the first RSL is in the low resistance state and the second RSL is in the high resistance state, the first RSL will transfer the potential at the electrode to the IL, so that substantially all of the voltage is applied across the second RSL. This voltage will switch the second RSL if it is of the appropriate magnitude and polarity.

[0095] Moreover, an RSL can use a material that can be operated as a unipolar or bipolar device, such as described in Sun et al., "Coexistence of the bipolar and unipolar resistive switching behaviours in Au/SrTiO3/Pt cells," J. Phys. D: Appl. Phys. 44, 125404, March 10, 2011, incorporated herein by reference.

[0096] FIG. 4C is a graph depicting I-V characteristics of another example unipolar RSL. Compared to the characteristic of FIG. 4A, negative voltages are used instead of positive during the set and reset processes. In the set process, line 434 represents the I-V characteristic of the RSL when in the high-resistivity, reset state, and line 436 represents a transition to the low-resistivity, set state at Vset. In the reset process, line 430 represents the I-V characteristic of the RSL when in the low-resistivity, set state, and line 432 represents a transition to the high-resistivity, reset state at Vreset. Vread, Vreset, Vset and Vf are all negative voltages. In a read operation, a fixed voltage Vread>Vreset can be applied, in response to which the sensed current is Ia in the set state or Ib in the reset state.

[0097] FIG. 4D is a graph depicting I-V characteristics of an example bipolar RSL. Here, opposite polarity voltages are used for the set and reset processes. Moreover, positive voltages are used for the set process and negative voltages are used for the reset process. In this bipolar RSL, the set process occurs when a positive voltage is applied, and the reset process occurs when a negative voltage is applied. In the set process, line 444 represents the I-V characteristic of the RSL when in the high-resistivity, reset state, and line 446 represents a transition to the low-resistivity, set state at Vset. In the reset process, line 440 represents the I-V characteristic of the RSL when in the low-resistivity, set state, and line 442 represents

a transition to the high-resistivity, reset state at Vreset. Vset and Vf are positive voltages and Vreset is a negative voltage.

[0098] FIG. 4E is a graph depicting I-V characteristics of another example bipolar RSL. In this bipolar RSL, the reset process occurs when a positive voltage is applied, and the set process occurs when a negative voltage is applied. In the set process, line 454 represents the I-V characteristic of the RSL when in the high-resistivity, reset state, and line 456 represents a transition to the low-resistivity, set state at Vset. In the reset process, line 450 represents the I-V characteristic of the RSL when in the low-resistivity, set state, and line 452 represents a transition to the high-resistivity, reset state at Vreset. Vset and Vf are positive voltages and Vreset is a negative voltage.

[0099] Although the Ireset level in Fig. 4D and Fig. 4C is higher than the Iset level, it should be emphasized that it can be the other way around. This means that Iset level in Fig. 4D and Fig. 4C can be higher than the Ireset level for the opposite polarity.

[00100] FIG. 5 depicts an embodiment of a circuit for reading the state of a memory cell. A portion of a memory array includes memory cells 550, 552, 554 and 556. Two of the many bit lines and two of the many word lines are depicted. Bit line 559 is coupled to cells 550 and 554, and bit line 557 is coupled to cells 552 and 556. Bit line 559 is the selected bit line and may be at 2 V, for instance. Bit line 557 is an unselected bit line and may be at ground, for instance. Word line 547 is the selected word line and may be at 0 V, for instance. Word line 549 is an unselected word line and may be at 2 V, for instance.

[00101] A read circuit for one of the bit lines 559 is depicted to be connected to the bit line via transistor 558, which is controlled by a gate voltage supplied by column decoder 312 in order to select or unselect the corresponding bit line. Transistor 558 connects the bit line to a Data bus 563. Write circuit 560 (which is part of system control logic 330) is connected to the Data bus. Transistor 562 connects to the Data bus and operates as a clamp device that is controlled by clamp control circuit 564 (which is part of system control logic 330). Transistor 562 is also connected to a sense amp 566, which includes a data latch 568. The output of sense amp 566 is connected to a data out terminal (to system control logic 330, a controller and/or a host). Write circuit 560 is also connected to the sense amp 566 and the data latch 568.

-18-

[00102]When attempting to read the state of the RSME, all word lines are first biased at Vread (e.g., approximately 2 V) and all bit lines are at ground. The selected word line is then pulled to ground. For example, this discussion will assume that memory cell 550 is selected for reading. One or more selected bit lines 559 are pulled to Vread through the data bus (by turning on transistor 558) and the clamp device (transistor 562, which receives ~2 V + Vth, the threshold voltage of the transistor 562). The clamp device's gate is above Vread but controlled to keep the bit line near Vread. In one approach, current is pulled by the selected memory cell 550 through transistor 562 from a sense node in the sense amp. The sense node can receive a reference current that is between a high-resistivity state current and a lowresistivity state current. The sense node moves corresponding to the current difference between the cell current and the reference current. Sense amp 566 generates a data out signal by comparing the sensed voltage to a reference read voltage. If the memory cell current is larger than the reference current, the memory cell is in the low-resistivity state and the voltage at the sense node will be lower than the reference voltage. If the memory cell current is smaller than the reference current, the memory cell is in the high-resistivity state and the voltage at the sense node will be higher than the reference voltage. The output data signal from the sense amp 566 is latched in data latch 568.

[00103] Referring again to FIG. 4A, for example, while in the high-resistivity state, if the voltage Vset and sufficient current is applied, the RSL will be set to the low-resistivity state. Line 404 shows the behavior when Vset is applied. The voltage will remain somewhat constant and the current will increase toward Iset\_limit. At some point, the RSL will be set and the device behavior will be based on line 406. Note that the first time the RSL is set, Vf (the forming voltage) is needed to set the device. After that, Vset is sufficient to set the device be used. The forming voltage Vf may be greater than Vset in absolute magnitude.

[00104] While in the low-resistivity state (line 400), if Vreset and sufficient current (Ireset) are applied, the RSL will be reset to the high-resistivity state. Line 400 shows the behavior when Vreset is applied. At some point, the RSL will be reset and the device behavior will be based on line 402.

[00105] In one embodiment, Vset is approximately 7 V, Vreset is approximately 9 V, Iset\_limit is approximately 10  $\mu$ A and Ireset could be as low as 100 nA. These voltages and currents apply to the circuit of FIG. 5 where we have a RSME and a diode in series.

[00106] FIGs. 6A-6M can be a cross-sectional view in a vertical or horizontal plane of an RSME, for instance.

[00107] FIG. 6A depicts an example memory cell having a RSME and a steering element (SE) below the RSME. The memory cell can have various configurations. One configuration is a stacked configuration in which each type of material is provided in a layer, and each layer is positioned beneath the layer above it and typically has a similar cross-sectional area. In another possible configuration, one or more layers can be arranged end-to-end with one or more other layers (see FIGs. 6F-6J).

[00108] Note that, in the figures, any two layers or materials which are pictured as being adjacent to one another may be in contact with one another. However, unless otherwise specified, this is not required, and any two layers or materials which are pictured as being adjacent to one another may be separated by one or more layers of other materials which are not depicted. Additionally, in some cases, a material can be formed as a byproduct of fabrication, such as a SiOx layer which is formed on an Si layer. Such byproducts are not necessarily depicted in the figures. Moreover, variations of the described implementations are possible. For example, the order of layers in each implementation can be reversed so that the word line is on top and the bit line is on the bottom, for instance. One or more intermediate layers can be provided between each of the layers depicted. Also, the position of the steering element can be changed so that it is located above or below other layers including the RSLs. The orientation of the layers can be modified from vertical to horizontal or any other orientation. Multiple layers or portions which can form a common conductive path are said to be serially connected.

[00109] The memory cell includes a bit line contact (BLC) material such as W or NiSi, which is connected to a bit line of a memory device. The bit line is a type of control line, so that the BLC is also a contact to a first control line. After the BLC in a serial path is a first adhesion layer (AL1) such as TiN which helps the BLC adhere to the RSME, as well as acting as a barrier. A TiN layer can be deposited by any conventional method, such as sputtering. After the RSME in the serial path is a steering element (SE) such as a diode. The steering element allows a signal such as a voltage or current to be applied selectively to one or more memory cells, via word lines and bit lines, to individually control the cells such as to change their respective data states by switching their RSMEs. The resistance-switching

-20-

behavior of the RSME is independent of the SE. The SE could have a resistance-switching behavior itself; however, this behavior would be independent of the resistance-switching behavior of the RSME.

[00110] After the SE in the serial path is a second adhesion layer (AL2) such as TiN. After the AL2 in the serial path is a word line contact (WLC) material such as W or NiSi, which is connected to a word line of a memory device. The word line is a type of control line, so that the WLC is also a contact to a second control line. The depicted portions of the memory cell are arranged thus serially.

[00111] FIG. 6B depicts an alternative configuration of a memory cell having a RSME, where the steering element (SE) is above the RSME. The order of the other layers from top to bottom can be reversed as well, from bottom to top.

[00112] FIG. 6C depicts an example implementation of the RSME of FIG. 6A as a mirror resistive switch (MRS) in a vertical stack. The RSME includes a first electrode (E1), which is a top electrode in some configurations, a first resistance-switching layer (RSL1) and a conductive intermediate layer (IL), which acts as a scattering layer, coupling electrode or coupling layer. The RSME also includes a second RSL (RSL2), and a second electrode (EL2), which is a bottom electrode in some configurations. The RSLs can be reversible RSLs, for instance. A reversible RSL can be switched from one state to another state and back to the one state. The IL is electrically between, and in series with, E1 and E2. RSL1 is electrically between, and in series with, E2 and IL. "Electrically between" or similar can mean in an electrically conductive path. For example, the IL can be electrically between E1 and E2 with or without being physically between E1 and E2.

[00113] For example, an RSME can be formed by connecting two bipolar memristor (memory-resistor) elements anti-serially into one mirror resistive switch (MRS). A memristor is a passive two-terminal circuit element in which the resistance is a function of the history of the current through and voltage across the device. Such a MRS can be made of a first memristive element which includes an E1 such as n-type Silicon, RSL1, which can be a transition metal oxide such as Hafnium Oxide (HfO2) or an Hafnium Silicon Oxynitride (HfSiON) and an IL, which can be an oxidizable electrode (such as TiN) which is capable of undergoing a chemical reaction with oxygen.

[00114] The RSME includes a second memristive element which is made of the same (or different) materials, but in a reverse order, sharing the oxidizable electrode of the IL. Moreover, the first and second memristive elements can both have bipolar or unipolar I-V (current-voltage) characteristics, in one approach. In another approach, one of the memristive elements has a unipolar characteristic and the other memristive element has a bipolar characteristic. By merging the two memristive elements to one RSME, the RSME has an I-V characteristic which is a superposition of the I-V characteristics of the constituent memristive elements, but with the additional benefit, that it is operating at much lower currents than the individual memristive elements.

[00115] More generally, the RSME will have an I-V characteristic which is a superposition of the I-V characteristics of the constituent RSLs, but enables operation at low currents.

[00116] The IL acts as a scattering layer by scattering electrons which enter the IL from the RSLs, thereby slowing an electron flow which does not contribute to the switching mechanism, to avoid damage to a steering element. Moreover, the IL acts as a coupling electrode or layer which is capacitive coupled to a voltage which is applied to the RSME by setting potentials of E1 and E2.

[00117] Through such scattering, the IL provides a resistance which reduces a peak current flow during a set or reset process while achieving a low current operation. The current limiting operation is believed to originate from two aspects of the IL layer. First, hot electrons are scattered very well in the IL layer by an electron-electron interaction. Second, as soon as one of the RSLs starts to break down and deliver excess charge Q onto the IL, the applied voltage on the RSL is effectively reduced by V=Q/C, where C is the capacitance of the IL layer towards the electrodes E1 and E2. At the same time, a higher voltage is now at the second RSL, inducing a breakdown of the second RSL. Because the available amount of charge Q is limited, the current which can flow here is also very limited. In this way, this RSME enables the operation of the memory cell at low currents. The resistance is believed to be based on the ability of the IL to scatter electrons and give very efficient negative feedback to the applied bias voltage so that small conductive filaments are formed which allow switching to occur at low currents. Without the IL, a filament with very low resistance would

-22-

be formed when a voltage is applied, leading to a high current peak (due to the relationship of I=V/R) in the memory cell and the required switching currents would also be very high.

[00118] The RSME has a mirror configuration relative to the IL because the sequence of an RSL and an electrode extends on either side of the IL. A mirror configuration may also use the same material for the RSLs and electrodes. The combination of E1, RSL1 and the IL forms a first memristive (memory-resistor) element, and the combination of E2, RSL2 and the IL forms a second memristive element. The two memristive elements can be bipolar memristor elements which are connected anti-serially or serially into one mirror resistive switch (MRS).

[00119] In use, when a voltage is applied across E1 and E2, an electric field (E) is generated which is the voltage divided by the distance between E1 and E2. The IL can float, which means it is not directly driven with a voltage/current signal and instead can be capacitively coupled to one or more other electrodes (such as E1 and/or E2) which are directly driven with a voltage/current signal. Due to capacitive coupling, one portion of the voltage between E1 and E2 will be imposed from E1 to the coupling layer and across RSL1, while another portion of the voltage between E1 and E2 will be imposed from the coupling layer to E2 and across RSL2. The voltage is divided across each RSL in proportion to each RSL's resistance.

**[00120]** Furthermore, the first memristor may have a first I-V characteristic, while the second memristor has a second I-V characteristic, so that the overall I-V characteristic of the memory cell is a superposition of the I-V characteristics of the first and second memristors, but with the additional benefit, that it is operating at much lower currents than the individual memristive elements. In one approach, the I-V characteristics of the first and second memristors differ but have the same polarity. In another approach, the I-V characteristics of the first and second memristors have opposite polarities. FIGs. 4A-4E, discussed previously, provide example I-V characteristics of a RSL.

[00121] The elements of the RSME can be provided in many possible configurations which are detailed further below. Example materials for E1 include n+ Si (polysilicon), p+ Si (polysilicon), TiN, TiSix, TiAlN, TiAl, W, WN, WSix, Co, CoSi, p+ Si, Ni and NiSi. Example materials for RSL1 and RSL2 include metallic materials such as MeOx and MeN. However, non-metallic materials could also be used, as discussed in some of the

-23-

embodiments herein. RSL1 and RSL2 can be of the same type or of different types. A RSL could also be a phase change cell, carbon-based, carbon nanotube-based, nano-ionic memory, conductive bridge, or a cell which changes its phase, spin, magnetic component, and so forth. The RSLs can have an on-resistance (conductive state resistance) in the  $M\Omega$  range, e.g., 1-10  $M\Omega$  or more. This is in contrast to programmable metallization cells (PMCs) such as a conductive-bridging RAM, or CBRAM, which form quantum point contacts, and have a much lower resistance of about 25  $K\Omega$  or lower. The higher resistance provides a low current operation and better scalability.

[00122] Example materials for E2 include n+ Si, n+ SiC, p+ SiC and p+ Si (polysilicon), TiN, TiAlN, TiAl, W, WN Co, CoSi, p+ Si, Ni and NiSi. Particular combinations of materials in the different layers can be advantageous. Various configurations are discussed in further detail below.

[00123] Example materials for the IL include TiN, TiN, Al, Zr, La, Y, Ti, TiAlN, TixNy, TiAl alloy and p+ SiC. The IL can thus be made of an oxidizable material (e.g., TiN, Al, Zr, La, Y, Ti) or a non-oxidizable material (e.g., TiAlN, TixNy, TiAl alloy andCarbon, including, e.g., graphene, amorphous carbon, carbon nanotubes, carbon with different crystal structures and p+ SiC). Generally, the same material of E1 and E2 can be used for the IL layer. In some cases, one or more oxide layers are formed intentionally or un-intentionally, as a byproduct of the deposition and formation step. For example, Si can be oxidized by deposition of MeOx on top of the Si. Even TiN or other suggested metals might be oxidized on one side by MeOx deposition and can be oxidized at the interface by an interfacial reaction of MeOx and TiN.

[00124] As mentioned, E1, E2 and the IL are made of a conductive material. A conductive material can be characterized by its conductivity  $\sigma$ =1/ $\rho$  or its reciprocal, which is resistivity  $\rho$ =E/J. Conductivity is measured in siemens per meter (S/m), and resistivity is measured in ohm-meters ( $\Omega$ -m) or  $\Omega$ -cm. E is the magnitude of the electric field in V/m and J is the magnitude of the current density in A/m2. For an insulator,  $\rho$ >108  $\Omega$ -cm or  $\sigma$ <10-8 S/cm. For a semiconductor, 10-3  $\Omega$ -cm < $\rho$ <108  $\Omega$ -cm or 103 S/cm > $\sigma$ >10-8 S/cm. For a conductor, 10-3  $\Omega$ -cm > $\rho$  or 103 S/cm < $\sigma$ . A semiconductor can be distinguished from a conductor in that a semiconductor is typically formed by doping an insulator to be p-type or

-24-

n-type semiconductor, while a conductor does not rely on doping. A semiconductor can also be distinguished from a conductor in that a semiconductor allows current to flow based on the polarity of an applied voltage, so that current can strongly flow in one direction but not the opposite direction. The direction in which a semiconductor allows a forward current to flow depends on whether it is a p-type or n-type semiconductor. In contrast, a conductor allows current to flow equally well in either direction. A conductive material is meant to include a semiconductor (a semiconductive material) and a conductor. A conductor may also be referred to as a conductive material. A conductor has a higher conductivity than a semiconductor.

[00125] Note that the RSME does not rely on a high band-gap triple stack (a relatively high band gap material between layers of a relatively low band gap material) since the IL is a conductive material which can received a coupling voltage.

[00126] FIG. 6D depicts an example implementation of the RSME of FIG. 6A using multiple ILs of different types between RSLs. Multiple adjacent intermediate layers are used, including a first IL (IL1) of type "1" and a second IL (IL2) of type "2." An advantage of this embodiment is that the ILs can be of different types, which have different scattering properties and work functions, to provide an additional capability to tailor the performance of the RSME. Moreover, the use of multiple ILs of the same or different types can increase scattering/resistance in the path, thereby decreasing current flow since I=V/R. Multiple adjacent ILs can increase scattering, as can a thicker single IL. However, a thicker IL poses a scaling challenge in that, if the stack height increases, the aspect ratio for the pillar-etch increases. As a result, fabrication processes such as etching, cleaning and gap-fill become very challenging. It may be preferable to have two (or more) adjacent (or non-adjacent) thinner ILs (or similar or dissimilar properties/materials) instead of one thicker IL. For example, two ILs of 5 nm thickness may provide comparable scattering as a single thicker IL of, e.g., 20 nm.

[00127] IL1 and IL2 can be of different materials having different resistivity and crystal structure, for instance. They could also be of the same material, but may have different crystal structure or orientation or different grain-size, that would scatter the charge carriers differently. As another example, one IL can be composed of a fine-grained material or nanoparticles (that may be same or different than the other IL).

-25-

[00128] If RSL1 and RSL2 are of different materials, and IL1 and IL2 are of different materials and/or types of materials, the optimal placement of the ILs with respect to the RSLs would be material-dependent.

[00129] One possible implementation uses a pn-junction with IL1 being n+ Si and IL2 being p+ Si. IL1 and IL2 can each have a thickness of at least 20 nm, for instance. Another possible combination uses a metal such as TiN for one of the ILs and n+ or p+ Si for another of the ILs. See FIG. 10C, for example.

[00130] FIG. 6E depicts an example implementation of the RSME of FIG. 6A using a repeating RSL/IL pattern. The pattern or combination of an RSL and an IL is repeated at least twice. For example, RSL1 and a first IL (IL1) are provided, in addition to RSL2 and a second IL (IL2). The third RSL (RSL3) is adjacent to E2. The RSLs can be of the same or different types, and the ILs can be of the same or different types. An advantage of this embodiment is that multiple scattering layers can increase the amount of scattering/resistance in the path of the RSME. Additionally, the ability to use ILs and RSLs of different types provides an additional capability to tailor the performance of the RSME.

[00131] It is possible that the three RSLs have a multitude of characteristics (all the same, two the same and one different, all different, etc.) The use of more than one IL together with dissimilar RSLs will change the characteristics of the RSME and provide additional functionality to tune its performance.

[00132] When a voltage is applied across the RSME, it is divided across each RSL according to each RSLs resistance. In one possible implementation, two of the RSLs have the same I-V characteristic, and the other RSL has a different I-V characteristic, so that the two RSLs are both in a low resistance state when the other RSL is in a high resistance state, for instance, or the two RSLs are both in a high resistance state when the other RSL is in a low resistance state. Other variations are possible.

[00133] FIG. 6F depicts an example implementation of the RSME of FIG. 6A where each layer of the RSME extends horizontally and one or more of the layers are arranged end-to-end. Instead of a fully stacked (vertical) configuration, portions of the RSME are arranged laterally of (to the side of), or end-to-end with, other portions of the RSME. For example, E1, RSL1 and the IL are in one stack, while the RSL2 and E2 are in another stack, and the RSL2 is arranged side-to-side with the IL. Referring to FIG. 6A, the BLC and AL1 can be

provided above E1, and the SE, AL2 and WLC can be provided below E2. A non-conductive (NC) layer can be provided under the IL, in one possible approach, and arranged side-to-side with E2. The portions/layers of the RSME are still arranged serially. In another possible implementation, E2 is on the side of the RSL2 rather than under it, so that three portions (IL, RSL2 and E2) are arranged end-to-end. Other variations are possible. Having portions of the RSME extend end-to-end or otherwise laterally of one another provides an additional capability to tailor the layout of the RSME. For example, the height of the RSME can be reduced. In one approach, the BLC and AL1 can be provided above E1, and the SE, AL2 and WLC can be provided below E2.

[00134] FIG. 6G depicts another example implementation of the RSME of FIG. 6A where each layer of the RSME extends horizontally and one or more of the layers are arranged end-to-end. Portions of the RSME are arranged laterally of, or end-to-end with, other portions of the RSME. RSL1, IL and RSL2 are in one stack, while E2, a non-conductive layer (NC) and E2 are in another, adjacent stack. E1 is arranged at the side of RSL1, end-to-end, and E2 is arranged at the side of RSL2, end-to-end. The portions can still be said to be arranged serially, e.g., in a serial path of E1, RSL1, IL, RSL2, E2. In another option, E1 extends laterally of and above RSL, for instance, and E2 extends laterally of and below RSL. In one approach, the BLC and AL1 can be provided above E1, and the SE, AL2 and WLC can be provided below E2.

[00135] Generally, it can be said that at least one E1, E2, IL, RSL1 and RSL2 can be arranged laterally, at least in part, of at least one other of E1, E2, IL, RSL1 and RSL2.

[00136] In Fig. 6F and 6G, the lateral arrangement is end-to-end. For instance, RSL1 is arranged laterally, end-to-end, with E1 and/or RSL2 is arranged laterally, end-to-end, with E2. Also, the IL is arranged laterally, end-to-end, with at least one of RSL1 and RSL2.

[00137] FIG. 6H depicts another example implementation of the RSME of FIG. 6A where each layer of the RSME extends vertically. Portions of the RSME are arranged laterally of, or face-to-face with, other portions of the RSME. The BLC can be above, below or to the side of E1, while the WLC is above, below or to the side of E2, for instance. The BLC and WLC are in a serial path with the RSME. Fabrication can involve n repeated cycles of a layer deposition and a layer spacer etch, with a final CMP step. For example, the E1 layer can be deposited, as a horizontally extending layer, then etched to form the vertically

extending portion shown. The RSL1 layer can then be deposited, as a horizontally extending layer, then etched to form the vertically extending portion shown. This is repeated for each of the IL, RSL2 and E2 portions. In one approach, the AL1 and BLC (FIG. 6A) extend vertically upward from E1 and the SE, AL2 and WLC extend vertically downward from E2.

**[00138]** Two or more of the layers can be arranged laterally of one another, face-to-face. For example, RSL1, the IL and RSL2 can be each arranged laterally with one another, face-to-face. Also, E1, RSL1, the IL, RSL2 and E2 can be each arranged laterally with one another, face-to-face.

[00139] The RSME portions of, e.g., FIGs. 6D-6H have a rectangular cross-section, compared to the L-shaped cross-section of FIG. 6I and the U-shaped cross-section of FIG. 6J. FIG. 6I depicts another example implementation of the RSME of FIG. 6A which includes L-shaped portions for RSL1, IL, RSL2 and E2. For example, assume the crosssectional view is in a vertical or horizontal plane with perpendicular axes x and y. In the x direction, E1 has a thickness t1x, RSL1 has a thickness t2x, IL has a thickness t3x, RSL2 has a thickness t4x and E2 has a thickness t5x. In the y direction, E1 has a thickness t1y, RSL1 has a thickness t2y, IL has a thickness t3y, RSL2 has a thickness t4y and E2 has a thickness t5y. The x-direction thickness can be the same or different than the corresponding ydirection thickness for each portion. The order of the layers could be reversed so that they extend in the order E2, RSL2, IL, RSL1, E1 instead of E1, RSL1, IL, RSL2, E2. The BLC can be above, below or to the side of E1, while the WLC is above, below or to the side of E2, for instance. The BLC and WLC are in a serial path with the RSME. By providing L-shaped portions, conductive filaments can form in a set process of the RSME, where the filaments extend in both x- and y-directions. Since there is a relatively large area over which filaments an extend, their creation is potentially facilitated. The implementation pictured can be rotated by 90 or 180 degrees as well.

[00141] In this approach, portions of the layers are arranged laterally of one another, similar to the concept of FIGs. 6F-6H, but the layers are in nested L-shapes, having two portions extending at a right angle from one another. For example, the L-shaped RSL2 is nested within the L-shaped E2, the L-shaped IL is nested within the L-shaped RSL2, and the L-shaped RSL1 is nested within the L-shaped RSL1 but

is not itself L-shaped in this example. Each portion can be the same or different in one or more dimensions.

[00142] Here, it can be said that at least one E1, E2, IL, RSL1 and RSL2 is arranged laterally, at least in part, of at least one other of E1, E2, IL, RSL1 and RSL2.

FIG. 6J depicts another example implementation of the RSME of FIG. 6A which [00143] includes U-shaped portions for RSL1, IL, RSL2 and E2. For example, assume the crosssectional view is in a vertical or horizontal plane with perpendicular axes x and y. In the x direction, E1 has a thickness t1x, RSL1 has thickness t2xa and t2xb, IL has thickness t3xa and t3xb, RSL2 has thickness t4xa and t4xb, and E2 has thicknesses t5xa and t5xb. In the y direction, E1 has a thickness t1y, RSL1 has a thickness t2y, IL has a thickness t3y, RSL2 has a thickness t4y, and E2 has a thickness t5y. The xa thicknesses can be the same or different than the corresponding xb thicknesses. Also, the xy thicknesses can be the same or different than the corresponding xa and/or xb thicknesses. The order of the layers could be reversed so that they extend in the order E2, RSL2, IL, RSL1, E1 instead of E1, RSL1, IL, RSL2, E2. The BLC can be above, below or to the side of E1, while the WLC is above, below or to the side of E2, for instance. The BLC and WLC are in a serial path with the RSME. By providing U-shaped portions, conductive filaments can form in a set process of the RSME, where the filaments extend in the x-direction on either side of E1 and in the y-direction. The implementation pictured can be rotated by 90 or 180 degrees as well.

[00144] In this approach, portions of the layers are arranged laterally of one another, similar to the concept of FIGs. 6F-6H, but the layers are in nested U-shapes, having two parallel portions extending at a right angle to a base portion. For example, the U-shaped RSL2 is nested within the U-shaped E2, the U-shaped IL is nested within the U-shaped RSL2, and the U-shaped RSL1 is nested within the U-shaped IL. E1 is nested within the U-shaped RSL1 but is not itself U-shaped in this example. Each portion can be the same or different in one or more dimensions.

[00145] Generally, any of the vertical stack embodiments can be adapted to an L- or U-shaped embodiment.

[00146] Here, it can be said that at least one E1, E2, IL, RSL1 and RSL2 is arranged laterally, at least in part, of at least one other of E1, E2, IL, RSL1 and RSL2.

[00147] FIG. 6K1 depicts an example implementation of the RSME of FIG. 6A which uses one RSL and one breakdown layer, below the RSL. RSL1 is used as discussed previously, but a breakdown layer is used between the IL and E2 in place of a RSL2. The breakdown layer is a material which does not have a resistance-switching behavior, and can provide a baffle layer between the IL and E2. A material with a resistance-switching behavior can typically be switched repeatedly between starting and ending resistance states. In contrast, a breakdown material is a material which has been broken down by the application of a relatively high voltage and/or current from an initial state, with an associated I-V characteristic, to a breakdown state, with another associated I-V characteristic, and generally can transition only once from the initial state to the breakdown state. A resistanceswitching material can be considered to be a many-times programmable material while a breakdown material can be considered to be a one-time programmable material. Here, programmable can include having the ability to change a resistance state. Although a resistance-switching material can be paired with a fuse or antifuse to form a one-time programmable, the resistance-switching material itself remains many-times programmable. A one-time programmable material is useful, e.g., in setting a unique identifier for a chip, or setting operating parameters such as a clock or voltage parameter.

[00148] Example materials for the breakdown layer (and an associated range of resistivity  $\rho$  for some examples before breakdown, in the initial state) include: SiN ( $\rho$ =1014  $\Omega$ -cm for Si3N4 at 25 C), SiO2 ( $\rho$ =1014-1016  $\Omega$ -cm at 25 C), SiC ( $\rho$ =102-106  $\Omega$ -cm), SiCN, SiON or any layer which can be broken down, e.g., changed from a higher resistance, generally non-conductive state to a lower resistance, conductive state, but is not generally known as a reversible resistance-switching material itself. The breakdown layer can be a material which maintains a resistance of at least about 1-10 M $\Omega$  while being conductive in the breakdown state. The resistance in the initial state is typically one or more orders of magnitude higher than in the breakdown state. If the resistance of the layer is too low, it is less effective as a protective layer. The resistance of the breakdown layer material is R= $\rho$ I/A. where I is the length of the material and A is the cross-sectional area. The length is the breakdown layer thickness. Knowing  $\rho$  and R, size of the material can be chosen using A and I.

[00149] The breakdown layer can be a one-time-programmable breakdown layer. Such a breakdown layer can be considered to be a non-switchable breakdown layer or a one-time

-30-

switchable breakdown layer because the breakdown process is irreversible. That is, once the breakdown layer is broken down from the starting non-conductive state, the breakdown layer remains in the broken down state and cannot return to the starting state. In contrast, in some cases, a unipolar or bipolar cell can be operated in a one-time-programmable mode but is usually not physically broken down while maintaining a resistance of at least about 1-10  $M\Omega$  while being conductive.

**[00150]** One or more RSLs can be configured in a breakdown state such as by applying a relatively high voltage or current to the RSL. For example, an applied voltage may be significantly higher than the threshold voltage of the material. The breakdown process may be due in part to thermal effects. See FIGs. 6K2 and 6K3 for further details.

[00151] FIG. 6K2 is a graph showing a transition from an initial state to a breakdown state for a breakdown layer. The transition can be achieved by applying a current or voltage across the breakdown layer for a period of time which can be extended, e.g., several minutes. At a time tb, a current through the breakdown layer increases step-wise (since the resistance decreases step wise) when a breakdown event occurs. In some cases, multiple breakdown events can occur. For an applied voltage, the voltage applied across the RSME will be divided across the breakdown layer and RSL1 in proportion to their respective resistances. RSL1 can be configured in a low resistance state so that essentially all of the voltage is applied across the breakdown layer.

[00152] FIG. 6K3 is a graph showing an I-V characteristic of a breakdown layer in an initial state (solid line) and in a breakdown state (dashed line). For a given voltage, the current is higher (and the resistance is lower) in the breakdown state. An RSME in which a breakdown layer is in the initial state can be distinguished from an RSME in which the breakdown layer is in the breakdown state, so that a bit of data can be stored according to the state of the breakdown layer. The RSL can further be modulated between two states to store a bit of data. By applying appropriate read voltages, the states of the breakdown layer and RSL can be determined.

[00153] FIG. 6L depicts an example implementation of the RSME of FIG. 6A which uses one reversible RSL (RSL1) and one breakdown RSL, above RSL1. This is an alternative to the configuration of FIG. 6K1.