(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2022-144242

(P2022-144242A)

(43)公開日 令和4年10月3日(2022.10.3)

(51)国際特許分類

H 0 4 N 5/378(2011.01)

H 0 4 N 5/374(2011.01)

F I

H 0 4 N 5/378

H 0 4 N 5/374テーマコード(参考)

5 C 0 2 4

審査請求 未請求 請求項の数 20 O L (全19頁)

(21)出願番号

特願2021-45158(P2021-45158)

(22)出願日

令和3年3月18日(2021.3.18)

(71)出願人

000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

110003281

特許業務法人大塚国際特許事務所

小林 秀央

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

吉田 大介

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者

F ターム(参考) 5C024 CX06 CY42 HX13 HX17

HX21 HX23 HX35 HX44

HX50

(54)【発明の名称】 光電変換装置、光電変換システムおよび移動体

## (57)【要約】

【課題】光電変換装置の動作の多様性を高めるために有利な技術を提供する。

【解決手段】光電変換装置は、複数の行および複数の列を構成するように配置された複数の画素を有する画素アレイと、前記画素アレイから信号を読み出す複数の読み出回路を含む読み出部とを備える。前記読み出部は、前記複数の読み出回路の各々は、サンプルホールド部を含み、前記サンプルホールド部は、前記画素アレイから出力されるリセットレベルを保持する第1サンプルホールド回路、および、前記画素アレイから出力される光信号レベルを保持する第2サンプルホールド回路を含む。前記複数の読み出回路は、第1グループを構成する複数の第1読み出回路と、第2グループを構成する複数の第2読み出回路とを含む。前記複数の第1読み出回路の少なくとも一部は、第1制御線を通して与えられる第1制御信号によって制御され、前記複数の第2読み出回路の少なくとも一部は、第2制御線を通して与えられる第2制御信号によって制御される。

【選択図】図 3

**【特許請求の範囲】****【請求項 1】**

複数の行および複数の列を構成するように配置された複数の画素を有する画素アレイと、前記画素アレイから信号を読み出す複数の読出回路を含む読出部と、を備える光電変換装置であって、

前記読出部は、前記複数の読出回路の各々は、サンプルホールド部を含み、前記サンプルホールド部は、前記画素アレイから出力されるリセットレベルを保持する第1サンプルホールド回路、および、前記画素アレイから出力される光信号レベルを保持する第2サンプルホールド回路を含み、

前記複数の読出回路は、第1グループを構成する複数の第1読出回路と、第2グループを構成する複数の第2読出回路とを含み、

前記複数の第1読出回路の少なくとも一部は、第1制御線を通して与えられる第1制御信号によって制御され、前記複数の第2読出回路の少なくとも一部は、第2制御線を通して与えられる第2制御信号によって制御される、

ことを特徴とする光電変換装置。

**【請求項 2】**

複数の動作モードを有し、

前記複数の動作モードは、前記第1制御信号のアクティブ期間と前記第2制御信号のアクティブ期間とが互いに異なるモードを含む、

ことを特徴とする請求項1に記載の光電変換装置。

20

**【請求項 3】**

前記第1制御信号および前記第2制御信号を発生する発生回路を更に備える、

ことを特徴とする請求項1又は2に記載の光電変換装置。

**【請求項 4】**

前記第1制御信号および前記第2制御信号をそれぞれ外部から取り込む第1パッドおよび第2パッドを更に備える、

ことを特徴とする請求項1又は2に記載の光電変換装置。

**【請求項 5】**

前記第1制御信号は、前記複数の第1読出回路を第1状態および第2状態を含む複数の状態のいずれかに設定する信号であり、

前記第2制御信号は、前記複数の第2出回路を前記複数の状態のいずれかに設定する信号であり、

30

前記第2状態は、前記第1状態よりも消費電力が小さい状態である、

ことを特徴とする請求項1乃至4のいずれか1項に記載の光電変換装置。

**【請求項 6】**

前記複数の読出回路の各々は、前記サンプルホールド部から提供される信号をそれぞれA/D変換するA/D変換器を更に含む、

ことを特徴とする請求項1乃至5のいずれか1項に記載の光電変換装置。

**【請求項 7】**

前記A/D変換器は、

型A/D変換器を含む、

40

ことを特徴とする請求項6に記載の光電変換装置。

**【請求項 8】**

前記複数の第1読出回路の各々は、それに属する前記

型A/D変換器の入力ノードの電位を前記第1制御信号に応じて固定する電位固定器を含み、

前記複数の第2読出回路の各々は、それに属する前記

型A/D変換器の入力ノードの電位を前記第2制御信号に応じて固定する電位固定器を含む、

ことを特徴する請求項7に記載の光電変換装置。

**【請求項 9】**

前記読出部は、前記サンプルホールド部の各々の出力を少なくとも2つの前記A/D変換器に供給するスイッチング回路を含む、

50

ことを特徴とする請求項 6 乃至 8 のいずれか 1 項に記載の光電変換装置。

【請求項 10】

前記読出部は、前記第 1 読出回路が割り当てられた画素の信号と前記第 2 読出回路が割り当てられた画素の信号とに応じた信号を生成可能に構成されている、

ことを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の光電変換装置。

【請求項 11】

前記読出部は、

前記第 1 グループを構成する第 1 読出回路の前記第 1 サンプルホールド回路の出力と前記第 2 グループを構成する第 2 読出回路の前記第 1 サンプルホールド回路の出力とを電気的に接続する第 1 スイッチと、

前記第 1 グループを構成する第 1 読出回路の前記第 2 サンプルホールド回路の出力と前記第 2 グループを構成する第 2 読出回路の前記第 2 サンプルホールド回路の出力とを電気的に接続する第 2 スイッチと、を更に含む、

ことを特徴とする請求項 1 乃至 8 のいずれか 1 項に記載の光電変換装置。

【請求項 12】

前記サンプルホールド部は、前記第 1 サンプルホールド回路の出力と前記第 1 サンプルホールド回路の出力とを接続する抵抗素子を含む、

ことを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の光電変換装置。

【請求項 13】

前記読出部は、前記第 1 読出回路の出力と前記第 2 読出回路の出力とを平均化する回路を含む、

ことを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の光電変換装置。

【請求項 14】

前記第 1 サンプルホールド回路は、第 1 容量素子および第 1 アンプを含み、

前記第 2 サンプルホールド回路は、第 2 容量素子および第 2 アンプを含む、

ことを特徴とする請求項 1 乃至 13 のいずれか 1 項に記載の光電変換装置。

【請求項 15】

前記第 1 容量素子と前記第 2 容量素子とは互いに隣り合うように配置されている、

ことを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の光電変換装置。

【請求項 16】

前記第 1 アンプと前記第 2 アンプとは互いに隣り合うように配置されている、

ことを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の光電変換装置。

【請求項 17】

前記第 1 容量素子と前記第 2 容量素子とは互いに隣り合うように配置され、

前記第 1 アンプと前記第 2 アンプとは互いに隣り合うように配置されている、

ことを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載の光電変換装置。

【請求項 18】

請求項 1 乃至 17 のいずれか 1 項に記載の光電変換装置と、

前記光電変換装置が出力する信号を処理する信号処理部と、

を備えることを特徴とする光電変換システム。

【請求項 19】

請求項 1 乃至 17 のいずれか 1 項に記載の光電変換装置と、

前記光電変換装置が出力する信号を処理する信号処理部と、

を備えることを特徴とする移動体。

【請求項 20】

複数の画素を有する画素アレイから信号を読み出す複数の読出回路を含む読出部を備える基板であって、

前記読出部は、前記複数の読出回路の各々は、サンプルホールド部を含み、前記サンプルホールド部は、前記画素アレイから出力されるリセットレベルを保持する第 1 サンプルホールド回路、および、前記画素アレイから出力される光信号レベルを保持する第 2 サン

10

20

30

40

50

プルホールド回路を含み、

前記複数の読み出回路は、第1グループを構成する複数の第1読み出回路と、第2グループを構成する複数の第2読み出回路とを含み、

前記複数の第1読み出回路の少なくとも一部は、第1制御線を通して与えられる第1制御信号によって制御され、前記複数の第2読み出回路の少なくとも一部は、第2制御線を通して与えられる第2制御信号によって制御される、

ことを特徴とする基板。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、光電変換装置、光電変換システムおよび移動体に関する。

【背景技術】

【0002】

特許文献1には、画素アレイ部と、行選択部と、負荷MOS部と、サンプル&ホールド部と、アナログ-デジタル変換部と、メモリ部と、データ処理部と、出力部と、タイミング制御部とを備えるイメージセンサが記載されている。アナログ-デジタル変換部は、例えば、デルタ-シグマ型アナログ-デジタル変換器(AD変換器)である。AD変換器は、第1積分器、第2積分器、量子化器、及び、デシメーションフィルタを有する。

【先行技術文献】

20

【特許文献】

【0003】

【特許文献1】国際公開第2019/069614号

【発明の概要】

【発明が解決しようとする課題】

【0004】

画素アレイから信号を読み出す読み出回路を複数のグループに分割し、該複数のグループを別個の制御信号で制御する構成を有する光電変換装置は、その動作の多様性を高めるために有利である。このような構成は、例えば、複数のグループの全てに同じ動作をさせたり、少なくとも1つのグループの動作を休止させたり、少なくとも1つのグループの動作を低消費電力状態にさせたりする機能を提供しうる。特許文献1には、このような観点に関する開示も示唆もない。

30

【0005】

本発明は、光電変換装置の動作の多様性を高めるために有利な技術を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の1つの側面は、複数の行および複数の列を構成するように配置された複数の画素を有する画素アレイと、前記画素アレイから信号を読み出す複数の読み出回路を含む読み出部と、を備える光電変換装置であって、前記読み出部は、前記複数の読み出回路の各々は、サンプルホールド部を含み、前記サンプルホールド部は、前記画素アレイから出力されるリセットレベルを保持する第1サンプルホールド回路、および、前記画素アレイから出力される光信号レベルを保持する第2サンプルホールド回路を含み、前記複数の読み出回路は、第1グループを構成する複数の第1読み出回路と、第2グループを構成する複数の第2読み出回路とを含み、前記複数の第1読み出回路の少なくとも一部は、第1制御線を通して与えられる第1制御信号によって制御され、前記複数の第2読み出回路の少なくとも一部は、第2制御線を通して与えられる第2制御信号によって制御される。

40

【発明の効果】

【0007】

本発明によれば、光電変換装置の動作の多様性を高めるために有利な技術が提供される

50

。

## 【図面の簡単な説明】

## 【0008】

【図1】第1実施形態の光電変換装置の構成を示す図。

【図2】画素の構成例を示す図。

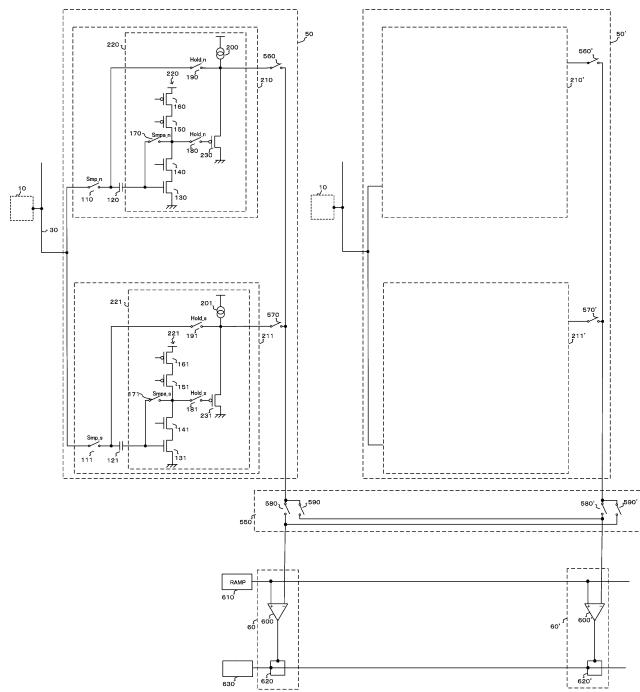

【図3】第1実施形態のサンプルホールド回路およびA/D変換器の構成例を示す図。

【図4】第1実施形態のサンプルホールド回路の駆動例を示す図。

【図5】第1制御線、第2制御線およびサンプルホールド部の物理的な配置例を模式的に示す図。

【図6】第1サンプルホールド回路の第1容量素子および第1反転増幅器、および、第2サンプルホールド回路の第2容量素子および第2反転増幅器の物理的な配置例を模式的に示す図。 10

【図7】第1サンプルホールド回路の第1容量素子および第1反転増幅器、および、第2サンプルホールド回路の第2容量素子および第2反転増幅器の他の物理的な配置例を模式的に示す図。

【図8】第1サンプルホールド回路の第1容量素子および第1反転増幅器、および、第2サンプルホールド回路の第2容量素子および第2反転増幅器の更に他の物理的な配置例を模式的に示す図。

【図9】第2実施形態の光電変換装置におけるサンプルホールド回路およびA/D変換器の構成例を示す図。 20

【図10】第3実施形態の光電変換装置の構成を示す図。

【図11】第3実施形態の光電変換装置におけるサンプルホールド回路およびA/D変換器の構成例を示す図。

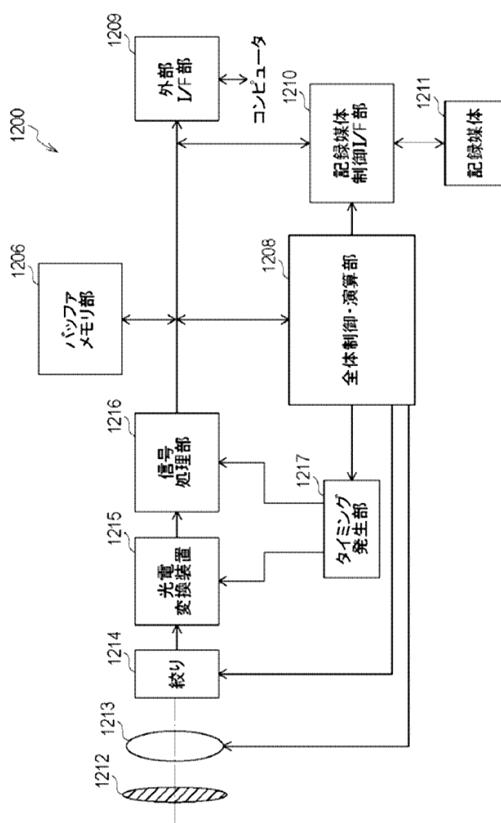

【図12】一実施形態の光電変換システムの構成を示す図。

【図13】一実施形態の光電変換システムおよび移動体の構成を示す図。

## 【発明を実施するための形態】

## 【0009】

以下、添付図面を参照して実施形態を詳しく説明する。なお、以下の実施形態は特許請求の範囲に係る発明を限定するものではない。実施形態には複数の特徴が記載されているが、これらの複数の特徴の全てが発明に必須のものとは限らず、また、複数の特徴は任意に組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参照番号を付し、重複した説明は省略する。 30

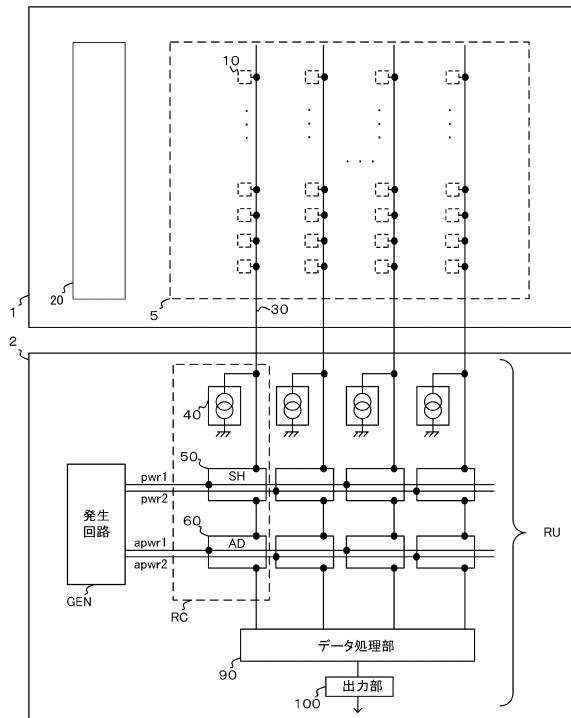

## 【0010】

図1には、第1実施形態の光電変換装置ISDの構成が示されている。光電変換装置ISDは、イメージセンサあるいは撮像装置として構成されうる。他の観点において、光電変換装置ISDは、画像を撮像し、撮像した画像またはそれを処理して得られる画像または情報を外部装置、例えば、記憶装置、処理装置、表示装置、通信装置等に出力するように構成されうる。

## 【0011】

光電変換装置ISDは、例えば、画素アレイ5および読出部RUを備えうる。画素アレイ5は、複数の行および複数の列を構成するように配置された複数の画素10を有する。行に沿った方向は、行方向と呼ぶことができ、列に沿った方向は、列方向と呼ぶことができる。便宜的に、行方向は、水平方向あるいは第1方向と呼ぶことができ、列方向は、垂直方向あるいは第2方向と呼ぶことができる。画素アレイ5には、複数の垂直信号線30が配置されている。画素アレイ5における複数の画素10が構成する複数の列の各々に対して少なくとも1つの垂直信号線30が割り当てられうる。読出部RUは、画素アレイ5から信号を読み出す複数の読出回路RCを含む。各読出回路RCは、1つの垂直信号線30に対して接続されうる。光電変換装置ISDは、更に、画素アレイ5の行を選択する行選択回路20を備える。 40

## 【0012】

10

20

30

40

50

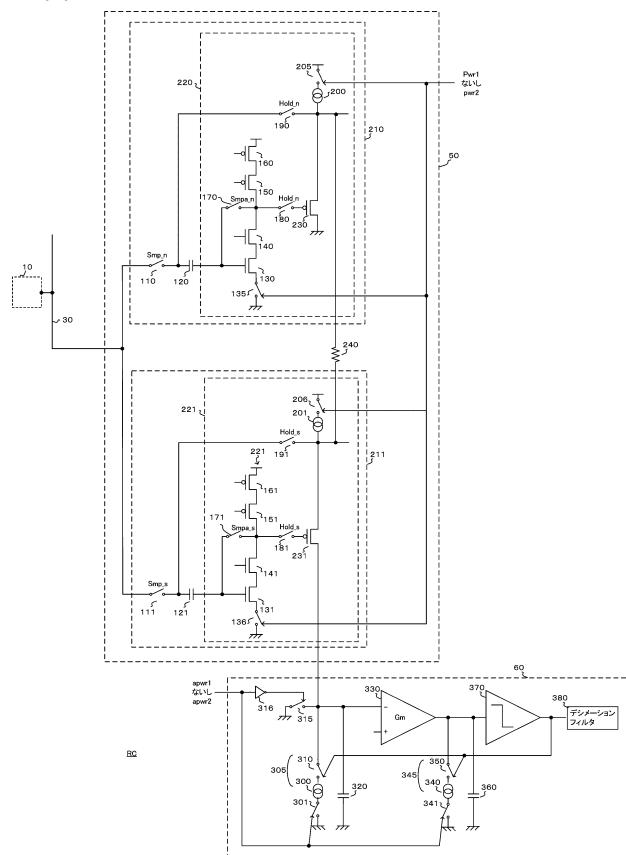

読み出回路 R C は、例えば、電流源 4 0 と、サンプルホールド部 5 0 と、A D (アナログ - デジタル) 変換器 6 0 とを含みうる。電流源 4 0 は、垂直信号線 3 0 に接続され、垂直信号線 3 0 に定電流を流す。サンプルホールド部 5 0 は、画素アレイ 5 の選択された画素 1 0 から垂直信号線 3 0 を介して出力される信号をサンプルホールドする。この信号は、画素アレイ 5 の選択された画素 1 0 から垂直信号線 3 0 を介して出力されるリセットレベルと、画素アレイ 5 の選択された画素 1 0 から垂直信号線 3 0 を介して出力される光信号レベルとを含みうる。図 3 に例示されるように、各読み出回路 R C は、画素アレイ 5 から垂直信号線 3 0 を介して出力されるリセットレベル、光信号レベルをそれぞれ保持する第 1 、第 2 サンプルホールド回路 2 1 0 、 2 1 1 を含みうる。A D 変換器 6 0 は、サンプルホールド部 5 0 から出力される信号をアナログ - デジタル変換 (A D 変換) する。A D 変換器 6 0 は、例えば、スロープ型 A D 変換器、逐次比較型 A D 変換器または (デルタシグマ) 型 A D 変換器でありうるが、これらに限定されるものではない。

#### 【 0 0 1 3 】

その他、読み出部 R U は、複数の読み出回路 R C から出力されるデータあるいは画像を処理する処理部 9 0 と、データを処理部 9 0 によって処理されたデータあるいは画像を出力する出力部 1 0 0 とを含みうる。データ処理部 9 0 は、複数の読み出回路 R C から出力されるデータあるいは画像を処理した画像を生成してもよいし、その画像を更に処理して目的とするデータを生成してもよい。データ処理部 9 0 による処理は、例えば、複数の読み出回路 R C から出力されるデータあるいは画像を補正する処理、および、複数の読み出回路 R C から出力されるデータあるいは画像に対する補間処理を含みうる。

#### 【 0 0 1 4 】

一例において、画素アレイ 5 は、第 1 基板 1 に配置され、読み出部 R U は、第 2 基板に配置されてよい。行選択回路 2 0 は、第 1 基板 1 に配置されてもよいし、第 2 基板 2 に配置されてよい。しかしながら、画素アレイ 5 および読み出部 R U は、1 つの基板に配置されてもよい。また、読み出部 R U を構成する複数の要素は、複数の基板に分割して配置されてもよい。

#### 【 0 0 1 5 】

複数の読み出回路 R C は、第 1 グループを構成する複数の第 1 読出回路と、第 2 グループを構成する複数の第 2 読出回路とを含みうる。図 1 に示された例では、奇数列に配置された読み出回路 R C は、第 1 読出回路であり、偶数列に配置された読み出回路 R C が第 2 読出回路であるが、これは一例に過ぎない。複数の第 1 読出回路は、第 1 制御線 p w r 1 、 a p w r 1 を通して与えられる第 1 制御信号によって制御され、複数の第 2 読出回路は、第 2 制御線 p w r 2 、 a p w r 2 を通して与えられる第 2 制御信号によって制御される。なお、本明細書では、説明の簡略化のために、信号線を識別する名称は、その信号線に出力される信号を識別する名称としても用いられる。例えば、第 1 制御線 p w r 1 を通して第 1 制御信号 p w r 1 が第 1 読出回路に与えられる。

#### 【 0 0 1 6 】

光電変換装置 I S D は、第 1 制御信号 p w r 1 、 a p w r 1 および第 2 制御信号 p w r 2 、 a p w r 2 を発生する発生回路 G E N を備えうる。あるいは、光電変換装置 I S D は、第 1 制御信号 p w r 1 、 a p w r 1 および第 2 制御信号 p w r 2 、 a p w r 2 をそれぞれ外部から取り込む第 1 パッドおよび第 2 パッドを備えてもよい。第 1 パッドおよび第 2 パッドは、光電変換装置 I S D を構成する 1 又は複数の基板を封止するパッケージの第 1 ピンおよび第 2 ピンにそれぞれ接続されうる。光電変換装置 I S D は、複数の動作モードを有することができ、該複数の動作モードは、第 1 制御信号 p w r 1 、 a p w r 1 のアクティブ期間と第 2 制御信号 p w r 2 、 a p w r 2 のアクティブ期間とが互いに異なるモードを含みうる。

#### 【 0 0 1 7 】

表 1 には、第 1 、第 2 、第 3 モードにおける第 1 制御信号 p w r 1 、 a p w r 1 および第 2 制御信号 p w r 2 、 a p w r 2 の論理レベルが例示されている。第 1 制御信号 p w r 1 、 a p w r 1 は、複数の第 1 読出回路を第 1 状態および第 2 状態を含む複数の状態のい

10

20

30

40

50

すれかに設定する信号でありうる。第2制御信号pwr2、apwr2は、複数の第2出回路を該複数の状態のいずれかに設定する信号でありうる。該第2状態は、該第1状態よりも消費電力が小さい状態でありうる。

【0018】

【表1】

| モード   | pwr1 | pwr2 | apwr1 | apwr2 |

|-------|------|------|-------|-------|

| 第1モード | H    | H    | H     | H     |

| 第2モード | H    | L    | H     | L     |

| 第3モード | L    | H    | L     | H     |

10

【0019】

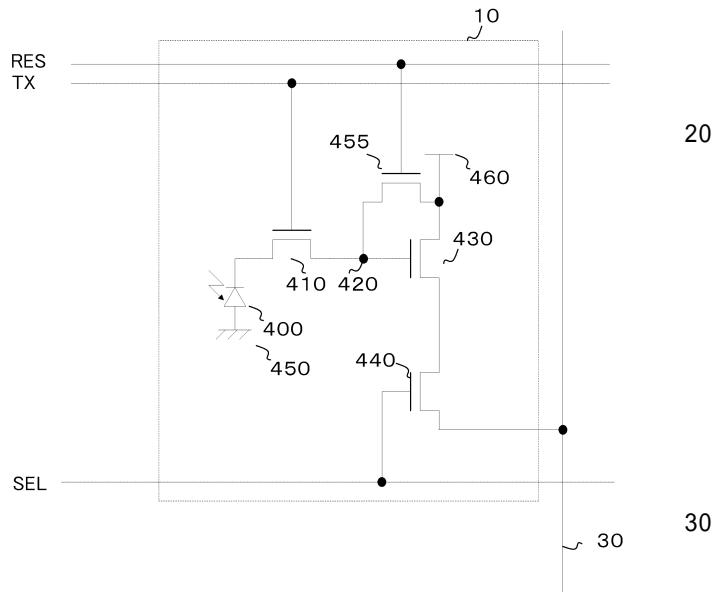

図2には、画素10の構成例が示されている。画素10は、例えば、光電変換素子400、転送トランジスタ410、リセットトランジスタ455、増幅トランジスタ430および選択トランジスタ440を含む。光電変換素子400は、例えば、フォトダイオードでありうる。光電変換素子400は、主電極のうちの一方が、接地電位450に接続されており、受光した光をその光量に応じた電荷量の信号電荷（例えば、光電子）に光電変換し蓄積しうる。光電変換素子400の主電極のうちの他方は、転送トランジスタ410を介して増幅トランジスタ430のゲート電極に電気的に接続されうる。増幅トランジスタ430のゲート電極を含むノード420は、フローティングディフュージョンとして機能しうる。フローティングディフュージョンは、光電変換素子400で生成された信号電荷を信号電圧に変換する電荷電圧変換部である。

20

【0020】

転送トランジスタ410のゲート電極には、行選択回路20から転送信号TXが供給される。転送トランジスタ410が転送信号TXに応じて導通状態になることによって、光電変換素子400で光電変換され蓄積された信号電荷がフローティングディフュージョンであるノード420に転送される。

20

【0021】

リセットトランジスタ455は、電源電位460とノード420との間に接続されうる。ここで、トランジスタがAとBとの間に接続されていると表現した場合、トランジスタの2つの主電極のうち一方がAに電気的に接続され、2つの主電極のうち他方がBに電気的に接続されていることを示す。また、前記表現において、トランジスタのゲート電極はAにもBにも接続されていない。リセットトランジスタ455のゲート電極には、行選択回路20からリセット信号RESが供給される。リセットトランジスタ455がリセット信号RESに応じて導通状態になることによって、ノード420（フローティングディフュージョン）の電位が電源電位460に応じた電位にリセットされ、フローティングディフュージョンの電荷が掃き出される。

30

【0022】

増幅トランジスタ430は、そのゲート電極がノード420に、2つの主電極のうち一方が電源電位460に、2つの主電極のうち他方が選択トランジスタ440に、それぞれ接続されうる。増幅トランジスタ430は、光電変換素子400の光電変換によって得られた信号を読み出すソースフォロワの入力部を構成しうる。つまり、増幅トランジスタ430は、2つの主電極のうち他方が選択トランジスタ440を介して垂直信号線30に電気的に接続される。増幅トランジスタ430と垂直信号線30に接続された電流源40とは、ノード420の電圧に応じた電位を垂直信号線30に出力するソースフォロワを構成する。

40

【0023】

選択トランジスタ440は、増幅トランジスタ430と垂直信号線30との間に接続されうる。選択トランジスタ440のゲート電極には、行選択回路20から選択信号SELが供給される。選択トランジスタ440が選択信号SELに応じて導通状態になることによって、画素10が選択状態となり、増幅トランジスタ430から出力される信号が垂直

50

信号線 3 0 に伝達される。

【 0 0 2 4 】

画素 1 0 の回路構成は、図 2 に示される構成に限定されるものではない。例えば、選択トランジスタ 4 4 0 は、電源電位 4 6 0 と増幅トランジスタ 4 3 0 との間に接続されてもよい。また、図 2 に示される構成では、画素 1 0 は、転送トランジスタ 4 1 0 、リセットトランジスタ 4 5 5 、増幅トランジスタ 4 3 0 および選択トランジスタ 4 4 0 を含む構成を有するが、画素 1 0 の構成は、これに限られるものではない。例えば、選択トランジスタ 4 4 0 を省略し、増幅トランジスタ 4 3 0 が選択トランジスタとしても機能させててもよい。また、光電変換装置 1 0 0 0 に要求される仕様などに応じて、トランジスタの数を増やしもよい。画素 1 0 からは、リセットトランジスタ 4 5 5 によってノード 4 2 0 の電位をリセットしたときのリセットレベルと、光電変換素子 4 0 0 からノード 4 2 0 に電荷を転送したときの光信号レベルとが時分割で出力されうる。

【 0 0 2 5 】

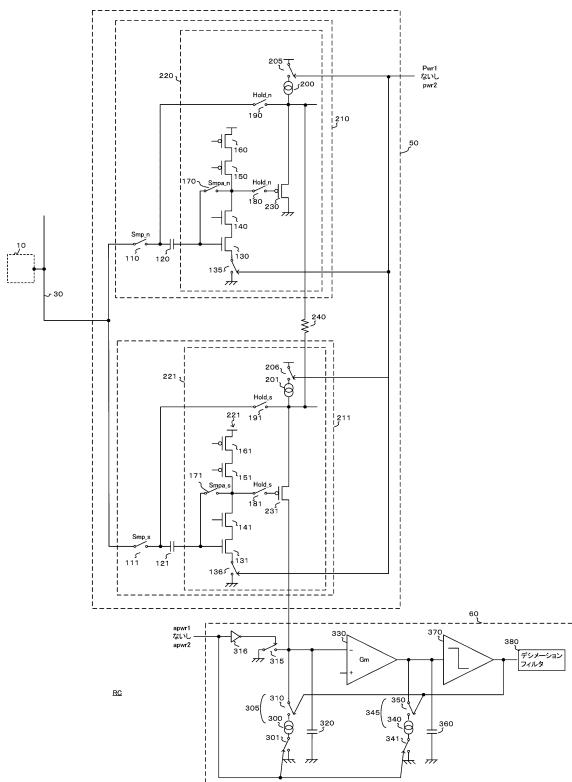

図 3 には、第 1 実施形態のサンプルホールド回路 5 0 および A D 変換器 6 0 の構成例が示されている。図 3 に示された構成例では、各読出回路 R C は、第 1 、第 2 サンプルホールド回路 2 1 0 、 2 1 1 を含む。第 1 サンプルホールド回路 2 1 0 は、画素アレイ 5 から垂直信号線 3 0 を介して出力されるリセットレベルをサンプルホールドする。第 2 サンプルホールド回路 2 1 1 は、画素アレイ 5 から垂直信号線 3 0 を介して出力される光信号レベルをサンプルホールドする。

【 0 0 2 6 】

第 1 サンプルホールド回路 2 1 0 は、例えば、スイッチ 1 1 0 、第 1 容量素子 1 2 0 および第 1 反転増幅器（第 1 アンプ） 2 2 0 を含みうる。スイッチ 1 1 0 は、光電変換装置 I S D が備える不図示の制御回路が発生する制御信号 S m p \_ n に従って、垂直信号線 3 0 と容量素子 1 2 0 との間の接続を制御しうる。反転増幅器 2 2 0 は、例えば、ソース接地回路およびソースフォロア回路の組み合わせによって構成されうる。反転増幅器 2 2 0 は、例えば、トランジスタ 1 3 0 、 1 4 0 、 1 5 0 、 1 6 0 、 2 3 0 、スイッチ 1 7 0 、 1 8 0 、 1 9 0 、および、電流源 2 0 0 を含みうる。スイッチ 1 7 0 は、例えば、ソース接地回路の入出力間に接続されており、不図示の制御回路が発生する制御信号 S m p a \_ n によって制御されうる。反転増幅器 2 2 0 からは、リセットレベルを反転増幅した信号が、不図示の制御回路が発生する制御信号 H o l d \_ n に従って出力されうる。

【 0 0 2 7 】

第 2 サンプルホールド回路 2 1 1 は、サンプルホールド回路 2 1 0 と同様の構成を有しうる。具体的には、第 2 サンプルホールド回路 2 1 1 は、例えば、スイッチ 1 1 1 、第 2 容量素子 1 2 1 および第 2 反転増幅器（第 2 アンプ） 2 2 1 を含みうる。スイッチ 1 1 1 は、不図示の制御回路が発生する制御信号 S m p \_ s に従って、垂直信号線 3 0 と容量素子 1 2 1 との間の接続を制御しうる。反転増幅器 2 2 1 は、ソース接地回路およびソースフォロア回路の組み合わせによって構成されうる。反転増幅器 2 2 1 は、例えば、トランジスタ 1 3 1 、 1 4 1 、 1 5 1 、 1 6 1 、 2 3 1 、スイッチ 1 7 1 、 1 8 1 、 1 9 1 、および、電流源 2 0 1 を含みうる。スイッチ 1 7 1 は、例えば、ソース接地回路の入出力間に接続されており、不図示の制御回路が発生する制御信号 S m p a \_ n によって制御されうる。反転増幅器 2 2 1 からは、光信号レベルを反転増幅した信号が、不図示の制御回路が発生する制御信号 H o l d \_ s に従って出力されうる。

【 0 0 2 8 】

リセットレベルをサンプルホールドするサンプルホールド回路 2 1 0 の出力端と光信号レベルをサンプルホールドするサンプルホールド回路 2 1 1 の出力端とは、抵抗素子 2 4 0 によって接続されうる。抵抗素子 2 4 0 を流れる電流 I は、サンプルホールド回路 2 1 0 の出力端の電位、つまりリセットレベルに応じた電位を V n 、サンプルホールド回路 2 1 1 の出力端の電位、つまり光信号レベルに応じた電位を V s 、抵抗素子 2 4 0 の抵抗値を R とすると、

$$I = (V_n - V_s) / R$$

10

20

30

40

50

と表される。電流  $I$  は、A D 変換器 6 0 に供給される。抵抗素子 2 4 0 を流れる電流  $I$  は、リセットレベルに応じたリセット信号の電位  $V_n$  と光信号レベルに応じた電位  $V_s$  との差分に比例する。したがって、電流  $I$  が A D 変換器 6 0 に入力される段階で C D S ( 相関 2 重サンプリング ) が行われていることになる。

#### 【 0 0 2 9 】

図 3 に示された構成例では、A D 変換器 6 0 は、

型 A D 変換器で構成されている。

型のアナログデジタル変換回路 3 9 0 は、例えば、第 1 積分器、第 2 積分器、量子化器 3 7 0 およびデシメーションフィルタ 3 8 0 を含みうる。第 1 積分器は、積分容量 3 2 0 によって構成されうる。第 2 積分器は、電圧を電流に変換する G m セル 3 3 0 および積分容量 3 6 0 によって構成されうる。第 1 積分器の入力ノードには、電流源 3 0 0 およびスイッチ 3 1 0 を含む D A ( デジタル - アナログ ) 変換器 3 0 5 の出力が接続されうる。D A 変換器 3 0 5 は、量子化器 3 7 0 の出力に応じた電流を電流  $I$  から減じる。第 2 積分器の入力ノードには、電流源 3 4 0 およびスイッチ 3 5 0 を含む D A 変換器 3 4 5 の出力が接続されうる。D A 変換器 3 4 5 は、G m セル 3 3 0 の出力電流から量子化器 3 7 0 の出力に応じた電流を減じる。

#### 【 0 0 3 0 】

型 A D 変換器として構成された A D 変換器 6 0 では、量子化器 3 7 0 の出力を D A 変換器 3 0 5 、 3 4 5 を通して第 1 積分器および第 2 積分器にフィードバックする動作が行われる。量子化器 3 7 0 の出力を D A 変換器 3 0 4 、 3 4 5 によってフィードバックしながら第 1 、第 2 積分器を通すことによって 2 次のノイズシェーピング特性を得ることができる。さらに、量子化器 3 7 0 の後段に配されているデシメーションフィルタ 3 8 0 によって高域ノイズを除去することで、精度が高いアナログデジタル変換出力を得ることができる。

#### 【 0 0 3 1 】

図 4 には、サンプルホールド回路 2 1 0 、 2 1 1 の駆動例が示されている。図 4 には、垂直信号線 3 0 の電位、サンプルホールド回路 2 1 0 、 2 1 1 の各スイッチの制御信号 S m p \_ n 、 S m p a \_ n 、 H l o d \_ n 、 s m p \_ s 、 s m p a \_ s 、 h l o d \_ s のそれぞれの波形が示されている。図 4 の波形において、制御信号がハイレベルの間、それが入力されるスイッチがオン状態 ( 導通状態 ) になり、制御信号がローレベルの間、それが入力されるスイッチがオフ状態 ( 不導通状態 ) になるものとする。

#### 【 0 0 3 2 】

まず、時刻  $t_1$  において、制御信号 S m p \_ n 、 S m p a \_ n がハイレベルになり、リセットレベルをサンプルホールドするためのサンプルホールド回路 2 1 0 において、スイッチ 1 1 0 、 1 7 0 がオン状態になる。次いで、制御信号 S m p a \_ n がハイレベルからローレベルに遷移する時刻  $t_2$  において、リセットレベルに応じた電位  $V_n$  がサンプリングされて容量素子 1 2 0 に蓄積される。

#### 【 0 0 3 3 】

次に、時刻  $t_3$  において、制御信号 S m p \_ n がハイレベルからローレベルへ遷移し、制御信号 H o l d \_ n がハイレベルとなり、スイッチ 1 8 0 、 1 9 0 がオン状態になる。これによって、サンプルホールド回路 2 1 0 において、容量素子 1 2 0 がリセットレベルに応じた電位  $V_n$  をホールドする。容量素子 1 2 0 にサンプリングされホールドされた電位  $V_n$  に応じた電位がサンプルホールド回路 2 1 0 から出力される。

#### 【 0 0 3 4 】

時刻  $t_4$  において、垂直信号線 3 0 に画素 1 0 からの光信号レベルの出力が開始される。次いで、時刻  $t_5$  において、制御信号 S m p \_ s 、 S m p a \_ s がハイレベルになり、光信号レベルをサンプルホールドするためのサンプルホールド回路 2 1 1 において、スイッチ 1 1 0 、 1 7 0 がオン状態になる。次いで、制御信号 S m p a \_ s がハイレベルからローレベルに遷移する時刻  $t_6$  において、光信号レベルに応じた電位  $V_s$  がサンプリングされて容量素子 1 2 0 に蓄積される。

#### 【 0 0 3 5 】

10

20

30

40

50

次いで、時刻  $t_7$  において制御信号  $Smp\_s$  がハイレベルからローレベルに遷移し、時刻  $t_8$  において、制御信号  $Hol\_d\_n$  がハイレベルとなり、スイッチ  $181, 191$  がオン状態になる。これによって、サンプルホールド回路  $211$  において、容量素子  $121$  が光信号レベルに応じた電位  $V_s$  をホールドする。容量素子  $121$  にサンプリングされホールドされた電位  $V_s$  がサンプルホールド回路  $210$  から出力される。上述したように、サンプルホールド回路  $210$  の出力端の電位  $V_n$  とサンプルホールド回路  $211$  の出力端のデータ信号の電位  $V_s$  との差に応じた電流が  $DA$  変換器  $60$  に入力される。次いで、時刻  $t_9$  において、制御信号  $Hol\_d\_n, Hol\_d\_s$  がローレベルになる。

#### 【0036】

各読み出回路  $RC$  のサンプルホールド部  $50$  には、電源ラインと接地ラインとの間の経路を遮断するスイッチが設けられる。具体的には、サンプルホールド回路  $210$  には、電源ラインと接地ラインとの間の経路を遮断するスイッチ  $135, 205$  が設けられ、サンプルホールド回路  $211$  には、電源ラインと接地ラインとの間の経路を遮断するスイッチ  $136, 206$  が設けられる。また、各読み出回路  $RC$  の  $AD$  変換器  $60$  において、電源ラインと接地ラインとの間の経路を遮断するスイッチが設けられる。具体的には、 $AD$  変換器  $60$  には、電源ラインと接地ラインとの間の経路を遮断するスイッチ  $301, 341$  が設けられる。

#### 【0037】

第1グループを構成する複数の第1読み出回路のサンプルホールド回路  $210$  のスイッチ  $135, 205$  には、第1制御信号  $pwr_1$  が供給される。第1グループを構成する複数の第1読み出回路の  $AD$  変換器  $60$  のスイッチ  $301, 341$  には、第1制御信号  $apwr_1$  が供給される。第2グループを構成する複数の第2読み出回路のサンプルホールド回路  $210$  のスイッチ  $135, 205$  には、第2制御信号  $pwr_2$  が供給される。第2グループを構成する複数の第2読み出回路の  $AD$  変換器  $60$  のスイッチ  $301, 341$  には、第2制御信号  $apwr_2$  が供給される。

#### 【0038】

表1に示された第1モードでは、第1制御信号  $pwr_1, apwr_1$  がハイレベルで、第2制御信号  $pwr_2, apwr_2$  がハイレベルに駆動されるので、第1グループおよび第2グループの双方が第1状態（通常動作状態）となる。

#### 【0039】

表1に示された第2モードでは、第1制御信号  $pwr_1, apwr_1$  がハイレベルで、第2制御信号  $pwr_2, apwr_2$  がローレベルに駆動されるので、第1グループが第1状態（通常動作状態）、第2グループが第2状態（省電力状態）となる。図1の例では、第2モードにおいて、第1グループの読み出回路  $RC$ 、即ち第1読み出回路である奇数列の読み出回路  $RC$  が第1状態（通常動作状態）となり、第2グループの読み出回路  $RC$ 、即ち第2読み出回路である偶数列の読み出回路  $RC$  が第2状態（省電力状態）となる。

#### 【0040】

表1に示された第3モードでは、第1制御信号  $pwr_1, apwr_1$  がローレベルで、第2制御信号  $pwr_2, apwr_2$  がハイレベルに駆動されるので、第1グループが第2状態（省電力状態）、第2グループが第1状態（通常動作状態）となる。図1の例では、第3モードにおいて、第1グループの読み出回路  $RC$ 、即ち第1読み出回路である奇数列の読み出回路  $RC$  が第2状態（省電力状態）となり、第2グループの読み出回路  $RC$ 、即ち第2読み出回路である偶数列の読み出回路  $RC$  が第1状態（通常動作状態）となる。

#### 【0041】

量子化器  $370$  の出力をローレベルに固定できるように量子化器  $370$  を構成し、第2状態（省電力状態）では、量子化器  $370$  の出力をローレベルに固定し、これによりスイッチ  $310, 350$  をオフさせてよい。この場合、スイッチ  $301, 341$  は不要であり、制御信号  $apwr_1$  または  $apwr_2$  によって量子化器  $370$  の出力を制御すればよい。

#### 【0042】

10

20

30

40

50

読み出回路 R C は、スイッチ 205、206、301（又は 310）をオフするとき、A D 変換器 60（Gm セル 330）の入力ノードの電位を制御信号 a p w r 1 または a p w r 2 に応じて固定する電位固定器 315 を備えうる。他の観点において、読み出回路 R C は、電流源 200、201、300 をオフするときに A D 変換器 60（Gm セル 330）の入力ノードの電位を制御信号 a p w r 1 または a p w r 2 に応じて固定する電位固定器 315 を備えうる。ここで、電位固定器 315 が存在しない場合、電流源 200、201、300 をオフするときに A D 変換器 60（Gm セル 330）の入力ノードがフローティング状態になりうる。この場合、カップリングノイズ、電源ラインの電位変動、接地ラインの電位変動が A D 変換器 60（例えば、Gm セル 330）の誤動作を引き起こし、電力を消費しうる。電位固定器 315 は、このような問題を解決するために有効である。

10

## 【0043】

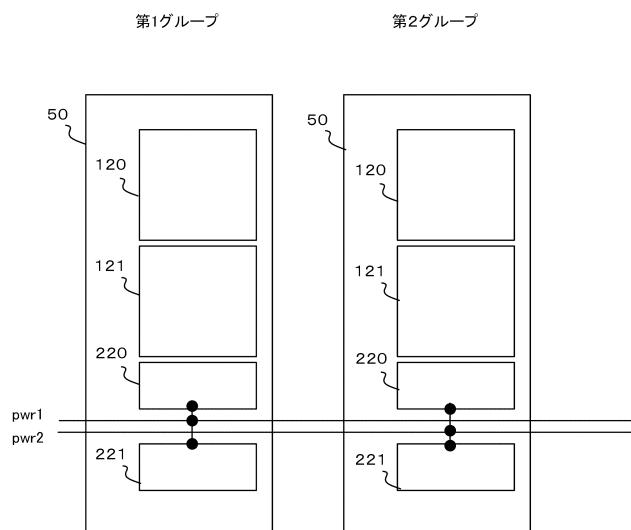

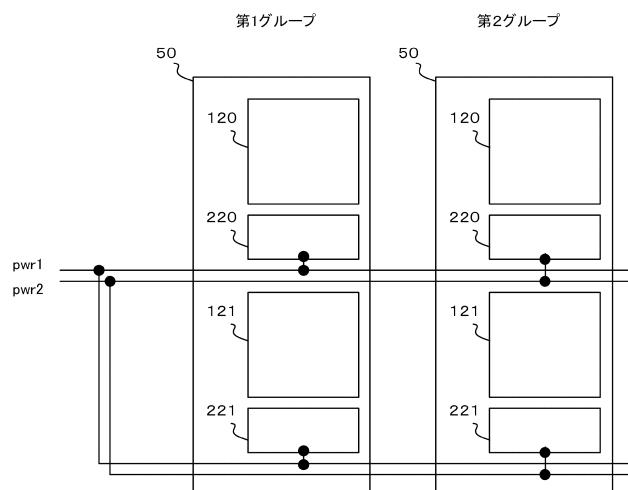

図 5 には、第 1 制御線 p w r 1、第 2 制御線 p w r 2 およびサンプルホールド部 50 の物理的な配置例が模式的に示されている。1 つのサンプルホールド部 50 のサンプルホールド回路 210、211 の双方に対して、第 1 制御線 p w r 1 のおよび第 2 制御線 p w r 2 のいずれ一方が接続される。図 1 の例に従えば、奇数列（第 1 グループ）のサンプルホールド部 50 のサンプルホールド回路 210、211 には第 1 制御線 p w r 1 が接続される。一方、偶数列（第 2 グループ）のサンプルホールド部 50 のサンプルホールド回路 210、211 には第 2 制御線 p w r 2 が接続される。また、第 1 グループの複数のサンプルホールド部 50 によって第 1 制御線 p w r 1 が共有され、第 2 グループの複数のサンプルホールド部 50 によって第 2 制御線 p w r 2 が共有される。このような構成は、第 1 制御線 p w r 1 のおよび第 2 制御線 p w r 2 の配線の単純化に有利である。

20

## 【0044】

図 6 には、第 1 サンプルホールド回路 210 の第 1 容量素子 120 および第 1 反転増幅器 220、および、第 2 サンプルホールド回路 211 の第 2 容量素子 121 および第 2 反転増幅器 221 の物理的な配置例が模式的に示されている。図 6 に例示されるように、第 1 容量素子 120 と第 2 容量素子 120 とは、行方向に関して、互いに隣り合うように配置されうる。また、第 1 反転増幅器 220 と第 2 反転増幅器 221 とは、行方向に関して、互いに隣り合うように配置されうる。

## 【0045】

図 7 には、第 1 サンプルホールド回路 210 の第 1 容量素子 120 および第 1 反転増幅器 220、および、第 2 サンプルホールド回路 211 の第 2 容量素子 121 および第 2 反転増幅器 221 の他の物理的な配置例が模式的に示されている。図 7 に例示されるように、第 1 容量素子 120 と第 2 容量素子 120 とは、列方向に関して、互いに隣り合うように配置されうる。また、第 1 反転増幅器 220 と第 2 反転増幅器 221 とは、列方向に関して、互いに隣り合うように配置されうる。

30

## 【0046】

図 6 および図 7 に示例示されるように、第 1 容量素子 120 と第 2 容量素子 120 とを隣接して配置する構成は、1 容量素子 120 と第 2 容量素子 120 との間の容量値のばらつきを低減するために有利である。また、第 1 反転増幅器 220 と第 2 反転増幅器 221 とを隣接して配置する構成は、第 1 反転増幅器 220 と第 2 反転増幅器 221 との間の特性のばらつきを低減するために有利である。容量値のばらつきの低減および反転増幅器（アンプ）の特性ばらつきの低減は、CDS 性能の向上に有利である。更に、このような構成は、制御線 p w r 1、p w r 2 の配線面積を低減するために有利である。

40

## 【0047】

図 8 には、第 1 サンプルホールド回路 210 の第 1 容量素子 120 および第 1 反転増幅器 220、および、第 2 サンプルホールド回路 211 の第 2 容量素子 121 および第 2 反転増幅器 221 の更に他の物理的な配置例が模式的に示されている。図 8 の構成例は、ばらつきの低減、反転増幅器（アンプ）の特性ばらつきの低減、および、制御線の配線面積の低減の観点で図 6 または図 7 に示された構成例より劣るが、本発明は、このような配置を排除するものではない。

50

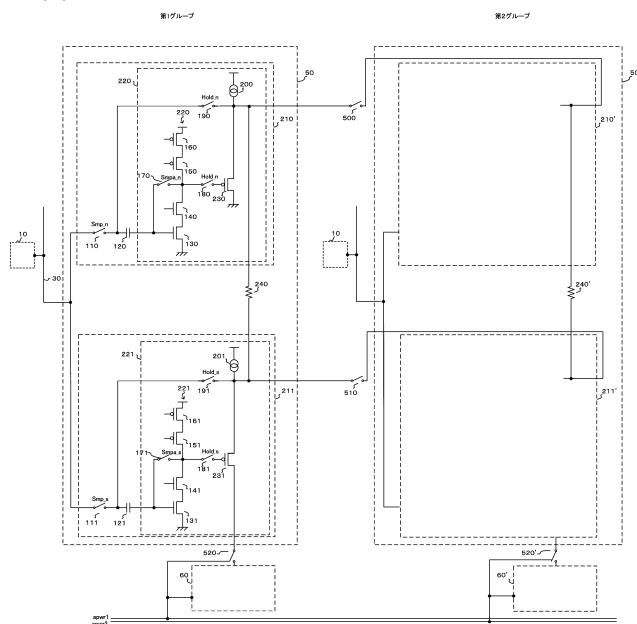

## 【0048】

図9には、第2実施形態の光電変換装置ISDにおけるサンプルホールド回路50およびAD変換器60の構成例が示されている。第2実施形態として言及しない事項は、第1実施形態に従う。第2実施形態では、読出部RUは、第1読出回路が割り当てられた画素の信号と第2読出回路が割り当てられた画素の信号とに応じた信号を生成可能に構成されている。読出部RUは、第2モードまたは第3モードにおいて、第1読出回路が割り当てられた画素の信号と第2読出回路が割り当てられた画素の信号とに応じた信号を生成しうる。ここで、第1読出回路を構成するサンプルホールド部50およびAD変換器60と第2読出回路を構成するサンプルホールド部50およびAD変換器60とを区別するために、後者を示す符号に'を付して説明する。

10

## 【0049】

読出部RUは、例えば、第1スイッチ500と、第2スイッチ510とを含みうる。ここで、1つの第1読出回路と1つの第2読出回路とに対して、1つの第1スイッチ500と1つの第2スイッチ510とが設けられうる。他の観点で説明すると、互いに隣り合う1つの第1読出回路と1つの第2読出回路とに対して、1つの第1スイッチ500と1つの第2スイッチ510とが設けられうる。第1スイッチ500は、第1グループの第1読出回路50の第1サンプルホールド回路210の出力と第2グループの第2読出回路50'の第1サンプルホールド回路210'の出力とを電気的に接続可能に配置されうる。第2スイッチ510は、第1グループの第1読出回路50の第2サンプルホールド回路211の出力と第2グループの第2読出回路50'の第2サンプルホールド回路211'の出力とを電気的に接続可能に配置されうる。第1スイッチ500および第2スイッチ510は、第2モードおよび第3モードにおいて、オンするように制御されうる。

## 【0050】

第1スイッチ500をオンさせることによって、第1グループの第1読出回路50の第1サンプルホールド回路210の出力端の電位Vnと第2グループの第2読出回路50'の第1サンプルホールド回路210'の出力端の電位Vn'が平均化されうる。第2スイッチ510をオンさせることによって、第1グループの第1読出回路50の第2サンプルホールド回路211の出力端の電位Vsと第2グループの第2読出回路50'の第2サンプルホールド回路211'の出力端の電位Vs'が平均化されうる。

30

## 【0051】

第2実施形態によれば、第2モードまたは第3モードにおいて、省電力化を達成しつつ、2つの画素の信号の平均化によるノイズ化を実現することができる。

## 【0052】

図10には、第3実施形態の光電変換装置ISDの構成が示されている。図11には、第3実施形態の光電変換装置ISDにおけるサンプルホールド回路50およびAD変換器60の構成例が示されている。第3実施形態として言及しない事項は、第1実施形態に従う。第3実施形態では、複数のサンプルホールド部50と複数のAD変換器60との間にスイッチング回路550が配置されている。スイッチング回路550は、第2モードおよび第3モードにおいて、通常動作状態のサンプルホールド回路50の出力をそのサンプルホールド回路50と同一列のAD変換器60と、そのAD変換器60と隣り合うAD変換器60'とに供給しうる。つまり、スイッチング回路550は、第2モードおよび第3モードにおいて、デマルチプレクサとして機能する。第2モードおよび第3モードにおいて、データ処理部90は、同一のサンプルホールド回路50から信号が供給された2つのAD変換器60、60'の出力を平均化する回路を有しうる。これにより、複数のサンプルホールド部50の全体の消費電力を低下させつつ、平均化によるノイズ化を図ることができる。

40

## 【0053】

第1状態に維持されるサンプルホールド回路50の個数と第2状態に維持されるサンプルホールド回路50の個数との比率は、1:1である必要はなく、例えば、1:2、または、1:3等でもよい。スイッチング回路550は、第2および第3モードにおいて、通

50

常動作状態に維持されるサンプルホールド回路 50 の出力をそのサンプルホールド回路 50 と同一列の A/D 変換器 60 と他の少なくとも 1 つの列の A/D 変換器 60' とに供給するように構成されうる。換言すると、スイッチング回路 550 は、サンプルホールド部 50 の出力を少なくとも 2 つの A/D 変換器 60 に提供するように構成されうる。

#### 【0054】

スイッチング回路 550 は、第 1 読出回路のサンプルホールド部 50 に割り当てられたスイッチ 580、590 と、第 2 読出回路のサンプルホールド部 50' に割り当てられたスイッチ 580'、590' とを含みうる。第 1 モードでは、スイッチ 580、580' がオンされ、第 2 モードでは、スイッチ 580、590 がオンされ、第 3 モードでは、スイッチ 580'、590' がオンされうる。

10

#### 【0055】

A/D 変換器 60 は、型 A/D 変換器であってもよいが、他の形式の A/D 変換器であってもよい。一例として、図 11 には、A/D 変換器 60 がシングルスロープ型 A/D 変換器で構成された例が示されている。各 A/D 変換器 60 は、比較器 600 と、メモリ 620 とを組みうる。各 A/D 変換器 60 の比較器 600 には、複数の A/D 変換器 60 に対して共通に設けられたランプ信号発生器 610 からランプ信号が供給されうる。各 A/D 変換器 60 の比較器 600 は、スイッチング回路 550 から供給される信号（ノイズレベル、光信号レベル）とランプ信号とを比較し、比較結果を出力しうる。各 A/D 変換器 60 のメモリ 620 には、複数の A/D 変換器 60 に対して共通に設けられたカウンタ 630 からカウント値が供給され、メモリ 620 は、比較器 600 からの比較結果が反転したことに応じてカウント値をラッチしうる。比較器 60 は、オートゼロ動作用の容量やスイッチを有してもよい。

20

#### 【0056】

第 2 モードでは、例えば、サンプルホールド部 50' が第 2 状態にされ、スイッチ 580、590 がオンされ、スイッチ 580'、590' がオフされる。そして、A/D 変換器 60、60' でサンプルホールド部 50 から時分割で供給されるノイズレベル、光信号レベルが A/D 変換なされる。データ処理部 90 は、A/D 変換器 60 から出力されるノイズレベルと光信号レベルとの差分を演算する CDS 处理、および、A/D 変換器 60' から出力されるノイズレベルと光信号レベルとの差分を演算する CDS 处理を実行する回路を含みうる。また、データ処理部 90 は、A/D 変換器 60 からの信号の CDS 处理の結果と A/D 変換器 60' からの信号の CDS 处理の結果とを平均化する回路を含みうる。

30

#### 【0057】

第 1 実施形態は、読出回路 RC を構成するサンプルホールド部 50 および A/D 変換器 60 の双方が第 1 制御信号または第 2 制御信号で制御される例である。第 2、第 3 実施形態は、読出回路 RC を構成するサンプルホールド部 50 および A/D 変換器 60 のうちサンプルホールド部 50 が第 1 制御信号または第 2 制御信号で制御される例である。第 1 制御信号は、第 1 グループを構成する複数の第 1 読出回路 RC の少なくとも一部を制御する信号として理解することができ、第 2 制御信号は、第 1 グループを構成する複数の第 2 読出回路 RC の少なくとも一部を制御する信号として理解することができる。

40

#### 【0058】

光電変換装置 ISD の構成は、上記の例に限定されない。例えば、画素 10 は、フローティングディフュージョンの容量を変更可能に構成されてもよい。このような機能を有する画素を採用する場合、フレーム毎にフローティングディフュージョンの容量を変更してもよいし、各行の読出期間中にフローティングディフュージョンの容量を変更してもよい。また、画素 10 は、複数の光電変換素子でフローティングディフュージョンを共有する構造を有しもよい。また、複数の光電変換素子は、マイクロレンズを共有してもよい。第 2 モードおよび第 3 モードは、1 つのマイクロレンズを共有する 2 つの光電変換素子のそれぞれの信号を低消費電力、低ノイズで読み出すために有利である。1 つのマイクロレンズを共有する 2 つの光電変換素子の出力、デフォーカス量あるいは位相差を検出するためには、1 つの画素列に複数の垂直信号線が設けられる場合、1 つの画素に

50

複数の選択トランジスタが設けられてもよい。

【0059】

以下、上記の各実施形態の光電変換装置を用いた光電変換システムの一例を説明する。

【0060】

図12は、本実施形態に係る光電変換システム1200の構成を示すブロック図である。本実施形態の光電変換システム1200は、光電変換装置1215を含む。ここで、光電変換装置1215は、上述の実施形態で述べた光電変換装置ISDである。光電変換システム1200は、例えば、撮像システムとして用いることができる。撮像システムの具体例としては、デジタルスチルカメラ、デジタルカムコーダー、監視カメラ等が挙げられる。図12では、光電変換システム1200としてデジタルスチルカメラの例を示している。

10

【0061】

図12に示す光電変換システム1200は、光電変換装置1215、被写体の光学像を光電変換装置1215に結像させるレンズ1213、レンズ1213を通過する光量を可変にするための絞り1214、レンズ1213の保護のためのバリア1212を有する。レンズ1213および絞り1214は、光電変換装置1215に光を集光する光学系である。

【0062】

光電変換システム1200は、光電変換装置1215から出力される出力信号の処理を行う信号処理部1216を有する。信号処理部1216は、必要に応じて入力信号に対して各種の補正、圧縮を行って出力する信号処理の動作を行う。光電変換システム1200は、更に、画像データを一時的に記憶するためのバッファメモリ部1206、外部コンピュータ等と通信するための外部インターフェース部（外部I/F部）1209を有する。更に光電変換システム1200は、撮像データの記録または読み出しを行うための半導体メモリ等の記録媒体1211、記録媒体1211に記録または読み出しを行うための記録媒体制御インターフェース部（記録媒体制御I/F部）1210を有する。記録媒体1211は、光電変換システム1200に内蔵されてもよく、着脱可能であってもよい。また、記録媒体制御I/F部1210から記録媒体1211との通信や外部I/F部1209からの通信は無線によってなされてもよい。

20

【0063】

更に光電変換システム1200は、各種演算を行うとともにデジタルスチルカメラ全体を制御する全体制御・演算部1208、光電変換装置1215と信号処理部1216に各種タイミング信号を出力するタイミング発生部1217を有する。ここで、タイミング信号などは外部から入力されてもよく、光電変換システム1200は、少なくとも光電変換装置1215と、光電変換装置1215から出力された出力信号を処理する信号処理部1216とを有すればよい。第4の実施形態にて説明したようにタイミング発生部1217は光電変換装置に搭載されてもよい。全体制御・演算部1208およびタイミング発生部1217は、光電変換装置1215の制御機能の一部または全部を実施するように構成してもよい。

30

【0064】

光電変換装置1215は、画像用信号を信号処理部1216に出力する。信号処理部1216は、光電変換装置1215から出力される画像用信号に対して所定の信号処理を実施し、画像データを出力する。また、信号処理部1216は、画像用信号を用いて、画像を生成する。また、信号処理部1216は、光電変換装置1215から出力される信号に対して測距演算を行ってもよい。なお、信号処理部1216やタイミング発生部1217は、光電変換装置に搭載されてもよい。つまり、信号処理部1216やタイミング発生部1217は、画素が配された基板に設けられていてもよいし、別の基板に設けられている構成であってもよい。上述した各実施形態の光電変換装置を用いて撮像システムを構成することにより、より良質の画像が取得可能な撮像システムを実現することができる。

40

【0065】

50

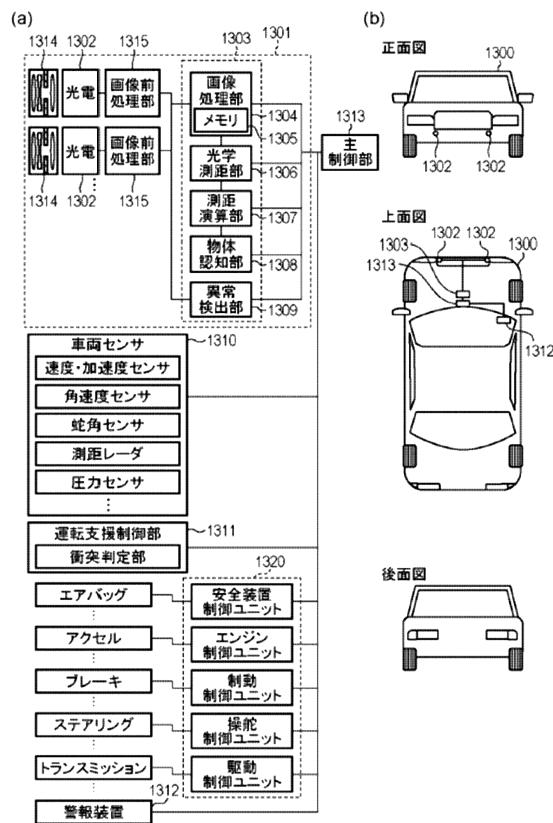

本実施形態の光電変換システムおよび移動体について、図13を用いて説明する。図13は、車両システムとこれに搭載される撮像を行う光電変換システムの一例を示したものである。光電変換システム1301は、光電変換装置1302、画像前処理部1315、集積回路1303、光学系1314を含む。光学系1314は、光電変換装置1302に被写体の光学像を結像する。光電変換装置1302は、光学系1314により結像された被写体の光学像を電気信号に変換する。光電変換装置1302は、上述の光電変換装置1302である。画像前処理部1315は、光電変換装置1302から出力された信号に対して所定の信号処理を行う。画像前処理部1315の機能は、光電変換装置1302内に組み込まれていてもよい。光電変換システム1301には、光学系1314、光電変換装置1302および画像前処理部1315が、少なくとも2組設けられており、各組の画像前処理部1315からの出力が集積回路1303に入力されるようになっている。

10

#### 【0066】

集積回路1303は、撮像システム用途向けの集積回路であり、メモリ1305を含む画像処理部1304、光学測距部1306、測距演算部1307、物体認知部1308、異常検出部1309を含む。画像処理部1304は、画像前処理部1315の出力信号に対して、現像処理や欠陥補正等の画像処理を行う。メモリ1305は、撮像画像の一次記憶、撮像画素の欠陥位置を格納する。光学測距部1306は、被写体の合焦や、測距を行う。測距演算部1307は、複数の光電変換装置1302により取得された複数の画像データから測距情報の算出を行う。物体認知部1308は、車、道、標識、人等の被写体の認知を行う。異常検出部1309は、光電変換装置1302の異常を検出すると、主制御部1313に異常を発報する。

20

#### 【0067】

集積回路1303は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよいし、これらの組合せによって実現されてもよい。また、FPGA(Field Programmable Gate Array)やASIC(Application Specific Integrated Circuit)等によって実現されてもよいし、これらの組合せによって実現されてもよい。

30

#### 【0068】

主制御部1313は、光電変換システム1301、車両センサ1310、制御ユニット1320等の動作を統括・制御する。主制御部1313を持たず、光電変換システム1301、車両センサ1310、制御ユニット1320が個別に通信インターフェースを有して、それぞれが通信ネットワークを介して制御信号の送受を行う(例えばCAN規格)方法も取り得る。

40

#### 【0069】

集積回路1303は、主制御部1313からの制御信号を受け或いは自身の制御部によって、光電変換装置1302へ制御信号や設定値を送信する機能を有する。

#### 【0070】

光電変換システム1301は、車両センサ1310に接続されており、車速、ヨーレート、舵角などの自車両走行状態および自車外環境や他車・障害物の状態を検出することができる。車両センサ1310は、対象物までの距離情報を取得する距離情報取得手段である。また、光電変換システム1301は、自動操舵、自動巡航、衝突防止機能等の種々の運転支援を行う運転支援制御部1311に接続されている。特に、衝突判定機能に関しては、光電変換システム1301や車両センサ1310の検出結果を基に他車・障害物との衝突推定・衝突有無を判定する。これにより、衝突が推定される場合の回避制御、衝突時の安全装置起動を行う。

#### 【0071】

また、光電変換システム1301は、衝突判定部での判定結果に基づいて、ドライバーに警報を発する警報装置1312にも接続されている。例えば、衝突判定部の判定結果として衝突可能性が高い場合、主制御部1313は、ブレーキをかける、アクセルを戻す、

50

エンジン出力を抑制するなどして、衝突を回避、被害を軽減する車両制御を行う。警報装置 1312 は、音等の警報を鳴らす、カーナビゲーションシステムやメーターパネルなどの表示部画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

【0072】

発明は上記実施形態に制限されるものではなく、発明の精神及び範囲から離脱することなく、様々な変更及び変形が可能である。従って、発明の範囲を公にするために請求項を添付する。

【符号の説明】

【0073】

I S D : 光電変換装置、5 : 画素アレイ、R U : 読出部、R C : 読出回路、5 : サンプルホールド部、210 : 第1サンプルホールド回路、211 : 第2サンプルホールド回路、p w r 1、a p w r 1 : 第1制御線、第1制御信号、p w r 2、a p w r 2 : 第2制御線、第2制御信号

【図面】

【図1】

【図2】

ISD

40

50

【図3】

【図7】

【図8】

【図9】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】