(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6211850号 (P6211850)

(45) 発行日 平成29年10月11日(2017.10.11)

(24) 登録日 平成29年9月22日(2017.9.22)

(51) Int.Cl. F 1

HO1L

29/786

(2006.01)

HO1L

29/78

618E

GO2F

1/1368

(2006.01)

HO1L

29/78

618B

HO1L

29/78

618G

GO2F 1/1368

請求項の数 5 (全 36 頁)

(21) 出願番号 特願2013-163834 (P2013-163834)

(22) 出願日 平成25年8月7日 (2013.8.7) (65) 公開番号 特開2014-57055 (P2014-57055A)

(43) 公開日 平成26年3月27日 (2014.3.27) 審査請求日 平成28年8月5日 (2016.8.5) (31) 優先権主張番号 特願2012-178723 (P2012-178723)

(32) 優先日 平成24年8月10日 (2012.8.10)

(33) 優先権主張国 日本国(JP)

||(73)特許権者 000153878

株式会社半導体エネルギー研究所神奈川県厚木市長谷398番地

||(72)発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 市川 武宜

最終頁に続く

### (54) 【発明の名称】半導体装置

### (57)【特許請求の範囲】

### 【請求項1】

第1の酸化物半導体膜と、

前記第1の酸化物半導体膜上方の第2の酸化物半導体膜と、

前記第2の酸化物半導体膜上方の第3の酸化物半導体膜と、を有し、

前記第2の酸化物半導体膜は、結晶構造を有し、

前記第2の酸化物半導体膜の伝導帯下端は、前記第1の酸化物半導体膜の伝導帯下端に 比べて真空準位から深く、

前記第2の酸化物半導体膜の伝導帯下端は、前記第3の酸化物半導体膜の伝導帯下端に 比べて真空準位から深く、

前記第2の酸化物半導体膜は、局在準位による吸収係数が3×10<sup>3</sup>/cm以下であることを特徴とする半導体装置。

### 【請求項2】

第1の窒化絶縁膜と、

前記第1の窒化絶縁膜上方の第1の酸化物半導体膜と、

前記第1の酸化物半導体膜上方の第2の酸化物半導体膜と、

前記第2の酸化物半導体膜上方の第3の酸化物半導体膜と、を有し、

前記第2の酸化物半導体膜は、結晶構造を有し、

前記第2の酸化物半導体膜の伝導帯下端は、前記第1の酸化物半導体膜の伝導帯下端に 比べて真空準位から深く、

前記第2の酸化物半導体膜の伝導帯下端は、前記第3の酸化物半導体膜の伝導帯下端に 比べて真空準位から深く、

前記第2の酸化物半導体膜は、局在準位による吸収係数が3×10<sup>3</sup>/cm以下であることを特徴とする半導体装置。

### 【請求項3】

請求項1または請求項2において、

前記第1の酸化物半導体膜及び前記第3の酸化物半導体膜に含まれるSiの濃度は、 $3 \times 10^{-18}$  /  $cm^3$  以下であり、

前記第1の酸化物半導体膜及び前記第3の酸化物半導体膜に含まれる炭素の濃度は、3 × 10 <sup>18</sup> / c m <sup>3</sup> 以下であることを特徴とする半導体装置。

10

20

### 【請求項4】

請求項1乃至3のいずれか一において、

前記第3の酸化物半導体膜は、前記第2の酸化物半導体膜よりも結晶化度が低いことを 特徴とする半導体装置。

### 【請求項5】

請求項1乃至4のいずれか一において、

前記第1の酸化物半導体膜は、前記第2の酸化物半導体膜よりも結晶化度が低いことを 特徴とする半導体装置。

【発明の詳細な説明】

#### 【技術分野】

[00001]

酸化物半導体を用いる半導体装置及びその作製方法に関する。

[00002]

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

### 【背景技術】

[0003]

近年、半導体装置の開発が進められ、CPUやメモリが主に用いられている。CPUは、半導体ウェハから切り離された半導体集積回路(少なくともトランジスタ及びメモリ)を有し、接続端子である電極が形成された半導体素子の集合体である。

30

### [0004]

CPUやメモリなどの半導体回路(ICチップ)は、回路基板、例えばプリント配線板に 実装され、様々な電子機器の部品の一つとして用いられる。

[0005]

チャネル形成領域に酸化物半導体膜を用いてトランジスタなどを作製し、表示装置に応用する技術が注目されている。例えば、酸化物半導体膜として酸化亜鉛(ZnO)を用いるトランジスタが挙げられる。

[0006]

酸化物半導体膜を用いたトランジスタを、透光性を有する基板上に形成し、画像表示装置のスイッチング素子などに用いる技術が特許文献1及び特許文献2で開示されている。

40

#### [0007]

また、単結晶基板上に酸化物半導体を用いたトランジスタを有する半導体装置が特許文献 3に開示されている。

【先行技術文献】

## 【特許文献】

[0008]

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

【特許文献3】特開2011-109079号公報

【発明の概要】

#### 【発明が解決しようとする課題】

#### [0009]

酸化物半導体膜を用いるトランジスタは、酸化物半導体膜と接する絶縁膜の影響、即ち、 酸化物半導体膜と絶縁膜の界面状態により電気特性が左右される。

#### [0010]

また、製造過程で酸素欠損を多く含む酸化物半導体膜を用いたトランジスタは、長期信頼性が低い。従って、できるだけ酸素欠損が少ない酸化物半導体膜を用いたトランジスタを製造することが求められる。また、成膜時または成膜後にプラズマに曝すことによる酸化物半導体膜へのダメージを低減することも求められる。

#### [0011]

このような問題に鑑み、本発明の一態様は、信頼性が高く、安定した電気特性を示す半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置を作製することを課題の一とする。

【課題を解決するための手段】

#### [0012]

2層以上の酸化物半導体膜を積層し、酸素欠損の少ない酸化物半導体膜をキャリアパスと する埋め込みチャネル型のトランジスタを作製する。

#### [0013]

具体的には、第1の酸化物半導体膜上に結晶構造を有する第2の酸化物半導体膜を積層し、第2の酸化物半導体膜上に第3の酸化物半導体膜を少なくとも含む多層構造のトランジスタを作製する。

#### [0014]

第1の酸化物半導体膜によって第2の酸化物半導体膜を下方に配置されるシリコン絶縁膜から離間し、上方に配置されるシリコン絶縁膜の成膜時または導電膜形成後のエッチング時にプラズマに曝すことによる第2の酸化物半導体膜へのダメージを第3の酸化物半導体膜によって低減する。

#### [0015]

本明細書で開示する本発明の一つは、第1の酸化物半導体膜上に結晶構造を有する第2の酸化物半導体膜と、第2の酸化物半導体膜上に第3の酸化物半導体膜とを有し、第1の酸化物半導体膜の伝導帯下端及び第3の酸化物半導体膜の伝導帯下端に比べて第2の酸化物半導体膜の伝導帯下端が真空準位から最も深くなることを特徴とする半導体装置である。

### [0016]

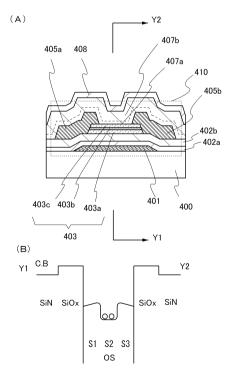

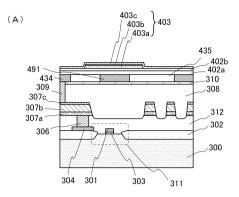

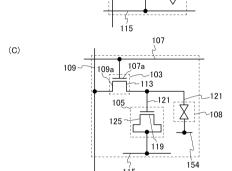

図1(A)にトランジスタの断面の一例を示しており、トランジスタ410は、絶縁表面を有する基板400上にゲート電極401、窒化シリコン膜である第1のゲート絶縁膜402a、酸化シリコン膜である第2のゲート絶縁膜402b、第1の酸化物半導体膜403a、第2の酸化物半導体膜403b、第3の酸化物半導体膜403c、ソース電極またはドレイン電極として機能する電極層405a、405bを有する。また、第3の酸化物半導体膜403c上に酸化シリコン膜である保護絶縁膜407a、407b、窒化シリコン膜である保護絶縁膜408が設けられている。

#### [0017]

結晶構造を有する第2の酸化物半導体膜は、伝導帯(コンダクションバンドとも呼ぶ)が井戸型構造(ウェル構造とも呼ぶ)を構成するように適宜材料を選択する。なお、伝導帯が井戸型構造の一例を図1(B)に示す。なお、図1(B)に示す模式図は、図1(A)中のY1-Y2断面におけるエネルギーバンド図であり、窒化シリコン膜で挟まれた酸化物半導体膜の積層部分のみを図示している。

### [0018]

また、第14族元素の一つであるシリコンや炭素が不純物として酸化物半導体膜に含まれてしまうとドナーを作って酸化物半導体膜がn型化するため、第1の酸化物半導体膜及び第3の酸化物半導体膜に含まれるSiの濃度(二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)により得られる濃度)は

10

20

30

40

$3 \times 10^{-1}$  <sup>8</sup> / c m <sup>3</sup> 以下、好ましくは  $3 \times 10^{-1}$  <sup>7</sup> / c m <sup>3</sup> 以下とする。また、第 1 の酸化物半導体膜及び第 3 の酸化物半導体膜に含まれる炭素濃度は  $3 \times 10^{-1}$  <sup>8</sup> / c m <sup>3</sup> 以下、好ましくは  $3 \times 10^{-1}$  <sup>7</sup> / c m <sup>3</sup> 以下とする。特に第 2 の酸化物半導体膜に第 1 4 族元素などの不純物が多く混入しないように、第 1 の酸化物半導体膜及び第 3 の酸化物半導体膜を挟む、または囲む構成とすることが好ましい。即 5、第 1 の酸化物半導体膜及び第 3 の酸化物半導体膜は、シリコンなどの第 1 4 族元素が第 2 の酸化物半導体膜に混入することを防ぐバリア層とも呼べる。バリア層が上下に配置されるため、勿論、第 2 の酸化物半導体膜には、第 1 4 族元素などの不純物がほとんど含まれず、例えば  $5 \times 10^{-1}$  <sup>8</sup> / c m <sup>3</sup> 以下、好ましくは  $3 \times 10^{-1}$  <sup>7</sup> / c m <sup>3</sup> 以下であり、炭素の濃度は  $3 \times 10^{-1}$  <sup>8</sup> / c m <sup>3</sup> 以下、好ましくは  $3 \times 10^{-1}$  <sup>7</sup> / c m <sup>3</sup> 以下である。

[0019]

このような積層構造とすることで第2の酸化物半導体膜がキャリアパスとなり、酸素欠損の含有量が低い領域をキャリアが走行する。キャリアが、酸化物半導体膜の積層の下方または上方に配置されるシリコン絶縁膜から離間された領域を流れる構造となるため、酸素欠損の影響を低減することができる。

[0020]

また、水素や水分が不純物として酸化物半導体膜の積層に含まれてしまうとドナーを作り n型化するため、酸化物半導体膜の積層の上方または下方に水素や水分が外部から侵入す ることを防止する保護膜(窒化絶縁膜、代表的には窒化シリコン膜など)を設けることは 、井戸型構造を実現する上で有用である。

【0021】

本明細書で開示する他の発明の一つは、第1の窒化絶縁膜上に第1の酸化物半導体膜上に結晶構造を有する第2の酸化物半導体膜と、第2の酸化物半導体膜上に第3の酸化物半導体膜と、第3の酸化物半導体膜上に第2の窒化絶縁膜と、を有し、第1の酸化物半導体膜の伝導帯下端及び第3の酸化物半導体膜の伝導帯下端に比べて第2の酸化物半導体膜の伝導帯下端が真空準位から最も深くなることを特徴とする半導体装置である。第1の窒化絶縁膜及び第2の窒化絶縁膜を設けることで高い信頼性を実現することができる。

[0022]

また、多層構造を構成する各酸化物半導体膜は、少なくともインジウム(In)を1×1 $0^{-1}$  9 / c m  $^3$  以上含み、ACスパッタリング法またはDCスパッタリング法で成膜することのできるスパッタリングターゲットを用いて成膜する。スパッタリングターゲットにインジウムを含ませることで導電性が高まるため、ACスパッタリング法またはDCスパッタリング法で成膜することを容易なものとする。第1の酸化物半導体膜及び第3の酸化物半導体膜を構成する材料は、InM1 $_{\times}$  Z n  $_{\times}$  O  $_{z}$  (X 1、Y > 1、Z > 0、M 1 = G a、H f 等の金属元素)で表記できる材料を用いる。ただし、第1の酸化物半導体膜及び第3の酸化物半導体膜を構成する材料にG a を含ませる場合、含ませる G a の割合が多い、具体的には I n M 1  $_{\times}$  Z n  $_{\times}$  O  $_{z}$  で表記できる材料でX = 1 0 を超えると成膜時に粉が発生する恐れがあり、ACスパッタリング法またはDCスパッタリング法で成膜することが困難となり、不適である。

[ 0 0 2 3 ]

[0024]

第1の酸化物半導体膜の伝導帯下端及び第3の酸化物半導体膜の伝導帯下端に比べて第2の酸化物半導体膜の伝導帯下端が真空準位から最も深くなるような井戸型構造を構成するように、第1、第2、及び第3の酸化物半導体膜の材料を適宜選択する。具体的には、第2の酸化物半導体膜は、第1の酸化物半導体膜及び第3の酸化物半導体膜よりもインジウ

10

20

30

40

20

30

40

50

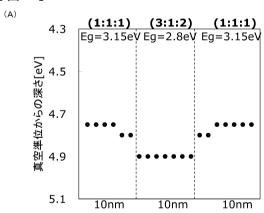

ムの含有量が多い材料を用いる。第1、第2、及び第3の酸化物半導体膜中のインジウムやガリウムなどの含有量は、飛行時間型二次イオン質量分析法(TOF-SIMSともいう)や、X線電子分光法(XPSともいう)で比較できる。なお、酸化物半導体のイオン化ポテンシャルは紫外線光電子分光分析(UPS:U1traviolet Photoelectron Spectroscopy)等で測定することができる。代表的なUPSの測定装置としてはVersaProbe(ULVAC-PHI社製)を用いる。また、電子親和力とは、真空準位(E )から伝導帯端(Ec)までのエネルギー差である。また、エネルギーバンドギャップ(Eg)は、全自動分光エリプソメーターUT-300を用いて測定することができる。イオン化ポテンシャルの値からエネルギーバンドギャップを差し引くことで伝導帯のエネルギーを算出し、単層または積層のバンド構造を作成することができる。この手法により、本明細書において開示する積層構造を用いることで埋め込みチャネルが形成されていることを確認することができる。図2(A)及び図2(B)にその一例を示す。

[0025]

図2(A)は、In:Ga:Zn=1:1:1 [原子数比]の組成を有するIn・Ga・Zn酸化物のスパッタリングターゲットを用いて酸素100%雰囲気下で膜厚10nm成膜した後、In:Ga:Zn=3:1:2 [原子数比]の組成を有するIn・Ga・Zn酸化物のスパッタリングターゲットを用いてアルゴン100%雰囲気下で膜厚10nm成膜した後、In:Ga:Zn=1:1:1 [原子数比]の組成を有するIn・Ga・Zn酸化物のスパッタリングターゲットを用いて酸素100%雰囲気下で膜厚10nm成酸で積層させたサンプルを作製し、全自動分光エリプソメーターUT・300を用いて測定し、真空準位から伝導帯までのエネルギーを算出したデータであり、そのデータに基づいて作成したバンド構造を図2(B)に示す。図2(B)では、第1の酸化物半導体膜の伝導帯下端及び第3の酸化物半導体膜の伝導帯下端に比べて第2の酸化物半導体膜の伝導帯下端方空準位から最も深くなるような井戸型構造を構成していることがわかる。

[0026]

また、第1の酸化物半導体膜上に結晶構造を有する第2の酸化物半導体膜を積層するため、結晶構造の異なるヘテロ構造と呼ぶことができる。

[0027]

トランジスタの半導体膜となる酸化物半導体膜を上記積層構成とすることにより、チャネルが形成される領域、少なくとも第 2 の酸化物半導体膜は、一定電流測定法(CPM:Constant Photocurrent Method)により測定された局在準位による吸収係数を  $3\times10^{-3}$  / cm 以下)とすることができる。

[0028]

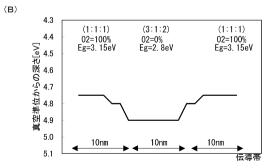

また、上記積層構成では、第1、第2、及び第3の酸化物半導体膜を用いて一つの井戸型構造を形成する構成例を示したが、特に限定されず、第2の酸化物半導体膜を多層として複数の井戸型構造を構成してもよく、その一例を図3に示す。

[0029]

第1、第2、及び第3の酸化物半導体膜としては、CAAC-OS(C A×is Aligned Crystalline O×ide Semiconductor)膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜などを用いる。なお、、第2の酸化物半導体膜は、CAAC-OS膜であることが好ましい。本明細書等において、CAAC-OS膜とは、c軸が酸化物半導体膜の表面に概略垂直である結晶を含む酸化物半導体膜をいう。CAAC-OS膜に対し、X線回折(XRD:X-Ray Diffraction)装置を用いて構造解析を行うと、例えばInGaZnO4の結晶を有するCAAC-OS膜のout-of-plane法による解析では、回折角(2)が31°近傍にピークが現れる場合がある。このピークは、InGaZnO4の結晶の(009)面に帰属されることから、CAAC-OS膜の結晶が c軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

#### [0030]

CAAC-OS層は、完全な単結晶ではなく、完全な非晶質でもない。CAAC-OS膜 は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が1 00mm未満の立方体内に収まる大きさである。従って、CAAC - OS膜に含まれる結 晶部は、一辺が10nm未満、5nm未満または3nm未満の立方体内に収まる大きさの 場合も含まれる。CAAC-OS膜を透過型電子顕微鏡(TEM:Transmissi on Electron Microscope)によって観察すると、明確な結晶部同 士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない 。そのため、CAAC・OS膜は、結晶粒界に起因する電子移動度の低下が起こりにくい といえる。

### [0031]

CAAC-OS膜に含まれる結晶は、c軸がCAAC-OS膜の被形成面の法線ベクトル または表面の法線ベクトルに平行な方向に揃っている。なお、異なる結晶間で、それぞれ a軸及びb軸の向きが異なっていてもよい。本明細書等において、単に垂直と記載する場 合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合 、 - 5 °以上5 °以下の範囲も含まれることとする。

[0032]

なお、CAAC-OS層において、結晶部の分布が一様でなくてもよい。例えば、CAA C-OS層の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形 成面の近傍に対し表面の近傍では結晶部の占める割合が高くなる、即ち結晶化度が高くな ることがある。また、CAAC-OS層にも酸素を添加されることにより、当該元素や酸 素の添加領域において結晶化度が低下することもある。

20

10

#### [0033]

CAAC-OS膜に含まれる結晶のc軸は、CAAC-OS膜の被形成面の法線ベクトル または表面の法線ベクトルに平行な方向に揃うため、CAAC-OS膜の形状(被形成面 の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお 、結晶部のc軸の方向は、CAAC-OS膜が形成されたときの被形成面の法線ベクトル または表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または 成膜後に加熱処理などの結晶化処理を行うことにより形成される。

[0034]

30

40

50

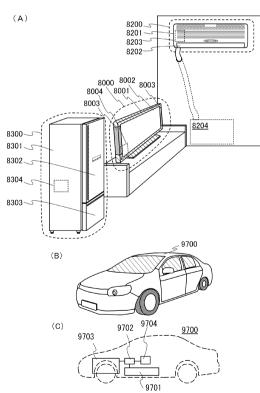

CAAC-OS膜は、スパッタリングターゲットを用いて形成する。ここで、c軸が上面 の法線ベクトルに平行である結晶領域を有する酸化物半導体からなるスパッタリングター ゲットの作製方法について説明する(図14参照)。

[0035]

まず、スパッタリングターゲットの原料を秤量する(ステップS101)。

[0036]

ここでは、スパッタリングターゲットの原料として、 InO、原料(Inの原料)、 Ga  $O_{\gamma}$  原料(Gaの原料)、及び、 $ZnO_{Z}$  原料(Znの原料)を用意する。なお、X、YおよびZは任意の正数であり、例えばXは1.5、Yは1.5、Zは1とすればよい。も ちろん、上記の原料は一例であり、所望の化合物を得るために適宜原料を選択すればよい 。例えば、GaO、原料に代えて、MO、原料を用いてもよい。なお、Mは、Sn、Hf またはA1とすればよい。または、Mは、ランタノイドであるLa、Ce、Pr、Nd、 Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、YbまたはLuとしてもよい。本実 施の形態では三種の原料を用いた例を示すが、これに限定されない。例えば、本実施の形 態を四種以上の原料を用いた場合に適用しても構わないし、一種または二種の原料を用い た場合に適用しても構わない。

[0037]

次に、InO $_{\rm X}$ 原料、GaO $_{\rm Y}$ 原料およびZnO $_{\rm Z}$ 原料を所定の比率で混合する。

[0038]

所定の比率としては、例えば、InO $_{x}$ 原料、GaO $_{y}$ 原料およびZnO $_{z}$ 原料が、2:

20

30

40

50

(7)

2:1、8:4:3、3:1:1、1:1:1、1:3:2、4:2:3、1:1:2、3:1:4または3:1:2のmol数比とする。このような比率を有する混合材料を用いることで、c軸が上面の法線ベクトルに平行である結晶領域を有する酸化物半導体からなるスパッタリング用ターゲットを得やすくなる。

#### [0039]

より具体的には、 In:Ga:Zn=1:1:1 [原子数比]の組成を有する In-Ga:Zn 酸化物のスパッタリングターゲットを作製する場合は、  $In_2O_3:Ga_2O_3:ZnO=1:1:2$  [mol数比]となるように、それぞれの原料を秤量する。

#### [0040]

なお、 $GaO_{\gamma}$ 原料に代えて、 $MO_{\gamma}$ 原料を用いた場合も、 $InO_{\chi}$ 原料、 $MO_{\gamma}$ 原料およびZnOZ原料は、2:2:1、8:4:3、3:1:1、1:1:1、1:3:2、4:2:3、1:1:2、3:1:4または3:1:2の $mol_{\chi}$ 0

#### [0041]

まず湿式方式によるスパッタリングターゲットの作製方法について述べる。スパッタリングターゲットの原料を秤量後、原料をボールミル等で粉砕及び混合して化合物粉末を作製する。複数の原料を混合した後、第1の焼成を行うことで結晶性酸化物を生成し、結晶性酸化物を粉砕することで化合物粉末とする。化合物粉末の粒径を0.01μm以上1μm以下、好ましくは0.01μm以上0.5μm以下、さらに好ましくは0.01μm以上0.3μm以下とする。さらに、当該化合物粉末に、イオン交換水、有機添加物等を混合してスラリーを作製する(ステップS111)。

#### [0042]

次いで、水分を透過するフィルタが敷かれた型にスラリーを流し込んで、水分を除去する。当該型は、金属製または酸化物製を用いればよく、矩形または丸形の上面形状を有する。また当該型は、底部に1つ又は複数の穴が設けられた構造を有すればよい。該穴を複数設けると、スラリーの水分を速やかに除去することができる。当該フィルタは、多孔性樹脂、布等を用いればよい。

#### [0043]

スラリー中の水分の除去は、スラリーが流し込まれた型の底部に設けられている穴からの減圧排水により行われる。次いで、減圧排水により水分を除去されたスラリーをさらに自然乾燥させる。これにより、水分が除去されたスラリーは、型の内部の形状に成形される(ステップS113)。

# [0044]

次いで、得られた成形体を、酸素( $O_2$ )雰囲気中1400 で第2の焼成を行う(ステップS114)。以上により、湿式方式によりスパッタリングターゲットを得ることができる。

#### [0045]

次いで乾式方式によるスパッタリングターゲットの作製方法について述べる。スパッタリングターゲットの原料を秤量後、原料をボールミル等で粉砕及び混合して化合物粉末を作製する(ステップS121)。

### [0046]

得られた化合粉末を型に敷き詰め、プレス装置にて加圧することにより、当該原料粉を成形し成形体を得る(ステップS122)。

### [0047]

得られた成形体を電気炉等の加熱装置内に設置し、酸素( $O_2$ )雰囲気中1400 で焼成する(ステップS123)。なお本実施の形態では、ステップS122及びステップS123のように、成形工程及び焼成工程が分かれている方式を、コールドプレス方式と呼ぶこととする。コールドプレス方式に対して、成形工程及び焼成工程を同時に行うホットプレス方式について、以下に説明する。

### [0048]

まず上述したステップS121までの工程を行う。得られた化合物粉末を型に敷き詰め、

当該型をアルゴン(Ar)雰囲気中1000 で加熱しながら、型内部に設けられた化合物粉末をプレス装置により加圧する。このように、化合物粉末を焼成しながら加圧することにより、当該化合物粉末を成形し成形体を得ることができる(ステップS125)。

#### [0049]

ここで I n G a Z n O  $_4$  を含むスパッタリングターゲットを使用する方法について説明する。

#### [0050]

In Ga Zn O4を含むスパッタリングターゲットを使用して CAAC OS膜の成膜が行われる様子を以下に詳細に説明する。まず、スパッタリング用ターゲットにイオンが衝突し、結晶性を有するスパッタリング粒子が剥離する。スパッタリング粒子に含まれる結晶粒は、スパッタリング用ターゲットの表面と平行な劈開面を有する。また、結晶粒は、原子間の結合の弱い部分を有する。結晶粒にイオンが衝突した際に、原子間の結合の弱い部分の原子間結合が切れる。従って、スパッタリング粒子は、劈開面および原子間の結合の弱い部分によって切断され、平板状で剥離する。

#### [0051]

または、結晶粒の一部が劈開面から粒子として剥離し、プラズマに曝されることで原子間 の結合の弱い部分から結合が切れ、複数のスパッタリング粒子が生成される。

#### [0052]

イオンとして酸素の陽イオンを用いることで、成膜時のプラズマダメージを軽減することができる。従って、イオンがスパッタリング用ターゲットの表面に衝突した際に、スパッタリング用ターゲットの結晶化度が低下することを抑制できる。

#### [0053]

スパッタリング粒子は、正に帯電させることが好ましい。スパッタリング粒子が、正に帯電するタイミングは特に問わないが、具体的にはイオンの衝突時に電荷を受け取ることで正に帯電させればよい。または、プラズマが生じている場合、スパッタリング粒子をプラズマに曝すことで正に帯電させればよい。または、酸素の陽イオンであるイオンをスパッタリング粒子の側面、上面または下面に結合させることで正に帯電させればよい。

#### [0054]

次に、スパッタリング粒子の被成膜面に堆積する様子を詳細に説明する。

### [0055]

成膜中において、被成膜面はスパッタリング粒子が数層堆積した表面を有する。スパッタリング粒子が正に帯電していることで、スパッタリング粒子は被成膜面において、他のスパッタリング粒子の堆積していない領域に堆積していく。これは、スパッタリング粒子が正に帯電していることにより、スパッタリング粒子同士が互いに反発し合うためである。

### [0056]

このようにして堆積したスパッタリング粒子は、被成膜面に垂直な方向に結晶の c 軸が揃っており、酸化物膜は、 C A A C - O S 膜となる。

### [0057]

また、CAAC-OS膜を形成するには、成膜時の基板温度を上げることが好ましく、200以上550以下とする。なお、CAAC-OS膜は、酸素を多く含み、酸素欠損が低減された膜となる。

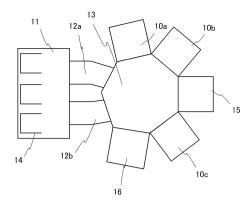

#### [0058]

また、図1(A)に示す埋め込みチャネルを形成する3層の酸化物半導体膜は、順次積層する工程を大気に触れることなく連続的に行う場合、図11に上面図を示す製造装置を用いればよい。

### [0059]

図11に示す製造装置は、枚葉式マルチチャンバー設備であり、3つのスパッタ装置10a、10b、10cや、被処理基板を収容するカセットポート14を3つ有する基板供給室11や、ロードロック室12a、12bや、搬送室13や、基板加熱室15、16などを有している。なお、基板供給室11及び搬送室13には、被処理基板を搬送するための

10

20

30

40

搬送ロボットがそれぞれ配置されている。スパッタ装置10a、10b、10c、搬送室 13、及び基板加熱室15、16は、水素及び水分をほとんど含まない雰囲気(不活性雰 囲気、減圧雰囲気、乾燥空気雰囲気など)下に制御することが好ましく、例えば、水分に ついては露点 - 40 以下、好ましくは露点 - 50 以下の乾燥窒素雰囲気とする。図 1 1の製造装置を用いた作製工程の手順の一例は、まず、基板供給室11から被処理基板を 搬送し、ロードロック室12aと搬送室13を経て基板加熱室15に移動させ、基板加熱 室15で被処理基板に付着している水分を真空ベークなどで除去し、その後、搬送室13 を経てスパッタ装置10cに被処理基板を移動させ、スパッタ装置10c内で1層目の酸 化物半導体膜S1を成膜する。そして、大気に触れることなく、搬送室13を経てスパッ 夕装置 1 0 a に被処理基板を移動させ、スパッタ装置 1 0 a 内で 2 層目の酸化物半導体膜 S 2 を成膜する。そして、大気に触れることなく、搬送室 1 3 を経てスパッタ装置 1 0 b に被処理基板を移動させ、スパッタ装置10b内で3層目の酸化物半導体膜S3を成膜す る。必要であれば、大気に触れることなく、搬送室13を経て基板加熱室16に被処理基 板を移動させ、加熱処理を行う。このように、図11の製造装置を用いることによって大 気に触れることなく、作製プロセスを進めることができる。また、図11の製造装置のス パッタ装置は、スパッタリングターゲットを変更することで大気に触れることのないプロ セスを実現できる。また、図11の製造装置のスパッタ装置は、平行平板型スパッタリン グ装置、イオンビームスパッタリング装置、または対向ターゲット式スパッタリング装置 などを用いればよい。対向ターゲット式スパッタリング装置は、被成膜面がプラズマから 遠く、成膜ダメージが小さいため、結晶化度の高いCAAC-OS膜を形成することがで きる。

[0060]

スパッタ装置10a、10b、10cでの酸化物半導体膜の成膜において、成膜ガスとして、水素、水、水酸基又は水素化物などの不純物濃度が低い高純度ガスを用いる。

[0061]

また、基板加熱室16は、減圧下、又は窒素、酸素、超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で-55 )以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、若しくは希ガス(アルゴン、ヘリウムなど)の雰囲気下として、加熱処理を行えばよいが、上記窒素、酸素、超乾燥エア、または希ガス等の雰囲気に水、水素などが含まれないことが好ましい。また、加熱処理装置に導入する窒素、酸素、または希ガスの純度を、6N(99.99999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

[0062]

本発明の一態様に係る半導体装置は、酸化物半導体膜を用いたトランジスタ、若しくは該トランジスタを含んで構成される回路を含む。例えば、LSIや、CPUや、電源回路に搭載されるパワーデバイスや、メモリ、サイリスタ、コンバータ、イメージセンサなどを含む半導体集積回路、液晶表示パネルに代表される電気光学装置や発光素子を有する発光表示装置を部品として搭載した電子機器も半導体装置に含まれる。

【発明の効果】

[0063]

本発明の一態様によって、信頼性が高く、安定した電気特性を示す酸化物半導体を用いた 半導体装置を提供することができる。信頼性の高い半導体装置を作製できる。

【図面の簡単な説明】

[0064]

【図1】本発明の一態様を示す断面図である。

【図2】(A)は、真空準位から伝導帯までのエネルギーを算出したデータであり、(B)は、そのデータに基づいて作成したバンド構造である。

【図3】本発明の一態様を示すバンド構造の一例である。

【図4】本発明の一態様を示す工程断面図である。

10

20

30

40

30

40

50

- 【図5】本発明の一態様を示す断面図である。

- 【図6】本発明の一態様を示す回路図である。

- 【図7】本発明の一態様を示すブロック図である。

- 【図8】本発明の表示装置を説明する図、及び画素を説明する回路図である。

- 【図9】表示装置を説明する上面図である。

- 【図10】表示装置を説明する断面図である。

- 【図11】半導体装置の製造装置の一例を示す上面図である。

- 【図12】電子機器を説明する図である。

- 【図13】電子機器を説明する図である。

- 【図14】本発明のスパッタリングターゲットの作製工程を示すフローチャートを示す図 10 である。

【発明を実施するための形態】

#### [0065]

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は 以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれ ば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈さ れるものではない。

#### [0066]

### (実施の形態1)

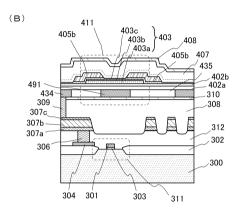

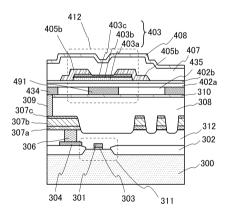

本実施の形態では、半導体装置の一形態を、図4(A)及び図4(B)を用いて説明する。本実施の形態では、下部に第1の半導体材料を用いたトランジスタ311を有し、上部に第2の半導体材料を用いたトランジスタ411を有するものである。

### [0067]

ここで、第1の半導体材料と第2の半導体材料は異なるバンドギャップを持つ材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコンなど)とし、第2の半導体材料を酸化物半導体とすることができる。シリコンなどの材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

### [0068]

半導体装置に用いる基板 3 0 0 は、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、 S O I ( S i l i c o n o n I n s u l a t o r )基板などを用いることができ、トランジスタのチャネル形成領域は、半導体基板中、又は半導体基板上に形成することができる。図 4 に示す半導体装置は、半導体基板中にチャネル形成領域を形成して下部のトランジスタを作製する例である。

#### [0069]

図4(A)及び図4(B)に示す半導体装置においては、基板300に単結晶シリコン基板を用いて、該単結晶シリコン基板にトランジスタ311を形成しており、第1の半導体材料として単結晶シリコンを用いている。トランジスタ311は、pチャネル型トランジスタである。トランジスタ311は、公知の作製方法によって作製する。また、公知の作製方法によって、トランジスタ311と同じ基板上にnチャネル型トランジスタも作製することができる。nチャネル型トランジスタとpチャネル型トランジスタを適宜組み合わせてCMOS(相補型金属酸化物半導体:Complementary Metal Oxide Semiconductor)回路を構成し、様々な回路を設けることができる。

# [0070]

トランジスタ311は、チャネル形成領域、ソース領域、ドレイン領域、ゲート絶縁膜303、ゲート電極301を有している。また、トランジスタ311を囲むように素子分離絶縁膜302上にはトランジスタ311と電気的に接続される電極層304が設けられる。

20

30

40

50

#### [0071]

電極層304及びトランジスタ311を覆って第1の層間絶縁膜312が形成され、電極層304に達する開口を第1の層間絶縁膜312に形成し、導電膜を成膜した後、研磨処理(例えば、化学的機械研磨法(Chemical Mechanical Polishing:CMP))などを用いて平坦化する。第1の層間絶縁膜312の開口には、第1の配線層306及び第1の層間絶縁膜312上に導電膜を成膜した後、マスクを用いて選択的に導電膜を除去して所望の形状の第2の配線層を形成する。本実施の形態において、第2の配線層は3層構造とし、チタン膜である第1の導電膜307a、アルミニウム膜である第2の導電膜307b、チタン膜である第3の導電膜307cの順で形成する。

[0072]

次いで、第2の配線層を覆う第2の層間絶縁膜308を形成し、バリア層310を積層する。そして、第2の配線層に達する開口を第2の層間絶縁膜308及びバリア層310に形成し、導電膜を成膜した後、CMPなどを用いて平坦化する。開口には、第3の配線層309が形成される。

[0073]

バリア層 3 1 0 は、下部のトランジスタ 3 1 1 と上部のトランジスタ 4 1 1 の間に設けられる。バリア層 3 1 0 は、トランジスタ 3 1 1 の近傍に含まれる水素などの不純物が上部のトランジスタ 4 1 1 に拡散しないように設けられている。また、バリア層 3 1 0 は、後の熱処理で放出される水素が少ない、または水素が放出されない材料膜を用いることが好ましい。よって、不純物等の遮断機能の高い、緻密な無機絶縁膜(例えば、酸化アルミニウム膜、窒化シリコン膜など)を用いることが好ましい。具体的には、バリア層 3 1 0 としてプラズマ C V D 法を用いて、シラン(S i H  $_4$  )と窒素(N  $_2$  )の混合ガスを供給して成膜する窒化シリコン膜を用いる。

[0074]

次いで、バリア層310上にトランジスタ411を作製する。

[0075]

バリア層上に導電膜を形成し、選択的にエッチングを行って第4の配線層434及びゲート電極491を形成する。

[0076]

次いで、ゲート電極 4 9 1 を覆う絶縁膜 4 3 5 を形成した後、 C M P などを用いて平坦化する。

[0077]

次いで、第1のゲート絶縁膜402aと第2のゲート絶縁膜402bを形成する。第1のゲート絶縁膜402a及び第2のゲート絶縁膜402bの膜厚は、1nm以上100nm以下とし、スパッタリング法、MBE法、CVD法、PLD法、ALD法等を適宜用いて形成することができる。第1のゲート絶縁膜402aは、窒化シリコン膜を用いる。また、第2のゲート絶縁膜402bの材料として、酸化シリコン、酸化ガリウム、酸化アルミニウム、酸化室化シリコン、窒化酸化シリコン、酸化ハフニウム、または酸化タンタルなどの酸化物絶縁膜を用いる。第2のゲート絶縁膜402bは、後に形成する酸化物半導体膜と接するため、層中(バルク中)に少なくとも化学量論的組成を超える量の酸素が存在することが好ましい。

[0078]

また、第2のゲート絶縁膜402bとしてプラズマCVD法を用いて膜厚20nmの酸化シリコン膜を成膜し、酸化シリコン膜の成膜後に酸素欠損を修復するためのマイクロ波プラズマ処理を行ってラジカル酸化処理を行ってもよい。例えば、高密度プラズマ装置を用い、2.45GHzの電源を用いて3800Wとし、圧力を106.67Paとし、基板温度を325 とし、アルゴン流量を900sccmとし、酸素流量を5sccmとする。高密度プラズマ装置は、1×10<sup>1 1</sup> / cm 3 以上のプラズマ密度を達成できる装置を指している。例えば、3kW~6kWのマイクロ波電力を印加してプラズマを発生させる

。また、第2のゲート絶縁膜402bの形成前に、高密度プラズマ装置を用いて亜酸化窒素(N<sub>2</sub>O)と希ガスとを導入して行われるプラズマ処理を行ってもよい。

### [0079]

次いで、第2のゲート絶縁膜402b上に、酸化物半導体膜の積層を成膜する。

### [0800]

第1の酸化物半導体膜403a、第2の酸化物半導体膜403bを形成し、加熱処理を行った後、マスクを用いて選択的にエッチングする。

### [0081]

本実施の形態では、基板温度を室温とし、In:Ga:Zn=1:3:2の原子数比のターゲットを用いて、第1の酸化物半導体膜403aを成膜する。第1の酸化物半導体膜403aの膜厚は、10nm以上40nm以下、好ましくは20nm以上30nm以下とする。第1の酸化物半導体膜403aの膜厚を大きくすることで、下地膜(シリコンを含む絶縁膜)からのSiの拡散を防止することができる。また、結晶構造を有する第2の酸化物半導体膜403bの成膜には、基板温度を400 とし、In:Ga:Zn=1:1:1の原子数比のターゲットを用いる。第2の酸化物半導体膜403bは、表面と略垂直な方向にC軸が配向した結晶を含む膜であり、CAAC・OS膜とすることが好ましい。第2の酸化物半導体膜403bの膜厚は、5nm以上10nm以下とする。

#### [0082]

第2の酸化物半導体膜403bの成膜温度は、400以上550以下、好ましくは450以上500以下とする。ただし、既に形成している配線層が耐えられる温度範囲で行うこととする。また、加熱処理は、減圧下又は窒素雰囲気下で300以上600以下、好ましくは300以上500以下、さらに好ましくは350以上450以下として酸化物半導体膜中の過剰な水素(水や水酸基を含む)を除去(脱水化または脱水素化)する。そして、熱処理終了後の加熱温度を維持、またはその加熱温度から徐冷しながら同じ炉に高純度の酸素ガス、又は超乾燥エア(CRDS方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で-55)以下、好ましくは1ppm以下、より好ましくは10ppb以下の空気)を導入する。酸素ガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給する。

### [0083]

次いで、第2の酸化物半導体膜403bの上面及び側面を接して覆うように第3の酸化物半導体膜403cを形成する。また、第3の酸化物半導体膜403cも酸化物半導体膜中の過剰な水素(水や水酸基を含む)を除去(脱水化または脱水素化)するための熱処理を行ってもよく、酸素ガスを用いて第3の酸化物半導体膜403cに酸素を供給してもよい

### [0084]

また、第3の酸化物半導体膜403cの成膜には、基板温度を室温とし、In:Ga:Zn=1:3:2の原子数比のターゲットを用いる。第3の酸化物半導体膜403cは、第1の酸化物半導体膜403aとほぼ成膜条件が同じであり、膜全体がほぼ同じ膜質を有する。第3の酸化物半導体膜403cの膜厚は、10nm以上40nm以下、好ましくは20nm以上30nm以下とする。この段階での断面図が図4(A)に相当する。

### [0085]

次いで、第3の酸化物半導体膜403c上に導電膜を形成し、これを加工して電極層405a及び電極層405b(これと同じ層で形成される配線を含む)を形成する。次いで、 希釈フッ酸でウェットエッチングして第3の酸化物半導体膜403cの一部を薄膜化させる。

#### [0086]

次いで、電極層405a及び電極層405b及び露出した酸化物半導体膜の積層膜403 を覆うように、絶縁膜407を形成する。絶縁膜407としてはプラズマCVD法、スパッタリング法により形成することができ、酸化シリコン膜、酸化ガリウム膜、酸化アルミ 10

20

30

40

20

30

40

50

二ウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜等を単層で、又は積層して用いることができる。また、プラズマダメージを低減するため、プラズマダメージの少ない成膜条件で酸化物半導体膜の積層膜403を覆う第1の酸化絶縁膜を形成し、その上に膜中に酸素を多く含む成膜条件で第2の酸化絶縁膜を積層する構成とすることが好ましい。なお、酸化物半導体膜の積層膜403と接する絶縁膜407として、酸化絶縁膜を形成すると、該酸化絶縁膜によって酸化物半導体膜の積層膜403へ酸素を供給することが可能となるため、好ましい。本実施の形態では、絶縁膜407として窒素を有する酸化絶縁膜を用いる。

#### [0087]

次いで、絶縁膜407にイオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて酸素を添加する。酸化物半導体膜の積層膜403への酸素の供給は、酸化物半導体膜の積層膜の成膜後であれば、そのタイミングは特に限定されない。また、酸素の導入は複数回行ってもよい。

### [0088]

絶縁膜407を形成後、加熱処理を行う。酸化物半導体膜の積層膜403は、エッチングや成膜時のプラズマに曝され、ダメージを受けて形成される酸素欠損を含むため、酸化物半導体に与えられたダメージを回復させるための加熱処理を行い、酸素を供給することによって酸素欠損を低減させる。該熱処理の温度は、代表的には、200 以上450 以下とする。当該加熱処理により、窒素を有する酸化絶縁膜に含まれる窒素を放出させることができる。なお、当該加熱処理により、窒素を有する酸化絶縁膜から、水、水素等を脱離させることができる。本実施の形態では、窒素及び酸素の混合雰囲気で、350 、1時間の加熱処理を行う。酸化物半導体膜に含まれる水素原子及び酸素原子が、加熱処理により、酸化物半導体膜、酸化物半導体膜及び窒素を有する酸化絶縁膜の界面、または窒素を有する酸化絶縁膜、若しくはその表面において結合し、水分子となり、窒素を有する酸化絶縁膜、若しくはその表面において、酸素原子が脱離した位置は酸素欠損となるが、窒素を有する酸化絶縁膜に含まれる化学量論的組成を満たす酸素よりも多くの酸素の子が酸素欠損の位置へ移動し、酸素欠損を低減する。

#### [0089]

# [0090]

こうして、絶縁膜407形成後の加熱処理によって、酸化物半導体膜から、窒素、水素、または水が脱離することで、膜中の窒素、水素、または水の含有量を約10分の一程度まで低減することができる。

### [0091]

次いで、絶縁膜407上に保護絶縁膜408を形成する。保護絶縁膜408としては、酸化アルミニウム膜、または窒化シリコン膜を形成する。保護絶縁膜408は、外部からの水素や水分などの不純物の混入を防ぐ役割を果たす。

#### [0092]

以上の作製プロセスによって、本実施の形態のトランジスタ411を形成することができ

# [0093]

本実施の形態で示すトランジスタは、トランジスタの電流経路(チャネル)として機能する第2の酸化物半導体膜403bを挟んで、第2の酸化物半導体膜403bよりもキャリア密度が低い第1の酸化物半導体膜403aを含む構成とする。これによって、チャネルを酸化物半導体膜の積層膜403に接する絶縁膜界面

20

30

50

から遠ざけ、埋め込みチャネルを形成することができる。また、第2の酸化物半導体膜403bには可能な限り酸素を含ませることができるため、酸素欠損が少なく、トランジスタの信頼性が向上する。

### [0094]

(実施の形態2)

本実施の形態では、実施の形態1と一部異なる例を以下に説明する。本実施の形態は、実施の形態1の酸化物半導体膜の積層膜403の形成方法や酸素の供給方法などが異なる例である。

[0095]

下部に第1の半導体材料を用いたトランジスタ311を作製し、第2の層間絶縁膜308、バリア層310、及び第3の配線層309を形成するまでは実施の形態1と同一であるため、ここでは詳細な説明は省略する。

[0096]

バリア層上に導電膜を形成し、選択的にエッチングを行って第4の配線層434及びゲート電極491を形成する。

[0097]

次いで、ゲート電極491を覆う絶縁膜435を形成した後、CMPなどを用いて平坦化する。絶縁膜435は、窒素を有する酸化絶縁膜を用いる。

[0098]

次いで、第1のゲート絶縁膜402aと第2のゲート絶縁膜402bを形成する。第1のゲート絶縁膜402aとして窒素を有する酸化絶縁膜を用いる。

[0099]

また、第2のゲート絶縁膜402bとしてプラズマCVD法を用いて膜厚20nmの酸化シリコン膜を用い、酸化シリコン膜の成膜後に酸素欠損を修復するためのマイクロ波プラズマ処理を行ってラジカル酸化処理を行ってもよい。

[0100]

次いで、第2のゲート絶縁膜402b上に、図11に示す製造装置を用いて、酸化物半導体膜の積層を大気に触れることなく成膜する。

[0101]

第 1 の酸化物半導体膜 4 0 3 a 、第 2 の酸化物半導体膜 4 0 3 b 、第 3 の酸化物半導体膜 4 0 3 c を形成する。

[0102]

第1の酸化物半導体膜403a、第2の酸化物半導体膜403b、及び第3の酸化物半導体膜403cの成膜温度は、室温以上550以下、好ましくは200以上400未満とする。第2の酸化物半導体膜403bは、CAAC-OS膜とするため、成膜温度は、200以上550以下とする。また、第1の酸化物半導体膜403a、及び第3の酸化物半導体膜403cは、結晶化度の低い膜とするため、室温以上200未満とする

[0103]

次いで、マスクを用いて選択的にエッチングして島状の酸化物半導体膜の積層膜 403 を 00 形成する。

[0104]

次いで、第3の酸化物半導体膜403c上に導電膜を形成し、これを加工して電極層405a及び電極層405b(これと同じ層で形成される配線を含む)を形成する。次いで、 希釈フッ酸でウェットエッチングして第3の酸化物半導体膜403cの一部を薄膜化させる。

[0105]

次いで、電極層405a及び電極層405b及び露出した酸化物半導体膜の積層膜403を覆うように、絶縁膜407を形成する。絶縁膜407として積層構造が好ましく、プラズマダメージを低減するため、プラズマダメージの少ない成膜条件で酸化物半導体膜の積

層膜 4 0 3 を覆う第 1 の酸化絶縁膜を形成し、その上に膜中に酸素を多く含む成膜条件で第 2 の酸化絶縁膜を積層する構成とすることが好ましい。

### [0106]

また、絶縁膜407にイオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて酸素を添加してもよい。酸化物半導体膜の積層膜403への酸素の供給は、酸化物半導体膜の積層膜403の成膜後であれば、そのタイミングは特に限定されない。また、酸素の導入は複数回行ってもよい。

### [0107]

絶縁膜407を形成後、350 以上450 以下の加熱処理を行う。絶縁膜435、第1のゲート絶縁膜402a、及び第2のゲート絶縁膜402bに含まれる酸素を酸化物半導体膜の積層膜403へ供給する。また、絶縁膜407として、実施の形態1に示した窒素を有する酸化絶縁膜を用い、絶縁膜407に含まれる酸素を酸化物半導体膜の積層膜403へ供給してもよい。

### [0108]

次いで、絶縁膜407上に保護絶縁膜408を形成する。保護絶縁膜408としては、酸化アルミニウム膜、または窒化シリコン膜を形成する。保護絶縁膜408は、外部からの水素や水分などの不純物の混入を防ぐ役割を果たす。

### [0109]

以上の作製プロセスによって、図 5 に示すようにトランジスタ 3 1 1 の上方に本実施の形態のトランジスタ 4 1 2 を形成することができる。

#### [0110]

また、本実施の形態は実施の形態1と自由に組み合わせることができる。

## [0111]

### (実施の形態3)

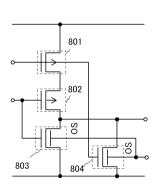

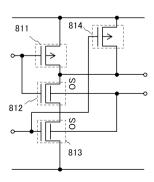

実施の形態1または実施の形態2に示すトランジスタを使用した半導体装置の一例として、論理回路であるNOR型回路の回路図の一例を図6(A)に示す。図6(B)はNAND型回路の回路図である。

#### [0112]

図6(A)に示すNOR型回路において、pチャネル型トランジスタであるトランジスタ801、802は、図4(B)に示すトランジスタ311と同様な構造を有する、チャネル形成領域に単結晶シリコン基板を用いたトランジスタとし、nチャネル型トランジスタであるトランジスタ803、804は、図4(B)に示すトランジスタ411、及び図5で示すトランジスタ412と同様な構造を有するチャネル形成領域に酸化物半導体膜を用いたトランジスタを用いる。

### [0113]

なお、図6(A)に示すNOR型回路において、トランジスタ803、804は、酸化物半導体膜を介して、ゲート電極と重なる位置にトランジスタの電気的特性を形御する導電層を設けてもよい。該導電層の電位を制御し、例えばGNDとすることでトランジスタ803、804のしきい値電圧をよりプラスとし、さらにノーマリーオフのトランジスタとすることができる。

### [0114]

また、図 6 ( B )に示す N A N D 型回路では、 p チャネル型トランジスタであるトランジスタ 8 1 1 、 8 1 4 は、図 4 に示すトランジスタ 3 1 1 と同様な構造を有し、 n チャネル型トランジスタであるトランジスタ 8 1 2 、 8 1 3 は、図 4 ( B )に示すトランジスタ 4 1 1、及び図 5 で示すトランジスタ 4 1 2 と同様な構造を有するチャネル形成領域に酸化物半導体膜を用いたトランジスタを用いる。

#### [0115]

なお、図6(B)に示すNAND型回路において、トランジスタ812、813は、酸化物半導体膜を介して、ゲート電極と重なる位置にトランジスタの電気的特性を形御する導電層を設けてもよい。該導電層の電位を制御し、例えばGNDとすることでトランジスタ

10

20

30

40

20

30

40

50

8 1 2 、 8 1 3 のしきい値電圧をよりプラスとし、さらにノーマリーオフのトランジスタとすることができる。

### [0116]

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、消費電力を十分に低減することができる

#### [0117]

また、異なる半導体材料を用いた半導体素子を積層することにより、微細化及び高集積化 を実現し、かつ安定で高い電気的特性を付与された半導体装置、及び該半導体装置の作製 方法を提供することができる。

### [0118]

また、本実施の形態では、実施の形態 2 に示すトランジスタを使用したNOR型回路とNAND型回路の例を示したが、特に限定されず、実施の形態 1 または実施の形態 2 に示すトランジスタを使用してAND型回路やOR回路などを形成することができる。例えば、実施の形態 1 または実施の形態 2 に示すトランジスタを使用して電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶装置)を作製することもできる。

### [0119]

#### (実施の形態4)

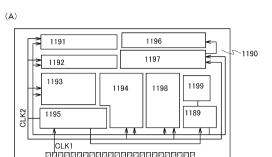

本実施の形態では、半導体装置の一例として、図4(B)に示すトランジスタ411、及び図5で示すトランジスタ412のいずれか一を少なくとも一部に用いたCPU(Central Processing Unit)について説明する。

### [0120]

図7(A)は、CPUの具体的な構成を示すブロック図である。図7(A)に示すCPUは、基板1190上に、ALU1191(ALU:Arithmetic logicunit、演算回路)、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース1198(Bus I / F)、書き換え可能なROM1199、及びROMインターフェース1189(ROM I / F)を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199及びROMインターフェース1189は、別チップに設けてもよい。もちろん、図7(A)に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

### [0121]

バスインターフェース 1 1 9 8 を介して C P U に入力された命令は、インストラクションデコーダ 1 1 9 3 に入力され、デコードされた後、 A L U コントローラ 1 1 9 2 、インタラプトコントローラ 1 1 9 7 、タイミングコントローラ 1 1 9 5 に入力される。

### [0122]

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

#### [0123]

また、タイミングコントローラ 1 1 9 5 は、ALU 1 1 9 1、ALUコントローラ 1 1 9 2、インストラクションデコーダ 1 1 9 3、インタラプトコントローラ 1 1 9 4、及びレジスタコントローラ 1 1 9 7の動作のタイミングを制御する信号を生成する。例えばタイ

20

30

40

50

ミングコントローラ 1 1 9 5 は、基準クロック信号 C L K 1 を元に、内部クロック信号 C L K 2 を生成する内部クロック生成部を備えており、内部クロック信号 C L K 2 を上記各種回路に供給する。

### [0124]

図7(A)に示すCPUでは、レジスタ1196に、メモリセルが設けられている。

#### [0125]

図7(A)に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有するメモリセルにおいて、フリップフロップによるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。フリップフロップによるデータの保持が選択されている場合、レジスタ1196内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内のメモリセルへの電源電圧の供給を停止することができる。

#### [0126]

電源停止に関しては、図7(B)または図7(C)に示すように、メモリセル群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を設けることにより行うことができる。以下に図7(B)及び図7(C)の回路の説明を行う。

### [ 0 1 2 7 ]

図 7 ( B ) 及び図 7 ( C ) では、メモリセルへの電源電位の供給を制御するスイッチング素子に、図 4 ( B ) に示すトランジスタ 4 1 1、及び図 5 で示すトランジスタ 4 1 2 のいずれか一を含む記憶回路の構成の一例を示す。

### [0128]

図7(B)に示す記憶装置は、スイッチング素子1141と、メモリセル1142を複数有するメモリセル群1143とを有している。メモリセル群1143が有する各メモリセル1142には、スイッチング素子1141を介して、ハイレベルの電源電位VDDが供給されている。さらに、メモリセル群1143が有する各メモリセル1142には、信号INの電位と、ローレベルの電源電位VSSの電位が与えられている。

### [0129]

図 7 ( B ) では、スイッチング素子 1 1 4 1 として、図 4 ( B ) に示すトランジスタ 4 1 1、及び図 5 で示すトランジスタ 4 1 2 のいずれかーを用いており、該トランジスタは、そのゲート電極に与えられる信号 S i g A によりスイッチングが制御される。

#### [0130]

なお、図7(B)では、スイッチング素子1141がトランジスタを一つだけ有する構成を示しているが、特に限定されず、トランジスタを複数有していてもよい。スイッチング素子1141が、スイッチング素子として機能するトランジスタを複数有している場合、上記複数のトランジスタは並列に接続されていてもよいし、直列に接続されていてもよいし、直列と並列が組み合わされて接続されていてもよい。

### [0131]

また、図 7 ( B ) では、スイッチング素子 1 1 4 1 により、メモリセル群 1 1 4 3 が有する各メモリセル 1 1 4 2 への、ハイレベルの電源電位 V D D の供給が制御されているが、スイッチング素子 1 1 4 1 により、ローレベルの電源電位 V S S の供給が制御されていてもよい。

## [0132]

また、図7(C)には、メモリセル群1143が有する各メモリセル1142に、スイッチング素子1141を介して、ローレベルの電源電位VSSが供給されている、記憶装置の一例を示す。スイッチング素子1141により、メモリセル群1143が有する各メモリセル1142への、ローレベルの電源電位VSSの供給を制御することができる。

### [0133]

メモリセル群と、電源電位VDDまたは電源電位VSSの与えられているノード間に、ス

20

30

40

50

イッチング素子を設け、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合においてもデータを保持することが可能であり、消費電力の低減を行うことができる。具体的には、例えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力を停止している間でも、CPUの動作を停止することができ、それにより消費電力を低減することができる。

### [0134]

ここでは、CPUを例に挙げて説明したが、DSP(Digital Signal Processor)、カスタムLSI、FPGA(Field Programmable Gate Array)等のLSIにも応用可能である。

#### [0135]

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適 宜組み合わせて用いることができる。

#### [0136]

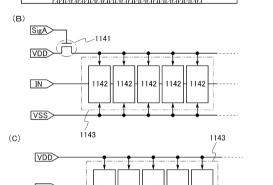

(実施の形態5)

本実施の形態では、液晶表示装置を例にして本発明の一態様である半導体装置を説明する

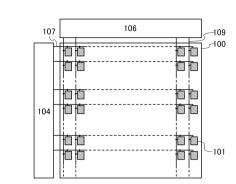

### [0137]

図8(A)に、半導体装置の構成例を示す図を示す。図8(A)に示す半導体装置は、画素部100と、走査線駆動回路104と、信号線駆動回路106と、各々が平行又は略平行に配設され、且つ走査線駆動回路104によって電位が制御されるm本の走査線107と、各々が平行又は略平行に配設され、且つ信号線駆動回路106によって電位が制御されるn本の信号線109と、を有する。さらに、画素部100はマトリクス状に配設された複数の画素101を有する。また、走査線107に沿って、各々が平行又は略平行に配設された容量線115は、信号線109に沿って、各々が平行又は略平行に配設されていてもよい。

### [0138]

各走査線107は、画素部100においてm行n列に配設された画素101のうち、いずれかの行に配設されたn個の画素101と電気的に接続される。また、各信号線109は、m行n列に配設された画素101のうち、いずれかの列に配設されたm個の画素101に電気的と接続される。m、nは、ともに1以上の整数である。また、各容量線115は、m行n列に配設された画素101のうち、いずれかの行に配設されたn個の画素101と電気的に接続される。なお、容量線115が、信号線109に沿って、各々が平行又は略平行に配設されている場合は、m行n列に配設された画素101のうち、いずれかの列に配設されたm個の画素101に電気的と接続される。

### [0139]

図8(B)は、図8(A)に示す半導体装置が有する画素101の回路図の一例である。図8(B)に示す画素101は、ゲート電極が走査線107と電気的に接続され、ソース電極が信号線109と電気的に接続されたトランジスタ103と、一方の電極がトランジスタ103のドレイン電極と電気的に接続され、他方の電極が一定の電位を供給する容量線115と電気的に接続された容量素子105と、画素電極がトランジスタ103のドレイン電極及び容量素子105の一方の電極に電気的に接続され、画素電極と対向して設けられる電極(対向電極)が対向電位を供給する配線に電気的に接続された液晶素子108と、を有する。

## [0140]

液晶素子108は、トランジスタ103及び画素電極が形成される基板と、対向電極が形成される基板とで挟持される液晶の光学的変調作用によって、光の透過または遮光を制御する素子である。なお、液晶の光学的変調作用は、液晶にかかる電界(横方向の電界、縦方向の電界又は斜め方向の電界を含む。)によって制御される。

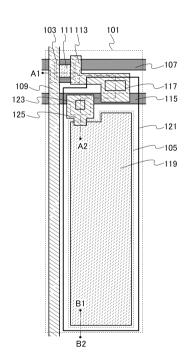

### [0141]

次いで、液晶表示装置の画素101の具体的な構成例について説明する。画素101の

20

30

40

50

上面図を図9に示す。なお、図9においては、対向電極及び液晶素子を省略する。

### [0142]

図9において、走査線107は、信号線109に略直交する方向(図9中左右方向)に延伸して設けられている。信号線109は、走査線107に略直交する方向(図9中上下方向)に延伸して設けられている。容量線115は、走査線107と平行方向に延伸して設けられている。なお、走査線107及び容量線115は、走査線駆動回路104(図8(A)参照)と電気的に接続されており、信号線109は、信号線駆動回路106(図8(A)参照)に電気的に接続されている。

### [0143]

トランジスタ103は、走査線107及び信号線109が交差する領域に設けられている。トランジスタ103は、少なくとも、チャネル形成領域を有する酸化物半導体膜の積層膜111と、ゲート電極と、ゲート絶縁膜(図9に図示せず)と、ソース電極と、及びドレイン電極とを含む。

### [0144]

酸化物半導体膜の積層膜111は、図10に示すように、第1の酸化物半導体膜111a、第2の酸化物半導体膜111b、第3の酸化物半導体膜111cの順で積層する。第1の酸化物半導体膜111aの伝導帯下端及び第3の酸化物半導体膜111cの伝導帯下端に比べて第2の酸化物半導体膜111bの伝導帯下端が真空準位から最も深くなるような井戸型構造を構成するように、第1の酸化物半導体膜111a、第2の酸化物半導体膜111a、第2の酸化物半導体膜111a、第2の酸化物半導体膜111cの材料を適宜選択する。本実施の形態では、In:Ga:Zn=1:3:2の原子数比のターゲットを用いて第1の酸化物半導体膜111aと第3の酸化物半導体膜111cを形成し、In:Ga:Zn=1:1:1の原子数比のターゲットを用いて第2の酸化物半導体膜111bを形成する。酸化物半導体膜の積層膜111により、埋め込みチャネルを形成し、酸素欠損が少なく、トランジスタ103の信頼性を向上させる。

### [0145]

また、酸化物半導体膜の積層膜 1 1 1 は適切な条件にて成膜または加熱処理することでトランジスタのオフ電流を極めて低減することができるため、半導体装置の消費電力を低減することができる。

# [0146]

また、走査線107は、トランジスタ103のゲート電極としても機能し、信号線109はトランジスタ103のソース電極としても機能する。導電膜113は、トランジスタ103のドレイン電極として機能し、開口117を通じて画素電極121と電気的に接続されている。なお、図9において、画素電極121はハッチングを省略して図示している。また、以下において、トランジスタのゲート電極を指し示す場合にも走査線107と記載し、トランジスタのソース電極を指し示す場合にも信号線109と記載する。

## [0147]

容量素子105は、画素101内の容量線115及び信号線109で囲まれる領域に設けられている。容量素子105は、開口123に設けられた導電膜125を通じて容量線115と電気的に接続されている。容量素子105は、透光性を有する酸化物半導体膜の積層膜119と、透光性を有する画素電極121と、誘電体膜として、トランジスタ103に含まれ、透光性を有する絶縁膜(図9に図示せず)とで構成されている。即ち、容量素子105は透光性を有する。

## [0148]

このように酸化物半導体膜の積層膜119は透光性を有するため、画素101内に容量素子105を大きく(大面積に)形成することができる。従って、開口率を低減させず、又は開口率を向上させつつ、電荷容量を大きくした半導体装置を得ることができる。また、開口率を向上することによって表示品位の良い半導体装置を得ることができる。

### [0149]

ここで、酸化物半導体を用いたトランジスタの特徴について記載する。酸化物半導体を

20

30

40

50

用いたトランジスタはnチャネル型トランジスタである。また、酸化物半導体に含まれる酸素欠損はキャリアを生成することがあり、トランジスタの電気特性及び信頼性を低下させる恐れがある。例えば、トランジスタのしきい値電圧をマイナス方向に変動し、ゲート電圧が0 V の場合にドレイン電流が流れてしまうことがある。このように、ゲート電圧が0 V の場合にドレイン電流が流れてしまうことをノーマリーオン特性という。なお、ゲート電圧が0 V の場合にドレイン電流が流れていないとみなすことができるトランジスタをノーマリーオフ特性という。

### [0150]

酸化物半導体膜の積層膜111に含まれる欠陥、代表的には酸素欠損はできる限り低減されていることが好ましい。例えば、磁場の向きを膜面に対して平行に印加した電子スピン共鳴法によるg値=1.93のスピン密度(酸化物半導体膜に含まれる欠陥密度に相当する。)は、測定器の検出下限以下まで低減されていることが好ましい。酸化物半導体膜に含まれる欠陥、代表的には酸素欠損をできる限り低減することで、トランジスタ103がノーマリーオン特性となることを抑制することができ、半導体装置の電気特性及び信頼性を向上させることができる。

#### [0151]

酸化物半導体膜の積層膜111に含まれる不純物(水素、水分、第14族元素など)はできる限り低減されていることが好ましく、高純度化させた酸化物半導体膜とし、i型とすることでトランジスタ103がノーマリーオン特性となることを抑制でき、トランジスタ103のオフ電流を極めて低減することができる。従って、良好な電気特性に有する半導体装置を作製できる。また、信頼性を向上させた半導体装置を作製することができる。

[ 0 1 5 2 ]

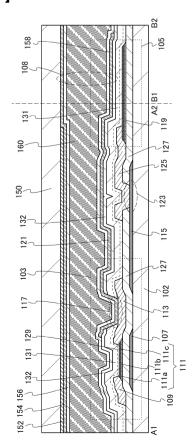

次いで、図9の一点鎖線A1-A2間及び一点鎖線B1-B2間における断面図を図10に示す。

#### [0153]

液晶表示装置の画素 1 0 1 の断面構造は以下の通りである。液晶表示装置は、基板 1 0 2 上に形成される素子部と、基板 1 5 0 上に形成される素子部と、該 2 つの素子部で挟まれる液晶層とを有する。

### [0154]

はじめに、基板102上に形成される素子部の構造について説明する。基板102上に、 トランジスタ103のゲート電極として機能する走査線107と、走査線107と同一表 面上に設けられている容量線115とが設けられている。走査線107及び容量線115 上にゲート絶縁膜127が設けられている。ゲート絶縁膜127の走査線107と重畳す る領域上に酸化物半導体膜の積層膜111が設けられており、ゲート絶縁膜127上に酸 化物半導体膜の積層膜119が設けられている。酸化物半導体膜の積層膜111上、及び ゲート絶縁膜127上にトランジスタ103のソース電極として機能する信号線109と トランジスタ103のドレイン電極として機能する導電膜113とが設けられている。 ゲート絶縁膜127には容量線115に達する開口123が設けられており、開口123 ゲート絶縁膜127上、及び酸化物半導体膜の積層膜119上に導電膜125が設けら れている。ゲート絶縁膜127上、信号線109上、酸化物半導体膜の積層膜111上、 導電膜113上、導電膜125上、酸化物半導体膜の積層膜119上にトランジスタ10 3の保護絶縁膜として機能する絶縁膜129、絶縁膜131、及び絶縁膜132が設けら れている。絶縁膜129、絶縁膜131、及び絶縁膜132には導電膜113に達する開 口117が設けられており、開口117及び絶縁膜132上に画素電極121が設けられ ている。また、画素電極121及び絶縁膜132上に配向膜として機能する絶縁膜158 が設けられている。なお、基板102と、走査線107及び容量線115並びにゲート絶 縁膜127との間には下地絶縁膜が設けられていてもよい。

#### [0155]

本構成での容量素子105は、一対の電極のうち一方の電極として機能するのが酸化物 半導体膜の積層膜111と同じ工程で成膜された酸化物半導体膜の積層膜119であり、 一対の電極のうち他方の電極が画素電極121であり、一対の電極の間に設けられた誘電体膜が絶縁膜129、絶縁膜131、及び絶縁膜132である。

#### [0156]

以下に、上記構造の構成要素について詳細を記載する。

### [0157]

基板102の材質などに大きな制限はないが、少なくとも、半導体装置の作製工程において行う熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、プラスチック基板などがあり、ガラス基板としては、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス若しくはアルミノケイ酸ガラス等の無アルカリガラス基板を用いるとよい。なお、基板102として石英基板、サファイア基板などを用いることもできる。

[0158]

走査線107及び容量線115は、モリブデン(Mo)、チタン(Ti)、タングステン(W)タンタル(Ta)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)などの金属材料又はこれらを主成分とする合金材料を用いた、単層構造又は積層構造で設ける。

### [0159]

走査線107及び容量線115の一例としては、シリコンを含むアルミニウムを用いた 単層構造、アルミニウム上にチタンを積層する二層構造、窒化チタン上にチタンを積層す る二層構造、窒化チタン上にタングステンを積層する二層構造、窒化タンタル上にタング ステンを積層する二層構造、銅・マグネシウム・アルミニウム合金上に銅を積層する二層 構造、窒化チタン上に銅を積層し、さらにその上にタングステンを形成する三層構造など がある。

#### [0160]

また、走査線107及び容量線115の材料として、画素電極121に適用可能な透光性を有する導電性材料を用いることができる。

#### [0161]

走査線107及び容量線115において、低抵抗材料であるアルミニウムや銅を用いることが好ましい。アルミニウムや銅を用いることで、信号遅延を低減し、表示品位を高めることができる。なお、アルミニウムは耐熱性が低く、ヒロック、ウィスカー、あるいはマイグレーションによる不良が発生しやすい。アルミニウムのマイグレーションを防ぐため、アルミニウムに、モリブデン、チタン、タングステンなどの、アルミニウムよりも融点の高い金属材料を積層することが好ましい。また、銅を用いる場合も、マイグレーションによる不良や銅元素の拡散を防ぐため、モリブデン、チタン、タングステンなどの、銅よりも融点の高い金属材料を積層することが好ましい。

#### [0162]

ゲート絶縁膜127は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウム又はGa-Zn系金属酸化物などの絶縁材料を用いた、単層構造又は積層構造で設ける。なお、酸化物半導体膜の積層膜111である酸化物半導体膜との界面特性を向上させるため、ゲート絶縁膜127において少なくとも酸化物半導体膜の積層膜111と接する領域は酸化絶縁膜で形成することが好ましい。

[0163]

また、ゲート絶縁膜127に、酸素、水素、水などに対するバリア性を有する絶縁膜を設けることで、酸化物半導体膜の積層膜111からの酸素の外部への拡散と、外部から当該酸化物半導体膜の積層膜への水素、水等の侵入を防ぐことができる。酸素、水素、水等などに対するバリア性を有する絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム、窒化シリコンなどがある。

### [0164]

50

10

20

30

20

30

40

50

また、ゲート絶縁膜 1 2 7 として、ハフニウムシリケート( $HfSiO_x$ )、窒素を有するハフニウムシリケート( $HfSi_xO_yN_z$ )、窒素を有するハフニウムアルミネート( $HfAl_xO_yN_z$ )、酸化ハフニウム、酸化イットリウムなどのhigh-k材料を用いることでトランジスタ 1 0 3 のゲートリークを低減できる。

### [0165]

また、ゲート絶縁膜127は、以下の積層構造とすることが好ましい。第1の窒化シリコン膜として、欠陥量が少ない窒化シリコン膜を設け、第1の窒化シリコン膜上に第2の窒化シリコン膜として、水素脱離量及びアンモニア脱離量の少ない窒化シリコン膜を設け、第2の窒化シリコン膜上に、上記ゲート絶縁膜127で羅列した酸化絶縁膜のいずれかを設けることが好ましい。

### [0166]

第 2 の室化シリコン膜としては、昇温脱離ガス分析法において、水素分子の脱離量が 5  $\times$  1 0  $^2$   $^1$  分子 / c m  $^3$  未満、好ましくは 3  $\times$  1 0  $^2$   $^1$  分子 / c m  $^3$  以下、さらに好ましくは 1  $\times$  1 0  $^2$   $^1$  分子 / c m  $^3$  以下であり、アンモニア分子の脱離量が 1  $\times$  1 0  $^2$   $^2$  分子 / c m  $^3$  未満、好ましくは 5  $\times$  1 0  $^2$   $^1$  分子 / c m  $^3$  以下である室化絶縁膜を用いることが好ましい。上記第 1 の室化シリコン膜及び第 2 の室化シリコン膜をゲート絶縁膜 1 2 7 の一部として用いることで、ゲート絶縁膜 1 2 7 として、欠陥量が少なく、且つ水素及びアンモニアの脱離量の少ないゲート絶縁膜を形成することができる。この結果、ゲート絶縁膜 1 2 7 に含まれる水素及び窒素の、半導体膜の積層膜 1 1 1 への移動量を低減することが可能である。

#### [ 0 1 6 7 ]

トランジスタにおいて、酸化物半導体膜の積層膜111及びゲート絶縁膜の界面またはゲート絶縁膜に捕獲準位(界面準位ともいう。)が存在すると、トランジスタのしきい値電圧の変動、代表的にはしきい値電圧のマイナス方向への変動、及びトランジスタがオン状態となるときにドレイン電流が一桁変化するのに必要なゲート電圧を示すサブスレッショルド係数(S値)の増大の原因となる。この結果、トランジスタごとに電気特性がばらつくという問題がある。このため、ゲート絶縁膜として、欠陥量の少ない窒化シリコン膜を用いることで、また、第1の酸化物半導体膜111aと接する領域に酸化絶縁膜を設けることで、しきい値電圧のマイナスシフトを低減すると共に、S値の増大を抑制することができる。

### [0168]

ゲート絶縁膜127の厚さは、5nm以上400nm以下、より好ましくは10nm以上300nm以下、より好ましくは50nm以上250nm以下とするとよい。

#### [0169]

本実施の形態においては、第1の酸化物半導体膜111a、及び第3の酸化物半導体膜111cは結晶化度の低い膜とし、第2の酸化物半導体膜111bは、結晶構造を有する膜とする。第1の酸化物半導体膜111aは結晶化度の低い膜として成膜し、第2の酸化物半導体膜111bを成膜した後、加熱処理(200 以上550 以下)を行い、その後、第3の酸化物半導体膜111cを形成する。図11に示す製造装置を用いて大気に触れることなく上記工程を行うことが好ましい。また、酸化物半導体膜の積層膜111と同じ工程で形成される酸化物半導体膜の積層膜119においても1層目と3層目が結晶化度の低い膜であり、2層目が結晶構造を有して結晶化度の高い膜となっており、CAAC-OS膜となっている。また、酸化物半導体膜の積層膜111の厚さは、1nm以上100nm以下、好ましくは1nm以上50nm以下、更に好ましくは3nm以上20nm以下とする。

# [0170]

埋め込みチャネルを形成することができるトランジスタ103とすることで、酸素欠損が 少なく、トランジスタの信頼性が向上する。

### [0171]

また、酸化物半導体膜の積層膜111及び酸化物半導体膜の積層膜119に適用可能な酸

20

30

40

50

化物半導体として、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタ103のオフ電流を低減することができる。

### [0172]

トランジスタ103のソース電極として機能する信号線109、トランジスタ103のドレイン電極として機能する導電膜113、及び容量素子105の酸化物半導体膜の積層膜119と容量線115とを電気的に接続する導電膜125は、走査線107及び容量線115に適用できる材料を用いた、単層構造又は積層構造で設ける。

#### [0173]

トランジスタ103の保護絶縁膜、及び容量素子105の誘電体膜として機能する絶縁膜129と、絶縁膜131と、絶縁膜132とは、ゲート絶縁膜127に適用できる材料を用いた絶縁膜である。特に、絶縁膜129及び絶縁膜131は酸化絶縁膜とし、絶縁膜132は窒化絶縁膜とすることが好ましい。また、絶縁膜132を窒化絶縁膜とすることで外部から水素や水などの不純物がトランジスタ103(特に第2の酸化物半導体膜111b)に侵入することを抑制できる。なお、絶縁膜129は設けない構成であってもよい

### [0174]

また、絶縁膜129及び絶縁膜131の一方又は双方は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜で有ることが好ましい。このようにすることで、当該酸化物半導体膜からの酸素の脱離を防止するとともに、酸素過剰領域に含まれる当該酸素を酸化物半導体膜に移動させ、酸素欠損を低減することが可能となる。例えば、昇温脱離ガス分析(以下、TDS分析とする。)によって測定される酸素分子の放出量が、1.0×10<sup>18</sup>分子/cm³以上ある酸化絶縁膜を用いることで、当該酸化物半導体膜に含まれる酸素欠損を低減することができる。なお、絶縁膜129及び絶縁膜131の一方又は双方において、化学量論的組成よりも過剰に酸素を含む領域(酸素過剰領域)が部分的に存在している酸化絶縁膜であってもよく、少なくとも半導体膜の積層膜111と重畳する領域に酸素過剰領域が存在することで、当該酸化物半導体膜からの酸素の脱離を防止する領域に酸素過剰領域に含まれる当該酸素を酸化物半導体膜に移動させ、酸素欠損を低減することが可能となる。

## [0175]

絶縁膜131が化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜である場合、絶縁膜129は、酸素を透過する酸化絶縁膜とすることが好ましい。なお、絶縁膜129において、外部から絶縁膜129に入った酸素は、全て絶縁膜129を通過して移動せず、絶縁膜129にとどまる酸素もある。また、あらかじめ絶縁膜129に含まれており、絶縁膜129から外部に移動する酸素もある。そこで、絶縁膜129は酸素の拡散係数が大きい酸化絶縁膜であることが好ましい。

## [0176]

また、絶縁膜129は第3の酸化物半導体膜111cと接することから、酸素を透過させるだけではなく、第3の酸化物半導体膜111cとの界面準位が低くなる酸化絶縁膜であることが好ましい。例えば、絶縁膜129は絶縁膜131よりも膜中の欠陥密度が低い酸化絶縁膜であることが好ましい。具体的には、電子スピン共鳴測定によるg値=2.001(E´・center)のスピン密度が3.0×10<sup>17</sup>spins/cm³以下、好ましくは5.0×10<sup>16</sup>spins/cm³以下の酸化絶縁膜である。なお、電子スピン共鳴測定によるg値=2.001のスピン密度は、絶縁膜129に含まれるダングリングボンドの存在量に対応する。

# [0177]

絶縁膜129の厚さは、5nm以上150nm以下、好ましくは5nm以上50nm以下、好ましくは10nm以上30nm以下とすることができる。絶縁膜131の厚さは、30nm以上500nm以下、好ましくは150nm以上400nm以下とすることができる。

#### [0178]

絶縁膜132を窒化絶縁膜とする場合、絶縁膜129及び絶縁膜131の一方又は双方が窒素に対するバリア性を有する絶縁膜であることが好ましい。例えば、緻密な酸化絶縁膜とすることで窒素に対するバリア性を有することができ、具体的には、25 において0.5重量%のフッ酸を用いた場合のエッチング速度が10nm/分以下である酸化絶縁膜とすることが好ましい。

#### [0179]

なお、絶縁膜129及び絶縁膜131の一方又は双方を、酸化室化シリコン又は窒化酸化シリコンなど、窒素を含む酸化絶縁膜とする場合、SIMSより得られる窒素濃度は、SIMS検出下限以上3×10 $^2$ 0 a t o m s / c m  $^3$  未満、好ましくは1×10 $^1$ 8 a t o m s / c m  $^3$  以下とすることが好ましい。このようにすることで、トランジスタ103に含まれる酸化物半導体膜の積層膜111への窒素の移動量を少なくすることができる。また、このようにすることで、窒素を含む酸化絶縁膜自体の欠陥量を少なくすることができる。

#### [0180]

絶縁膜 1 3 2 として、水素含有量が少ない窒化絶縁膜を設けてもよい。当該窒化絶縁膜としては、例えば、 T D S 分析によって測定される水素分子の放出量が、 5 . 0 × 1 0  $^2$   $^1$  m o 1 e c u 1 e s / c m  $^3$  未満であり、好ましくは 3 . 0 × 1 0  $^2$   $^1$  m o 1 e c u 1 e s / c m  $^3$  未満であり、さらに好ましくは 1 . 0 × 1 0  $^2$   $^1$  m o 1 e c u 1 e s / c m  $^3$  未満である窒化絶縁膜である。

#### [0181]

絶縁膜132は、外部から水素や水などの不純物の侵入を抑制する機能を発揮できる厚さとする。例えば、50nm以上200nm以下、好ましくは50nm以上150nm以下、さらに好ましくは50nm以上100nm以下とすることができる。

#### [0182]

画素電極121は、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料で設ける。また、図8(A)に示す走査線駆動回路104や信号線駆動回路106を同一基板上に形成することもでき、走査線駆動回路104や信号線駆動回路106に配置するトランジスタとして酸化物半導体膜を用いたトランジスタを作製する場合、画素電極121と同じ工程で酸化物半導体膜の上方にバックゲートとして機能する電極を形成してもよい。バックゲートとして機能する電極を形成してもよい。バックゲートとして機能する電極を形成してもよい。バックゲートとして機能する電極を表記を定益線駆動回路104や信号線駆動回路106のトランジスタの上方に重なる位置に配置することによって信頼性を向上させることができる。

#### [0183]

次に、基板150上に設けられる素子部の構造について説明する。基板150上に、遮光膜152と、遮光膜152上に画素電極121と対向して設けられる電極(対向電極154)が設けられている。また、対向電極154上に配向膜として機能する絶縁膜156が設けられている。

## [0184]

遮光膜152は、バックライト又は外部からの光がトランジスタ103に照射されることを抑制する。遮光膜152は、金属や、顔料を含む有機樹脂などの材料を用いて形成することができる。なお、遮光膜152は、画素101のトランジスタ103上の他、走査線駆動回路104、信号線駆動回路106(図8を参照。)等の画素部100以外の領域に設けてもよい。

#### [0185]

なお、隣り合う遮光膜152の間に、所定の波長の光を透過させる機能を有する着色膜を設けてもよい。さらには、遮光膜152及び着色膜と、対向電極154の間にオーバーコート膜を設けてもよい。

10

20

30

40

20

30

40

50

#### [0186]

対向電極154は、画素電極121に示す透光性を有する導電性材料を適宜用いて設ける

### [0187]

液晶素子108は、画素電極121、対向電極154、及び液晶層160を含む。なお、基板102の素子部に設けられた配向膜として機能する絶縁膜158、及び基板150の素子部に設けられた配向膜として機能する絶縁膜156によって、液晶層160が挟持されている。また、画素電極121及び対向電極154は液晶層160を介して重なる。

#### [0188]

ここで、本実施の形態に示す画素 1 0 1 に含まれる各構成要素の接続について、図 8 (C)に示す回路図及び図 1 0 に示す断面図を用いて説明する。

#### [0189]

図8(C)は、図8(A)に示す半導体装置が有する画素101の詳細な回路図の一例である。図8(C)及び図10に示すように、トランジスタ103は、ゲート電極107aを含む走査線107と、ソース電極109aを含む信号線109と、ドレイン電極113aを含む導電膜113とを有する。

#### [0190]

容量素子105において、導電膜125を介して容量線115と接続する酸化物半導体膜の積層膜119が一方の電極として機能する。また、ドレイン電極113aを含む導電膜113に接続する画素電極121が他方の電極として機能する。また、酸化物半導体膜の積層膜119及び画素電極121の間に設けられる、絶縁膜129、絶縁膜131、及び絶縁膜132が誘電体膜として機能する。

#### [0191]

液晶素子108は、画素電極121、対向電極154、並びに画素電極121及び対向電極の間に設けられる液晶層160で構成される。

### [0192]

容量素子105において、酸化物半導体膜の積層膜119は、酸化物半導体膜の積層膜1 11と同一の構成であっても、容量素子105の電極として機能する。なぜなら、画素電 極 1 2 1 をゲート電極、絶縁膜 1 2 9 、絶縁膜 1 3 1 及び絶縁膜 1 3 2 をゲート絶縁膜、 容量線115をソース電極又はドレイン電極と機能させることが可能であり、この結果、 容量素子105をトランジスタと同様に動作させ、酸化物半導体膜の積層膜119を導通 状態にすることができるからである。即ち、容量素子105をMOSキャパシタとするこ とが可能であり、容量線115に印加する電位を制御することで酸化物半導体膜の積層膜 119を導通状態とさせ、酸化物半導体膜の積層膜119を容量素子の一方の電極として 機能させることができる。この場合、容量線115に印加する電位を以下のようにする。 画素電極121の電位は、液晶素子108(図8(C)を参照。)を動作させるために、 プラス方向及びマイナス方向に変動する。容量素子105(MOSキャパシタ)を常に導 通状態にさせておくためには、容量線115の電位を、常に、画素電極121に印加する 電位よりも容量素子105(MOSキャパシタ)のしきい値電圧分以上低くしておく必要 がある。つまり、酸化物半導体膜の積層膜119と酸化物半導体膜の積層膜111は同一 の構成であるため、容量線115の電位をトランジスタ103のしきい値電圧分以上低く しておけばよい。このようにすることで、チャネルが形成されるため、容量素子105( MOSキャパシタ)を常に導通状態とすることができる。

# [0193]

また、酸化物半導体膜の積層膜111及び酸化物半導体膜の積層膜119上に設けられる絶縁膜129を、酸素を透過させると共に、第3の酸化物半導体膜111cとの界面準位が低くなる酸化絶縁膜とし、絶縁膜131を、酸素過剰領域を含む酸化絶縁膜又は化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜とすることで、酸化物半導体膜の積層膜111へ酸素を供給することが容易になり、酸化物半導体膜の積層膜111からの酸素の脱離を防止すると共に、絶縁膜131に含まれる当該酸素を酸化物半導体膜の

積層膜111に移動させ、酸化物半導体膜の積層膜111に含まれる酸素欠損を低減することが可能となる。この結果、トランジスタ103がノーマリーオン特性となることを抑制することができると共に、容量素子105(MOSキャパシタ)が、常に導通状態とせしめるように、容量線115に印加する電位を制御することが可能であるため、半導体装置の電気特性及び信頼性を向上させることができる。

#### [0194]

また、絶縁膜131上に設けられる絶縁膜132として、窒化絶縁膜を用いることで、外部から水素や水などの不純物が、酸化物半導体膜の積層膜111及び酸化物半導体膜の積層膜119に侵入することを抑制できる。さらには、絶縁膜132として、水素含有量が少ない窒化絶縁膜を設けることで、トランジスタ103及び容量素子105(MOSキャパシタ)の電気特性変動を抑制することができる。

#### [0195]

また、画素101内に容量素子105を大きく(大面積に)形成することができる。従って、開口率を低減させず、又は開口率を向上させつつ、電荷容量を大きくした半導体装置を得ることができる。また、開口率を向上することによって表示品位の良い半導体装置を得ることができる。

### [0196]

### (実施の形態6)

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用すること ができる。電子機器としては、テレビ、モニタ等の表示装置、照明装置、デスクトップ型 或いはノート型のパーソナルコンピュータ、ワードプロセッサ、DVD(Digital Versatile Disc)などの記録媒体に記憶された静止画又は動画を再生す る画像再生装置、ポータブルCDプレーヤ、ラジオ、テープレコーダ、ヘッドホンステレ オ、ステレオ、コードレス電話子機、トランシーバ、携帯電話、自動車電話、携帯型ゲー ム機、電卓、携帯情報端末、電子手帳、電子書籍、電子翻訳機、音声入力機器、ビデオカ メラ、デジタルスチルカメラ、電気シェーバ、電子レンジ等の高周波加熱装置、電気炊飯 器、電気洗濯機、電気掃除機、エアコンディショナーなどの空調設備、食器洗い器、食器 乾燥器、衣類乾燥器、布団乾燥器、電気冷蔵庫、電気冷凍庫、電気冷凍冷蔵庫、DNA保 存用冷凍庫、煙感知器、放射線測定器、透析装置等の医療機器、などが挙げられる。さら に、誘導灯、信号機、ベルトコンベア、エレベータ、エスカレータ、産業用ロボット、電 力貯蔵システム等の産業機器も挙げられる。また、石油を用いたエンジンや、非水系ニ 電池からの電力を用いて電動機により推進する移動体なども、電子機器の範疇に含まれる ものとする。上記移動体として、例えば、電気自動車(EV)、内燃機関と電動機を併せ 持ったハイブリッド車(HEV)、プラグインハイブリッド車(PHEV)、これらのタ イヤ車輪を無限軌道に変えた装軌車両、電動アシスト自転車を含む原動機付自転車、自動 ニ輪車、電動車椅子、ゴルフ用カート、小型又は大型船舶、潜水艦、ヘリコプター、航空 機、ロケット、人工衛星、宇宙探査機や惑星探査機、宇宙船が挙げられる。これらの電子 機器の具体例を図12、及び図13に示す。

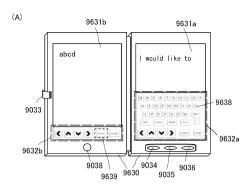

### [0197]

図12(A)及び図12(B)は2つ折り可能なタブレット型端末である。図12(A)は、開いた状態であり、タブレット型端末は、筐体9630、表示部9631a、表示部9631b、表示モード切り替えスイッチ9034、電源スイッチ9035、省電力モード切り替えスイッチ9036、留め具9033、操作スイッチ9038、を有する。

## [0198]

図12(A)及び図12(B)に示すような携帯機器においては、画像処理や演算処理を行うCPUが使用されている。そのCPUに実施の形態4に示したCPUを用いることが可能であり、用いた場合、携帯機器の消費電力を低減することができる。

#### [0199]

また、表示部9631a、9631bは、実施の形態5に示した表示装置を用いることができ、用いた場合、信頼性を向上することができる。

10

20

30

40

#### [0200]

また、表示部9631aは、一部をタッチパネルの領域9632aとすることができ、表示された操作キー9638にふれることでデータ入力をすることができる。なお、表示部9631aにおいては、一例として半分の領域が表示のみの機能を有する構成、もう半分の領域がタッチパネルの機能を有する構成を示しているが該構成に限定されない。表示部9631aの全ての領域がタッチパネルの機能を有する構成としても良い。例えば、表示部9631aの全面をキーボードボタン表示させてタッチパネルとし、表示部9631bを表示画面として用いることができる。

### [0201]

また、表示部9631bにおいても表示部9631aと同様に、表示部9631bの一部をタッチパネルの領域9632bとすることができる。また、タッチパネルのキーボード表示切り替えボタン9639が表示されている位置に指やスタイラスなどでふれることで表示部9631bにキーボードボタン表示することができる。

### [0202]

また、タッチパネルの領域9632aとタッチパネルの領域9632bに対して同時にタッチ入力することもできる。

### [0203]

また、表示モード切り替えスイッチ9034は、縦表示又は横表示などの表示の向きを切り替え、白黒表示やカラー表示の切り替えなどを選択できる。省電力モード切り替えスイッチ9036は、タブレット型端末に内蔵している光センサで検出される使用時の外光の光量に応じて表示の輝度を最適なものとすることができる。タブレット型端末は光センサだけでなく、ジャイロ、加速度センサ等の傾きを検出するセンサなどの他の検出装置を内蔵させてもよい。

#### [0204]

また、図12(A)では表示部9631bと表示部9631aの表示面積が同じ例を示しているが特に限定されず、一方のサイズともう一方のサイズが異なっていてもよく、表示の品質も異なっていてもよい。例えば一方が他方よりも高精細な表示を行える表示パネルとしてもよい。

### [0205]

図12(B)は、閉じた状態であり、タブレット型端末は、筐体9630、太陽電池9633、充放電制御回路9634、バッテリー9635、DCDCコンバータ9636を有する。なお、図12(B)では充放電制御回路9634の一例としてバッテリー9635、DCDCコンバータ9636を有する構成について示している。

### [0206]

なお、タブレット型端末は2つ折り可能なため、未使用時に筐体9630を閉じた状態にすることができる。従って、表示部9631a、表示部9631bを保護できるため、耐久性に優れ、長期使用の観点からも信頼性の優れたタブレット型端末を提供できる。

### [0207]

また、この他にも図12(A)及び図12(B)に示したタブレット型端末は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報をタッチ入力操作又は編集するタッチ入力機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。

## [0208]

タブレット型端末の表面に装着された太陽電池9633によって、電力をタッチパネル、表示部、又は映像信号処理部等に供給することができる。なお、太陽電池9633は、筐体9630の片面又は両面に設けることができ、バッテリー9635の充電を効率的に行う構成とすることができる。なおバッテリー9635としては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。

### [0209]

50

10

20

30

20

30

40

50

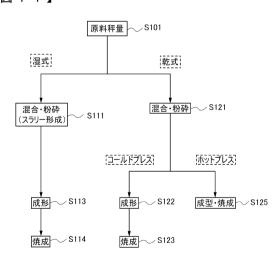

また、図12(B)に示す充放電制御回路9634の構成、及び動作について図12(C)にプロック図を示し説明する。図12(C)には、太陽電池9633、バッテリー9635、DCDCコンバータ9636、コンバータ9637、スイッチSW1乃至SW3、表示部9631について示しており、バッテリー9635、DCDCコンバータ9636、コンバータ9637、スイッチSW1乃至SW3が、図12(B)に示す充放電制御回路9634に対応する箇所となる。

#### [0210]

まず外光により太陽電池9633により発電がされる場合の動作の例について説明する。太陽電池で発電した電力は、バッテリー9635を充電するための電圧となるようDCDCコンバータ9636で昇圧又は降圧がなされる。そして、表示部9631の動作に太陽電池9633からの電力が用いられる際にはスイッチSW1をオンにし、コンバータ9637で表示部9631に必要な電圧に昇圧又は降圧をすることとなる。また、表示部9631での表示を行わない際には、SW1をオフにし、SW2をオンにしてバッテリー9635の充電を行う構成とすればよい。

#### [0211]

なお太陽電池9633については、発電手段の一例として示したが、特に限定されず、圧電素子(ピエゾ素子)や熱電変換素子(ペルティエ素子)などの他の発電手段によるバッテリー9635の充電を行う構成であってもよい。例えば、無線(非接触)で電力を送受信して充電する無接点電力伝送モジュールや、また他の充電手段を組み合わせて行う構成としてもよい。

#### [0212]

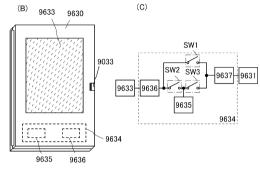

図13(A)において、テレビジョン装置8000は、筐体8001に表示部8002が組み込まれており、表示部8002により映像を表示し、スピーカ部8003から音声を出力することが可能である。

#### [0213]

また、表示部8002は、実施の形態5に示した表示装置を用いることができ、用いた場合、信頼性を向上することができる。

#### [0214]

テレビジョン装置8000は、受信機やモデムなどを備えていてもよい。テレビジョン装置8000は、受信機により一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線又は無線による通信ネットワークに接続することにより、一方向(送信者から受信者)又は双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

#### [0215]

また、テレビジョン装置8000は、情報通信を行うためのCPUや、メモリを備えていてもよい。テレビジョン装置8000は、実施の形態4に示したCPUを用いることが可能である。

### [0216]

図13(A)において、室内機8200及び室外機8204を有するエアコンディショナーは、実施の形態6のCPUを用いた電子機器の一例である。具体的に、室内機8200は、筐体8201、送風口8202、CPU8203等を有する。図13(A)において、CPU8203が、室内機8200に設けられている場合を例示しているが、CPU8203は室外機8204に設けられていてもよい。或いは、室内機8200と室外機8204の両方に、CPU8203が設けられていてもよい。実施の形態4に示したCPUをエアコンディショナーのCPUに用いることによって省電力化が図れる。

### [0217]

図13(A)において、電気冷凍冷蔵庫8300は、酸化物半導体を用いたCPUを備える電子機器の一例である。具体的に、電気冷凍冷蔵庫8300は、筐体8301、冷蔵室用扉8302、冷凍室用扉8303、CPU8304等を有する。図13(A)では、CPU8304が、筐体8301の内部に設けられている。実施の形態4に示したCPUを

50

電気冷凍冷蔵庫8300のCPU8304に用いることによって省電力化が図れる。

### [0218]

図13(B)において、電子機器の一例である電気自動車の例を示す。電気自動車970 0には、二次電池9701が搭載されている。二次電池9701の電力は、制御回路97 02により出力が調整されて、駆動装置9703に供給される。制御回路9702は、図 示しないROM、RAM、CPU等を有する処理装置9704によって制御される。実施 の形態4に示したCPUを電気自動車9700のCPUに用いることによって省電力化が 図れる。

### [0219]

駆動装置9703は、直流電動機若しくは交流電動機単体、又は電動機と内燃機関と、を 組み合わせて構成される。処理装置9704は、電気自動車9700の運転者の操作情報 (加速、減速、停止など)や走行時の情報(上り坂や下り坂等の情報、駆動輪にかかる負 荷情報など)の入力情報に基づき、制御回路9702に制御信号を出力する。制御回路9 702は、処理装置9704の制御信号により、二次電池9701から供給される電気エ ネルギーを調整して駆動装置9703の出力を制御する。交流電動機を搭載している場合 は、図示していないが、直流を交流に変換するインバータも内蔵される。

#### [0220]

1 1 3

1 1 3 a

1 1 5

1 1 7

導電膜

容量線

開口

ドレイン電極

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

```

【符号の説明】

20

[0221]

1 0 a

スパッタ装置

1 0 b

スパッタ装置

1 0 c

スパッタ装置

1 1

基板供給室

1 2 a

ロードロック室

1 2 b

ロードロック室

1 3

搬送室

1 4

カセットポート

1 5

基板加熱室

1 6

30

基板加熱室

1 0 0

画素部

1 0 1

画素

1 0 2

基板

1 0 3

トランジスタ

1 0 4

走查線駆動回路

1 0 5

容量素子

1 0 6

信号線駆動回路

1 0 7

走査線

ゲート電極

1 0 7 a

40

1 0 8

液晶素子

1 0 9

信号線

ソース電極

109a

1 1 1

積層膜

1 1 1 a

酸化物半導体膜

1 1 1 b

酸化物半導体膜

1 1 1 c

酸化物半導体膜

```

| 1 1 9            | 積層膜                      |    |

|------------------|--------------------------|----|

| 1 2 1            | 画素電極                     |    |

| 1 2 3            | 開口                       |    |

| 1 2 5            | 導電膜                      |    |

| 1 2 7            | ゲート絶縁膜                   |    |

| 1 2 9            |                          |    |

| 1 3 1            | 絶縁膜                      |    |

| 1 3 2            | 絶縁膜                      |    |

| 1 5 0            | 基板                       |    |

| 1 5 2            | 遮光膜                      | 10 |

| 1 5 4            | 対向電極                     |    |

| 1 5 6            | 絶縁膜                      |    |

| 1 5 8            | 絶縁膜                      |    |

| 1 6 0            | 液晶層                      |    |

| 3 0 0            | 基板                       |    |

| 3 0 1            | ゲート電極                    |    |

| 3 0 2            | 素子分離絶縁膜                  |    |

| 3 0 3            | ゲート絶縁膜                   |    |

| 3 0 4            | 電極層                      |    |

| 3 0 6            | 配線層                      | 20 |

| 3 0 7 a          | 導電膜                      |    |

| 3 0 7 b          | 導電膜                      |    |

| 3 0 7 c          | 導電膜                      |    |

| 3 0 8            | 層間絶縁膜                    |    |

| 3 0 9            | 配線層                      |    |

| 3 1 0            | バリア層                     |    |

| 3 1 1            | トランジスタ                   |    |

| 3 1 2            | 層間絶縁膜                    |    |

| 4 0 0            | 基板                       |    |

| 4 0 1            | ゲート電極                    | 30 |

| 4 0 2 a          | ゲート絶縁膜                   |    |

| 4 0 2 b          | ゲート絶縁膜                   |    |

| 4 0 2 5          | 積層膜                      |    |

| 4 0 3 a          | 酸化物半導体膜                  |    |

| 4 0 3 b          | 酸化物半導体膜                  |    |

| 4 0 3 b          | 酸化物半導体膜                  |    |

| 4 0 5 a          | 電極層                      |    |

| 4 0 5 b          | 電極層                      |    |

| 407              |                          |    |

| 4 0 7<br>4 0 7 a | 保護絶縁膜                    | 40 |

| 4 0 7 a          | 保護絶縁膜                    |    |

| 4075             |                          |    |

| 4 0 8            | 保 護 絶 縁 膜<br>ト ラ ン ジ ス タ |    |

| 4 1 1            | トランジスタ<br>トランジスタ         |    |

| 4 1 1            |                          |    |

| 4 1 2            | トランジスタ                   |    |

| 4 3 4            | 配線層                      |    |

| 4 3 5<br>4 9 1   | 絶縁膜                      |    |

|                  | ゲート電極                    |    |

| 8 0 1            | トランジスタ                   | 50 |

| 8 0 2            | トランジスタ                   | 50 |

```

8 0 3

トランジスタ

8 0 4

トランジスタ

8 1 1

トランジスタ

8 1 2

トランジスタ

8 1 3

トランジスタ

8 1 4

トランジスタ

1 1 4 1

スイッチング素子

1 1 4 2

メモリセル

1 1 4 3

メモリセル群

ROMTUターフェース

10

1 1 8 9

1 1 9 0

基板

1 1 9 1

ALU

1 1 9 2

ALUコントローラ

1 1 9 3

インストラクションデコーダ

インタラプトコントローラ

1 1 9 4

1 1 9 5

タイミングコントローラ

1 1 9 6

レジスタ

1 1 9 7

レジスタコントローラ

1 1 9 8

バスインターフェース

20

1 1 9 9

ROM

8 0 0 0

テレビジョン装置

8 0 0 1

筐体

8 0 0 2

表示部

8 0 0 3

スピーカ部

8 2 0 0

室内機

8 2 0 1

筐体

8 2 0 2

送風口

8 2 0 3

CPU

8 2 0 4

室外機

30

8 3 0 0

電気冷凍冷蔵庫

8 3 0 1

筐体

8 3 0 2

冷蔵室用扉

8 3 0 3

冷凍室用扉

8 3 0 4

CPU

9 0 3 3

留め具

9 0 3 4

スイッチ

9 0 3 5

電源スイッチ

9 0 3 6

スイッチ

9 0 3 8

操作スイッチ

40

9 6 3 0

筐体

9 6 3 1

表示部

9 6 3 1 a

表示部

9 6 3 1 b

表示部

9 6 3 2 a

領域

9 6 3 2 b

領域

9 6 3 3

太陽電池

9 6 3 4

充放電制御回路

9 6 3 5

バッテリー

DCDCコンバータ

9 6 3 6

50

9 6 3 7

コンバータ

```

| 9 | 6 | 3 | 8 | 操 作 キ ー |

|---|---|---|---|---------|

| 9 | 6 | 3 | 9 | ボタン     |

| 9 | 7 | 0 | 0 | 電気自動車   |

| 9 | 7 | 0 | 1 | 二次電池    |

| 9 | 7 | 0 | 2 | 制御回路    |

| 9 | 7 | 0 | 3 | 駆動装置    |

| 9 | 7 | 0 | 4 | 処理装置    |

# 【図2】

【図3】

【図4】

【図5】

【図6】

(A)

(B)

# 【図7】

# 【図8】 (A)

(B)

107

~103

# 【図9】

VSS (

# 【図10】

【図11】

【図12】

【図13】

【図14】

### フロントページの続き

# (56)参考文献 特開2012-134475(JP,A)

特開2012-084851(JP,A)

特開2011-138934(JP,A)

特開2011-228689(JP,A)

特開2012-054547(JP,A)

特開2012-134467(JP,A)

国際公開第2005/021436(WO,A1)

特開2012-064932(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 29/786

G02F 1/1368