(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-5809

(P2007-5809A)

(43) 公開日 平成19年1月11日(2007.1.11)

| (51) Int.C1.                  | F 1        | テーマコード (参考) |

|-------------------------------|------------|-------------|

| <b>HO1L 21/3205 (2006.01)</b> | HO1L 21/88 | T 5FO33     |

| <b>HO1L 23/52 (2006.01)</b>   | HO1L 23/12 | 5O1P        |

| <b>HO1L 23/12 (2006.01)</b>   | HO1L 21/92 | 6O4R        |

| <b>HO1L 21/60 (2006.01)</b>   |            |             |

審査請求 未請求 請求項の数 23 O L (全 37 頁)

|              |                              |          |                                                            |

|--------------|------------------------------|----------|------------------------------------------------------------|

| (21) 出願番号    | 特願2006-173775 (P2006-173775) | (71) 出願人 | 506218642<br>米輯電子股▲分▼有限公司<br>台灣新竹科學工業園區園區二路47號30<br>1/302室 |

| (22) 出願日     | 平成18年6月23日 (2006.6.23)       | (72) 発明者 | 弁理士 服部 雅紀<br>林 茂雄<br>台灣新竹市金山十街28号                          |

| (31) 優先権主張番号 | 60/693,549                   | (72) 発明者 | 周 健康<br>台灣台南縣新化鎮全興里12鄰竹子脚24<br>7号之72                       |

| (32) 優先日     | 平成17年6月24日 (2005.6.24)       | (72) 発明者 | 陳 科宏<br>台灣高雄市三民区遼寧一街104号                                   |

| (33) 優先権主張国  | 米国(US)                       |          |                                                            |

最終頁に続く

(54) 【発明の名称】線路デバイスの製造方法

## (57) 【要約】

【課題】ストレスリリーフと接触窓構造の間隔距離の微小化を可能にする線路デバイス構造の製作過程及びその構造を提供する。

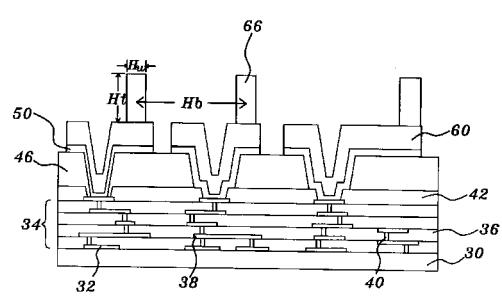

【解決手段】基板と、第一金属柱体68と、第二金属柱体と、を備え、第一金属柱体68は、基板上に位置し、第一金属柱体68の最大横寸法Hwを第一金属柱体68の高度Htで割ると4より小さく、かつ第一金属柱体68の高度が20μmから300μmの間であって、第二金属柱体は、基板上に位置し、第二金属柱体の最大横寸法を第二金属柱体の高度で割ると4より小さく、かつ第一金属柱体の中心点から第二金属柱体の中心点までの距離Hbが10μmから250μmの間である。

【選択図】図7a

**【特許請求の範囲】****【請求項 1】**

線路デバイス構造であって、

基板と、第一金属柱体と、第二金属柱体と、を備え、

第一金属柱体は、基板上に位置し、前記第一金属柱体の最大幅を第一金属柱体の高さで割ると4より小さく、かつ第一金属柱体の高さが20μmから300μmの間であって、

第二金属柱体は、基板上に位置し、前記第二金属柱体の最大幅を第二金属柱体の高さで割ると4より小さく、かつ第一金属柱体の高さが20μmから300μmの間であって、かつ前記第一金属柱体の中心点から前記第二金属柱体の中心点までの距離が10μmから250μmの間であることを特徴とする線路デバイス構造。

10

**【請求項 2】**

厚さ20μmから300μmの第一重合物層を前記基板上に形成させ、かつ前記第一金属柱体及び前記第二金属柱体を被覆することを特徴とする請求項1に記載の線路デバイス構造。

**【請求項 3】**

前記第一金属柱体は厚さ30μmから100μmの金層を備えることを特徴とする請求項1に記載の線路デバイス構造。

**【請求項 4】**

前記第一金属柱体は厚さ30μmから100μmの銅層を備えることを特徴とする請求項1に記載の線路デバイス構造。

20

**【請求項 5】**

金属接続線路で第一金属柱体と第二金属柱体とを接続することを特徴とする請求項1に記載の線路デバイス構造。

**【請求項 6】**

前記基板は、半導体基板、前記半導体基板上に位置する第一金属構造、金属線路上に位置しつつ窒化シリコン化合物含有の保護層、前記保護層上に位置する第二金属構造、及び前記保護層内に位置する開口が第一金属構造を露出する第一パッドを備え、

前記第二金属構造は第一パッドと接続する第二パッドを備え、かつ前記第一パッドの見下ろし図から見た位置は、前記第二パッドの見下ろし図から見た位置とは違って、前記第一金属柱体は第二パッド上に位置することを特徴とする請求項1に記載の線路デバイス構造。

30

**【請求項 7】**

前記第一金属柱体上に位置する突出塊を備え、前記突出塊は事前に形成した外部回路と接続し、突出塊は厚さ10μmから30μmの金層を備えることを特徴とする請求項1に記載の線路デバイス構造。

**【請求項 8】**

前記第一金属柱体上に位置する突出塊を備え、前記突出塊は事前に形成した外部回路と接続し、突出塊は厚さ10μmから150μmの錫はんだ層を備えることを特徴とする請求項1に記載の線路デバイス構造。

40

**【請求項 9】**

前記第一金属柱体上に位置するパッドを備え、前記パッドの最大幅は、前記第一金属柱の最大幅より大きく、前記パッドはワイヤー製作過程で製作したワイヤーとの接続に用いられることを特徴とする請求項1に記載の線路デバイス構造。

**【請求項 10】**

前記第一金属柱体の頂面はワイヤー製作過程で製作したワイヤーとの接続に用いられることを特徴とする請求項1に記載の線路デバイス構造。

**【請求項 11】**

前記第一金属柱体及び前記第二金属柱体を接続する金属コイルを備えることを特徴とする請求項1に記載の線路デバイス構造。

**【請求項 12】**

50

第二金属構造及び突出塊を備え、前記第二金属構造は前記第一金属柱体と接続するパッドを備え、かつ前記パッドの見下ろし図から見た位置は、前記第一金属柱体の見下ろし図から見た位置とは違って、前記突出塊はパッド上に位置し、事前に形成した外部回路と接続し、前記突出塊は厚さ  $10 \mu m$  から  $30 \mu m$  の金層を備えることを特徴とする請求項 1 に記載の線路デバイス構造。

【請求項 1 3】

第二金属構造及び突出塊を備え、前記第二金属構造は基板上に位置し、前記第二金属構造は前記第一金属柱体と接続するパッドを備え、かつ前記パッドの見下ろし図から見た位置は、前記第一金属柱体の見下ろし図から見た位置とは違って、前記突出塊はパッド上に位置し、事前に形成した外部回路と接続し、前記突出塊は厚さ  $10 \mu m$  から  $30 \mu m$  の錫はんだ層を備えることを特徴とする請求項 1 に記載の線路デバイス構造。

10

【請求項 1 4】

基板上に位置する第二金属構造を備え、前記第二金属構造は前記第一金属柱体と接続するパッドを備え、かつ前記パッドの見下ろし図から見た位置は、前記第一金属柱体の見下ろし図から見た位置とは違って、前記パッドはワイヤー製作過程で製作したワイヤーとの接続に用いられることを特徴とする請求項 1 に記載の線路デバイス構造。

【請求項 1 5】

線路デバイス構造であって、

半導体基板と、第一金属柱体と、第二金属柱体と、絶縁層と、第一突出塊と、第一突出塊と、を備え、

20

第一金属柱体は、前記半導体基板上に位置し、前記第一金属柱体の最大幅を第一金属柱体の高さで割ると 4 より小さく、かつ第一金属柱体の高さが  $20 \mu m$  から  $300 \mu m$  の間であり、

第二金属柱体は、前記半導体基板上に位置し、前記第二金属柱体の最大幅を第二金属柱体の高さで割ると 4 より小さく、かつ第一金属柱体の高さが  $20 \mu m$  から  $300 \mu m$  の間であり、

30

絶縁層は、前記半導体基板上に位置し、かつ第一金属柱体及び第二金属柱体を被覆し、

第一突出塊は、前記第一金属柱体や前記絶縁層に位置し、かつ事前に形成した外部回路との接続に適し、

第二突出塊は、前記第二金属柱体や前記絶縁層に位置し、かつ事前に形成した外部回路との接続に適し、前記第一突出塊の中心点から第二突出塊の中心点までの距離は  $10 \mu m$  から  $250 \mu m$  の間であることを特徴とする線路デバイス構造。

【請求項 1 6】

前記第一突出塊の中心点から前記第二突出塊の中心点までの距離が  $100 \mu m$  から  $200 \mu m$  の間であることを特徴とする請求項 1 5 に記載の線路デバイス構造。

【請求項 1 7】

前記第一金属柱体は厚さ  $20 \mu m$  から  $300 \mu m$  の間の金層を備えることを特徴とする請求項 1 5 に記載の線路デバイス構造。

【請求項 1 8】

前記第一金属柱体は厚さ  $20 \mu m$  から  $300 \mu m$  の間の銅層を備えることを特徴とする請求項 1 5 に記載の線路デバイス構造。

40

【請求項 1 9】

前記第一金属柱体は厚さ  $10 \mu m$  から  $30 \mu m$  の間の金層を供えることを特徴とする請求項 1 5 に記載の線路デバイス構造。

【請求項 2 0】

前記第一金属柱体は厚さ  $10 \mu m$  から  $150 \mu m$  の間の錫はんだ層を備えることを特徴とする請求項 1 5 に記載の線路デバイス構造。

【請求項 2 1】

第一絶縁層の材質はポリイミドを含むことを特徴とする請求項 1 5 に記載の線路デバイス構造。

50

## 【請求項 2 2】

導体基部上に位置する第一金属構造、前記第一金属構造上に位置する窒化シリコン化合物含有の保護層、前記保護層上に位置する第二金属構造、及び前記保護層内に位置する開口が第一金属構造を露出する第一パッドを備え、前記第二金属構造は第一パッドと接続する第二パッドを備え、かつ前記第一パッドの見下ろし図から見た位置は、前記第二パッドの見下ろし図から見た位置とは違って、前記第一金属柱体は第二パッド上に位置することを特徴とする請求項 1 5 に記載の線路デバイス構造。

## 【請求項 2 3】

前記第一絶縁層上及び前記第一金属柱体上に位置する第一金属構造を備え、金属構造は第一金属柱体と接続するパッドを備え、かつ前記パッドの見下ろし図から見た位置は、前記第二パッドの見下ろし図から見た位置とは違って、前記第一突出塊は前記パッド上に位置することを特徴とする請求項 1 5 に記載の線路デバイス構造。

10

20

30

40

50

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本発明は、線路デバイスの製造方法に関し、特に I C の性能を有効に改善する線路デバイスの製造方法に関する。

## 【背景技術】

## 【0 0 0 2】

半導体ウェハは密度が持続増加かつ幾何学的な図案を縮小する I C の製造に用いられ、多層の導電層と絶縁層の構造を通して、異なる層の半導体デバイス間の内部接続と隔絶効果を提供する。例えば主動と受動デバイス・薄膜トランジスター・シーモス (CMOS)・コンデンサ・チャージャー・抵抗等の大型 I C の中において、異なる層状構造と半導体デバイス間に、数個の電磁特性接続部の増加が必要である。また同時に組立式の I C にとって、ワイヤーの大量増加も必要である。そのため、これらのワイヤーは I C チップの中にある保護層から通り抜けて、外部に露出し、最後は出力入力パッドと接続している。このワイヤーはチップパッケージングの外部接触構造と接続するために用いられる。

## 【0 0 0 3】

ウェハレベルチップスケールパッケージ (WLCSP) はいわゆるウェハレベルの方式で I C チップをパッケージする技術であって、伝統式のチップカットした後、單一ユニットのパッケージ製作過程とは異なる。ゆえにチップを單一ユニットにカットし、最終的のチップキャリヤーパッケージ前、例えばボール・グリッド・アレイ (BGA) パッケージを行う前に、WLCSPはウェハの製造・パッケージ・テストとウェーハ・レベル・バーンイン (WLB I) を整合させることができる。その長所は、占める体積と厚さを縮小するによって、より小さい寸法・より軽い重量・相対的に簡単な組立過程・全体の生産コストの低減及びより良い電磁特性が得られる。かつWLCSPは一つのデバイスをシリコン材料から顧客先までの運送過程が簡略され、I C のチップパッケージ生産量がアップされると同時に、コストも低減される。ただし、製造能力と構造の信頼度が関係しているので、非常に大きなチャレンジに直面している。

## 【0 0 0 4】

WLCSPは基本的にウェーハ作製過程中の接合デバイス作製過程とデバイス保護作製過程へ拡張するのが可能であって、WLCSPの第一ステップにおいて、半導体 I C 線路の再構成可能技術を通してポストパッシベーション (Post-Passivation) を形成させ、標準パッドの距離を広げる。そのため、低コストの半田ステンを形成させ、シルあるいは整列定位式半田は実現される。再構成可能技術の発表に対して、例えば特許文献 1 ~ 3 の申請発表者は、本発明の申請者とは同一者であって、本特許で発表しているように、一重の線路配置層は半導体構造の出力入力パッドと接続する。このRDL層はポストパッシベーションの重

合物層や弾性材質層に形成させ、マスク製作過程を利用して製造したポスト状接触窓をこのRDL層上に形成させ、本反応後形成されたポスト状接触窓の側方向は独立であって、全然支えられていないし、またフリップチップアセンブリ技術を利用して、上記反応後形成された構造体は、もう一步進んでチップキャリヤーパッケージに組合わされている。このポストパッセーション構造とそれに対応する製作過程は、ICパッケージの中に存在する間隔距離の問題を解決改善できるとしても、しかしインテグレーテッド規模が持続増加に要求されたICは、もっと厳しく制限されるはずであって、またストレス誘導によって生じたダメージに対しても、潜在的なリスクである。

## 【0005】

特許文献4に、別のRDL層のポストパッセーション構造のWLCSPを含んでいる。このRDL層はポストパッセーションの上の重合物層に形成させ、RDL層上を別の重合物層で被せ、かつこの重合物層はエッチングやドリルによってミクロビアス(Micro-vias)を形成させ、更に金属をミクロビアスの穴を充填して内部接続を形成させ、いわゆる導電柱体である。しかし、上重合物層と下重合物層は、RDL層と接触させないために、一つのクロム-銅層によって隔離され、もう一つは上記の導電柱体の突出した尾端にある無電気めっき・スクリーンプリンティング或いはステンシルされた錫鉛に接着されている。導電柱体は重合物層の外部へ延伸しているし、また上記構造の頂部表面はスムーズではないので、高解析度のリソグラフィーを達成できない前提で、導電柱体でミクロビアスを形成させ、また電気めっきで錫鉛を形成することは達成されず、最終的にはICパッケージの中にある接触窓の間隔距離は制限される。しかもこの制限は重合物層の厚さ増加につれて、益々目立つようになる。しかし重合物層の厚さ増加につれて、満足されるストレスリリーフを提供している。

## 【0006】

この点について、下記に述べる。また上記のように、下重合物層は上重合物層と隔離されているために、下重合物層は単独してより良いストレスリリーフを提供できず、かつ現在の下重合物層の厚さはRDL層の側方移動を低減するため、薄く製造されるので、ストレスリリーフはいくらか弱くなつて、この問題は下記で論議する。

## 【0007】

構造の信頼度の中の一つのチャレンジは、充分なストレスリリーフを提供するによって、上記のWLCSPで形成された多層構造を供給する。それには半導体ICチップと定額外のポストパッセーション構造が含まれる。例で説明すると、保護層上に結合した薄膜は双せん断応力に影響され、かつこの応力は熱に誘導されて生じた。式(1)の中にポストパッセーションの中にある双せん断応力の数学理論模擬方程式を示し、式の中にICチップの中のシリコン基材構造の物理パラメーターを提供する。

## 【0008】

## 【数1】

$$\sigma_{ppt} = \frac{1}{6R} \frac{Y_s x_{Si}^2}{(1-v_{Si})x_{ppt}} \quad (1)$$

40

## 【0009】

ppt: ポストパッセーションの薄膜の中にある双せん断応力

R: シリコン基板が熱で湾曲する曲率半径

Y<sub>s</sub>: シリコン基板のヤング率

v<sub>Si</sub>: シリコン基板のポアソン比

x<sub>Si</sub>: シリコン基板の厚さ

## 【0010】

x<sub>Si</sub>: ポストパッセーション薄膜的厚さ

上記の方程式より、シリコン基板のポアソン比が上昇する以外に、二種類の方法で双せん

50

ん断応力を降下させることができる。

(a)  $\times S_i$  を低下させる。これはシリコン基板をもっと薄く置くことを意味する。或いは (b)  $\times p_{p,t}$  を増大する。これはポストパッセーション構造の厚さを増加させることを意味する。

#### 【0011】

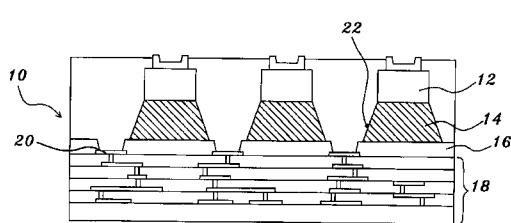

図1は周知のポストパッセーション構造10であって、それには一つのRDL層12と一つのストレスリリーフする重合物層14を含む。このストレスリリーフする重合物層14はまたストレスバッファー層(stress buffer layer)とも呼ばれている。半導体ICチップ18の表面の保護層16上に形成し、その中の重合物層14は弾性材料・エポキシ樹脂・低誘電率材料或いはその他の重合物材料が使用される。弾性材料は主に接合構造に充分な機械弾性を提供するためであって、上記の式(1)の中に推論した結果を見ると、ICチップ18の上に重合物層14を被せると、ICチップ18の上の構造に形成させたストレスは、全て吸収また緩衝されるので、ICチップ18に発生する局部ダメージが低減され、特に精密かつ複雑なICチップ18電路にとって、ポストパッセーション構造10の信頼度はこれによって上昇する。また式(1)の中の関係式に従えば、緩衝効果の表現は重合物層14の厚さの増加につれて良くなる。

#### 【0012】

しかし厚い重合物層14の利用時に、よく一つの問題に直面する。図1で示しているRDL層12は通常銅で構成され、ICチップ18の出力入力パッド20を外部回路と接続する。パッド20の最頂端に、同時にまた別々に錫鉛の突出塊或いは銅導電柱体が形成された時、RDL層12は真下層のパッケージ構造は非常に緊密に連結され、その中のパッケージ構造は一つのチップキャリヤであっても良いため、RDL層12は重合物層14によって、一定傾斜度を持った斜面22と定義される。このRDL層12は出力入力パッド20を形成する一つのより低いIC平面から、徐々に一つのより高いIC平面へ上昇する。例えば、重合物層14頂部にある斜面22は、金属化ステップで厚い重合物層14開口部に被ることによって決定する。実際的な応用において、斜面22の傾斜度は各重合物層14の異なる開口によって変わるし、各開口は実際の製造過程の条件と重合物本体の根本的な物理性質と特性によって決定される。例えば、材料表面にあるエネルギーと関連する濡れ接触角、例で説明すると、多くの状況において、IC保護層16上にある重合物層14斜面22の傾斜度は約45度であるので、RDL層12は一定量の側方移動によって、ICの中のパッド20から重合物層14の頂端まで延伸する。ゆえに、この側方移動はRDL層12を仕組み時、一定量の許容値を許容するようになった。最終的に、この許容された許容値は、異なる開口の重合物層14によって形成された各種類の斜面22の傾斜率を許容し、各RDL層の側方移動は異なっているので、隣同士の接触窓間の間隔距離は制限され、この中の接触窓は共同また別々に錫鉛の突出塊或いは銅体に定義され、かつ接触窓構造と保護層上の開口との距離はそれにつれて増加するため、ポストパッセーション構造と真下層のパッケージ構造との間は、微小間隔距離が維持されない。逆にもし厚い重合物層14が採用されない場合に、ストレスの緩衝不足によって、精密なICチップの中の電路はストレス誘導によって、ダメージを来たす。また大きい導電柱体にとって、側方支持力が不足であるため、出力入力構造の間隔距離は制限される。しかし大きい導電柱体構造は充分な距離を提供するかとが可能で、出力入力パッド20とICチップ18の中の電磁特性電路との間に产生する結合静電容量(coupling Capacitance)を降下させることができるために、大きな導電柱体構造は必要である。

#### 【0013】

上に提出した議題は、ポストパッセーション構造上の接触窓構造との間隔距離縮減によって、来たした問題に対して実現可能であって、またこのため、ICの中のインテグレーテッド規模が阻害されている。

この点を考慮に入れて、WLCSP及びそれと対応する製作過程を提出ことによって、ストレスリリーフを改善すると同時に、接触窓構造の間隔距離の微小化を達成する。

#### 【0014】

10

20

30

40

50

【特許文献1】米国特許第6,645,136号

【特許文献2】米国特許第6,784,087号

【特許文献3】米国特許第6,818,545号

【特許文献4】米国特許第6,103,552号

【発明の開示】

【発明が解決しようとする課題】

【0015】

本発明の主な目的は、線路デバイスの製造方法を提供し、それはストレスリリーフと接触窓構造の間隔距離の微小化を提供することができる。本発明に基づいて、その間隔距離は250μm以下であり、かつピンホール数を400個以下の目標に抑えることも達成できる。10

本発明のもう一つの目的は、線路デバイスの製造方法を提供し、それは一つのRDLに支持されているポストパッセーション構造を含み、それは保護層上に、相対厚さがより薄い支持層を形成させ、例えば重合物層によって、RDL構造間の隙間を支持し、また相対厚さがより厚い支持層を形成する。例えば重合物層によって、隣同士に位置する層状パッキング構造間のRDL構造間にある隙間が支持される。

【課題を解決するための手段】

【0016】

本発明は上記の目的のために、線路デバイスの製造方法を提供する。その製作過程に半導体基部とその半導体基部の上に位置する金属層及びその半導体基部の上とその金属層上に位置する第一重合物層を提供する。その第一重合物層を研磨する。第二重合物層をその第一重合物層上に形成させ、第二重合物層中の一つの開口にその金属層を露出する。20

【0017】

本発明は上記の目的のために、線路デバイスの製造方法を提供する。その製作過程に半導体基部とその半導体基部の上に位置する金属柱を提供し、その金属柱の最大幅を第一金属柱及び第二金属柱の高さで割ると4より小さく、また第一金属柱の高さは20μmから300μmである。半導体基部の上に第一絶縁層を形成し、かつその金属柱を被覆する。第一絶縁層上に第二絶縁層を形成し、第二絶縁層の開口に第一金属柱を露出する。

【0018】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体ウェハとその半導体ウェハの上に位置する第一金属層及びその半導体ウェハとその第一金属層上に位置する一つの重合物層を提供し、その中の半導体ウェハは多数のトランジスターを含み、その多数のトランジスターは3価や5価イオンをその半導体ウェハまで混ぜ合う。その重合物層を研磨する。その重合物層とその第一金属層上に一つの第二金属層を形成する。その第二金属層上に一つの図案定義層を形成させ、その図案定義層中にある一つの開口に第二金属層を露出する。その開口に露出する第二金属層上に一つの第三金属層を形成する。その図案定義層を除去する。その第三金属層下以外の第二金属層を除去する。30

【0019】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体ウェハとその半導体ウェハの上に位置する一つの金属柱を提供し、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmであって、その中の半導体ウェハは多数のトランジスターを含み、その多数のトランジスターは3価や5価イオンをその半導体ウェハまで混ぜ合う。一つの絶縁層をその半導体ウェハの上に形成させ、かつその金属柱を被覆する。一つの第一金属層をその絶縁層及びその金属柱の上に形成する。その第一金属層上に一つの図案定義層を形成させ、その図案定義層中にある一つの開口に第一金属層を露出する。その開口に露出する第一金属層上に一つの第二金属層を形成する。その図案定義層を除去する。その第二金属層下以外の第一金属層を除去する。40

【0020】

10

20

30

40

50

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの第一金属層及びその半導体基部とその第一金属層上に一つの重合物層を提供する。その重合物層を研磨する。一つの突出塊をその第一金属層上に形成させ、形成された突出塊はその重合物層と第一金属層上に一つの第二金属層を含む。その第二金属層上に一つの図案定義層を形成させ、その図案定義層中にある一つの開口に第二金属層を露出する。その開口に露出する第二金属層上に一つの第三金属層を形成する。その図案定義層を除去する。その第三金属層下以外の第二金属層を除去する。

#### 【0021】

本発明は上記の目的のために、一種の線路構造の製作デバイス過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属柱を提供し、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの絶縁層をその半導体基部の上に形成させ、かつその金属柱を被覆する。その絶縁層内部に一つの開口を形成させ、その金属柱を露出する。

#### 【0022】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属層及びその半導体基部とその金属層上に位置する重合物層を提供する。その重合物層を研磨する。その重合物層内部に一つの開口を形成させ、その金属層を露出する。

#### 【0023】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属柱を提供し、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの絶縁層をその半導体基部の上に形成させ、かつその金属柱を被覆する。その絶縁層をエッチングする。

#### 【0024】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属柱及びその半導体基部とその金属柱の上に位置する一つの重合物層を提供する。重合物層を除去し、その金属柱の一つの頂面を露出させ、かつその頂面からその重合物層間の高さは10μmから150μmである。

#### 【0025】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属層及びその半導体基部とその金属層上に位置する一つの重合物層を提供する。その重合物層を研磨する。その重合物層をエッチングする。

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部を提供する。一つの重合物層をその半導体基部の上に提供し、その重合物層内の一つ開口の深度は10μmから300μmである。一つの金属層をその重合物層上及びその開口内に形成させ、開口以外のその金属層を除去する。

#### 【0026】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属柱を提供し、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの絶縁層をその半導体基部の上に形成させ、かつその金属柱を被覆する。一つの突出塊をその金属層上に形成する。その突出塊は外部回路と接続する。その半導体基部と外部回路間に一つの第二絶縁層を形成する。

#### 【0027】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出

10

20

30

40

50

し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属層及びその半導体基部上とその金属層上に位置する一つの第一重合物層を提供する。その第一重合物層を研磨する。一つの突出塊をその金属層に形成する。その突出塊は外部回路と接続する。その半導体基部と外部回路間に一つの第二重合物層を形成する。

## 【0028】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属層及びその半導体基部の上とその金属層上に位置する一つの第一重合物層を提供する。その第一重合物層を研磨する。一つの突出塊をその金属層上に形成させ、その突出塊は一つの電気めつき製作過程を含む。

10

## 【0029】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属柱を提供し、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの絶縁層をその半導体基部の上に形成させ、かつその金属柱を被覆する。一つの突出塊をその金属柱の上に形成する。その突出塊は一つの電気めつき製作過程を含む。

## 【0030】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属層及びその半導体基部の上とその金属層上に位置する一つの重合物層を提供する。その重合物層を研磨する。一つのワイヤー製作過程で一つのワイヤーを形成させ、その金属層の上接続する。

20

## 【0031】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部とその半導体基部の上に位置する一つの金属柱を提供し、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの絶縁層をその半導体基部の上に形成させ、かつその金属柱を被覆する。一つのワイヤー製作過程で一つのワイヤーを形成させ、その金属柱の上接続する。

30

## 【0032】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの基板を提供する。その基板の上に一つの第一金属柱を置き、その第一金属柱の最大幅をその第一金属柱の高さで割ると、4より小さく、またその第一金属柱の高さは20μmから300μmである。その基板の上に一つの第二金属柱を置き、その第二金属柱の最大幅をその第二金属柱の高さで割ると、4より小さく、またその第二金属柱の高さは20μmから300μmである。第一金属柱の中心点から第二金属柱の中心点までの距離は10μmから250μmである。

## 【0033】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部を提供する。その半導体基部の上に一つの第一金属柱を置き、その第一金属柱の最大幅をその第一金属柱の高さで割ると、4より小さく、またその第一金属柱の高さは20μmから300μmである。その半導体基部の上に一つの第二金属柱を置き、その第二金属柱の最大幅をその第二金属柱の高さで割ると、4より小さく、またその第二金属柱の高さは20μmから300μmである。一つの第二金属柱を20μmから300μmの間に置く。一つの絶縁層をその半導体基部上に置き、かつその第一及び第二金属柱を被覆する。一つの第一突出塊をその第一金属柱の上に形成する。一つの第二突出塊をその第二金属柱の上に形成させ、その第一突出塊の中心点から第二突出塊の中心点までの距離は10μmから250μmである。

40

## 【0034】

50

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部を提供する。その半導体基部の上に一つの第一金属柱を置き、その第一金属柱の最大幅をその第一金属柱の高さで割ると、4より小さく、またその第一金属柱の高さは20μmから300μmである。一つの第二金属柱をその半導体基部の上に置き、その第二金属柱の最大幅をその第二金属柱の高さで割ると、4より小さく、またその第二金属柱の高さは20μmから300μmである。一つの金属線路でその第一金属柱の頂面と第二金属柱の頂面を接続し、その金属線路の材質は金を含む。

#### 【0035】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部を提供する。その半導体基部の上に一つの第一金属柱を置き、その第一金属柱の最大幅をその第一金属柱の高さで割ると、4より小さく、またその第一金属柱の高さは20μmから300μmである。一つの第二金属柱をその半導体基部の上に置き、その第二金属柱の最大幅をその第二金属柱の高さで割ると、4より小さく、またその第二金属柱の高さは20μmから300μmである。一つの金属線路でその第一金属柱の頂面と第二金属柱の頂面を接続する。一つの重合物層を金属線路の上に置く。

#### 【0036】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部を提供する。その半導体基部の上に一つの金属柱を置き、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmであって、一つのワイヤー製作過程で一つのワイヤーを形成させ、その金属柱やその重合物層と接続する。

#### 【0037】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部を提供する。その半導体基部の上に一つの金属柱を置き、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの重合物層を金属線路の上に置き、かつその金属柱を被覆する。一つの突出塊は、その金属柱の上に形成させ、その厚さは10μmから150μmである。

#### 【0038】

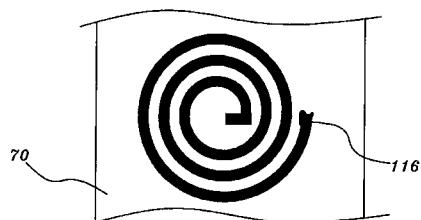

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、その製作過程に一つの半導体基部を提供する。その半導体基部の上に一つの金属柱を置き、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの重合物層を半導体基部の上に置き、かつその金属柱を被覆する。一つの金属コイルをその半導体基部の上に置き、その金属コイルの厚さは1μmから15μmである。

#### 【0039】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、それに一つの半導体基部を提供する。その半導体基部の上に一つの金属柱を置き、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの突出塊は、その金属柱の上に形成させ、その突出塊の厚さは10μmから30μmの金層を含む。

#### 【0040】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、それに一つの半導体基部を提供する。その半導体基部の上に一つの金属柱を置き、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの突出塊は、その金属柱の上に形成させ、その突出塊はチタン含有の一つの金層を含む。

#### 【0041】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出

10

20

30

40

50

し、それに一つの半導体基部を提供する。その半導体基部の上に一つの金属柱を置き、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの突出塊は、その金属柱の上に形成させ、その突出塊はクロム含有の一つの金層を含む。

【0042】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、それに一つの半導体基部を提供する。その半導体基部の上に一つの金属柱を置き、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの突出塊は、その金属柱の上に形成させ、その突出塊はタンタル含有の一つの金層を含む。

10

【0043】

本発明は上記の目的のために、一種の線路デバイス構造の製作過程及びその構造を提出し、それに一つの半導体基部を提供する。その半導体基部の上に一つの金属柱を置き、その金属柱の最大幅をその金属柱の高さで割ると、4より小さく、またその金属柱の高さは20μmから300μmである。一つの第一重合物層を半導体基部の上に置き、かつその金属柱を被覆する。一つの基板を置く。一つの突出塊は、その金属柱とその基板間に位置し、一つの第二重合物層はその基板とその半導体基部間に位置し、かつその突出塊を被覆する。

【0044】

以下は具体実施例と添付した図式で詳しく説明すると、本発明の目的・技術内容・特徴及び達成効果が理解しやすくなる。

【発明を実施するための最良の形態】

【0045】

本発明は一種の線路デバイス構造の製作過程及びその構造であって、半導体基部に数多くの金属柱(Post)構造を形成させ、かつ隣同士の金属柱の間隔距離は250μm以下に縮小され、下記は数種の異なる実施例について説明する。

(第一実施例)

【0046】

第一実施例の線路デバイス構造の製作過程は図2に示す。まず一つの半導体基部30を提供し、この半導体基部30の形式はシリコン基部やガリウム砒素基部(GAAS)あるいはシリコンゲルマニウム基部であって、シリコン・オン・インシュレーター(silicon-on-insulator, SOI)の基部で、半導体基部30はこの実施例の中では円形の一つの半導体ウェハであり、かつこの半導体ウェハ30は一つの主動表面があつて、半導体ウェハ30の主動表面は、5価や3価イオン(例えばホウ素イオンやリンイオン等)と通して、数個の電子デバイス32を形成させ、この電子デバイス32は金属酸化物半導体はMOSデバイス(MOS devices)やPチャンネルMOSデバイス(p-channel MOS devices)或いはnチャンネルMOSデバイス(n-channel MOS devices)またはBICMOSデバイス(BICMOS devices)やバイポーラトランジスタ(Bipolar Junction Transistor, BJT)や拡散区(Diffusion area)やレジスター(resistor)やキャパシタ(capacitor)及びCMOS等である。

30

【0047】

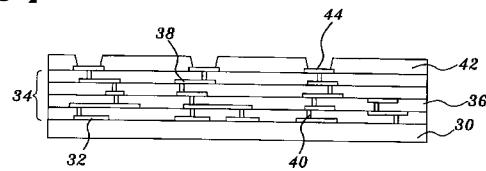

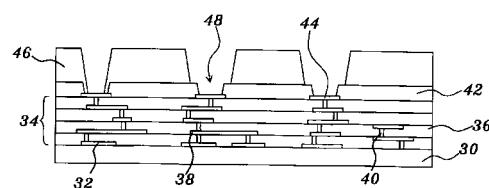

図3を参照する。半導体ウェハ30の主動表面に一つの細い接続構造34を形成させ、この細い接続構造34は複数の厚さが3μm以下の薄膜絶縁層36及び厚さが3μm以下の細い線路層38で構成され、その中の細い線路層38は銅金属材質やアルミ金属材質を選択し、薄膜絶縁層36はまた誘電体バリアとも呼ばれ、普通は化学気相法で形成させ、この薄膜絶縁層36は酸化シリコンや化学気相法のテトラエトキシシラン(TEOS)酸化物、Si<sub>x</sub>Ge<sub>y</sub>、窒化シリコン化合物或いは窒酸化シリコン化合物、またスピンドローティング法で形成されたガラス(SOG)、フッ化ガラス(FSG)、シリク層(SiLK)、ブラックダイヤ薄膜(Black Diamond)、ポリアリレンエーテル(polyarylene ether)、ポリベンゾオキサゾール(polybenzoxazole, PBO)、多孔性シリカ(porous silicon oxide)である。或いはその薄膜絶縁層36は誘電率(FPI)が3以下の材質である。

40

50

## 【0048】

複数の細い線路層38形成中、半導体ウェハ30の過程において、金属ダマシン製作過程では、まず一つの拡散阻止層を一つの薄膜絶縁層36開口内底部及び側壁上及び薄膜絶縁層36上の表面にスパッタリングし、例えば銅材質のシード層を拡散阻止層にスパッタリングした後、銅層をこのシード層に電気めっきし、また光CMP(chemical mechanical polishing, CMP)方式で薄膜絶縁層36開口外部の銅層・シード層と拡散阻止層を薄膜絶縁層36の上表面が露出するまで除去する。もう一つの方法はまずアルミ層やアルミ合金層を薄膜絶縁層36上にスパッタリングし、リソグラフィーエッチング方式でアルミ層やアルミ合金層を図案化する。この細い線路層38は薄膜絶縁層36のスルーホール40を通過してお互いに接続し、或いは電子デバイス32と接続し、細い線路層38の一般厚さは0.1μmから0.5μmであって、リソグラフィーの製作過程において、5倍(5X)ステッパー(steppe)或いはスキャナーまたより良い機械を利用して、細い線路層38を製作する。10

## 【0049】

次は化学気相法(CVD)を利用して、半導体基部30の表面に保護層42を設置し、この保護層42複数の裂け目がパッド44に露出し、これより半導体基部30内の電子デバイス32を湿気や外部のイオン性不純物(foreign ion contamination)の破壊を保護し、つまり保護層42は可動イオン(mobile ions)(例えばナトリウムイオン)・水分(moisture)・遷移金属(transition metal)(例えば金・銀・銅)及びその他の雑質(impurity)の穿通によって、保護層42下方にあるトランジスター・多結晶シリコン抵抗デバイス或いは多結晶シリコンコンデンサデバイスの電子デバイス32やを細い金属線路への破壊を防止しする。保護目的を達成するため、通常は酸化シリコン(silicon oxide)・酸化シリコン化合物・リン化シリコンガラス・窒化シリコン(silicon oxide)及び窒化シリコン(silicon oxy-nitride)で保護層42を組成する。20

## 【0050】

保護層42の第一種製作方式は、まず化学気相法を利用して、厚さ0.2μmから1.2μmの一酸化シリコン層を形成させた後、化学気相法を利用して、厚さ0.2μmから1.2μmの一酸化シリコン層をその酸化シリコン層上に形成させる。

保護層42の第二種製作方式は、まず化学気相法を利用して、厚さ0.2μmから1.2μmの一酸化シリコン層を形成させた後、プラズマ強化型の化学気相法を利用して、厚さ0.05μmから0.15μmの一酸化シリコン層をその窒酸化シリコン層上に形成させる。30

## 【0051】

保護層42の第三種製作方式は、まず化学気相法を利用して、厚さ0.05μmから0.15μmの一窒酸化シリコン層を形成させた後、化学気相法を利用して、厚さ0.2μmから1.2μmの一酸化シリコン層をその窒酸化シリコン層に形成させてから、化学気相法を利用して、厚さ0.2μmから1.2μmの一窒化シリコン層をその酸化シリコン層上に形成させる。

## 【0052】

保護層42の第四種製作方式は、まず化学気相法を利用して、厚さ0.2μmから0.5μmの一酸化シリコン層を形成させた後、スピンドルコート法(spin-coating)を利用して、厚さ0.5μmから1μmの二酸化シリコン層をその一酸化シリコン層に形成させてから、化学気相法を利用して、厚さ0.2μmから1.2μmの三窒化シリコン層をその二酸化シリコン層上に形成させる。40

## 【0053】

保護層42の第五種製作方式は、まず高密度プラズマ化学気相法(HDP-CVD)を利用して、厚さ0.5μmから2μmの一酸化シリコン層を形成させてから、化学気相法を利用して、厚さ0.2μmから1.2μmの一窒化シリコンをその酸化シリコン層の上に形成させる。

## 【0054】

保護層42の第六種製作方式は、まず厚さ0.2μmから3μmの不純物を注入していないシリコンガラス(undoped silicate glass, USG)を形成させてから、例えはテトラエトキシシラン(TEOS)酸化物・borophosphosilicateガラス(borophosphosilicate glass, PSG)或いはphosphosilicateガラス(phosphosilicate glass, PSG)等の厚さ0.5μmから3μmの絶縁層をその不純物を注入していないシリコンガラスの上に形成させた後、化学気相法を利用して、厚さ0.2μmから1.2μmの一窒化シリコン層をその絶縁層上に形成させる。

## 【0055】

保護層42の第七種製作方式は、選択的にまず化学気相法を利用して、厚さ0.05μmから0.15μmの一窒酸化シリコン層を形成させた後、また化学気相法を利用して、厚さ0.2μmから1.2μmの一窒化シリコン層をその二窒酸化シリコン層或いはその酸化シリコン層上に形成させ、それか選択的にまず化学気相法を利用して、厚さ0.05μmから0.15μmの三窒酸化シリコン層をその窒化シリコン層の上に形成させ、また化学気相法を利用して、厚さ0.2μmから1.2μmの一酸化シリコン層をその三窒酸化シリコン層或いは窒化シリコン層上に形成させる。

## 【0056】

保護層42の第八種製作方式は、まず化学気相法(PECVD)を利用して、厚さ0.2μmから1.2μm一酸化シリコン層を形成させた後、スピンドルコートィング法(spin-coating)を利用して、厚さ0.5μmから1μmの二酸化シリコン層をその一酸化シリコン層に形成させてから、化学気相法を利用して、厚さ0.2μmから1.2μmの三窒化シリコン層をその二酸化シリコン層上に形成させ、また化学気相法を利用して、厚さ0.2μmから1.2μmの一窒化シリコン層をその三酸化シリコン層上に形成させ、それから化学気相法を利用して、厚さ0.2μmから1.2μmの四酸化シリコン層をその窒化シリコン層上に形成させる。

## 【0057】

保護層42の第九種製作方式は、まず高密度プラズマ化学気相法(HDP-CVD)を利用して、厚さ0.2μmから2μmの一酸化シリコン層を形成させてから、また化学気相法を利用して、厚さ0.2μmから1.2μmの一窒化シリコン層をその一酸化シリコン層上に形成させ、それから高密度プラズマ化学気相法(HDP-CVD)を利用して、厚さ0.5μmから2μmの二酸化シリコン層をその窒化シリコン層上に形成させる。

## 【0058】

保護層42の第十種製作方式は、まず化学気相法を利用して、厚さ0.2μmから1.2μmの一酸化シリコン層を形成させてから、また化学気相法を利用して、厚さ0.2μmから1.2μmの一酸化シリコン層をその一窒化シリコン層上に形成させ、それから化学気相法を利用して、厚さ0.2μmから1.2μmの二窒化シリコン層をその酸化シリコン層上に形成させる。

保護層42の厚さは一般0.35μm以上であって、状況が良ければ、窒化シリコン層の厚さは一般0.3μm以上である。

## 【0059】

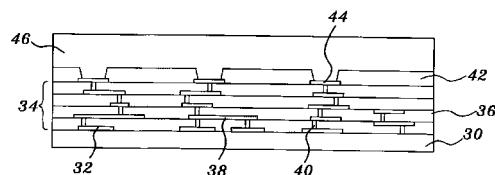

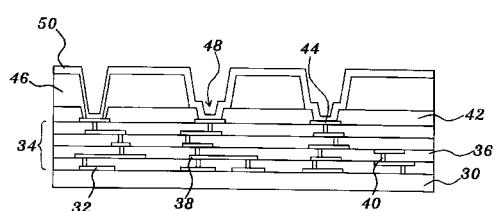

保護層42が完成した後、図4aで示すように、今度は厚さ3μmから50μmの第一重合物層46をその保護層42上形成させ、この第一重合物層46は絶縁機能を持っているし、かつこの第一重合物層46の材質は熱塑性プラスチック・熱固性プラスチック・ポリイミド(polyimide, PI)、ベンゾシクロブテン(benzo-cyclo-butene, BCB)・ポリウレタン(polyurethane)・エポキシ樹脂・ポリp-キシレン類高分子・溶接マスク材料・弹性材料或いは多孔性誘電材料等から選択する。この第一重合物層46の設置方式はホットラミネーションドライフィルム方式やスクリーンプリント或いはスピンドルコートィング方式を含む。それから図4bで示すように、エッチング方式を利用して、この第一重合物層46に対して図案化を行ない、半導体基部30上のパッド44に数多くの開口48が露出する。ここで注意することは、第一重合物層46は感光材質である場合、リソグラフィープロセス(photolithography process)を利用して、この第一重合物層46を図案化する。

10

20

30

40

50

第一重合物層 4 6 は感光材質ではない場合、リソグラフィーエッチングプロセス (photolithography process and etching process) を利用して、この第一重合物層 4 6 を図案化する。

#### 【 0 0 6 0 】

第一重合物層 4 6 を図案化した後、ベーキング加熱やマイクロウェーブ加熱或いは赤外線加熱で 200 から 320 までの温度を加熱し、あるいは加熱で 320 から 450

までの温度を加熱し、第一重合物層 4 6 を硬化 (curing) させる。硬化後の第一重合物層 4 6 の体積は縮小し、かつ第一重合物層 4 6 の含水率は 1 % 以下で、この含水率は第一重合物層 4 6 を温度 425 から 450 において、その重量変化率は 1 % 以下である。

#### 【 0 0 6 1 】

図 5 で示すように、スパッタリング方式で厚さ 400 から 7000 の一つの第一粘着 / 阻害層 50 (Adhesion / Barrier / seed layer) を第一重合物層 4 6 及びパッド上に形成させ、この第一粘着 / 阻害層 50 の材質はチタン金属・窒化チタン・チタンタングステン合金・タンタル金属層・クロム・クロム銅合金或いは窒化タンタルの中の一層や組み合わせた場合、少なくともその中の一種を使用し、かつ第一粘着 / 阻害層 50 は、その第一粘着 / 阻害層 50 の上に形成シード層させる。このシード層は次の金属線路の設置に役立っているので、シード層の材質は次の金属線路の材質によって変化する。後続だ実施例の粘着 / 阻害層の上すべて形成シード層させる。

#### 【 0 0 6 2 】

シード層上は電気めっきで形成された銅材質の金属線路の場合は、シード層の材料は銅の方が良い。銀材質の金属線路を電気めっきする場合は、シード層の材料は銀の方が良い。パラジウム材質の金属線路を電気めっきする場合は、シード層の材料はパラジウムの方が良い。プラチナ材質の金属線路を電気めっきする場合は、シード層の材料はプラチナの方が良い。ロジウム材質の金属線路を電気めっきする場合は、シード層の材料はロジウムの方が良い。ルテニウム材質の金属線路を電気めっきする場合は、シード層の材料はルテニウムの方が良い。レニウム材質の金属線路を電気めっきする場合は、シード層の材料はレニウムの方が良い。ニッケル材質の金属線路を電気めっきする場合は、シード層の材料はニッケルの方が良い。

#### 【 0 0 6 3 】

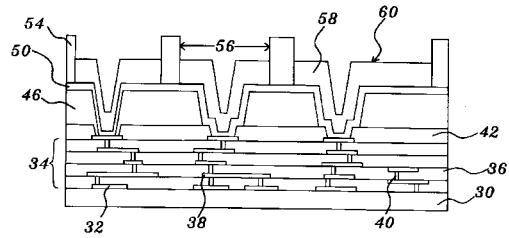

次は図 6 a で示すように、一つの第一図案化ハードンフォトレジスト層 54 (hardened photoresist) をこの第一粘着 / 阻害層 50 上のシード層上に形成させ、この第一図案化ハードンフォトレジスト層 54 は数個の開口 56 によって、部分の第一粘着 / 阻害層 50 上のシード層上を露出させ、この開口 56 、1倍 (1X) ステッパー (steppers) 或いはスキャナー (scanners) またより良い機械を利用して形成させ、この第一図案化ハードンフォトレジスト層 54 を除去すると。それから開口 36 内の第一粘着 / 阻害層 50 上のシード層上を露出させ、に一つの厚さ 1  $\mu$ m から 50  $\mu$ m の第一金属層 58 を電気めっきし、この第一金属層 58 のより良い厚さは 2  $\mu$ m から 30  $\mu$ m の間であって、第一金属層 58 を細い接続構造 34 と接続させ、この第一金属層 58 の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウム或いはニッケルの中の一層や組み合わせた場合、少なくともその中の一種を使用し、この第一図案化ハードンフォトレジスト層 54 を除去すると、一つの第一 RDL 線路層 60 を形成させ、注意する特点是この第一 RDL 線路層 60 は主に第一金属層 58 を開口 48 の上に形成させ、また一部の第一重合物層 4 6 上へ延伸させている。単に開口 48 の上に形成されているではなく、延伸した第一金属層 58 は次の線路設置に役立っている。

#### 【 0 0 6 4 】

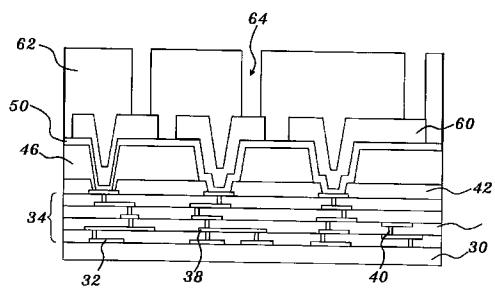

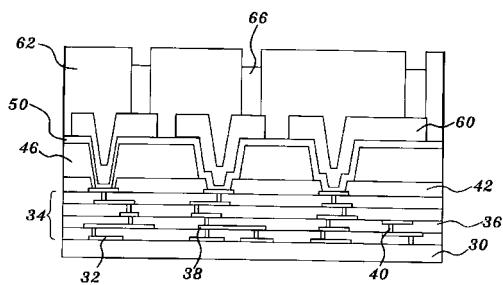

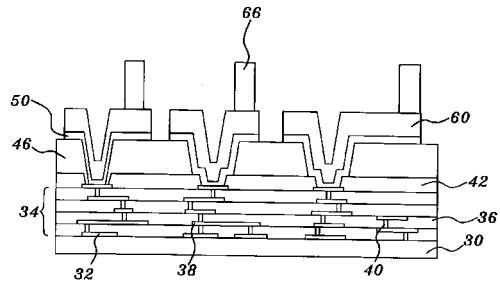

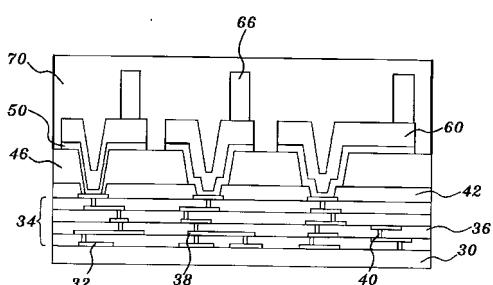

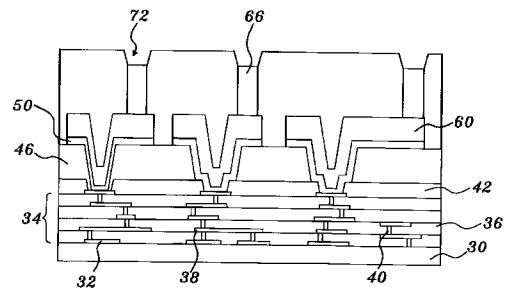

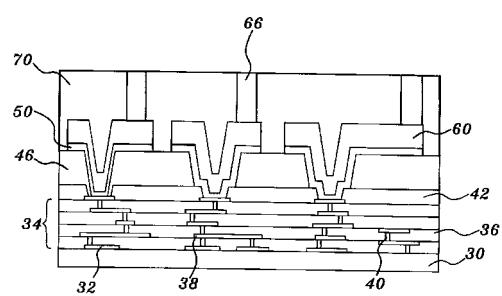

図 6 b で示すように、次は一つの第二図案化ハードンフォトレジスト層 62 を第一 RDL 線路層 60 上及び第一粘着 / 阻害層 50 上のシード層上に形成させ、この第二図案化ハードンフォトレジスト層 62 は数個の開口 64 によって、この第一 RDL 線路層 60 の第一金属層 58 を露出させる。それから図 6 c で示すように、電気めっきで形成された厚さ 20  $\mu$ m から 300  $\mu$ m の一つの第二金属層 66 はこの開口 64 内に形成させ、かつこの第

10

20

30

40

50

二金属層 6 6 の最大 幅は  $3 \mu m$  から  $50 \mu m$  であって、この第二金属層 6 6 の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウム或いはニッケルの中の一種や組み合わせた場合、少なくともその中の一種を使用し、この第二金属層 6 6 のより良い厚さは  $30 \mu m$  から  $100 \mu m$  の間である。

## 【 0 0 6 5 】

この第二金属層 6 6 の材質は銅、第一 RDL 線路層 6 0 のより良い一番階は銅であり、この第二金属層 6 6 の材質は銀、第一 RDL 線路層 6 0 のより良い一番階は銀であり、この第二金属層 6 6 の材質はパラジウム、第一 RDL 線路層 6 0 のより良い一番階はパラジウムであり、この第二金属層 6 6 の材質はプラチナ、第一 RDL 線路層 6 0 のより良い一番階はプラチナであり、この第二金属層 6 6 の材質はロジウム、第一 RDL 線路層 6 0 のより良い一番階はロジウムであり、この第二金属層 6 6 の材質はルテニウム、第一 RDL 線路層 6 0 のより良い一番階はルテニウムであり、この第二金属層 6 6 の材質はレニウム、第一 RDL 線路層 6 0 のより良い一番階はレニウムであり、この第二金属層 6 6 の材質はニッケル、第一 RDL 線路層 6 0 のより良い一番階はニッケルである。

10

## 【 0 0 6 6 】

図 6 d で示すように、次は第二図案化ハードンフォトレジスト層 6 2 を除去し、また同じように過酸化水素を利用して、第一金属層 5 8 下の第一粘着 / 阻害層 5 0 をエッティング除去し、過酸化水素以外にも、ヨード含有エッティング液、例えばヨードカリ等のエッティング液を使用して良い。図 6 e で示すように、この第一金属層 5 8 下のシード層及び第一粘着 / 阻害 / シード層 5 0 を除去するステップは第二図案化ハードンフォトレジスト層 6 2 或いは第一図案化ハードンフォトレジスト層 5 4 を除去した後に行っても良い。

20

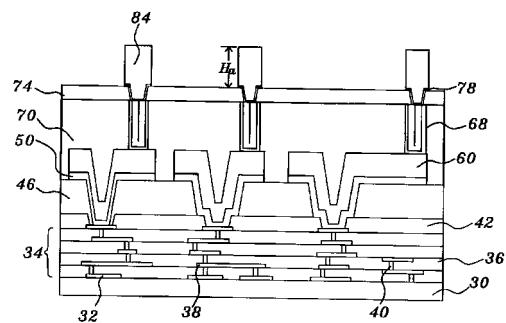

## 【 0 0 6 7 】

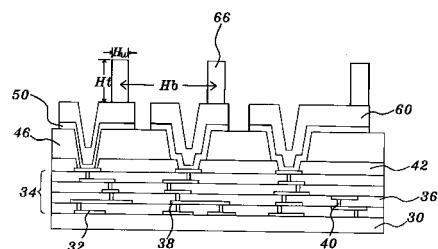

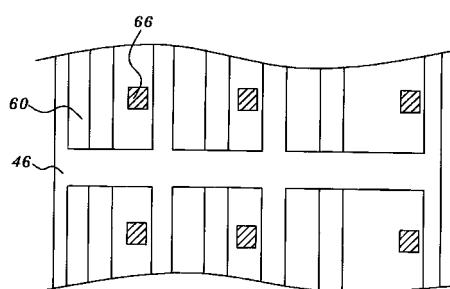

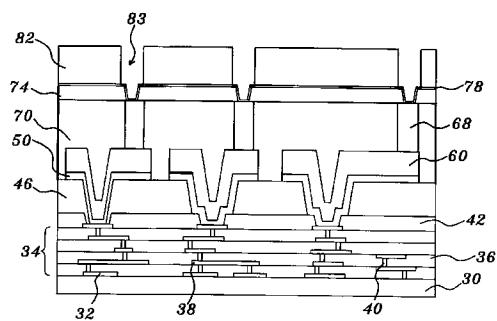

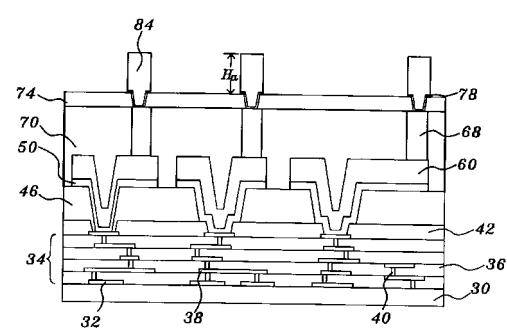

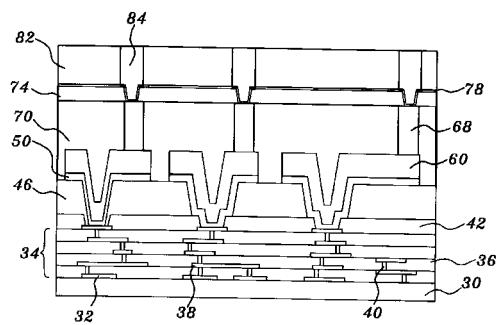

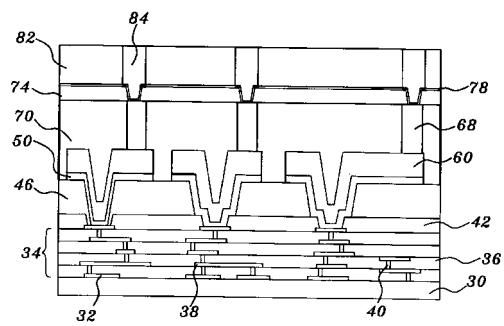

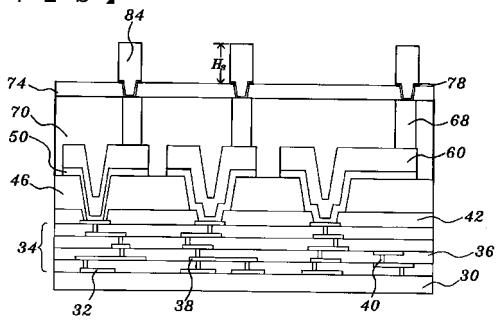

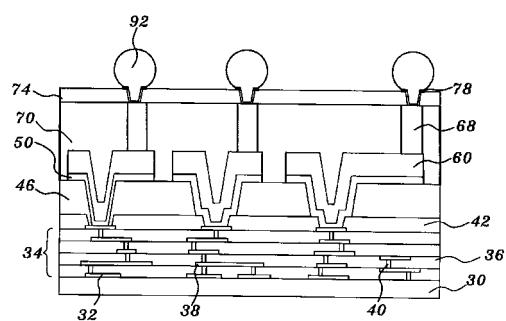

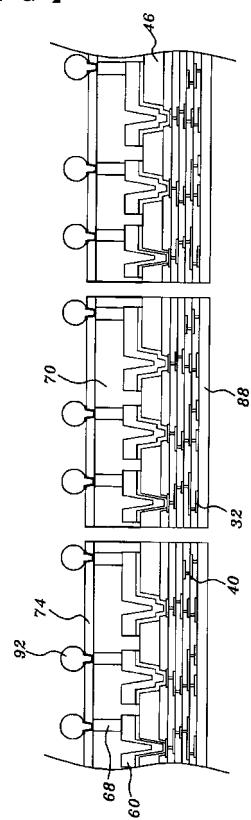

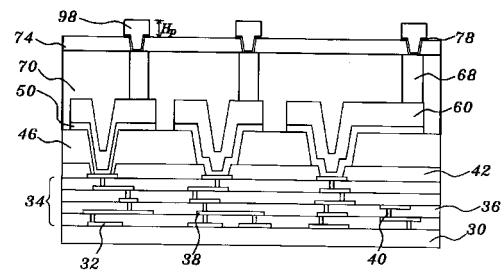

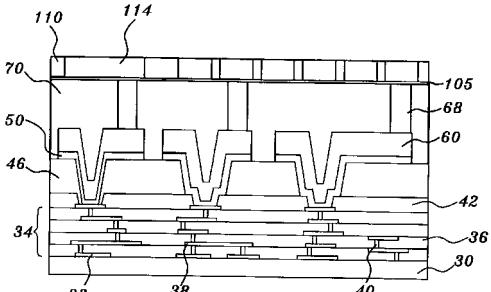

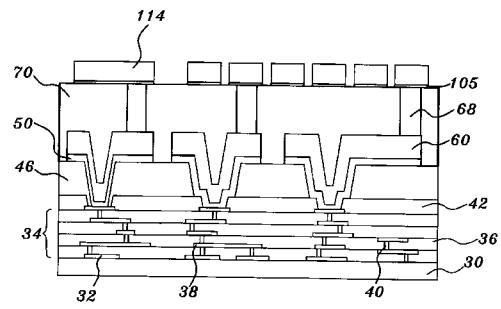

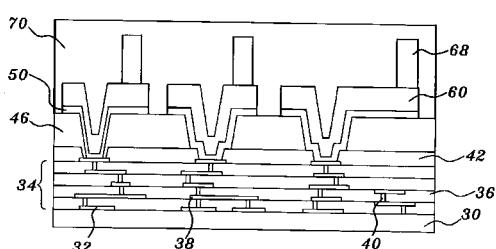

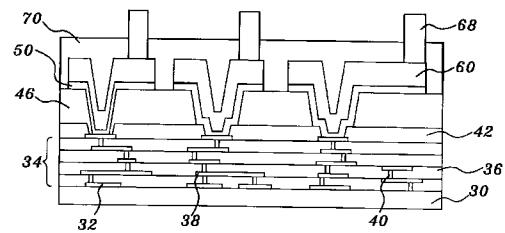

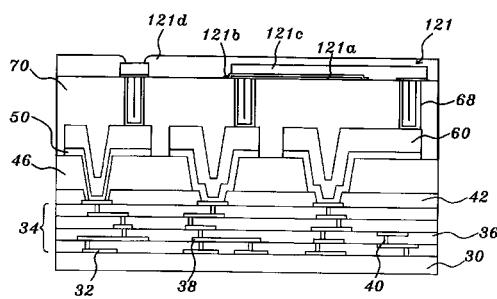

図 7 a 及び図 7 b で示すように、第一金属層 5 8 下の第一粘着 / 阻害層 5 0 を除去した後、各第二金属層 6 6 、即ちコスト発明を定義する金属柱体 6 8 の最大幅  $H_w$  を高さ  $H_t$  で割ると、4 より小さい柱体であって、この数値は 3 或いは 2 より小さくなるのも可能である。この金属柱体 6 8 の最大横幅は  $3 \mu m$  から  $50 \mu m$  である。この金属柱体 6 8 は細小な柱体であって、上記の金属層或いは線路層とは異なって、かつ隣同士の金属柱体 6 8 の中心から中心の間隔距離  $H_b$  は  $10 \mu m$  から  $250 \mu m$  の間であって、また  $10 \mu m$  から  $200 \mu m$  ・  $10 \mu m$  から  $175 \mu m$  ・  $10 \mu m$  から  $150 \mu m$  のより良い間隔距離に縮小することも可能である。図 7 b にこの金属柱体 6 8 を第二金属層 6 6 に設置した見下ろし図を示す。図より明らかに分かることはこの金属柱体 6 8 は開口 4 8 上の RDL 線路層 6 0 上に形成されているではなく、RDL 線路層 6 0 から延伸した区域の上に形成されている。

30

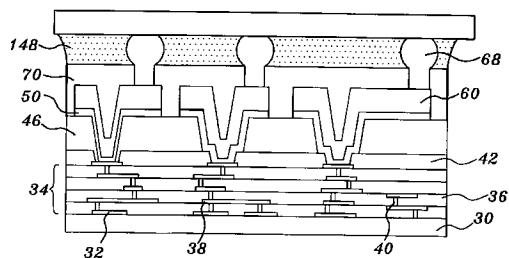

## 【 0 0 6 8 】

図 8 a で示すように、一つの第二重合物層 7 0 がこの半導体基部 3 0 上に、金属柱体 6 8 を被覆し、この第二重合物層 7 0 の材質は熱塑性プラスチック・熱固性プラスチック・ポリイミド (polyimide, PI) 、ベンゾシクロブテン (benzo-cyclo-butene, BCB) ・ポリウレタン (polyurethane) ・エポキシ樹脂・ポリ  $p$ -キシレン類高分子・溶接マスク材料・弾性材料或いは多孔性誘電材料等から選択する。この第二重合物層 7 0 の設置方式はスクリーンプリント或いはスピンドルコート方式である。図 8 b を参照すると、スクリーンプリント方式で設置する場合は、直接第二重合物層 7 0 内に多数開口 7 2 を形成させ、かつ金属柱体 6 8 頂端に露出する。スピンドルコート方式で第二重合物層 7 0 を設置する場合は、一つの図案化ステップを通して、多数開口 7 2 を形成させてから、金属柱体 6 8 頂端に露出する。この第二重合物層 7 0 をスピンドルコート方式で設置するなら、リソグラフィーエッティング方式で開口 7 2 を形成する。図 8 c で示すように、この金属柱体 6 8 の露出方式は開口 7 2 以外に、研磨方式で金属柱体 6 8 を露出することも可能であるが、研磨ステップを行う前に、まず第二重合物層 7 0 を硬化 (Curing) させた後、化学物理研磨 (CMP) で第二重合物層 7 0 を研磨し、金属柱体 6 8 を露出させる。硬化ステップはベーキング加熱やマイクロウェーブ加熱或いは赤外線加熱の一つを選ぶ。

40

## 【 0 0 6 9 】

ここで予め説明したいことは、数多くの実施例は図 8 b 及び図 8 c 中の構造より延伸し

50

たので、本発明にとって、この二つの図に半導体基部 30 上に、多数の金属柱体 68 を形成させ、隣同士の金属柱間に細間隔距離 (fine pitch) の特徴が見られ、その間隔距離は 10  $\mu\text{m}$  から 250  $\mu\text{m}$  の間であって、かつ金属柱体 68 の最大幅  $H_w$  を高さ  $H_t$  で割ると、4 より小さいであるので、下記の数多くの実施例は、全てこの金属柱体 68 に対して、変化を行ない、第一実施例は、図 8 c の構造を基礎としている。

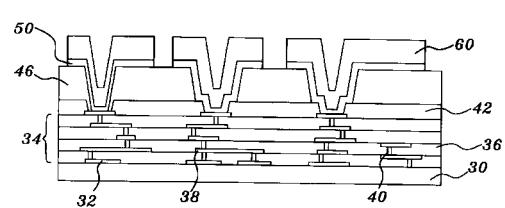

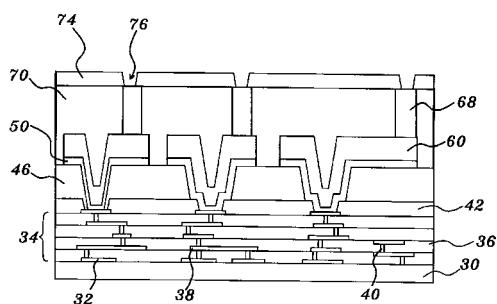

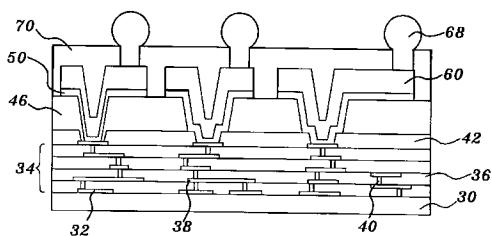

### 【0070】

図 9 で示すように、塗る方法を利用して、一つの第三重合物層 74 を第二重合物層 70 上に形成させ、この第三重合物層 74 に対して、図案化ステップで多数開口 72 を形成する。この第三重合物層 74 の図案化ステップはリソグラフィーやリソグラフィーエッチング方式である。またドライフィルム型式で図案化した第三重合物層 74 を第二重合物層 70 上にホットラミネーションし、或いはスクリーンプリント方式を利用して、第三重合物層 74 を第二重合物層 70 上に形成する。この第三重合物層 74 の材質は熱塑性プラスチック・熱固性プラスチック・ポリイミド (polyimide, PI)、ベンゾシクロブテン (benzo-cyclo-butene, BCB)・ポリウレタン (polyurethane)・エポキシ樹脂・ポリp-キシレン類高分子・溶接マスク材料・弾性材料或いは多孔性誘電材料等から選択する。

### 【0071】

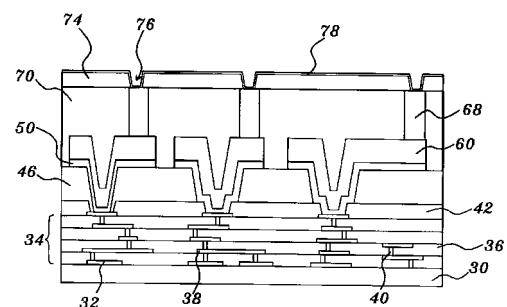

図 10 a で示すように、スパッタリング方式で厚さ 400 から 7000 の一つの第二粘着 / 阻害層 78 を第三重合物層 74 及び金属柱体 68 頂端の表面上に形成させ、この第二粘着 / 阻害層 78 の材質はチタン金属・窒化チタン・チタンタングステン合金・タンタル金属層・クロム・クロム銅合金或いは窒化タンタルの中の一種や組み合わせた場合、その第二粘着 / 阻害層 78 の上に形成シード層させる、少なくともその中の一種を使用する。次は図 10 b で示すように、一つの第三図案化ハードンフォトレジスト層 82 を第二粘着 / 阻害層 78 のシード層に形成させ、この第三図案化ハードンフォトレジスト層 82 はポジフォトレジスト型式であって、この第三図案化ハードンフォトレジスト層 82 の数個の開口 83 は、開口 76 上及び開口 76 周辺の第二粘着 / 阻害層 78 のシード層に露出する。

### 【0072】

次は図 10 c で示すように、電気めっき方式で一つの第三金属層 84 を開口 83 内に露出するかつ第二粘着 / 阻害層 78 上のシード層上に形成させ、この第三金属層 84 の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウム或いはニッケルの中の一種や組み合わせた場合、少なくともその中の一種を使用する。図 10 d で示すように、次は同じように過酸化水素を利用して、第三金属層 84 下の第二粘着 / 阻害層 78 をエッチング除去し、過酸化水素以外にも、ヨード含有エッチング液、例えばヨードカリ等のエッチング液を使用して良い。ここで注意することは、この第三金属層 84 はめっきによって形成された厚さの差異である。第三金属層 84 の材質の差異と厚さの差異によって、半導体基部 30 を外部回路と接続時、異なる型式と応用が生じる。即ち異なる応用に従って、第三図案化ハードンフォトレジスト層 82 の厚さ・開口 83 幅及び開口 82 の形成位置が変わってくるので、また第三金属層 84 は電気めっきによって、異なる厚さ・位置及び材質になってくる。上記の外部回路はフレキ基板・半導体チップ・プリント配線板・セラミック基板或いはガラス基板等である。

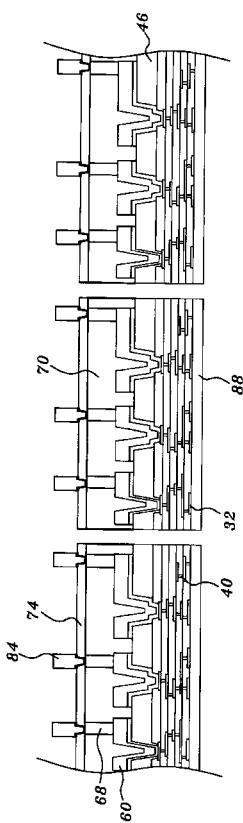

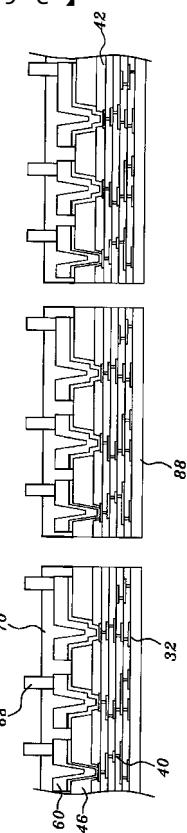

### 【0073】

本実施例において、この第三金属層 84 が形成された型式は、突出塊 (bump)・パッド (pad)、RDL 或いははんだ (solder) である。上記の図 10 d で示すように、第三金属層 84 の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、かつ形成された第三金属層 84 の厚さ ( $H_a$ ) は 5  $\mu\text{m}$  から 30  $\mu\text{m}$  の間である時、より良い厚さは 10  $\mu\text{m}$  から 25  $\mu\text{m}$  の間であるので、この第三金属層 84 を突出塊 86 と定義する。かつ隣同士の突出塊 86 の中心から中心の間隔距離 250  $\mu\text{m}$  小さいであるの間であって、また 200  $\mu\text{m}$ ・150  $\mu\text{m}$  のより良い間隔距離に縮小することも可能である。また図 11 で示すように、この半導体基部 30 をカットし、半導体基部 30 を複数の半導体ユニット 88 に形成させ、各半導体ユニット 88 上の突出塊 86 は ACF の形成によ

10

20

30

40

50

って、一つの外部回路と接続できる。

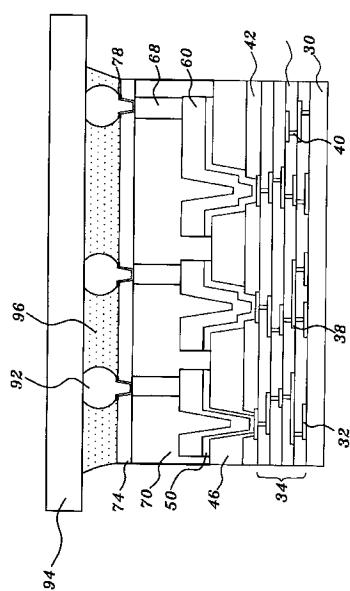

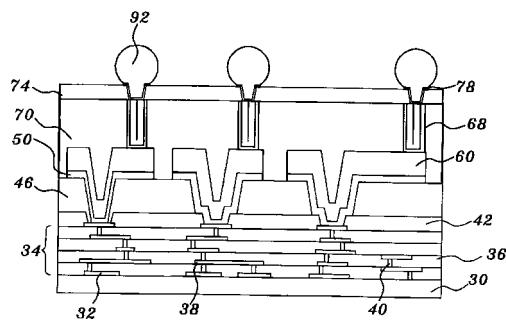

【0074】

図12a及図12bで示すように、第三金属層84の材質ははんだ・錫鉛合金・錫銀銅合金或いは無鉛はんだの一つであって、かつ形成された第三金属層84の厚さ(Ha)は20μmから150μmの間である時、より良い厚さは30μmから105μmの間である。次は図12cで示すように、この半導体基部30を加熱し、この第三金属層84が加熱されると、球状に溶融されるので、この球状に溶融された第三金属層84を錫ボール92と定義する、かつ隣同士の錫ボール92の中心から中心の間隔距離250μm小さいである間であって、また200μm・150μmのより良い間隔距離に縮小することも可能である。第三金属層84の第三種方法は、電気めっきで形成された厚さ1μmから100μmの一つの銅層はこの第三图案化ハーダンフォトレジスト層82の開口83内に形成させ、続いて電気めっきで形成された厚さ1μmから10μmの一つのニッケル層は銅層の上層にあり、最後電気めっきで形成された厚さ20μmから150μmの一つの錫層或いは錫銀層或いは錫銀銅合金層はニッケル層の上層にある。

それからこの半導体基部30を図12dで示すようにカットし、半導体基部30を複数の半導体ユニット88に形成させ、各半導体ユニット88上の錫ボール92は外部基板94上に接合可であって、この基板94は半導体チップ・プリント配線板・セラミック基板或いはガラス基板である。

【0075】

図12eで示すように、この半導体ユニット88上の錫ボール92は外部基板94上に接合した時、その半導体ユニット88を外部基板94と接合する前に、まず一つの第四重合物層96を基板94上に形成させ、この第四重合物層96の材質は熱塑性プラスチック・熱固性プラスチック・ポリイミド(polyimide, PI)、ベンゾシクロブテン(benzo-cyclo-butene, BCB)・ポリウレタン(polyurethane)・エポキシ樹脂・ポリp-キシレン類高分子・溶接マスク材料・弾性材料或いは多孔性誘電材料等から選択する。この第四重合物層96の形成方式は、一つの图案化されたドライフィルム(dry film)をその基板94上にホットラミネーションし、或いは一つの感光性ドライフィルムをその基板94上にホットラミネーションした後、リソグラフィー方式で感光性ドライフィルムを图案化し、或いはスクリーンプリント方式で第四重合物層96を基板94上に形成させ、或いはスピンドルコーティング方式で一つの感光性薄膜を基板94上に形成させ、またリソグラフィー方式で感光性ドライフィルム或いはスピンドルコーティング方式で一つの非感光性薄膜を基板94上に形成させ、リソグラフィーエッチング方式で非感光性薄膜を图案化する。半導体ユニット88上の錫ボール92が基板94と接合した後加熱し、第四重合物層96を硬化させ、この加熱ステップはベーキング加熱やマイクロウェーブ加熱或いは赤外線加熱等の方式を選択する。

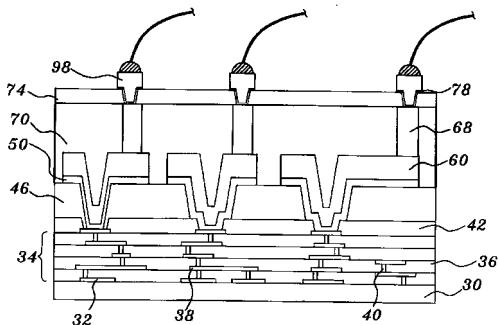

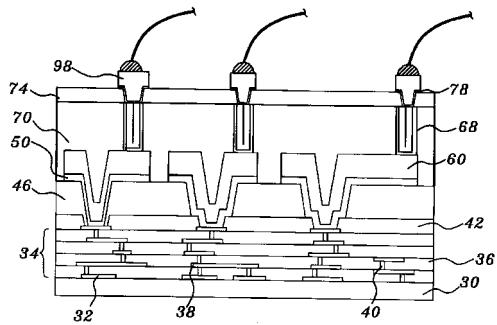

【0076】

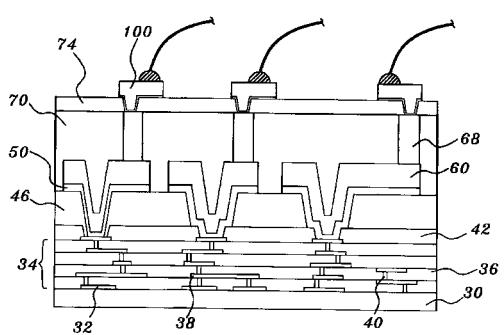

図13a及び図13bで示すように、第三金属層84の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、かつ形成された第三金属層84の厚さ(Ha)は1μmから15μmの間である時、より良い厚さは2μmから10μmの間である。この第三金属層84をパッド98と定義し、かつ隣同士のパッド98の中心から中心の間隔距離250μm小さいである間であって、また200μm・150μmのより良い間隔距離に縮小することも可能である、このパッド98はワイヤー製作過程で一つのワイヤーを形成させ、外部回路と接続する。

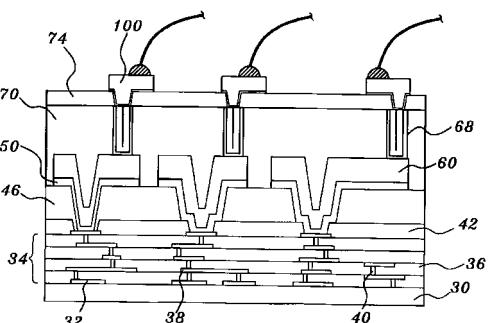

【0077】

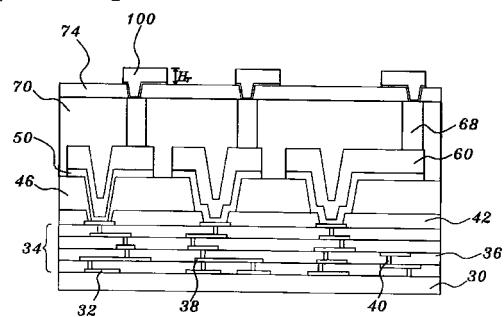

図14a及び図14bで示すように、第三金属層84の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、かつ形成された第三金属層84の厚さ(Ha)は5μmから30μmの間である時、より良い厚さは10μmから25μmの間であって、かつこの第三金属層84の形成位置は第三重合物層74の開口76上以外に、開口76側方の第二粘着/阻害層78上にも形成させ、この第三金属層84をRDL層100と定義し、このRDL層100はワイヤー製作過程で一つのワイヤーを形成させ、外部回路

と接続する。ここで強調説明したいことは、開口 7 6 側方の第三金属層 8 4 はパッド 9 8 の機能に類似し、このような偏心設計は、上記のパッド 9 8 の寸法が過小時、ワイヤー製作過程で必要なワイヤー面積が不足し、ワイヤー製作過程が困難になることを防ぐためである。

#### 【 0 0 7 8 】

本実施例の図 9 から図 14 b の中の突出塊 (bump)・パッド (pad)、RDL 或いははんだ (solder) 等の応用は、全て図 8 c の構造より延伸し、ただしこれらの応用は、同じように直接図 8 c の構造より延伸することができ、原因は図 9 の構造は図 8 c の構造の第三重合物層 7 4 より形成させ、またこの第三重合物層 7 4 を多数開口に図案化され、しかし図 8 b の構造は研磨によって金属柱体 6 8 を露出させたではなく、図案化方式で多数開口で金属柱体 6 8 を露出させ、また第三重合物層 7 4 を設置する必要性がなくなったので、即ち図 8 b の構造は図 8 c の構造に第三重合物層 7 4 を加えたようであり、ゆえに図 9 から延伸する図 10 a ~ d、図 11、図 12 a ~ e、図 13 a ~ b、図 14 a ~ b の突出塊 (bump)・パッド (pad)、RDL 或いははんだ (solder) 等の応用についての説明は省略する。

10

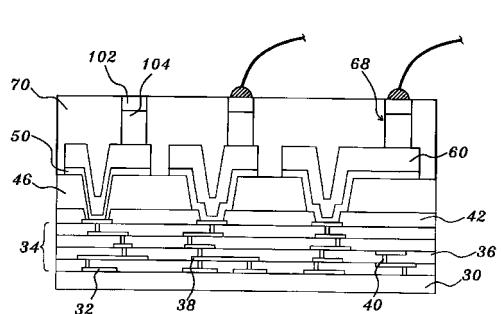

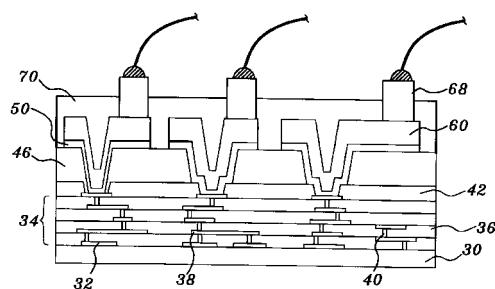

#### 【 0 0 7 9 】

##### ( 第二実施例 )

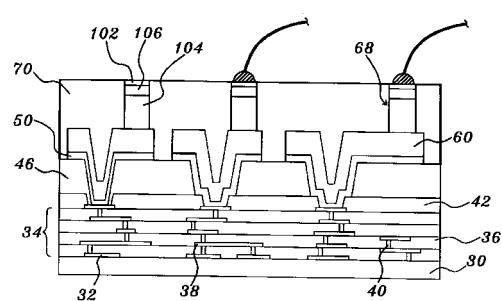

本実施例は第一実施例の図 8 c からの延伸である。図 15 a を参照すると、この実施例の中の金属柱体 6 8 頂部は一つの金層 1 0 2 であって、この金層 1 0 2 の厚さ 1  $\mu$ m から 30  $\mu$ m、この金属柱体 6 8 の金属 1 0 2 上に、ワイヤー製作過程で一つのワイヤー 1 0 4 を形成させ、外部回路と接続する。ここで注意することは、金層 1 0 2 以下の金属は銅層 1 0 4・ニッケル層 1 0 6 (銅・ニッケル・金構造)、この銅層 1 0 4 の厚さ 1 0  $\mu$ m から 1 0 0  $\mu$ m、このニッケル層 1 0 6 の厚さ 1  $\mu$ m から 30  $\mu$ m、或いは図 15 b で示すように、この金層 1 0 2 は銅層 1 0 4 の上層にあり、この金層 1 0 2 の厚さ 1  $\mu$ m から 30  $\mu$ m、或いは図 15 c で示すように、金属柱体 6 8 全体の材質は金である、この金属柱体 6 8 厚さ 1 0  $\mu$ m から 1 0 0  $\mu$ m。

20

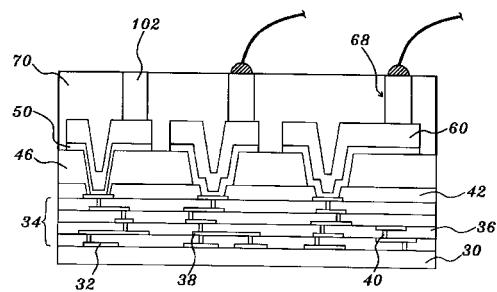

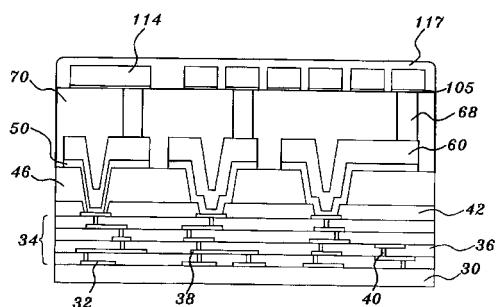

#### 【 0 0 8 0 】

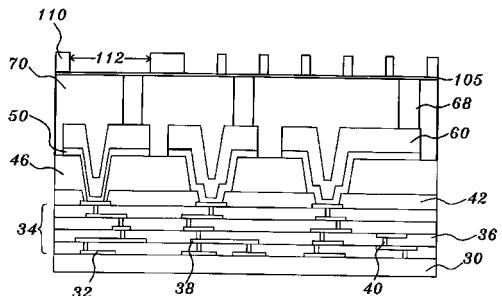

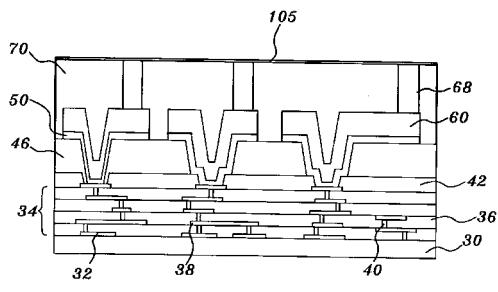

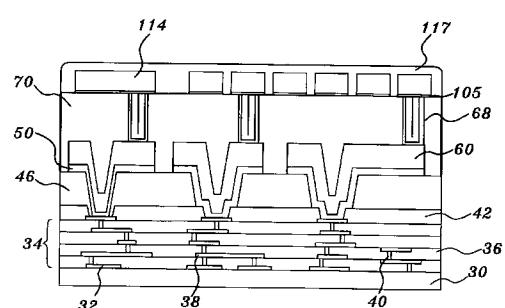

##### ( 第三実施例 )

本実施例は第一実施例の図 8 c からの延伸である。図 16 a を参照すると、一つの第三粘着 / 阻害層 1 0 5 を第二重合物層 7 0 上に形成する、その第三粘着 / 阻害層 1 0 5 の上に形成シード層させる、図 16 b で示すように、一つの第四図案化ハーダンフォトレジスト層 1 1 0 を第三粘着 / 阻害層 1 0 5 上に形成させ、この第四図案化ハーダンフォトレジスト層 1 1 0 内には多数開口 1 1 2 があって、その中少なくとも一つの開口 1 1 2 が金属柱体 6 8 の上方に位置し、かつこの開口 1 1 2 は図 16 c で示すように、コイル状を電気めっきして、一つの第四金属層 1 1 4 を第四図案化ハーダンフォトレジスト層 1 1 0 の開口 1 1 2 内に形成する、その第四金属層 1 1 4 の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、この第四金属層 1 1 4 の厚さ 1  $\mu$ m から 30  $\mu$ m、その第四金属層 1 1 4 は複合の金属層使用される、電気めっきで形成された厚さ 1  $\mu$ m から 30  $\mu$ m の一つの銅層であり、続いて電気めっきで形成された厚さ 1  $\mu$ m から 1 0  $\mu$ m の一つのニッケル層は銅層の上層にあり、最後電気めっきで形成された厚さ 1  $\mu$ m から 1 0  $\mu$ m の一つの金はニッケル層の上層にある。

30

#### 【 0 0 8 1 】

図 16 d で示すように、第四図案化ハーダンフォトレジスト層 1 1 0 を除去し、かつ同じように過酸化水素やヨード含有エッチング液を使用して、第四図案化ハーダンフォトレジスト層 1 1 0 下の第三粘着 / 阻害層 1 0 5 を除去した後、図 16 e で示すように、この第四金属層 1 1 4 はコイル状を呈するので、この第四金属層 1 1 4 を一つの第一コイル金属層 1 1 6 と定義し、その中の第一コイル金属層 1 1 6 は金属柱体 6 8 を通して半導体基部 3 0 と接続する。図 16 f で示すように、半導体基部 3 0 と接続する以外に、ワイヤー製作過程を通して外部回路と接続することも可能である (図示せず)。またこの第一コイル金属層 1 1 6 をダメージ及び水気の浸入から保護するために、一つの保護層 1 1 7 を形

40

50

成することができる、その保護層 117 の厚さは 5  $\mu\text{m}$  から 25  $\mu\text{m}$  である。この保護層 117 の材質は有機化合物或いは無機化合物で、例えば熱塑性プラスチック・熱固性プラスチック・ポリイミド (polyimide, PI)、ベンゾシクロブテン (benzo-cyclo-butene, BCB)・ポリウレタン (polyurethane)・エポキシ樹脂・ポリp-キシレン類高分子・溶接マスク材料・弾性材料・多孔性誘電材料・酸化シリコン (silicon oxide)、酸化シリコン化合物、ケイ素-リングガラス・窒化けい素 (silicon nitride) 及び SiON (silicon oxy-nitride) 等から組成する。この第一コイル金属層 116 はインダクター・コンデンサー及び抵抗等の受動デバイスの領域に応用される。

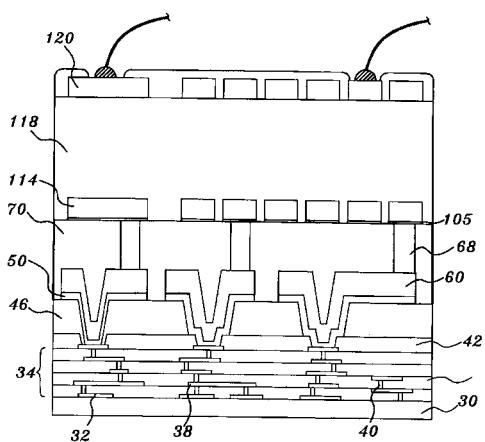

#### 【0082】

ここでこの第一コイル金属層 116 がコンデンサー受動デバイスでの応用を列記し、図 16 g を参照すると、第一コイル金属層 116 が一つの第五重合物層 118 を被覆し、この第五重合物層 118 の厚さは 20  $\mu\text{m}$  から 300  $\mu\text{m}$  の間であって、この第五重合物層 118 の材質はポリイミド (polyimide, PI) であり、この第二コイル金属層 120 は外部回路との接続が可能である。外部回路の電流に変化が起きた時、第二線圈金属層 120 を通して、誘導起電力が生じ、第一コイル金属層 116 がこれを感應して、生じた信号を半導体基部 30 へ伝送され、この受動デバイスの製作解説はここで完了する。

#### 【0083】

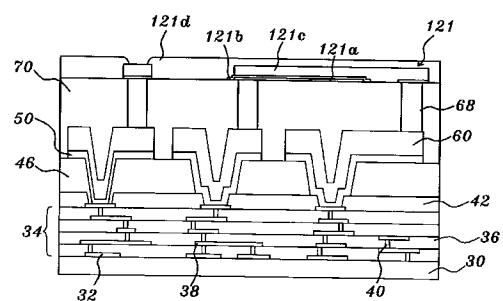

上記の電気めっき方式を利用すると、第二重合物層 70 上に一つのコンデンサーデバイス 121 (capacitor) を形成することも可能であって、図 16 h で示すように、第二重合物層 70 に厚さ 500 から 5000 の一つの低誘電層 121a を設け、この低誘電層 121a の材質はチタン・チタンタングステン合金・タンタル或いは窒化タンタル等であって、かつこの低誘電層 121a は一つの金属柱体 68 と接続してから、低誘電層 121a 上に一つの高誘電層 121b を被覆し、この高誘電層 121b の材質は窒酸化化合物・酸化シリコン (silicon oxide) 化合物或いはポリイミド (polyimide, PI) であって、隣同士の金属柱体 68 上を電気めっきで一つの低抵抗金属層 121c を形成させ、この低誘電層 121a は二種類の方法を形成させ、一種類はもう一つの方法に厚さ 400 から 7500 の一つの粘着 / 阻害層は第二重合物層 70 と高誘電層 121b の上層にあり、この粘着 / 阻害層の材質はチタン・チタンタングステン合金・タンタル或いは窒化タンタル等であって、続いてもう一つの方法に厚さ 500 から 5000 の一つのシード層は粘着 / 阻害層の上層にあり、続いて電気めっきで形成された厚さ 1  $\mu\text{m}$  から 30  $\mu\text{m}$  の一つの銅層はシード層の上層にあり、続いて電気めっきで形成された厚さ 1  $\mu\text{m}$  から 10  $\mu\text{m}$  の一つのニッケル層は銅層の上層にある。

#### 【0084】

別の方法はもう一つの方法に厚さ 400 から 7500 の一つの粘着 / 阻害層は第二重合物層 70 と高誘電層 121b の上層にあり、続いてもう一つの方法に厚さ 500 から 5000 の一つのシード層は粘着 / 阻害層の上層にあり、最後電気めっきで形成された厚さ 1  $\mu\text{m}$  から 30  $\mu\text{m}$  の金層は金の材質シード層の上層にあり、隣同士の金属柱体 68 に電圧を加えると、高誘電層 121b の上下側に大きな電圧差が形成され、この構造はコンデンサー機能を持っている。最後はこのコンデンサーデバイス 121 を損害から守るため、この低抵抗金属層 121c 及び第二重合物層 70 の上に保護層 121d を被覆するのも可能である。

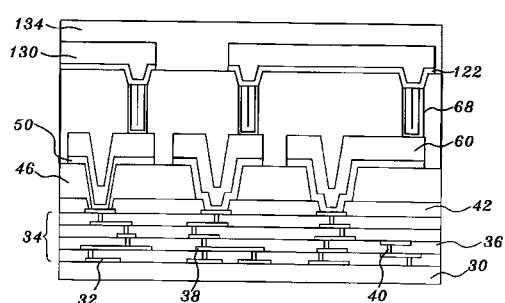

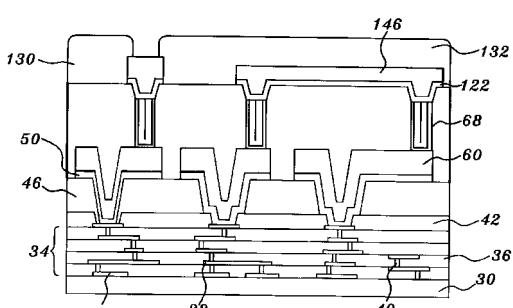

#### 【0085】

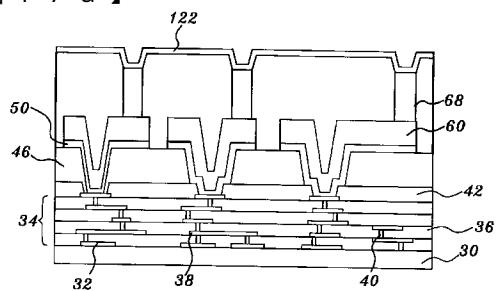

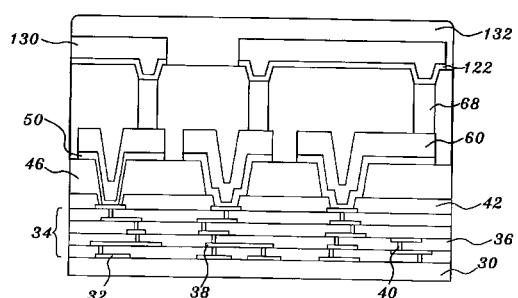

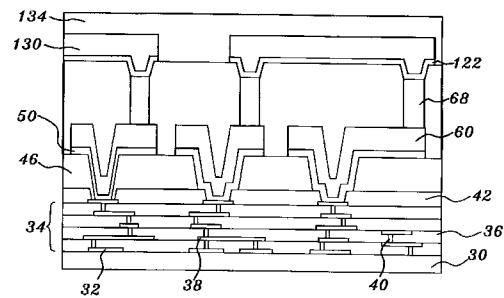

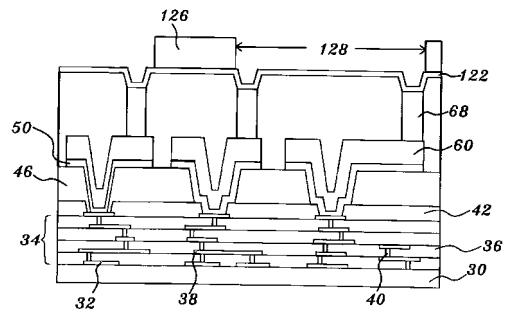

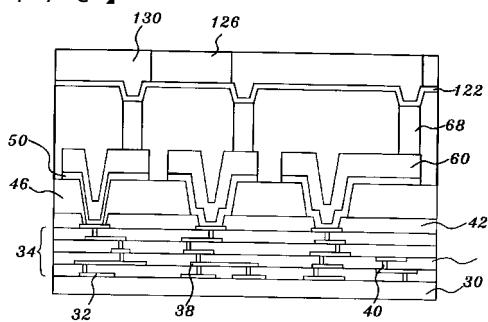

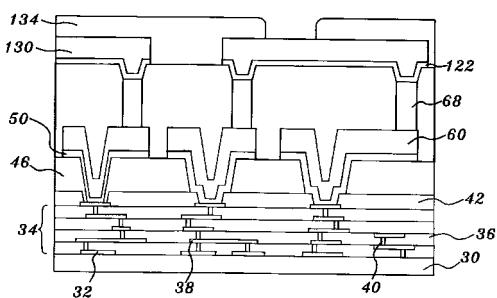

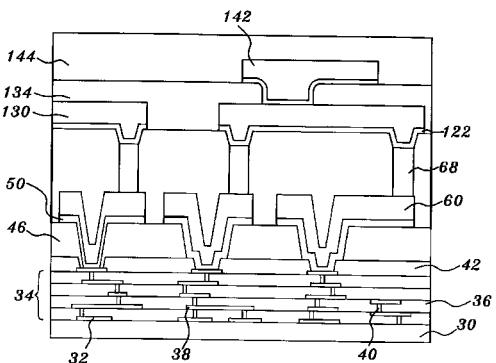

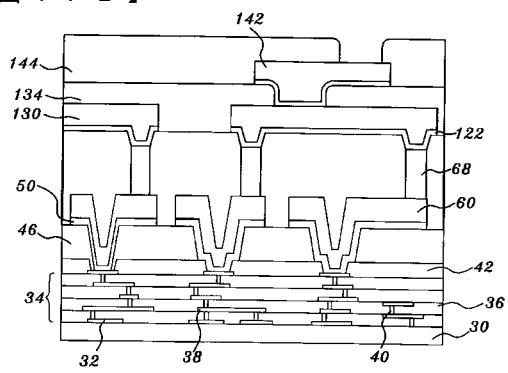

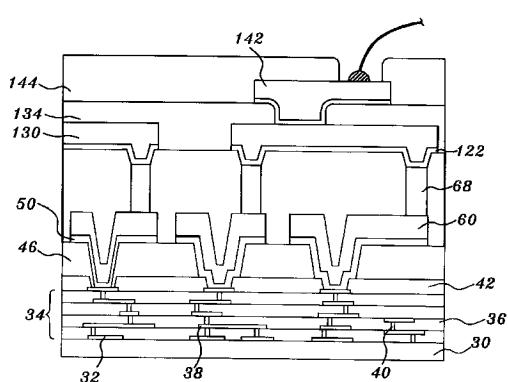

##### (第四実施例)

本実施例は第一実施例の図 8b の延伸であって、図 17a で示すように、一つの第四粘着 / 阻害層 122 を第二重合物層 70 上に形成させ、この第四粘着 / 阻害層 122 の材質はチタン・チタンタングステン合金・タンタル或いは窒化タンタル等であって、このシード層の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、図 17b で示すように、一つの第五図案化ハーダンフォトレジスト層 126 を第四粘着 / 阻害層 122 上に形成させ、この第五図案化ハーダンフォトレジスト層 126 内に多数開口 128 があって、その中の二つの開口 128 が金属柱体 68 の上方に位置し、図 17

10

20

30

40

50

c で示すように、電気めっきで形成された厚さ  $\mu\text{m}$  から  $30\text{ }\mu\text{m}$  の一つの第五金属層 130 を第五图案化ハーダンフォトレジスト層 126 の開口 128 内の第四粘着 / 阻害 / シード層 122 上に形成させ、かつこの第五金属層 130 は低抵抗で、例えば金・銀或いは銅等である。次は図 17 d で示すように、第五图案化ハーダンフォトレジスト層 126 を除去し、また同じように過酸化水素やヨード含有エッチング液を使用して、第五图案化ハーダンフォトレジスト層 110 下の第四粘着 / 阻害層 122 を除去した後、この第五金属層 130 を二つの金属柱体 68 に接続し、この第五金属層 130 は二つの金属柱体 68 の電流通路であって、またダメージや水気の浸入から保護するために、一つの保護層 132 を第二重合物層 70 及び第五金属層 130 上に形成することができる、この第五金属層 130 の厚さ  $1\text{ }\mu\text{m}$  から  $30\text{ }\mu\text{m}$ 、その第五金属層 130 は複合の金属層使用される、電気めっきで形成された厚さ  $1\text{ }\mu\text{m}$  から  $30\text{ }\mu\text{m}$  の一つの銅層、続いて電気めっきで形成された厚さ  $1\text{ }\mu\text{m}$  から  $10\text{ }\mu\text{m}$  の一つのニッケル層は銅層の上層にあり、最後は電気めっきで形成された厚さ  $1\text{ }\mu\text{m}$  から  $10\text{ }\mu\text{m}$  の一つの金層はニッケル層の上層にある。

10

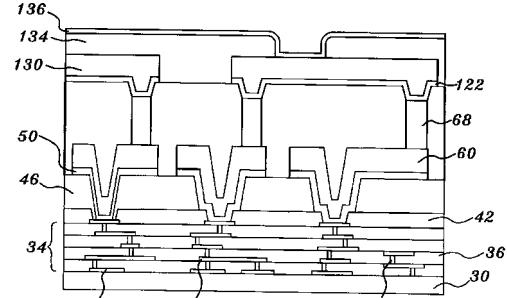

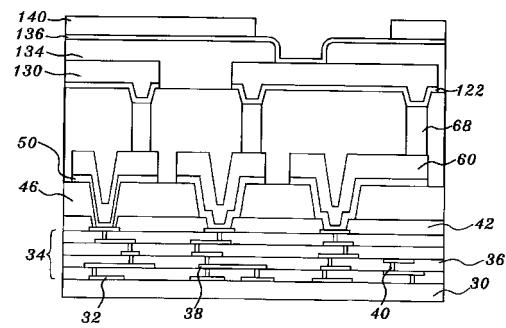

#### 【0086】

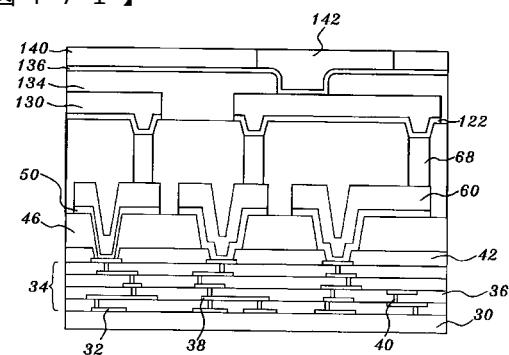

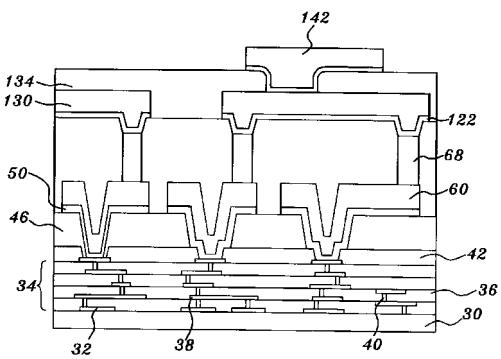

第五金属層 130 をメタルは路線を連がる以外に、多層線路構造への延伸も可能である。図 17 e で示すように、一つの第六重合物層 134 を第二重合物層 70 及び第五金属層 130 上に形成された後、図 17 f で示すように、この第六重合物層 134 の多数開口を第五金属層 130 に露出するように图案化し、図 17 g で示すように、順序によって一つの第五粘着 / 阻害層 136 をスパッタリングし、この第五粘着 / 阻害層 136 の材質はチタン・チタンタングステン合金・タンタル或いは窒化タンタル等であって、このシード層の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、図 17 h で示すように、一つの第六图案化ハーダンフォトレジスト層 140 を上に形成させ、この第六图案化ハーダンフォトレジスト層 140 の多数開口を第六重合物層 134 の開口に露出させ、図 17 i で示すように、一つの第六金属層 142 を第六图案化ハーダンフォトレジスト層 140 上に形成させ、この第六金属層 142 の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、この第六金属層 142 の厚さ  $1\text{ }\mu\text{m}$  から  $30\text{ }\mu\text{m}$ 、その第六金属層 142 は複合の金属層使用される、電気めっきで形成された厚さ  $1\text{ }\mu\text{m}$  から  $30\text{ }\mu\text{m}$  の一つの銅層であり、続いて電気めっきで形成された厚さ  $1\text{ }\mu\text{m}$  から  $10\text{ }\mu\text{m}$  の一つのニッケル層は銅層の上層にあり、最後電気めっきで形成された厚さ  $1\text{ }\mu\text{m}$  から  $10\text{ }\mu\text{m}$  の一つの金はニッケル層の上層にある。

20

#### 【0087】

図 17 j で示すように、第六图案化ハーダンフォトレジスト層 140 及び第六金属層 142 下方以外と第五粘着 / 阻害層 136 とシード層を除去した後、図 17 k で示すように、一つの第七重合物層 144 を第六重合物層 134 及第六金属層 142 上に形成させ、その第七重合物層 144 た厚さ  $10\text{ }\mu\text{m}$  から  $25\text{ }\mu\text{m}$  の一つの、図 17 l で示すように、この第七重合物層 144 の多数開口を第六金属層 142 に露出するように图案化し、図 17 m で示すように、ワイヤー製作過程で一つのワイヤーを第六金属層 142 に露出させ、外部回路と接続する。

30

#### 【0088】

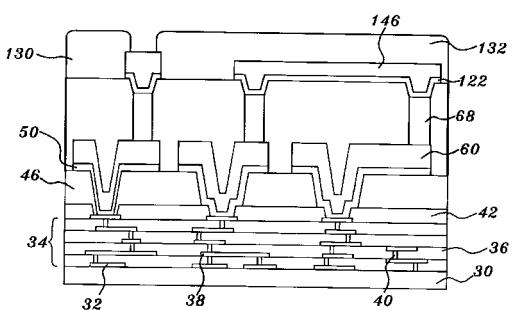

##### (第五実施例)

本実施例は第一実施例の図 8 b の延伸であって、かつ本実施例は第四実施例と似て、図 18 で示すように、本実施例の形成方式は第四実施例と同じで、異なる点は第四実施例の中の第五金属層 130 は低抵抗材質であるので、第五金属層 130 の電流は速やかに流通することができるが、第五実施例（図 18 参照）の第七金属層 146 は高抵抗材質で、例えばクロム / ニッケル合金（Cr / Ni）・チタン・タングステン等であって、かつ第七金属層 146 の厚さは  $1\text{ }\mu\text{m}$  から  $3\text{ }\mu\text{m}$  であるので、第七金属層 146 は本実施例において、抵抗デバイスとして用いられる。

40

#### 【0089】

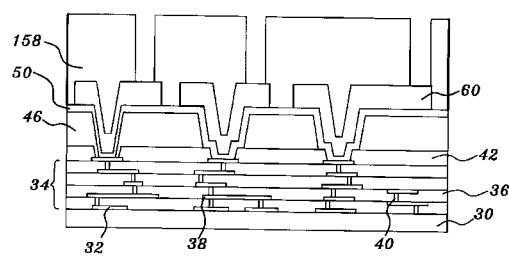

##### (第六実施例)

上記の第一から第五実施例は図 8 b 及び図 8 c 構造の延伸であるが、本実施例は図 8 a

50

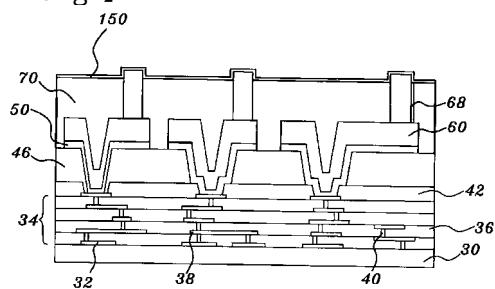

構造の延伸である。図19a及び図19bで示すように、本実施例はエッチング方式を利用し、一部分の第二重合物層70を高さ1μmから150μmの金属柱体68が露出するまで除去し、この露出高さは金属柱体頂面から第二重合物層70頂面までの距離であって、もし金属柱体68の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムである時、金属柱体68のより良い露出高さは15μmから30μmの間である。この金属柱体68は突出塊として使用され、図19cで示すように、同じカットステップを行ない、この半導体基部30を複数半導体ユニット88にカットし、同じように各半導体ユニット88上の突出塊86はACFの形成によって、一つの外部回路と接続できる。

## 【0090】

10

もし金属柱体68の材質ははんだ・錫鉛合金・錫銀合金・錫銀銅合金或いは無鉛はんだである時、金属柱体68のより良い露出高さは50μmから100μmの間である。図19dで示すように、同じ加熱ステップで外部に露出する金属柱体68をボール状(はんだ錫ボール)に溶融してから、図19eで示すように、同じカットステップを行ない、この半導体基部30を複数半導体ユニット88にカットし、各半導体ユニット88上の突出塊86を外部基板と接合させ、また半導体ユニットと基板間に一つの第八重合物層148を形成させ、各ボール状突出塊を被覆する。

## 【0091】

20

図19fで示すように、もし金属柱体68の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムである時、金属柱体68のより良い露出高さは1μmから15μmの間である。この露出した金属柱体68はパッドとして使用し、このパッドはワイヤー製作過程で一つのワイヤーを形成させ、その金属層やその重合物層と接続する。

## 【0092】

30

図19gで示すように、もし露出した金属柱体68の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムであって、かつ露出高さは5000から10μmの間である時、一つの第六粘着/阻害層150を第二重合物層70及び金属柱体68の露出表面に形成させ、この第六粘着/阻害層150の材質はチタン・チタンタングステン合金・タンタル或いは窒化タンタル等であって、このシード層は第六粘着/阻害層150の上層にあり、このシード層の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、この第六粘着/阻害層150に厚さ1000から7500の一つ。

## 【0093】

40

図19hで示すように、一つの第七図案化ハードンフォトレジスト層152を第六粘着/阻害層150上に形成させ、第七図案化ハードンフォトレジスト層152の多数開口は第六粘着/阻害層150に露出し、図19iで示すように、一つの第八金属層154を第七図案化ハードンフォトレジスト層152の開口内に形成させ、図19jで示すように、第七図案化ハードンフォトレジスト層152を除去し、また第八金属層154下以外の第六粘着/阻害/シード層150も除去する。この第八金属層154は、メタル路線をつなぎ、二つの金属柱体68の間と接続する。この第八金属層154の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、この第八金属層154の厚さ1μmから30μm、その第八金属層154は複合の金属層使用される、電気めっきで形成された厚さ1μmから30μmの一つの銅層であり、続いて電気めっきで形成された厚さ1μmから10μmの一つのニッケル層は銅層の上層にあり、最後電気めっきで形成された厚さ1μmから10μmの一つの金はニッケル層の上層にある。

## 【0094】

50

図19kで示すように、最後は第八金属層154及び第二重合物層70を損害から守るため、保護層154として被覆する。その保護層154の材質は熱塑性プラスチック・熱固性プラスチック・ポリイミド(polyimide, PI)、ベンゾシクロブテン(benzo-cyclo-butene, BCB)・ポリウレタン(polyurethane)・エポキシ樹脂・ポリp-キシレン類高分子

・溶接マスク材料・弾性材料・多孔性誘電材料・酸化シリコン (silicon oxide)・酸化シリコン化合物・リン化シリコンガラス・窒化シリコン (silicon oxide) 及び窒酸化シリコン (silicon oxy-nitride) 等から選択する。

【0095】

このエッティングを利用し、金属柱体 68 を露出させる方法は、上記の突出塊・パッド及びメタルは路線の接続に応用される以外に、またコイル構造・コンデンサー構造及び抵抗構造にも応用される。製作ステップは上記の実施例とは似ているので、繰り返して説明しない。

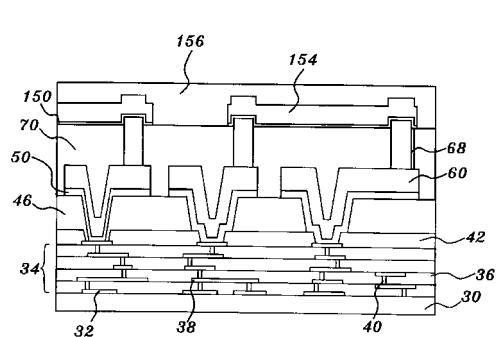

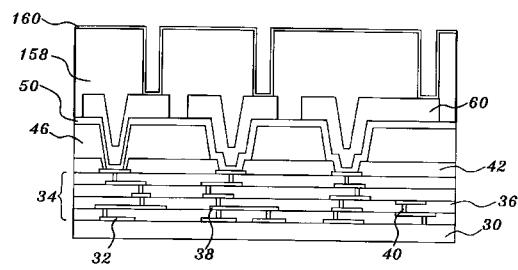

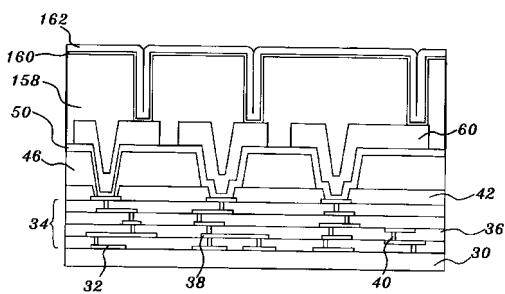

(第七実施例)

【0096】

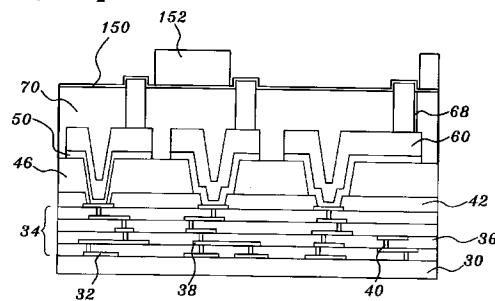

本実施例の構造は図 8c の構造と似て、異なる点は金属柱体 68 及び第二重合物層 70 の製作過程が違うだけで、図 20a で示すように、この第一 RDL 層 60 を半導体基部 30 に形成後、一つの第九図案化ハードンフォトレジスト層 158 をこの第一 RDL 層 60 上及び第一粘着 / 阻害 / シード層 50 上に形成させ、この第九図案化ハードンフォトレジスト層 158 の多数開口を第一 RDL 層 60 に露出させ、かつ第九図案化ハードンフォトレジスト層 158 の開口深度は 20 μm から 300 μm の間である。

【0097】

この第九図案化ハードンフォトレジスト層 158 の材質は熱塑性プラスチック・熱固性プラスチック・ポリイミド (polyimide, PI)、ベンゾシクロブテン (benzo-cyclo-butene, BCB)・ポリウレタン (polyurethane)・エポキシ樹脂・ポリp-キシレン類高分子・溶接マスク材料・弾性材料或いは多孔性誘電材料等から選択する。かつこの第九図案化ハードンフォトレジスト層 158 の形成方式は一つの図案化されたドライフィルム (dry film) をその半導体基板 30 上にホットラミネーションし、或いは一つの感光性ドライフィルムを半導体基板 30 上にホットラミネーションした後、リソグラフィー方式で感光性ドライフィルムを図案化し、或いは一つの非感光性薄膜を半導体基板 30 上にホットラミネーションし、またリソグラフィー方式で非感光性薄膜を図案化し、或いはスクリーンプリント方式で第九図案化重合物層 158 を半導体基板 30 上に形成させ、或いはスピンドルティング方式で一つの感光性薄膜を半導体基板 30 上に形成させ、またリソグラフィー方式で感光性ドライフィルム或いはスピンドルティング方式で一つの非感光性薄膜を半導体基板 30 上に形成させ、またリソグラフィーエッティング方式で非感光性薄膜を図案化する。

【0098】

図 20b で示すように、一つの厚さ 400 から 7000 の第七粘着 / 阻害層 160 を第九図案化重合物層 158 及び第九図案化重合物層 158 開口内の第一 RDL 層 60 上に形成させ、この第七粘着 / 阻害層 160 の材質はチタン・チタンタングステン合金・タンタル或いは窒化タンタル等であって、このシード層は第七粘着 / 阻害層 160 の上層にあり、このシード層の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、この第六粘着 / 阻害層 150 に厚さ 1000 から 7500 の一つ。

【0099】

図 20c で示すように、ダマシン (Damascene) 方式で一つの第九金属層 162 を第七粘着 / 阻害 / シード層 160 上に形成された後、第九図案化重合物層 158 の開口を詰め込む、この第八金属層 154 の材質は金・銅・銀・パラジウム・プラチナ・ロジウム・ルテニウム・レニウムで、この第九金属層 162 の厚さ 1 μm から 30 μm、その第九金属層 162 は複合の金属層使用される、電気めっきで形成された厚さ 1 μm から 30 μm の一つの銅層であり、続いて電気めっきで形成された厚さ 1 μm から 10 μm の一つのニッケル層は銅層の上層にあり、最後電気めっきで形成された厚さ 1 μm から 10 μm の一つの金はニッケル層の上層にある。

【0100】

図 20d で示すように、一つの研磨ステップで第九図案化重合物層 158 の開口以外の第九金属層 162 及び第七粘着 / 阻害層 160 を除去し、金属柱体 68 の設置を完成させ

10

20

30

40

50

る。この金属柱体68の最大幅Hwを高さHtで割ると、4より小さい柱体であって、この金属柱体68の最大横幅は3μmから50μmである。かつ隣同士の金属柱体68の間隔距離Hbは10μmから250μmの間である。

#### 【0101】

ダマシン(Damascene)方式で形成された金属柱体68の構造は、上記の図8cの中で掲示した構造が非常に似ているので、このあとの第九図案化重合物層158及び金属柱体68上にその他のデバイス製作方式は同じステップである。

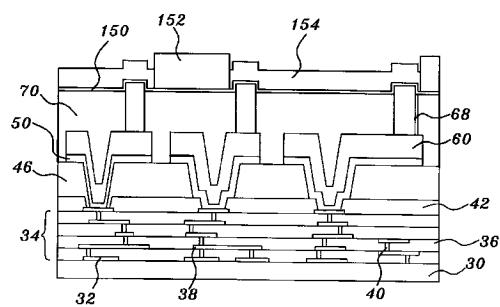

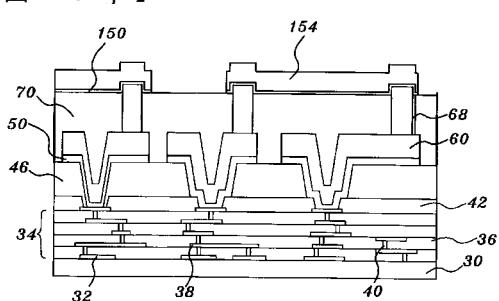

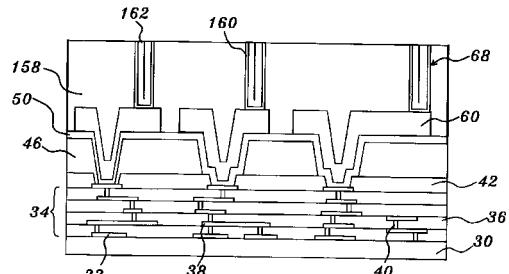

図21aから図21dで示すように、この図は第九図案化重合物層158及び金属柱体68上に、突出塊・パッド・錫ボールとRDL層の製作を掲示し、その製作過程の部分は上記の実施例で説明したので、ここでは最終の完成構造のみを掲示し、製作過程の部分は略す。

#### 【0102】

図22から図25で示すように、この図は第九図案化重合物層158及び金属柱体68上に、メタルは路線を接続する(interconnection)・コイル・コンデンサー・バイス・抵抗デバイスを掲示し、その製作過程の部分は上記の実施例で説明したので、ここでは最終の完成構造のみを掲示し、製作過程の部分は略す。

本発明はストレスリリーフと接触窓構造の間隔距離の微小化を提供し、本発明に基づくと、その間隔距離は250μm以下で、かつピンホール数を400個以下の目標に抑えることも達成できる。またIC機能の改善が認められ、かつ低電源ICエレメントのIC金属接続線路の抵抗及び負荷を大幅に下げることが可能である。

#### 【0103】

以上論述したのは実施例で本発明の特徴を説明し、その目的はこの技術を熟知している者が本発明の内容をよく理解し、それに従って実施するのみであって、本発明の請求範囲を限定するものではない。ゆえに、他の本発明で掲示した精神から逸脱することなく、修飾または修正によって、完成した同効力のものは、下記で述べる請求範囲に含まれるべきである。

#### 【図面の簡単な説明】

##### 【0104】

【図1】従来技術の断面説明図。

【図2】本発明の第一実施例による半導体基部の断面説明図。

【図3】本発明の第一実施例による半導体基部上に細い接続構造及び保護層設置時の断面説明図。

【図4a】本発明の第一実施例で形成された第一重合物層の断面説明図。

【図4b】本発明の第一実施例で形成された第一重合物層の断面説明図。

【図5】本発明の第一実施例で形成された第一粘着/阻害層の断面説明図。

【図6a】本発明の第一実施例で形成された第一RDL層及び金属柱体の断面説明図。

【図6b】本発明の第一実施例で形成された第一RDL層及び金属柱体の断面説明図。

【図6c】本発明の第一実施例で形成された第一RDL層及び金属柱体の断面説明図。

【図6d】本発明の第一実施例で形成された第一RDL層及び金属柱体の断面説明図。

【図6e】本発明の第一実施例で形成された第一RDL層及び金属柱体の断面説明図。

【図7a】本発明の第一実施例で形成された金属柱体物性の説明図。

【図7b】本発明の第一実施例で形成された金属柱体物性の平面図。

【図8a】本発明の第一実施例で形成された第二重合物層の断面説明図。

【図8b】本発明の第一実施例で形成された第二重合物層開口の断面説明図。

【図8c】本発明の第一実施例で研磨した第二重合物層の断面説明図。

【図9】本発明の第一実施例で形成された第三重合物層の断面説明図。

【図10a】本発明の第一実施例で形成された第三金属層の断面説明図。

【図10b】本発明の第一実施例で形成された第三金属層の断面説明図。

【図10c】本発明の第一実施例で形成された第三金属層の断面説明図。

【図10d】本発明の第一実施例で形成された第三金属層の断面説明図。

10

20

30

40

50

- 【図11】本発明の第一実施例の半導体基部カット時の断面説明図。

- 【図12a】本発明の第一実施例で形成された錫ボールの断面説明図。

- 【図12b】本発明の第一実施例で形成された錫ボールの断面説明図。

- 【図12c】本発明の第一実施例で形成された錫ボールの断面説明図。

- 【図12d】本発明の第一実施例の半導体基部カット時及び基板に接合する断面説明図。

- 【図12e】本発明の第一実施例の半導体基部カット時及び基板に接合する断面説明図。

- 【図13a】本発明の第一実施例の金属柱体ワイヤー製作過程時の断面説明図。

- 【図13b】本発明の第一実施例の金属柱体ワイヤー製作過程時の断面説明図。

- 【図14a】本発明の第一実施例で形成されたRDL層が金属柱体上の断面説明図。

- 【図14b】本発明の第一実施例で形成されたRDL層が金属柱体上の断面説明図。

- 【図15a】本発明の第二実施例の銅／ニッケル／金或いは銅／金の金属柱体ワイヤー製作時の断面説明図。

- 【図15b】本発明の第二実施例の銅／ニッケル／金或いは銅／金の金属柱体ワイヤー製作時の断面説明図。

- 【図15c】本発明の第二実施例の銅／ニッケル／金或いは銅／金の金属柱体ワイヤー製作時の断面説明図。

- 【図16a】本発明の第三実施例で形成された第一コイル金属層が金属柱体上の断面説明図。

- 【図16b】本発明の第三実施例で形成された第一コイル金属層が金属柱体上の断面説明図。

- 【図16c】本発明の第三実施例で形成された第一コイル金属層が金属柱体上の断面説明図。

- 【図16d】本発明の第三実施例で形成された第一コイル金属層が金属柱体上の断面説明図。

- 【図16e】本発明の第三実施例で形成された第一コイル金属層が金属柱体上の断面説明図。

- 【図16f】本発明の第三実施例で形成された第一コイル金属層が金属柱体上の断面説明図。

- 【図16g】本発明の第三実施例で形成された第二コイル金属層の断面説明図。

- 【図16h】本発明の第三実施例で形成されたコンデンサーデバイスが金属柱体上の断面説明図。

- 【図17a】本発明の第四実施例で形成された二つの金属柱体の金属層と接続時の断面説明図。

- 【図17b】本発明の第四実施例で形成された二つの金属柱体の金属層と接続時の断面説明図。

- 【図17c】本発明の第四実施例で形成された二つの金属柱体の金属層と接続時の断面説明図。

- 【図17d】本発明の第四実施例で形成された二つの金属柱体の金属層と接続時の断面説明図。

- 【図17e】本発明の第四実施例で形成された多層線路層が金属柱体上の断面説明図。

- 【図17f】本発明の第四実施例で形成された多層線路層が金属柱体上の断面説明図。

- 【図17g】本発明の第四実施例で形成された多層線路層が金属柱体上の断面説明図。

- 【図17h】本発明の第四実施例で形成された多層線路層が金属柱体上の断面説明図。

- 【図17i】本発明の第四実施例で形成された多層線路層が金属柱体上の断面説明図。

- 【図17j】本発明の第四実施例で形成された多層線路層が金属柱体上の断面説明図。

- 【図17k】本発明の第四実施例で形成された多層線路層が金属柱体上の断面説明図。

- 【図17l】本発明の第四実施例で形成された多層線路層が金属柱体上の断面説明図。

- 【図17m】本発明の第四実施例で形成された多層線路層が金属柱体上の断面説明図。

- 【図18】本発明の第五実施例で形成された抵抗デバイスが金属柱体上の断面説明図。

- 【図19a】本発明の第六実施例で利用したエッチング方式で一部分の第二重合物層を除

去した断面説明図。

【図19b】本発明の第六実施例で利用したエッティング方式で一部分の第二重合物層を除去した断面説明図。

【図19c】本発明の第六実施例の半導体基部カット時の断面説明図。

【図19d】本発明の第六実施例で形成された錫ボールとカットステップの断面説明図。

【図19e】本発明の第六実施例で形成された錫ボールとカットステップの断面説明図。

【図19f】本発明の第六実施例で形成されたパッドの断面説明図。

【図19g】本発明の第六実施例で形成された二つの金属柱体の金属層と接続時の断面説明図。

【図19h】本発明の第六実施例で形成された二つの金属柱体の金属層と接続時の断面説明図。 10

【図19i】本発明の第六実施例で形成された二つの金属柱体の金属層と接続時の断面説明図。

【図19j】本発明の第六実施例で形成された二つの金属柱体の金属層と接続時の断面説明図。

【図19k】本発明の第六実施例で形成された二つの金属柱体の金属層と接続時の断面説明図。

【図20a】本発明の第七実施例で形成された第九図案化重合物層が半導体基部上の断面説明図。

【図20b】本発明の第七実施例のダマシン方式で形成された金属柱体の断面説明図。 20

【図20c】本発明の第七実施例のダマシン方式で形成された金属柱体の断面説明図。

【図20d】本発明の第七実施例のダマシン方式で形成された金属柱体の断面説明図。

【図21a】本発明のその他の実施例で形成された突出塊・パッド・錫ボール・RDL層構造の断面説明図。

【図21b】本発明のその他の実施例で形成された突出塊・パッド・錫ボール・RDL層構造の断面説明図。

【図21c】本発明のその他の実施例で形成された突出塊・パッド・錫ボール・RDL層構造の断面説明図。

【図21d】本発明のその他の実施例で形成された突出塊・パッド・錫ボール・RDL層構造の断面説明図。 30

【図22】本発明のその他の実施例で形成された快速電流通路(freeway)・コイル・コンデンサー・抵抗デバイス構造の断面説明図。

【図23】本発明のその他の実施例で形成された快速電流通路(freeway)・コイル・コンデンサー・抵抗デバイス構造の断面説明図。

【図24】本発明のその他の実施例で形成された快速電流通路(freeway)・コイル・コンデンサー・抵抗デバイス構造の断面説明図。

【図25】本発明のその他の実施例で形成された快速電流通路(freeway)・コイル・コンデンサー・抵抗デバイス構造の断面説明図。

#### 【符号の説明】

##### 【0105】

10 : ポストパッショナリゼーション構造、12 : RDL層、14 : 重合物層、16 : 保護層、

18 : 半導体ICチップ、20 : パッド、22 : 斜面、30 : 半導体基部、32 : 電子エレメント、34 : 細い接続構造、36 : 薄膜絶縁層、38 : 細い線路層、40 : スルーホール、42 : 保護層、44 : パッド、46 : 第一重合物層、48 : 開口、50 : 第一粘着/阻害層、54 : 第一図案化ハーダンフォトレジスト層、56 : 開口、58 : 第一金属層、60 : 第一RDL層、62 : 第二図案化ハーダンフォトレジスト層、64 : 開口、66 : 第二金属層、68 : 金属柱体、70 : 第二重合物層、72 : 開口、74 : 第三重合物層、76 : 開口、78 : 第二粘着/阻害層、82 : 第三図案化ハーダンフォトレジスト層、83 : 開口、84 : 第三金属層、86 : 突出塊、88 : 半導体ユニット、92 : 錫ボール、94 : 基板、96 : 第四重合物層、98 : パッド、100 : RDL層、102 : 金層、1 40

04: 銅層、105: 第三粘着/阻害層、106: ニッケル層、110: 第四図案化ハーダンフォトレジスト層、112: 開口、114: 第四金属層、116: 第一コイル金属層、117: 保護層、118: 第五重合物層、120: 第二コイル金属層、121: コンデンサーデバイス、121a: 低誘電層、121b: 絶縁層、121c: 低抵抗金属層、121d: 保護層、122: 第四粘着/阻害層、126: 第五図案化ハーダンフォトレジスト層、128: 開口、130: 第五金属層、132: 保護層、134: 第六重合物層、136: 第五粘着/阻害層、140: 第六図案化ハーダンフォトレジスト層、142: 第六金属層、144: 第七重合物層、146: 第七金属層、148: 第八重合物層、150: 第六粘着/阻害層、152: 第七図案化ハーダンフォトレジスト層、154: 第八金属層、156: 保護層、158: 第九図案化重合物層、160: 第七粘着/阻害層、162: 第九金属層

10

第九金属層

【図1】

【図2】

【図3】

【図4a】

【図4b】

【図5】

【図 6 a】

【図 6 b】

【図 6 c】

【図 6 d】

【図 6 e】

【図 7 a】

【図 7 b】

【図 8 a】

【図 8 b】

【図 8 c】

【図 9】

【図 10 a】

【図 10 b】

【図 10 d】

【図 10 c】

【図11】

【図12a】

【図12b】

【図12c】

【図12d】

【図 1 2 e】

【図 1 3 a】

【図 1 3 b】

【図 1 4 a】

【図 1 5 a】

【図 1 4 b】

【図 1 5 b】

【図 1 5 c】

【図 1 6 b】

【図 1 6 a】

【図 1 6 c】

【図 1 6 d】

【図 1 6 f】

【図 1 6 e】

【図 1 6 g】

【図16h】

【図17a】

【図17d】

【図17e】

【図17b】

【図17c】

【図17f】

【図17g】

【図17h】

【図17i】

【図17j】

【図17k】

【図17l】

【図17m】

【図18】

【図19a】

【図19b】

【図19c】

【図19d】

【図19e】

【図19f】

【図19g】

【図 19 h】

【図 19 i】

【図 19 j】

【図 19 k】

【図 20 a】

【図 20 b】

【図 20 c】

【図 20 d】

【図21a】

【図21b】

【図21c】

【図21d】

【図22】

【図24】

【図23】

【図25】

---

フロントページの続き

F ターム(参考) 5F033 HH07 HH08 HH11 HH13 HH14 HH18 HH21 HH23 HH32 JJ01

JJ07 JJ08 JJ11 JJ13 JJ14 JJ18 JJ21 JJ23 JJ32 JJ33

KK07 KK08 KK11 KK13 KK14 MM01 MM05 MM13 NN06 NN07

PP15 PP27 QQ08 QQ48 QQ74 RR04 RR06 RR08 RR09 RR11

RR14 RR15 RR21 RR22 RR29 SS04 SS11 SS15 SS21 SS22

TT01 VV07 VV09 VV10 WW01 WW02 XX19