(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

**特許第4357576号

(P4357576)**

(45) 発行日 平成21年11月4日(2009.11.4)

(24) 登録日 平成21年8月14日(2009.8.14)

(51) Int.Cl.

**F02D 45/00 (2006.01)**

F 1

F O 2 D 45/00 3 7 6 F

F O 2 D 45/00 3 7 6 E

請求項の数 2 (全 14 頁)

(21) 出願番号 特願2008-112537 (P2008-112537)

(22) 出願日 平成20年4月23日 (2008.4.23)

(62) 分割の表示 特願2004-291291 (P2004-291291)

分割

原出願日 平成16年10月4日 (2004.10.4)

(65) 公開番号 特開2008-180234 (P2008-180234A)

(43) 公開日 平成20年8月7日 (2008.8.7)

審査請求日 平成20年4月23日 (2008.4.23)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100110423

弁理士 曽我 道治

(74) 代理人 100084010

弁理士 古川 秀利

(74) 代理人 100094695

弁理士 鈴木 憲七

(74) 代理人 100111648

弁理士 梶並 順

(74) 代理人 100122437

弁理士 大宅 一宏

(74) 代理人 100147566

弁理士 上田 俊一

最終頁に続く

(54) 【発明の名称】電子制御装置

## (57) 【特許請求の範囲】

## 【請求項 1】

バッテリからイグニッシュョンスイッチによって応動する開閉素子と主電源回路を介して給電されて動作するマイクロプロセッサと、上記主電源回路を介して給電されると共に上記バッテリから副電源回路を介して常時給電され、主電源回路から給電されない状態であっても副電源回路からの給電によりデータが保持されて、更新されるデータを一時記憶する揮発性メモリと、を備えた電子制御装置であって、

上記バッテリから上記副電源回路を介して上記揮発性メモリへ給電が行われた後の、上記イグニッシュョンスイッチの1回目のオンであることを示す初回起動信号を発生する初回起動信号発生手段と、

上記バッテリと上記副電源回路との接続点にバッテリ配線断線検出回路を有し、上記イグニッシュョンスイッチがオンされて上記マイクロプロセッサに上記主電源回路から給電がある状態で、上記バッテリから上記副電源回路を介して上記揮発性メモリへ給電が行われていないことを上記バッテリ配線断線検出回路を通じ検出した場合に副電源給電異常信号を発生する副電源給電異常信号発生手段と、

上記初回起動信号に従って、上記揮発性メモリへ給電が行われた後の上記イグニッシュョンスイッチの1回目のオン時に上記揮発性メモリの初期化を行う第1の揮発性メモリ初期化手段と、

上記イグニッシュョンスイッチがオンされて上記マイクロプロセッサに上記主電源回路から給電が開始された時に、上記副電源給電異常信号が発生されれば、上記初回起動信

号の状態を無視して上記揮発性メモリの初期化を行う第2の揮発性メモリ初期化手段と、上記副電源給電異常信号に基づきユーザへ警告を発生する副電源給電異常警告手段と、を備え、

上記初回起動信号発生手段は上記イグニッシュョンスイッチがオフしている状態で、上記副電源の給電が一旦切られてから再接続され、その後に上記イグニッシュョンスイッチが再びオンしたことを示す第1レベルにより1回目のオンであることを記憶し、その後この記憶に基づき上記マイクロプロセッサに上記初回起動信号となる信号を発生し、上記第1レベルを第2レベルとすることにより2回目以降と判断できるように動作するラッチ手段を有し、上記第1の揮発性メモリ初期化手段は上記初回起動信号に基づいて上記揮発性メモリの初期化を行い、

上記イグニッシュョンスイッチがオンしている状態で、上記マイクロプロセッサが上記副電源給電異常信号発生手段の発生する副電源給電異常信号に従い、上記副電源給電異常と判定した場合に、上記第2の揮発性メモリ初期化手段を動作させない初期化禁止手段をさらに備え、

上記副電源給電異常警告手段が、上記初期化禁止手段により上記第2の揮発性メモリ初期化手段を動作させない場合にも、上記イグニッシュョンスイッチがオンされている状態での上記副電源給電異常信号に基づき、ユーザへ警告を発生し、

上記初回起動信号発生手段は上記ラッチ手段を構成するラッチ回路と判定回路とラッチセット回路によって構成され、

上記ラッチ回路は上記イグニッシュョンスイッチがオフしている状態で、上記バッテリの接続が一旦切られてから再接続され、その後に上記イグニッシュョンスイッチが再びオンしたときに出力信号が上記第1レベルのリセット状態となる記憶回路であり、

上記判定回路は上記記憶回路の出力信号の論理レベルを判定して上記マイクロプロセッサに上記初回起動信号となる判定信号を入力する回路であり、

上記ラッチセット回路は上記マイクロプロセッサが発生したセット指令信号によって、上記ラッチ回路に対してセット信号を供給して上記第2レベルの出力信号にする回路であり、

上記第1の揮発性メモリ初期化手段は上記ラッチ回路と判定回路を介して入力された上記初回起動信号に基づいて上記揮発性メモリの初期化を行ってから、上記ラッチセット回路を介して上記ラッチ回路をセットし、

上記初期化禁止手段は、上記副電源給電異常信号発生手段が発生する副電源給電異常信号に従い、上記マイクロプロセッサが副電源給電異常信号と判定した時に、上記イグニッシュョンスイッチがオンした直後の初回動作では上記第2の揮発性メモリ初期化手段が有効とし、上記イグニッシュョンスイッチがオンしている状態で上記副電源給電異常信号が発生した場合には上記第2の揮発性メモリ初期化手段を動作させない

ことを特徴とする電子制御装置。

## 【請求項2】

上記副電源給電異常信号に従い、上記マイクロプロセッサが副電源給電異常と判定した時に、これを記憶する副電源給電異常記憶手段をさらに備えたことを特徴とする請求項1に記載の電子制御装置。

## 【発明の詳細な説明】

### 【技術分野】

### 【0001】

この発明は、例えば自動車の内燃機関の制御に使用される、データを保持する揮発性のメモリを備えた電子制御装置に関する。

## 【背景技術】

### 【0002】

内燃機関において、燃料噴射量や空気量、点火時期などのデータは、ばらつきや経年劣化により予め設定されているデータとの誤差が生じる。このような誤差は電子制御装置内のマイクロプロセッサによって演算され、演算結果を元に燃料噴射量や空気量等の誤差補

正を行っている。そしてこのような誤差補正はマイクロプロセッサによって誤差補正データとして揮発性メモリとしての例えばRAMに記憶され、イグニッションスイッチがオフであってバッテリから主電源回路を介して給電されていない状態であっても、RAMはバッテリから副電源回路を介して常時給電されているため誤差補正データは保持される。

#### 【0003】

内燃機関に使用されているアクチュエータやセンサ等の故障状況はマイクロプロセッサにより監視し、故障と判断すると故障データをRAMに記憶する。

#### 【0004】

電子制御装置に給電するバッテリは劣化等の理由により交換される場合がある。また、RAMに記憶した故障データを初期化するためにバッテリを取り外すこともある。バッテリから副電源回路を介しての給電が停止された時、給電が停止されている時間によっては消去が不十分な状態となるためRAMに記憶された誤差補正データや故障データは不定値となる。不定値となった誤差補正データや故障データを用いて内燃機関の制御を実施すると、排気ガスの悪化や、ドライバビリティの悪化が発生する。従ってバッテリを再取り付け後に、イグニッションスイッチがオンされる時、マイクロプロセッサでRAMの初期化を行う必要がある。

10

#### 【0005】

たとえば、特許文献1では、制御データと、制御データの反転したデータとを1組のデータとしてRAMに記憶し、バッテリからの副電源回路を介しての給電が停止された時、給電が停止されている時間によっては消去が不十分な状態となるため、RAMに記憶された誤差補正データは不定値となり、制御データと反転データの反転値が等しくならないことを用いてRAMを初期化する条件としている。

20

#### 【0006】

【特許文献1】特開平6-250940号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

上記のような電子制御装置のRAMの初期化判定条件を用いると、バッテリを取り外した際にRAMに記憶された一部のデータのみが不定値となった場合に、制御データと反転データの反転値が等しくなる可能性があり、RAMの初期化が行われず、排気ガスの悪化や、ドライバビリティの悪化するような制御データとなっている可能性があった。

30

#### 【0008】

また、制御データとともに反転データも記憶する容量が必要となるため、RAMの必要な記憶容量が2倍になってしまっていた。

#### 【0009】

また、制御データと反転データの反転値を比較する処理はイグニッションスイッチをオンした後の内燃機関を始動する前に必要なので、RAMの全領域のデータを比較する必要がある場合もあり、内燃機関が始動可能な状態になるまでに時間を要する場合があった。

#### 【0010】

この発明は、余分なメモリ容量や時間を必要とせず、速やかに揮発性メモリの初期化の要否を判定する電子制御装置を提供することを目的とする。特に、揮発性メモリへ給電が開始された後の最初のマイクロプロセッサの動作開始時にのみ揮発性メモリの初期化を行うようにしたり、また揮発性メモリへの給電状態に基づき揮発性メモリの初期化の要否を判定するようにした。

40

#### 【課題を解決するための手段】

#### 【0011】

この発明は、バッテリからイグニッションスイッチによって応動する開閉素子と主電源回路を介して給電されて動作するマイクロプロセッサと、上記主電源回路を介して給電されると共に上記バッテリから副電源回路を介して常時給電され、主電源回路から給電されない状態であっても副電源回路からの給電によりデータが保持されて、更新されるデータ

50

を一時記憶する揮発性メモリと、を備えた電子制御装置であって、上記バッテリから上記副電源回路を介して上記揮発性メモリへ給電が行われた後の、上記イグニッシュョンスイッチの1回目のオンであることを示す初回起動信号を発生する初回起動信号発生手段と、上記バッテリと上記副電源回路との接続点にバッテリ配線断線検出回路を有し、上記イグニッシュョンスイッチがオンされて上記マイクロプロセッサに上記主電源回路から給電がある状態で、上記バッテリから上記副電源回路を介して上記揮発性メモリへ給電が行われていないことを上記バッテリ配線断線検出回路を通じ検出した場合に副電源給電異常信号を発生する副電源給電異常信号発生手段と、上記初回起動信号に従って、上記揮発性メモリへ給電が行われた後の上記イグニッシュョンスイッチの1回目のオン時に上記揮発性メモリの初期化を行う第1の揮発性メモリ初期化手段と、上記イグニッシュョンスイッチがオンされて上記マイクロプロセッサに上記主電源回路から給電が開始された時に、上記副電源給電異常信号が発生されれば、上記初回起動信号の状態を無視して上記揮発性メモリの初期化を行う第2の揮発性メモリ初期化手段と、上記副電源給電異常信号に基づきユーザへ警告を発生する副電源給電異常警告手段と、を備え、上記初回起動信号発生手段は上記イグニッシュョンスイッチがオフしている状態で、上記副電源の給電が一旦切られてから再接続され、その後に上記イグニッシュョンスイッチが再びオンしたことを示す第1レベルにより1回目のオンであることを記憶し、その後この記憶に基づき上記マイクロプロセッサに上記初回起動信号となる信号を発生し、上記第1レベルを第2レベルとすることにより2回目以降と判断できるように動作するラッチ手段を有し、上記第1の揮発性メモリ初期化手段は上記初回起動信号に基づいて上記揮発性メモリの初期化を行い、上記イグニッシュョンスイッチがオンしている状態で、上記マイクロプロセッサが上記副電源給電異常信号発生手段の発生する副電源給電異常信号に従い、上記副電源給電異常と判定した場合に、上記第2の揮発性メモリ初期化手段を動作させない初期化禁止手段をさらに備え、上記副電源給電異常警告手段が、上記初期化禁止手段により上記第2の揮発性メモリ初期化手段を動作させない場合にも、上記イグニッシュョンスイッチがオンされている状態での上記副電源給電異常信号に基づき、ユーザへ警告を発生し、上記初回起動信号発生手段は上記ラッチ手段を構成するラッチ回路と判定回路とラッチセット回路によって構成され、上記ラッチ回路は上記イグニッシュョンスイッチがオフしている状態で、上記バッテリの接続が一旦切られてから再接続され、その後に上記イグニッシュョンスイッチが再びオンしたときに出力信号が上記第1レベルのリセット状態となる記憶回路であり、上記判定回路は上記記憶回路の出力信号の論理レベルを判定して上記マイクロプロセッサに上記初回起動信号となる判定信号を入力する回路であり、上記ラッチセット回路は上記マイクロプロセッサが発生したセット指令信号によって、上記ラッチ回路に対してセット信号を供給して上記第2レベルの出力信号にする回路であり、上記第1の揮発性メモリ初期化手段は上記ラッチ回路と判定回路を介して入力された上記初回起動信号に基づいて上記揮発性メモリの初期化を行ってから、上記ラッチセット回路を介して上記ラッチ回路をセットし、上記初期化禁止手段は、上記副電源給電異常信号発生手段が発生する副電源給電異常信号に従い、上記マイクロプロセッサが副電源給電異常信号と判定した時に、上記イグニッシュョンスイッチがオンした直後の初回動作では上記第2の揮発性メモリ初期化手段が有効とし、上記イグニッシュョンスイッチがオンしている状態で上記副電源給電異常信号が発生した場合には上記第2の揮発性メモリ初期化手段を動作させないことを特徴とする電子制御装置にある。

#### 【発明の効果】

#### 【0012】

この発明では、余分なメモリ容量や時間を必要とせずに、速やかに揮発性メモリの初期化の要否を判定する。特に、揮発性メモリへ給電が開始された後の最初のイグニッシュョンスイッチがオンされてマイクロプロセッサが動作を開始した時にのみ、揮発性メモリの初期化を行うようにしたり、また揮発性メモリへの給電状態に基づき揮発性メモリの初期化の要否を判定したことにより、揮発性メモリの初期化の効率化が図られた。

#### 【発明を実施するための最良の形態】

#### 【0013】

10

20

30

40

50

### 実施の形態 1 .

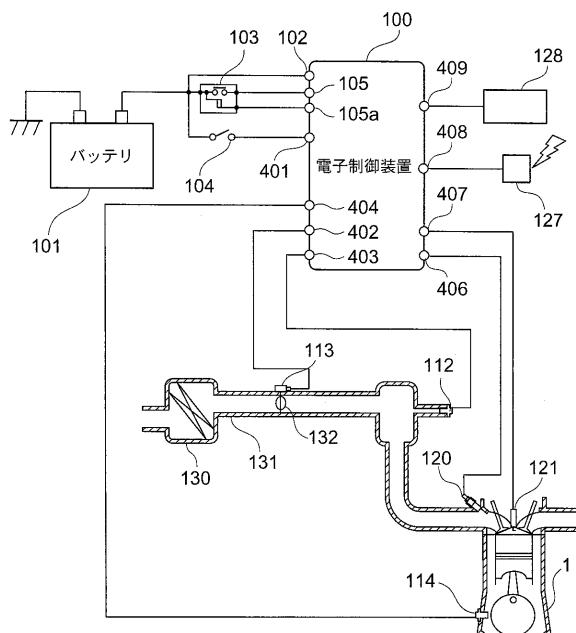

図1はこの発明による電子制御装置を設けた内燃機関の制御系の概略構成図である。内燃機関1において、吸気管131を介して吸入される空気はエアークリーナ130により浄化され、スロットル132により空気量が調整される。この吸入される空気量は吸気管131内に設置された圧力センサ112によって検出される。また、スロットル132の開度を検出するスロットル開度センサ113と、内燃機関1の回転角を検出する内燃機関回転角検出センサ114と、圧力センサ112との検出信号が電子制御装置100に入力され、内燃機関1の状態を認識し、内燃機関1に供給する燃料噴射量を調整する燃料噴射用インジェクタ120や点火装置121が制御される。

#### 【0014】

10

電子制御装置100は内燃機関1の制御ばらつきを押さえるため、予め記憶しているデータを基に制御ばらつき量の補正データを記憶する機能を有する。また、電子制御装置100は内燃機関1の状態や、圧力センサ112やスロットル開度センサ113等のセンサの故障の判定も行なっており、その故障情報や内燃機関1の状態を警告装置127やサービス用テスタ128を介して外部のユーザ等に伝達する。補正データや故障情報は電子制御装置100内に保持される。さらに電子制御装置100は電源リレー103やイグニッションスイッチ104を介してバッテリ101より給電される。電子制御装置100の符号を付けた各端子は図2のものに対応する。

#### 【0015】

20

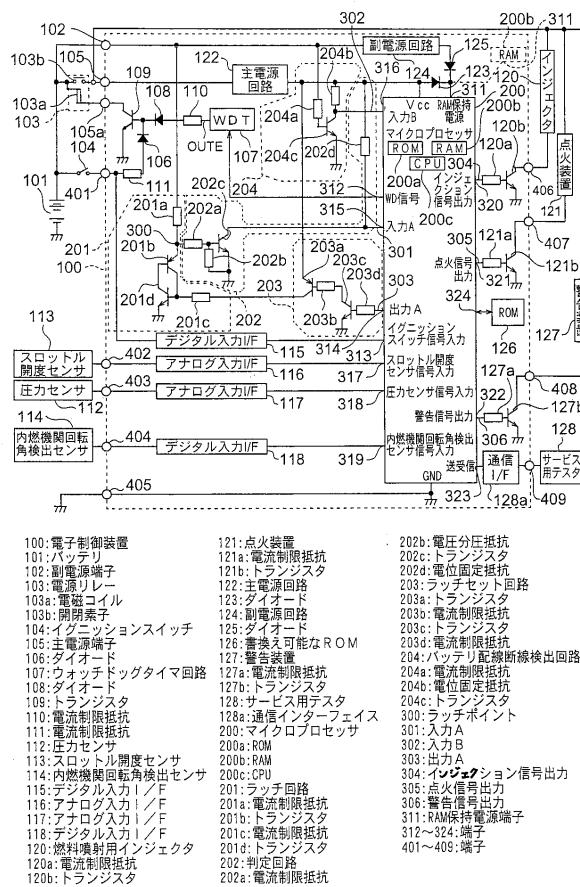

図2は電子制御装置100の構成の一例を示すものである。電子制御装置100にはバッテリ101が、このバッテリ101から常時給電される副電源端子102において接続され、副電源端子102は副電源回路124とダイオード125を介してマイクロプロセッサ200のRAM保持電源端子311に接続されている。

#### 【0016】

30

電子制御装置100にはまた、バッテリ101がイグニッションスイッチ104を介して端子401において接続され、端子401は電流制限抵抗111とダイオード106とを介してトランジスタ109のベースに接続され、トランジスタ109のコレクタは端子105aを介して電源リレー103の電磁コイル103aの一端に接続されていて、電磁コイル103aの他端はバッテリ101に接続されている。トランジスタ109のエミッタは接地されている。イグニッションスイッチ104をオンすることによりトランジスタ109のベースに給電が行われると、電磁コイル103aからトランジスタ109のコレクタに電流が流れ、電源リレー103の開閉素子103bはオン(閉じる)する。開閉素子103bは一端がバッテリ101、他端が主電源端子105に接続され、主電源端子105は主電源回路122を介してマイクロプロセッサ200のVcc端子に接続され、開閉素子103bがオンすることでバッテリ101からマイクロプロセッサ200に給電されてマイクロプロセッサ200は動作を開始する。

#### 【0017】

40

また、マイクロプロセッサ200が正しく動作している時に端子312より発生するWD信号により、ウォッチドッグタイマ(WDT)回路107は”Hi(H)”レベルを出力し(OUTE信号)、電流制限抵抗110とダイオード108を介してトランジスタ109のベースに”Hi”レベル信号が供給される。従って電磁コイル103aからトランジスタ109のコレクタに電流が流れ、電源リレー103の開閉素子103bはオンする。従ってマイクロプロセッサ200が正しく動作していればイグニッションスイッチ104がオフされてもマイクロプロセッサ200への給電は維持される。そしてイグニッションスイッチ104がオフになったことを示すイグニッションスイッチ信号がデジタル入力I/F(インターフェイス)115を介してマイクロプロセッサ200の端子313に入力されると、マイクロプロセッサ200はイグニッションスイッチ104がオフになったことを認識する。そしてマイクロプロセッサ200のCPU200cは動作停止処理を行い、動作停止処理終了時にWD信号が停止されてウォッチドッグタイマ(WDT)回路107の出力が”Lo(L)”レベルになると、開閉素子103bはオフ(開放)して、主電源端子105

50

を介しての給電は停止される。

**【0018】**

電子制御装置100はバッテリ101とこれにより常時給電される副電源端子102でも接続されて、副電源回路124とダイオード125を介してマイクロプロセッサ200のRAM保持電源端子311に給電がされていれば、開閉素子103bの状態に関わらず、補正データや故障情報のような更新される回数の多いデータがマイクロプロセッサ200内の揮発性メモリとしての例えばRAM200bに一時記憶される。

**【0019】**

主電源回路122からマイクロプロセッサ200のVcc端子に給電されている場合は、ダイオード123を介してRAM保持電源端子311にも給電される。尚、ダイオード123、125はトランジスタの論理回路などを用いて構成してもよい。また、マイクロプロセッサ200の内部に示されているRAM200bは、RAM保持電源端子311と同様の端子を有するRAM(破線で示す)をマイクロプロセッサ200の外部に接続するようにしてよい。

10

**【0020】**

ラッチ回路201(201a～201d、300を含む)において、副電源端子102に接続された電流制限抵抗201aはトランジスタ201bのエミッタに接続され、トランジスタ201bのベースはトランジスタ201dのコレクタに接続され、トランジスタ201bのコレクタはトランジスタ201dのベースに接続され、トランジスタ201dのベースにはさらに電流制限抵抗201cが接続され、トランジスタ201dのエミッタは接地されている。そして電流制限抵抗201cに給電が行われれば、電流制限抵抗201cへの給電停止後も、トランジスタ201bと201dはオン状態となり、電流制限抵抗201aを介してトランジスタ201bのエミッタに流れる電流が遮断するまで、トランジスタ201bとトランジスタ201dのオン状態を維持し、ラッチポイント300が”Lo”レベルに保持される。

20

**【0021】**

ラッチセット回路203(203a～203dを含む)において、マイクロプロセッサ200の端子314から出力A303が電流制限抵抗203dを介してトランジスタ203cのベースに接続され、トランジスタ203cのコレクタが電流制限抵抗203bを介してトランジスタ203aのベースに接続され、トランジスタ203cのエミッタは接地されている。トランジスタ203aのコレクタはラッチ回路201の電流制限抵抗201cに接続され、トランジスタ203aのエミッタは主電源回路122に接続されている。マイクロプロセッサ200の端子314からの出力A303が”Hi”レベルを示すとトランジスタ203cと203aは共にオンし、これにより主電源回路122からラッチ回路201の電流制限抵抗201cに給電を行う。

30

**【0022】**

ラッチ回路201のトランジスタ201bのエミッタであるラッチポイント300は、副電源端子102から給電されている時にラッチセット回路203により”Lo”レベルにされれば、副電源端子102から給電されている限り”Lo”レベルを維持する。

40

**【0023】**

判定回路202(202a～202dを含む)において、トランジスタ202cのベースには電流制限抵抗202aを介してラッチ回路201のラッチポイント300が接続され、またトランジスタ202cのベース-エミッタ間に電圧分圧抵抗202bが接続され、さらにトランジスタ202cのエミッタは接地されている。トランジスタ202cのコレクタは電位固定抵抗202dの一端およびマイクロプロセッサ200の入力A301の端子315に接続されている。また電位固定抵抗202dの他端は主電源回路122に接続されている。そして主電源回路122が給電状態でラッチポイント300が”Lo”であれば、マイクロプロセッサ200の入力A301は”Hi”レベルとなり、ラッチポイント300が”Hi”であればマイクロプロセッサ200の入力A301は”Lo”レベルとなる。

50

## 【0024】

バッテリ配線断線検出回路204(204a～204cを含む)において、バッテリ101が副電源端子102を介して電流制限抵抗204aの一端に接続され、電流制限抵抗204aの他端はトランジスタ204cのベースに接続され、トランジスタ204cのコレクタはマイクロプロセッサ200の入力B302が入力される端子316と電位固定抵抗204bの一端とに接続され、電位固定抵抗204bの他端は主電源回路122に接続される。イグニッシュョンスイッチ104をオンして主電源回路122が給電をしている状態で、バッテリ101が副電源端子102を介して電流制限抵抗204aに給電している時は、マイクロプロセッサ200の入力B302は”Lo”となり、バッテリ101が副電源端子102を介して電流制限抵抗204aに給電していない時はマイクロプロセッサ200の入力B302は”Hi”となり、副電源供給異常が判定できるようになっている。尚、電流制限抵抗204aの接続元は副電源回路124とダイオード125の間でもかまわないのである。

## 【0025】

さらに外部のスロットル開度センサ113、圧力センサ112、内燃機関回転角検出センサ114が、電子制御装置100の端子402～404、アナログ入力I/F116、117、デジタル入力I/F118を介してマイクロプロセッサ200の端子317～319にそれぞれに接続され、スロットル開度センサ信号、圧力センサ信号、内燃機関回転角検出センサ信号を入力する(アナログ信号はマイクロプロセッサ200内でA/D変換されて使用される)。また、外部の燃料噴射用インジェクタ120、点火装置121、警告装置127を、マイクロプロセッサ200の端子320～322からのインジェクション信号出力304、点火信号出力305、警告信号出力306によりそれぞれ、電流制限抵抗120a、121a、127a、トランジスタ120b、121b、127b、電子制御装置100の端子406～408を介して制御する。また、マイクロプロセッサ200の端子323と電子制御装置100の端子409間の通信I/F128aを介してサービス用テスト128と通信を行い、さらにマイクロプロセッサ200の端子324には書き換え可能なROM126が接続されている。

## 【0026】

この発明は、バッテリ101からイグニッシュョンスイッチ104によって応動する開閉素子103bと主電源回路122を介して給電されて動作するマイクロプロセッサ200と、バッテリ101から副電源回路124を介して常時給電され、更新される回数の多いデータを一時記憶する不揮発性のRAM200bとを備え、主電源回路122から給電されていない状態であっても副電源回路124からの給電によってRAM200bのデータが保持される電子制御装置100に関するものである。このような構成の装置の場合、バッテリ101が取り外されてしまうと、その間はRAM200bにおける消去が不十分な状態となることが起こり得る。このような不十分なデータの消去はデータを不確定なものにする。そこでこのような不確定なRAM200bのデータを制御に用いないようにするために、バッテリ101を副電源回路124に接続し、RAM200bに給電が行われた後のイグニッシュョンスイッチ104の1回目のオンと2回目以降のオンとを判別するための初回起動信号(1回目のオンを示す)を発生するようにし、マイクロプロセッサ200の起動時に、RAMの初期化を行なうか否かの判定を行うためにこの初回起動信号を用いるようにした。そしてマイクロプロセッサ200は、RAM200bに給電が行われた後のイグニッシュョンスイッチ104の1回目のオンであれば、RAMの初期化を行なうようにした。

## 【0027】

初回起動信号の発生に関し、バッテリ101が副電源端子102に接続されて副電源回路124から給電が行われるようになってからイグニッシュョンスイッチ104の1回目のオンでは、マイクロプロセッサ200の入力A301は”Lo”レベルであり、イグニッシュョンスイッチ104の1回目のオンの時にマイクロプロセッサ200によりラッチポイント300を”Lo”レベルにさせた後のイグニッシュョンスイッチ104の2回目以降の

オンでは、マイクロプロセッサ 200 の入力 A301 は "Hi" レベルになり、マイクロプロセッサ 200 が、副電源端子 102 からバッテリ 101 により給電が行われてからイグニッションスイッチ 104 の 1 回目のオンか 2 回目以降のオンかを、マイクロプロセッサ 200 への入力 A301 (初回起動信号) のレベルが異なることにより認識できるようにしたものである。1 回目のオンを示す初回起動信号は、入力 A301 が "Lo" レベルの信号となる。

#### 【0028】

またこの発明は、イグニッションスイッチ 104 がオンされてマイクロプロセッサ 200 に主電源回路 122 から給電がある状態で、バッテリ 101 から副電源回路 124 を介して給電されていない状態(副電源回路 124 にバッテリ 101 が接続されていない状態)を示す副電源給電異常信号を発生するようにし、これに従って RAM の初期化を行なったり、警告の発生を行ったりする。

10

#### 【0029】

副電源給電異常信号の発生に関し、イグニッションスイッチ 104 がオンされて主電源回路 122 が給電をしている状態で、バッテリ 101 が副電源端子 102 を介して電流制限抵抗 204a に給電している時(副電源回路 124 にバッテリ 101 が接続された状態)は、マイクロプロセッサ 200 の入力 B302 は "Lo" レベルとなり、バッテリ 101 が副電源端子 102 を介して電流制限抵抗 204a に給電していない時(副電源回路 124 にバッテリ 101 が接続されていない状態)はマイクロプロセッサ 200 の入力 B302 は "Hi" レベルとなる。副電源回路 124 を介して給電されていない状態(副電源回路 124 にバッテリ 101 が接続されていない状態)を示す副電源給電異常信号は、入力 B302 が "Hi" レベルの信号となる。

20

#### 【0030】

また初回起動信号は、バッテリ 101 が副電源端子 102 に接続されたことを前提として、その後のイグニッションスイッチ 104 の 1 回目のオンと 2 回目以降のオンで異なるレベルの信号となるが、バッテリ 101 が副電源端子 102 に接続されていない状態では判定回路 202 のトランジスタ 202c はオフとなり、マイクロプロセッサ 200 の入力 A301 は "Hi" レベルとなり、2 回目以降のオンと判定してしまう。そこで上述の副電源給電異常信号により、バッテリ 101 が副電源端子 102 に接続されていないことがマイクロプロセッサ 200 の入力 B302 の状態により判定できるようにしたため、副電源給電異常と判定した場合は初回起動信号による判定は無効にして RAM の初期化を行なうようにマイクロプロセッサ 200 が判断するようにする。

30

#### 【0031】

また副電源給電異常警告は、マイクロプロセッサ 200 の警告信号出力 306 と電流制限抵抗 127a とトランジスタ 127b により行われ、マイクロプロセッサ 200 が副電源給電異常を判定したとき、電子制御装置 100 の外部に設置された警告装置 127 に信号を送り、ユーザに警告を促したり、また、マイクロプロセッサ 200 の端子 324 に接続された書き換え可能な ROM(又は不揮発性 RAM であってもよい) 126 に記憶して、通信 I/F 128a を介して外部のサービス用テスト 128 に副電源給電異常であることが判るコードを転送する。ROM(又は不揮発性 RAM) 126 は副電源端子 102 に給電されていない状態でもデータを記憶可能なメモリである。

40

#### 【0032】

なお、初回起動信号発生手段がラッチ回路 201 と判定回路 202 とラッチセット回路 203 とマイクロプロセッサ 200 (CPU 200c) で構成され、副電源給電異常信号発生手段がバッテリ配線断線検出回路 204 とマイクロプロセッサ 200 (CPU 200c) とで構成され、揮発性メモリ初期化手段および第 2 の揮発性メモリ初期化手段がマイクロプロセッサ 200 (CPU 200c) で構成され、副電源給電異常警告手段がマイクロプロセッサ 200 (CPU 200c) と電流制限抵抗 127a とトランジスタ 127b と警告装置 127 で構成され、副電源給電異常記憶手段がマイクロプロセッサ 200 (CPU 200c) と ROM(又は不揮発性 RAM) 126 で構成される。

50

## 【0033】

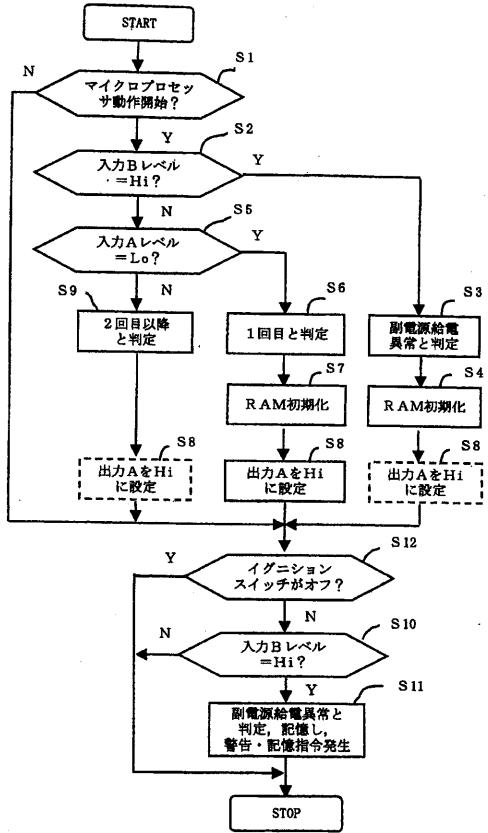

図3はこの発明における電子制御装置のマイクロプロセッサの処理を示すフローチャートであり、イグニッションスイッチ104がオフからオンになってマイクロプロセッサ200にバッテリ101から主電源回路122を介して給電があり、マイクロプロセッサ200が動作を開始した以降に実行される処理である。

## 【0034】

ステップS1においてマイクロプロセッサ200の動作開始又は継続動作が判定され、ステップS2でマイクロプロセッサ200の入力B302のレベルが”Hi”レベルと判定された場合には、ステップS3でバッテリ101から副電源端子102に給電されておらず副電源給電異常と判定して、ステップS4でRAM200bの初期化の処理を行う。尚、ステップS4の処理後にも、後述のステップS8の出力A303のレベルを”Hi”レベルにする処理を実施してもよい。10

## 【0035】

ステップS2において、マイクロプロセッサ200の入力B302のレベルが”Lo”レベルと判定された場合には、バッテリ101から副電源端子102に給電されていると判定して、ステップS5に進み、ステップS5でマイクロプロセッサ200の入力A301の状態を確認する処理を行い、マイクロプロセッサ200の入力A301のレベルが”Lo”レベルの場合には、ステップS6でイグニッションスイッチ104の1回目のオンかつバッテリ101から副電源端子102に給電されていると判定し、マイクロプロセッサ200はステップS7のRAM200bの初期化の処理を行なってからステップS8に進み、出力A303のレベルを”Hi”レベルにする。また、ステップS5でマイクロプロセッサ200の入力A301のレベルが”Hi”レベルの場合には、ステップS9でイグニッションスイッチ104の2回目以降のオンかつバッテリ101から副電源端子102に給電されていると判定する。尚、ステップS9の処理後に、ステップS8の出力A303のレベルを”Hi”にする処理を実施してもよい。20

## 【0036】

そしてその後、マイクロプロセッサ200に主電源回路122から給電がある通常の制御時において、ステップS12でイグニッションスイッチ104のオン／オフ状態を判定して、オフであれば処理を終了する。ステップS10でマイクロプロセッサ200の入力B302のレベルが”Hi”レベルと判定され、バッテリ101から副電源端子102に給電されていないと判定された場合には、RAMの初期化は行わずに、ステップS11で副電源給電異常と判定して、警告や異常の記憶を行い、その後に例えば処理を終了する。動作終了後は、マイクロプロセッサは他の制御プログラムを実行し、所定時間後には再度ステップS1～S11を実行する。30

## 【0037】

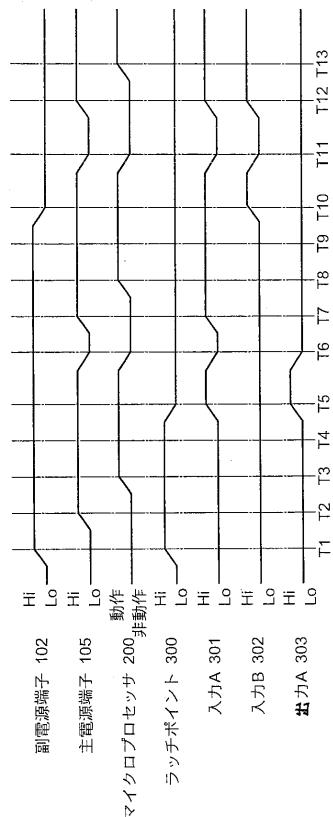

図4にはバッテリからの給電開始時からの電子制御装置の動作タイミングチャート、図5にはT4～T5、T8～T9、およびT10、T13時点でのそれぞれの各信号とマイクロプロセッサの動作の関係図を示す。図4において、給電前、副電源端子102および主電源端子105は”Lo”レベル(無給電状態)にあり、マイクロプロセッサ200は非動作状態、ラッチポイント300、マイクロプロセッサ200の入力A301、入力B302、出力A303はそれぞれ”Lo”レベルにある。時点T1は、バッテリ101の接続による副電源端子102への給電(電圧供給)が開始された状態を示す。これにより副電源端子102は”Hi”レベル(給電状態)になり、これに接続されたラッチポイント300も”Hi”レベルになる。40

## 【0038】

時点T2は、イグニッションスイッチ104がオンされることにより、トランジスタ109がオン状態になり電源リレー103の開閉素子103bが閉じ、主電源端子105への給電が開始された状態を示す。これにより主電源端子105は”Hi”レベル(給電状態)になる。時点T3は、主電源回路122を介してマイクロプロセッサ200に給電が行われ、マイクロプロセッサ200が動作を開始した状態を示す。時点T4は、マイクロ50

プロセッサ200の入力A301、入力B302が共に”Lo”レベルであることから、マイクロプロセッサ200が副電源端子102への給電開始後のイグニッシュョンスイッチ104の1回目のオンと判定した状態を示す。副電源端子102からの”Hi”レベル信号によりトランジスタ202c、204cが共にオン状態になるため入力A301、入力B302は共に”Lo”レベルのままとなる。

#### 【0039】

時点T5は、マイクロプロセッサ200のRAM200bを初期化し、マイクロプロセッサ200の出力A303が”Hi”レベルに設定され、ラッチポイント300を”Lo”レベルにすることにより、マイクロプロセッサ200の入力A301が”Hi”レベルにされる状態を示す。ここでは、マイクロプロセッサ200は図3のフローチャートのステップS2、S5～S8に従い、入力B302、入力A301が共に”Lo”レベルなので、RAM200bの初期化、出力A303の”Hi”レベルへの設定を行う。これによりトランジスタ203c、203a、201d、201bがオン状態になり、ラッチポイント300が”Lo”レベルにされる。そしてラッチポイント300が”Lo”レベルにされたことによりトランジスタ202cはオフ状態になり入力A301が”Hi”レベルにされる。なおトランジスタ201b、201dによりラッチポイント300の”Lo”レベルは副電源端子102への給電がなくなるまで保持される。

#### 【0040】

時点T6は、イグニッシュョンスイッチ104がオフされたことにより開閉素子103bが開放され主電源端子105への給電が停止された状態を示す。ここでは、イグニッシュョンスイッチ104がオフされたことにより、このことを示すイグニッシュョンスイッチ信号がデジタル入力I/F(インターフェイス)115を介してマイクロプロセッサ200の端子313に入力され、マイクロプロセッサ200がイグニッシュョンスイッチ104がオフになったことを認識するとCPU200cは動作停止処理を行い、動作停止処理終了時にWD信号が停止されてWDT回路107の出力が”Lo”レベルになるとトランジスタ109がオフ状態になり電磁コイル103aの電流が停止され、開閉素子103bは開放されて主電源端子105を介しての給電は停止される。これにより主電源端子105は”Lo”レベル(無給電状態)、マイクロプロセッサ200は非動作状態、主電源端子105に接続された入力A301は”Lo”レベルとなり、出力A303も”Lo”レベルに戻される(図3のステップS12参照)。

#### 【0041】

時点T7は、イグニッシュョンスイッチ104が再度オンにされ開閉素子103bが閉じて主電源端子105への給電が開始された状態を示す。これにより主電源端子105は”Hi”レベル(給電状態)になり、ラッチポイント300が”Lo”レベルなのでトランジスタ202cはオフ状態にあるため、主電源回路122を介して主電源端子105に接続された入力A301は”Hi”レベルにされる。時点T8は、主電源回路122を介してマイクロプロセッサ200が給電されているため、マイクロプロセッサ200が動作を開始した状態を示す。時点T9は、マイクロプロセッサ200の入力A301が”Hi”レベル、入力B302が”Lo”レベルにあることから、マイクロプロセッサ200が副電源端子102への給電開始後のイグニッシュョンスイッチ104の2回目以降のオンと判定した状態を示す。マイクロプロセッサ200は図3のフローチャートのステップS2、S5、S9に従い、入力A301が”Hi”レベル、入力B302が”Lo”レベルなのでRAM200bの初期化等は行わない。

#### 【0042】

時点T10は、通常の制御中にバッテリ配線の断線等の理由により副電源端子102への給電が停止してしまった状態を示す。これにより、副電源端子102は”Lo”レベル(無給電状態)になりトランジスタ204cがオフ状態になったことにより、入力A301、入力B302が共に”Hi”レベルになり、マイクロプロセッサ200は副電源給電異常と判定する。但しこの時は、RAM初期化判定の後なのでRAMの初期化は行わずに、上述の電子制御装置100の外部に設置された警告装置127に警告信号出力306を送

10

20

30

40

50

り、ユーザに警告を促したり、また、マイクロプロセッサ200の端子324に接続された書き換え可能なROM(又は不揮発性RAM)126に副電源給電異常のデータを記憶して、例えば通信I/F128aを介して外部のサービス用テスタ128に副電源給電異常であることが判るコードを転送する(図3のステップS10～S11参照)。そして時点T11は、イグニッションスイッチ104がオフされ開閉素子103bが開放され主電源端子105への給電が停止した状態を示す。これにより副電源端子102及び主電源端子105が共に”Lo”レベル(無給電状態)になり、マイクロプロセッサ200は非動作状態となり、入力A301、入力B302及び出力A303が全て”Lo”レベルとなる。

#### 【0043】

時点T12は、イグニッションスイッチ104が再びオンされて開閉素子103bが閉じて主電源端子105への給電が開始される状態を示す。副電源端子102への給電がなくトランジスタ202c、204cが共にオフ状態なので入力A301及び入力B302は共に”Hi”レベルとなる。そして時点T13は、イグニッションスイッチ104がオンされてマイクロプロセッサ200が動作開始したマイクロプロセッサ200のRAM初期化判定時なので、マイクロプロセッサ200が判定を行い、入力A301及び入力B302が共に”Hi”レベルであるので、副電源給電異常と判定しさらにRAMを初期化する状態を示す(図3のステップS3～S4参照)。

#### 【0044】

なお図3のステップS3においてRAMの初期化と同時に、図3のステップS11と同様に、上述の副電源給電異常にに関する警告信号出力306を送り、ユーザに警告を促したり、また、ROM(又は不揮発性RAM)126に副電源給電異常のデータを記憶して、外部のサービス用テスタ128に副電源給電異常であることが判るコードを転送するようにしてもよい。また、副電源給電異常と判定し、RAMの初期化を行ったことを、警告信号出力306として送り、ユーザに警告を促したり、また、ROM(又は不揮発性RAM)126に副電源給電異常のデータとして記憶して、外部のサービス用テスタ128に副電源給電異常であることが判るコードを転送するようにしてもよい。

#### 【0045】

このように構成することにより、バッテリ101を接続した後のイグニッションスイッチ104が1回目のオンと2回目以降のオンを速やかに判定して、必要な時にRAMを初期化することができる。また、主電源端子105への給電がある時に、副電源端子102に給電されているか否かを確実に検出することができる。さらに、イグニッションスイッチ104をオンした後に副電源端子102に給電されていないときは、イグニッションスイッチ104が1回目のオンであるか否かの判定を無効にしてRAMの初期化を行うことで、不定値となったRAMの制御データを使用せずに内燃機関を制御できる。

#### 【0046】

また、副電源端子102に給電されていないことを検知した場合に、副電源端子102に給電されていないことによる不確定な誤差補正データや故障データを記憶しているRAMがイグニッションスイッチ104をオンする度に初期化されることを異常としてユーザに警告することができる。

#### 【0047】

また、副電源端子102に給電されていないことを検知した場合に、副電源端子102に給電されていないことを、給電されていない状態でもデータを記憶するROMや不揮発性RAMに記憶させることにより、サービス用テスタなどを介して外部に副電源給電異常を知らせることができる。

#### 【図面の簡単な説明】

#### 【0048】

【図1】この発明による電子制御装置を設けた内燃機関の制御系の概略構成図である。

【図2】図1の電子制御装置の構成の一例を示す図である。

【図3】この発明による電子制御装置のマイクロプロセッサの処理を示すフローチャートである。

10

20

30

40

50

【図4】この発明におけるバッテリからの給電開始時からの電子制御装置の動作タイミングチャートである。

【図5】図4の所定の時点でのそれぞれの各信号とマイクロプロセッサの動作の関係を示す図である。

【符号の説明】

【0049】

1 内燃機関、100 電子制御装置、101 バッテリ、102 副電源端子、103 電源リレー、103a 電磁コイル、103b 開閉素子、104 イグニッションスイッチ、105 主電源端子、106, 108, 123, 125 ダイオード、107 ウォッヂドッグタイム回路、109, 120b, 121b, 127b, 201b, 201d, 202c, 203a, 203c, 204c トランジスタ、110, 111, 120a, 127a, 201a, 201c, 202a, 203b, 203d, 204a 電流制限抵抗、112 圧力センサ、113 スロットル開度センサ、114 内燃機関回転角検出センサ、115, 118 デジタル入力I/F、116, 117 アナログ入力I/F、120 燃料噴射用インジェクタ、121 点火装置、122 主電源回路、124 副電源回路、126 書換え可能なROM、127 警告装置、128 サービス用テスト、128a 通信インターフェイス、130 エーカーリーナ、131 吸気管、132 スロットル、200 ROM、200b RAM、200c CPU、201 ラッチ回路、202 判定回路、202b 電圧分圧抵抗、202d, 204b 電位固定抵抗、203 ラッチセット回路、204 バッテリ配線断線検出回路、300 ラッチポイント、301 入力A、302 入力B、303 出力A、304 インジェクション信号出力、305 点火信号出力、306 警告信号出力、311 RAM保持電源端子、312~324, 401~409 端子。

【図1】

1:内燃機関

100:電子制御装置

101:バッテリ

102:副電源端子

103:電源リレー

104:イグニッションスイッチ

112:圧力センサ

113:スロットル開度センサ

114:内燃機関回転角検出センサ

120:燃料噴射用インジェクタ

121:点火装置

127:警告装置

128:サービス用テスト

130:エーカーリーナ

131:吸気管

132:スロットル

【図2】

【図3】

【図4】

【図5】

|                            | T4-T5                                                      | T8-T9      | T10-T13    |

|----------------------------|------------------------------------------------------------|------------|------------|

| パッテリから主電源端子の供給状態           | Hi                                                         | Hi         | Lo         |

| マイクロプロセッサの入力A 301          | Hi                                                         | Hi         | Hi         |

| マイクロプロセッサの入力B 302          | Lo                                                         | Hi         | Hi         |

| マイクロプロセッサ 200の判定           | Hi                                                         | Hi         | Hi         |

| 上記判定後のマイクロプロセッサの出力A 303の処理 | Lo→Hi                                                      | —          | —          |

| マイクロプロセッサ 200のRAMの初期化      | 実行                                                         | —          | —          |

|                            | パッテリ101の接続からバッテリ101の接続から<br>マイクロニッショングループ104が<br>2回目のオンと判定 | 副電源給電異常と判定 | 副電源給電異常と判定 |

---

フロントページの続き

(72)発明者 山口 真吾

東京都千代田区丸の内二丁目 7番3号 三菱電機株式会社内

(72)発明者 神崎 将造

東京都千代田区九段北一丁目 13番5号 三菱電機エンジニアリング株式会社内

審査官 畑津 圭介

(56)参考文献 特開2002-195094(JP,A)

(58)調査した分野(Int.Cl., DB名)

F 02 D 45 / 00