**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>6</sup>

G11C 11/40

(45) 공고일자 1996년02월05일

(11) 공고번호 96-001784

---

|           |               |           |               |

|-----------|---------------|-----------|---------------|

| (21) 출원번호 | 특1992-0001096 | (65) 공개번호 | 특1992-0015375 |

| (22) 출원일자 | 1992년01월25일   | (43) 공개일자 | 1992년08월26일   |

---

|            |                                                   |

|------------|---------------------------------------------------|

| (30) 우선권주장 | 91-25506 1991년01월25일 일본(JP)                       |

| (71) 출원인   | 닛본덴기 가부시끼가이샤 세끼모또 타다히로<br>일본국 도쿄도 미나도꾸 시바 5쪽에 7-1 |

|          |                                                                                   |

|----------|-----------------------------------------------------------------------------------|

| (72) 발명자 | 후꾸다 다케시<br>일본국 가나가와쿄 가와사끼시 나카하라구 고스기마찌 1쪽에 403-53<br>분덴기 아이씨 마이크로컴퓨터 시스템 가부시끼가이샤내 |

| (74) 대리인 | 이상희, 구영창, 주성민                                                                     |

**심사관 : 이해평 (책자공보 제4321호)**

---

**(54) 반도체 기억 장치**

---

**요약**

내용 없음.

**대표도**

**도1**

**영세서**

[발명의 명칭]

반도체 기억 장치

[도면의 간단한 설명]

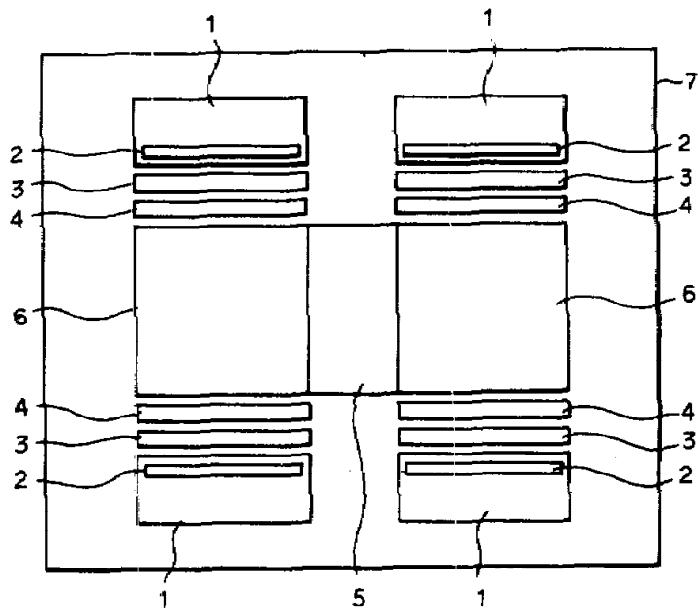

제1도는 본 발명의 제1실시예의 반도체 기억 장치 전체를 개략적으로 도시한 평면도.

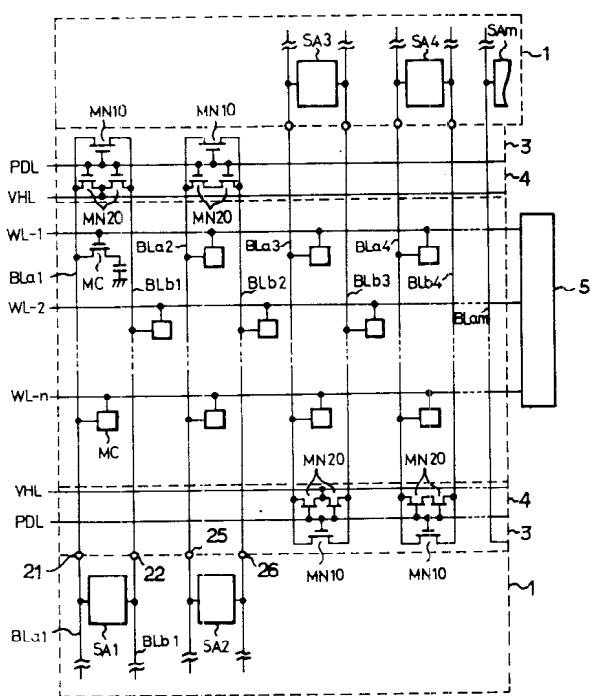

제2도는 제1도에 도시한 반도체 기억 장치의 구체적 회로 구성을 도시한 회로도.

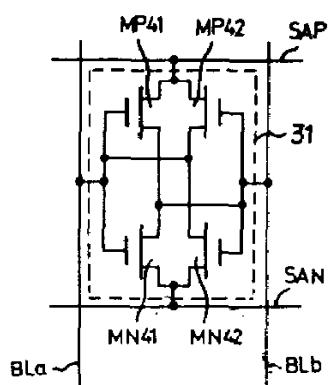

제3도는 감지 증폭기의 회로 구성을 도시한 회로도.

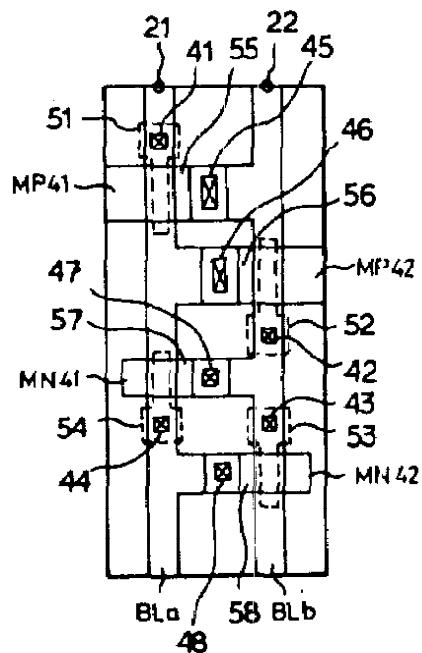

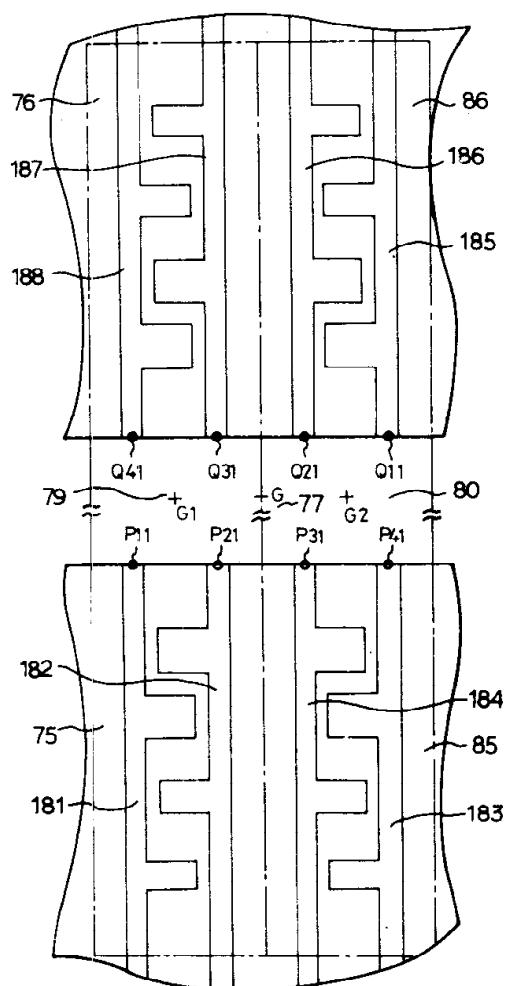

제4도는 제3도에 도시한 감지 증폭기의 일부의 배치 패턴을 개략적으로 도시한 평면도.

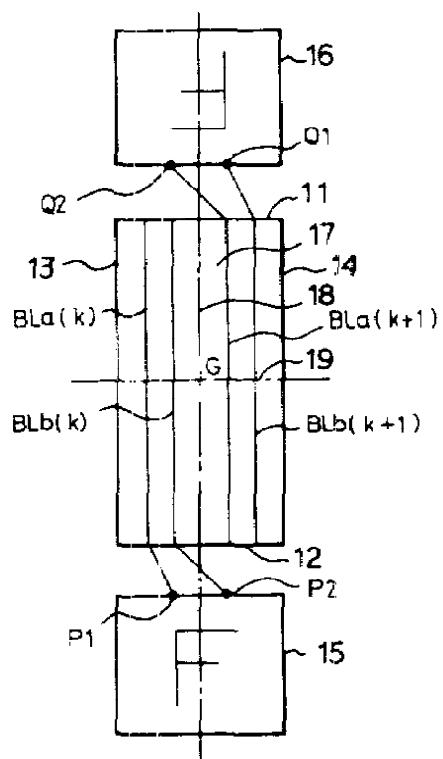

제5도는 제1도에 도시한 반도체 기억 장치의 주변 회로, 메모리 셀 형성 영역 및 비트선 쌍의 침상 배치를 도시한 평면도.

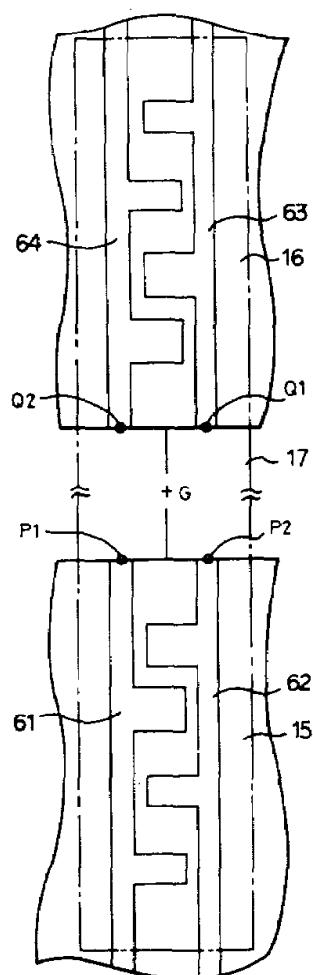

제6도는 제3도에 도시한 반도체 기억 장치의 주변 회로 중 일부의 배치 패턴을 도시한 평면도.

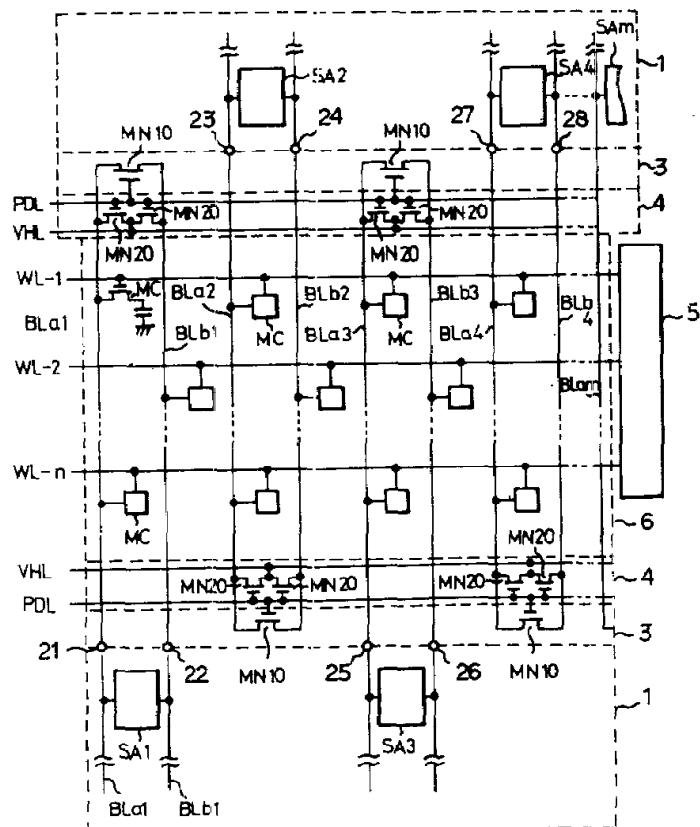

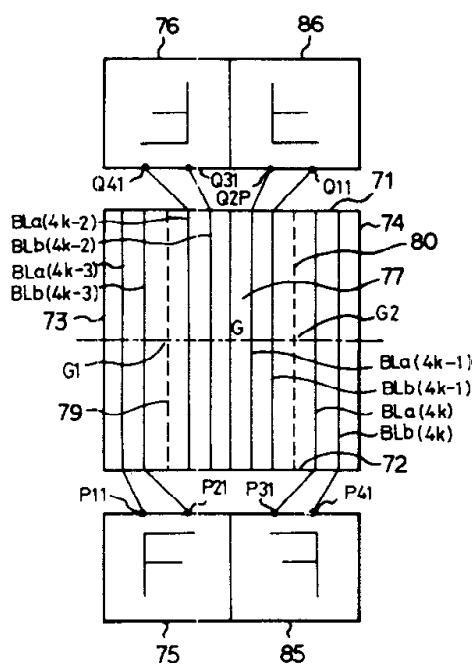

제7도는 본 발명의 제2실시예의 반도체 기억 장치의 주변 회로, 메모리 형성 영역 및 비트선의 침상 배치를 도시하는 평면도.

제8도는 제7도에 도시한 반도체 기억 장치의 주변 회로의 일부 배치 패턴을 도시한 평면도.

제9도는 본 발명의 제2실시예의 반도체 기억 장치의 구체적 회로 구성을 도시한 회로도.

\* 도면의 주요부분에 대한 부호의 설명

1 : 주변 회로부

2, 31, SA, SA1, SA2, SA3, SA4, SA<sub>m</sub> : 감지 증폭기

3 : 비트선 평형화 회로 4 : 비트선 전위공급 회로

5 : 행 디코더 6 : 메모리 셀 형성부

7 : 반도체 칩 11, 12, 13, 14, 71, 72, 73, 74 : 단변

15, 16, 75, 76, 85, 86 : 주변 회로 17, 77, 79, 80 : 메모리 셀 형성 영역

18, 19 : 중심선

21, 22, 23, 24, 25, 26, 27, 28, P1, P2, P11, P21, P31, P41, Q1, Q2, Q11, Q21, Q31, Q41 : 비트

## 선 쌍 접속점

BLa1/BLb1, BLa2/BLb2, BLa3/BLb3, BLa4/BLb4, BLa/BLb, BLam/BLbm, BLa(k)/BLb(k),

BLa(k+1)/BLb(k+1), BLa(4K-3)/BLb(4k-3), BLa(4k-2)/BLb(4k-2), BLa(4k-1)/BLb(4k-1),

BLa(4K)/BLb(4K) : 비트선 쌍

61, 62, 63, 64, 181, 182, 183, 184, 185, 186, 187, 188 : 금속 배선 패턴

WL-1, WL-2, WL-n : 워드선 PDL, SAN, SAP : 신호선

VHL : 전원선

MN10, MN20, MN41, MN42, MP41, MP42 : 트랜지스터

MC : 메모리 셀 41, 42, 43, 44, 45, 46, 47, 48 : 접촉 훌

51, 52, 53, 54 : 게이트 전극 G, G1, G2 : 중심선의 교점

## [발명의 상세한 설명]

본 발명은 반도체 장치에 관한 것으로, 특히 DRAM(Dynamic Random Access Memory)의 주변 회로 배치에 관한 것이다.

일반적으로, DRAM 등의 반도체 기억 장치는 메모리 셀을 배열하여 형성한 메모리 셀 어레이 형성부와 그것에 인접하는 감지 증폭기, 열 디코더, 행 디코더 등의 주변 회로로 구성되어 있다. 이들 주변 회로는, 메모리 셀 어레이 1 : 1 대응하여 배치되어 서로 상보적 관계에서 전압이 각각 인가되는 복수의 비트선 쌍의 각각에 대해 하나씩 설치된 감지 증폭기 등의 특정 주변 회로는 상기 비트선 쌍마다 설치할 필요가 있다. 따라서, 이들 특정 주변 회로는 상기 메모리 셀 어레이 형성부의 1변을 따라 배치된다.

근래, 반도체 가공 기술의 미세화가 진행되어, 상기 메모리 셀 1비트당 칩상의 면적은 축소되고 있어서 비트성 쌍의 간격(반복 피치폭)도 축소되고 있다.

한편, 화상 메모리로 대표되는 시스템 고유 기능에 적용한 이른바 전용 반도체 메모리가 널리 시판 사용되고 있다. 전용 반도체 메모리에서는 직렬 데이터 전송, 플래쉬 클리어(flash clear) 등의 시스템 기능을 실현하는 회로를 상기 비트선 쌍마다 주변 회로로서 설치한다.

상기 전용 반도체 메모리에 이용되는 주변 회로에는 상기 감지 증폭기외에 라인 버퍼 회로, 직렬 스위치 회로 등이 부가되어 메모리 칩 전체로서 구성이 복잡해져 대규모로 된다.

즉, 이들 주변 회로를 상기 메모리 셀 어레이 형성부의 1변을 따라 상기 비트선 쌍의 반복 피치폭으로 배치하기가 곤란하다. 가령, 상기 반복 피치 폭을 고려하지 않고 상기 주변 회로를 배치하면, 주변 회로의 구성 소자인 트랜지스터의 특성 밸런스가 맞지 않을 뿐만 아니라 상기 비트선 쌍이 길어져서 비트선 쌍의 저항 및 용량이 증대한다.

그 결과, 신호 판독 또는 기입시에 비트선 쌍의 전압 변화에 지연을 일으키기 때문에, 반도체 기억 장치의 판독·기입 속도를 현저히 저하시킬 뿐만 아니라, 오동작을 일으킨다.

따라서, 본 발명의 목적은 주변 회로의 구성 소자인 트랜지스터 및 비트선 쌍의 특성 밸런스를 확보함과 동시에 비트선 쌍 길이의 균형을 맞추고, 따라서 기입·판독 속도의 저하나 오동작의 발생을 방지한 반도체 기억 장치를 제공하는 것이다.

본 발명의 반도체 장치는 반도체 기판의 표면에, 제1방향으로 뻗는 제1 및 제2단변(端邊)과 상기 제1방향과 직각 방향인 제2방향으로 뻗는 제3 및 제4단변에 의해 각각 둘러싸인 복수의 4각 평면 형상의 메모리 셀 형성 영역과, 상기 복수의 메모리 셀 형성 영역에 상기 제1방향으로 배열된 메모리 셀 형성부와, 상기 각 메모리 셀 형성 영역의 각각에 배열 형성된 복수의 메모리 셀과, 상기 메모리 셀 형성 영역내에서 각각 해당하는 상기 복수의 메모리 셀을 접속시켜 동 영역내를 각각 상기 제2방향으로 뻗어 형성된 제1 및 제2비트선 쌍과, 상기 제1단변을 따라 제1단변에 대향해서 상기 메모리 셀 형성 영역의 외측에 형성되어 제1 및 제2접속점을 갖는 제1주변 회로와, 상기 제2단변을 따라 상기 제2단변에 대향하여 상기 메모리 셀 형성 영역의 외측에 형성되고 제1 및 제2접속점을 갖는 제2주변 회로를 구비하며, 상기 제1주변 회로와 상기 제2주변 회로는 상기 제1단변의 중점과 상기 제2단변의 중점을 연결하는 제1중심선과 상기 제3단변의 중점과 상기 제4단변의 중점을 연결하는 제2중심선과의 교점에 관해 점대칭으로 배치 형성되고, 상기 제1주변 회로의 상기 제1 및 제2접속점에 상기 제1 비트선 쌍이 접속되며, 상기 제2주변 회로의 상기 제1 및 제2접속점에 상기 제2비트선 쌍이 접속되는 것을 특징으로 한다.

또 상기 제1 및 제2주변 회로중 서로 인접하는 복수개를 선대칭으로 배치할 수도 있다.

제1도를 참조하면, 본 발명의 제1실시예의 반도체 기억 장치를 구성하는 반도체 칩(7)은 메모리 셀이 어레이 형상으로 배치된 메모리 셀 형성부(6)과, 워드선을 입력 어드레스에 따라 선택하는 행 디코더(5)와, 비트선 쌍을 동일 전위로 균형을 이루게 하는 비트선 평형화 회로(3)과, 비트선 전위 공급 회로(4)와, 감지 증폭기(2)를 갖는 주변 회로부(1) 등을 포함한다(이 반도체 기억 장치는 주변 회로부로서 다른 회로도 구비하고 있으나, 설명의 편의상 그 밖의 회로는 생략한다).

감지 증폭기(2)를 포함하는 주변 회로부(1)은 메모리 셀 형성부(6)를 구성하는 비트선 쌍에 각각 접속되기 때문에 메모리 셀 형성부(6)의 근방에 배치된다. 구체적으로는, 주변 회로부(1)은 메모리 셀 형성부(6)의 서로 평행한 2변을 각각 따라서 메모리 셀 형성부(6)에서 보아 외측에 배치된다.

다음에 제2도를 병행하여 참조하면, 본 실시예에서의 메모리 셀 형성부(6)은 각각이 하나의 N 채널 트랜지스터와 하나의 용량 소자로 이루어지고 어레이 형상으로 배치된 복수의 메모리 셀(MC)로 구성

된다[소위 1트랜지스터 1캐패시터형 셀(MC)를 어레이 형상으로 배치하여 형성되어 있다].

메모리 셀(MC)의 각각에는 1개의 워드선(예를 들면 WL1-1, WL2-2, ..., WL-n)과 2개를 1쌍으로 하는 비트선 쌍[예를 들면 BLa1/BLb1, BLa2/BLb2, ..., BLam/BLbm]이 각각 접속되어 있다.

상기 비트선 쌍의 각각은 주변 회로부(1)과 접속점(21) 내지 접속점(28)에서 접속된다. 주변 회로부(1)에 포함되는 감지 증폭기[SA(예를 들면 SA1, SA2, ...)]는 트랜지스터 특성, 부유 용량 등의 점에서 좌우 균형을 이룬 플립 플롭형 회로로 구성된다. 제3도를 참조하면, P 채널 트랜지스터(MP41)과 N 채널 트랜지스터(MN41)로 제1인버터 회로를 구성하며, P 채널 트랜지스터(MP42)와 N 채널 트랜지스터(MN42)로 제2인버터 회로를 구성하고, 이들 제1 및 제2인버터 회로의 출력을 제2 및 제1인버터 회로의 입력으로 각각 귀환시켜 플립플롭을 구성한다. 제1 및 제2인버터 회로의 각각의 입력에 비트선 쌍(BLa, BLb)를 접속하여 감지 증폭기(31)를 구성한다.

감지 증폭기(31)의 반도체 칩상의 배치를 도시한 제4도를 참조하면, 트랜지스터(MP41)에서 폴리실리콘막으로 형성된 게이트 전극(51)은 접촉 훌(41)을 통해 금속 배선, 즉 비트선(BLa)에 접속되고, 소스·드레인 경로는 접촉 훌(45)를 통해 비트선(BLb)과 신호선(SAP)에 접속된다. 트랜지스터(MP42)는 상기 트랜지스터(MP41)과 균형을 맞추어 배치되고, 폴리실리콘 막의 게이트 전극(52)는 접촉 훌(42)를 통해 비트선(BLb)에 접속되며, 소스·드레인 경로는 접촉 훌(46)을 통해 비트선(BLa)과 신호선(SAP)에 접속된다. 또 트랜지스터(MN41)에 있어서, 폴리실리콘 막의 게이트 전극(54)는 접촉 훌(44)를 통해 상기 비트선(BLa)에 접속되고, 소스·드레인 경로는 접촉 훌(47)을 통해 비트선(BLb)과 신호선(SAN)에 접속된다. 트랜지스터(MN42)도 상기 트랜지스터(MN41)과 균형을 맞추어 배치되고, 폴리실리콘 막으로 형성된 전극(53)은 접촉 훌(43)을 통해 비트선(BLb)에 접속되며, 소스·드레인 경로는 접촉 훌(48)을 통해 상기 비트선(BLa)과 신호선(SAN)에 접속된다.

감지 증폭기(31)은 반도체 칩상에 비트선 쌍(BLa 및 BLb)에 대해 균형을 맞춘 배치로 형성된다.

감지 증폭기(31)은 활성화 신호(도시하지 않음)에 의해 신호선(SAP 및 SAN)에 적정한 전위를 공급하여 동작된다.

다음에 제5도를 참조하면, 도면에 도시한 본 발명의 제1실시예의 반도체 기억 장치에 있어서는, 제2도에서 k번째의 비트선 쌍[BLa(k)/BLb(k)]과 그것에 인접하는 (k+1)번째의 비트선 쌍[BLa(k+1)/BLb(k+1)]을 포함하는 메모리 셀 형성 영역(17)에 대응하는 주변 회로(15 및 16)이 메모리 셀 형성 영역(7)의 단변(12 및 11)을 따라 메모리 셀 형성 영역(17)에서 보아 외측에 형성된다. 또 상기 주변 회로(15 및 16)은 단변(11 및 12)의 종점과 단변(13 및 14)의 종점을 연결하는 중심선(18 및 19)의 교점(G)에 관해 점대칭으로 배치 형성된다. 비트선 쌍[BLa(k)/BLb(k)]는 주변 회로(15)의 상기 메모리 셀 형성 영역(17)에 대향하는 1변상의 접속점(P1 및 P2)를 통해 주변 회로(15)와 접속된다. 마찬가지로, 비트선 쌍[BLa(k+1)/BLb(k+1)]은 주변 회로(16)의 상기 메모리 셀 영역(17)에 대향하는 1변상의 접속점(Q1 및 Q2)를 통해 주변 회로(16)와 접속되어 있다. 주변 회로(15)의 배치 방향을 F로 나타내면 주변 회로(16)의 배치 방향은 역 F자로 나타난다(제5도 참조).

제5도의 주변 회로(15 및 16)이 제3도의 감지 증폭기(31)를 포함하는 경우인 제4도에 대응하는 배지 패턴의 일부 평면도를 도시한 제6도를 참조하면, 이 도면에서 제5도와 동일 구성 부분에는 동일 참조 번호 및 부호를 부가한다. 주변 회로(15)에 포함되는 감지 증폭기의 금속 배선 패턴(61 및 62)은 접속점(P1 및 P2)에 접속되고, 주변 회로(16)에 포함되는 감지 증폭기의 금속 배선 패턴(63 및 61)은 접속점(Q1 및 Q2)에 접속되며, 금속 배선 패턴(61 및 63) 및 금속 배선 패턴(62 및 64)은 각각 교점(G)에 관해 점대칭으로 배치되어 있다. 다음에 다시 제2도를 참조하면, 반도체 기억 장치의 독출 동작시에는 프리차지 신호(도시하지 않음)가 신호선(PDL)을 하이 레벨에서 로우 레벨로 동작시키고 트랜지스터(MN10 및 MN20)를 각각 오프한다. 그후, 행 디코더(5)에 의해 선택된 하나의 워드선(WL-i)가 활성화한다. 그 워드선(WL-i)에 접속되어 있는 복수의 메모리 셀(MC)의 기억 내용이 각각의 비트선 쌍에 공급된다. 비트선 쌍을 구성하는 비트선[BLa(k)와 BLb(k)]중 어느 한쪽이 메모리 셀(MC)의 기억 내용에 따라 전원 라인(VHL)의 전위보다도 저 전위로 되고, 다른쪽의 비트선은 상기 전원 라인(VHL)의 전위로 된다[메모리 셀(MC)에 로우 레벨이 기억되어 있는 경우], 비트선 쌍의 전위 차를 감지 증폭기(SA)에서 증폭하여, 행 디코더(도시하지 않음)에 의해 선택된 하나의 비트선 쌍을 통해 출력 회로(도시하지 않음)에 송출함으로써 하나의 기억 내용에 대한 독출 동작이 종료한다.

다음에 제7도를 참조하면, 본 발명의 제2실시예의 반도체 장치의 배치는 제2도에 있어서 (4k-3)번째, (4k-2)번째, (4k-1)번째 및 (4k)번째의 비트선 쌍[BLa(4k-3)/BLb(4k-3), BLa(4k-2)/BLb(4k-2), BLa(4k-1)/BLb(4k-1) 및 BLa(4k)/BLb(4k)]를 포함하는 메모리 셀 형성 영역(77)에 대응하는 각각의 주변 회로(75, 76, 85 및 86)이 메모리 셀 형성 영역(77)의 단변(72 및 71)을 따라 메모리 셀 형성 영역(77)에서 보아 외측에 형성된다. 그리고 상기 주변 회로(75 및 76)은 비트선 쌍의(4k-3)번째와 (4k-2)번째를 포함하는 메모리 셀 형성 영역(79)의 교점(G1)에 대해 점대칭으로 배치된다. 마찬가지로, 주변 회로(85 및 86)은 비트선 쌍의 (4k-1)번째와 (4k)번째를 포함하는 메모리 셀 형성 영역(80)의 교점(G2)에 대해 점대칭으로 배치된다. 또 이들 4개의 비트선 쌍을 포함하는 메모리 셀 형성 영역(77)의 교점(G)에 관해 상기 주변 회로(75 및 85)와 주변 회로(76 및 86)은 점대칭으로 형성 배치된다. 즉, 주변 회로(75 및 85) 및 주변 회로(76 및 86)은 교점(G)를 통해 상기 단변(74 또는 73)과 평행인 중심선에 대해 점대칭으로 형성된다.

제7도의 주변 회로(75, 76, 85 및 86)이 제3도의 감지 증폭기(31)를 포함하는 경우인 제4도에 대응하는 배지 패턴의 일부 평면도를 도시한 제8도를 참조하면, 제7도와 동일 구성 부분에는 동일 참조 번호 및 부호를 붙인다. 주변 회로(75 및 85)에 포함되는 감지 증폭기의 금속 배선 패턴(181, 182, 183 및 184)은 각각 접속점(P11, P21, P31 및 P41)에 접속되고, 주변 회로(76 및 86)에 포함되는 감지 증폭기의 금속 배선 패턴(185, 186, 187 및 188)은 각각 접속점(Q11, Q21, Q31 및 Q41)에 접속되며, 이들 금속 배선 패턴(181, 182, 183 및 184)은 금속 배선 패턴(185, 186, 187 및 188)과의 교점(G)에 대해 점대칭으로 형성 배치된다.

제2실시예의 반도체 기억 장치는 연속하는 4비트의 비트선 쌍에 접속하는 주변 회로를 2비트씩 1조

로 하여 메모리 형성부의 상하 부분에 주변 회로부를 갖는 배치로 형성할 수 있다(제9도 참조).

제2실시예의 독출 동작은 제1실시예와 동일하므로 설명을 생략한다.

이상 설명한 바와 같이, 본 발명의 반도체 기억 장치는 비트선 쌍마다 설치할 필요가 있는 특정한 주변 회로의 배치를 메모리 셀 형성 영역의 중심선으로 이루어지는 교점에 대해 점대칭으로 함으로써 감지 증폭기 등의 구성 소자의 균형을 맞출 뿐만 아니라 비트선 쌍의 균형을 확보하고, 따라서 데이터의 판독·기입 속도의 저하 및 오동작을 방지한다.

본 발명에 따른 화상 메모리 비트선 쌍의 응답 속도는 종래 기술의 경우보다 25ns 정도 빨라져서 고속 화상 메모리를 실현할 수 있다.

### (57) 청구의 범위

#### 청구항 1

제1방향으로 연장하는 제1 및 제2단변(side)과, 상기 제1방향과 직각 방향인 제2방향으로 연장하는 제3 및 제4단변에 의해 정해진 4각 평면 형상을 각각 갖고 있고 상기 제1방향으로 정렬하여 배열되는 다수의 메모리 셀 형성 영역; 상기 각각의 메모리 셀 형성 영역에 배열되어 형성된 다수의 메모리 셀; 상기 각각의 메모리 셀 형성 영역에 형성되어 상기 제2방향으로 연장하는 제1 및 제2비트선 쌍; 상기 제1방향으로 배열되고, 각각이 상기 메모리 셀 형성 영역들 중 관련된 한 메모리 셀 형성 영역의 상기 제1단변의 외측에 형성되며, 상기 제1비트선 쌍에 접속된 제1 및 제2접속점을 갖고 있는 다수의 제1주변 회로; 및 상기 제1방향으로 배열되고, 각각이 상기 메모리 셀 형성 영역들 중 관련된 한 메모리 셀 형성 영역의 상기 제2단변의 외측에 형성되며, 상기 제2비트선 쌍에 접속된 제3 및 제4접속점을 갖고 있는 다수의 제2주변 회로를 반도체 기판의 표면상에 표함하고; 상기 각각의 제1주변 회로는 상기 제1단변의 중심과 제2단변의 중심을 교차하는 라인의 좌측상에 상기 제1접속점을 갖고 상기 라인의 우측상에 상기 제2접속점을 갖도록 상기 제1단변을 따라 상기 제2비트선 쌍 쪽으로 시프트되고, 상기 라인의 좌측상에 상기 제3접속점을 갖고 상기 라인의 우측상에 상기 제4접속점을 갖도록 상기 제2단변을 따라 상기 제1비트선 쌍 쪽으로 시프트되는 것을 특징으로 하는 반도체 기억 장치.

#### 청구항 2

제1항에 있어서, 상기 각각의 제1 및 제2주변 회로는 감지 증폭기를 포함하는 것을 특징으로 하는 반도체 기억 장치.

#### 청구항 3

제1방향으로 연장하는 제1 및 제2단변과, 상기 제1방향과 직각 방향인 제2방향으로 연장하는 제3 및 제4단변에 의해 정해지는 메모리 셀 영역; 상기 메모리 셀 영역에 형성되어, 상기 제1방향으로 서로 평행하게 뻗어있는 제1 및 제2비트선을 갖고 있는 제1비트선 쌍; 상기 메모리 셀 영역에 형성되어, 상기 제1방향으로 서로 평행하게 뻗어있는 제3 및 제4비트선을 갖고 있는 제2비트선 쌍; 상기 메모리 셀 영역의 상기 제3단변에 인접하게 형성되어, 각각 상기 제1비트선 쌍의 상기 제1 및 제2비트선에 접속된 제1 및 제2단자를 갖고 있는 제1감지 증폭기; 및 상기 메모리 셀 영역의 상기 제4단변에 인접하게 형성되어, 각각 상기 제2비트선 쌍의 상기 제3 및 제4비트선에 접속된 제3 및 제4단자를 갖고 있는 제2감지 증폭기를 포함하고; 상기 제1 및 제2감지 증폭기가 상기 제1방향으로 정렬하여 배열되도록, 상기 제1감지 증폭기는 상기 제3단변을 따라 상기 제2비트선 쌍 쪽으로 시프트되고 상기 제2감지 증폭기는 상기 제4단변을 따라 상기 제1비트선 쌍 쪽으로 시프트되는 것을 특징으로 하는 반도체 기억 장치.

#### 청구항 4

제3항에 있어서, 상기 제1비트선 쌍은 상기 제3단변의 중심과 상기 제4단변의 중심을 교차하는 라인의 좌측상에 배치되고, 상기 제2비트선 쌍은 상기 라인의 우측상에 배치되며, 상기 제1감지 증폭기의 상기 제1단자 및 상기 제2감지 증폭기의 사이 제3단자는 상기 라인의 좌측상에 배치되고, 상기 제1감지 증폭기의 상기 제2단자 및 상기 제2감지 증폭기의 상기 제4단자는 상기 라인의 우측상에 배치되는 것을 특징으로 하는 반도체 기억 장치.

#### 청구항 5

제1방향으로 연장하는 제1 및 제2단변과, 상기 제1방향과 직각 방향인 제2방향으로 연장하는 제3 및 제4단변에 의해 정해지는 메모리 셀 영역; 상기 제1단변에 인접한 상기 메모리 셀 영역에 형성되어, 상기 제1방향으로 서로 평행하게 뻗어있는 제1 및 제2비트선을 갖고 있는 제1비트선 쌍; 상기 제2단변에 인접한 상기 메모리 셀 영역에 형성되어, 상기 제1방향으로 서로 평행하게 뻗어있는 제3 및 제4비트선을 갖고 있는 제2비트선 쌍; 상기 제1비트선 쌍과 상기 제2비트선 쌍 사이의 상기 메모리 셀 영역에 형성되어, 상기 제1방향으로 서로 평행하게 뻗어있는 제5 및 제6비트선을 갖고 있는 제3비트선 쌍; 상기 제2비트선 쌍과 상기 제3비트선 쌍 사이의 상기 메모리 셀 영역에 형성되어, 상기 제1방향으로 서로 평행하게 뻗어있는 제7 및 제8비트선을 갖고 있는 제4비트선 쌍; 상기 메모리 셀 영역의 상기 제3단변에 인접하게 형성되어, 각각 상기 제1비트선 쌍의 상기 제1 및 제2비트선에 접속된 제1 및 제2단자를 갖고 있는 제1감지 증폭기; 상기 메모리 셀 영역의 상기 제4단변에 인접하게 형성되어, 각각 상기 제2비트선 쌍의 상기 제3 및 제4비트선에 접속된 제3 및 제4단자를 갖고 있는 제2감지 증폭기; 상기 메모리 셀 영역의 상기 제4단변에 인접하게 형성되어, 각각 상기 제3비트선 쌍의 상기 제5 및 제6비트선에 접속된 상기 제5 및 제6단자를 갖고 있는 제3감지 증폭기; 및 상기 메모리 셀 영역의 상기 제4단변에 인접하게 형성되어, 각각 상기 제4비트선 쌍의 상기 제7 및 제8비트선에 접속된 제7 및 제8단자를 갖고 있는 제4감지 증폭기를 포함하고, 상기 제1 및 제3감지

증폭기가 상기 제1방향으로 정렬하여 배열되도록, 상기 제1감지 증폭기는 상기 제3단변을 따라 상기 제3비트선 쌍 쪽으로 시프트되고 상기 제3감지 증폭기는 상기 제4단변을 따라 상기 제1비트선 쌍 쪽으로 시프트되며; 상기 제2 및 제4감지 증폭기가 상기 제1방향으로 정렬하여 배열되도록, 상기 제2감지 증폭기는 상기 제3단변을 따라 상기 제4비트선 쌍 쪽으로 시프트되고 상기 제4감지 증폭기는 상기 제4단변을 따라 상기 제2비트선 쌍 쪽으로 시프트되는 것을 특징으로 하는 반도체 기억 장치.

#### 청구항 6

제5항에 있어서, 상기 제1감지 증폭기는 상기 제1과 제3비트선 쌍 사이에서 상기 제1방향으로 연장하는 제1라인의 좌측상에 상기 제1단자를 갖고 있고 상기 제1라인의 우측상에 상기 제2단자를 갖고 있으며, 상기 제3감지 증폭기는 상기 제1라인의 좌측상에 상기 제5단자를 갖고 있고 상기 제1라인의 우측상에 상기 제6단자를 갖고 있으며, 상기 제2감지 증폭기는 상기 제2와 제4비트선 쌍 사이에서 상기 제1방향으로 상기 제1라인에 평행하게 뻗어있는 제2라인의 좌측상에 상기 제3단자를 갖고 있고 상기 제2라인의 우측상에 상기 제4단자를 갖고 있으며, 상기 제4감지 증폭기는 상기 제2라인의 좌측상에 상기 제7단자를 갖고 있고 상기 제2라인의 우측상에 상기 제8단자를 갖고 있는 것을 특징으로 하는 반도체 기억 장치.

#### 도면

##### 도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9