등록특허 10-2329900

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2021년11월23일

(11) 등록번호 10-2329900

(24) 등록일자 2021년11월18일

- (51) 국제특허분류(Int. Cl.)

*H04L 25/03* (2006.01) *H02J 50/12* (2016.01)

*H02J 50/60* (2016.01) *H02J 50/80* (2016.01)

*H04L 25/02* (2006.01) *H04L 25/49* (2006.01)

- (52) CPC특허분류

*H04L 25/03343* (2013.01)

*H02J 50/12* (2016.02)

- (21) 출원번호 10-2016-7032564

- (22) 출원일자(국제) 2015년05월08일

심사청구일자 2020년04월21일

- (85) 번역문제출일자 2016년11월22일

- (65) 공개번호 10-2017-0016829

- (43) 공개일자 2017년02월14일

- (86) 국제출원번호 PCT/JP2015/002347

- (87) 국제공개번호 WO 2015/182047

국제공개일자 2015년12월03일

- (30) 우선권주장

JP-P-2014-112685 2014년05월30일 일본(JP)

(56) 선행기술조사문현

KR100643606 B1\*

KR1020060003371 A\*

US20140064404 A1\*

\*는 심사관에 의하여 인용된 문현

전체 청구항 수 : 총 26 항

심사관 : 황철규

(54) 발명의 명칭 송신 장치, 수신 장치, 및 통신 시스템

**(57) 요 약**

본원 발명의 송신 장치는, 데이터 신호의 천이 패턴에 의거하여, 데이터 신호에 대한 엠파시스를 실행할지의 여부를 판단하는 송신 제어 회로와, 상기 송신 제어 회로에 의해 판정된 결과에 의거하여, 상기 엠파시스를 선택적으로 실행하여, 적어도 하나의 송신 신호를 생성하는 송신 드라이버를 구비하다.

**대 표 도** - 도5

(52) CPC특허분류

*H02J 50/60* (2016.02)

*H02J 50/80* (2016.02)

*H04L 25/0272* (2013.01)

*H04L 25/028* (2013.01)

*H04L 25/03878* (2013.01)

*H04L 25/4917* (2013.01)

(72) 발명자

**스기오카 타츠야**

일본국 도쿄도 미나토쿠 코난 1-7-1 소니 주식회사

내

**하야시 히로아키**

일본국 도쿄도 미나토쿠 코난 1-7-1 소니 주식회사

내

## 명세서

### 청구범위

#### 청구항 1

송신 장치에 있어서,

데이터 신호에 의거하여 선택적으로 엠파시스를 행하는 것에 의해 3개의 송신 신호를 생성하며, 상기 데이터 신호의 천이 패턴에 의거하여, 데이터 신호에 대한 엠파시스를 실행할지의 여부를 판단하는 송신 제어 회로를 구비하고,

상기 3개의 송신 신호는 각각 높은 전압 상태, 낮은 전압 상태 및 중간 전압 상태의 사이에서 천이하고,

상기 송신 제어 회로에 의해 판정된 결과에 의거하여, 상기 엠파시스를 선택적으로 실행하여, 적어도 하나의 송신 신호를 생성하는 송신 드라이버를 구비하는 것을 특징으로 하는 송신 장치.

#### 청구항 2

제1항에 있어서,

상기 데이터 신호는, 송신 심볼의 시퀀스를 나타내고,

상기 송신 제어 회로는, 연속한 2개의 송신 심볼을 비교하고, 그 비교 결과에 의거하여 엠파시스를 실행할지의 여부를 판단하는 것을 특징으로 하는 송신 장치.

#### 청구항 3

제1항에 있어서,

상기 송신 제어 회로는, 상기 천이 패턴과, 엠파시스를 실행할지의 여부를 나타내는 플래그 사이의 관계를 나타내는 루업 테이블을 포함하며, 상기 루업 테이블에 의거하여, 엠파시스를 실행할지의 여부를 판단하는 것을 특징으로 하는 송신 장치.

#### 청구항 4

제3항에 있어서,

상기 루업 테이블은, 프로그램 가능하게 구성되어 있는 것을 특징으로 하는 송신 장치.

#### 청구항 5

제1항에 있어서,

상기 송신 드라이버는, 상기 적어도 하나의 송신 신호의 고주파 성분을 선택적으로 크게 하는 엠파시스를 선택적으로 실행하는 것을 특징으로 하는 송신 장치.

#### 청구항 6

제5항에 있어서,

상기 적어도 하나의 송신 신호는, 복수의 전압 상태 중의 제1의 전압 상태로부터 상기 복수의 전압 상태 중의 제2의 전압 상태로 천이하고,

상기 송신 제어 회로는, 대응하는 천이 중 일부의 천이에서 적어도 하나의 송신 신호에 대해 엠파시스가 실행되어야 할 것으로 판단하는 것을 특징으로 하는 송신 장치.

#### 청구항 7

제5항에 있어서,

상기 적어도 하나의 송신 신호는, 3개의 송신 신호이고,

상기 3개의 송신 신호들은, 높은 전압 상태, 낮은 전압 상태 및 중간 전압 상태로부터 다른 전압 상태로 천이하고,

상기 송신 제어 회로는, 높은 전압 상태 또는 중간 전압 상태로부터 낮은 전압 상태로 천이하는 각각의 송신 신호 모두에 대해 엠파시스가 실행되어야 할 것으로 판단하고,

상기 송신 제어 회로는, 낮은 전압 상태 또는 중간 전압 상태로부터 높은 전압 상태로 천이하는 각각의 송신 신호 모두에 대해 엠파시스가 실행되어야 할 것으로 판단하는 것을 특징으로 하는 송신 장치.

#### 청구항 8

제7항에 있어서,

상기 송신 제어 회로는, 높은 전압 상태 또는 낮은 전압 상태로 유지되는 각각의 송신 신호 모두에 대해 엠파시스가 실행되어야 할 것으로 판단하는 것을 특징으로 하는 송신 장치.

#### 청구항 9

제7항에 있어서,

상기 송신 제어 회로는, 높은 전압 상태 또는 낮은 전압 상태로부터 중간 전압 상태로 송신하는 각각의 송신 신호 모두에 대해 엠파시스가 실행되지 않아야 할 것으로 판단하고,

상기 송신 제어 회로는, 중간 전압 상태로 유지되는 각각의 송신 신호 모두에 대해 엠파시스가 실행되지 않아야 할 것으로 판단하는 것을 특징으로 하는 송신 장치.

#### 청구항 10

제5항에 있어서,

상기 적어도 하나의 송신 신호는, 제1의 송신 신호, 제2의 송신 신호 및 제3의 송신 신호이고,

제1의 송신 신호, 제2의 송신 신호 및 제3의 송신 신호 중 하나는, 높은 전압 상태, 낮은 전압 상태 및 중간 전압 상태 중의 하나로부터 다른 전압 상태로 천이하고,

상기 송신 제어 회로는, 상기 제1의 송신 신호가 상기 높은 전압 상태로부터 상기 중간 전압 상태로 변화하고, 상기 제2의 송신 신호가 상기 낮은 전압 상태로부터 상기 높은 전압 상태로 변화하고, 상기 제3의 송신 신호가 상기 중간 전압 상태로부터 상기 낮은 전압 상태로 변화하는 경우에, 상기 제2의 송신 신호 및 상기 제3의 송신 신호에 대해 엠파시스가 실행되어야 할 것으로 판단하는 것을 특징으로 하는 송신 장치.

#### 청구항 11

제5항에 있어서,

상기 적어도 하나의 송신 신호는, 제1의 송신 신호, 제2의 송신 신호 및 제3의 송신 신호이고,

제1의 송신 신호, 제2의 송신 신호 및 제3의 송신 신호 중 하나는, 높은 전압 상태, 낮은 전압 상태 및 중간 전압 상태 중의 하나로부터 다른 전압 상태로 천이하고,

상기 송신 제어 회로는, 상기 제1의 송신 신호와 상기 제2의 송신 신호 사이의 제1의 차분 신호, 상기 제2의 송신 신호와 상기 제3의 송신 신호 사이의 제2의 차분 신호, 상기 제1의 송신 신호와 상기 제3의 송신 신호 사이의 제3의 차분 신호 각각의 모든 극성이 변화하는 경우에, 엠파시스를 실행하여야 할 것으로 판단하는 것을 특징으로 하는 송신 장치.

#### 청구항 12

제1항에 있어서,

상기 송신 드라이버는, 상기 적어도 하나의 송신 신호의 저주파 성분을 선택적으로 작게 하도록 엠파시스를 선택적으로 실행하는 것을 특징으로 하는 송신 장치.

### 청구항 13

제12항에 있어서,

상기 적어도 하나의 송신 신호는, 복수의 전압 상태 중의 제1의 전압 상태로부터 상기 복수의 전압 상태 중의 제2의 전압 상태로 천이하고,

상기 송신 제어 회로는, 상기 복수의 전압 상태 중의 일부의 전압 상태로 유지되는 상기 적어도 하나의 송신 신호에 대해 엠파시스가 실행되어야 할 것으로 판단하는 것을 특징으로 하는 송신 장치.

### 청구항 14

제12항에 있어서,

상기 적어도 하나의 송신 신호는 3개의 송신 신호이고,

상기 3개의 송신 신호 중 하나는, 높은 전압 상태, 낮은 전압 상태 및 중간 전압 상태 중의 하나로부터 다른 전압 상태로 천이하고,

상기 송신 제어 회로는, 높은 전압 상태 또는 낮은 전압 상태로 유지되는 각각의 송신 신호 모두에 대해 엠파시스가 실행되어야 할 것으로 판단하는 것을 특징으로 하는 송신 장치.

### 청구항 15

제14항에 있어서,

상기 송신 제어 회로는, 중간 전압 상태로 유지되는 각각의 송신 신호 모두에 대해 엠파시스가 실행되지 않아야 할 것으로 판단하는 것을 특징으로 하는 송신 장치.

### 청구항 16

제1항에 있어서,

상기 적어도 하나의 송신 신호는, 복수의 송신 신호이고,

상기 송신 제어 회로는, 상기 복수의 송신 신호에 대해 엠파시스를 실행할지의 여부를 각각 판단하는 것을 특징으로 하는 송신 장치.

### 청구항 17

제1항에 있어서,

상기 적어도 하나의 송신 신호는 복수의 송신 신호이고,

상기 송신 제어 회로는, 상기 복수의 송신 신호에 대해 엠파시스를 실행할지의 여부를 일괄하여 판단하는 것을 특징으로 하는 송신 장치.

### 청구항 18

데이터 신호를 생성하는 CMOS 이미지 센서와,

제1항에 기재된 송신 장치를 포함하는 것을 특징으로 하는 활상 시스템.

### 청구항 19

제1항에 기재된 송신 장치로부터 적어도 하나의 송신 신호를 수신하여 제1의 출력 신호를 출력하는 제1의 수신 회로와,

상기 적어도 하나의 송신 신호에 대한 이퀄라이즈를 실행하는 이퀄라이저와,

적어도 하나의 이퀄라이즈된 송신 신호를 상기 이퀄라이저로부터 수신하며 제2의 출력 신호를 수신하는 제2의 수신 회로와,

상기 적어도 하나의 송신 신호의 천이 패턴에 의거하여, 상기 제1의 출력 신호 및 상기 제2의 출력 신호를 선택

하는 선택 제어 회로를 구비한 것을 특징으로 하는 수신 장치.

### 청구항 20

제19항에 있어서,

상기 선택 제어 회로는, 상기 적어도 하나의 송신 신호에서의 전압 상태의 시퀀스를 판단하고, 상기 전압 상태의 시퀀스의 시간적으로 이웃하는 2개의 전압 상태를 비교하고, 그 비교 결과에 의거하여, 상기 제1의 출력 신호 및 상기 제2의 출력 신호를 선택하는 것을 특징으로 하는 수신 장치.

### 청구항 21

제19항에 있어서,

상기 선택 제어 회로는, 상기 천이 패턴과 엠파시스를 실행할지의 여부를 나타내는 플래그 사이의 관계를 나타내는 루크 테이블을 포함하며, 상기 루크 테이블에 의거하여, 상기 제1의 출력 신호 및 상기 제2의 출력 신호를 선택하는 것을 특징으로 하는 수신 장치.

### 청구항 22

제19항에 있어서,

상기 이퀄라이저는, 상기 적어도 하나의 송신 신호의 고주파 성분을 크게 하도록 이퀄라이즈를 실행하는 것을 특징으로 하는 수신 장치.

### 청구항 23

제19항에 있어서,

상기 적어도 하나의 송신 신호는, 3개의 송신 신호이고,

상기 3개의 송신 신호 중 하나는, 높은 전압 상태, 낮은 전압 상태 및 중간 전압 상태 중의 하나로부터 다른 전압 상태로 천이하는 것을 특징으로 하는 수신 장치.

### 청구항 24

데이터 신호를 생성하는 회로와,

제19항에 기재된 수신 장치를 포함하는 것을 특징으로 하는 장치.

### 청구항 25

데이터 신호에 의거하여 선택적으로 엠파시스를 행하는 것에 의해 3개의 송신 신호를 생성하며, 상기 데이터 신호의 천이 패턴에 의거하여, 데이터 신호에 대한 프리-엠파시스를 실행할지의 여부를 판단하는 송신 제어 회로를 구비하고,

상기 3개의 송신 신호는 각각 높은 전압 상태, 낮은 전압 상태 및 중간 전압 상태의 사이에서 천이하고,

상기 송신 제어 회로에 의한 판정에 의거하여, 상기 프리-엠파시스를 선택적으로 실행하여, 적어도 하나의 송신 신호를 생성하는 송신 드라이버를 포함하는 송신 장치와,

상기 적어도 하나의 송신 신호의 천이 패턴에 의거하여, 제1의 출력 신호 및 제2의 출력 신호를 선택하는 선택 제어 회로를 구비하는 것을 특징으로 하는 통신 시스템.

### 청구항 26

제19항에 기재된 수신 장치를 포함하는 것을 특징으로 하는 통신 시스템.

## 발명의 설명

## 기술 분야

[0001] 본 개시는, 신호를 송신하는 송신 장치, 신호를 수신하는 수신 장치, 및 신호를 송수신하는 통신 시스템에 관한

것이다.

## 배경기술

[0002] 근래의 전자 기기의 고기능화 및 다기능화에 수반하여, 전자 기기에는, 반도체 칩, 센서, 표시 디바이스 등의 다양한 디바이스가 탑재된다. 이들의 디바이스 사이에서는, 많은 데이터의 교환이 행하여지고, 그 데이터량은, 전자 기기의 고기능화 및 다기능화에 응하여 많아져 오고 있다. 그래서, 종종, 예를 들면 수Gbps로 데이터를 송수신 가능한 고속 인터페이스를 이용하여, 데이터의 교환이 행하여진다.

[0003] 고속 인터페이스에서의 통신 성능의 향상을 도모하기 위해, 종종 엠파시스(프리엠파시스, 디엠파시스)나, 이퀄라이저가 사용된다. 프리엠파시스는, 송신시에 신호의 고주파 성분을 미리 강조하는 것이고(예를 들면 특허 문현 1), 디엠파시스는, 송신시에 신호의 저주파 성분을 미리 작게 하는 것이다. 또한, 이퀄라이저는, 수신시에 신호의 고주파 성분을 크게 하는 것이다. 이에 의해, 통신 시스템에서는, 전송로에 의한 신호의 감쇠의 영향을 억제할 수 있고, 통신 성능의 향상을 도모할 수 있도록 되어 있다.

## 선행기술문헌

### 특허문현

[0004] (특허문현 0001) 특허 문현 1 : 일본국 특개2011-142382호 공보

## 발명의 내용

### 해결하려는 과제

[0005] 이와 같이, 통신 시스템에서는, 통신 성능의 향상이 요망되고 있고, 더 한층의 통신 성능의 향상이 기대되고 있다.

[0006] 본 개시는 이러한 문제점을 감안하여 이루어진 것으로, 그 목적은, 통신 성능을 높일 수 있는 송신 장치, 수신 장치, 및 통신 시스템을 제공하는 것에 있다.

### 과제의 해결 수단

[0007] 본 개시의 한 실시예에 따른 송신 장치는, 데이터 신호의 천이 패턴에 의거하여, 데이터 신호에 대한 엠파시스를 실행할지의 여부를 판단하는 송신 제어 회로와, 상기 송신 제어 회로에 의해 판정된 결과에 의거하여, 상기 엠파시스를 선택적으로 실행하여, 적어도 하나의 송신 신호를 생성하는 송신 드라이버를 구비한다.

[0008] 본 개시의 한 실시예에 따른 수신 장치는, 적어도 하나의 송신 신호를 수신하며 제1의 출력 신호를 출력하는 제1의 수신 회로와, 상기 적어도 하나의 송신 신호에 대한 이퀄라이즈를 실행하는 이퀄라이저와, 적어도 하나의 이퀄라이즈된 송신 신호를 상기 이퀄라이저로부터 수신하며 제2의 출력 신호를 수신하는 제2의 수신 회로와, 상기 적어도 하나의 송신 신호의 천이 패턴에 의거하여, 상기 제1의 출력 신호 및 상기 제2의 출력 신호를 선택하는 선택 제어 회로를 구비한다.

[0009] 본 개시의 한 실시예에 따른 통신 시스템은, 데이터 신호의 천이 패턴에 의거하여, 데이터 신호에 대한 프리-엠파시스를 실행할지의 여부를 판단하는 송신 제어 회로와, 상기 송신 제어 회로에 의한 판정에 의거하여, 상기 프리-엠파시스를 선택적으로 실행하여, 적어도 하나의 송신 신호를 생성하는 송신 드라이버를 포함하는 송신 장치와, 상기 적어도 하나의 송신 신호의 천이 패턴에 의거하여, 제1의 출력 신호 및 제2의 출력 신호를 선택하는 선택 제어 회로를 구비한다.

[0010] 본 개시의 한 실시예에 따른 통신 시스템은, 송신 장치와, 수신 장치를 포함하고, 상기 수신 장치는, 적어도 하나의 송신 신호를 수신하며 제1의 출력 신호를 출력하는 제1의 수신 회로와, 상기 적어도 하나의 송신 신호에 대한 이퀄라이즈를 실행하는 이퀄라이저와, 적어도 하나의 이퀄라이즈된 송신 신호를 상기 이퀄라이저로부터 수신하며 제2의 출력 신호를 수신하는 제2의 수신 회로와, 상기 적어도 하나의 송신 신호의 천이 패턴에 의거하여, 상기 제1의 출력 신호 및 상기 제2의 출력 신호를 선택하는 선택 제어 회로를 구비한다.

## 발명의 효과

- [0011] 본 개시의 제1의 송신 장치, 제1의 통신 시스템, 및 제2의 통신 시스템에 의하면, 선택적으로 엠피시스를 행하도록 하였기 때문에, 통신 성능을 높일 수 있다.

- [0012] 본 개시의 제2의 송신 장치에 의하면, 데이터 신호에서의 시간적으로 이웃하는 2개의 송신 심볼을 비교하고, 그 비교 결과에 의거하여 송신 신호의 전압 레벨을 보정하도록 하였기 때문에, 통신 성능을 높일 수 있다.

- [0013] 본 개시의 수신 장치, 및 제2의 통신 시스템에 의하면, 제1의 수신부 또는 제2의 수신부가 수신한 1 또는 복수의 송신 신호의 천이 패턴에 의거하여, 제1의 출력 신호 또는 제2의 출력 신호를 선택하도록 하였기 때문에, 통신 성능을 높일 수 있다.

- [0014] 또한, 여기에 기재된 효과는 반드시 한정되는 것이 아니고, 본 개시 중에 기재된 어느 하나의 효과가 있어도 좋다.

### 도면의 간단한 설명

- [0015] 도 1은 본 개시의 실시의 형태에 관한 통신 시스템의 한 구성례를 도시하는 블록도.

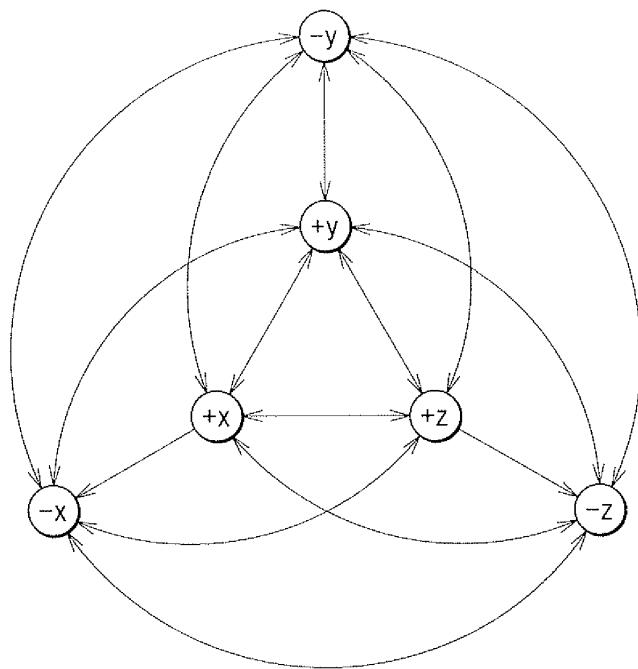

- 도 2는 도 1에 도시한 통신 시스템이 송수신하는 신호의 전압 상태를 도시하는 설명도.

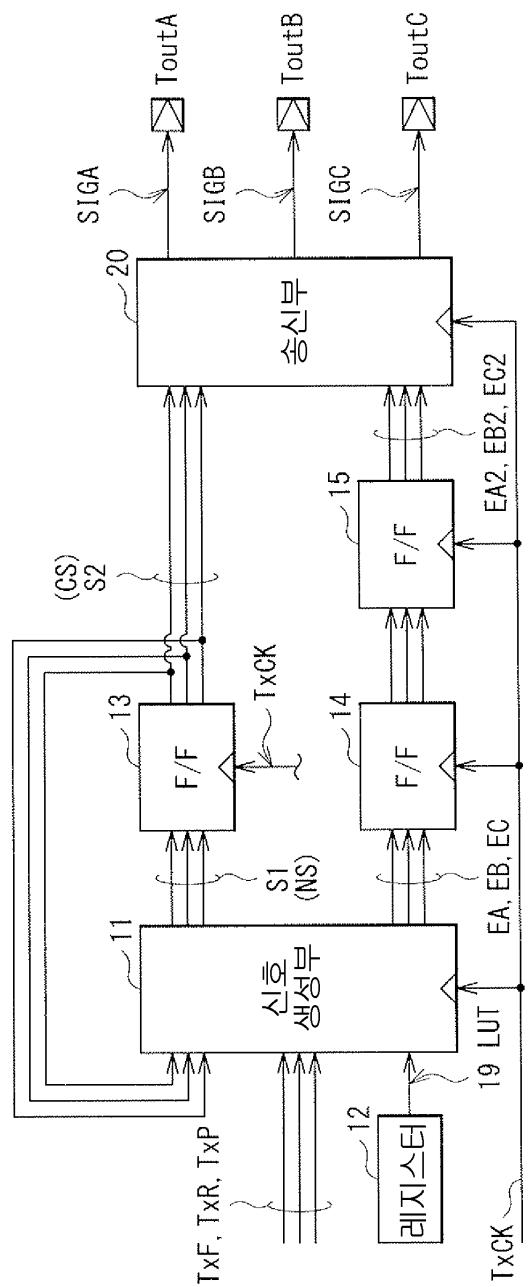

- 도 3은 제1의 실시의 형태에 관한 송신 장치의 한 구성례를 도시하는 블록도.

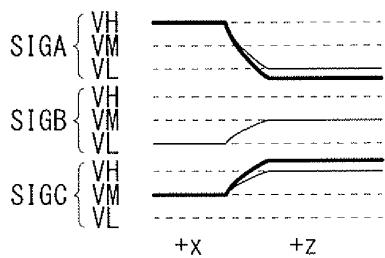

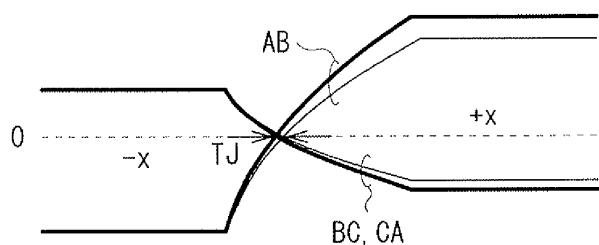

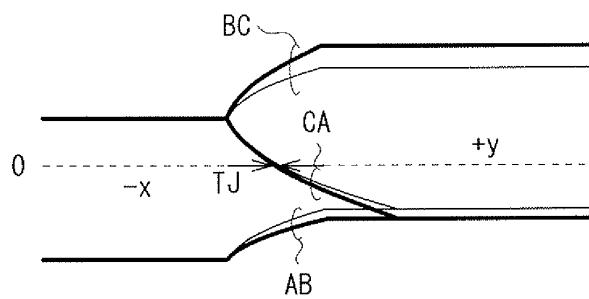

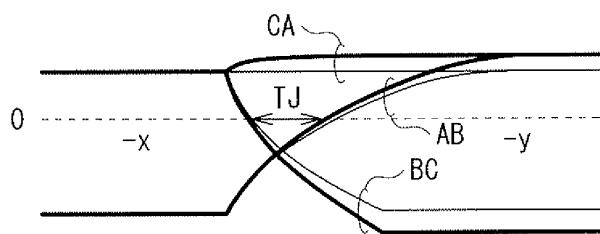

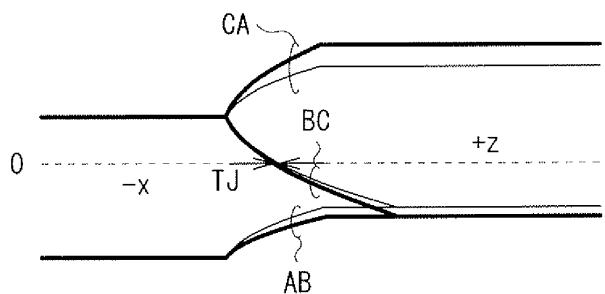

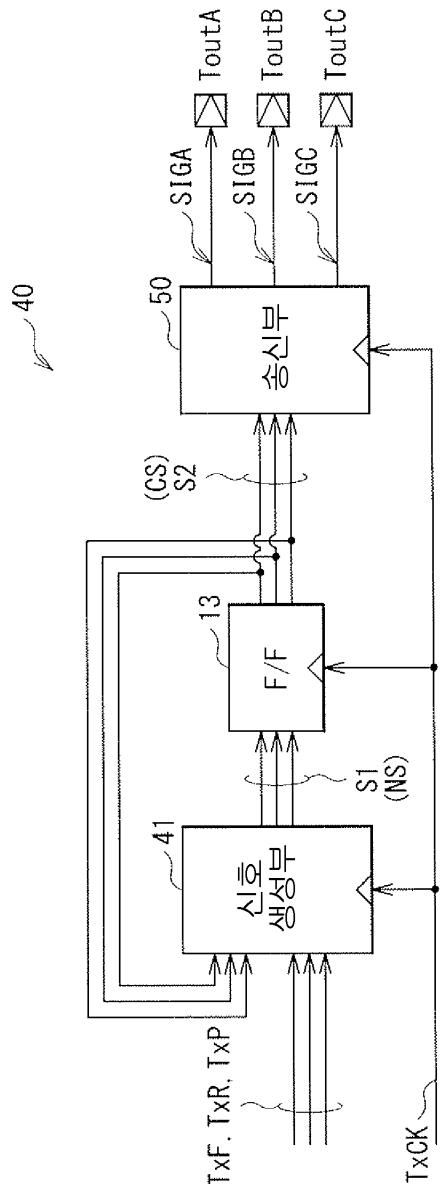

- 도 4는 도 1에 도시한 통신 시스템이 송수신하는 심볼의 천이를 도시하는 설명도.

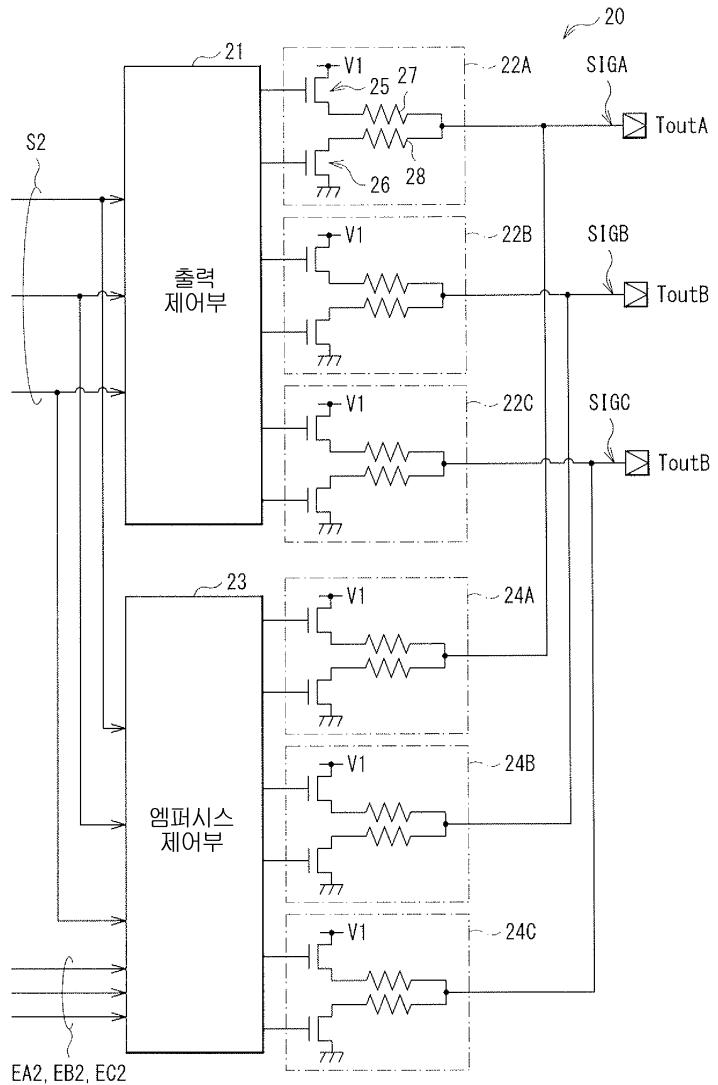

- 도 5는 도 3에 도시한 송신부의 한 구성례를 도시하는 회로도.

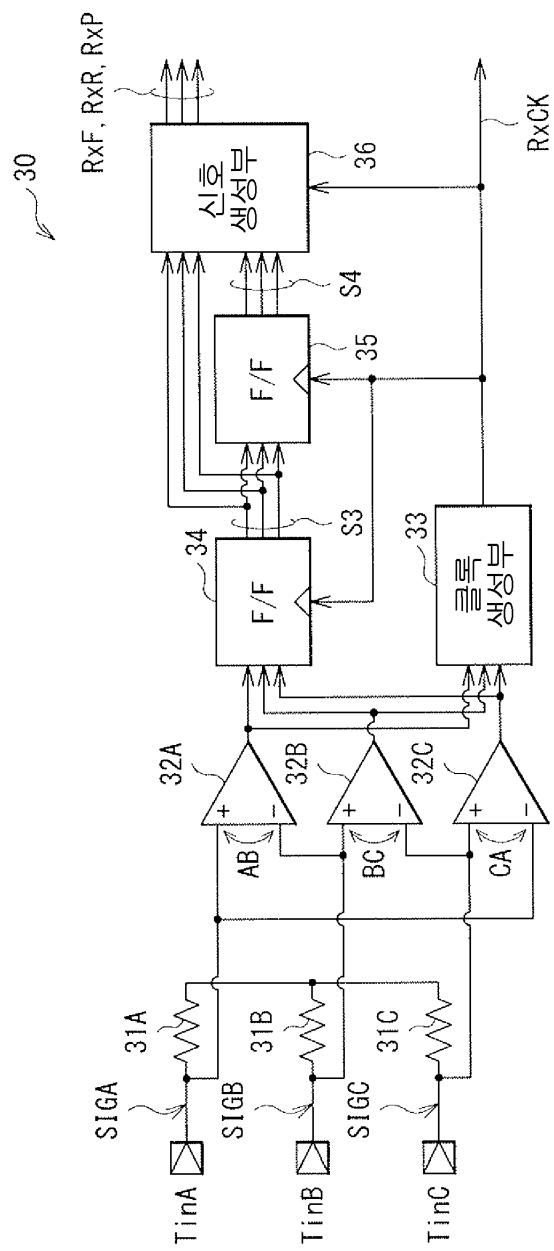

- 도 6은 제1의 실시의 형태에 관한 수신 장치의 한 구성례를 도시하는 블록도.

- 도 7은 도 6에 도시한 수신 장치의 수신 동작의 한 예를 도시하는 설명도.

- 도 8은 도 3에 도시한 신호 생성부의 한 동작례를 도시하는 표.

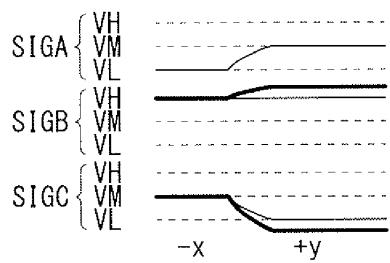

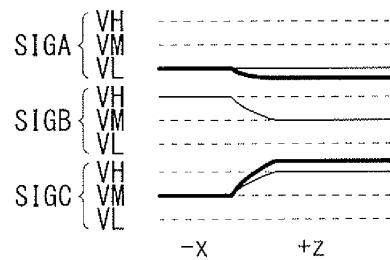

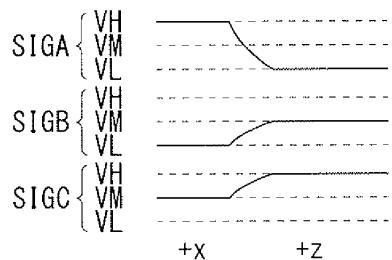

- 도 9A는 도 3에 도시한 송신 장치의 한 동작례를 도시하는 과정도.

- 도 9B는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 9C는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 9D는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 9E는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

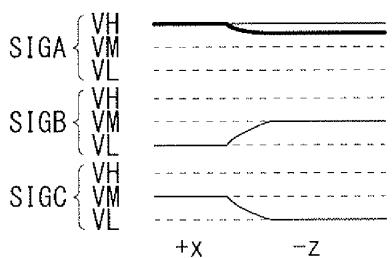

- 도 10A는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 10B는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 10C는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 10D는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 10E는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 11A는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 11B는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 11C는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 11D는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 11E는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 12A는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 12B는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 12C는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 12D는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과정도.

- 도 12E는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 13은 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 14는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 15는 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 16은 도 3에 도시한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 17은 비교례에 관한 송신 장치의 한 동작례를 도시하는 과형도.

- 도 18은 비교례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 19는 제1의 실시의 형태의 변형례에 관한 신호 생성부의 한 동작례를 도시하는 표.

- 도 20은 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 한 구성례를 도시하는 블록도.

- 도 21은 도 20에 도시한 신호 생성부의 한 동작례를 도시하는 표.

- 도 22는 제1의 실시의 형태의 다른 변형례에 관한 신호 생성부의 한 구성례를 도시하는 블록도.

- 도 23은 제1의 실시의 형태의 다른 변형례에 관한 신호 생성부의 한 동작례를 도시하는 표.

- 도 24A는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 한 동작례를 도시하는 과형도.

- 도 24B는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 24C는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 24D는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 24E는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 25A는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 25B는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 25C는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 25D는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 25E는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 26은 제1의 실시의 형태의 다른 변형례에 관한 통신 시스템의 한 구성례를 도시하는 블록도.

- 도 27은 도 26에 도시한 수신 장치의 한 구성례를 도시하는 블록도.

- 도 28은 도 26에 도시한 송신 장치의 한 구성례를 도시하는 블록도.

- 도 29는 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 30은 제1의 실시의 형태의 다른 변형례에 관한 송신 장치의 다른 동작례를 도시하는 과형도.

- 도 31은 제2의 실시의 형태에 관한 송신 장치의 한 구성례를 도시하는 블록도.

- 도 32는 도 31에 도시한 송신부의 한 구성례를 도시하는 회로도.

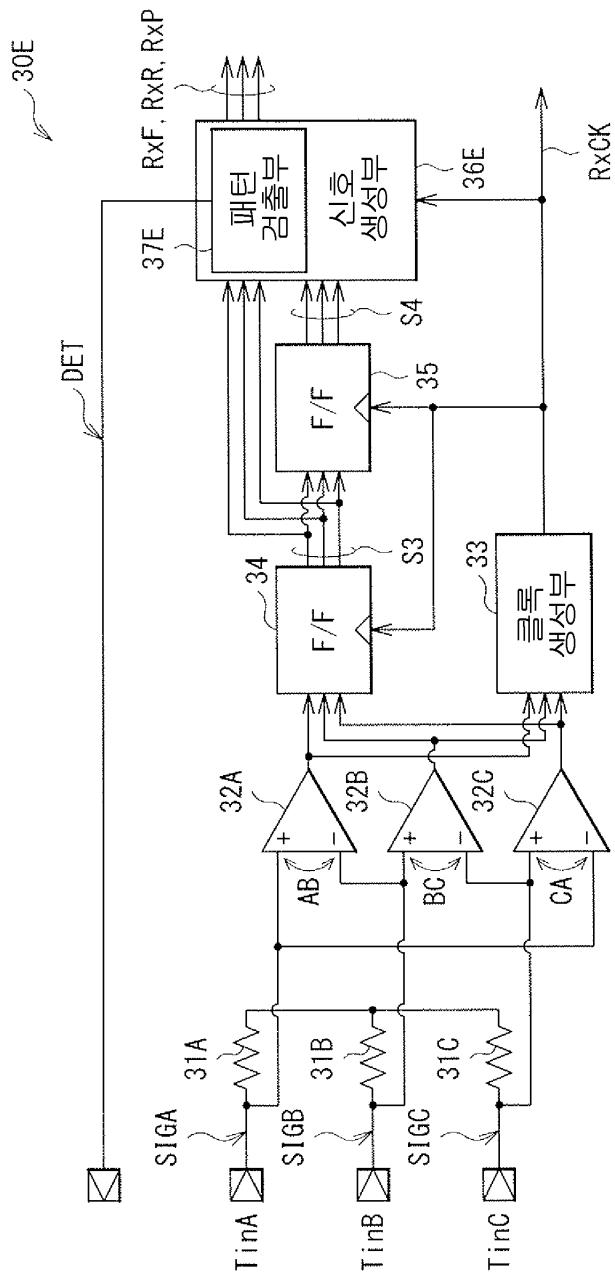

- 도 33은 제2의 실시의 형태에 관한 수신 장치의 한 구성례를 도시하는 블록도.

- 도 34는 도 33에 도시한 수신 장치의 한 동작례를 도시하는 과형도.

- 도 35는 도 33에 도시한 수신 장치의 다른 동작례를 도시하는 과형도.

- 도 36은 도 33에 도시한 수신 장치의 다른 동작례를 도시하는 과형도.

- 도 37은 도 33에 도시한 수신 장치의 다른 동작례를 도시하는 과형도.

- 도 38은 실시의 형태에 관한 통신 시스템이 적용된 스마트 폰의 외관 구성을 도시하는 사시도.

- 도 39는 실시의 형태에 관한 통신 시스템이 적용된 어플리케이션 프로세서의 한 구성례를 도시하는 블록도.

도 40은 실시의 형태에 관한 통신 시스템이 적용된 이미지 센서의 한 구성례를 도시하는 블록도.

### 발명을 실시하기 위한 구체적인 내용

- [0016] 이하, 본 개시의 실시의 형태에 관해, 도면을 참조하여 상세히 설명한다. 또한, 설명은 이하의 순서로 행한다.

- [0017] 1. 제1의 실시의 형태(엠퍼시스를 이용한 예)

- [0018] 2. 제2의 실시의 형태(이퀄라이저를 이용한 예)

- [0019] 3. 적용례

- [0020] (1. 제1의 실시의 형태)

- [0021] 구성례

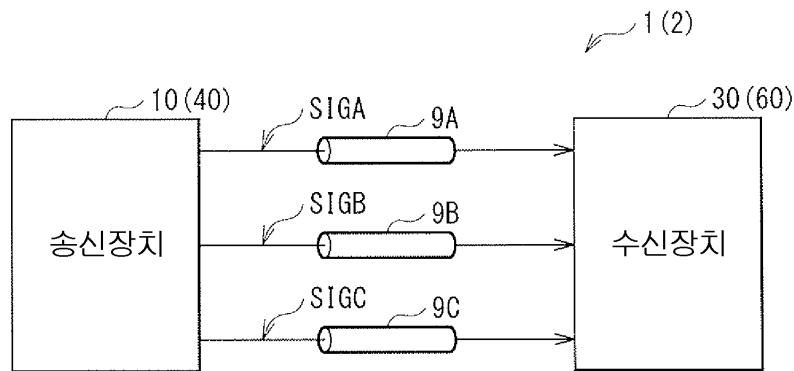

- [0022] 도 1은, 제1의 실시의 형태에 관한 송신 장치가 적용된 통신 시스템의 한 구성례를 도시하는 것이다. 통신 시스템(1)은, 프리엠퍼시스에 의해 통신 품질의 향상을 도모하는 것이다.

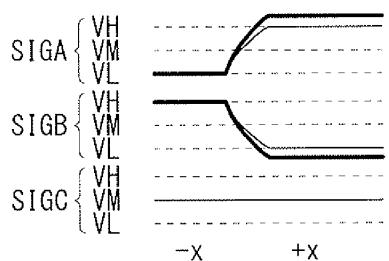

- [0023] 통신 시스템(1)은, 송신 장치(10)와, 수신 장치(30)를 구비하고 있다. 이 통신 시스템(1)에서는, 송신 장치(10)가, 수신 장치(30)에 대해, 전송로(9A, 9B, 9C)를 통하여 신호(SIGA, SIGB, SIGC)를 각각 송신하도록 되어 있다. 신호(SIGA, SIGB, SIGC)는, 각각, 3개의 전압 상태(SH, SM, SL)의 사이에서 천이하는 것이다. 여기서, 전압 상태(SH)는, 고레벨 전압(VH)에 대응하는 상태이다. 즉, 전압 상태(SH)가 나타내는 전압은, 후술하는 바와 같이, 고레벨 전압(VH)에 더하여, 이 고레벨 전압(VH)에 대해 프리엠퍼시스를 행한 경우의 전압도 포함하는 것이다. 마찬가지로, 전압 상태(SM)는, 중레벨 전압(VM)에 대응하는 상태이고, 전압 상태(SL)는, 저레벨 전압(VL)에 대응하는 상태이다.

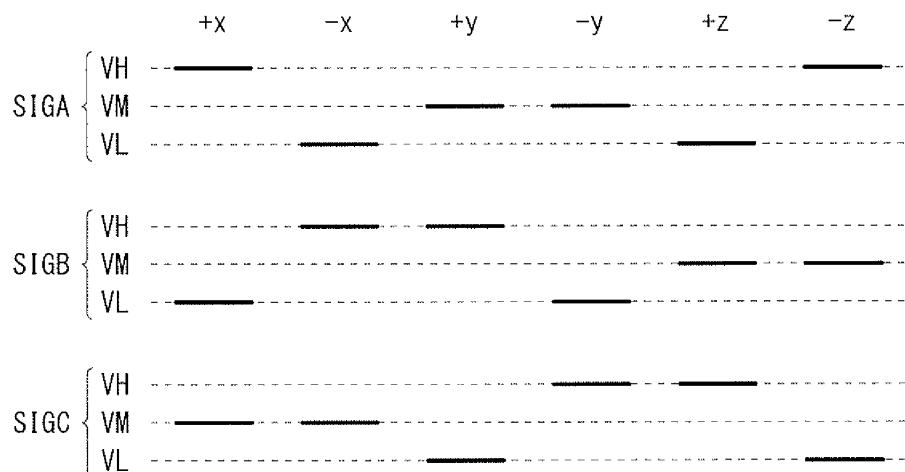

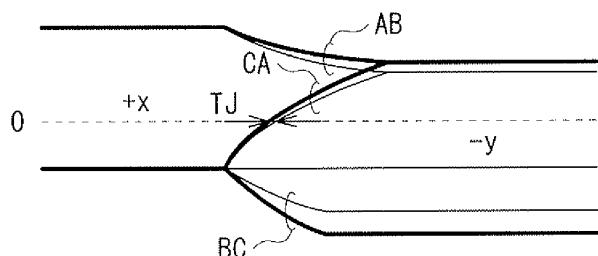

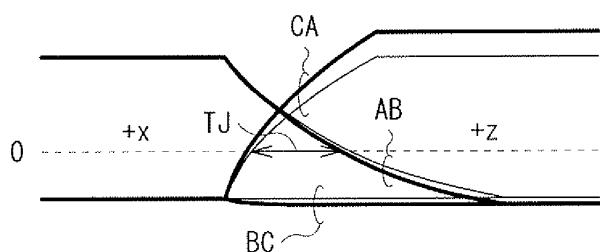

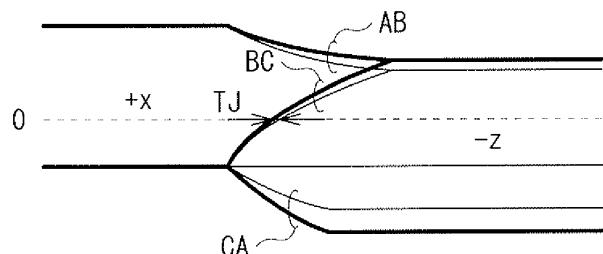

- [0024] 도 2는, 신호(SIGA, SIGB, SIGC)의 전압 상태를 도시하는 것이다. 송신 장치(10)는, 3개의 신호(SIGA, SIGB, SIGC)를 이용하여, 6개의 심볼"+x", "-x", "+y", "-y", "+z", "-z"를 송신한다. 예를 들면, 심볼"+x"를 송신하는 경우에는, 송신 장치(10)는, 신호(SIGA)를 전압 상태(SH)(예를 들면 고레벨 전압(VH))로 하고 신호(SIGB)를 전압 상태(SL)(예를 들면 저레벨 전압(VL))로 하고 신호(SIGC)를 전압 상태(SM)(예를 들면 중레벨 전압(VM))로 한다. 심볼"-x"를 송신하는 경우에는, 송신 장치(10)는, 신호(SIGA)를 전압 상태(SL)로 하고 신호(SIGB)를 전압 상태(SH)로 하고 신호(SIGC)를 전압 상태(SM)로 한다. 심볼"+y"를 송신하는 경우에는, 송신 장치(10)는, 신호(SIGA)를 전압 상태(SM)로 하고 신호(SIGB)를 전압 상태(SL)로 하고 신호(SIGC)를 전압 상태(SH)로 한다. 심볼"-y"를 송신하는 경우에는, 송신 장치(10)는, 신호(SIGA)를 전압 상태(SM)로 하고 신호(SIGB)를 전압 상태(SL)로 하고 신호(SIGC)를 전압 상태(SH)로 한다. 심볼"+z"를 송신하는 경우에는, 송신 장치(10)는, 신호(SIGA)를 전압 상태(SH)로 하고 신호(SIGB)를 전압 상태(SM)로 하고 신호(SIGC)를 전압 상태(SL)로 한다. 심볼"-z"를 송신하는 경우에는, 송신 장치(10)는, 신호(SIGA)를 전압 상태(SH)로 하고 신호(SIGB)를 전압 상태(SM)로 하고 신호(SIGC)를 전압 상태(SL)로 하도록 되어 있다.

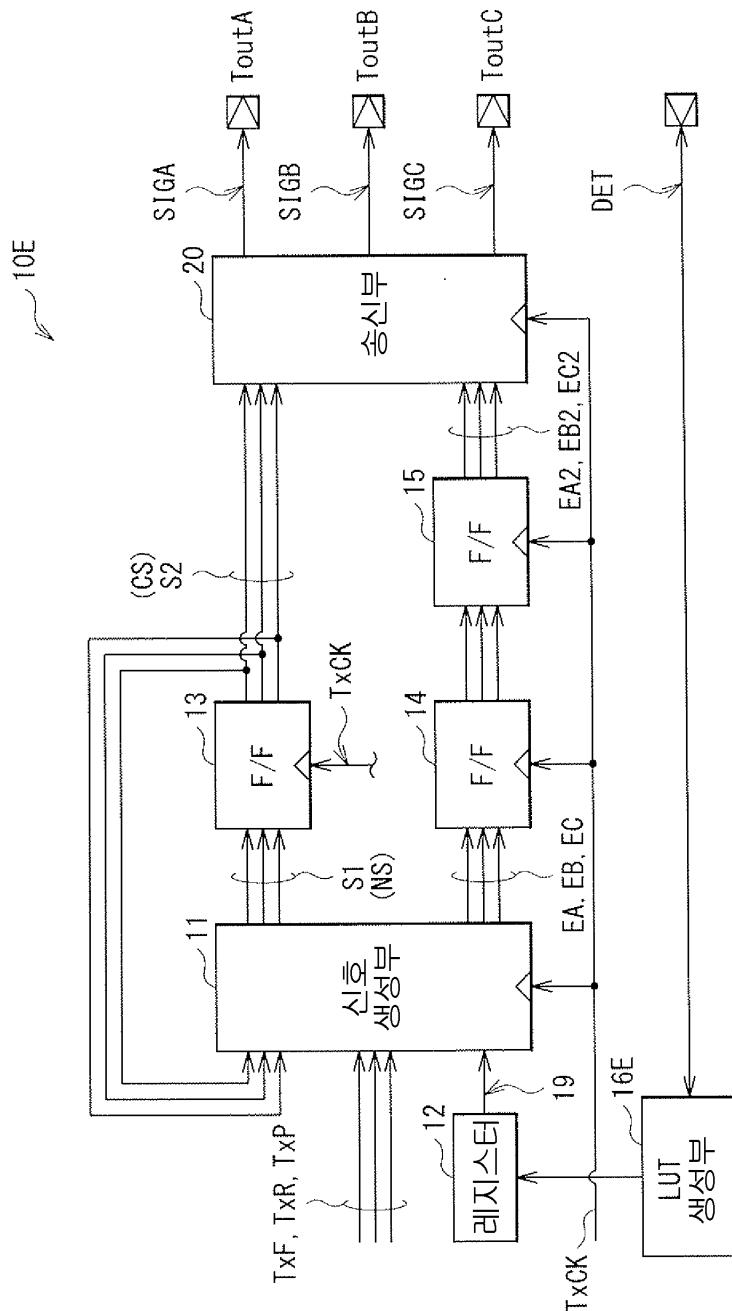

- [0025] 도 3은, 송신 장치(10)의 한 구성례를 도시하는 것이다. 송신 장치(10)는, 신호 생성부(11)와, 레지스터(12)와, 플립플롭(F/F)(13~15)과, 송신부(20)를 갖고 있다.

- [0026] 신호 생성부(11)는, 심볼(CS), 신호(TxF, TxR, TxP), 및 클록(TxCK)에 의거하여, 심볼(NS)을 구하는 것이다. 여기서, 심볼(CS, NS)은, 각각, 6개의 심볼"+x", "-x", "+y", "-y", "+z", "-z" 중의 어느 하나를 나타내는 것이다. 심볼(CS)은 현재 송신하고 있는 심볼(현재의 심볼)이고, 심볼(NS)은 다음에 송신하는 심볼(다음의 심볼)이다.

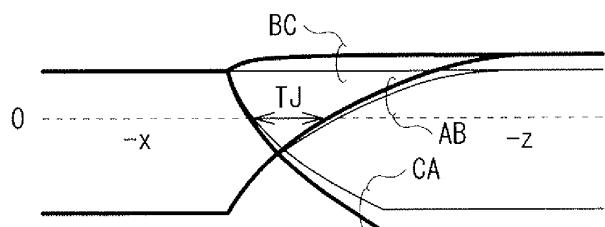

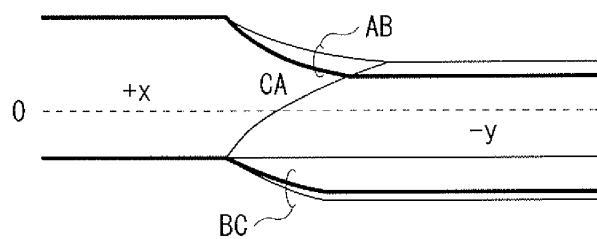

- [0027] 도 4는, 신호 생성부(11)의 동작을 도시하는 것이다. 이 도 4는, 6개의 심볼"+x", "-x", "+y", "-y", "+z", "-z"와, 그들 사이의 천이를 도시하고 있다.

- [0028] 신호(TxF)는, "+x"와 "-x"의 사이에서 심볼을 천이시키고, "+y"와 "-y"의 사이에서 심볼을 천이시키고, "+z"와 "-z"의 사이에서 심볼을 천이시키는 것이다. 구체적으로는, 신호(TxF)가 "1"인 경우에는, 심볼의 극성을 변경하도록(예를 들면 "+x"로부터 "-x"로) 천이하고, 신호(TxF)가 "0"인 경우에는, 이와 같은 천이를 행하지 않도록 되어 있다.

- [0029] 신호(TxR, TxP)는, 신호(TxF)가 "0"인 경우에 있어서, "+x"와 "+x" 이외와의 사이, "+y"와 "+y" 이외와의 사이, "+z"와 "+z" 이외와의 사이에서 심볼을 천이시키는 것이다. 구체적으로는, 신호(TxR)가 "1"이고, 또한 신호(TxP)가 "0"인 경우에는, 심볼의 극성을 유지한 채로, 도 4에서 우회전으로(예를 들면 "+x"로부터 "+y"로)

천이하고, 신호(TxR)가 "1"이고, 또한 신호(TxP)가 "1"인 경우에는, 심볼의 극성을 변경함과 함께, 도 4에서 우회전으로 (예를 들면 "+x"로부터 "-y"로) 천이한다. 또한, 신호(TxR)가 "0"이고, 또한 신호(TxP)가 "0"인 경우에는, 심볼의 극성을 유지한 채로, 도 4에서 좌회전으로 (예를 들면 "+x"로부터 "+z"로) 천이하고, 신호(TxR)가 "0"이고, 또한 신호(TxP)가 "1"인 경우에는, 심볼의 극성을 변경함과 함께, 도 4에서 좌회전으로 (예를 들면 "+x"로부터 "-z"로) 천이한다.

[0030] 이와 같이, 신호 생성부(11)에서는, 신호(TxF, TxR, TxP)에 의해, 심볼의 천이의 방향이 특정된다. 따라서, 신호 생성부(11)는, 현재의 심볼(CS)과, 이들의 신호(TxF, TxR, TxP)에 의거하여, 다음의 심볼(NS)을 구할 수 있다. 그리고, 신호 생성부(11)는, 이 심볼(NS)을, 이 예에서는, 3비트의 신호(S1)를 이용하여 플립플롭(13)에 공급하도록 되어 있다.

[0031] 또한, 신호 생성부(11)는, 레지스터(12)로부터 공급된 LUT(Look Up Table)(19)에 의거하여, 신호(EA, EB, EC)를 생성하는 기능도 갖고 있다. 신호(EA)는, 신호(SIGA)에 관해 프리앰페리스를 행하는지의 여부를 나타내는 것이고, 신호 생성부(11)는, 신호(EA)를 액티브로 함에 의해, 신호(SIGA)에 대해 프리앰페리스를 행하도록 제어한다. 마찬가지로, 신호(EB)는, 신호(SIGB)에 관해 프리앰페리스를 행하는지의 여부를 나타내는 것이고, 신호 생성부(11)는, 신호(EC)를 액티브로 함에 의해, 신호(SIGC)에 대해 프리앰페리스를 행하도록 제어한다. 또한, 신호(EC)는, 신호(SIGC)에 관해 프리앰페리스를 행하는지의 여부를 나타내는 것이고, 신호 생성부(11)는, 신호(EC)를 액티브로 함에 의해, 신호(SIGC)에 대해 프리앰페리스를 행하도록 제어한다. LUT(19)는, 현재의 심볼(CS)과, 신호(TxF, TxR, TxP)와, 신호(EA, EB, EC)와의 관계를 나타낸 것이다. 신호 생성부(11)는, 현재의 심볼(CS) 및 신호(TxF, TxR, TxP)에 의거하여, 이 LUT(19)를 참조하여, 신호(EA, EB, EC)를 생성한다. 환언하면, 신호 생성부(11)는, 시간적으로 이웃하는 2개의 심볼(현재의 심볼(CS) 및 다음의 심볼(NS)), 즉 연속한 2개의 심볼에 따르고, 신호(EA, EB, EC)를 생성하도록 되어 있다.

[0032] 이 구성에 의해, 신호 생성부(11)는, 예를 들면, 전압 상태(SH, SM, SL)의 사이의 천이 중의 일부의 천이에 대해 선택적으로 프리앰페리스를 행할 수가 있음과 함께, 신호(SIGA, SIGB, SIGC) 중의 일부의 신호에 대해 선택적으로 프리앰페리스를 행할 수가 있도록 되어 있다.

[0033] 레지스터(12)는, LUT(19)를 기억하는 것이다. 이 LUT(19)는, 예를 들면, 송신 장치(10)의 전원 투입시에, 도시하지 않은 어플리케이션 프로세서로부터, 이 레지스터(12)에 기록되도록 되어 있다.

[0034] 플립플롭(13)은, 신호(S1)를, 클록(TxCK)의 1클록분 지연시켜, 3비트의 신호(S2)로서 출력하는 것이다. 즉, 플립플롭(13)은, 신호(S1)가 나타내는 다음의 심볼(NS)을 클록(TxCK)의 1클록분 지연시킴에 의해, 현재의 심볼(CS)을 생성하고 있다. 그리고, 플립플롭(13)은, 그 신호(S2)를, 신호 생성부(11) 및 송신부(20)에 공급하도록 되어 있다.

[0035] 플립플롭(14)은, 신호(EA, EB, EC)를, 클록(TxCK)의 1클록분 지연시켜, 각각 출력하는 것이다. 플립플롭(15)은, 플립플롭(14)의 3개의 출력 신호를, 클록(TxCK)의 1클록분 지연시켜, 신호(EA2, EB2, EC2)로서 각각 출력하는 것이다. 그리고, 플립플롭(15)은, 그 신호(EA2, EB2, EC2)를 송신부(20)에 공급하도록 되어 있다.

[0036] 송신부(20)는, 신호(S2) 및 신호(EA2, EB2, EC2)에 의거하여, 신호(SIGA, SIGB, SIGC)를 생성하는 것이다.

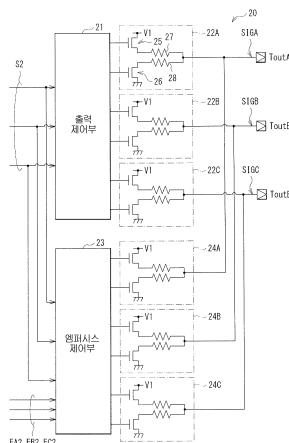

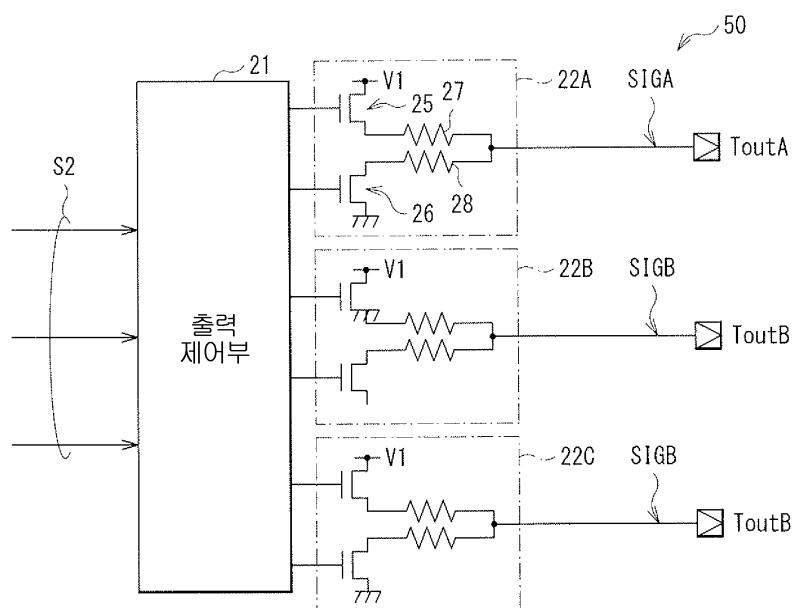

[0037] 도 5는, 송신부(20)의 한 구성례를 도시하는 것이다. 송신부(20)는, 출력 제어부(21)와, 출력부(22A, 22B, 22C)와, 엠퍼리스 제어부(23)와, 출력부(24A, 24B, 24C)를 갖고 있다.

[0038] 출력 제어부(21)는, 신호(S2)에 의거하여, 출력부(22A, 22B, 22C)에 제어 신호를 공급하고, 출력부(22A, 22B, 22C)의 동작을 제어하는 것이다.

[0039] 출력부(22A)는, 출력 제어부(21)로부터 공급된 제어 신호에 의거하여, 신호(SIGA)의 전압 상태를, 전압 상태(SH, SM, SL) 중의 어느 하나로 설정하는 것이다. 출력부(22B)는, 출력 제어부(21)로부터 공급된 제어 신호에 의거하여, 신호(SIGB)의 전압 상태를, 전압 상태(SH, SM, SL) 중의 어느 하나로 설정하는 것이다. 출력부(22C)는, 출력 제어부(21)로부터 공급된 제어 신호에 의거하여, 신호(SIGC)의 전압 상태를, 전압 상태(SH, SM, SL) 중의 어느 하나로 설정하는 것이다.

[0040] 이 구성에 의해, 송신부(20)는, 신호(S2)가 나타내는 심볼(CS)에 의거하여, 신호(SIGA, SIGB, SIGC)를, 도 2에 도시한 바와 같이, 심볼(CS)에 대응하는 전압 상태(SH, SM, SL)로 설정할 수 있도록 되어 있다.

[0041] 이하, 송신부(20)의 출력부(22A)에 관해 보다 상세히 설명한다. 출력부(22B, 22C)에 관해서도 마찬가지이다.

- [0042] 출력부(22A)는, 트랜지스터(25, 26)와, 저항 소자(27, 28)를 갖고 있다. 트랜지스터(25, 26)는, 이 예에서는, N 채널 MOS(Metal Oxide Semiconductor)형의 FET(Field Effect Transistor)이다. 트랜지스터(25)의 게이트에는 출력 제어부(21)로부터 제어 신호가 공급되고, 드레인에는 전압(V1)이 공급되고, 소스는 저항 소자(27)의 일단에 접속되어 있다. 트랜지스터(26)의 게이트에는 출력 제어부(21)로부터 제어 신호가 공급되고, 드레인은 저항 소자(28)의 일단에 접속되고, 소스는 접지되어 있다. 저항 소자(27, 28)는, 통신 시스템(1)에서의 종단(終端) 저항으로서 기능하는 것이다. 저항 소자(27)의 일단은 트랜지스터(25)의 소스에 접속되고, 타단은, 저항 소자(28)의 타단에 접속됨과 함께, 출력 단자(ToutA)에 접속되어 있다. 저항 소자(28)의 일단은 트랜지스터(26)의 드레인에 접속되고, 타단은, 저항 소자(27)의 타단에 접속됨과 함께, 출력 단자(ToutA)에 접속되어 있다.

- [0043] 예를 들면 신호(SIGA)를 전압 상태(SH)로 설정하는 경우에는, 출력 제어부(21)는, 고레벨의 제어 신호를 트랜지스터(25)에 공급함과 함께, 저레벨의 제어 신호를 트랜지스터(26)에 공급한다. 이에 의해, 트랜지스터(25)가 온 상태가 됨과 함께 트랜지스터(26)가 오프 상태가 되고, 트랜지스터(25)를 통하여 출력 전류가 흐르고, 신호(SIGA)가 전압 상태(SH)로 설정된다. 또한, 예를 들면 신호(SIGA)를 전압 상태(SL)로 설정하는 경우에는, 출력 제어부(21)는, 저레벨의 제어 신호를 트랜지스터(25)에 공급함과 함께, 고레벨의 제어 신호를 트랜지스터(26)에 공급한다. 이에 의해, 트랜지스터(25)가 오프 상태가 됨과 함께 트랜지스터(26)가 온 상태가 되고, 트랜지스터(26)를 통하여 출력 전류가 흐르고, 신호(SIGA)가 전압 상태(SL)로 설정된다. 또한, 예를 들면 신호(SIGA)를 전압 상태(SM)로 설정하는 경우에는, 출력 제어부(21)는, 저레벨의 제어 신호를 트랜지스터(25, 26)에 공급한다. 이에 의해, 트랜지스터(25, 26)가 오프 상태가 되고, 수신 장치(30)의 저항 소자(31A, 31B, 31C)(후술)에 의해, 신호(SIGA)가 전압 상태(SM)로 설정되도록 되어 있다.

- [0044] 앰페시스 제어부(23)는, 신호(S2) 및 신호(EA2, EB2, EC2)에 의거하여, 출력부(24A, 24B, 24C)의 동작을 제어하는 것이다. 구체적으로는, 앰페시스 제어부(23)는, 신호(S2) 및 신호(EA2)에 의거하여, 출력부(24A)에 대해 제어 신호를 공급하고, 신호(S2) 및 신호(EB2)에 의거하여, 출력부(24B)에 대해 제어 신호를 공급하고, 신호(S2) 및 신호(EC2)에 의거하여, 출력부(24C)에 대해 제어 신호를 공급하도록 되어 있다.

- [0045] 출력부(24A)는, 앰페시스 제어부(23)로부터 공급된 제어 신호에 의거하여, 신호(SIGA)에 대해 프리앰페시스를 행하는 것이다. 출력부(24B)는, 앰페시스 제어부(23)로부터 공급된 제어 신호에 의거하여, 신호(SIGB)에 대해 프리앰페시스를 행하는 것이다. 출력부(24C)는, 앰페시스 제어부(23)로부터 공급된 제어 신호에 의거하여, 신호(SIGC)에 대해 프리앰페시스를 행하는 것이다. 제어부(24A, 24B, 24C)의 구성은, 출력부(22A, 22B, 22C)와 마찬가지이다.

- [0046] 이 구성에 의해, 송신부(20)는, 신호(EA2)가 액티브인 경우에, 신호(SIGA)에 대해 프리앰페시스를 행하여, 신호(EB2)가 액티브인 경우에, 신호(SIGB)에 대해 프리앰페시스를 행하여, 신호(EC2)가 액티브인 경우에, 신호(SIGC)에 대해 프리앰페시스를 행하도록 되어 있다.

- [0047] 또한, 송신부(20)는, 이 구성으로 한정되는 것이 아니고, 다른 다양한 구성이 적용 가능하다.

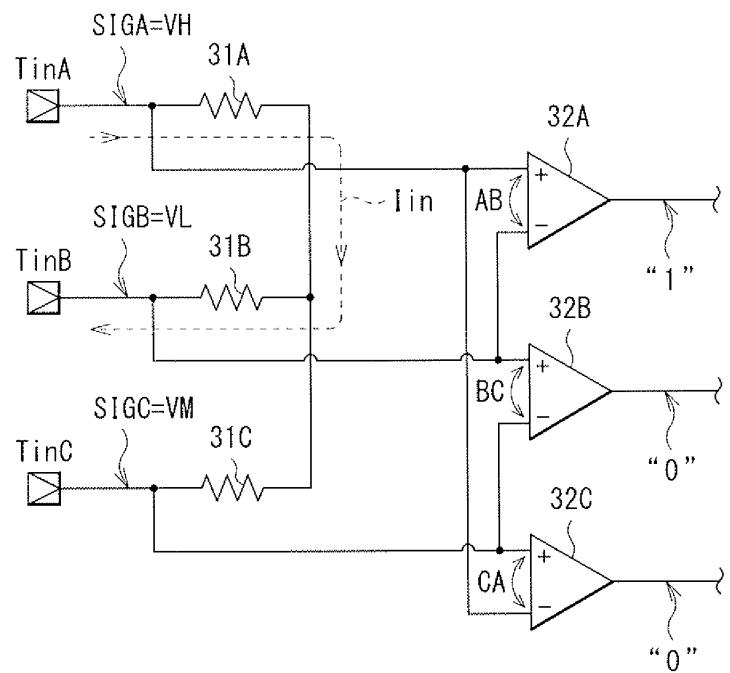

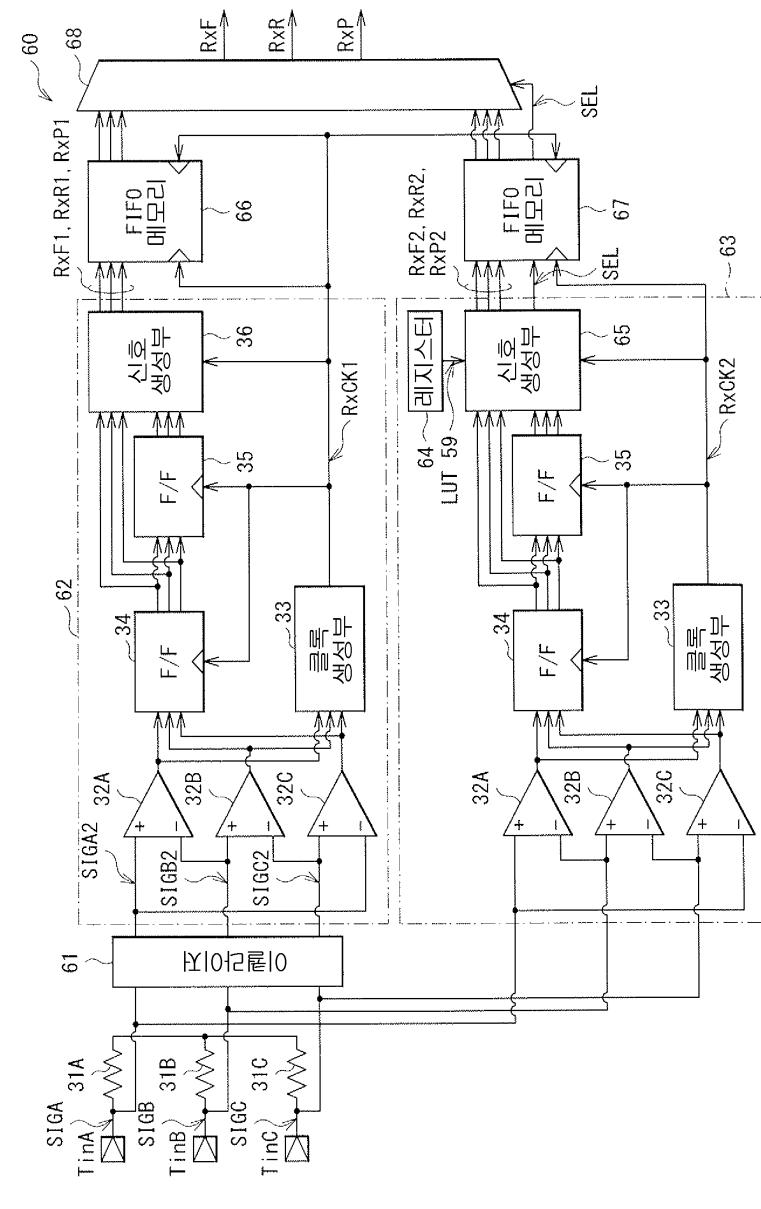

- [0048] 도 6은, 수신 장치(30)의 한 구성례를 도시하는 것이다. 수신 장치(30)는, 저항 소자(31A, 31B, 31C)와, 앰플리파이어(32A, 32B, 32C)와, 클록 생성부(33)와, 플립플롭(F/F)(34, 35)과, 신호 생성부(36)를 갖고 있다.

- [0049] 저항 소자(31A, 31B, 31C)는, 통신 시스템(1)에서의 종단 저항으로서 기능하는 것이다. 저항 소자(31A)의 일단은 입력단자(TinA)에 접속됨과 함께 신호(SIGA)가 공급되고, 타단은 저항 소자(31B, 31C)의 타단에 접속되어 있다. 저항 소자(31B)의 일단은 입력단자(TinB)에 접속됨과 함께 신호(SIGB)가 공급되고, 타단은 저항 소자(31A, 31C)의 타단에 접속되어 있다. 저항 소자(31C)의 일단은 입력단자(TinC)에 접속됨과 함께 신호(SIGC)가 공급되고, 타단은 저항 소자(31A, 31B)의 타단에 접속되어 있다.

- [0050] 앰플리파이어(32A, 32B, 32C)는, 각각, 정입력단자에서의 신호와 부입력단자에서의 신호의 차분에 응한 신호를 출력하는 것이다. 앰플리파이어(32A)의 정입력단자는, 앰플리파이어(32C)의 부입력단자 및 저항 소자(31A)의 일단에 접속됨과 함께 신호(SIGA)가 공급되고, 부입력단자는, 앰플리파이어(32B)의 정입력단자 및 저항 소자(31B)의 일단에 접속됨과 함께 신호(SIGB)가 공급된다. 앰플리파이어(32B)의 정입력단자는, 앰플리파이어(32A)의 부입력단자 및 저항 소자(31B)의 일단에 접속됨과 함께 신호(SIGB)가 공급되고, 부입력단자는, 앰플리파이어(32C)의 정입력단자 및 저항 소자(31C)의 일단에 접속됨과 함께 신호(SIGC)가 공급된다. 앰플리파이어(32C)의 정입력단자는, 앰플리파이어(32B)의 부입력단자 및 저항 소자(31C)의 일단에 접속됨과 함께 신호(SIGC)가 공급되고, 부입력단자는, 앰플리파이어(32A)의 정입력단자 및 저항 소자(31A)에 접속됨과 함께 신호(SIGA)가 공급된다.

- [0051] 이 구성에 의해, 앰플리파이어(32A)는, 신호(SIGA)와 신호(SIGB)와의 차분(AB)(SIGA-SIGB)에 응한 신호를 출력하고, 앰플리파이어(32B)는, 신호(SIGB)와 신호(SIGC)와의 차분(BC)(SIGB-SIGC)에 응한 신호를 출력하고, 앰플리파이어(32C)는, 신호(SIGC)와 신호(SIGA)와의 차분(CA)(SIGC-SIGA)에 응한 신호를 출력하도록 되어 있다.

- [0052] 도 7은, 앰플리파이어(32A, 32B, 32C)의 한 동작례를 도시하는 것이다. 이 예에서는, 신호(SIGA)는 고레벨 전압(VH)이고, 신호(SIGB)는 저레벨 전압(VL)이고, 신호(SIGC)는 중레벨 전압(VM)이다. 이 경우에는, 입력단자(TinA), 저항 소자(31A), 저항 소자(31B), 입력단자(TinB)의 순서로 전류(Iin)가 흐른다. 그리고, 앰플리파이어(32A)의 정입력단자에는 고레벨 전압(VH)이 공급됨과 함께 부입력단자에는 저레벨 전압(VL)이 공급되고, 차분(AB)은 정( $AB>0$ )이 되기 때문에, 앰플리파이어(32A)는 "1"을 출력한다. 또한, 앰플리파이어(32B)의 정입력단자에는 저레벨 전압(VL)이 공급됨과 함께 부입력단자에는 중레벨 전압(VM)이 공급되고, 차분(BC)은 부( $BC<0$ )가 되기 때문에, 앰플리파이어(32B)는 "0"을 출력한다. 또한, 앰플리파이어(32C)의 정입력단자에는 중레벨 전압(VM)이 공급됨과 함께 부입력단자에는 고레벨 전압(VH)이 공급되고, 차분(CA)은 부( $CA<0$ )가 되기 때문에, 앰플리파이어(32C)는 "0"을 출력하도록 되어 있다.

- [0053] 클록 생성부(33)는, 앰플리파이어(32A, 32B, 32C)의 출력 신호에 의거하여, 클록(RxCK)을 생성하는 것이다.

- [0054] 플립플롭(34)은, 앰플리파이어(32A, 32B, 32C)의 출력 신호를, 클록(RxCK)의 1클록분 지연시켜, 각각 출력하는 것이다. 즉, 플립플롭(34)의 출력 신호는, 현재의 심볼(CS2)을 나타내는 것이다. 여기서, 현재의 심볼(CS2)은, 심볼(CS, NS)과 마찬가지로, 6개의 심볼"+x", "-x", "+y", "-y", "+z", "-z" 중의 어느 하나를 나타내는 것이다.

- [0055] 플립플롭(35)은, 플립플롭(34)의 3개의 출력 신호를, 클록(RxCK)의 1클록분 지연시켜, 각각 출력하는 것이다. 즉, 플립플롭(35)은, 현재의 심볼(CS2)을 클록(RxCK)의 1클록분 지연시킴에 의해, 심볼(PS2)을 생성하고 있다. 이 심볼(PS2)은, 전에 수신한 심볼(전의 심볼)이고, 심볼(CS, NS, CS2)과 마찬가지로, 6개의 심볼"+x", "-x", "+y", "-y", "+z", "-z" 중의 어느 하나를 나타내는 것이다.

- [0056] 신호 생성부(36)는, 플립플롭(34, 35)의 출력 신호, 및 클록(RxCK)에 의거하여, 신호(RxF, RxR, RxP)를 생성하는 것이다. 이 신호(RxF, RxR, RxP)는, 송신 장치(10)에서의 신호(TxF, TxR, TxP)에 각각 대응하는 것이고, 심볼의 천이를 나타내는 것이다. 신호 생성부(36)는, 플립플롭(34)의 출력 신호가 나타내는 현재의 심볼(CS2)과, 플립플롭(35)의 출력 신호가 나타내는 전(前)의 심볼(PS2)에 의거하여, 심볼의 천이(도 4)를 특정하고, 신호(RxF, RxR, RxP)를 생성하도록 되어 있다.

- [0057] 여기서, 신호(S1, S2)는, 본 개시에서의 「데이터 신호」의 한 구체례에 대응한다. 신호(SIGA, SIGB, SIGC)는, 본 개시에서의 「1 또는 복수의 송신 신호」의 한 구체례에 대응한다. 신호 생성부(11)는, 본 개시에서의 「제어부」의 한 구체례에 대응한다.

- [0058] 동작 및 작용

- [0059] 계속해서, 본 실시의 형태의 통신 시스템(1)의 동작 및 작용에 관해 설명한다.

- [0060] (전체 동작 개요)

- [0061] 우선, 도 1 등을 참조하여, 통신 시스템(1)의 전체 동작 개요를 설명한다. 송신 장치(10)에서, 신호 생성부(11)는, 현재의 심볼(CS) 및 신호(TxF, TxR, TxP)에 의거하여, 다음의 심볼(NS)을 구하고, 신호(S1)로서 출력한다. 또한, 신호 생성부(11)는, 현재의 심볼(CS) 및 신호(TxF, TxR, TxP)에 의거하여, LUT(19)를 참조하여, 신호(EA, EB, EC)를 생성하여 출력한다. 플립플롭(13)은, 신호(S1)를, 클록(TxCK)의 1클록분 지연시켜, 신호(S2)로서 출력한다. 플립플롭(14)은, 신호(EA, EB, EC)를, 클록(TxCK)의 1클록분 지연시켜, 각각 출력한다. 플립플롭(15)은, 플립플롭(14)의 3개의 출력 신호를, 클록(TxCK)의 1클록분 지연시켜, 신호(EA2, EB2, EC2)로서 각각 출력한다. 송신부(20)는, 신호(S2) 및 신호(EA2, EB2, EC2)에 의거하여, 신호(SIGA, SIGB, SIGC)를 생성한다.

- [0062] 수신 장치(30)에서, 앰플리파이어(32A)는, 신호(SIGA)와 신호(SIGB)와의 차분(AB)에 응한 신호를 출력하고, 앰플리파이어(32B)는, 신호(SIGB)와 신호(SIGC)와의 차분(BC)에 응한 신호를 출력하고, 앰플리파이어(32C)는, 신호(SIGC)와 신호(SIGA)와의 차분(CA)에 응한 신호를 출력한다. 클록 생성부(33)는, 앰플리파이어(32A, 32B, 32C)의 출력 신호에 의거하여, 클록(RxCK)을 생성한다. 플립플롭(34)은, 앰플리파이어(32A, 32B, 32C)의 출력 신호를, 클록(RxCK)의 1클록분 지연시켜, 각각 출력한다. 플립플롭(35)은, 플립플롭(34)의 3개의 출력 신호를, 클록(RxCK)의 1클록분 지연시켜, 각각 출력한다. 신호 생성부(36)는, 플립플롭(34, 35)의 출력 신호, 및 클록

(RxCK)에 의거하여, 신호(RxF, RxR, RxP)를 생성한다.

[0063] (상세 동작)

[0064] 신호 생성부(11)는, 현재의 심볼(CS) 및 신호(TxF, TxR, TxP)에 의거하여, 다음의 심볼(NS)을 구함과 함께, LUT(19)를 참조하여, 신호(SIGA, SIGB, SIGC)에 관해 프리앰페시스를 행하는지의 여부를 나타내는 신호(EA, EB, EC)를 생성한다.

[0065] 도 8은, LUT(19)의 한 예를 도시하는 것이고, 현재의 심볼(CS)과, 신호(TxF, TxR, TxP)와, 신호(EA, EB, EC)와의 관계를 나타내고 있다. 또한, 이 도 8에서는, 설명의 편의상, 다음의 심볼(NS)도 나타내고 있다.

[0066] 신호 생성부(11)는, 현재의 심볼(CS) 및 신호(TxF, TxR, TxP)에 의거하여, 이 LUT(19)를 참조하여, 신호(EA, EB, EC)를 생성한다. 그리고, 플립플롭(14, 15)은, 이 신호(EA, EB, EC)를 지연시켜서 신호(EA2, EB2, EC2)를 생성하고, 송신부(20)는, 이 신호(EA2, EB2, EC2)에 의거하여, 신호(SIGA, SIGB, SIGC)에 대해 프리앰페시스를 행한다. 이하에, 현재의 심볼(CS)이 "+x"인 경우와, "-x"인 경우를 예로, 상세히 설명한다.

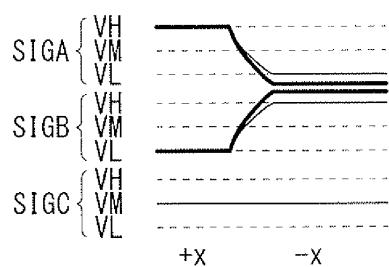

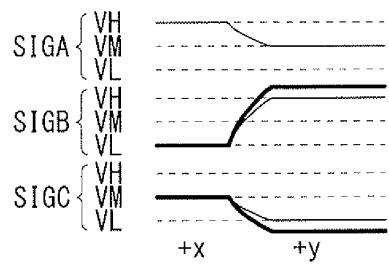

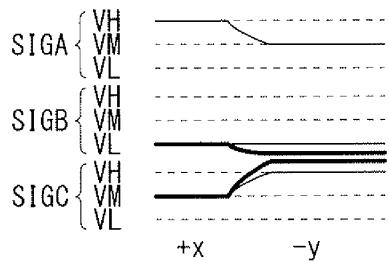

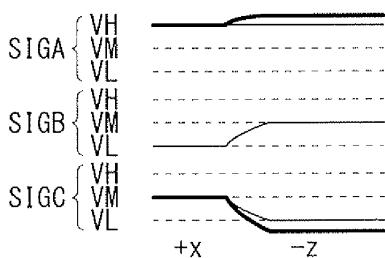

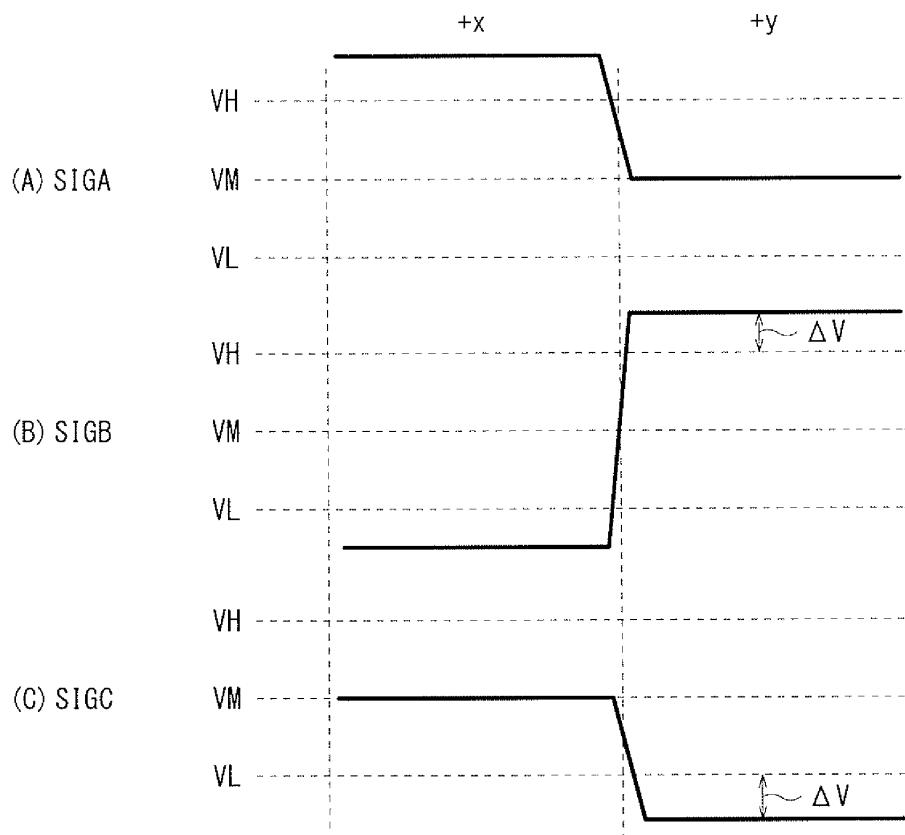

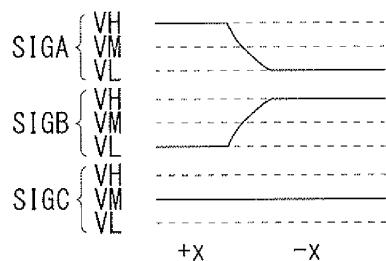

[0067] 도 9A~9E, 10A~10E는, 심볼이 "+x"로부터 "+x" 이외로 천이하는 경우의 동작을 도시하는 것이고, 도 9A~9E는, 신호(SIGA, SIGB, SIGC)의 파형을 도시하고, 도 10A~10E는, 차분(AB, BC, CA)의 파형을 도시한다. 도 9A, 10A는 "+x"로부터 "-x"로의 천이를 도시하고, 도 9B, 10B는 "+x"로부터 "+y"로의 천이를 도시하고, 도 9C, 10C는 "+x"로부터 "-y"로의 천이를 도시하고, 도 9D, 10D는 "+x"로부터 "+z"로의 천이를 도시하고, 도 9E, 10E는 "+x"로부터 "-z"로의 천이를 도시한다. 또한, 도 9A~9E, 10A~10E에서, 세선은 프리앰페시스를 행하지 않은 경우를 나타내고, 태선은 프리앰페시스를 행한 경우를 나타낸다. 이 예에서는, 전송로(9A~9C)의 길이는 충분히 단축하고 있다.

[0068] 심볼이 "+x"로부터 "-x"로 천이하는 경우에는, 신호 생성부(11)는, 도 8에 도시한 바와 같이, 신호(EA, EB, EC)를 "1", "1", "0"으로 한다. 이에 의해, 송신부(20)는, 도 9A에 도시한 바와 같이, 신호(SIGA)에 대해 프리앰페시스를 행하여, 고레벨 전압(VH)으로부터, 저레벨 전압(VL)보다도 낮은 전압으로 천이시킴과 함께, 신호(SIGB)에 대해 프리앰페시스를 행하여, 저레벨 전압(VL)으로부터, 고레벨 전압(VH)보다도 높은 전압으로 천이시킨다. 이 때, 송신부(20)는, 신호(SIGC)에 대해서는, 프리앰페시스를 행하지 않고, 중레벨 전압(VM)을 유지시킨다. 이에 의해, 도 10A에 도시한 바와 같이, 차분(AB)은, 프리앰페시스를 행하지 않은 경우에 비하여, 정의 전압으로부터 부의 전압으로 보다 빨리 천이하고, 차분(BC, CA)은, 프리앰페시스를 행하지 않은 경우에 비하여, 부로부터 정으로 보다 빨리 천이한다.

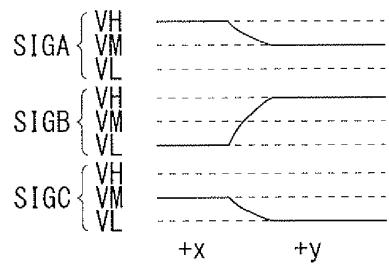

[0069] 심볼이 "+x"로부터 "+y"로 천이하는 경우에는, 신호 생성부(11)는, 도 8에 도시한 바와 같이, 신호(EA, EB, EC)를 "0", "1", "1"로 한다. 이에 의해, 송신부(20)는, 도 9B에 도시한 바와 같이, 신호(SIGB)에 대해 프리앰페시스를 행하여, 저레벨 전압(VL)으로부터, 고레벨 전압(VH)보다도 높은 전압으로 천이시킴과 함께, 신호(SIGC)에 대해 프리앰페시스를 행하여, 고레벨 전압(VH)으로부터, 저레벨 전압(VL)보다도 낮은 전압으로 천이시킨다. 이 때, 송신부(20)는, 신호(SIGA)에 대해서는 프리앰페시스를 행하지 않고, 고레벨 전압(VH)으로부터 중레벨 전압(VM)으로 천이시킨다. 즉, 신호(SIGA)는 전압 상태(SH)로부터 전압 상태(SM)로 천이하지만, 송신부(20)는, 이 신호(SIGA)에 대해서는 프리앰페시스를 행하지 않는다. 이에 의해, 도 10B에 도시한 바와 같이, 차분(AB)은, 프리앰페시스를 행하지 않은 경우에 비하여, 정으로부터 부로 보다 빨리 천이하고, 차분(BC)은, 프리앰페시스를 행하지 않은 경우에 비하여, 부로부터 정으로 보다 빨리 천이한다. 또한, 차분(CA)은 부의 상태를 유지한다.

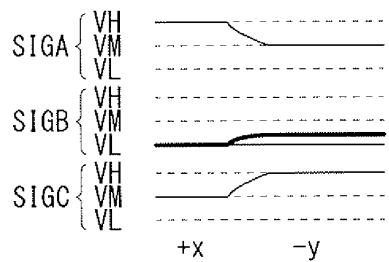

[0070] 심볼이 "+x"로부터 "-y"로 천이하는 경우에는, 신호 생성부(11)는, 도 8에 도시한 바와 같이, 신호(EA, EB, EC)를 "0", "1", "1"로 한다. 이에 의해, 송신부(20)는, 도 9C에 도시한 바와 같이, 신호(SIGB)에 대해 프리앰페시스를 행하여, 저레벨 전압(VL)으로부터, 저레벨 전압(VL)보다도 낮은 전압으로 천이시킴과 함께, 신호(SIGC)에 대해 프리앰페시스를 행하여, 중레벨 전압(VM)으로부터, 고레벨 전압(VH)보다도 높은 전압으로 천이시킨다. 즉, 신호(SIGB)는 전압 상태(SL)를 유지하지만, 송신부(20)는, 이 신호(SIGA)에 대해 프리앰페시스를 행한다. 이 때, 송신부(20)는, 신호(SIGA)에 대해서는, 프리앰페시스를 행하지 않고, 고레벨 전압(VH)으로부터 중레벨 전압(VM)으로 천이시킨다. 즉, 신호(SIGA)는 전압 상태(SH)로부터 전압 상태(SM)로 천이하지만, 송신부(20)는, 이 신호(SIGA)에 대해서는 프리앰페시스를 행하지 않는다. 이에 의해, 도 10C에 도시한 바와 같이, 차분(CA)은, 프리앰페시스를 행하지 않은 경우에 비하여, 부압으로부터 정압으로 보다 빨리 천이한다. 또한, 차분(AB)은 정의 상태를 유지하고, 차분(BC)은 부의 상태를 유지한다.

[0071] 심볼이 "+x"로부터 "+z"로 천이하는 경우에는, 신호 생성부(11)는, 도 8에 도시한 바와 같이, 신호(EA, EB, EC)를 "1", "0", "1"로 한다. 이에 의해, 송신부(20)는, 도 9D에 도시한 바와 같이, 신호(SIGA)에 대해 프리앰페

시스를 행하여, 고레벨 전압(VH)으로부터, 저레벨 전압(VL)보다도 낮은 전압으로 천이시킴과 함께, 신호(SIGC)에 대해 프리엠퍼시스를 행하여, 중레벨 전압(VM)으로부터, 고레벨 전압(VH)보다도 높은 전압으로 천이시킨다. 이 때, 송신부(20)는, 신호(SIGB)에 대해서는 프리엠퍼시스를 행하지 않고, 저레벨 전압(VL)으로부터 중레벨 전압(VM)으로 천이시킨다. 즉, 신호(SIGB)는 전압 상태(SL)로부터 전압 상태(SM)로 천이하지만, 송신부(20)는, 이 신호(SIGB)에 대해서는 프리엠퍼시스를 행하지 않는다. 이에 의해, 도 10D에 도시한 바와 같이, 차분(AB)은, 프리엠퍼시스를 행하지 않은 경우에 비하여, 정으로부터 부로 보다 빨리 천이하고, 차분(CA)은, 프리엠퍼시스를 행하지 않은 경우에 비하여, 부로부터 정으로 보다 빨리 천이한다. 또한, 차분(BC)은 부의 상태를 유지한다.

[0072] 심볼이 "+x"로부터 "-z"로 천이하는 경우에는, 신호 생성부(11)는, 도 8에 도시한 바와 같이, 신호(EA, EB, EC)를 "1", "0", "1"로 한다. 이에 의해, 송신부(20)는, 도 9E에 도시한 바와 같이, 신호(SIGA)에 대해 프리엠퍼시스를 행하여, 고레벨 전압(VH)으로부터, 고레벨 전압(VH)보다도 낮은 전압으로 천이시킴과 함께, 신호(SIGC)에 대해 프리惫퍼시스를 행하여, 중레벨 전압(VM)으로부터, 저레벨 전압(VL)보다도 낮은 전압으로 천이시킨다. 즉, 신호(SIGA)는 전압 상태(SH)를 유지하지만, 송신부(20)는, 이 신호(SIGA)에 대해 프리惫퍼시스를 행한다. 이 때, 송신부(20)는, 신호(SIGB)에 대해서는 프리惫퍼시스를 행하지 않고, 저레벨 전압(VL)으로부터 중레벨 전압(VM)으로 천이시킨다. 즉, 신호(SIGB)는 전압 상태(SL)로부터 전압 상태(SM)로 천이하지만, 송신부(20)는, 이 신호(SIGB)에 대해서는 프리惫퍼시스를 행하지 않는다. 이에 의해, 도 10E에 도시한 바와 같이, 차분(BC)은, 프리惫퍼시스를 행하지 않은 경우에 비하여, 부로부터 정으로 보다 빨리 천이한다. 또한, 차분(AB)은 정의 상태를 유지하고, 차분(CA)은 부의 상태를 유지한다.

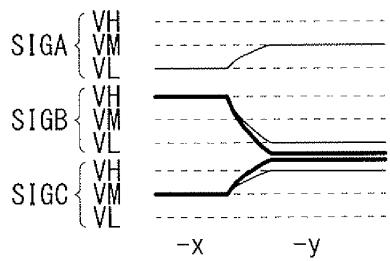

[0073] 도 11A~11E, 12A~12E는, 심볼이 "-x"로부터 "-x" 이외로 천이하는 경우의 동작을 도시하는 것이고, 도 11A~11E는, 신호(SIGA, SIGB, SIGC)의 과형을 도시하고, 도 12A~12E는, 차분(AB, BC, CA)의 과형을 도시한다. 도 11A, 12A는 "-x"로부터 "+x"로의 천이를 도시하고, 도 11B, 12B는 "-x"로부터 "+y"로의 천이를 도시하고, 도 11C, 12C는 "-x"로부터 "-y"로의 천이를 도시하고, 도 11D, 12D는 "-x"로부터 "+z"로의 천이를 도시하고, 도 11E, 12E는 "-x"로부터 "-z"로의 천이를 나타낸다.

[0074] 심볼이 "-x"로부터 "+x"로 천이하는 경우에는, 신호 생성부(11)는, 도 8에 도시한 바와 같이, 신호(EA, EB, EC)를 "1", "1", "0"으로 한다. 이에 의해, 송신부(20)는, 도 11A에 도시한 바와 같이, 신호(SIGA)에 대해 프리惫퍼시스를 행하여, 저레벨 전압(VL)으로부터, 고레벨 전압(VH)보다도 높은 전압으로 천이시킴과 함께, 신호(SIGB)에 대해 프리惫퍼시스를 행하여, 고레벨 전압(VH)으로부터, 저레벨 전압(VL)보다도 낮은 전압으로 천이시킨다. 이 때, 송신부(20)는, 신호(SIGC)에 대해서는, 프리惫퍼시스를 행하지 않고, 중레벨 전압(VM)을 유지시킨다. 이에 의해, 도 12A에 도시한 바와 같이, 차분(AB)은, 프리惫퍼시스를 행하지 않은 경우에 비하여, 부로부터 정으로 보다 빨리 천이하고, 차분(BC, CA)은, 프리惫퍼시스를 행하지 않은 경우에 비하여, 정으로부터 부로 보다 빨리 천이한다.

[0075] 심볼이 "-x"로부터 "+y"로 천이하는 경우에는, 신호 생성부(11)는, 도 8에 도시한 바와 같이, 신호(EA, EB, EC)를 "0", "1", "1"로 한다. 이에 의해, 송신부(20)는, 도 11B에 도시한 바와 같이, 신호(SIGB)에 대해 프리惫퍼시스를 행하여, 고레벨 전압(VH)으로부터, 고레벨 전압(VH)보다도 낮은 전압으로 천이시킴과 함께, 신호(SIGC)에 대해 프리惫퍼시스를 행하여, 중레벨 전압(VM)으로부터, 저레벨 전압(VL)보다도 낮은 전압으로 천이시킨다. 즉, 신호(SIGB)는 전압 상태(SH)를 유지하지만, 송신부(20)는, 이 신호(SIGA)에 대해 프리惫퍼시스를 행한다. 이 때, 송신부(20)는, 신호(SIGA)에 대해서는, 프리惫퍼시스를 행하지 않고, 저레벨 전압(VL)으로부터 중레벨 전압(VM)으로 천이시킨다. 즉, 신호(SIGA)는 전압 상태(SL)로부터 전압 상태(SM)로 천이하지만, 송신부(20)는, 이 신호(SIGA)에 대해서는, 프리惫퍼시스를 행하지 않는다. 이에 의해, 도 12B에 도시한 바와 같이, 차분(CA)은, 프리惫퍼시스를 행하지 않은 경우에 비하여, 정으로부터 부로 보다 빨리 천이한다. 또한, 차분(BC)은 정의 상태를 유지하고, 차분(AB)은 부의 상태를 유지한다.

[0076] 심볼이 "-x"로부터 "-y"로 천이하는 경우에는, 신호 생성부(11)는, 도 8에 도시한 바와 같이, 신호(EA, EB, EC)를 "0", "1", "1"로 한다. 이에 의해, 송신부(20)는, 도 11C에 도시한 바와 같이, 신호(SIGB)에 대해 프리惫퍼시스를 행하여, 고레벨 전압(VH)으로부터, 저레벨 전압(VL)보다도 낮은 전압으로 천이시킴과 함께, 신호(SIGC)에 대해 프리惫퍼시스를 행하여, 중레벨 전압(VM)으로부터, 고레벨 전압(VH)보다도 높은 전압으로 천이시킨다. 이 때, 송신부(20)는, 신호(SIGA)에 대해서는, 프리惫퍼시스를 행하지 않고, 저레벨 전압(VL)으로부터 중레벨 전압(VM)으로 천이시킨다. 즉, 신호(SIGA)는 전압 상태(SL)로부터 전압 상태(SM)로 천이하지만, 송신부(20)는, 이 신호(SIGA)에 대해서는, 프리惫퍼시스를 행하지 않는다. 이에 의해, 도 12C에 도시한 바와 같이, 차분(AB)은, 프리惫퍼시스를 행하지 않은 경우에 비하여, 부로부터 정으로 보다 빨리 천이하고, 차분(BC)은, 프리惫퍼시스를 행하지 않은 경우에 비하여, 정으로부터 부로 보다 빨리 천이한다. 또한, 차분(CA)은 정의 상태를

유지한다.

[0077] 심볼이 "-x"로부터 "+z"로 천이하는 경우에는, 신호 생성부(11)는, 도 8에 도시한 바와 같이, 신호(EA, EB, EC)를 "1", "0", "1"로 한다. 이에 의해, 송신부(20)는, 도 11D에 도시한 바와 같이, 신호(SIGA)에 대해 프리엠퍼시스를 행하여, 저레벨 전압(VL)으로부터, 저레벨 전압(VL)보다도 낮은 전압으로 천이시킴과 함께, 신호(SIGC)에 대해 프리엠퍼시스를 행하여, 중레벨 전압(VM)으로부터, 고레벨 전압(VH)보다도 높은 전압으로 천이시킨다. 즉, 신호(SIGA)는 전압 상태(SL)를 유지하지만, 송신부(20)는, 이 신호(SIGA)에 대해 프리엠퍼시스를 행한다. 이 때, 송신부(20)는, 신호(SIGB)에 대해서는 프리엠퍼시스를 행하지 않고, 고레벨 전압(VH)으로부터 중레벨 전압(VM)으로 천이시킨다. 즉, 신호(SIGB)는 전압 상태(SH)로부터 전압 상태(SM)로 천이하지만, 송신부(20)는, 이 신호(SIGB)에 대해서는 프리惫퍼시스를 행하지 않는다. 이에 의해, 도 12D에 도시한 바와 같이, 차분(BC)은, 프리惫퍼시스를 행하지 않은 경우에 비하여, 정으로부터 부로 보다 빨리 천이한다. 또한, 차분(AB)은 부의 상태를 유지하고, 차분(CA)은 정의 상태를 유지한다.

[0078] 심볼이 "-x"로부터 "-z"로 천이하는 경우에는, 신호 생성부(11)는, 도 8에 도시한 바와 같이, 신호(EA, EB, EC)를 "1", "0", "1"로 한다. 이에 의해, 송신부(20)는, 도 11E에 도시한 바와 같이, 신호(SIGA)에 대해 프리惫퍼시스를 행하여, 저레벨 전압(VL)으로부터, 고레벨 전압(VH)보다도 높은 전압으로 천이시킴과 함께, 신호(SIGC)에 대해 프리惫퍼시스를 행하여, 중레벨 전압(VM)으로부터, 저레벨 전압(VL)보다도 낮은 전압으로 천이시킨다. 이 때, 송신부(20)는, 신호(SIGB)에 대해서는 프리惫퍼시스를 행하지 않고, 고레벨 전압(VH)으로부터 중레벨 전압(VM)으로 천이시킨다. 즉, 신호(SIGB)는 전압 상태(SH)로부터 전압 상태(SM)로 천이하지만, 송신부(20)는, 이 신호(SIGB)에 대해서는 프리惫퍼시스를 행하지 않는다. 이에 의해, 도 12E에 도시한 바와 같이, 차분(AB)은, 프리惫퍼시스를 행하지 않은 경우에 비하여, 부로부터 정으로 보다 빨리 천이하고, 차분(CA)은, 프리惫퍼시스를 행하지 않은 경우에 비하여, 정으로부터 부로 보다 빨리 천이한다. 또한, 차분(BC)은 정의 상태를 유지한다.

[0079] 이와 같이, 송신 장치(10)는, 신호(SIGA~SIGC) 중, 전압 상태(SL, SM)로부터 전압 상태(SH)로 천이하는 신호에 대해 프리惫퍼시스를 행함과 함께, 전압 상태(SH, SM)로부터 전압 상태(SL)로 천이한 신호에 대해 프리惫퍼시스를 행한다. 또한, 송신 장치(10)는, 신호(SIGA~SIGC) 중, 전압 상태(SL, SH)를 유지하는 신호에 대해서도 프리惫퍼시스를 행한다. 한편, 송신 장치(10)는, 신호(SIGA~SIGC) 중, 전압 상태(SL, SH)로부터 전압 정보(SM)로 천이하는 신호에 대해서는 프리惫퍼시스를 행하지 않고, 또한, 전압 상태(SM)를 유지하는 신호에 대해서도 프리惫퍼시스를 행하지 않는다.

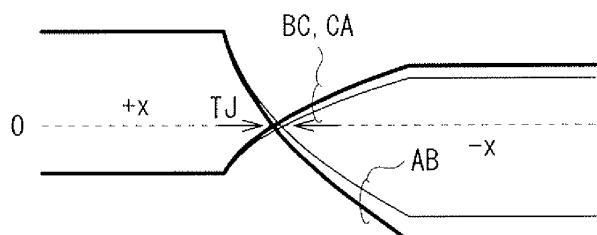

[0080] 앰플리파이어(32A~32C)는, 차분(AB, BC, CA)이 정인지 부인지에 응하여 신호를 생성하여 출력하다. 따라서, 이 통신 시스템(1)에서는, 지터(TJ)는, 도 10A~10E 및 도 12A~12E에 도시한 바와 같이, 차분(AB, BC, CA)이 "0"을 넘는 타이밍의 어긋남 폭으로 정의된다. 통신 시스템(1)에서는, 신호(SIGA~SIGC)에 대해 프리惫퍼시스를 행하도록 하였기 때문에, 신호의 천이가 가파르게 되기 때문에, 지터(TJ)를 작게 할 수 있다. 특히, 심볼"+x"로부터 "+y"로 천이하는 경우(도 10B)나, 심볼"+x"로부터 "+z"로 천이하는 경우(도 10D) 등, 차분(AB, BC, CA) 중의 2개가 "0"을 넘는 케이스에서는, 지터(TJ)를 효과적으로 개선할 수 있다.

[0081] 다음에, 심볼의 천이 중의 몇가지를 예로 들어, 보다 상세히 설명한다.

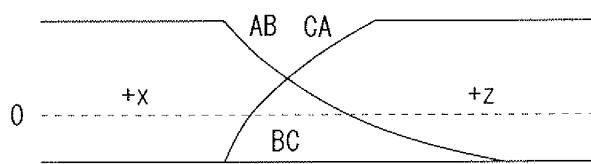

[0082] 우선, 심볼이 "+x"로부터 "+y"로 천이하는 경우에 관해 설명한다. 이 경우에는, 도 9B에 도시한 바와 같이, 신호(SIGA)가 전압 상태(SH)(예를 들면 고레벨 전압(VH))로부터 전압 상태(SM)(예를 들면 중레벨 전압(VM))로 천이하고, 신호(SIGB)가 전압 상태(SL)(예를 들면 저레벨 전압(VL))로부터 전압 상태(SH)로 천이하고, 신호(SIGC)가 전압 상태(SM)로부터 전압 상태(SL)로 천이한다. 이 경우에는, 도 10B에 도시한 바와 같이, 예를 들면, 차분(AB)의 천이 시간이 길어진다. 그 제1의 원인은, 신호(SIGA)가 중레벨 전압(VM)으로 천이하는 것이다. 즉, 신호(SIGA)를 중레벨 전압(VM)에 할 때, 송신부(20)의 출력부(22A)는, 트랜ジ스터(25, 26)의 양방을 오프 상태로 한다. 즉, 수신 장치(30)의 저항 소자(31A~31C)에 의해, 신호(SIGA)가 전압 상태(SM)로 설정된다. 그 결과, 신호(SIGA)의 천이 시간이 길어지고, 차분(AB)의 천이 시간도 또한 길어진다. 또한, 제2의 원인은, 차분(AB)의 전압 변화량이 큰 것이다.

[0083] 이와 같은 케이스는, 예를 들면, 심볼이 "+x"로부터 "+z"로 천이하는 경우(도 9D, 10D)에도 생긴다. 이 경우에는, 도 9D에 도시한 바와 같이, 신호(SIGA)가 전압 상태(SH)(예를 들면 고레벨 전압(VH))로부터 전압 상태(SL)(예를 들면 저레벨 전압(VL))로 천이하고, 신호(SIGB)가 전압 상태(SL)로부터 전압 상태(SM)(예를 들면 중레벨 전압(VM))로 천이하고, 신호(SIGC)가 전압 상태(SM)로부터 전압 상태(SH)로 천이한다. 그 밖, 심볼이 "-x"로부터 "-y"로 천이하는 경우(도 11C, 12C)나, 심볼이 "-x"로부터 "-z"로 천이하는 경우(도 11E, 12E) 등에서도 생

긴다.

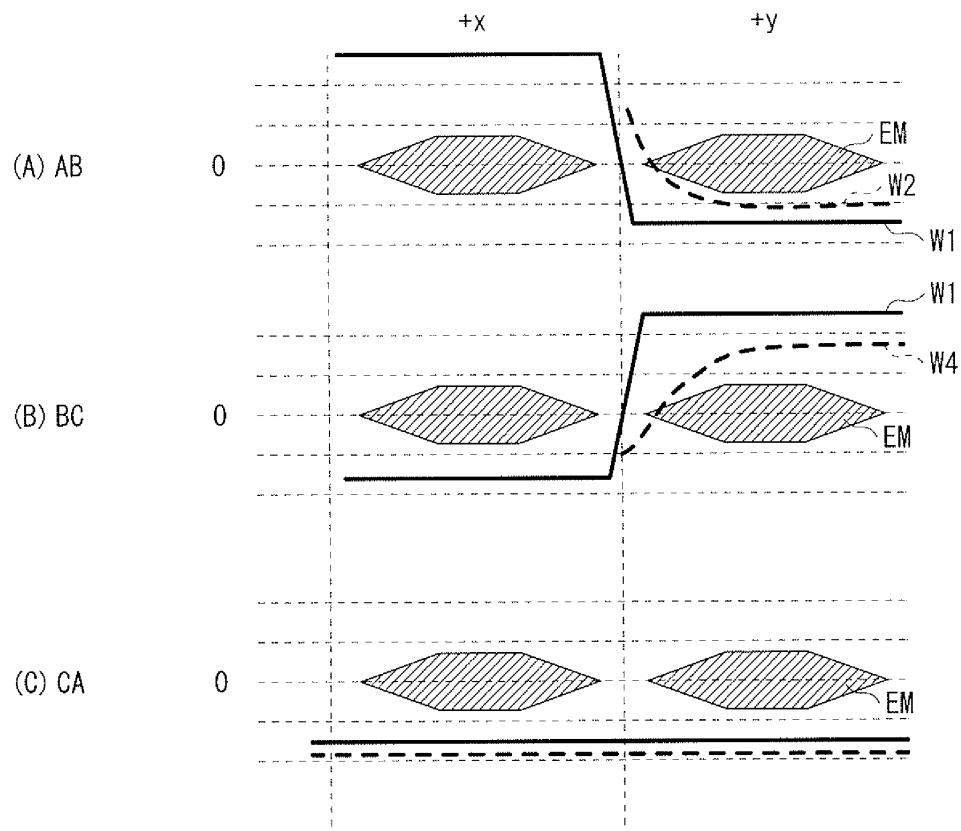

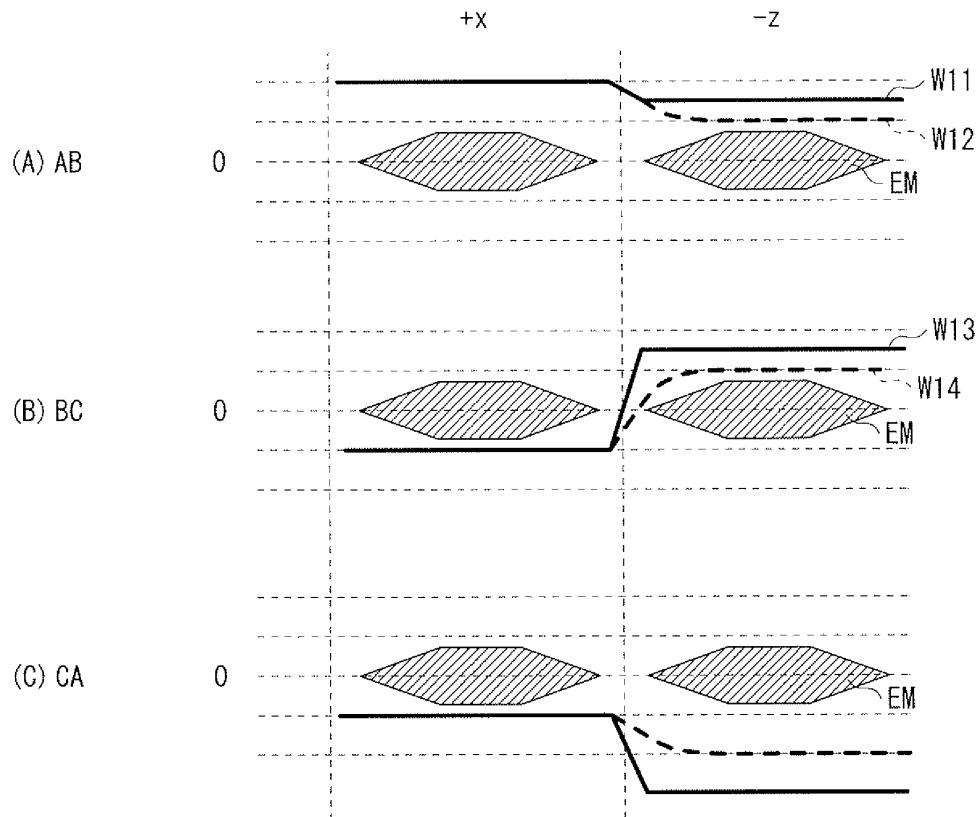

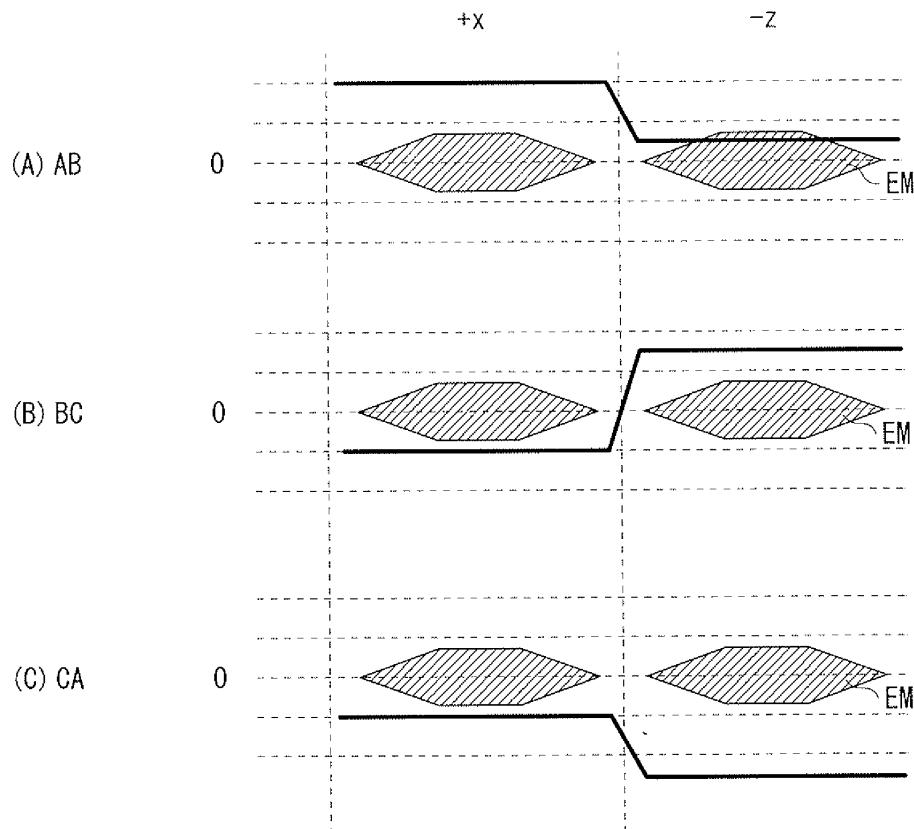

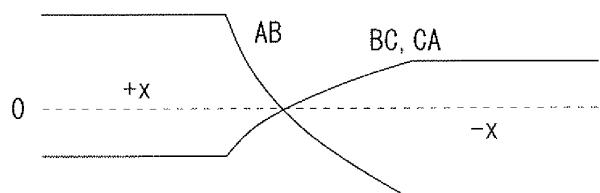

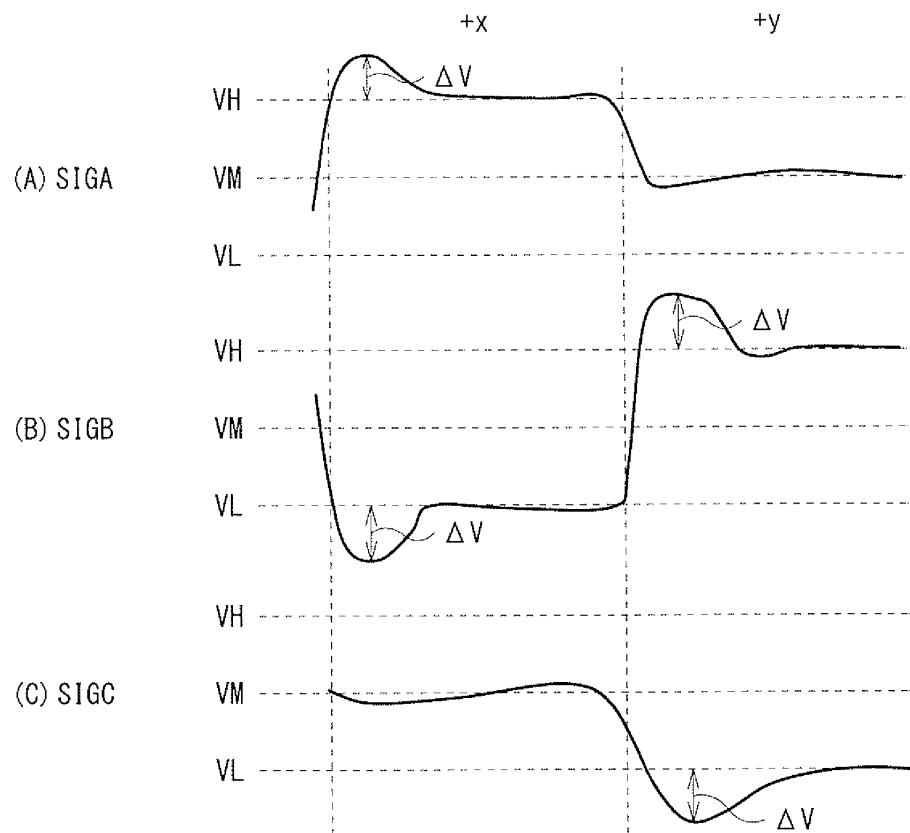

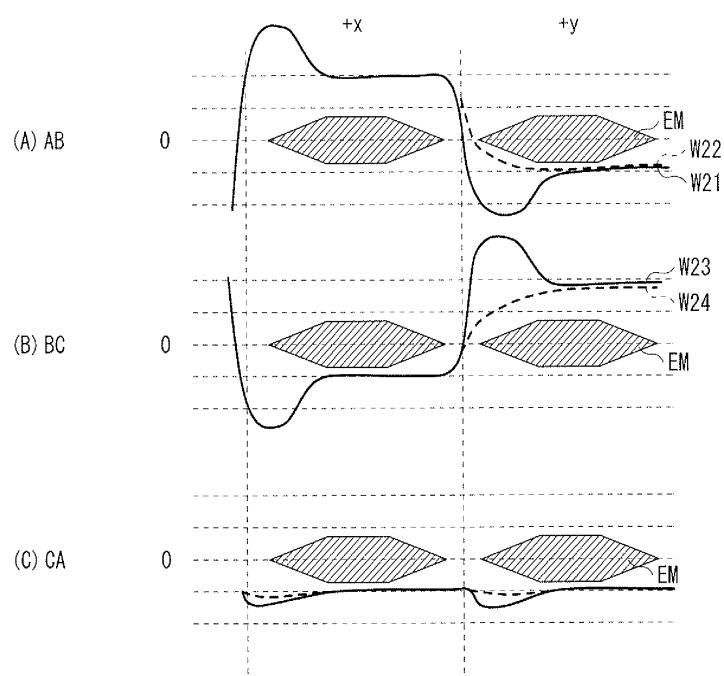

[0084] 도 13, 14는, 심볼이 "+x"로부터 "+y"로 천이하는 경우의 동작을 도시하는 것이고, 도 13(A)~(C)는, 신호(SIGA, SIGB, SIGC)의 과형을 각각 도시하고, 도 14(A)~(C)는, 차분(AB, BC, CA)의 과형을 각각 도시한다. 도 13은, 도 9B에 대응하고 있고, 도 14는, 도 10B에 대응하고 있다. 도 14에는, 아이 개구의 기준을 나타내는 아이 마스크(EM)를 아울러서 나타내고 있다.

[0085] 심볼이 "+x"로부터 "+y"로 천이할 때, 송신부(20)는, 도 13에 도시한 바와 같이, 신호(SIGB)의 천이를 전압( $\Delta V$ )만큼 엠피스함과 함께, 신호(SIGC)의 천이를 전압( $\Delta V$ )만큼 엠피스한다. 이 때, 차분(AB)은, 도 14의 과형(W1)과 같이 되고, 차분(BC)은, 도 14의 과형(W3)과 같이 된다. 이와 같이, 통신 시스템(1)에서는, 프리엠피스를 행하여, 과형의 천이를 가파르게 함에 의해, 아이를 넓게 할 수 있다. 가령, 신호(SIGA~SIGC)에 대해 프리엠피스를 행하지 않은 경우에는, 예를 들면, 차분(AB)은, 도 14의 과형(W2)과 같이 되고, 차분(BC)은, 도 14의 과형(W4)과 같이 된다. 즉, 이와 같은 경우에는, 과형의 천이가 무디어짐과 함께 차분의 진폭이 작아지기 때문에, 아이가 좁아질 우려가 있다. 한편, 통신 시스템(1)에서는, 신호(SIGA~SIGC)에 대해 프리엠피스를 행하도록 하였기 때문에, 아이를 넓게 할 수 있고, 통신 품질을 높일 수 있다.

[0086] 다음에, 심볼이 "+x"로부터 "-z"로 천이하는 경우에 관해 설명한다.

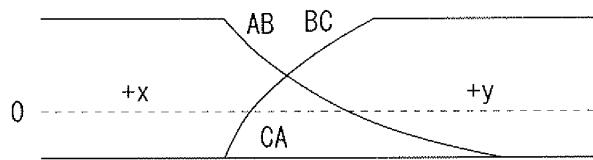

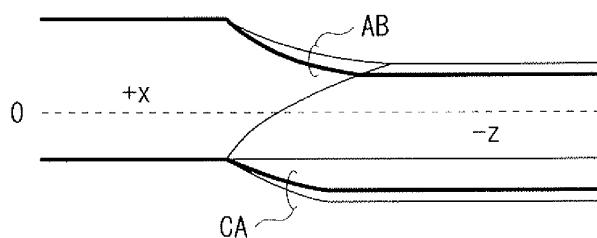

[0087] 도 15, 16은, 심볼이 "+x"로부터 "-z"로 천이하는 경우의 동작을 도시하는 것이고, 도 15(A)~(C)는, 신호(SIGA, SIGB, SIGC)의 과형을 각각 도시하고, 도 16(A)~(C)는, 차분(AB, BC, CA)의 과형을 각각 도시한다. 도 15는, 도 9E에 대응하고 있고, 도 16은, 도 10E에 대응하고 있다.

[0088] 심볼이 "+x"로부터 "-z"로 천이할 때, 송신부(20)는, 도 15에 도시한 바와 같이, 신호(SIGA)의 전압을 전압( $\Delta V$ )만큼 높은 전압으로 설정함과 함께, 신호(SIGC)의 천이를 전압( $\Delta V$ )만큼 엠피스한다. 즉, 송신부(20)는, 신호(SIGA)가 전압 상태(SH)를 유지함에도 불구하고, 신호(SIGA)에 대해 프리엠피스를 행하고, 또한, 신호(SIGB)가 전압 상태(SL)로부터 전압 상태(SM)로 천이함에도 불구하고, 신호(SIGB)에 대해 프리엠피스를 행하지 않는다. 환언하면, 송신 장치(10)는, 신호(SIGA, SIGC)를 선택하고, 이들에 대해 프리엠피스를 행한다. 이 때, 차분(AB)은, 도 16의 과형(W11)과 같이 되고, 차분(BC)은, 도 16의 과형(W13)과 같이 된다. 이와 같이, 통신 시스템(1)에서는, 프리엠피스를 행하여, 과형의 천이를 가파르게 함에 의해, 아이를 넓게 할 수 있다. 가령, 신호(SIGA~SIGC)에 대해 프리엠피스를 행하지 않은 경우에는, 예를 들면, 차분(AB)은, 도 16의 과형(W12)과 같이 되고, 차분(BC)은, 도 16의 과형(W14)과 같이 된다. 즉, 이와 같은 경우에는, 과형의 천이가 무디어짐과 함께 차분의 진폭이 작아지기 때문에, 아이가 좁아질 우려가 있다. 한편, 통신 시스템(1)에서는, 신호(SIGA~SIGC)에 대해 프리엠피스를 행하도록 하였기 때문에, 아이를 넓게 할 수 있고, 통신 품질을 높일 수 있다.

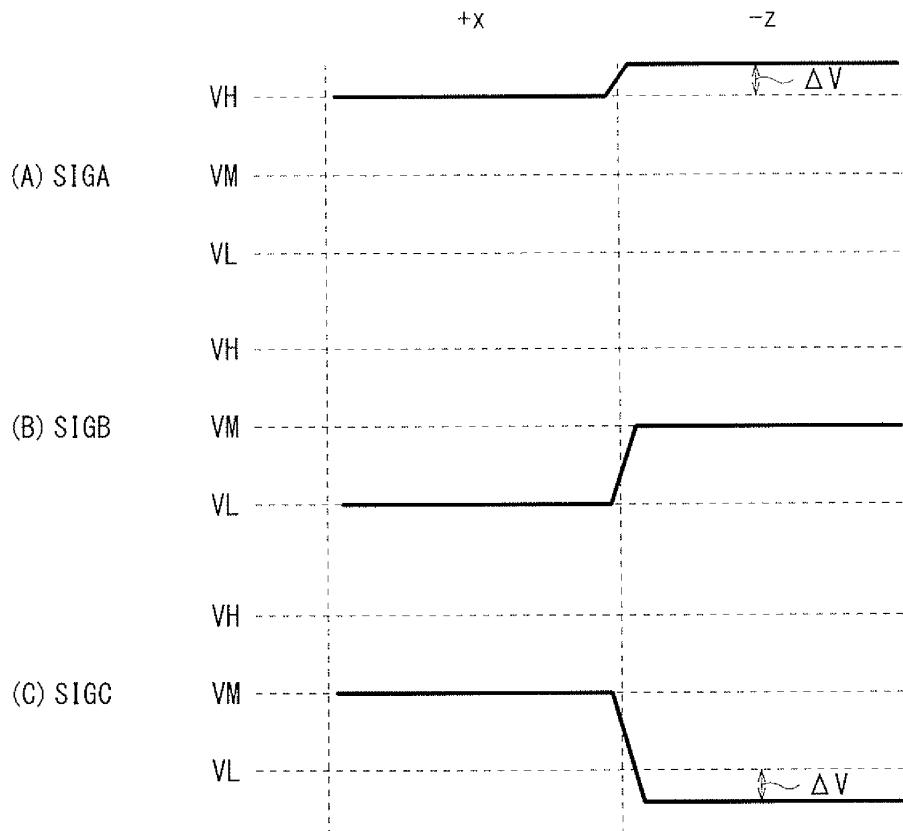

#### 비교례

[0089] 여기서, 비교례로서, 신호(SIGA~SIGC) 중, 전압 상태가 천이하는 것에 대해 프리엠피스를 행하고, 전압 상태가 천이하지 않는 것에 대해서는 프리엠피스를 행하지 않은 경우에 관해 검토한다.

[0090] 도 17, 18은, 심볼이 "+x"로부터 "-z"로 천이하는 경우의 동작을 도시하는 것이고, 도 17(A)~(C)는, 신호(SIGA, SIGB, SIGC)의 과형을 각각 도시하고, 도 18(A)~(C)는, 차분(AB, BC, CA)의 과형을 각각 도시한다.

[0091] 심볼이 "+x"로부터 "-z"로 천이할 때, 비교례에 관한 송신 장치(10R)는, 도 17에 도시한 바와 같이, 신호(SIGB)의 천이를 전압( $\Delta V$ )만큼 강조함과 함께, 신호(SIGC)의 천이를 전압( $\Delta V$ )만큼 강조한다. 즉, 전압 상태가 천이하는 신호(SIGB, SIGC)에 대해 프리엠피스를 행하고, 전압 상태가 변화하지 않는 신호(SIGA)에 대해서는 프리엠피스를 행하지 않는다. 이 때, 차분(AB)은, 도 18(A)와 같이 되고, 아이가 좁아질 우려가 있다.

[0092] 한편, 통신 시스템(1)에서는, 신호(SIGA~SIGC) 중, 프리엠피스를 행하는 신호를 선택하도록 하였다. 구체적으로는, 본 실시의 형태에 관한 송신 장치(10)는, 도 15에 도시한 바와 같이, 신호(SIGA)의 전압을 전압( $\Delta V$ )만큼 높은 전압으로 설정함과 함께, 신호(SIGC)의 천이를 전압( $\Delta V$ )만큼 엠피스하였다. 즉, 송신 장치(10)는, 신호(SIGA)가 전압 상태(SH)를 유지함에도 불구하고, 신호(SIGA)에 대해 프리엠피스를 행하고, 또한, 신호(SIGB)가 전압 상태(SL)로부터 전압 상태(SM)로 천이함에도 불구하고, 신호(SIGB)에 대해 프리엠피스를 행하지 않도록 하였다. 이에 의해, 통신 시스템(1)에서는, 아이가 좁아질 우려를 저감할 수 있고, 통신 품질을 높일 수 있다.

[0093] 이와 같이, 통신 시스템(1)에서는, 신호(SIGA~SIGC)에 대해 선택적으로 프리엠피스를 행하도록 하였기 때문

예, 예를 들면, 지터가 큰 천이인 경우에는 프리앰프시스를 행하고, 프리앰프시스를 행하 아이가 좁아질 것 같은 천이인 경우에는 프리앰프시스를 행하지 않도록 할 수 있다. 이에 의해, 통신 시스템(1)에서는, 통신 품질을 높일 수 있다.

#### [0095] 효과

[0096] 이상과 같이 본 실시의 형태에서는, 신호(SIGA~SIGC)에 대해 선택적으로 프리앰프시스를 행하도록 하였기 때문에, 통신 품질을 높일 수 있다.

#### [0097] 변형례 1-1

[0098] 상기 실시의 형태에서는, 도 8에 도시한 바와 같이, 6개의 심볼 사이의 어느 천이라도, 신호(SIGA, SIGB, SIGC) 중의 적어도 하나에 대해 프리앰프시스를 행하도록 하였지만, 이것으로 한정되는 것이 아니다. 이에 대신하여, 예를 들면, 6개의 심볼 사이의 천이 중의 일부에 관해서만 프리앰프시스를 행하도록 하여도 좋다. 이하에, 본 변형례에 관한 통신 시스템(1A)에 관해 상세히 설명한다.

[0099] 도 19는, 본 변형례에 관한 LUT(19A)의 한 예를 도시하는 것이다. 본 변형례에 관한 신호 생성부(11A)는, 이 LUT(19A)에 의거하여 신호(EA, EB, EC)를 생성한다. 신호 생성부(11A)는, 예를 들면, 심볼이 "+x"로부터 "-x"로 천이하는 경우, 심볼이 "+x"로부터 "-y"로 천이하는 경우, 및 심볼이 "+x"로부터 "-z"로 천이하는 경우에 는, 신호(EA, EB, EC)의 전부를 "0"으로 한다. 즉, 이들의 경우에는, 송신부(20)는, 신호(SIGA, SIGB, SIGC)의 어느 것에 대해서도 프리앰프시스를 행하지 않는다. 예를 들면, 심볼이 "+x"로부터 "-z"로 천이하는 경우에 있어서, 예를 들면 도 17, 18과 같이 프리앰프시스를 행하면, 아이가 좁아져 버리기 때문에, 본 변형례에서는, 이와 같은 경우에는 프리앰프시스를 행하지 않는다. 한편, 신호 생성부(11A)는, 예를 들면, 심볼이 "+x"로부터 "+y"로 천이하는 경우에는, 신호(EA, EB, EC)를 "0", "1", "1"로 하고 및 심볼이 "+x"로부터 "+z"로 천이하는 경우에는, 신호(EA, EB, EC)를 "1", "0", "1"로 한다. 즉, 이들의 경우에는, 도 10B, 10D에 도시한 바와 같이, 차분(AB)의 천이 시간이 길어지기 때문에, 송신부(20)는, 프리앰프시스를 행한다. 이와 같이 프리앰프시스를 행하는 케이스는 2종류 있다. 즉, 하나는, 신호(SIGA, SIGB, SIGC) 중의, 제1의 신호가 전압 상태(SH)(예를 들면 고레벨 전압(VH))로부터 전압 상태(SM)(예를 들면 중레벨 전압(VM))로 천이하고, 제2의 신호가 전압 상태(SL)(예를 들면 저레벨 전압(VL))로부터 전압 상태(SH)로 천이하고, 제3의 신호가 전압 상태(SM)로부터 전압 상태(SL)로 천이하는 케이스이다. 그리고, 또 하나는, 신호(SIGA, SIGB, SIGC) 중의, 제1의 신호가 전압 상태(SL)로부터 전압 상태(SM)로 천이하고, 제2의 신호가 전압 상태(SH)로부터 전압 상태(SL)로 천이하고, 제3의 신호가 전압 상태(SM)로부터 전압 상태(SH)로 천이하는 케이스이다. 환연하면, 신호(SIGA)의 전압 상태, 신호(SIGB)의 전압 상태, 및 신호(SIGC)의 전압 상태의 모두가 천이하는 케이스이다. 이와 같이, 통신 시스템(1A)에서는, 차분(AB, BC, CA)의 천이 시간 중의 어느 하나가 길어지는 경우에 한하여, 프리앰프시스를 행하고, 그 이외에서는 프리앰프시스를 행하지 않는다. 이와 같이 구성하여도, 상기 실시의 형태에 관한 통신 시스템(1)과 같은 효과를 얻을 수 있다.

[0100] 또한, 6개의 심볼 사이의 천이 중, 프리앰프시스를 행하는 천이는, 도 19의 예로 한정되는 것이 아니고, 어느 천이에 대해 프리앰프시스를 행하는지는 임의로 설정할 수 있다.

#### [0101] 변형례 1-2

[0102] 상기 실시의 형태에서는, 신호 생성부(11)는, 3개의 신호(EA, EB, EC)를 생성하고, 신호(SIGA~SIGC)에 대한 프리앰프시스를 각각 독립하여 제어하도록 하였지만, 이것으로 한정되는 것이 아니다. 이하에, 본 변형례에 관한 송신 장치(10B)에 관해 상세히 설명한다.

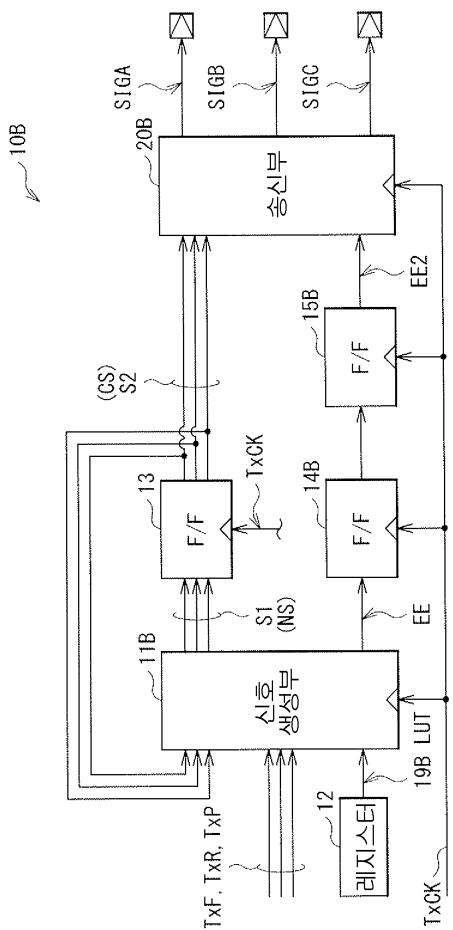

[0103] 도 20은, 송신 장치(10B)의 한 구성례를 도시하는 것이다. 송신 장치(10B)는, 신호 생성부(11B)와, 플립플롭(14B, 15B)과, 송신부(20B)를 갖고 있다. 신호 생성부(11B)는, 현재의 심볼(CS) 및 신호(TxF, TxR, TxP)에 의거하여, 다음의 심볼(NS)을 구함과 함께, LUT(19B)를 참조하여, 신호(EE)를 생성하는 것이다. 플립플롭(14B)은, 신호(EE)를, 클록(TxCK)의 1클록분 지연시켜, 출력하는 것이다. 플립플롭(15B)은, 플립플롭(14)의 출력 신호를, 클록(TxCK)의 1클록분 지연시켜, 신호(EE2)로서 출력하는 것이다. 송신부(20B)는, 신호(S2) 및 신호(EE2)에 의거하여, 신호(SIGA, SIGB, SIGC)를 생성하는 것이다. 그 때, 송신부(20B)는, 신호(EE2)가 액티브인 경우에는, 신호(SIGA, SIGB, SIGC)에 대해 프리앰프시스를 행하도록 되어 있다. 이 구성에 의해, 송신 장치(10B)에서는, 신호 생성부(11B)가, 신호(SIGA~SIGC)에 대한 프리앰프시스를 통합하여 제어하도록 되어 있다.

[0104] 도 21은, 본 변형례에 관한 LUT(19B)의 한 예를 도시하는 것이다. 신호 생성부(11B)는, 예를 들면, 심볼이 "+x"로부터 "-x"로 천이하는 경우, 심볼이 "+x"로부터 "-y"로 천이하는 경우, 및 심볼이 "+x"로부터 "-z"로 천이

하는 경우에는, 신호(EE)를 "0"으로 한다. 즉, 이들의 경우에는, 송신부(20B)는, 신호(SIGA, SIGB, SIGC)에 대해 프리앰프시스를 행하지 않는다. 한편, 신호 생성부(11B)는, 예를 들면, 심볼이 "+x"로부터 "+y"로 천이하는 경우, 및 심볼이 "+x"로부터 "+z"로 천이하는 경우에는, 신호(EE)를 "1"로 한다. 즉, 이들의 경우에는, 상기 변형례 1-1의 경우와 마찬가지로, 차분(AB)의 천이 시간이 길어지기 때문에, 송신부(20B)는, 신호(SIGA, SIGB, SIGC)에 대해 프리앰프시스를 행한다. 이와 같이, 통신 장치(10B)에서는, 차분(AB, BC, CA)의 천이 시간 중의 어느 하나가 길어지는 경우에 한하여, 프리앰프시스를 행하고, 그 이외에서는 프리앰프시스를 행하지 않도록 동작한다. 이와 같이 구성하여도, 상기 실시의 형태에 관한 통신 시스템(1)과 같은 효과를 얻을 수 있다.

[0105] 또한, 6개의 심볼 사이의 천이 중, 프리앰프시스를 행하는 천이는, 도 21의 예로 한정되는 것이 아니고, 어느 천이에 대해 프리앰프시스를 행하는지는 임의로 설정할 수 있다. 예를 들면, 차분(AB, BC, CA) 중의 어느 2개가 "0"을 넘어서 천이하는 경우에만 프리앰프시스를 행하도록 하여도 좋다. 또한, 예를 들면, 차분(AB, BC, CA)의 전부가 "0"을 넘어서 천이하는 경우에만 프리앰프시스를 행하도록 하여도 좋다.

[0106] 변형례 1-3

[0107] 신호 생성부(11)는, LUT(19)를 참조하여 신호(EA, EB, EC)를 생성하는 동작은, 소프트웨어에 의해 실현하여도 좋고, 하드웨어에 의해 실현하여도 좋다. 이하에, 하드웨어에 의해 실현하는 방법의 한 예를 나타낸다. 여기서는, 변형례 1-2에 관한 신호 생성부(11B)에 본 변형례를 적용한 예로 설명한다.

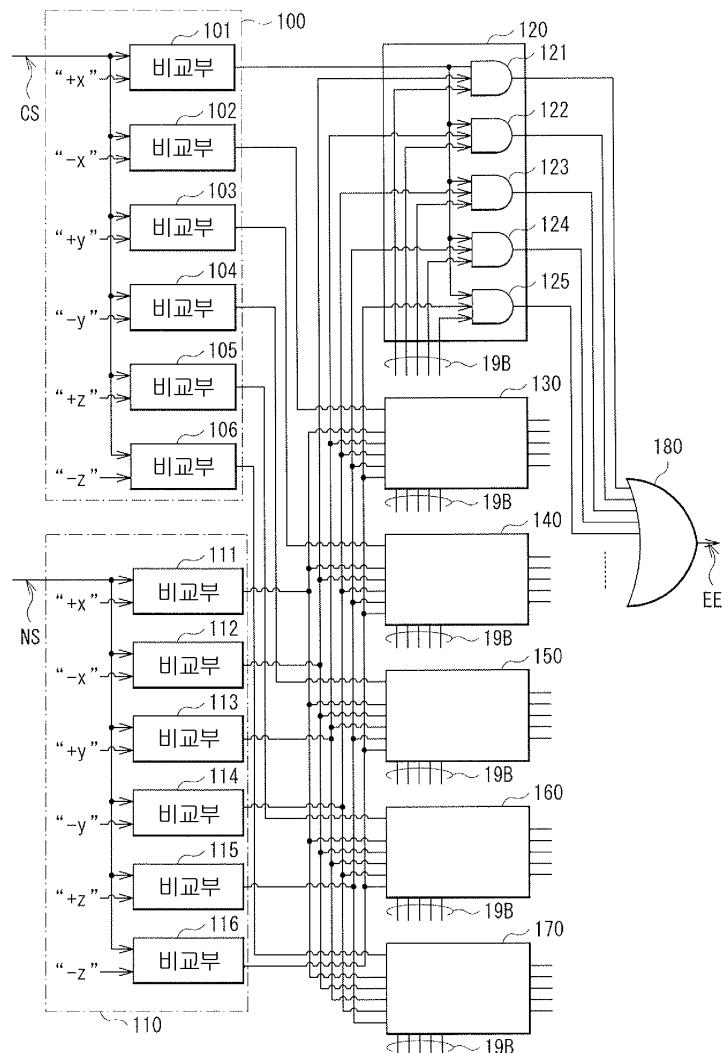

[0108] 도 22는, 본 변형례에 관한 신호 생성부(11C) 중, 신호(EE)를 생성하는 부분의 한 구성례를 도시하는 것이다. 이 예에서는, 신호 생성부(11C)는, 현재의 심볼(CS), 다음의 심볼(NS), 및 LUT(19B)에 의거하여, 신호(EE)를 생성하고 있다. 신호 생성부(11C)는, 심볼 판정부(100, 110)와, 논리 회로(120, 130, 140, 150, 160, 170)와, 논리합 회로(180)를 갖고 있다.

[0109] 심볼 판정부(100)는, 현재의 심볼(CS)이, 6개의 심볼"+x", "-x", "+y", "-y", "+z", "-z" 중의 어느 것인지를 판정하는 것이다. 심볼 판정부(100)는, 비교부(101~106)를 갖고 있다. 비교부(101)는, 현재의 심볼(CS)이 심볼"+x"인 경우에 "1"을 출력하는 것이다. 비교부(102)는, 현재의 심볼(CS)이 심볼"-x"인 경우에 "1"을 출력하는 것이다. 비교부(103)는, 현재의 심볼(CS)이 심볼"+y"인 경우에 "1"을 출력하는 것이다. 비교부(104)는, 현재의 심볼(CS)이 심볼"-y"인 경우에 "1"을 출력하는 것이다. 비교부(105)는, 현재의 심볼(CS)이 심볼"+z"인 경우에 "1"을 출력하는 것이다. 비교부(106)는, 현재의 심볼(CS)이 심볼"-z"인 경우에 "1"을 출력하는 것이다.

[0110] 심볼 판정부(110)는, 다음의 심볼(NS)이, 6개의 심볼"+x", "-x", "+y", "-y", "+z", "-z" 중의 어느 것인지를 판정하는 것이다. 심볼 판정부(110)는, 비교부(111~116)를 갖고 있다. 비교부(111)는, 다음의 심볼(NS)이 심볼"+x"인 경우에 "1"을 출력하는 것이다. 비교부(112)는, 다음의 심볼(NS)이 심볼"-x"인 경우에 "1"을 출력하는 것이다. 비교부(113)는, 다음의 심볼(NS)이 심볼"+y"인 경우에 "1"을 출력하는 것이다. 비교부(114)는, 다음의 심볼(NS)이 심볼"-y"인 경우에 "1"을 출력하는 것이다. 비교부(115)은, 다음의 심볼(NS)이 심볼"+z"인 경우에 "1"을 출력하는 것이다. 비교부(116)는, 다음의 심볼(NS)이 심볼"-z"인 경우에 "1"을 출력하는 것이다.

[0111] 논리 회로(120)는, 비교부(101)의 출력 신호, 비교부(112~116)의 출력 신호, 및 LUT(19B)에서의 프리앰프시스의 설정에 의거하여, 신호를 생성하는 것이다.

[0112] 논리곱 회로(120)는, 논리곱 회로(121~125)를 갖고 있다. 논리곱 회로(121)의 제1의 입력단자에는 비교부(101)의 출력 신호가 공급되고, 제2의 입력단자에는 비교부(112)의 출력 신호가 공급되고, 제3의 입력단자에는, LUT(19B)에 포함되는, 심볼(CS)="+x" 및 심볼(NS)="-x"에 대응하는 신호(EE)의 값(이 예에서는 "0")이 공급된다. 즉, 비교부(101)는, 현재의 심볼(CS)이 심볼"+x"인 경우에 "1"을 출력하는 것이고, 비교부(112)는, 다음의 심볼(NS)이 심볼"-x"인 경우에 "1"을 출력하는 것이기 때문에, 제3의 입력단자에는, 심볼(CS)="+x" 및 심볼(NS)="-x"에 대응하는 신호(EE)의 값이 공급된다. 마찬가지로, 논리곱 회로(122)의 제1의 입력단자에는 비교부(101)의 출력 신호가 공급되고, 제2의 입력단자에는 비교부(113)의 출력 신호가 공급되고, 제3의 입력단자에는, LUT(19B)에 포함되는, 심볼(CS)="+x" 및 심볼(NS)="+y"에 대응하는 신호(EE)의 값(이 예에서는 "1")이 공급된다. 논리곱 회로(123)의 제1의 입력단자에는 비교부(101)의 출력 신호가 공급되고, 제2의 입력단자에는 비교부(114)의 출력 신호가 공급되고, 제3의 입력단자에는, LUT(19B)에 포함되는, 심볼(CS)="+x" 및 심볼(NS)="-y"에 대응하는 신호(EE)의 값(이 예에서는 "0")이 공급된다. 논리곱 회로(124)의 제1의 입력단자에는 비교부(101)의 출력 신호가 공급되고, 제2의 입력단자에는 비교부(115)의 출력 신호가 공급되고, 제3의 입력단자에는, LUT(19B)에 포함되는, 심볼(CS)="+x" 및 심볼(NS)="+z"에 대응하는 신호(EE)의 값(이 예에서는 "1")이 공급된다. 논리곱 회로(125)의 제1의 입력단자에는 비교부(101)의 출력 신호가 공급되고, 제2의 입력단자에는 비교부

(116)의 출력 신호가 공급되고, 제3의 입력단자에는, LUT(19B)에 포함되는, 심볼(CS)="+x" 및 심볼(NS)="-z"에 대응하는 신호(EE)의 값(이 예에서는 "0")이 공급된다.

[0113] 이에 의해, 논리 회로(120)는, 도 21과 같이, 심볼(CS)="+x" 및 심볼(NS)="+y"인 경우에, 논리곱 회로(122)가 "1"을 출력하고, 심볼(CS)="+x" 및 심볼(NS)="+z"인 경우에, 논리곱 회로(124)가 "1"을 출력하도록 되어 있다.

[0114] 마찬가지로, 논리 회로(130)는, 비교부(102)의 출력 신호, 비교부(111, 113~116)의 출력 신호, 및 LUT(19B)에서의 프리앰피시스의 설정에 의거하여, 신호를 생성하는 것이다. 논리 회로(140)는, 비교부(103)의 출력 신호, 비교부(111, 112, 114~116)의 출력 신호, 및 LUT(19B)에서의 프리앰피시스의 설정에 의거하여, 신호를 생성하는 것이다. 논리 회로(150)는, 비교부(104)의 출력 신호, 비교부(111~113, 115, 116)의 출력 신호, 및 LUT(19B)에서의 프리앰피시스의 설정에 의거하여, 신호를 생성하는 것이다. 논리 회로(160)는, 비교부(105)의 출력 신호, 비교부(111~114, 116)의 출력 신호, 및 LUT(19B)에서의 프리앰피시스의 설정에 의거하여, 신호를 생성하는 것이다. 논리 회로(170)는, 비교부(106)의 출력 신호, 비교부(111~116)의 출력 신호, 및 LUT(19B)에서의 프리앰피시스의 설정에 의거하여, 신호를 생성하는 것이다. 논리 회로(130, 140, 150, 160, 170)는, 논리 회로(120)와 같은 구성을 갖고 있다.

[0115] 논리합 회로(180)는, 논리 회로(120, 130, 140, 150, 160, 170) 내의 모든 논리곱 회로의 출력 신호의 논리합을 구하는 것이다.

[0116] 이와 같이 구성하여도, 상기 실시의 형태에 관한 통신 시스템(1)과 같은 효과를 얻을 수 있다.

#### 변형례 1-4

[0118] 상기 실시의 형태에서는, 송신 장치(10)는, 신호(SIGA, SIGB, SIGC)에 대해 프리앰피시스를 행하도록 하였지만, 이것으로 한정되는 것이 아니고, 이에 대신하여, 예를 들면 디앰피시스를 행하도록 하여도 좋다. 이하에, 본 변형례에 관한 송신 장치(10D)에 관해, 상세히 설명한다.

[0119] 도 23은, 본 변형례에 관한 LUT(19D)의 한 예를 도시하는 것이다. 송신 장치(10D)의 신호 생성부(11D)는, 현재의 심볼(CS) 및 신호(TxF, TxR, TxP)에 의거하여, 이 LUT(19D)를 참조하여, 신호(EA, EB, EC)를 생성한다. 그리고, 송신 장치(10D)의 송신부(20D)는, 신호(EA2, EB2, EC2)에 의거하여, 신호(SIGA, SIGB, SIGC)에 대해 디앰피시스를 행한다. 이하에, 현재의 심볼(CS)이 "+x"인 경우를 예로, 상세히 설명한다.

[0120] 도 24A~24E, 25A~25E는, 심볼이 "+x"로부터 "+x" 이외로 천이하는 경우의 동작을 도시하는 것이고, 도 24A~24E는, 신호(SIGA, SIGB, SIGC)의 과형을 도시하고, 도 25A~25E는, 차분(AB, BC, CA)의 과형을 도시한다. 이 예에서는, 전송로(9A~9C)의 길이는 충분히 단축하고 있다.

[0121] 심볼이 "+x"로부터 "-x"로 천이하는 경우에는, 신호 생성부(11D)는, 도 23에 도시한 바와 같이, 신호(EA, EB, EC)를 "0", "0", "0"으로 한다. 이에 의해, 송신부(20D)는, 도 24A에 도시한 바와 같이, 신호(SIGA~SIGC)에 대해 디앰피시스를 행하지 않는다. 이에 의해, 차분(AB, BC, CA)은, 도 25A에 도시한 바와 같은 과형이 된다.

[0122] 심볼이 "+x"로부터 "+y"로 천이하는 경우에는, 신호 생성부(11D)는, 도 23에 도시한 바와 같이, 신호(EA, EB, EC)를 "0", "0", "0"으로 한다. 이에 의해, 송신부(20D)는, 도 24B에 도시한 바와 같이, 신호(SIGA~SIGC)에 대해 디앰피시스를 행하지 않는다. 이에 의해, 차분(AB, BC, CA)은, 도 25B에 도시한 바와 같은 과형이 된다.

[0123] 심볼이 "+x"로부터 "-y"로 천이하는 경우에는, 신호 생성부(11D)는, 도 23에 도시한 바와 같이, 신호(EA, EB, EC)를 "0", "1", "0"으로 한다. 이에 의해, 송신부(20D)는, 도 24C에 도시한 바와 같이, 신호(SIGB)에 대해 디앰피시스를 행하여, 저레벨 전압(VL)으로부터, 저레벨 전압(VL)보다도 높은 전압으로 천이시킨다. 이 때, 송신부(20D)는, 신호(SIGA, SIGC)에 대해서는, 디앰피시스를 행하지 않는다. 이에 의해, 차분(AB, BC, CA)은, 도 25C에 도시한 바와 같은 과형이 된다. 즉, 이 예에서는, "0"을 넘어서 천이하는 차분(CA)은, 디앰피스의 영향을 받지 않는다.

[0124] 심볼이 "+x"로부터 "+z"로 천이하는 경우에는, 신호 생성부(11D)는, 도 23에 도시한 바와 같이, 신호(EA, EB, EC)를 "0", "0", "0"으로 한다. 이에 의해, 송신부(20D)는, 도 24D에 도시한 바와 같이, 신호(SIGA~SIGC)에 대해 디앰피시스를 행하지 않는다. 이에 의해, 차분(AB, BC, CA)은, 도 25D에 도시한 바와 같은 과형이 된다.

[0125] 심볼이 "+x"로부터 "-z"로 천이하는 경우에는, 신호 생성부(11D)는, 도 23에 도시한 바와 같이, 신호(EA, EB, EC)를 "1", "0", "0"으로 한다. 이에 의해, 송신부(20D)는, 도 24E에 도시한 바와 같이, 신호(SIGA)에 대해 디앰피시스를 행하여, 고레벨 전압(VH)으로부터, 고레벨 전압(VH)보다도 낮은 전압으로 천이시킨다. 이 때, 송신

부(20D)는, 신호(SIGA, SIGB)에 대해서는, 디엠퍼시스를 행하지 않는다. 이에 의해, 차분(AB, BC, CA)은, 도25E에 도시한 바와 같은 과형이 된다. 즉, 이 예에서는, "0"을 넘어서 천이하는 차분(BC)은, 디엠퍼시스의 영향을 받지 않는다.

[0126] 이와 같이, 송신 장치(10D)에서는, 차분(AB, BC, CA) 중의 "0"을 넘어서 천이하는 것에 영향이 미치지 않도록, 디엠퍼시스를 행한다. 이와 같이 구성하여도, 상기 실시의 형태에 관한 통신 시스템(1)과 같은 효과를 얻을 수 있다.

[0127] 또한, 6개의 심볼 사이의 천이 중, 디엠퍼시스를 행하는 천이는, 도 23의 예로 한정되는 것이 아니고, 어느 천이에 대해 디엠퍼시스를 행하는지는 임의로 설정할 수 있다.

[0128] 변형례 1-5

[0129] 상기 실시의 형태에서는, 신호 생성부(11)는, 레지스터(12)에 격납된 LUT(19)를 이용하여 신호(EA, EB, EC)를 생성하였다. 그 때, 이 LUT(19)는, 프리엠퍼시스의 설정을 변경할 수 있도록 구성하여도 좋다. 이하에, 본 변형례에 관한 통신 시스템(1E)에 관해 상세히 설명한다.

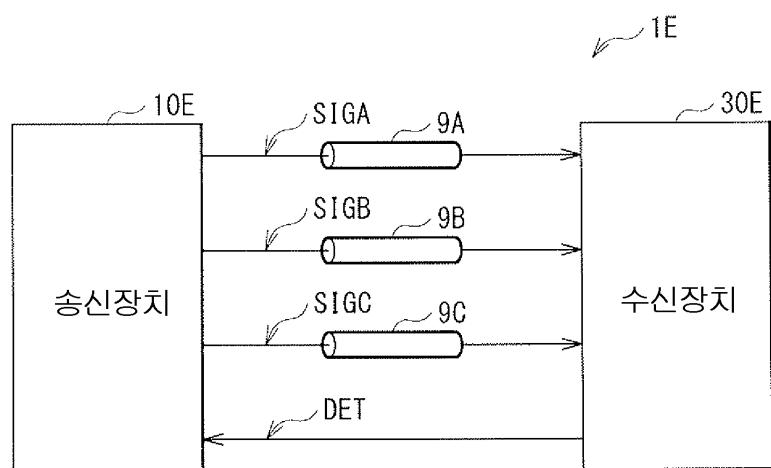

[0130] 도 26은, 통신 시스템(1E)의 한 구성례를 도시하는 것이다. 통신 시스템(1E)은, 수신 장치(30E)와, 송신 장치(10E)를 구비하고 있다. 통신 시스템(1E)은, 캘리브레이션용의 소정의 패턴을 송수신한 결과에 의거하여 프리엠퍼시스의 설정을 변경하는 것이다.

[0131] 도 27은, 수신 장치(30E)의 한 구성례를 도시하는 것이다. 수신 장치(30E)는, 신호 생성부(36E)를 갖고 있다. 신호 생성부(36E)는 패턴 검출부(37E)를 갖고 있다. 패턴 검출부(37E)는, 캘리브레이션 모드에서, 수신 장치(30E)가 수신한 신호의 패턴을 캘리브레이션용의 소정의 패턴과 비교하고, 그 비교 결과를 신호(DET)로서 송신 장치(10E)에 공급하는 것이다.

[0132] 도 28은, 송신 장치(10E)의 한 구성례를 도시하는 것이다. 송신 장치(10E)는, LUT 생성부(16E)를 갖고 있다. LUT 생성부(16E)는, 신호(DET)에 의거하여 LUT(19)를 생성하고, 레지스터(12)에 격납하는 것이다.

[0133] 여기서, 신호(DET)는, 본 개시에서의 「제어 신호」의 한 구체례에 대응한다. 패턴 검출부(37E)는, 본 개시에서의 「제어 신호 생성부」의 한 구체례에 대응한다. LUT 생성부(16E)는, 본 개시에서의 「테이블 설정부」의 한 구체례에 대응한다.

[0134] 이 통신 시스템(1E)에서는, 캘리브레이션 모드에서, 예를 들면 비트 에러 레이트가 낮아지도록, 프리惫퍼시스의 설정을 변경한다. 구체적으로는, 우선, 송신 장치(10E)가 캘리브레이션용의 소정의 패턴을 갖는 신호(SIGA~SIGC)를 송신한다. 그리고, 수신 장치(30E)는, 이 신호(SIGA~SIGC)를 수신하고, 패턴 검출부(37E)가, 그 수신한 신호의 패턴을 캘리브레이션용의 소정의 패턴과 비교하여, 그 비교 결과를 송신 장치(10E)에 통지한다. 그리고, 송신 장치(10E)의 LUT 생성부(16E)는, 이 비교 결과에 의거하여, 프리惫퍼시스의 설정을 변경한다. 통신 시스템(1E)에서는, 이와 같은 동작에 의해, 예를 들면 비트 에러 레이트가 낮아지도록, 프리惫퍼시스의 설정을 변경한다. 그리고, 프리惫퍼시스의 설정 종료 후에, 캘리브레이션 모드를 종료하여 통상의 데이터 전송을 행한다. 이와 같은 캘리브레이션은, 예를 들면, 전원 투입시에 실시하도록 하여도 좋고, 정기적으로 실시하도록 하여도 좋고, 교환되는 데이터량이 적은 때에 실시하도록 하여도 좋다.

[0135] 변형례 1-6

[0136] 상기 실시의 형태에서는, 현재의 심볼(CS)과, 신호(TxF, TxR, TxP)와, 신호(EA, EB, EC)와의 관계를 나타내는 LUT(19)를 이용하였지만, 이것으로 한정되는 것이 아니고, 이에 대신하여, 예를 들면, 다음의 심볼(NS)과, 신호(TxF, TxR, TxP)와, 신호(EA, EB, EC)와의 관계를 나타내는 LUT를 이용하여도 좋고, 또한, 예를 들면, 현재의 심볼(CS)과, 다음의 심볼(NS)과, 신호(EA, EB, EC)와의 관계를 나타내는 LUT를 이용하여도 좋다.

[0137] 변형례 1-7

[0138] 상기 실시의 형태에서는, 도 13 등에 도시한 바와 같이, 하나의 심볼을 송신하는 기간에 걸쳐서 프리惫퍼시스를 행하도록 하였지만, 이것으로 한정되는 것이 아니고, 이에 대신하여, 예를 들면, 도 29, 30에 도시하는 바와 같이, 신호(SIGA, SIGB, SIGC)의 천이 후의 소정의 기간만 프리惫퍼시스를 행하도록 하여도 좋다. 도 29, 30은, 심볼이 "+x"로부터 "+y"로 천이하는 경우를 도시하고 있다. 송신부(20)는, 도 29에 도시한 바와 같이, 신호(SIGA, SIGB, SIGC)의 천이 후의 소정의 기간만 프리惫퍼시스를 행한다. 이 때, 차분(AB)은, 도 30의 과형(W2 1)과 같이 되고, 차분(BC)은, 도 30의 과형(W23)과 같이 된다. 가령, 신호(SIGA~SIGC)에 대해 프리惫퍼시스를

행하지 않은 경우에는, 예를 들면, 차분(AB)은, 도 30의 과형(W22)과 같이 되고, 차분(BC)은, 도 30의 과형(W24)과 같이 된다. 즉, 이와 같은 경우에는, 과형의 천이가 무디어지기 때문에, 아이가 좁아질 우려가 있다. 한편, 본 변형례에서는, 신호(SIGA, SIGB, SIGC)의 천이 후의 소정의 기간만 프리앰페시스를 행하도록 하였기 때문에, 아이를 넓게 할 수 있고, 통신 품질을 높일 수 있다.

[0139] 기타의 변형례

[0140] 또한, 이들의 변형례 중의 2 이상을 조합시켜도 좋다.

[0141] (2. 제2의 실시의 형태)

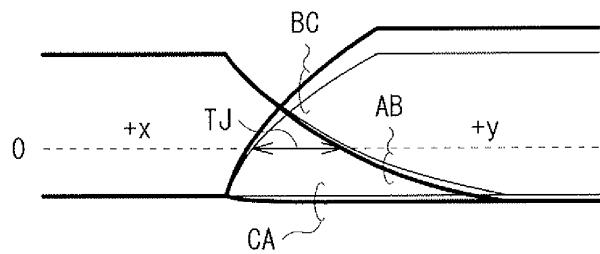

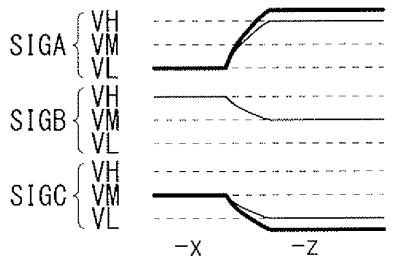

[0142] 다음에, 제2의 실시의 형태에 관한 통신 시스템(2)에 관해 설명한다. 통신 시스템(2)은, 이퀄라이저에 의해 통신 품질의 향상을 도모하는 것이다. 즉, 상기 제1의 실시의 형태에 관한 통신 시스템(1)에서는, 송신 장치(10)가 신호(SIGA~SIGC)에 대해 프리앰페시스를 행하도록 하였지만, 이 통신 시스템(2)에서는, 수신 장치가 신호(SIGA~SIGC)에 대해 이퀄라이즈를 행하는 것이다. 즉, 또한, 상기 제1의 실시의 형태에 관한 통신 시스템(1)과 실질적으로 동일한 구성 부분에는 동일한 부호를 붙이고, 적절히 설명을 생략한다.

[0143] 도 1에 도시한 바와 같이, 통신 시스템(2)은, 송신 장치(40)와, 수신 장치(60)를 구비하고 있다. 통신 시스템(2)은, 송신 장치(40)는 신호(SIGA~SIGC)에 대해 프리앰페시스를 행하지 않고, 수신 장치(60)가 신호(SIGA~SIGC)에 대해 이퀄라이즈를 행하는 것이다.

[0144] 도 31은, 송신 장치(40)의 한 구성례를 도시하는 것이다. 송신 장치(40)는, 신호 생성부(41)와, 송신부(50)를 갖고 있다. 신호 생성부(41)는, 제1의 실시의 형태에 관한 신호 생성부(11)와 마찬가지로, 현재의 심볼(CS), 신호(TxF, TxR, TxP), 및 클록(TxCK)에 의거하여, 다음의 심볼(NS)을 구하고, 신호(S1)로서 출력하는 것이다. 즉, 신호 생성부(41)는, 신호 생성부(11)로부터, 신호(EA, EB, EC)를 생성하는 기능을 생략한 것이다. 송신부(50)는, 신호(S2)에 의거하여, 신호(SIGA, SIGB, SIGC)를 생성하는 것이다.

[0145] 도 32는, 송신부(50)의 한 구성례를 도시하는 것이다. 송신부(50)는, 출력 제어부(21)와, 출력부(22A, 22B, 22C)를 갖고 있다. 즉, 송신부(50)는, 제1의 실시의 형태에 관한 송신부(20)로부터, 앰페시스 제어부(23) 및 출력부(24A~24C)를 생략한 것이다.

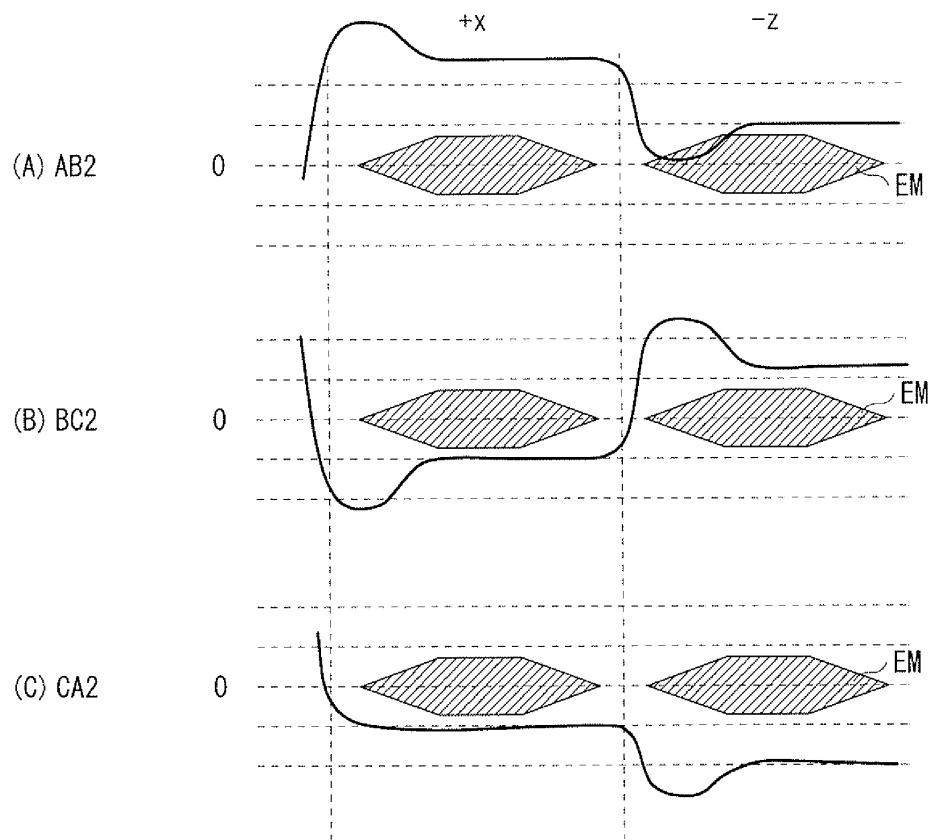

[0146] 도 33은, 수신 장치(60)의 한 구성례를 도시하는 것이다. 수신 장치(60)는, 이퀄라이저(61)와, 수신부(62, 63)와, FIFO(First In First Out) 메모리(66, 67)와, 셀렉터(68)를 갖고 있다.

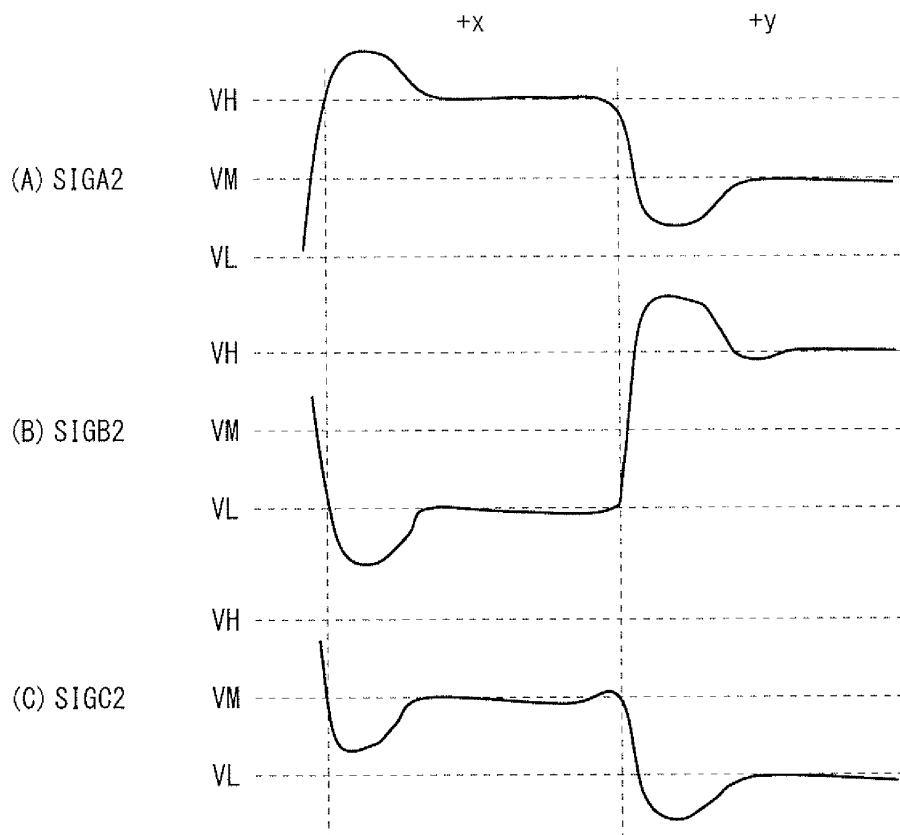

[0147] 이퀄라이저(61)는, 신호(SIGA)의 고주파 성분을 크게 하여 신호(SIGA2)로서 출력하고, 신호(SIGB)의 고주파 성분을 크게 하여 신호(SIGB2)로서 출력하고, 신호(SIGC)의 고주파 성분을 크게 하여 신호(SIGC2)로서 출력하는 것이다.

[0148] 수신부(62)는, 이퀄라이즈된 신호(SIGA2, SIGB2, SIGC2)에 의거하여, 신호(RxF1, RxR1, RxP1)와, 클록(RxCK1)을 생성하는 것이다. 수신부(62)는, 앰플리파이어(32A, 32B, 32C)와, 클록 생성부(33)와, 플립플롭(34, 35)과, 신호 생성부(36)를 갖고 있다. 즉, 수신부(62)는, 제1의 실시의 형태에 관한 수신 장치(30)와 같은 구성을이다.

[0149] 수신부(63)는, 이퀄라이즈되지 않은 신호(SIGA, SIGB, SIGC)에 의거하여, 신호(RxF2, RxR2, RxP2)와, 클록(RxCK2)을 생성하는 것이다. 수신부(63)는, 앰플리파이어(32A, 32B, 32C)와, 클록 생성부(33)와, 플립플롭(34, 35)과, 신호 생성부(65)와, 레지스터(64)를 갖고 있다. 즉, 수신부(63)는, 수신부(62)에서, 신호 생성부(36)를 신호 생성부(65)로 치환함과 함께, 레지스터(64)를 추가한 것이다.

[0150] 신호 생성부(65)는, 신호 생성부(36)와 마찬가지로, 플립플롭(34, 35)의 출력 신호, 및 클록(RxCK2)에 의거하여, 신호(RxF2, RxR2, RxP2)를 생성하는 것이다. 또한, 신호 생성부(65)는, 레지스터(64)로부터 공급된 LUT(59)에 의거하여, 신호(SEL)를 생성하는 기능도 갖고 있다. 신호(SEL)는, 이퀄라이즈된 신호(SIGA2, SIGB2, SIGC2)에 의거하여 생성한 신호(RxF1, RxR1, RxP1)와, 이퀄라이즈되지 않은 신호(SIGA, SIGB, SIGC)에 의거하여 생성한 신호(RxF2, RxR2, RxP2) 중의 어느 것을 선택하는지를 나타내는 것이다. LUT(59)는, 예를 들면, 현재의 심볼(CS2)과, 신호(RxF2, RxR2, RxP2)와, 신호(SEL)와의 관계를 나타낸 것이고, 예를 들면, 제1의 실시의 형태에 관한 LUT(19) 등과 마찬가지의 것이다. 신호 생성부(65)는, 현재의 심볼(CS2) 및 신호(RxF2, RxR2, RxP2)에 의거하여, 이 LUT(59)를 참조하여, 신호(SEL)를 생성하여 출력하도록 되어 있다.

[0151] 레지스터(64)는, LUT(59)를 기억하는 것이다. 이 LUT(64)는, 예를 들면, 수신 장치(60)의 전원 투입시에, 도시하지 않은 어플리케이션 프로세서로부터, 이 레지스터(64)에 기록되도록 되어 있다.

- [0152] FIFO 메모리(66)는, 수신부(62)로부터 공급된 신호(RxF1, RxR1, RxP1)를 일시적으로 기억하는 버퍼 메모리이다. 이 예에서는, FIFO 메모리(66)는, 클록(RxCK1)을 이용하여, 데이터의 기록 및 판독을 행하도록 되어 있다.

- [0153] FIFO 메모리(67)는, 수신부(63)로부터 공급된 신호(RxF2, RxR2, RxP2) 및 신호(SEL)를 일시적으로 기억하는 버퍼 메모리이다. 이 예에서는, FIFO 메모리(67)는, 클록(RxCK2)을 이용하여 데이터의 기록을 행함과 함께, 클록(RxCK1)을 이용하여 데이터의 판독을 행하도록 되어 있다.

- [0154] 셀렉터(68)는, FIFO 메모리(67)로부터 판독한 신호(SEL)에 의거하여, FIFO 메모리(66)로부터 판독된 신호(RxF1, RxR1, RxP1), 또는 FIFO 메모리(67)로부터 판독된 신호(RxF2, RxR2, RxP2)를 선택하고, 신호(RxF, RxR, RxP)로서 출력하는 것이다.

- [0155] 여기서, 수신부(63)는, 본 개시에서의 「제1의 수신부」의 한 구체례에 대응한다. 수신부(62)는, 본 개시에서의 「제2의 수신부」의 한 구체례에 대응한다. 신호 생성부(65) 및 셀렉터(68)는, 본 개시에서의 「선택 제어부」의 한 구체례에 대응한다.

- [0156] 다음에, 심볼의 천이 중의 몇가지를 예로 들어, 상세히 설명한다.

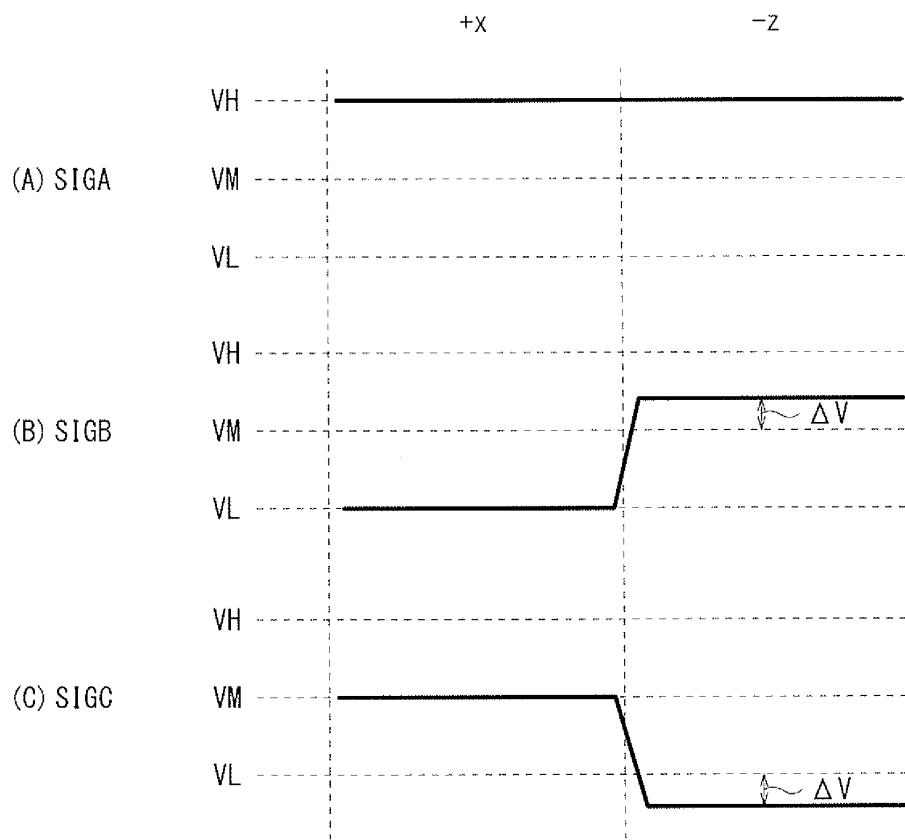

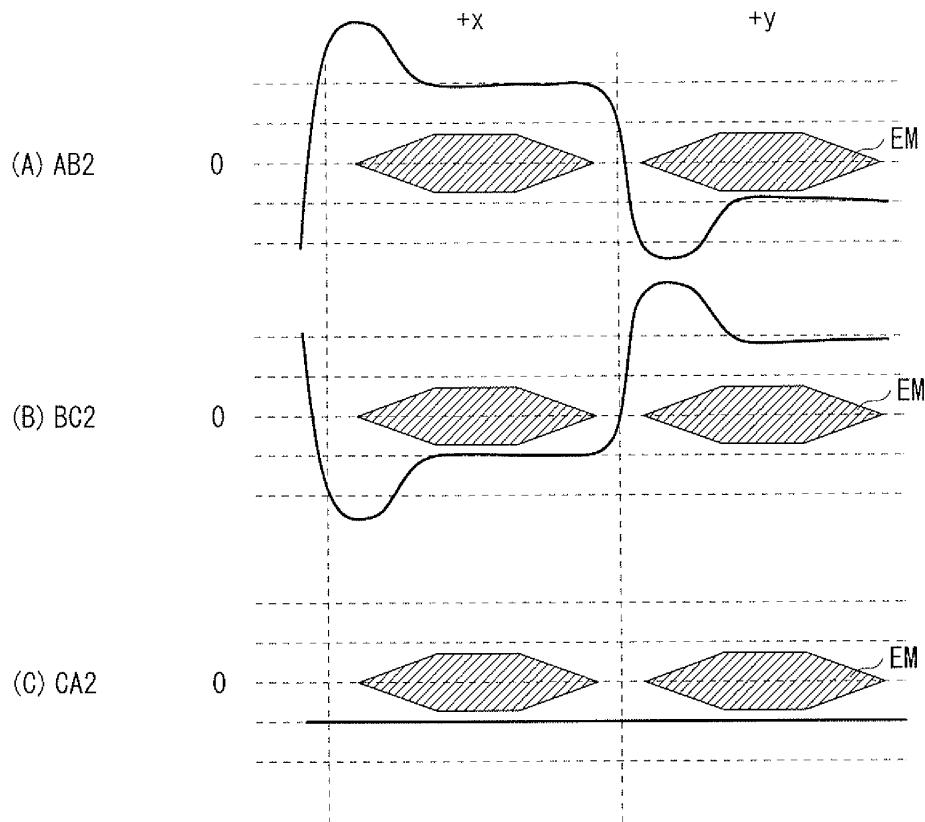

- [0157] 도 34 및 도 35는, 심볼이 "+x"로부터 "+y"로 천이하는 경우의 동작을 도시하는 것이고, 도 34(A)~(C)는, 이퀄라이즈된 신호(SIGA2, SIGB2, SIGC2)의 파형을 각각 도시하고, 도 35(A)~(C)는, 신호(SIGA2, SIGB2)의 차분(AB2), 신호(SIGB2, SIGC2)의 차분(BC2), 및 신호(SIGC2, SIGA2)의 차분(CA2)의 파형을 각각 도시한다. 이 예에서는, 전송로(9A~9C)의 길이는 충분히 단축하고 있다.

- [0158] 심볼이 "+x"로부터 "+y"로 천이할 때, 이퀄라이저(61)는, 도 34에 도시한 바와 같이, 신호(SIGA~SIGC)에서의 천이를 강조함에 의해, 신호(SIGA2~SIGC2)를 생성한다. 이 때, 차분(AB2, BC2, CA2)은, 도 35와 같이 된다. 이와 같이, 통신 시스템(2)에서는, 이퀄라이즈를 행하여, 파형의 천이를 가파르게 함에 의해, 아이를 넓게 할 수 있다. 따라서, 이와 같은 천이에서는, 셀렉터(68)는, 이퀄라이즈된 신호(SIGA2, SIGB2, SIGC2)에 의거하여 생성한 신호(RxF1, RxR1, RxP1)를 선택하여, 신호(RxF, RxR, RxP)로서 출력한다.

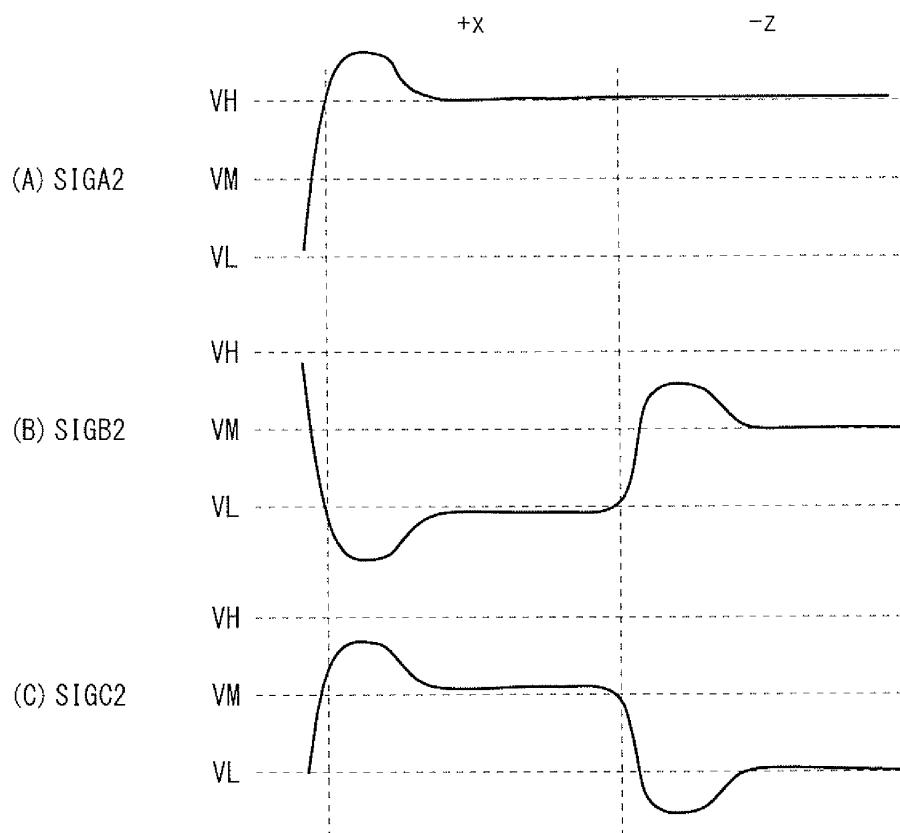

- [0159] 도 36 및 도 37은, 심볼이 "+x"로부터 "-z"로 천이하는 경우의 동작을 도시하는 것이고, 도 36(A)~(C)는, 이퀄라이즈된 신호(SIGA2, SIGB2, SIGC2)의 파형을 각각 도시하고, 도 37(A)~(C)는, 차분(AB2, BC2, CA2)의 파형을 각각 도시한다.

- [0160] 심볼이 "+x"로부터 "-z"로 천이할 때도, 이퀄라이저(61)는, 도 36에 도시한 바와 같이, 신호(SIGA~SIGC)에서의 천이를 강조함에 의해, 신호(SIGA2~SIGC2)를 생성한다. 이 때, 차분(AB2, BC2, CA2)은, 도 37과 같이 된다. 이와 같이, 차분(AB2)의 파형은, 도 37(A)에 도시한 바와 같이, 천이의 때에 언더 슈트가 생겨, 아이가 좁아질 우려가 있다. 따라서, 이와 같은 천이에서는, 셀렉터(68)는, 이퀄라이즈되지 않은 신호(SIGA, SIGB, SIGC)에 의거하여 생성한 신호(RxF2, RxR2, RxP2)를 선택하여, 신호(RxF, RxR, RxP)로서 출력한다.

- [0161] 이와 같이, 통신 시스템(2)에서는, 신호(SIGA, SIGB, SIGC)에 대해 선택적으로 이퀄라이즈를 행하도록 하였기 때문에, 예를 들면, 이퀄라이즈를 행하면 아이가 좁아지는 천이인 경우에는 이퀄라이즈를 행하지 않도록 할 수 있다. 이에 의해, 통신 시스템(2)에서는, 통신 품질을 높일 수 있다.

- [0162] 이상과 같이 본 실시의 형태에서는, 신호(SIGA~SIGC)에 대해 선택적으로 이퀄라이즈를 행하도록 하였기 때문에, 통신 품질을 높일 수 있다.

- [0163] 변형례 2-1

- [0164] 상기 실시의 형태에서는, 수신부(63)의 신호 생성부(65)가 신호(SEL)를 생성하도록 하였지만, 이것으로 한정되는 것이 아니고, 이에 대신하여, 예를 들면, 수신부(62)의 신호 생성부(36)가 신호(SEL)를 생성하여도 좋다. 또한, 수신부(62)의 신호 생성부(36) 및 수신부(63)의 신호 생성부(65)가 각각 신호(SEL)를 생성하고, 이들의 신호(SEL)에 의거하여, 셀렉터(68)가 선택 동작을 행하도록 하여도 좋다.

- [0165] 변형례 2-2

- [0166] 또한, 제1의 실시의 형태에 관한 송신 장치(10)와, 본 실시의 형태에 관한 수신 장치(60)를 조합시켜서, 통신 시스템을 구성하여도 좋다. 이 경우에는, 송신 장치(10)가 신호(SIGA, SIGB, SIGC)에 대해 프리앰프시스를 행하고, 수신 장치(60)가 신호(SIGA, SIGB, SIGC)에 대해 이퀄라이즈를 행하기 때문에, 보다 긴 전송로(9A, 9B, 9C)를 통하여 데이터의 송수신을 행할 수가 있다.

[0167] (3. 적용례)

[0168] 다음에, 상기 실시의 형태 및 변형례로 설명한 통신 시스템의 적용례에 관해 설명한다.

[0169] 도 38은, 상기 실시의 형태 등의 통신 시스템이 적용된 스마트 폰(300)(다기능 휴대 전화)의 외관을 도시하는 것이다. 이 스마트 폰(300)에는, 다양한 디바이스가 탑재되어 있고, 그들의 디바이스 사이에서 데이터의 교환을 행하는 통신 시스템에서, 상기 실시의 형태 등의 통신 시스템이 적용되어 있다.

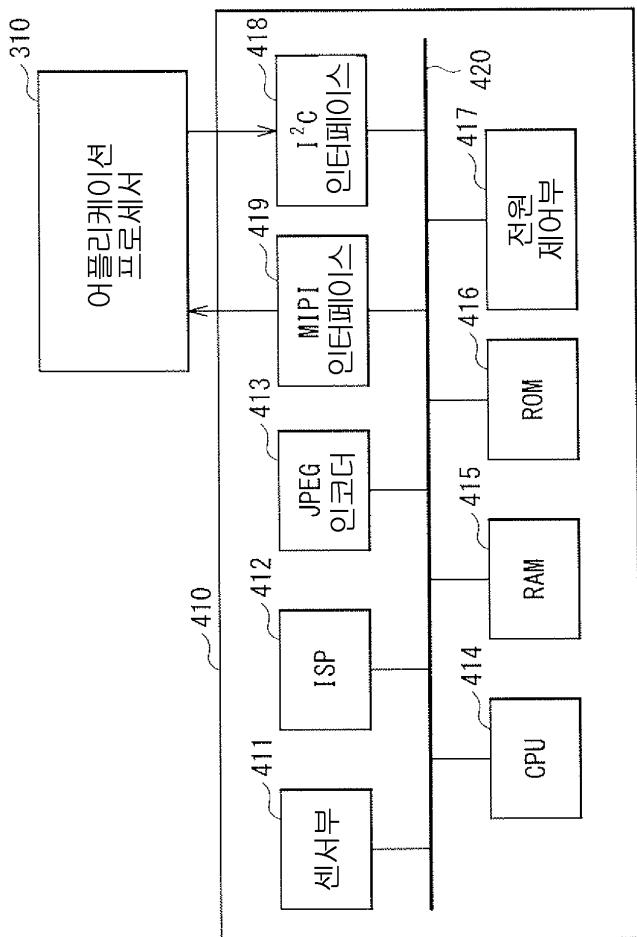

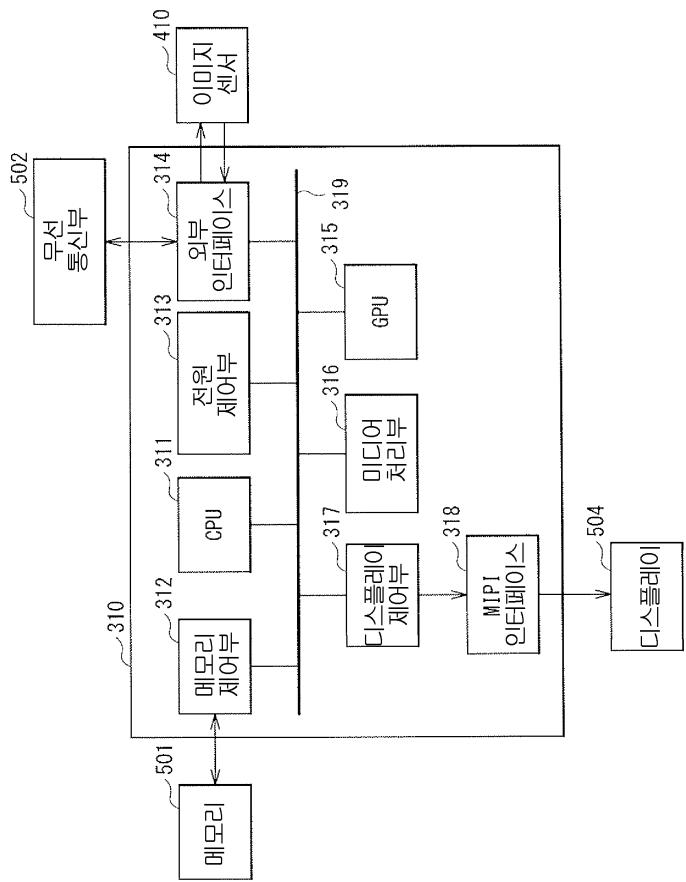

[0170] 도 39는, 스마트 폰(300)에 사용되는 어플리케이션 프로세서(310)의 한 구성례를 도시하는 것이다. 어플리케이션 프로세서(310)는, CPU(Central Processing Unit)(311)와, 메모리 제어부(312)와, 전원 제어부(313)와, 외부 인터페이스(314)와, GPU(Graphics Processing Unit)(315)와, 미디어 처리부(316)와, 디스플레이 제어부(317)와, MIPI(Mobile Industry Processor Interface) 인터페이스(318)를 갖고 있다. CPU(311), 메모리 제어부(312), 전원 제어부(313), 외부 인터페이스(314), GPU(315), 미디어 처리부(316), 디스플레이 제어부(317)는, 이 예에서는, 시스템 버스(319)에 접속되고, 이 시스템 버스(319)를 통하여, 서로 데이터의 교환을 할 수 있게 되어 있다.

[0171] CPU(311)는, 프로그램에 따라, 스마트 폰(300)에서 취급되는 다양한 정보를 처리하는 것이다. 메모리 제어부(312)는, CPU(311)가 정보 처리를 행할 때에 사용하는 메모리(501)를 제어하는 것이다. 전원 제어부(313)는, 스마트 폰(300)의 전원을 제어하는 것이다.

[0172] 외부 인터페이스(314)는, 외부 디바이스와 통신하기 위한 인터페이스이고, 이 예에서는, 무선 통신부(502) 및 이미지 센서(503)와 접속되어 있다. 무선 통신부(502)는, 휴대 전화의 기지국과 무선 통신을 하는 것이고, 예를 들면, 베이스밴드부나, RF(Radio Frequency) 프런트 엔드부 등을 포함하여 구성된다. 이미지 센서(503)는, 화상을 취득하는 것이고, 예를 들면 CMOS 센서를 포함하여 구성된다.

[0173] GPU(315)은, 화상 처리를 행하는 것이다. 미디어 처리부(316)는, 음성이나, 문자나, 도형 등의 정보를 처리하는 것이다. 디스플레이 제어부(317)는, MIPI 인터페이스(318)를 통하여, 디스플레이(504)를 제어하는 것이다. MIPI 인터페이스(318)는 화상 신호를 디스플레이(504)에 송신하는 것이다. 화상 신호로서는, 예를 들면, YUV 형식이나 RGB 형식 등의 신호를 이용할 수 있다. 이 MIPI 인터페이스(318)와 디스플레이(504)와의 사이의 통신 시스템에는, 예를 들면, 상기 실시의 형태 등의 통신 시스템이 적용된다.

[0174] 도 40은, 이미지 센서(410)의 한 구성례를 도시하는 것이다. 이미지 센서(410)는, 센서부(411)와, ISP(Image Signal Processor)(412)와, JPEG(Joint Photographic Experts Group) 인코더(413)와, CPU(414)와, RAM(Random Access Memory)(415)과, ROM(Read Only Memory)(416)과, 전원 제어부(417)와, I2C(Inter-Integrated Circuit) 인터페이스(418)와, MIPI 인터페이스(419)를 갖고 있다. 이들의 각 블록은, 이 예에서는, 시스템 버스(420)에 접속되고, 이 시스템 버스(420)를 통하여, 서로 데이터의 교환을 할 수 있게 되어 있다.

[0175] 센서부(411)는, 화상을 취득하는 것이고, 예를 들면 CMOS 센서에 의해 구성되는 것이다. ISP(412)는, 센서부(411)가 취득한 화상에 대해 소정의 처리를 행하는 것이다. JPEG 인코더(413)는, ISP(412)가 처리한 화상을 인코드하여 JPEG 형식의 화상을 생성하는 것이다. CPU(414)는, 프로그램에 따라 이미지 센서(410)의 각 블록을 제어하는 것이다. RAM(415)은, CPU(414)가 정보 처리를 행할 때에 사용하는 메모리이다. ROM(416)은, CPU(414)에서 실행되는 프로그램을 기억하는 것이다. 전원 제어부(417)는, 이미지 센서(410)의 전원을 제어하는 것이다. I2C 인터페이스(418)는, 어플리케이션 프로세서(310)로부터 제어 신호를 수취하는 것이다. 또한, 도시하지 않지만, 이미지 센서(410)는, 어플리케이션 프로세서(310)로부터, 제어 신호에 더하여 클록 신호도 수취하도록 되어 있다. 구체적으로는, 이미지 센서(410)는, 다양한 주파수의 클록 신호에 의거하여 동작할 수 있도록 구성되어 있다. MIPI 인터페이스(419)는, 화상 신호를 어플리케이션 프로세서(310)에 송신하는 것이다. 화상 신호로서는, 예를 들면, YUV 형식이나 RGB 형식 등의 신호를 이용할 수 있다. 이 MIPI 인터페이스(419)와 어플리케이션 프로세서(310) 사이의 통신 시스템에는, 예를 들면, 상기 실시의 형태 등의 통신 시스템이 적용된다.

[0176] 이상, 몇가지의 실시의 형태 및 변형례, 및 전자 기기에의 적용례를 들어 본 기술을 설명하였지만, 본 기술은 이들의 실시의 형태 등으로는 한정되지 않고, 여러가지의 변형이 가능하다.

[0177] 예를 들면, 상기한 각 실시의 형태에서는, 신호(SIGA, SIGB, SIGC)는, 각각, 3개의 전압 상태(SH, SM, SL) 사이에서 천이하는 것으로 하였지만, 이것으로 한정되는 것이 아니고, 이에 대신하여, 예를 들면, 2개의 전압 상태 사이에서 천이하여도 좋고, 또는 4개 이상의 전압 상태 사이에서 천이하여도 좋다.

[0178] 또한, 예를 들면, 상기한 각 실시의 형태에서는, 3개의 신호(SIGA, SIGB, SIGC)를 이용하여 통신을 행하였지만,

이것으로 한정되는 것이 아니고, 이에 대신하여, 예를 들면 2개의 신호를 이용하여 통신을 행하여도 좋고, 4개 이상의 신호를 이용하여 통신을 행하여도 좋다.

[0179] 또한, 본 명세서에 기재된 효과는 어디까지나 예시이고 한정되는 것이 아니라, 또한 다른 효과가 있어도 좋다.

[0180] 또한, 본 기술은 이하와 같은 구성으로 할 수 있다.

[0181] (1) 데이터 신호에 의거하여, 선택적으로 엠파시스를 행함에 의해 1 또는 복수의 송신 신호를 생성하는 송신부와,

[0182] 상기 데이터 신호의 천이 패턴에 의거하여 엠파시스를 행하는지의 여부를 판단하고 상기 송신부를 제어하는 제어부를 구비한 송신 장치.

[0183] (2) 상기 데이터 신호는, 송신 심볼의 시퀀스를 나타내고,

[0184] 상기 제어부는, 연속한 2개의 송신 심볼을 비교하고, 그 비교 결과에 의거하여 엠파시스를 행하는지의 여부를 판단하는 상기 (1)에 기재된 송신 장치.

[0185] (3) 상기 제어부는, 상기 천이 패턴과, 엠파시스를 행하는지의 여부를 나타내는 플래그와의 관계를 나타내는 루업 테이블을 가지며, 상기 루업 테이블에 의거하여, 엠파시스를 행하는지의 여부를 판단하는 상기 (1) 또는 (2)에 기재된 송신 장치.

[0186] (4) 상기 루업 테이블은, 프로그램 가능하게 구성되어 있는 상기 (3)에 기재된 송신 장치.

[0187] (5) 상기 송신부는, 상기 송신 신호의 고주파 성분을 크게 하도록 엠파시스를 행하는 상기 (1)부터 (4)의 어느 하나에 기재된 송신 장치.

[0188] (6) 각 송신 신호는, 복수의 전압 상태 사이에서 천이하고,

[0189] 상기 제어부는, 상기 복수의 전압 상태 사이의 천이 중의 일부의 천이에서, 그 송신 신호에 대해 엠파시스를 행하여야 할 것으로 판단하는 상기 (5)에 기재된 송신 장치.

[0190] (7) 상기 송신부는, 3개의 송신 신호를 생성하고,

[0191] 각 송신 신호는, 제1의 전압 상태와, 제2의 전압 상태와, 상기 제1의 전압 상태의 전압 레벨과 상기 제2의 전압 상태의 전압 레벨 사이의 전압 레벨을 갖는 제3의 전압 상태의 사이에서 천이하고,

[0192] 상기 제어부는,

[0193] 상기 3개의 송신 신호 중, 상기 제1의 전압 상태 및 상기 제3의 전압 상태로부터 상기 제2의 전압 상태로 천이 하는 송신 신호에 대해 엠파시스를 행하여야 할 것으로 판단하고,

[0194] 상기 3개의 송신 신호 중, 상기 제2의 전압 상태 및 상기 제3의 전압 상태로부터 상기 제1의 전압 상태로 천이 하는 송신 신호에 대해 엠파시스를 행하여야 할 것으로 판단하는 상기 (5) 또는 (6)에 기재된 송신 장치.

[0195] (8) 상기 제어부는, 상기 3개의 송신 신호 중, 상기 제1의 전압 상태 및 상기 제2의 전압 상태를 유지하는 송신 신호에 대해 엠파시스를 행하여야 할 것으로 판단하는 상기 (7)에 기재된 송신 장치.

[0196] (9) 상기 제어부는,

[0197] 상기 3개의 송신 신호 중, 상기 제1의 전압 상태 및 상기 제2의 전압 상태로부터 상기 제3의 전압 상태로 천이 하는 송신 신호에 대해 엠파시스를 행하여야 할 것이 아니라고 판단하고,

[0198] 상기 3개의 송신 신호 중, 상기 제3의 전압 상태를 유지하는 송신 신호에 대해 엠파시스를 행하여야 할 것이 아니라고 판단하는 상기 (7)에 기재된 송신 장치.

[0199] (10) 상기 송신부는, 제1의 송신 신호, 제2의 송신 신호, 및 제3의 송신 신호를 생성하고,

[0200] 각 송신 신호는, 제1의 전압 상태와, 제2의 전압 상태와, 상기 제1의 전압 상태의 전압 레벨과 상기 제2의 전압 상태의 전압 레벨 사이의 전압 레벨을 갖는 제3의 전압 상태의 사이에서 천이하고,

[0201] 상기 제어부는, 상기 제1의 송신 신호가 상기 제1의 전압 상태로부터 상기 제3의 전압 상태로 변화하고, 상기 제2의 송신 신호가 상기 제2의 전압 상태로부터 상기 제1의 전압 상태로 변화하고, 상기 제3의 송신 신호가 상기 제3의 전압 상태로부터 상기 제2의 전압 상태로 변화하는 경우에, 상기 제2의 송신 신호 및 상기 제3의 송신

신호에 대해 엠피시스를 행하여야 할 것으로 판단하는 상기 (5) 또는 (6)에 기재된 송신 장치.

[0202] (11) 상기 송신부는, 제1의 송신 신호, 제2의 송신 신호, 및 제3의 송신 신호를 생성하고,

[0203] 각 송신 신호는, 제1의 전압 상태와, 제2의 전압 상태와, 상기 제1의 전압 상태의 전압 레벨과 상기 제2의 전압 상태의 전압 레벨 사이의 전압 레벨을 갖는 제3의 전압 상태의 사이에서 천이하고,

[0204] 상기 제어부는, 상기 제1의 송신 신호와 상기 제2의 송신 신호와의 차분 신호, 상기 제2의 송신 신호와 상기 제3의 송신 신호와의 차분 신호, 상기 제1의 송신 신호와 상기 제3의 송신 신호와의 차분 신호의 모두가 극성을 변화시키는 경우에, 엠피시스를 행하여야 할 것으로 판단하는 상기 (5) 또는 (6)에 기재된 송신 장치.

[0205] (12) 상기 송신부는, 상기 송신 신호의 저주파 성분을 작게 하도록 엠피시스를 행하는 상기 (1)부터 (4)의 어느 하나에 기재된 송신 장치.

[0206] (13) 각 송신 신호는, 복수의 전압 상태 사이에서 천이하고,

[0207] 상기 제어부는, 각 송신 신호가, 상기 복수의 전압 상태 중의 일부의 전압 상태를 유지하는 경우에 있어서, 그 송신 신호에 대해 엠피시스를 행하여야 할 것으로 판단하는 상기 (12)에 기재된 송신 장치.

[0208] (14) 상기 송신부는, 3개의 송신 신호를 생성하고,

[0209] 각 송신 신호는, 제1의 전압 상태와, 제2의 전압 상태와, 상기 제1의 전압 상태의 전압 레벨과 상기 제2의 전압 상태의 전압 레벨 사이의 전압 레벨을 갖는 제3의 전압 상태의 사이에서 천이하고,

[0210] 상기 제어부는, 상기 3개의 송신 신호 중, 상기 제1의 전압 상태 및 상기 제2의 전압 상태를 유지하는 송신 신호에 대해 엠피시스를 행하여야 할 것으로 판단하는 상기 (12) 또는 (13)에 기재된 송신 장치.

[0211] (15) 상기 제어부는, 상기 3개의 송신 신호 중, 상기 제3의 전압 상태를 유지하는 송신 신호에 대해 엠피시스를 행하여야 할 것이 아니라고 판단하는 상기 (14)에 기재된 송신 장치.

[0212] (16) 상기 송신부는, 복수의 송신 신호를 생성하고,

[0213] 상기 제어부는, 상기 복수의 송신 신호에 대해 엠피시스를 행하는지의 여부를 각각 판단하는 상기 (1)부터 (15)의 어느 하나에 기재된 송신 장치.

[0214] (17) 상기 송신부는, 복수의 송신 신호를 생성하고,

[0215] 상기 제어부는, 상기 복수의 송신 신호에 대해 엠피시스를 행하는지의 여부를 일괄하여 판단하는 상기 (1)부터 (15)의 어느 하나에 기재된 송신 장치.

[0216] (18) 송신 심볼의 시퀀스를 나타내는 데이터 신호에 의거하여 1 또는 복수의 송신 신호를 생성함과 함께, 각 송신 신호의 전압 레벨을 보정하는 송신부와,

[0217] 상기 데이터 신호에서의, 시간적으로 이웃하는 2개의 송신 심볼을 비교하고, 그 비교 결과에 의거하여 상기 전압 레벨을 보정하도록 상기 송신부를 제어하는 제어부를 구비한 송신 장치.

[0218] (19) 1 또는 복수의 송신 신호를 수신하는 제1의 수신부와,

[0219] 상기 1 또는 복수의 송신 신호의 각각에 대해 이퀄라이즈를 행하는 이퀄라이저와,

[0220] 이퀄라이즈된 1 또는 복수의 송신 신호를 수신하는 제2의 수신부와,

[0221] 상기 제1의 수신부 또는 상기 제2의 수신부가 수신한 상기 1 또는 복수의 송신 신호의 천이 패턴에 의거하여, 상기 제1의 수신부의 제1의 출력 신호 또는 상기 제2의 수신부의 제2의 출력 신호를 선택하는 선택 제어부를 구비한 수신 장치.

[0222] (20) 상기 선택 제어부는, 상기 1 또는 복수의 송신 신호에서의 전압 상태의 시퀀스를 구하고, 시간적으로 이웃하는 2개의 전압 상태를 비교하고, 그 비교 결과에 의거하여, 상기 제1의 출력 신호 또는 상기 제2의 출력 신호를 선택하는 상기 (19)에 기재된 수신 장치.

[0223] (21) 상기 제어부는, 상기 천이 패턴과, 이퀄라이즈를 행하는지의 여부를 나타내는 플래그와의 관계를 나타내는 루프 테이블을 가지며, 상기 루프 테이블에 의거하여, 상기 제1의 출력 신호 또는 상기 제2의 출력 신호를 선택하는 상기 (19) 또는 (20)에 기재된 수신 장치.

- [0224] (22) 상기 이퀄라이저는, 상기 송신 신호의 고주파 성분을 크게 하도록 이퀄라이즈를 행하는 상기 (19)부터 (21)의 어느 하나에 기재된 수신 장치.

- [0225] (23) 상기 1 또는 복수의 송신 신호는, 3개의 송신 신호이고,

- [0226] 각 송신 신호는, 제1의 전압 상태와, 제2의 전압 상태와, 상기 제1의 전압 상태의 전압 레벨과 상기 제2의 전압 상태의 전압 레벨 사이의 전압 레벨을 갖는 제3의 전압 상태의 사이에서 천이하는 상기 (19)부터 (22)의 어느 하나에 기재된 수신 장치.

- [0227] (24) 1 또는 복수의 송신 신호를 송신하는 송신 장치와,

- [0228] 상기 1 또는 복수의 송신 신호를 수신하는 수신 장치를 구비하고,

- [0229] 상기 송신 장치는,

- [0230] 데이터 신호에 의거하여, 선택적으로 엠파시스를 행함에 의해 상기 1 또는 복수의 송신 신호를 생성하는 송신부와,

- [0231] 상기 데이터 신호의 천이 패턴에 의거하여 엠파시스를 행하는지의 여부를 판단하고 상기 송신부를 제어하는 제어부를 갖는 통신 시스템.

- [0232] (25) 상기 제어부는, 상기 천이 패턴과, 엠파시스를 행하는지의 여부를 나타내는 플래그와의 관계를 나타내는 루크 업 테이블을 가지며, 상기 루크 업 테이블에 의거하여, 엠파시스를 행하는지의 여부를 판단하고,

- [0233] 상기 수신 장치는,

- [0234] 상기 1 또는 복수의 송신 신호를 수신하는 수신부와,

- [0235] 상기 수신부가 수신한 상기 1 또는 복수의 송신 신호에 의거하여, 제어 신호를 생성하는 제어 신호 생성부를 또한 가지며,

- [0236] 상기 송신 장치는, 상기 제어 신호에 의거하여 상기 루크 업 테이블을 프로그램하는 테이블 설정부를 또한 갖는 상기 (24)에 기재된 통신 시스템.

- [0237] (26) 1 또는 복수의 송신 신호를 송신하는 송신 장치와,

- [0238] 상기 1 또는 복수의 송신 신호를 수신하는 수신 장치를 구비하고,

- [0239] 상기 송신 장치는,

- [0240] 데이터 신호에 의거하여, 선택적으로 엠파시스를 행함에 의해 상기 1 또는 복수의 송신 신호를 생성하는 송신부와,

- [0241] 상기 데이터 신호의 천이 패턴에 의거하여 엠파시스를 행하는지의 여부를 판단하고 상기 송신부를 제어하는 제어부를 가지며,

- [0242] 상기 수신 장치는,

- [0243] 상기 1 또는 복수의 송신 신호를 수신하는 제1의 수신부와,

- [0244] 상기 1 또는 복수의 송신 신호의 각각에 대해 이퀄라이즈를 행하는 이퀄라이저와,

- [0245] 이퀄라이즈된 1 또는 복수의 송신 신호를 수신하는 제2의 수신부와,

- [0246] 상기 제1의 수신부 또는 상기 제2의 수신부가 수신한 상기 1 또는 복수의 송신 신호의 천이 패턴에 의거하여, 상기 제1의 수신부의 제1의 출력 신호 또는 상기 제2의 수신부의 제2의 출력 신호를 선택하는 선택 제어부를 갖는 통신 시스템.

- [0247] 본원 발명의 또한 이하의 구성을 채용할 수 있다.

- [0248] (1) 송신 장치에 있어서,

- [0249] 데이터 신호에 의거하여, 선택적으로 엠파시스를 행함에 의해 1 또는 복수의 송신 신호를 생성하는 송신부와,

- [0250] 상기 데이터 신호의 천이 패턴에 의거하여 엠파시스를 행하는지의 여부를 판단하고 상기 송신부를 제어하는 제

여부를 구비한 송신 장치.

[0251] (2) 상기 데이터 신호는, 송신 심볼의 시퀀스를 나타내고,

[0252] 상기 제어부는, 연속한 2개의 송신 심볼을 비교하고, 그 비교 결과에 의거하여 엠파시스를 행하는지의 여부를 판단하는 (1)에 기재된 송신 장치.

[0253] (3) 상기 제어부는, 상기 천이 패턴과, 엠파시스를 행하는지의 여부를 나타내는 플래그와의 관계를 나타내는 루업 테이블을 가지며, 상기 루업 테이블에 의거하여, 엠파시스를 행하는지의 여부를 판단하는 (1)에 기재된 송신 장치.

[0254] (4) 상기 루업 테이블은, 프로그램 가능하게 구성되어 있는 (3)에 기재된 송신 장치.

[0255] (5) 상기 송신부는, 상기 송신 신호의 고주파 성분을 크게 하도록 엠파시스를 행하는 (1) 내지 (4)에 기재된 송신 장치.

[0256] (6) 각 송신 신호는, 복수의 전압 상태 사이에서 천이하고,

[0257] 상기 제어부는, 상기 복수의 전압 상태 사이의 천이 중의 일부의 천이에서, 그 송신 신호에 대해 엠파시스를 행하여야 할 것으로 판단하는 (5)에 기재된 송신 장치.

[0258] (7) 상기 송신부는, 3개의 송신 신호를 생성하고,

[0259] 각 송신 신호는, 제1의 전압 상태와, 제2의 전압 상태와, 상기 제1의 전압 상태의 전압 레벨과 상기 제2의 전압 상태의 전압 레벨 사이의 전압 레벨을 갖는 제3의 전압 상태의 사이에서 천이하고,

[0260] 상기 제어부는, 상기 3개의 송신 신호 중, 상기 제1의 전압 상태 및 상기 제3의 전압 상태로부터 상기 제2의 전압 상태로 천이하는 송신 신호에 대해 엠파시스를 행하여야 할 것으로 판단하고,

[0261] 상기 3개의 송신 신호 중, 상기 제2의 전압 상태 및 상기 제3의 전압 상태로부터 상기 제1의 전압 상태로 천이하는 송신 신호에 대해 엠파시스를 행하여야 할 것으로 판단하는 (5) 또는 (6)에 기재된 송신 장치.

[0262] (8) 상기 제어부는, 상기 3개의 송신 신호 중, 상기 제1의 전압 상태 및 상기 제2의 전압 상태를 유지하는 송신 신호에 대해 엠파시스를 행하여야 할 것으로 판단하는 (7)에 기재된 송신 장치.

[0263] (9) 상기 제어부는,

[0264] 상기 3개의 송신 신호 중, 상기 제1의 전압 상태 및 상기 제2의 전압 상태로부터 상기 제3의 전압 상태로 천이하는 송신 신호에 대해 엠파시스를 행하여야 할 것이 아니라고 판단하고,

[0265] 상기 3개의 송신 신호 중, 상기 제3의 전압 상태를 유지하는 송신 신호에 대해 엠파시스를 행하여야 할 것이 아니라고 판단하는 (7) 또는 (8)에 기재된 송신 장치.

[0266] (10) 상기 송신부는, 제1의 송신 신호, 제2의 송신 신호, 및 제3의 송신 신호를 생성하고,

[0267] 각 송신 신호는, 제1의 전압 상태와, 제2의 전압 상태와, 상기 제1의 전압 상태의 전압 레벨과 상기 제2의 전압 상태의 전압 레벨 사이의 전압 레벨을 갖는 제3의 전압 상태의 사이에서 천이하고,

[0268] 상기 제어부는, 상기 제1의 송신 신호가 상기 제1의 전압 상태로부터 상기 제3의 전압 상태로 변화하고, 상기 제2의 송신 신호가 상기 제2의 전압 상태로부터 상기 제1의 전압 상태로 변화하고, 상기 제3의 송신 신호가 상기 제3의 전압 상태로부터 상기 제2의 전압 상태로 변화하는 경우에, 상기 제2의 송신 신호 및 상기 제3의 송신 신호에 대해 엠파시스를 행하여야 할 것으로 판단하는 (5) 또는 (6)○ 기재된 송신 장치.

[0269] (11) 상기 송신부는, 제1의 송신 신호, 제2의 송신 신호, 및 제3의 송신 신호를 생성하고,

[0270] 각 송신 신호는, 제1의 전압 상태와, 제2의 전압 상태와, 상기 제1의 전압 상태의 전압 레벨과 상기 제2의 전압 상태의 전압 레벨 사이의 전압 레벨을 갖는 제3의 전압 상태의 사이에서 천이하고,

[0271] 상기 제어부는, 상기 제1의 송신 신호와 상기 제2의 송신 신호와의 차분 신호, 상기 제2의 송신 신호와 상기 제3의 송신 신호와의 차분 신호, 상기 제1의 송신 신호와 상기 제3의 송신 신호와의 차분 신호의 모두가 극성을 변화시키는 경우에, 엠파시스를 행하여야 할 것으로 판단하는 (5) 또는 (6)○ 기재된 송신 장치.

[0272] (12) 상기 송신부는, 상기 송신 신호의 저주파 성분을 작게 하도록 엠파시스를 행하는 (1) 내지 (4)에 기재된

송신 장치.

[0273] (13) 각 송신 신호는, 복수의 전압 상태 사이에서 천이하고,

[0274] 상기 제어부는, 각 송신 신호가, 상기 복수의 전압 상태 중의 일부의 전압 상태를 유지하는 경우에 있어서, 그 송신 신호에 대해 앰페시스를 행하여야 할 것으로 판단하는 (12)에 기재된 송신 장치.

[0275] (14) 상기 송신부는, 3개의 송신 신호를 생성하고,

[0276] 각 송신 신호는, 제1의 전압 상태와, 제2의 전압 상태와, 상기 제1의 전압 상태의 전압 레벨과 상기 제2의 전압 상태의 전압 레벨 사이의 전압 레벨을 갖는 제3의 전압 상태의 사이에서 천이하고,

[0277] 상기 제어부는, 상기 3개의 송신 신호 중, 상기 제1의 전압 상태 및 상기 제2의 전압 상태를 유지하는 송신 신호에 대해 앰페시스를 행하여야 할 것으로 판단하는 (12) 또는 (13)에 기재된 송신 장치.

[0278] (15) 상기 제어부는, 상기 3개의 송신 신호 중, 상기 제3의 전압 상태를 유지하는 송신 신호에 대해 앰페시스를 행하여야 할 것이 아니라고 판단하는 (14)에 기재된 송신 장치.

[0279] (16) 상기 송신부는, 복수의 송신 신호를 생성하고,

[0280] 상기 제어부는, 상기 복수의 송신 신호에 대해 앰페시스를 행하는지의 여부를 각각 판단하는 (1) 내지 (15)에 기재된 송신 장치.

[0281] (17) 상기 송신부는, 복수의 송신 신호를 생성하고,

[0282] 상기 제어부는, 상기 복수의 송신 신호에 대해 앰페시스를 행하는지의 여부를 일괄하여 판단하는 (1) 내지 (15)에 기재된 송신 장치.

[0283] (18) 송신 심볼의 시퀀스를 나타내는 데이터 신호에 의거하여 1 또는 복수의 송신 신호를 생성함과 함께, 각 송신 신호의 전압 레벨을 보정하는 송신부와,

[0284] 상기 데이터 신호에서의, 시간적으로 이웃하는 2개의 송신 심볼을 비교하고, 그 비교 결과에 의거하여 상기 전압 레벨을 보정하도록 상기 송신부를 제어하는 제어부를 구비한 것을 특징으로 하는 송신 장치.

[0285] (19) 1 또는 복수의 송신 신호를 수신하는 제1의 수신부와,

[0286] 상기 1 또는 복수의 송신 신호의 각각에 대해 이퀄라이즈를 행하는 이퀄라이저와,

[0287] 이퀄라이즈된 1 또는 복수의 송신 신호를 수신하는 제2의 수신부와,

[0288] 상기 제1의 수신부 또는 상기 제2의 수신부가 수신한 상기 1 또는 복수의 송신 신호의 천이 패턴에 의거하여, 상기 제1의 수신부의 제1의 출력 신호 또는 상기 제2의 수신부의 제2의 출력 신호를 선택 제어부를 구비한 것을 특징으로 하는 수신 장치.

[0289] (20) 상기 선택 제어부는, 상기 1 또는 복수의 송신 신호에서의 전압 상태의 시퀀스를 구하고, 시간적으로 이웃하는 2개의 전압 상태를 비교하고, 그 비교 결과에 의거하여, 상기 제1의 출력 신호 또는 상기 제2의 출력 신호를 선택하는 (19)에 기재된 수신 장치.

[0290] (21) 상기 제어부는, 상기 천이 패턴과, 이퀄라이즈를 행하는지의 여부를 나타내는 플래그와의 관계를 나타내는 루업 테이블을 가지며, 상기 루업 테이블에 의거하여, 상기 제1의 출력 신호 또는 상기 제2의 출력 신호를 선택하는 (19)에 기재된 수신 장치.

[0291] (22) 상기 이퀄라이저는, 상기 송신 신호의 고주파 성분을 크게 하도록 이퀄라이즈를 행하는 (19)에 기재된 수신 장치.

[0292] (23) 상기 1 또는 복수의 송신 신호는, 3개의 송신 신호이고,

[0293] 각 송신 신호는, 제1의 전압 상태와, 제2의 전압 상태와, 상기 제1의 전압 상태의 전압 레벨과 상기 제2의 전압 상태의 전압 레벨 사이의 전압 레벨을 갖는 제3의 전압 상태의 사이에서 천이하는 (19)에 기재된 수신 장치.

[0294] (24) 1 또는 복수의 송신 신호를 송신하는 송신 장치와,

[0295] 상기 1 또는 복수의 송신 신호를 수신하는 수신 장치를 구비하고,

- [0296] 상기 송신 장치는,

- [0297] 데이터 신호에 의거하여, 선택적으로 엠파시스를 행함에 의해 상기 1 또는 복수의 송신 신호를 생성하는 송신부와,

- [0298] 상기 데이터 신호의 천이 패턴에 의거하여 엠파시스를 행하는지의 여부를 판단하고 상기 송신부를 제어하는 제어부를 갖는 것을 특징으로 하는 통신 시스템.

- [0299] (25) 상기 제어부는, 상기 천이 패턴과, 엠파시스를 행하는지의 여부를 나타내는 플래그와의 관계를 나타내는 루크 테이블을 가지며, 상기 루크 테이블에 의거하여, 엠파시스를 행하는지의 여부를 판단하고,

- [0300] 상기 수신 장치는, 상기 1 또는 복수의 송신 신호를 수신하는 수신부와,

- [0301] 상기 수신부가 수신한 상기 1 또는 복수의 송신 신호에 의거하여, 제어 신호를 생성하는 제어 신호 생성부를 또한 가지며,

- [0302] 상기 송신 장치는, 상기 제어 신호에 의거하여 상기 루크 테이블을 프로그램하는 테이블 설정부를 또한 갖는 (25)에 기재된 통신 시스템.

- [0303] (26) 1 또는 복수의 송신 신호를 송신하는 송신 장치와,

- [0304] 상기 1 또는 복수의 송신 신호를 수신하는 수신 장치를 구비하고,

- [0305] 상기 송신 장치는, 데이터 신호에 의거하여, 선택적으로 엠파시스를 행함에 의해 상기 1 또는 복수의 송신 신호를 생성하는 송신부와,

- [0306] 상기 데이터 신호의 천이 패턴에 의거하여 엠파시스를 행하는지의 여부를 판단하고 상기 송신부를 제어하는 제어부를 가지며,

- [0307] 상기 수신 장치는,

- [0308] 상기 1 또는 복수의 송신 신호를 수신하는 제1의 수신부와,

- [0309] 상기 1 또는 복수의 송신 신호의 각각에 대해 이퀄라이즈를 행하는 이퀄라이저와,

- [0310] 이퀄라이즈된 1 또는 복수의 송신 신호를 수신하는 제2의 수신부와,

- [0311] 상기 제1의 수신부 또는 상기 제2의 수신부가 수신한 상기 1 또는 복수의 송신 신호의 천이 패턴에 의거하여, 상기 제1의 수신부의 제1의 출력 신호 또는 상기 제2의 수신부의 제2의 출력 신호를 선택하는 선택 제어부를 갖는 통신 시스템.

- [0312] 이상, 본 발명의 실시예를 도면을 참조하여 상술하여 왔지만, 구체적인 구성은 이 실시예에 한 정되는 것이 아니라, 본 발명의 요지를 일탈하지않는 범위의 설계의 변경 등이 있더라도 본 발명에 포함된다.

### 부호의 설명

[0313] 1, 1E, 2 : 통신 시스템

9A~9C : 전송로

10, 10B, 10E, 40 : 송신 장치

11, 11B : 신호 생성부

12 : 레지스터

13~15, 14B, 15B : 플립플롭

16E : LUT 생성부

19, 19B, 59 : LUT

20, 20B, 50 : 송신부

21 : 출력 제어부

22A~22C : 출력부

23 : 엠파시스 제어부

24A~24C : 출력부

25, 26 : 트랜지스터

27, 28 : 저항 소자

30, 30E, 60 : 수신 장치

31A~31C : 저항 소자

32A~32C : 앰플리파이어

33 : 클록 생성부

34, 35 : 플립플롭

36, 36E : 신호 생성부

37E : 패턴 검출부

61 : 이퀄라이저

62, 63 : 수신부

64 : 레지스터

65 : 신호 생성부

66, 67 : FIFO 메모리

68 : 셀렉터

100, 110 : 심볼 판정부

120, 130, 140, 150, 160, 170 : 논리 회로

121~125 : 논리곱 회로

180 : 논리합 회로

AB, BC, CA, AB2, BC2, CA2 : 차분

CS, CS2, NS, PS2 : 심볼

EA~EC, EE, EA2~EC2, EE2, SEL, SIGA~SIGC, SIGA2~SIGC2, S1, S2, RxF, RxR, RxP, RxF1, RxR1, RxP1, RxF2, RxR2, RxP2, TxF, TxR, TxP : 신호

DET: 검출 신호

EM : 아이 마스크

SH, SL, SM : 전압 상태

RxCK, RxCK1, RxCK2, TxCK : 클록

TinA, TinB, TinC : 입력단자

TJ : 저터

TouTA, TouTB, TouTC : 출력 단자

VH : 고레벨 전압

VL : 저레벨 전압

VM : 중레벨 전압

V1 : 전압

**도면****도면1****도면2**

도면3

도면4

도면5

도면6

## 도면7

## 도면8

| CS | TxF, TxR, TxP | NS | EA, EB, EC |

|----|---------------|----|------------|

| +x | 000           | +z | 101        |

|    | 001           | -z | 101        |

|    | 010           | +y | 011        |

|    | 011           | -y | 011        |

|    | 100           | -x | 110        |

| +y | 000           | +x | 110        |

|    | 001           | -x | 101        |

|    | 010           | +z | 101        |

|    | 011           | -z | 101        |

|    | 100           | -y | 011        |

| +z | 000           | +y | 011        |

|    | 001           | -y | 011        |

|    | 010           | +x | 110        |

|    | 011           | -x | 110        |

|    | 100           | -z | 101        |

| -x | 000           | -z | 101        |

|    | 001           | +z | 101        |

|    | 010           | -y | 011        |

|    | 011           | +y | 011        |

|    | 100           | +x | 110        |

| -y | 000           | -x | 110        |

|    | 001           | +x | 110        |

|    | 010           | -z | 101        |

|    | 011           | +z | 101        |

|    | 100           | +y | 011        |

| -z | 000           | -y | 011        |

|    | 001           | +y | 011        |

|    | 010           | -x | 110        |

|    | 011           | +x | 110        |

|    | 100           | +z | 101        |

## 도면9a

도면9b

도면9c

도면9d

도면9e

도면10a

도면 10b

도면 10c

도면 10d

도면 10e

도면 11a

도면11b

도면11c

도면11d

도면11e

도면12a

도면 12b

도면 12c

도면 12d

도면 12e

## 도면13

## 도면14

## 도면15

## 도면16

## 도면17

도면18

## 도면19

| CS | TxF, TxR, TxP | NS | EA, EB, EC |

|----|---------------|----|------------|

| +x | 000           | +z | 101        |

|    | 001           | -z | 000        |

|    | 010           | +y | 011        |

|    | 011           | -y | 000        |

|    | 100           | -x | 000        |

| +y | 000           | +x | 110        |

|    | 001           | -x | 000        |

|    | 010           | +z | 101        |

|    | 011           | -z | 000        |

|    | 100           | -y | 000        |

| +z | 000           | +y | 011        |

|    | 001           | -y | 000        |

|    | 010           | +x | 110        |

|    | 011           | -x | 000        |

|    | 100           | -z | 000        |

| -x | 000           | -z | 101        |

|    | 001           | +z | 000        |

|    | 010           | -y | 011        |

|    | 011           | +y | 000        |

|    | 100           | +x | 000        |

| -y | 000           | -x | 110        |

|    | 001           | +x | 000        |

|    | 010           | -z | 101        |

|    | 011           | +z | 000        |

|    | 100           | +y | 000        |

| -z | 000           | -y | 011        |

|    | 001           | +y | 000        |

|    | 010           | -x | 110        |

|    | 011           | +x | 000        |

|    | 100           | +z | 000        |

도면20

## 도면21

| CS | TxF, TxR, TxP | NS | EE |

|----|---------------|----|----|

| +x | 000           | +z | 1  |

|    | 001           | -z | 0  |

|    | 010           | +y | 1  |

|    | 011           | -y | 0  |

|    | 100           | -x | 0  |

| +y | 000           | +x | 1  |

|    | 001           | -x | 0  |

|    | 010           | +z | 1  |

|    | 011           | -z | 0  |

|    | 100           | -y | 0  |

| +z | 000           | +y | 1  |

|    | 001           | -y | 0  |

|    | 010           | +x | 1  |

|    | 011           | -x | 0  |

|    | 100           | -z | 0  |

| -x | 000           | -z | 1  |

|    | 001           | +z | 0  |

|    | 010           | -y | 1  |

|    | 011           | +y | 0  |

|    | 100           | +x | 0  |

| -y | 000           | -x | 1  |

|    | 001           | +x | 0  |

|    | 010           | -z | 1  |

|    | 011           | +z | 0  |

|    | 100           | +y | 0  |

| -z | 000           | -y | 1  |

|    | 001           | +y | 0  |

|    | 010           | -x | 1  |

|    | 011           | +x | 0  |

|    | 100           | +z | 0  |

도면22

## 도면23

| CS | TxF, TxR, TxP | NS | EA, EB, EC |

|----|---------------|----|------------|

| +x | 000           | +z | 000        |

|    | 001           | -z | 100        |

|    | 010           | +y | 000        |

|    | 011           | -y | 010        |

|    | 100           | -x | 000        |

| +y | 000           | +x | 000        |

|    | 001           | -x | 010        |

|    | 010           | +z | 000        |

|    | 011           | -z | 001        |

|    | 100           | -y | 000        |

| +z | 000           | +y | 000        |

|    | 001           | -y | 001        |

|    | 010           | +x | 000        |

|    | 011           | -x | 100        |

|    | 100           | -z | 000        |

| -x | 000           | -z | 000        |

|    | 001           | +z | 100        |

|    | 010           | -y | 000        |

|    | 011           | +y | 010        |

|    | 100           | +x | 000        |

| -y | 000           | -x | 000        |

|    | 001           | +x | 010        |

|    | 010           | -z | 000        |

|    | 011           | +z | 001        |

|    | 100           | +y | 000        |

| -z | 000           | -y | 000        |

|    | 001           | +y | 001        |

|    | 010           | -x | 000        |

|    | 011           | +x | 100        |

|    | 100           | +z | 000        |

## 도면24a

도면24b

도면24c

도면24d

도면24e

도면25a

도면25b

도면25c

도면25d

도면25e

도면26

도면27

도면28

## 도면29

## 도면30

도면31

도면32

## 도면33

도면34

## 도면35

도면36

도면37

도면38

도면39

도면40