(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 698 15 372 T2 2004.04.29

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 025 565 B1

(21) Deutsches Aktenzeichen: 698 15 372.3

(86) PCT-Aktenzeichen: PCT/US98/21939

(96) Europäisches Aktenzeichen: 98 953 641.2

(87) PCT-Veröffentlichungs-Nr.: WO 99/022376

(86) PCT-Anmeldetag: 20.10.1998

(97) Erstveröffentlichung durch das EPA: 09.08.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 04.06.2003

(47) Veröffentlichungstag im Patentblatt: 29.04.2004

(51) Int Cl.<sup>7</sup>: G11C 7/14

F23N 5/10

(30) Unionspriorität:

959681 24.10.1997 US

(84) Benannte Vertragsstaaten:

DE, FR, IT, NL

(73) Patentinhaber:

Artisan Components, Inc., Sunnyvale, Calif., US

(72) Erfinder:

KORNACHUK, P., Steve, Kanata, CA; BECKER, T.,

Scott, San Jose, US

(74) Vertreter:

LEINWEBER & ZIMMERMANN, 80331 München

(54) Bezeichnung: SELBSTGETAKTE HOCHGESCHWINDIGKEITSPEICHERSCHALTUNG UND VERFAHREN ZU IH-RERIMPLEMENTIERUNG

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

### HINTERGRUND DER ERFINDUNG

#### 1. GEBIET DER ERFINDUNG

[0001] Die vorliegende Erfindung bezieht sich im Allgemeinen auf integrierte Schaltungen, und im Besonderen auf Verfahren und Vorrichtungen für verbesserte Speicherschaltungen mit Eigen-Taktgeber.

#### 2. BESCHREIBUNG DES STANDS DER TECHNIK

[0002] Halbleiter-Speicherkerne sind im Allgemeinen in einem Matrix-Format angeordnet, so dass jede einzelne Kernzelle durch eine Wortleitung und ein Paar differentieller Bitleitungen gekoppelt ist. Um auf Daten zugreifen zu können, die in einer ausgewählten Kernzelle gespeichert sind, ist um einen Speicherkerne üblicherweise eine zugehörige Speicherzugriff-Schaltungsanordnung vorgesehen. Einige der wichtigsten Speicherzugriff-Schaltungsanordnungen umfassen z. B. typischerweise eine Adressier-Schaltungsanordnung zum Auswählen einer Kernzelle, Wortleitungstreiber zum Ansteuern einer ausgewählten Wortleitung und Leseverstärker zum Verstärken des von der ausgewählten Kernzelle zu lesenden Signals.

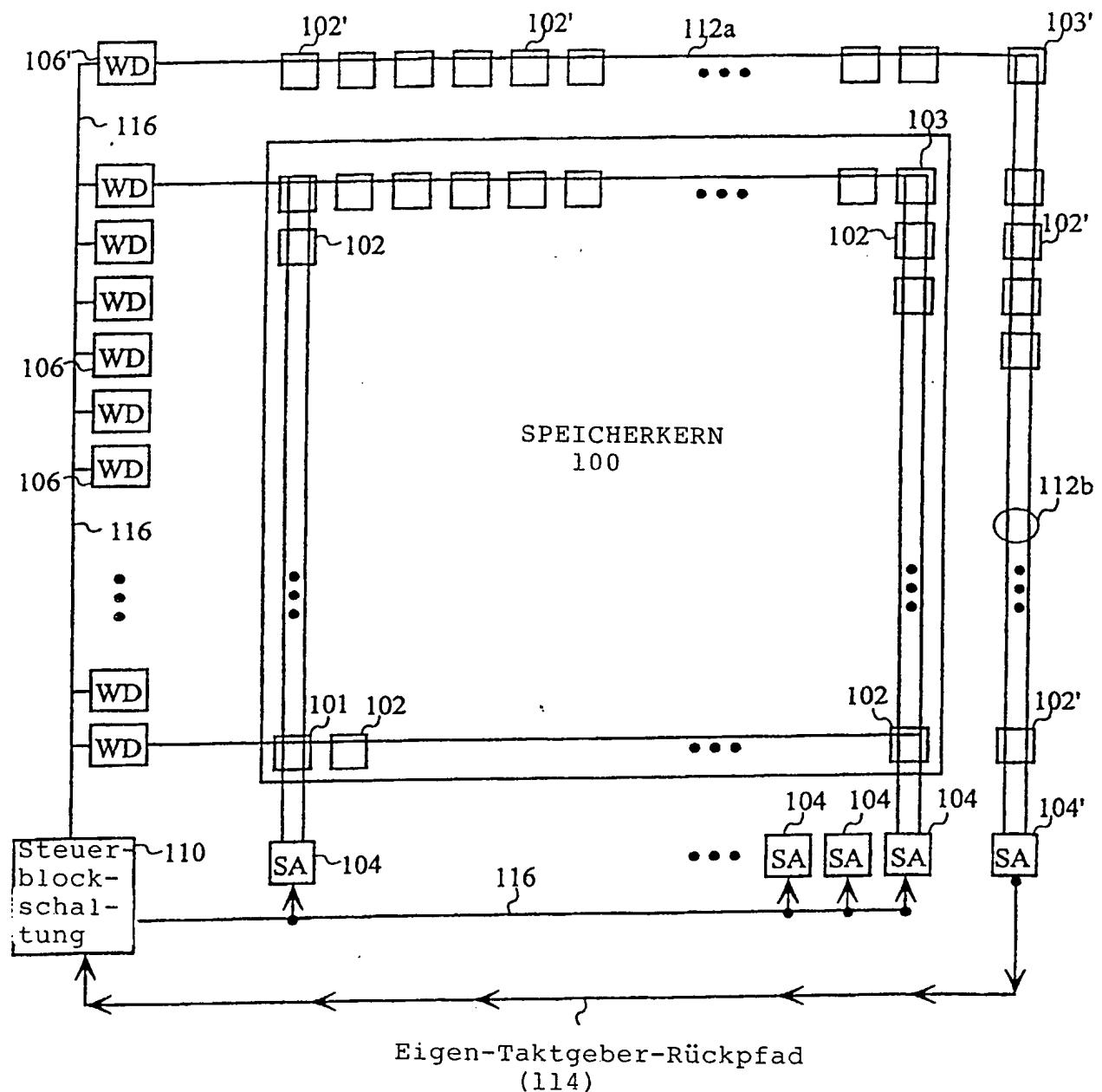

[0003] Zum leichteren Verständnis zeigt **Fig. 1** ein Blockschaltbild einer Speicherschaltung, die einen Speicherkerne **100** und zugehörige Zugriffs-Schaltungsanordnungen aufweist. Wie bei herkömmlichen Speicherkernekonfigurationen ist eine Vielzahl von Kernzellen **102** in einem Matrix-Format über den gesamten Speicherkerne **100** angeordnet. In diesem Beispiel wird eine Steuerblockschaltung **110** verwendet, um den Zugriff zu ausgewählten Speicherkernezellen **102** durch die Verwendung von Wortleitungstreibern **106** und Leseverstärkern (SA, sense amplifiers) **104** zu kontrollieren.

[0004] Die Steuerblockschaltung **110** ist in diesem Beispiel so konfiguriert, dass sie ein Signal erzeugt, das durch eine Anstiegsflanke des Signals **116** einen ausgewählten Wortleitungstreiber **106** auslöst. Wenn es beim Signal **116** zu einer Abfallflanke kommt (d. h. zu einem Zeitpunkt, der durch eine herkömmliche Eigen-Taktgeber-Architektur wie untenstehend beschrieben bestimmt wird), löst das Signal **116** das Lesen von Daten durch einen der ausgewählten Leseverstärkern **104** aus. Wie dargestellt sind die Wortleitungstreiber **106** durch den Einsatz von Wortleitungen mit jeder der Kernzellen **102** verbunden, die jede der Kernzellen **102** in einer horizontalen Richtung miteinander verbinden. Auf ähnliche Art und Weise sind die Leseverstärkern **104** in vertikaler Richtung durch die Verwendung von differentiellen Bitleitungen mit jeder der Kernzellen **102** verbunden.

[0005] In einer herkömmlichen Speicherschaltungsanordnung wird eine Eigen-Taktgeber-Architektur verwendet, die es einer Speicherschaltung ermög-

licht, zu bestimmen, wann der Leseverstärker **104** mit dem Lesen von Daten von den Kernzellen **102** im Speicherkerne **100** beginnen soll. Eigen-Taktgeber-Architekturen werden im Allgemeinen dazu benutzt, eine Standardverzögerung (d. h. eine Verzögerung, die normalerweise der Worst-case-Zeitverzögerung für einen gegebenen Kern entspricht) zu nähern, die herangezogen wird, wenn ein Zugriff auf eine beliebige Kernzelle **102** erfolgt. Die Eigen-Taktgeber-Architektur ist im Allgemeinen erforderlich, da die eigentliche Zeitverzögerung einer bestimmten Kernzelle **102** je nach Position der jeweiligen Kernzelle **102** unterschiedlich ist. Als Beispiel ist eine Kernzelle **103** an der von einem gegebenen Wortleitungstreiber **106** und einem gegebenen Leseverstärker **104** am weitesten entfernten Position angeordnet.

[0006] Aus diesem Grund ergibt sich aus der der Wortleitung zugeordneten RC-Verzögerung, welche Wortleitung den Wortleitungstreiber **106** mit der Kernzelle **103** koppelt, und der den Bitleitungen zugeordneten RC-Verzögerung, welche Bitleitungen einen Leseverstärker **104** mit der Kernzelle **103** koppeln, eine gemeinsame RC-Verzögerung, die größer ist als jede andere Kernzelle **102** im Speicherkerne **100**. Die zusammengesetzte RC-Verzögerung der Wortleitung und der Bitleitungen z. B., die mit einer Kernzelle **101** gekoppelt sind, wird kleiner sein als jede andere Kernzelle, die im Speicherkerne **100** angeordnet ist. Die Eigen-Taktgeber-Architektur, die einen Modell-Wortleitungstreiber **106'**, Kernzellen **102'**, eine Modell-Kernzelle **103'**, eine Modell-Wortleitung **112a**, Modell-Bitleitungen **112b**, einen Leseverstärker **104'** und einen Eigen-Taktgeber-Rückpfad **114** umfasst, dient daher dazu, die oben enrrähnte Standardverzögerungszeit festzusetzen.

[0007] Dementsprechend eignet sich die Eigen-Taktgeber-Architektur sehr gut dazu, abzuschätzen, wann ein ausreichender Bitleitungs-Ausgleich erreicht worden ist (d. h. aufgrund der Worst-case-Modell-Kernzelle **103'**), um eine Leseverstärkung korrekt durchführen zu können, um die Daten einer gegebenen Kernzelle **102** im Speicherkerne **100** zu lesen.

[0008] Beim Betreiben der Schaltung löst die Steuerblockschaltung am Modell-Wortleitungstreiber **106'** ein Auswahlsignal **116** aus, um auf die Modell-Kernzelle **103'** zuzugreifen. Wenn auf die Modell-Kernzelle **103'** zugegriffen worden ist, wird durch die Modell-Bitleitungen **112b**, den Leseverstärker **104'** und entlang des Eigen-Taktgeber-Rückpfads **114** ein Signal übermittelt, das an die Steuerblockschaltung **110** übertragen wird.

[0009] Ein besonderes Problem bei herkömmlichen Eigen-Taktgeber-Architekturen ist es, dass die Speicherschaltung zum Lesen der Daten schon bereit ist, sobald der Leseverstärker **104'** das Signal von der Modell-Kernzelle **103'** empfangen hat. Der zusätzliche Eigen-Taktgeber-Rückpfad **114** fügt jedoch notwendigerweise eine weitere RC-Verzögerung zur RC-Verzögerung der Modell-Wortleitung **112a** und

der Modell-Bitleitung **112b** hinzu. Diese zusätzliche durch den Eigen-Taktgeber-Rückpfad **114** eingeführte RC-Verzögerung verlangsamt jedoch einen Speicher-Zugriff-Schritt. Die Steuerblockschaltung **110** wird also kein Lesebereitschaftssignal **116** an einen gegebenen Leseverstärker **104** abgeben, bis die Steuerblockschaltung **110** das Signal vom Eigen-Takt-Rückpfad **114** erhält. Folglich ist die Leistung der gesamten Speicherschaltung bei Anwendungen, bei denen ein Hochgeschwindigkeits-Speicher-Zugriff erforderlich ist, aufgrund der zusätzlichen, durch den Eigen-Taktgeber-Rückpfad **114** eingeführten RC-Verzögerung beeinträchtigt.

[0010] Die EP-0432482, auf welcher der Oberbegriff zu Anspruch 1 beruht, offenbart einen RAM-Speicher, der eine Leer-Wortleitung mit demselben Muster und demselben Verknüpfungsglied wie die in RAM-Zellen vorgesehenen Wortleitungen aufweist, um diejenige der Wortleitungen zu detektieren, die bis zum Ende der Wortleitungen ausgewählt ist, und daraufhin einen Leseverstärker zu bedienen.

[0011] Angesichts der vorhergehenden Erläuterungen besteht Bedarf an einer Speicherschaltung mit Eigen-Taktgeber, die das Einführen unnötiger RC-Verzögerungen verhindert, wenn auf eine Worst-case-Modell-Kernzelle zugegriffen wird.

## ZUSAMMENFASSUNG DER ERFINDUNG

[0012] Allgemein gesagt erfüllt die vorliegende Erfindung diese Bedürfnisse, indem sie Verfahren und Vorrichtungen für Speicherschaltungen mit Eigen-Taktgeber bereitstellt, die unnötige RC-Verzögerungen eliminieren und Speicher-Zugriff-Schritte wesentlich beschleunigen. Es wird anerkannt werden, dass die vorliegende Erfindung auf unterschiedliche Arten umgesetzt werden kann, wie z. B. als Prozess, Apparatur, System, Vorrichtung oder Verfahren. Untenstehend werden mehrere Ausführungsformen der vorliegenden Erfindung beschrieben.

[0013] In einer Ausführungsform wird eine Speicherschaltung offenbart. Die Speicherschaltung beinhaltet einen Speicherkern, der eine Kernzellen-Matrix besitzt. Die Kernzellen-Matrix ist mit einer Vielzahl von Wortleitungen und einer Vielzahl von Bitleitungs-paaren verbunden. Die Speicherschaltung umfasst zudem einen Eigen-Taktgeber-Pfad, der eine Modell-Kernzelle aufweist, die an eine Modell-Wortleitung gekoppelt ist, die wiederum von einem Modell-Wortleitungstreiber angesteuert wird. Der Eigen-Taktgeber-Pfad beinhaltet ebenso einen Modell-Leseverstärker, der durch ein Modell-Bitleitungs-paar mit der Modell-Kernzelle gekoppelt ist. Die Modell-Wortleitung und das Modell-Bitleitungs-paar sind jeweils an eine Vielzahl von Leer-Kernzellen gekoppelt, um eine RC-Verzögerung einer Worst-case-Kernzelle der Kernzellen-Matrix anzunähern. Darüber hinaus ist die Modell-Wortleitung eine gefaltete Wortleitung, so dass die Modell-Wortleitung an einer Position endet, die sich nahe dem Modell-Wortlei-

tungstreiber befindet.

[0014] In einer anderen Ausführungsform wird ein Verfahren zur Herstellung einer Speicherschaltung mit Eigen-Taktgeber-Pfad offenbart. Das Verfahren beinhaltet das Bereitstellen eines Speicherkerns, der eine Kernzellen-Matrix aufweist. Das Verfahren umfasst zudem das Integrieren eines Eigen-Taktgeber-Pfads aus Kernzellen entlang einer Modell-Wortleitung und entlang eines Modell-Bitleitungs-paares. Die Modell-Wortleitung ist so gefaltet, dass eine Modell-Kernzelle im Wesentlichen an einem Ausgangspunkt der Modell-Wortleitung angeordnet ist und ein Endpunkt der Modell-Wortleitung mit der Modell-Kernzelle gekoppelt ist.

[0015] Die Aspekte und Vorteile der Endung werden aus der folgenden detaillierten Beschreibung und der Betrachtung der begleitenden Abbildungen ersichtlich, worin anhand von Beispielen die Prinzipien der Erfindung veranschaulicht werden.

## KURZBESCHREIBUNG DER ABBILDUNGEN

[0016] Die vorliegende Erfindung wird durch die folgende detaillierte Beschreibung zusammen mit den begleitenden Abbildungen besser verständlich, worin ähnliche Bezugszeichen ähnliche strukturelle Elemente bezeichnen.

[0017] **Fig. 1** zeigt ein Blockschaltbild einer Speicherschaltung, die einen Speicherkern und zugehörige Zugriff-Schaltungsanordnungen aufweist.

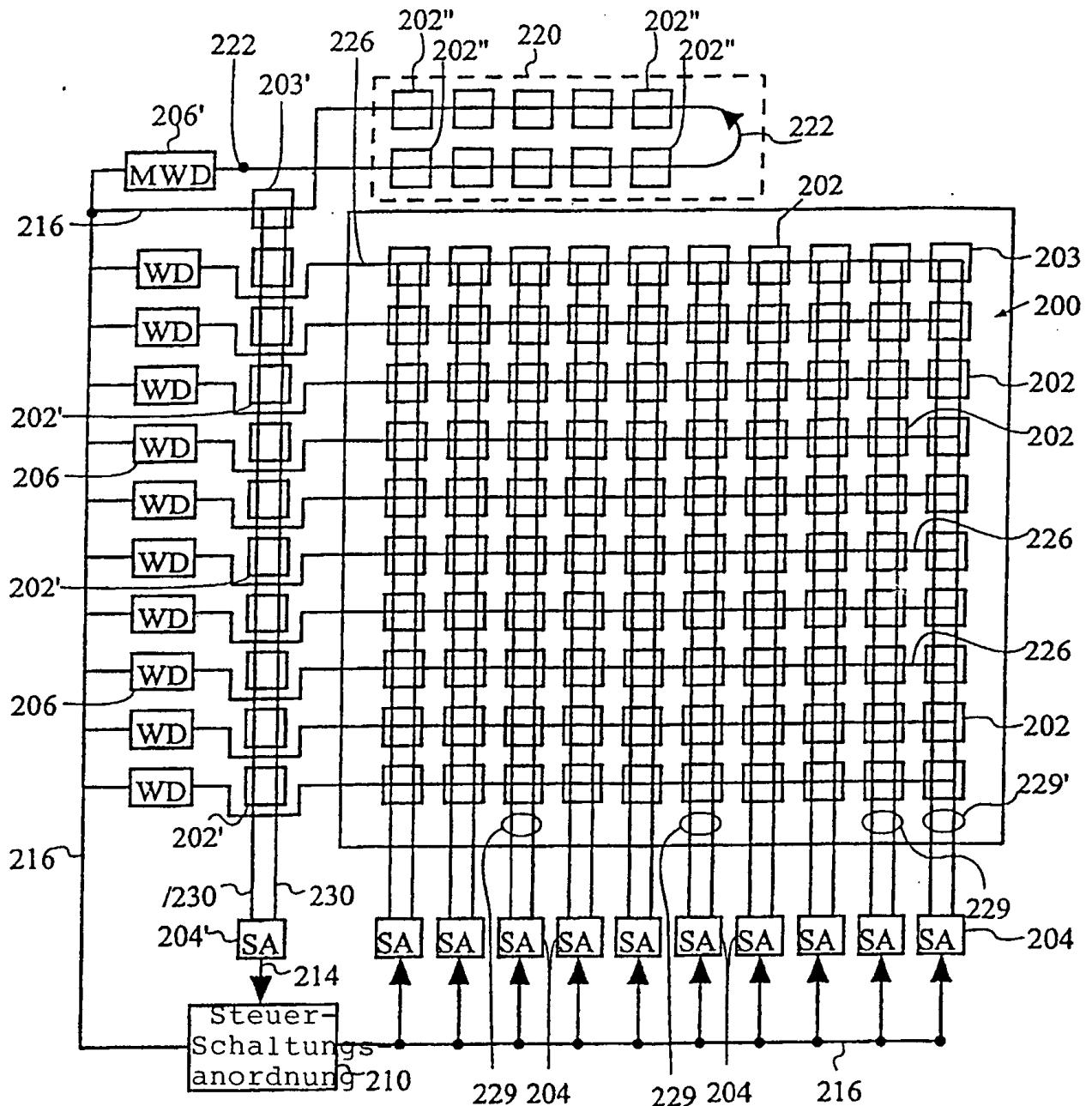

[0018] **Fig. 2A** zeigt eine Speicherschaltung, die einen Speicherkern besitzt, der eine Kernzellen-Matrix gemäß einer Ausführungsform der vorliegenden Erfindung beinhaltet.

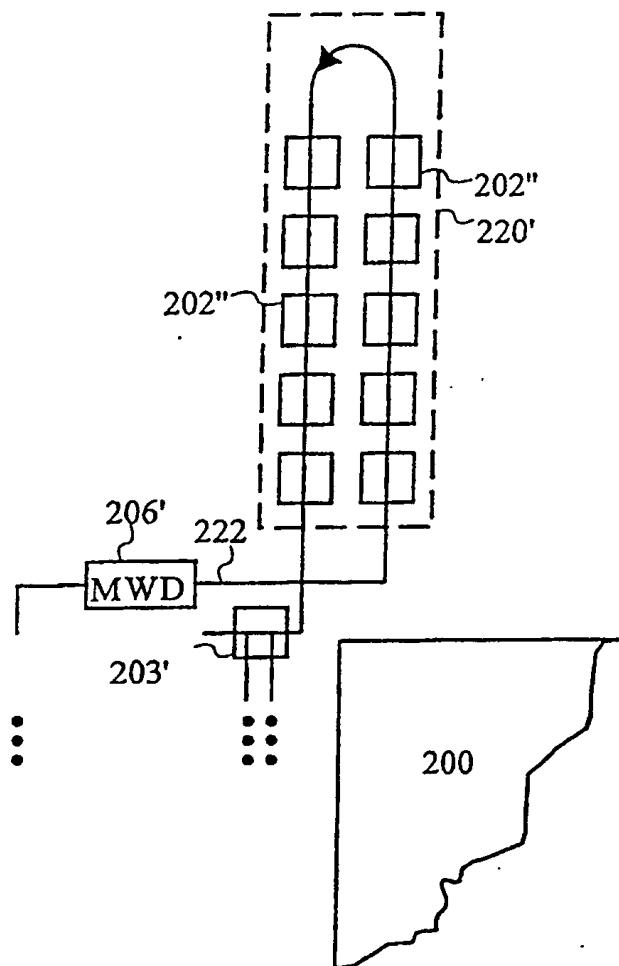

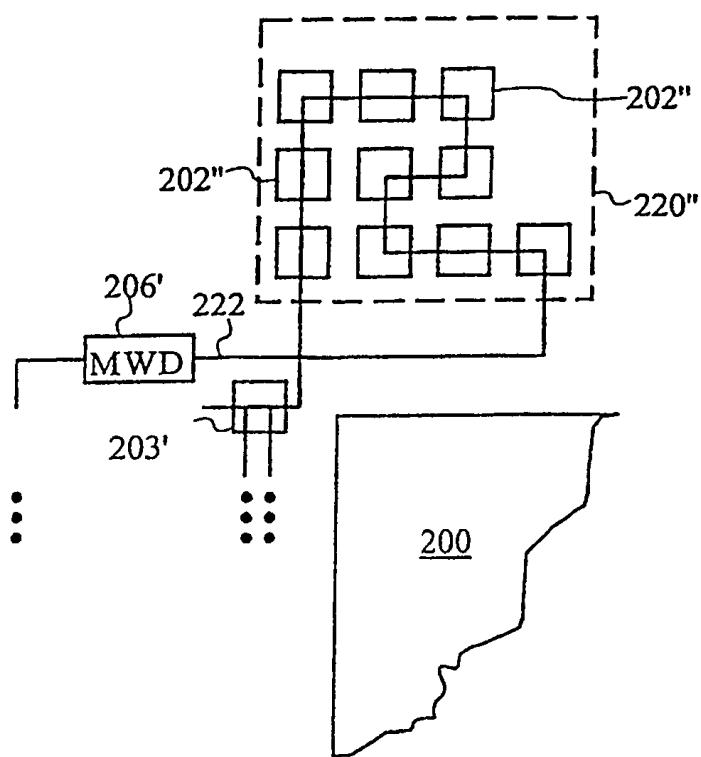

[0019] **Fig. 2B** und **2C** zeigen Anordnungen einer gefalteten Wortleitung gemäß einer alternativen Ausführungsform der vorliegenden Erfindung.

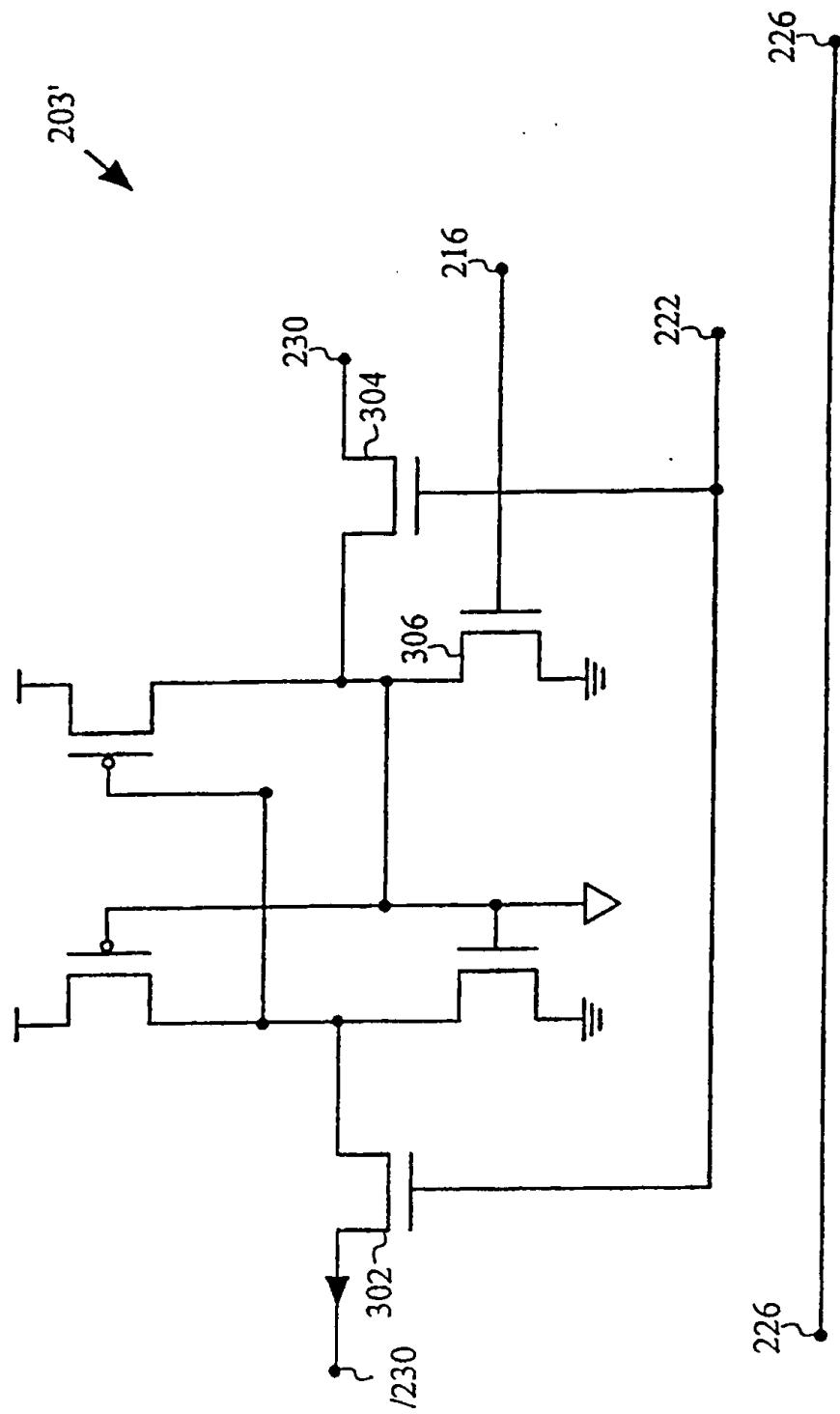

[0020] **Fig. 3** zeigt ein Beispiel einer Modell-Kernzelle gemäß einer Ausführungsform der vorliegenden Erfindung.

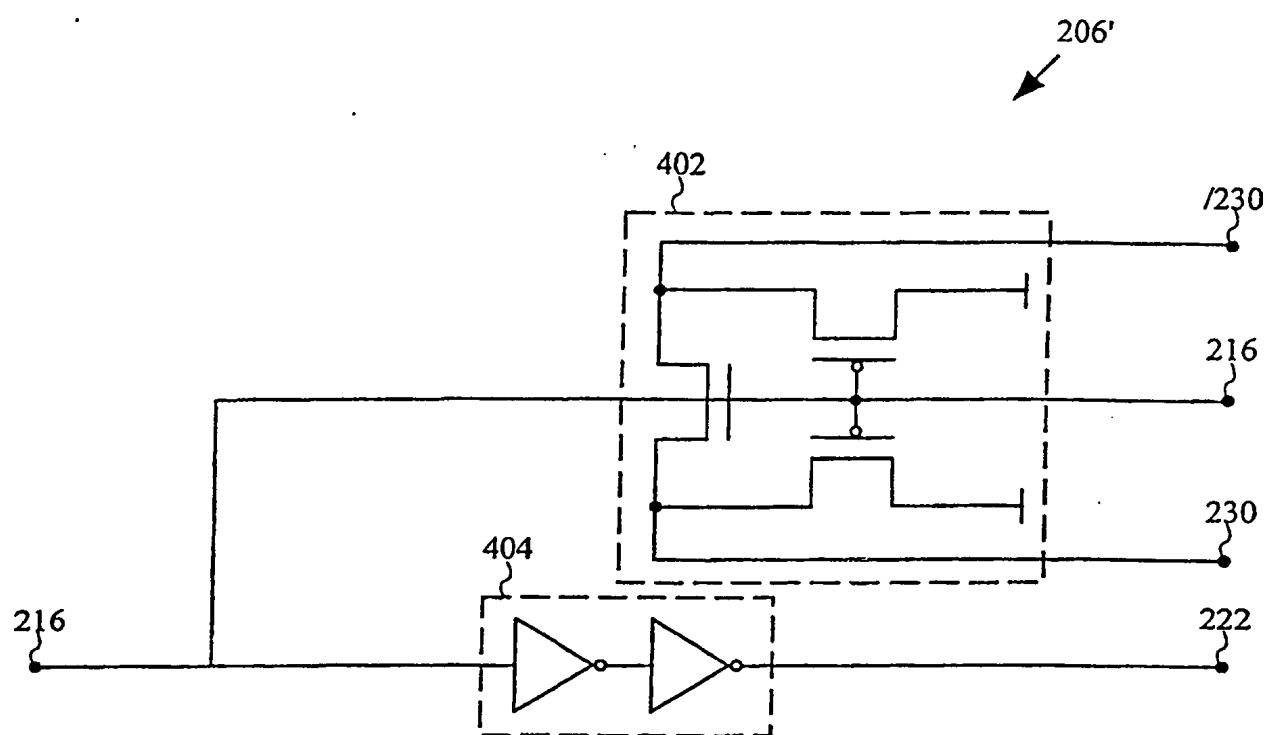

[0021] **Fig. 4** ist ein Beispiel eines Modell-Wortleitungstreibers wie in **Fig. 2A** oben dargestellt, gemäß einer Ausführungsform der vorliegenden Erfindung.

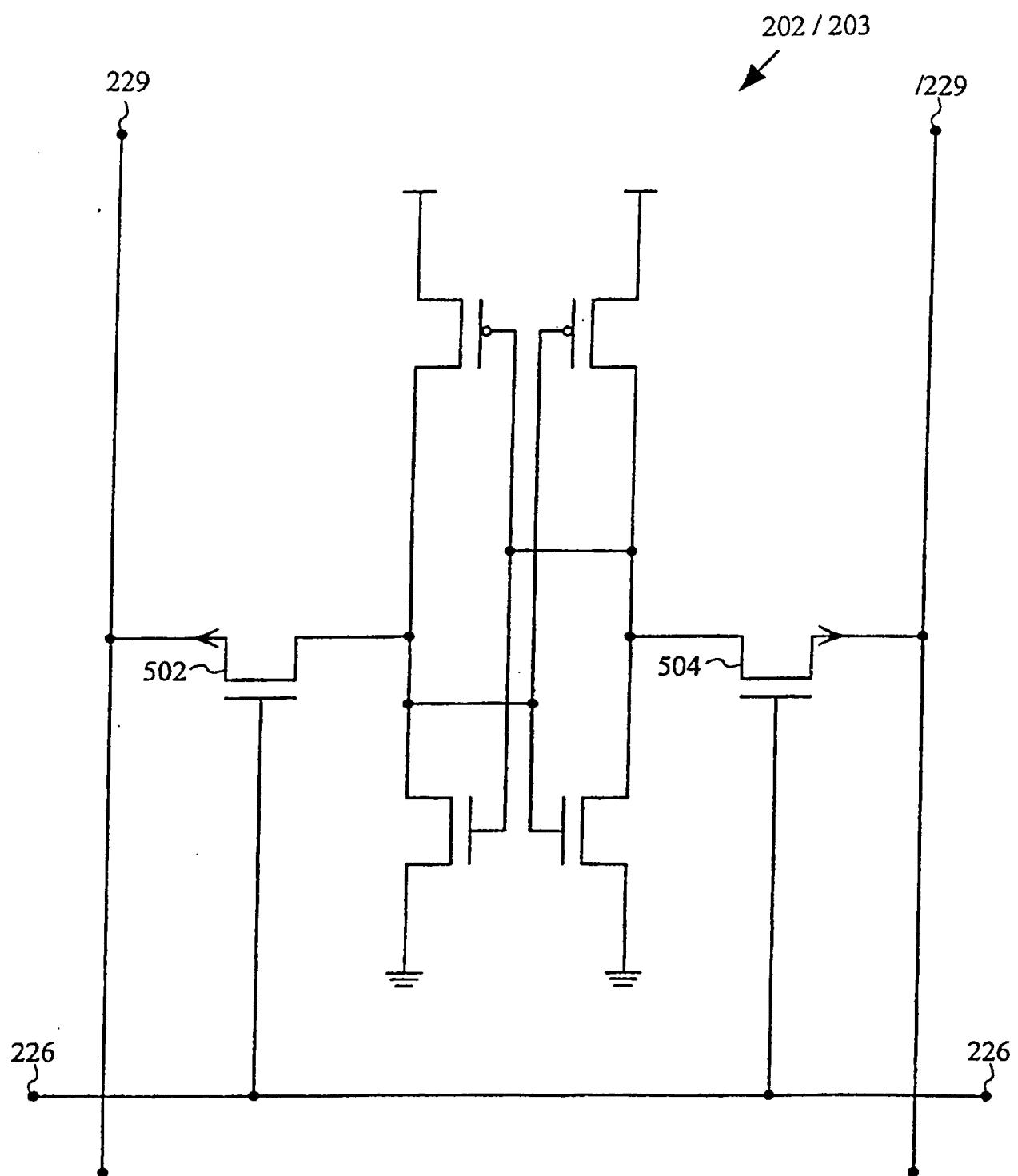

[0022] **Fig. 5A** zeigt ein Beispiel einer Kernzelle, die sich im Speicherkern gemäß einer Ausführungsform der vorliegenden Erfindung befindet.

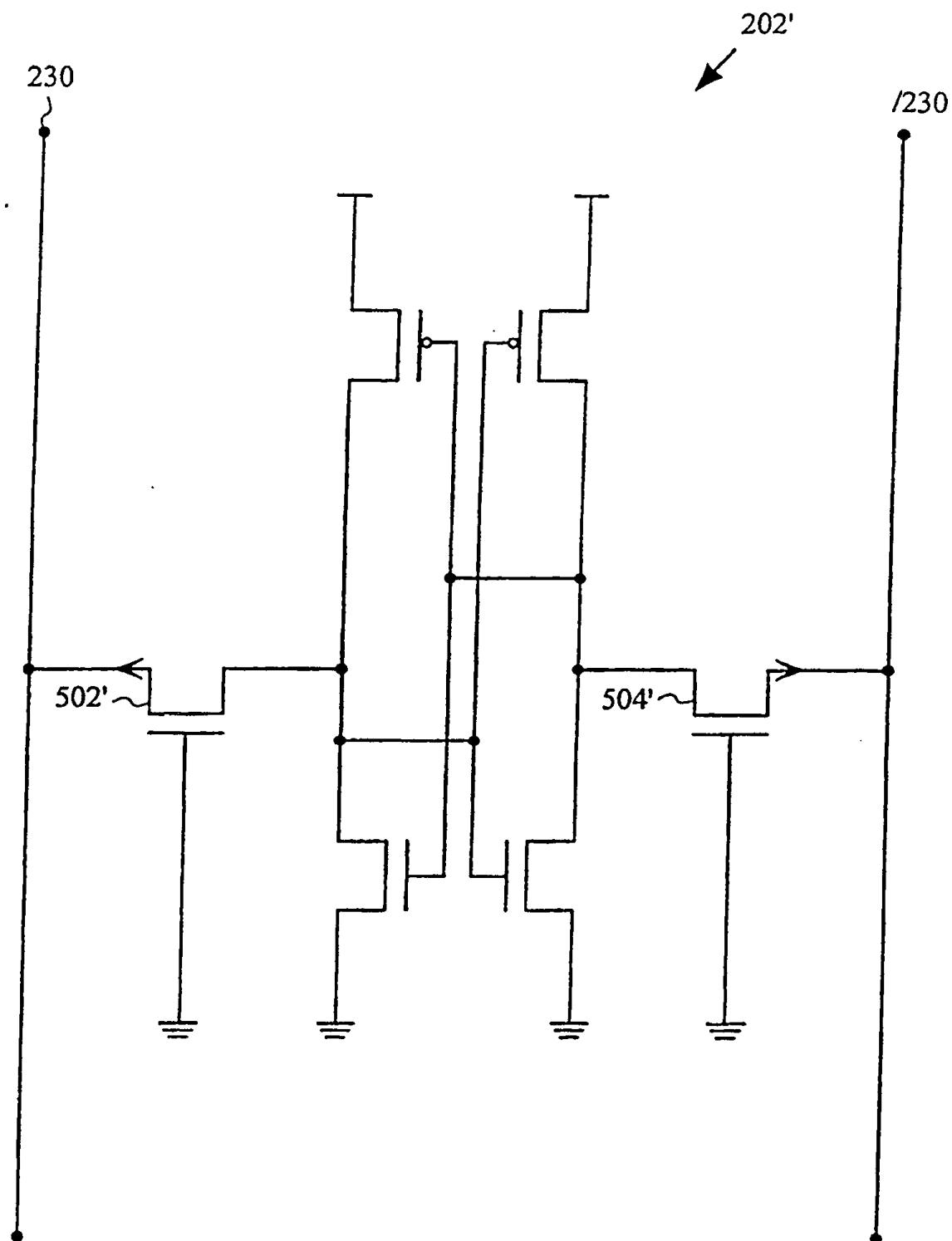

[0023] **Fig. 5B** zeigt ein Beispiel einer Kernzelle, die entlang der Modell-Bitleitungen gemäß einer Ausführungsform der vorliegenden Erfindung angeordnet ist.

[0024] **Fig. 5C** zeigt ein Beispiel einer Kernzelle, die entlang einer Modell-Wortleitung gemäß einer Ausführungsform der vorliegenden Erfindung angeordnet ist.

[0025] **Fig. 6** ist ein Beispielschaltungsdiagramm einer Steuerschaltung aus **Fig. 2A** gemäß einer Ausführungsform der vorliegenden Erfindung.

[0026] **Fig. 7** zeigt einen Modell-Pfad sowie ein Lese-Zeitgeberdiagramm 700 gemäß einer Ausführungsform der vorliegenden Erfindung.

## DETAILLIERTE BESCHREIBUNG DER BEVOR-ZUGTEN AUSFÜHRUNGSFORMEN

[0027] Es wird eine Erfindung für eine Speicherschaltung mit Eigen-Taktgeber offenbart, die unnötige RC-Verzögerungen eliminiert und Speicher-Zugriff-Schritte wesentlich beschleunigt. In der folgenden Beschreibung werden zahlreiche spezifische Details erläutert, um die vorliegende Erfindung umfassend verstehen zu können. Es wird jedoch für Fachleute auf dem Gebiet ersichtlich sein, dass in der Umsetzung der vorliegenden Erfindung auf manche oder sogar alle dieser Details verzichtet werden kann. Weithin bekannte Prozessschritte hingegen sind nicht detailliert ausgeführt worden, um ein Verstehen der vorliegenden Erfindung nicht unnötig zu erschweren.

[0028] **Fig. 2A** zeigt eine Speicherschaltung, die einen Speicherkerne **200** mit einer Kernzellen-Matrix **202** gemäß einer Ausführungsform der vorliegenden Erfindung aufweist. Wie dargestellt ist, sind die Kernzellen **202** durch Wortleitungen **226** in horizontaler Richtung mit Wortleitungstreibern **206** und durch Bitleitungen **229** in vertikaler Richtung mit Leseverstärkern **204** gekoppelt. Die Steuerschaltungsanordnung **210** wird ebenso als mit jedem der Wortleitungstreiber **206** und der Leseverstärker **204** gekoppelt dargestellt. In diesem Beispiel sind die Leseverstärker **204** als getrennte Blöcke veranschaulicht, wobei jedoch zu verstehen ist, dass ein Leseverstärker typischerweise eine Schaltung ist, die mit jeder der Bitleitungen **229** durch weithin bekannte Y-Decoder-Schaltungsanordnungen (nicht dargestellt) gekoppelt ist.

[0029] Wie bekannt ist, werden Y-Decoder zum Adressieren einer ausgewählten Spalte (d. h. Differenz-Bitleitungen) innerhalb des Speicherkerne **200** verwendet. Y-Decoder werden im Allgemeinen dazu eingesetzt, um die Seitenverhältnisse einer Speicher-Matrix durch Falten (d. h. Teilen) langer, adressierbarer Speicherspalten in mehrere kurze Speicherspalten zu verkleinern. Wenn diese einmal in mehrere Spalten geteilt worden sind, kann der Y-Decoder durch einen geeigneten Multiplexvorgang auf die adressierten Daten zugreifen.

[0030] In dieser Ausführungsform wird eine verbesserte Eigen-Taktgeber-Architektur offenbart, um mit dem Eigen-Taktgeber-Rückpfad **114**, wie er in der herkömmlichen Anordnung in **Fig. 1** verwendet wurde, verbundene Verzögerungen zu eliminieren. Wenn die RC-Verzögerungen von einer Wortleitung **222** und Differenz-Bitleitungen (**230**, **/230**) z. B. rasch durch ein Signal **214** (von dem Modell-Leseverstärker **204'**) an die Steuerschaltanordnung **210** übermittelt werden, wird unverzögerlich ein Lesebereitschaftssignal **216** wie in **Fig. 2A** dargestellt. übertragen. Die Eliminierung der RC-Verzögerung, die durch den Eigen-Taktgeber-Rückpfad herkömmlicher Anordnungen verursacht wird, wird in erster Linie durch eine gefaltete Wortleitung **220** ermöglicht.

[0031] Vorzugsweise schließt die gefaltete Wortlei-

tung **220** die Hälfte eines Sets an Kernzellen **202'** ein, die über der verbleibenden Hälfte angeordnet ist. Diese Anordnung stellt daher einen wirksamen Pfad bereit, um das Ende der Wortleitung **222** mit der Modell-Kernzelle **203'** zu verbinden, die sich nun ganz links oben vom Speicherkerne **200** befindet. Wie dargestellt ist, verbinden die Modell-Bitleitungen **230** und **/230** ein Set an Kernzellen **202'** miteinander, die zur Modell-Kernzelle **203'** führen. Wenn während des Betriebs die Steuerschaltungsanordnung **210** ein Wortleitungs-Freigabesignal mit einer Anstiegsflanke des Signals **216** an den Modell-Wortleitungstreiber **206'** übermittelt, wird die RC-Verzögerung lediglich für etwa den von der Wortleitung **222** und den Differenz-Bitleitungen **230** und **/230**, die zum Modell-Leseverstärker **204'** führen, durchlaufenden Pfad berechnet.

[0032] Zu diesem Zeitpunkt wird das Modell-Lesesignal **214** an die Steuerschaltungsanordnung **210** übermittelt. Wenn die Steuerschaltungsanordnung **210** das Signal **214** empfängt, leitet sie die Abfallflanke des Lesebereitschaftssignals **216** an den ausgewählten Leseverstärker **204** weiter. Es ist wichtig, festzustellen, dass die Eigen-Taktgeber-Architektur der vorliegenden Erfindung eine Standardverzögerung bereitstellt, die von allen Kernzellen **202** und der Kernzelle **203** des Speicherkerne **200** verwendet werden soll. Darüber hinaus ist die Standardverzögerung vorzugsweise nicht schlechter als die RC-Verzögerung des Worst-case-Falls für das Lesen der Kernzelle **203**.

[0033] **Fig. 2B** zeigt eine weitere Anordnung der gefalteten Wortleitung **220'** gemäß einer alternativen Ausführungsform der vorliegenden Erfindung. Wie dargestellt ist, ist die gefaltete Wortleitung **220'** im Vergleich zur gefalteten Wortleitung **220** aus **Fig. 2A** in einem 90° Winkel angeordnet. Diese Ausführungsform veranschaulicht, dass die gefaltete Wortleitung **220'** in einer beliebigen Art und Weise angeordnet werden kann, die das Layout für eine spezielle Anwendung geeignet macht, und muss nicht in einer horizontalen Ausrichtung vorgesehen sein. In **Fig. 2C** z. B. ist eine weitere Ausrichtungsmöglichkeit für eine gefaltete Wortleitung **220''** dargestellt. In diesem Beispiel ist die gefaltete Wortleitung **220''** in einer Anordnung angebracht, die das Anordnen anderer beliebiger Verknüpfungen in einer speziellen integrierten Schaltungsanordnung leichter durchführbar machen würde.

[0034] Es ist daher zu verstehen, dass die Art, in der die gefaltete Wortleitung angeordnet ist, unbedeutend ist, solange die gefaltete Wortleitung einen Endpfad der Wortleitung **222** vorsieht, der sich im Wesentlichen nahe des Ausgangs des Modell-Wortleitungstreibers **206'** befindet. Bei einer richtigen Anordnung wird keine übermäßige RC-Verzögerung in den Eigen-Taktgeber-Pfad eingeführt. Aus diesem Grund wird lediglich die repräsentative RC-Verzögerung der Modell-Wortleitung **222** und der Modell-Bitleitungen **230** und **/230** von der Steuerschaltungsanordnung

**210** herangezogen, um zu bestimmen, dass ein Leistungsbereitschaftssignal **216** an die gegebenen Leseverstärker **204** übermittelt werden soll.

[0035] **Fig. 3** zeigt ein Beispiel einer Modell-Kernzelle **203'** gemäß einer Ausführungsform der vorliegenden Erfindung. In dieser Ausführungsform ist eine Wortleitung **226** als eine Leitung dargestellt, die nicht mit der Modell-Kernzelle **203'** verbunden ist, sondern direkt in die Kernzellen **202** führt, die innerhalb des Speicherkerns **200** liegen. Die Modell-Wortleitung **222** ist jedoch mit einem Gate der Transistoren **302** und **304** gekoppelt. Ebenso dargestellt ist die Modell-Bitleitung **230**, die mit einem Anschluss des Transistors **304** verbunden ist, und die komplementäre Modell-Bitleitung **/230**, die mit einem Anschluss des Transistors **302** verbunden ist. Von der Steuerschaltungsanordnung **210** wird zudem ein Signal **216** an ein Gate eines Transistors **306** übermittelt. Im Allgemeinen ist die Modell-Kernzelle **203'** so konfiguriert, dass sie einen Pull-Down-Vorgang ausführt, der an die Pull-Down-Stärke einer Kernzelle **202** angenähert ist, die innerhalb eines Speicherkerns **200** liegt.

[0036] In einer weiteren Ausführungsform kann an der Modell-Kernzelle **203'** ein Feinabgleich vorgenommen werden, um die Pull-Down-Ansteuerung je nach Tiefe des jeweiligen Speicherkerns **200** zu erhöhen. Die Modell-Kernzelle **203'** kann z. B. durch mehr als eine Modell-Kernzelle ersetzt werden, um eine höhere Pull-Down-Stärke zu erzeugen, die für die Eliminierung jeglicher Verzögerungen, die durch die Steuerschaltungsanordnung **210** eingeführt werden können, oder von Verzögerungen, die mit dem Ansteuern größerer Speicherkerne verbunden sind, nützlich sein kann.

[0037] **Fig. 4** ist ein Beispiel für einen Modell-Wortleitungstreiber **206'** wie in **Fig. 2A** oben dargestellt gemäß einer Ausführungsform der vorliegenden Erfindung. Der Modell-Wortleitungstreiber **206'**, wie dargestellt, beinhaltet eine Vor-Ladungsschaltung **402**, die an die Modell-Bitleitungen **230** und **/230** sowie das Signal **216** gekoppelt ist. Ebenso veranschaulicht ist ein Puffer **404**, der das Signal **216** empfängt und ein gepuffertes Signal an die Modell-Wortleitung **222** abgibt. Im Allgemeinen wird der Modell-Wortleitungstreiber **206'**, wenn das Signal **216** auf HIGH geht (d. h. eine Anstiegsflanke erfährt), dazu veranlasst, einen Zugriffs-Schritt zu beginnen. Zudem ist der Puffer **404** mit ausreichend Verzögerung versehen, um die Verzögerung anzunähern, die durch Wortleitungstreiber **206** auftreten werden, die auf den Speicherkerne **200**, wie in **Fig. 2A** oben dargestellt, zugreifen.

[0038] **Fig. 5A** veranschaulicht ein Beispiel einer Kernzelle **202** und **203**, die sich im Speicherkerne **200** gemäß einer Ausführungsform der vorliegenden Erfindung befindet. Wie dargestellt ist, sind die komplementären Bitleitungen **229** und **/229** an Drainanschlüsse eines Paars von Durchlauf-Gate-Transistoren **502** bzw. **504** gekoppelt. Die Wortleitung **226** ist als an das Gate der Durchlauf-Gate-Transistoren **502**

und **504** gekoppelt gezeigt. Obwohl eine exemplarische Kernzelle **202/203** veranschaulicht ist, ist es zu verstehen, dass die Ausführungsformen der vorliegenden Erfindung auch auf andere Kernzellen und Speicherschaltungen anwendbar sind.

[0039] Die Ausführungsform der vorliegenden Erfindung kann auf eine beliebige Anzahl von Speicherschaltungen, wie ROM-Speicher-Schaltkreisen, RAM-Speicher-Schaltkreisen, SRAM-Speicher-Schaltkreisen, DRAM-Speicher-Schaltkreisen, EPROM-Speicher-Schaltkreisen, EEPROM-Speicher-Schaltkreisen etc., angewendet werden. Für weitere Informationen bezüglich Speicherschaltungen und Kernzellen kann auf das Buch „The Art of Electronics, 2<sup>nd</sup> Edition“ von Paul Horowitz und Winfield Hill, Seiten 812–820 (1996) verweisen werden. Diese Buch ist hierin durch Verweis eingeschlossen.

[0040] **Fig. 5B** ist ein Beispiel für eine Kernzelle **202'**, die entlang der Modell-Bitleitung gemäß einer Ausführungsform der vorliegenden Erfindung angeordnet ist. Wie dargestellt ist, ist die Bitleitung **230** mit einem Drainanschluss eines Durchlauf-Gate-Transistors **502'**, und die Bitleitung **/230** mit einem Drainanschluss eines Durchlauf-Gate-Transistors **504'** gekoppelt. In dieser Ausführungsform ist das Gate der Durchlauf-Gate-Transistoren **502'** und **504'** mit Erde verbunden. Jede der Kernzellen **202'** sind im Allgemeinen Leer-Kernzellen, die dazu verwendet werden, die auf den Bitleitungen **229'** des Speicherkerne **200** auftretende RC-Verzögerung anzunähern.

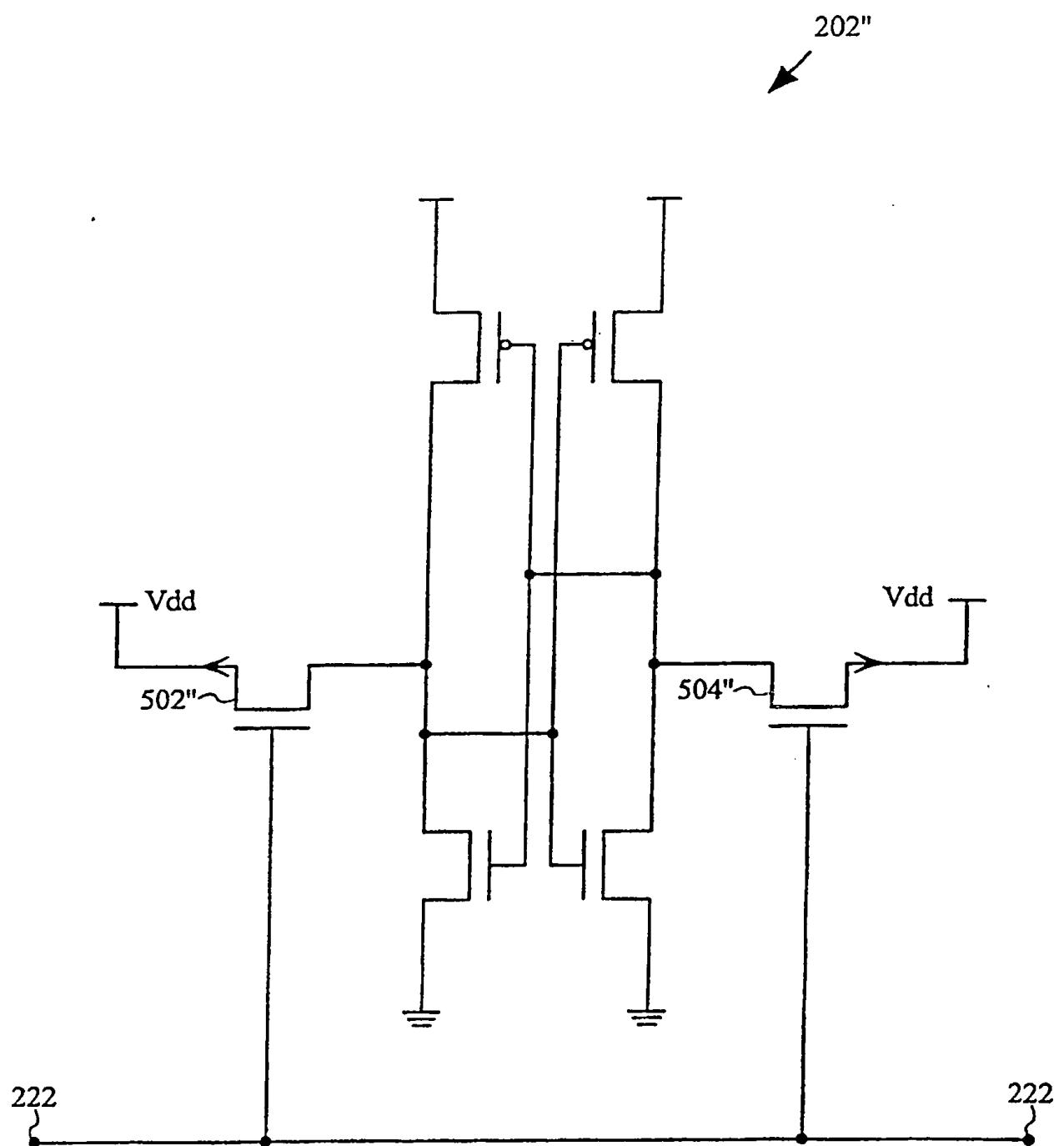

[0041] **Fig. 5C** zeigt ein Beispiel für eine Kernzelle **202''**, die entlang der Modell-Wortleitung **222** gemäß einer Ausführungsform der vorliegenden Erfindung angeordnet ist. Wie dargestellt ist, ist ein Drainanschluss eines Durchlauf-Gate-Transistors **502''** an Vdd, und ein Drainanschluss eines Durchlauf-Gate-Transistors **504''** an Vdd gekoppelt. In dieser Ausführungsform ist das Gate der Durchlauf-Gate-Transistoren **502''** und **504''** an die Modell-Wortleitung **222** gekoppelt. Jede der Kernzellen **202''** ist also im Allgemeinen eine Leer-Kernzelle, die dazu verwendet werden, die auf der Wortleitung **226** des Speicherkerne **200** auftretende RC-Verzögerung anzunähern.

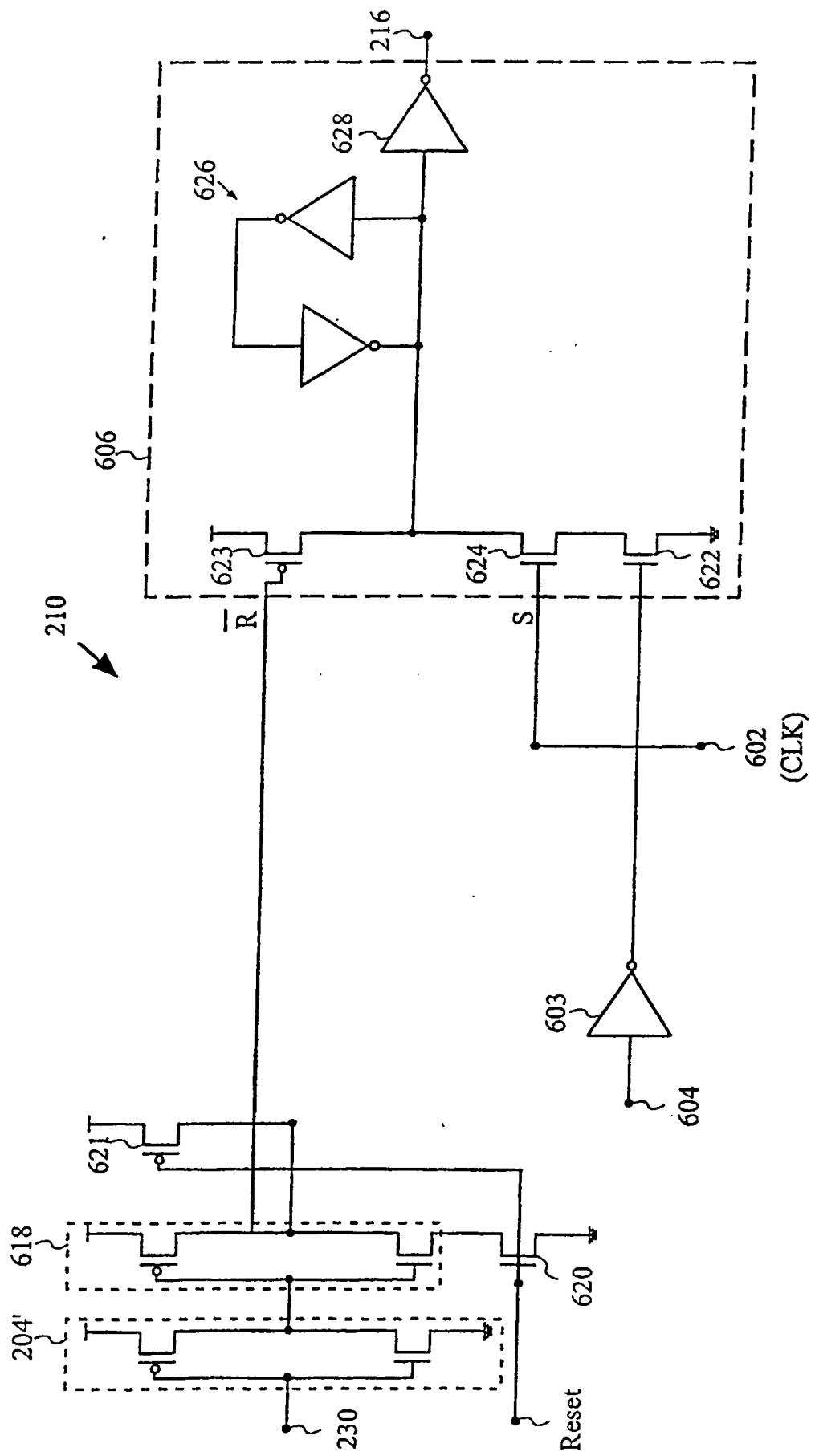

[0042] **Fig. 6** ist ein Beispielschaltungsdiagramm der Steuerschaltungsanordnung **210** aus **Fig. 2A** gemäß einer Ausführungsform der vorliegenden Erfindung. Die Steuerschaltungsanordnung **210** beinhaltet im Allgemeinen einen Modell-Leseverstärker **204'** sowie eine SET-/RESET-Latch-Schaltungsanordnung **606**. Die SET-/RESET-Latch-Schaltungsanordnung **606** umfasst im Allgemeinen einen Transistor **623**, der ein Reset(R)-Signal empfängt, sowie einen Transistor **624**, der ein SET(S)-Signal vom Taktgeber (CLK) **602** aufnimmt. Die SET-/RESET-Latch-Schaltungsanordnung **606** schließt ebenso einen Transistor **622** ein, dessen Gate mit dem Ausgang eines Puffers **603** gekoppelt ist, und der Puffer **603** weist einen Eingang **604** auf (d. h. einen Eingang, der eine Verzögerung der CLK **602** ist).

[0043] Weitere Bestandteile der SET-/RESET-Latch-Schaltungsanordnung **606** sind ein Latch **624** und ein Inverter **628**, der das Signal **216** erzeugt. Ebenfalls dargestellt ist ein Reset-Signal, das an ein Gate eines Transistors **620** sowie an ein Gate eines Transistors **621** übermittelt wird. In diesem Beispiel ist die Bitleitung **230** an den Modell-Leseverstärker **204'** gekoppelt, der als Inverter-Schaltung dargestellt ist. Der Ausgang des Modell-Leseverstärkers **204'** ist nun an einen Inverter **618** gekoppelt. Im Allgemeinen wird das Reset-Signal übermittelt, nachdem eine Abfallflanke des Signals **216** empfangen worden ist. Wie oben erwähnt wurde, wird der Leseverstärker, wenn das Signal **216** bei LOW liegt (d. h. eine Abfallflanke), mit einem Lesebereitschaftssignal versehen. Andererseits wird, wenn das Signal **216** auf HIGH geht, einem Wortleitungstreiber angezeigt, auf eine spezielle Zelle zuzugreifen.

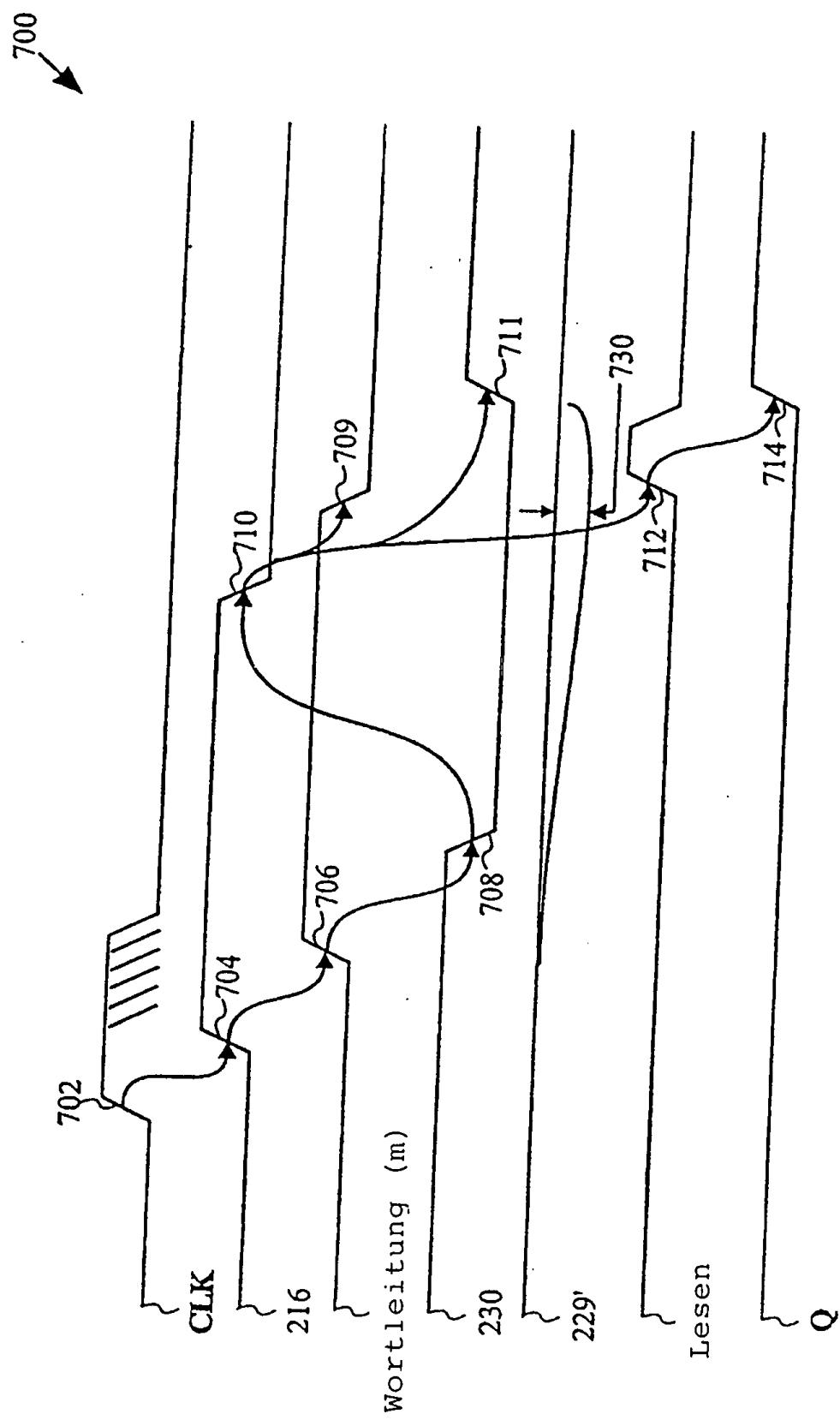

[0044] **Fig. 7** zeigt einen Modell-Pfad und ein Lese-Zeitgeberdiagramm **700** gemäß einer Ausführungsform der vorliegenden Erfindung. Am Anfang, wenn es bei einem Speicher-Zeitgeber(CLK)-Signal zu einer Anstiegsflanke **702** kommt, wird das Signal **216** dazu veranlasst, eine Anstiegsflanke **704** zu erzeugen. Die Anstiegsflanke **704** des Signals **216** führt daher dazu, dass alle adressierten Wortleitungen (einschließlich der Modell-Wortleitung) eine Anstiegsflanke **706** erfahren. Die Anstiegsflanke **706** veranlasst die Modell-Bitleitung **230** wiederum dazu, eine Abfallflanke **708** zu erzeugen. Die Abfallflanke **708** führt dann im Signal **216** zu einer Abfallflanke **710**. Durch die Abfallflanke **710** werden auch die Wortleitungen und Modell-Wortleitungen heruntergefahren, sowie die Eingangs-Latches geöffnet und die Bitleitung und die Datenpfade vorgeladen.

[0045] Wie oben erwähnt wurde, wird der Leseverstärker **204**, wenn beim Signal **216** eine Abfallflanke **710** auftritt, auch dazu angeleitet, das Lesen zu beginnen, wodurch die Abfallflanke **712** auf der Leseleitung erzeugt wird. Genauer gesagt erzeugt die Abfallflanke **710** auch eine Abfallflanke **709** für alle Adressier-Wortleitungen (einschließlich der Modellwortleitung) sowie eine Anstiegsflanke **711** in der Bitleitung **230**. Zusätzlich dazu führt die Anstiegsflanke **712** des Lesesignals zu einer Flanke **714** in einem Ausgang „Q“, der den Wert der gelesenen Daten, in diesem Fall eine logische „1“, wiedergibt. Es ist wichtig, festzustellen, dass die Anstiegsflanke **712** beinahe simultan auftritt, wenn gerade genug Bitleitungs-Ausgleich **730** für die Worst-case-Kernzelle **203** erreicht worden ist.

[0046] Da die RC-Verzögerung des Eigen-Taktgeber-Pfades **114** nach dem Stand der Technik eliminiert worden ist, ist die Zeit, die die Worst-case-Kernzelle **203** benötigt, um einen ausreichenden Bitleitungsausgleich zu erreichen, im Wesentlichen gleich, wie wenn die Modell-Kernzelle **203'** eine ausreichenden Bitleitungsausgleich erzielt hat. Eine Speicherschaltung ist vorteilhafterweise in der Lage, Zugriff-Schritte bei sehr hohen Geschwindigkeiten

durchzuführen, da unnötige Verzögerungen eliminiert werden sind.

[0047] Obwohl die obige Erfindung zum besseren Verständnis detailliert beschrieben worden ist, ist es offensichtlich, dass gewisse Veränderungen und Modifikationen innerhalb des Schutzmfangs der nachfolgenden Ansprüche vorgenommen werden können. Es ist deshalb zu verstehen, dass die verschiedenen Schaltungsdiagramme in einer beliebigen Form ausgeführt werden können, einschließlich z. B. ein beliebiges Halbleitersubstrat, Leiterplatten, gekapselte Schaltungen oder Software-Anwendungen.

[0048] Als Beispiel können Hardware-Beschreibungssprache(HDL, hardware description language)-Design- sowie -Synthese-Programme, wie VHDL® Hardware-Beschreibungssprache von IEEE New York (New York, USA) herangezogen werden, um die Layouts auf Silizium-Niveau zu entwerfen.. Dementsprechend sind die vorliegenden Ausführungsformen illustrativ, und nicht eingrenzend, zu verstehen, und die Erfindung ist nicht durch die hierin angeführten Details begrenzt, sondern kann innerhalb des Schutzmfangs und Äquivalenten der nachfolgenden Ansprüche verändert werden.

## Patentansprüche

1. Speicherschaltung, umfassend:

einen Speicherkerne (**200**) mit einer Matrix aus Kernzellen (**202**), wobei die Matrix aus Kernzellen mit einer Vielzahl von Wortleitungen (**226**) und einer Vielzahl von Bitleitungs-Paaren (**229**) gekoppelt ist; und.

einen Eigen-Taktgeber-Pfad mit einer Modell-Kernzelle (**203'**), die mit einer Modell-Wortleitung (**222**) gekoppelt ist, die von einem Modell-Wortleitungstreiber (**206'**) angesteuert wird, wobei der Eigen-Taktgeber-Pfad weiters einen Modell-Leseverstärker (**204'**) umfasst, der durch ein Modell-Bitleitungspaar (**236, 1230**) mit der Modell-Kernzelle gekoppelt ist, wobei die Modell-Wortleitung und das Modell-Bitleitungs-paar jeweils mit einer Vielzahl von Leer-Kernzellen (**202''**) gekoppelt sind, um eine RC-Verzögerung einer Worst-case-Kernzelle (**203**) der Kernzellen-Matrix anzunähern, **dadurch gekennzeichnet**, dass die Modell-Wortleitung (**222**) eine gefaltete Wortleitung (**222**) ist, so dass die Modell-Wortleitung an einer Position endet, die sich nahe dem Modell-Wortleitungstreiber (**206'**) befindet.

2. Speicherschaltung nach Anspruch 1, worin die Modell-Kernzelle (**203'**) mit dem Ende der Modell-Wortleitung (**222**) an der Position gekoppelt ist, die sich nahe dem Modell-Wortleitungstreiber (**206'**) befindet.

3. Speicherschaltung nach Anspruch 2, weiters umfassend:

eine Steuerschaltung (**210**), die so konfiguriert ist, dass sie den Eigen-Taktgeber-Pfad aktiviert, wobei die Steuerschaltung mit dem Modell-Leseverstärker

(204') gekoppelt ist, der durch ein Modell-Bitleitungs-paar (230, 1230) mit der Modellkernzelle (203') ge-koppelt ist.

4. Speicherschaltung nach Anspruch 3, worin die Steuerschaltung (210) so konfiguriert ist, dass sie ein Wortleitungs-Freigabesignal an den Modell-Wortleitungstreiber (206') übermittelt, um den Eigen-Taktgeber-Pfad zu aktivieren, so dass der Modell-Wortleitungstreiber einen Zugriff auf die Modell-Kernzelle (203') über die gefaltete Wortleitung (222) vornimmt.

5. Speicherschaltung nach Anspruch 4, worin die Steuerschaltung (210) ein Lesebereitschaftssignal erzeugt, das an einen Leseverstärker (204) des Speicherkerns (200') übermittelt wird.

6. Speicherschaltung nach Anspruch 5, worin die Steuerschaltung (230) das Lesebereitschaftssignal nach dem Empfang einer Eigen-Taktgeber-Pfad-RC-Verzögerung der Modell-Wortleitung (222) erzeugt und das Modell-Bitleitungspaar (230, 1230) an die Steuerschaltung übermittelt wird.

7. Speicherschaltung nach Anspruch 6, worin die Eigen-Taktgeber-Pfad-RC-Verzögerung im Wesentlichen gleich der RC-Verzögerung der Worst-case-Kernzelle ist.

8. Speicherschaltung nach Anspruch 7, worin die Worst-case-Kernzelle die am weitesten (203) von einem Wortleitungstreiber (206) und dem Leseverstärker (204) des Speicherkerns (200) entfernt gelegene Kernzelle der Kernzellen-Matrix (202) ist.

9. Speicherschaltung nach Anspruch 1, weiters umfassend:

eine Vielzahl von Wortleitungstreibern (206), die mit der Vielzahl von Wortleitungen (226) gekoppelt ist; und

eine Vielzahl von Leseverstärkern (24), die mit der Vielzahl von Bitleitungspaaren (229) gekoppelt ist.

10. Speicherschaltung nach Anspruch 2, worin eine Steuerschaltung (210) mit jedem der Vielzahl von Wortleitungstreibern (206) und jedem der Vielzahl von Leseverstärkern (204) gekoppelt ist, die mit der Kernzellen-Matrix (202) gekoppelt ist.

11. Speicherschaltung nach Anspruch 1, worin die Speicherschaltung aus der Gruppe ausgewählt ist, die aus einem ROM-Schaltkreis, einem RAM-Schaltkreis, einem SRAM-Schaltkreis, einem DRAM-Schaltkreis, einem EPROM-Schaltkreis und einem EEPROM-Schaltkreis besteht.

12. Verfahren zur Herstellung einer Speicherschaltung mit einem Eigen-Taktgeber-Pfad, folgende Schritte umfassend:

das Bereitstellen eines Speicherkerns (200) mit einer

Matrix aus Kernzellen (202); das Integrieren eines Eigen-Taktgeber-Pfads aus Leer-Kernzellen entlang ei-ner Modell-Wortleitung (222) und entlang eines Mo-dell-Bitleitungspaares (236, 1230), dadurch gekenn-zeichnet, dass die Modell-Wortleitung so gefaltet ist, dass eine Modell-Leerkernzelle (203') im Wesentli-chen am Ausgangspunkt der Modell-Wortleitung an-geordnet ist und ein Endpunkt der Modell-Wortleitung mit der Modell-Leerkernzelle gekoppelt ist.

13. Verfahren zur Herstellung einer Speicher-schaltung mit einem Eigen-Taktgeber-Pfad nach An-spruch 12, weiters folgenden Schritt umfassend: das Übermitteln eines Lesebereitschaftssignals an einen Leseverstärker (204) des Speicherkerns nach einem RC-Verzögerungssignal, das anzeigen, dass eine RC-Verzögerung entlang der Modell-Wortleitung (222) und eine RC-Verzögerung entlang des Mo-dell-Bitleitungspaares (230, 1230) vollständig sind.

14. Verfahren zur Herstellung einer Speicher-schaltung mit einem Eigen-Taktgeber-Pfad nach An-spruch 13, worin eine Abfallflanke des Lesebereit-schaftssignals den Leseverstärker (204) des Spei-cherkerns (200) auslöst.

15. Verfahren zur Herstellung einer Speicher-schaltung mit einem Eigen-Taktgeber-Pfad nach An-spruch 14, worin eine Anstiegsflanke des Lesebereit-schaftssignals einen Modell-Wortleitungstreiber (206') auslöst, der an die Modell-Wortleitung (22) am Ausgangspunkt der Modell-Wortleitung gekoppelt ist.

16. Verfahren zur Herstellung einer Speicher-schaltung mit einem Eigen-Taktgeber-Pfad nach An-spruch 15, worin die Speicherschaltung aus der aus einem ROM-Schaltkreis, einem RAM-Schaltkreis, ei-nem SRAM-Schaltkreis, einem DRAM-Schaltkreis, ei-nem EPROM-Schaltkreis und einem EE-PROM-Schaltkreis bestehenden Gruppe ausgewählt ist.

17. Speicherschaltung nach Anspruch 1, worin der Eigen-Taktgeber-Pfad eine Vielzahl von Kernzel-len (202', 202'') entlang der Modell-Wortleitung (222) und entlang des Modell-Bitleitungspaares (230, 1230) umfasst, wobei die Modell-Wortleitung so ge-faltet ist, dass eine erste Modell-Kernzelle im We-sentlichen am Ausgangspunkt der Modell-Wortlei-tung angeordnet ist und ein Endpunkt der Mo-dell-Wortleitung mit der ersten Modell-Kernzelle ge-koppelt ist.

18. Speicherschaltung nach Anspruch 17, worin das Modell-Bitleitungspaar (230, 1230) entlang einer Seite des Speicherkerns angeordnet ist, die an eine Vielzahl von Wortleitungstreibern (206) angrenzt.

19. Speicherschaltung nach Anspruch 18, worin ein Modell-Wortleitungstreiber (208') im Bereich der

Vielzahl von Wortleitungstreibern (**206**) ausgerichtet ist und der Modell-Wortleitungstreiber im Bereich der ersten Modell-Kernzelle angeordnet ist.

20. Speicherschaltung nach Anspruch 19, worin eine Steuerschaltung (**230**) so konfiguriert ist, dass sie die RC-Verzögerung empfängt, die durch eine kombinierte RC-Verzögerung der Modell-Wortleitung (**222**) und des Modell-Bitleitungspaares (**230**, 1230) ohne eine Rückweg-RC-Verzögerung definiert ist.

Es folgen 10 Blatt Zeichnungen

## Anhängende Zeichnungen

**FIG. 1**

(Stand der Technik)

FIG. 2A

FIG. 2B

FIG. 2C

FIG. 3

FIG. 4

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 6

Modell-Pfad und Lese-Taktgeber

FIG. 7