(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-278459

(P2008-278459A)

(43) 公開日 平成20年11月13日(2008.11.13)

(51) Int.Cl.

H04L 25/02

(2006.01)

F 1

H04L 25/02

テーマコード(参考)

J

5K029

審査請求 未請求 請求項の数 18 O L (全 23 頁)

(21) 出願番号 特願2008-26687 (P2008-26687)

(22) 出願日 平成20年2月6日 (2008.2.6)

(31) 優先権主張番号 特願2007-90145 (P2007-90145)

(32) 優先日 平成19年3月30日 (2007.3.30)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100107836

弁理士 西 和哉

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100140774

弁理士 大浪 一徳

(72) 発明者 南本 高志

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

F ターム(参考) 5K029 AA08 CC01 DD23 EE06 GG07

HH01

(54) 【発明の名称】通信システム、送信装置、受信装置及び通信方法並びに半導体素子

## (57) 【要約】

【課題】データ信号等の情報信号を通信する際ににおけるセキュリティの向上を図る。

【解決手段】情報を2値の状態値で規定する情報信号を送信する送信装置と、前記情報信号を受信する受信装置と、を備え、前記送信装置は、情報解読信号を生成する信号生成手段を含み、前記情報解読信号を前記情報信号と共に送信するものであり、前記情報信号の状態値が変化する場合には前記情報解読信号の状態値が変化せず、前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値が変化するものであり、前記受信装置は、受信した前記情報信号及び前記情報解読信号における状態値の変化点を基準にして前記情報信号の状態値を取得する情報取得手段を含む。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

情報を2値の状態値で規定する情報信号を送信する送信装置と、

前記情報信号を受信する受信装置と、を備え、

前記送信装置は、情報解読信号を生成する信号生成手段を含み、前記情報解読信号を前記情報信号と共に送信するものであり、前記情報信号の状態値が変化する場合には前記情報解読信号の状態値が変化せず、前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値が変化するものであり、

前記受信装置は、受信した前記情報信号及び前記情報解読信号における状態値の変化点を基準にして前記情報信号の状態値を取得する情報取得手段を含む、

ことを特徴とする通信システム。

10

**【請求項 2】**

情報を2値の状態値で規定する複数の情報信号を送信する送信装置と、

前記複数の情報信号を受信する受信装置と、を備え、

前記送信装置は、情報解読信号を生成する信号生成手段を含み、前記情報解読信号を前記複数の情報信号と共に送信するものであり、前記複数の情報信号の状態値が同じタイミングにおいて変化しない場合に前記情報解読信号の状態値が変化するものであり、

前記受信装置は、受信した前記複数の情報信号及び前記情報解読信号における状態値の変化点を基準にして前記複数の情報信号の各々の状態値を取得する情報取得手段を含む、

ことを特徴とする通信システム。

20

**【請求項 3】**

前記情報取得手段は、

前記情報信号における状態値の変化に同期して第1のパルス信号を発生する第1のパルス発生回路と、

前記情報解読信号における状態値の変化に同期して第2のパルス信号を発生する第2のパルス発生回路と、

前記第1のパルス信号と前記第2のパルス信号との論理和信号を出力する論理和回路と、

前記論理和信号を所定時間だけ遅延させる第1の遅延回路と、

前記第1の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値が前記情報信号に含まれる1情報分のビット数と一致した場合に一致検出信号を出力する一致検出回路と、

前記情報信号と前記第1の遅延回路によって遅延された前記論理和信号とを入力とし、当該論理和信号に同期して前記情報信号をシリアル-パラレル変換するシリアル-パラレル変換回路と、

前記一致検出信号に同期してシリアル-パラレル変換された前記情報信号を取得する信号処理回路と、

を備えること特徴とする請求項1記載の通信システム。

30

**【請求項 4】**

前記情報取得手段は、

前記複数の情報信号の各々に対応して設けられ、対応する情報信号における状態値の変化に同期して第1のパルス信号を発生する第1のパルス発生回路と、

前記情報解読信号における状態値の変化に同期して第2のパルス信号を発生する第2のパルス発生回路と、

前記複数の情報信号の各々に対応する前記第1のパルス信号と前記第2のパルス信号との論理和信号を出力する論理和回路と、

前記論理和信号を所定時間だけ遅延させる第1の遅延回路と、

前記第1の遅延回路によって遅延された前記論理和信号に同期してカウントし、当該カウント値が前記複数の情報信号に含まれる1情報分のビット数と一致した場合に一致検出信号を出力する一致検出回路と、

50

前記複数の情報信号の各々に対応して設けられ、対応する前記複数の情報信号の各々と前記第1の遅延回路によって遅延された前記論理和信号とを入力とし、当該論理和信号に同期して前記対応する前記複数の情報信号の各々をシリアル・パラレル変換するシリアル・パラレル変換回路と、

前記一致検出信号に同期してシリアル・パラレル変換された前記複数の情報信号の各々を取得する信号処理回路と、

を備えること特徴とする請求項2記載の通信システム。

#### 【請求項5】

前記第1のパルス発生回路は、

前記情報信号を所定時間だけ遅延させる第2の遅延回路と、

前記情報信号と前記第2の遅延回路によって遅延された前記情報信号との排他的論理和信号を前記第1のパルス信号として出力する第1の排他的論理和回路とから構成され、

前記第2のパルス発生回路は、

前記情報解読信号を所定時間だけ遅延させる第3の遅延回路と、

前記情報解読信号と前記第3の遅延回路によって遅延された前記情報解読信号との排他的論理和信号を前記第2のパルス信号として出力する第2の排他的論理和回路とから構成され、

前記一致検出回路は、

最大カウント数が前記情報信号に含まれる1情報分のビット数と同一に設定されており、前記第1の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値を示すビットデータをパラレルに出力するカウンタ回路と、

前記カウンタ回路からパラレルに出力される前記ビットデータの論理積信号を前記一致検出信号として出力する論理積回路とから構成されている、

ことを特徴とする請求項3または4に記載の通信システム。

#### 【請求項6】

前記送信装置は、

前記情報信号及び前記情報解読信号を無線送信する無線送信手段を備え、

前記受信装置は、

無線送信された前記情報信号及び前記情報解読信号を受信する無線受信手段を備える、

ことを特徴とする請求項1～5のいずれか一項に記載の通信システム。

#### 【請求項7】

情報を2値の状態値で規定する情報信号と情報解読信号とを送信する送信手段と、

前記情報解読信号を生成する信号生成手段と、を含み、

前記情報信号の状態値が変化する場合には前記情報解読信号の状態値が維持され、前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値が変化するものである、

ことを特徴とする送信装置。

#### 【請求項8】

情報を2値の状態値で規定する複数の情報信号と情報解読信号とを送信する送信手段と、

前記情報解読信号を生成する信号生成手段と、を含み、

前記複数の情報信号の状態値が同じタイミングにおいて変化しない場合に前記情報解読信号の状態値が変化するものである、

ことを特徴とする送信装置。

#### 【請求項9】

前記送信手段が、前記情報信号及び前記情報解読信号を無線送信する無線送信手段を含む、ことを特徴とする請求項7または8に記載の送信装置。

#### 【請求項10】

情報を2値の状態値で規定する情報信号と、情報解読信号と、を受信する受信手段と、前記情報解読信号における状態値の変化点を基準にして前記情報信号の状態値を取得す

10

20

30

40

50

る情報取得手段と、を備え、

前記情報信号の状態値が変化する場合には前記情報解読信号の状態値が維持され、前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値が変化するものである、

ことを特徴とする受信装置。

【請求項 1 1】

情報を 2 値の状態値で規定する複数の情報信号と、情報解読信号と、を受信する受信手段と、

前記複数の情報信号及び前記情報解読信号における状態値の変化点を基準にして前記複数の情報信号の各々の状態値を取得する情報取得手段と、を備え、

前記複数の情報信号の状態値が同じタイミングにおいて変化しない場合に前記情報解読信号の状態値が変化するものである、

ことを特徴とする受信装置。

【請求項 1 2】

前記情報取得手段は、

前記情報信号における状態値の変化に同期して第 1 のパルス信号を発生する第 1 のパルス発生回路と、

前記情報解読信号における状態値の変化に同期して第 2 のパルス信号を発生する第 2 のパルス発生回路と、

前記第 1 のパルス信号と前記第 2 のパルス信号との論理和信号を出力する論理和回路と、

前記論理和信号を所定時間だけ遅延させる第 1 の遅延回路と、

前記第 1 の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値が前記情報信号に含まれる 1 情報分のビット数と一致した場合に一致検出信号を出力する一致検出回路と、

前記情報信号と前記第 1 の遅延回路によって遅延された前記論理和信号とを入力とし、当該論理和信号に同期して前記情報信号をシリアル - パラレル変換するシリアル - パラレル変換回路と、

前記一致検出信号に同期してシリアル - パラレル変換された前記情報信号を取得する信号処理回路と、

を備えること特徴とする請求項 1 0 記載の受信装置。

【請求項 1 3】

前記情報取得手段は、

前記複数の情報信号の各々に対応して設けられ、対応する情報信号における状態値の変化に同期して第 1 のパルス信号を発生する第 1 のパルス発生回路と、

前記情報解読信号における状態値の変化に同期して第 2 のパルス信号を発生する第 2 のパルス発生回路と、

前記複数の情報信号の各々に対応する前記第 1 のパルス信号と前記第 2 のパルス信号との論理和信号を出力する論理和回路と、

前記論理和信号を所定時間だけ遅延させる第 1 の遅延回路と、

前記第 1 の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値が前記複数の情報信号に含まれる 1 情報分のビット数と一致した場合に一致検出信号を出力する一致検出回路と、

前記複数の情報信号の各々に対応して設けられ、対応する前記複数の情報信号の各々と前記第 1 の遅延回路によって遅延された前記論理和信号とを入力とし、当該論理和信号に同期して前記対応する前記複数の情報信号の各々をシリアル - パラレル変換するシリアル - パラレル変換回路と、

前記一致検出信号に同期してシリアル - パラレル変換された前記複数の情報信号の各々を取得する信号処理回路と、

を備えること特徴とする請求項 1 1 記載の受信装置。

10

20

30

40

50

**【請求項 1 4】**

前記第1のパルス発生回路は、

前記情報信号を所定時間だけ遅延させる第2の遅延回路と、

前記情報信号と前記第2の遅延回路によって遅延された前記情報信号との排他的論理和信号を前記第1のパルス信号として出力する第1の排他的論理和回路とから構成され、

前記第2のパルス発生回路は、

前記情報解読信号を所定時間だけ遅延させる第3の遅延回路と、

前記情報解読信号と前記第3の遅延回路によって遅延された前記情報解読信号との排他的論理和信号を前記第2のパルス信号として出力する第2の排他的論理和回路とから構成され、

前記一致検出回路は、

最大カウント数が前記情報信号に含まれる1情報分のビット数と同一に設定されており、

前記第1の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、

カウント値を示すビットデータをパラレルに出力するカウンタ回路と、

前記カウンタ回路からパラレルに出力される前記ビットデータの論理積信号を前記一致検出信号として出力する論理積回路とから構成されている、

ことを特徴とする請求項12または13に記載の受信装置。

10

**【請求項 1 5】**

前記受信手段が、無線送信された前記情報信号及び前記情報解読信号を受信する無線受信手段を含む、

20

ことを特徴とする請求項10～14のいずれか一項に記載の受信装置。

**【請求項 1 6】**

送信側から情報を2値の状態値で規定する情報信号と情報解読信号とを送信し、

受信側で前記情報信号と前記情報解読信号とを受信し、かつ、受信側で前記情報信号及び前記情報解読信号における状態値の変化点を基準にして前記情報信号の状態値を取得するものあり、

前記情報信号の状態値が変化する場合には前記情報解読信号の状態値が変化せず、前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値が変化するものである、

30

ことを特徴とする通信方法。

**【請求項 1 7】**

情報を2値の状態値で規定する情報信号を生成する情報信号生成回路と、

情報解読信号を生成する情報解読信号生成回路と、

前記情報信号と前記情報解読信号とを出力する送信回路を含み、

前記情報解読信号生成回路は、

前記情報信号の状態値が変化する場合には前記情報解読信号の状態値を変化させず、

前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値を変化させる、機能を含む半導体素子。

**【請求項 1 8】**

情報を2値の状態値で規定する情報信号と、情報解読信号とを入力とし、

前記情報信号における状態値の変化に同期して第1のパルス信号を発生する第1のパルス発生回路と、

前記情報解読信号における状態値の変化に同期して第2のパルス信号を発生する第2のパルス発生回路と、

前記第1のパルス信号と前記第2のパルス信号との論理和信号を出力する論理和回路と、

40

前記論理和信号を所定時間だけ遅延させる第1の遅延回路と、

前記第1の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値が前記情報信号に含まれる1情報分のビット数と一致した場合に一致検出信号を出力する一致検出回路と、

50

前記情報信号と前記第1の遅延回路によって遅延された前記論理和信号とを入力とし、当該論理和信号に同期して前記情報信号をシリアル・パラレル変換するシリアル・パラレル変換回路と、

前記一致検出信号に同期してシリアル・パラレル変換された前記情報信号を取得する信号処理回路と、

を備えること特徴とする半導体素子。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、通信システム、送信装置、受信装置及び通信方法並びに半導体素子に関する。

10

【背景技術】

【0002】

例えば、下記特許文献1には、クロック同期型の通信方式において、送信側はクロック信号の立ち上がりまたは立ち下がりまでにデータ信号のレベルを確定する一方、受信側はクロック信号の立ち上がりまたは立ち下がりに同期してデータ信号のレベルを取得していく、取得したデータ信号をシリアル・パラレル変換するなどして復号化を行う技術が開示されている。

【特許文献1】特開平6-46041号公報

20

【発明の開示】

【発明が解決しようとする課題】

【0003】

上記従来技術では、第三者であってもクロック信号とデータ信号との区別が容易なため、受信側と同様の手続きによりデータ信号の復号化を行うことが可能であり、情報の漏洩などセキュリティ上の問題が生じる。

【0004】

本発明は、このような事情に鑑みてなされたものであり、データ信号等の情報信号を通信する際ににおけるセキュリティの向上を図ることを目的とする。

【課題を解決するための手段】

【0005】

上記目的を達成するために、本発明に係る通信システムは、情報を2値の状態値で規定する情報信号を送信する送信装置と、前記情報信号を受信する受信装置と、を備え、前記送信装置は、情報解読信号を生成する信号生成手段を含み、前記情報解読信号を前記情報信号と共に送信するものであり、前記情報信号の状態値が変化する場合には前記情報解読信号の状態値が変化せず、前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値が変化するものであり、前記受信装置は、受信した前記情報信号及び前記情報解読信号における状態値の変化点を基準にして前記情報信号の状態値を取得する情報取得手段を含む、ことを特徴とする。

このような特徴を有する通信システムによれば、情報信号と情報解読信号との区別やそれぞれの信号の役割を判別することが困難となり、仮に第三者が両信号を読み取ったとしてもその復号化を行うことができず、情報の漏洩を防止することが可能となる。その結果、データ信号等の情報信号を通信する際ににおけるセキュリティの向上を図ることが可能である。

【0006】

また、本発明に係る通信システムでは、情報を2値の状態値で規定する複数の情報信号を送信する送信装置と、前記複数の情報信号を受信する受信装置と、を備え、前記送信装置は、情報解読信号を生成する信号生成手段を含み、前記情報解読信号を前記複数の情報信号と共に送信するものであり、前記複数の情報信号の状態値が同じタイミングにおいて変化しない場合に前記情報解読信号の状態値が変化するものであり、前記受信装置は、受信した前記複数の情報信号及び前記情報解読信号における状態値の変化点を基準にして前

40

50

記複数の情報信号の各々の状態値を取得する情報取得手段を含む、ことが好ましい。

このような構成を採用することにより、送信装置側から複数の情報信号を送信する場合であっても、情報の漏洩を防止することができ、その結果、情報信号を通信する際ににおけるセキュリティの向上を図ることが可能である。

#### 【0007】

また、本発明に係る通信システムにおいて、前記情報取得手段は、前記情報信号における状態値の変化に同期して第1のパルス信号を発生する第1のパルス発生回路と、前記情報解読信号における状態値の変化に同期して第2のパルス信号を発生する第2のパルス発生回路と、前記第1のパルス信号と前記第2のパルス信号との論理和信号を出力する論理和回路と、前記論理和信号を所定時間だけ遅延させる第1の遅延回路と、前記第1の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値が前記情報信号に含まれる1情報分のビット数と一致した場合に一致検出信号を出力する一致検出回路と、前記情報信号と前記第1の遅延回路によって遅延された前記論理和信号とを入力とし、当該論理和信号に同期して前記情報信号をシリアル・パラレル変換するシリアル・パラレル変換回路と、前記一致検出信号に同期してシリアル・パラレル変換された前記情報信号を取得する信号処理回路とを備えることが好ましい。

このような構成を採用することにより、受信装置側において簡単な回路構成で情報信号を取得（復号化）することができるので、受信装置の低コスト化、設計作業効率の向上及び設計期間の短縮を図ることができる。

#### 【0008】

また、本発明に係る通信システムでは、前記送信装置が複数の前記情報信号を送信する場合において、前記情報取得手段は、前記複数の情報信号の各々に対応して設けられ、対応する情報信号における状態値の変化に同期して第1のパルス信号を発生する第1のパルス発生回路と、前記情報解読信号における状態値の変化に同期して第2のパルス信号を発生する第2のパルス発生回路と、前記複数の情報信号の各々に対応する前記第1のパルス信号と前記第2のパルス信号との論理和信号を出力する論理和回路と、前記論理和信号を所定時間だけ遅延させる第1の遅延回路と、前記第1の遅延回路によって遅延された前記論理和信号に同期してカウントし、当該カウント値が前記複数の情報信号に含まれる1情報分のビット数と一致した場合に一致検出信号を出力する一致検出回路と、前記複数の情報信号の各々に対応して設けられ、対応する前記複数の情報信号の各々と前記第1の遅延回路によって遅延された前記論理和信号とを入力とし、当該論理和信号に同期して前記対応する前記複数の情報信号の各々をシリアル・パラレル変換するシリアル・パラレル変換回路と、前記一致検出信号に同期してシリアル・パラレル変換された前記複数の情報信号の各々を取得する信号処理回路と、を備えることが好ましい。

このような構成を採用することにより、送信装置側から複数の情報信号を送信する場合におけるセキュリティの向上、及び受信装置の低コスト化、設計作業効率の向上及び設計期間の短縮を両立させることができる。

#### 【0009】

また、本発明に係る通信システムにおいて、前記第1のパルス発生回路は、前記情報信号を所定時間だけ遅延させる第2の遅延回路と、前記情報信号と前記第2の遅延回路によって遅延された前記情報信号との排他的論理和信号を前記第1のパルス信号として出力する第1の排他的論理和回路とから構成され、前記第2のパルス発生回路は、前記情報解読信号を所定時間だけ遅延させる第3の遅延回路と、前記情報解読信号と前記第3の遅延回路によって遅延された前記情報解読信号との排他的論理和信号を前記第2のパルス信号として出力する第2の排他的論理和回路とから構成され、前記一致検出回路は、最大カウント数が前記情報信号に含まれる1情報分のビット数と同一に設定されており、前記第1の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値を示すビットデータをパラレルに出力するカウンタ回路と、前記カウンタ回路からパラレルに出力される前記ビットデータの論理積信号を前記一致検出信号として出力する論理積回路とから構成されていることが好ましい。

10

20

30

40

50

上述した第1のパルス発生回路、第2のパルス発生回路及び一致検出回路を、遅延回路や排他的論理和回路、カウンタ回路、論理積回路等の汎用回路を用いて構成することによって、より一層受信装置の低コスト化、設計作業効率の向上及び設計期間の短縮に寄与することができる。

【0010】

また、本発明に係る通信システムにおいて、前記送信装置は、前記情報信号及び前記情報解読信号を無線送信する無線送信手段を備え、前記受信装置は、無線送信された前記情報信号及び前記情報解読信号を受信する無線受信手段を備えるような構成を採用しても良い。

このような構成を採用することにより、有線通信のみならず無線通信にて情報信号の通信を行う際におけるセキュリティの向上を図ることが可能である

10

【0011】

また、本発明に係る送信装置は、情報を2値の状態値で規定する情報信号と情報解読信号とを送信する送信手段と、前記情報解読信号を生成する信号生成手段と、を含み、前記情報信号の状態値が変化する場合には前記情報解読信号の状態値が維持され、前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値が変化するものである、ことを特徴とする。

このような特徴を有する送信装置によれば、情報の漏洩を防止することができ、データ信号等の情報信号を通信する際ににおけるセキュリティの向上を図ることが可能である。

20

【0012】

また、本発明に係る送信装置では、情報を2値の状態値で規定する複数の情報信号と情報解読信号とを送信する送信手段と、前記情報解読信号を生成する信号生成手段と、を含み、前記複数の情報信号の状態値が同じタイミングにおいて変化しない場合に前記情報解読信号の状態値が変化するものである、ことが好ましい。

このような構成を採用することにより、送信装置側から複数の情報信号を送信する場合であっても、情報の漏洩を防止することができ、その結果、情報信号を通信する際ににおけるセキュリティの向上を図ることが可能である。

30

【0013】

また、本発明に係る送信装置において、前記送信手段が、前記情報信号及び前記情報解読信号を無線送信する無線送信手段を含むような構成を採用しても良い。

このような構成を採用することにより、有線通信のみならず無線通信にて情報信号の通信を行う際ににおけるセキュリティの向上を図ることが可能である。

【0014】

一方、本発明に係る受信装置は、情報を2値の状態値で規定する情報信号と、情報解読信号と、を受信する受信手段と、前記情報解読信号における状態値の変化点を基準にして前記情報信号の状態値を取得する情報取得手段と、を備え、前記情報信号の状態値が変化する場合には前記情報解読信号の状態値が維持され、前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値が変化するものである、ことを特徴とする

このような特徴を有する受信装置によれば、情報の漏洩を防止することができ、データ信号等の情報信号を通信する際ににおけるセキュリティの向上を図ることが可能である。

40

【0015】

また、本発明に係る受信装置では、情報を2値の状態値で規定する複数の情報信号と、情報解読信号と、を受信する受信手段と、前記複数の情報信号及び前記情報解読信号における状態値の変化点を基準にして前記複数の情報信号の各々の状態値を取得する情報取得手段と、を備え、前記複数の情報信号の状態値が同じタイミングにおいて変化しない場合に前記情報解読信号の状態値が変化するものである、ことが好ましい。

このような構成を採用することにより、送信装置側から複数の情報信号を送信する場合であっても、情報の漏洩を防止することができ、その結果、情報信号を通信する際ににおけるセキュリティの向上を図ることが可能である。

50

【0016】

また、本発明に係る受信装置において、前記情報取得手段は、前記情報信号における状態値の変化に同期して第1のパルス信号を発生する第1のパルス発生回路と、前記情報解読信号における状態値の変化に同期して第2のパルス信号を発生する第2のパルス発生回路と、前記第1のパルス信号と前記第2のパルス信号との論理和信号を出力する論理和回路と、前記論理和信号を所定時間だけ遅延させる第1の遅延回路と、前記第1の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値が前記情報信号に含まれる1情報分のビット数と一致した場合に一致検出信号を出力する一致検出回路と、前記情報信号と前記第1の遅延回路によって遅延された前記論理和信号とを入力とし、当該論理和信号に同期して前記情報信号をシリアル-パラレル変換するシリアル-パラレル変換回路と、前記一致検出信号に同期してシリアル-パラレル変換された前記情報信号を取得する信号処理回路とを備えることが好ましい。

このような構成を採用することにより、受信装置側において簡単な回路構成で情報信号を取得（復号化）することができるので、受信装置の低コスト化、設計作業効率の向上及び設計期間の短縮を図ることができる。

#### 【0017】

また、本発明に係る受信装置では、前記送信装置が複数の前記情報信号を送信する場合において、前記情報取得手段は、前記複数の情報信号の各々に対応して設けられ、対応する情報信号における状態値の変化に同期して第1のパルス信号を発生する第1のパルス発生回路と、前記情報解読信号における状態値の変化に同期して第2のパルス信号を発生する第2のパルス発生回路と、前記複数の情報信号の各々に対応する前記第1のパルス信号と前記第2のパルス信号との論理和信号を出力する論理和回路と、前記論理和信号を所定時間だけ遅延させる第1の遅延回路と、前記第1の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値が前記複数の情報信号に含まれる1情報分のビット数と一致した場合に一致検出信号を出力する一致検出回路と、前記複数の情報信号の各々に対応して設けられ、対応する前記複数の情報信号の各々と前記第1の遅延回路によって遅延された前記論理和信号とを入力とし、当該論理和信号に同期して前記対応する前記複数の情報信号の各々をシリアル-パラレル変換するシリアル-パラレル変換回路と、前記一致検出信号に同期してシリアル-パラレル変換された前記複数の情報信号の各々を取得する信号処理回路とを備えることが好ましい。

このような構成を採用することにより、送信装置側から複数の情報信号を送信する場合におけるセキュリティの向上、及び受信装置の低コスト化、設計作業効率の向上及び設計期間の短縮を両立させることができる。

#### 【0018】

また、本発明に係る受信装置において、前記第1のパルス発生回路は、前記情報信号を所定時間だけ遅延させる第2の遅延回路と、前記情報信号と前記第2の遅延回路によって遅延された前記情報信号との排他的論理和信号を前記第1のパルス信号として出力する第1の排他的論理和回路とから構成され、前記第2のパルス発生回路は、前記情報解読信号を所定時間だけ遅延させる第3の遅延回路と、前記情報解読信号と前記第3の遅延回路によって遅延された前記情報解読信号との排他的論理和信号を前記第2のパルス信号として出力する第2の排他的論理和回路とから構成され、前記一致検出回路は、最大カウント数が前記情報信号に含まれる1情報分のビット数と同一に設定されており、前記第1の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値を示すビットデータをパラレルに出力するカウンタ回路と、前記カウンタ回路からパラレルに出力される前記ビットデータの論理積信号を前記一致検出信号として出力する論理積回路とから構成されていることが好ましい。

上述した第1のパルス発生回路、第2のパルス発生回路及び一致検出回路を、遅延回路や排他的論理和回路、カウンタ回路、論理積回路等の汎用回路を用いて構成することによって、より一層受信装置の低コスト化、設計作業効率の向上及び設計期間の短縮に寄与することができる。

#### 【0019】

10

20

30

40

50

また、本発明に係る受信装置において、前記受信手段が、無線送信された前記情報信号及び前記情報解読信号を受信する無線受信手段を含むような構成を採用しても良い。

このような構成を採用することにより、有線通信のみならず無線通信にて情報信号の通信を行う際ににおけるセキュリティの向上を図ることが可能である。

#### 【0020】

さらに、本発明に係る通信方法は、送信側から情報を2値の状態値で規定する情報信号と情報解読信号とを送信し、受信側で前記情報信号と前記情報解読信号とを受信し、かつ、受信側で前記情報信号及び前記情報解読信号における状態値の変化点を基準にして前記情報信号の状態値を取得するものであり、前記情報信号の状態値が変化する場合には前記情報解読信号の状態値が変化せず、前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値が変化するものである、ことを特徴とする。

このような特徴を有する通信方法によれば、情報の漏洩を防止することができ、データ信号等の情報信号を通信する際ににおけるセキュリティの向上を図ることが可能である。

#### 【0021】

本発明に係る送信機能を有する半導体素子は、情報を2値の状態値で規定する情報信号を生成する情報信号生成回路と、情報解読信号を生成する情報解読信号生成回路と、前記情報信号と前記情報解読信号とを出力する送信回路を含み、前記情報解読信号生成回路は、前記情報信号の状態値が変化する場合には前記情報解読信号の状態値を変化させず、前記情報信号の状態値が変化しない場合には前記情報解読信号の状態値を変化させる、機能を含む。このような送信機能を有する半導体素子を使用することで、前記の送信装置を構成することができる。

#### 【0022】

また、本発明に係る受信機能を有する半導体素子は、情報を2値の状態値で規定する情報信号と、情報解読信号とを入力とし、前記情報信号における状態値の変化に同期して第1のパルス信号を発生する第1のパルス発生回路と、前記情報解読信号における状態値の変化に同期して第2のパルス信号を発生する第2のパルス発生回路と、前記第1のパルス信号と前記第2のパルス信号との論理和信号を出力する論理和回路と、前記論理和信号を所定時間だけ遅延させる第1の遅延回路と、前記第1の遅延回路によって遅延された前記論理和信号に同期してカウント動作を行い、カウント値が前記情報信号に含まれる1情報分のビット数と一致した場合に一致検出信号を出力する一致検出回路と、前記情報信号と前記第1の遅延回路によって遅延された前記論理和信号とを入力とし、当該論理和信号に同期して前記情報信号をシリアル-パラレル変換するシリアル-パラレル変換回路と、前記一致検出信号に同期してシリアル-パラレル変換された前記情報信号を取得する信号処理回路と、を備えること特徴とする。このような受信機能を有する半導体素子を使用することで、前記受信装置を構成することができる。

#### 【発明を実施するための最良の形態】

#### 【0023】

以下、本発明に係る通信システム、送信装置及び受信装置並びに通信方法の一実施形態について図面を参照しながら説明する。なお、以下では、本実施形態に係る通信システムとして、電子回路における回路ブロック同士の通信（つまり有線通信）を例示して説明する。

#### 【0024】

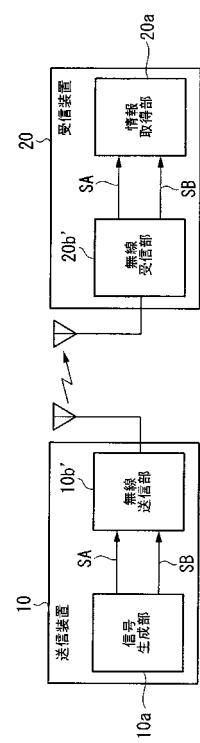

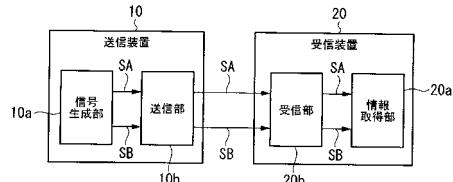

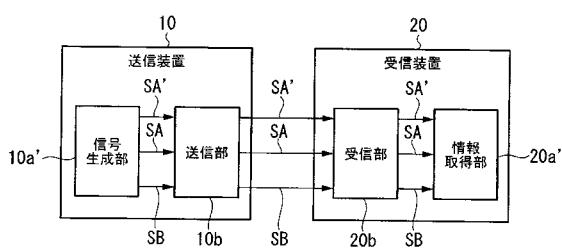

図1は本実施形態に係る通信システムの構成ブロック図である。この図1に示すように、本実施形態に係る通信システムは、送信装置10と受信装置20とから構成されている。これら送信装置10及び受信装置20は、電子回路における送信側回路ブロックと受信側回路ブロックであり、例えばC P U (Central Processing Unit)やマイクロプロセッサ、その他の回路から構成されているものである。送信装置10と受信装置20とは、2つの信号線を介して互いに接続されている。また、送信装置10は、その構成要素として信号生成部10a（信号生成手段）及び送信部（送信手段）10bを備え、受信装置20は情報取得部20a（情報取得手段）及び受信部（受信手段）20bを備えている。

## 【0025】

送信装置10において、信号生成部10aは、情報を2値の状態値（ハイレベル、ロー レベル）で規定する情報信号SAと、情報解読信号SBとを生成する。ここで、情報信号SAの状態値が変化する場合には情報解読信号SBの状態値が変化せず、情報信号SAの状態値が変化しない場合には情報解読信号SBの状態値が変化するものである。送信部10bは、情報信号SAを一方の信号線を介して受信装置20（詳細には受信部20b）に送信すると共に、情報解読信号SBを他方の信号線を介して受信装置20（詳細には受信部20b）に送信する。ここで、情報信号SAはシリアルデータであり、当該情報信号SAに含まれる情報としては、ペイロード等のデータ本体や、ヘッダ等の通信の制御に関する制御情報でも良く、また、これらデータ本体と制御情報の組み合わせでも良い。

10

## 【0026】

受信装置20において、受信部20bは、送信装置10から受信した情報信号SA及び情報解読信号SBを情報取得部20aに出力する。情報取得部20aは、情報信号SA及び情報解読信号SBにおける状態値の変化点を基準にして情報信号SAの状態値（つまり情報信号SAに含まれる情報）を取得する。以下、この情報取得部20aについて、図2を参照して詳細に説明する。

## 【0027】

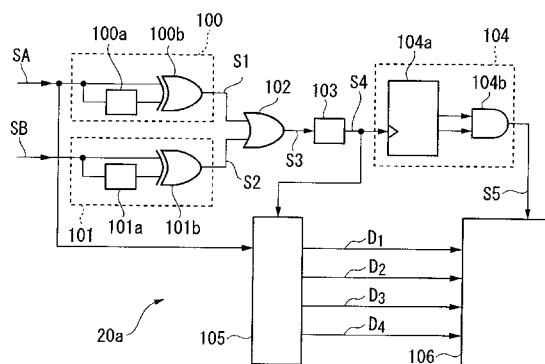

図2は、情報取得部20aの内部構成ブロック図である。この図2に示すように、情報取得部20aは、第1のパルス発生回路100、第2のパルス発生回路101、論理和回路102、遅延回路103、一致検出回路104、シフトレジスタ105及びコントローラ106から構成されている。

20

## 【0028】

第1のパルス発生回路100は、遅延回路100a及び排他的論理和回路100bから構成されている。遅延回路100aは、情報信号SAを入力とし、当該情報信号SAを所定時間だけ遅延させて排他的論理和回路100bに出力する。排他的論理和回路100bは、情報信号SAと遅延回路100aによって遅延された情報信号SAとを入力とし、これら両信号の排他的論理和信号を第1のパルス信号S1として論理和回路104に出力する。つまり、これら遅延回路100a及び排他的論理和回路100bで構成される第1のパルス発生回路100は、情報信号SAにおける状態値の変化に同期して、遅延回路100aの遅延時間分に相当するパルス幅を有する第1のパルス信号S1を出力する。これら遅延回路100a及び排他的論理和回路100bは、本発明における第2の遅延回路及び第1の排他的論理和回路に相当する構成要素である。

30

## 【0029】

第2のパルス発生回路101は、遅延回路101a及び排他的論理和回路101bから構成されている。遅延回路101aは、情報解読信号SBを入力とし、当該情報解読信号SBを所定時間だけ遅延させて排他的論理和回路101bに出力する。排他的論理和回路101bは、情報解読信号SBと遅延回路101aによって遅延された情報解読信号SBとを入力とし、これら両信号の排他的論理和信号を第2のパルス信号S2として論理和回路104に出力する。つまり、これら遅延回路101a及び排他的論理和回路101bで構成される第2のパルス発生回路101は、情報解読信号SBにおける状態値の変化に同期して、遅延回路101aの遅延時間分に相当するパルス幅を有する第2のパルス信号S2を出力する。これら遅延回路101a及び排他的論理和回路101bは、本発明における第3の遅延回路及び第2の排他的論理和回路に相当する構成要素である。

40

## 【0030】

論理和回路102は、第1のパルス信号S1と第2のパルス信号S2との論理和信号S3を遅延回路103に出力する。遅延回路103は、論理和信号S3を所定時間だけ遅延させ、遅延パルス信号S4として一致検出回路104及びシフトレジスタ105に出力する。この遅延回路103は本発明における第1の遅延回路に相当する構成要素である。

## 【0031】

一致検出回路104は、カウンタ回路104a及び論理積回路104bから構成されてい

50

る。カウンタ回路 104a は、最大カウント数が情報信号 SA に含まれる 1 情報分のビット数と同一に設定されており、遅延パルス信号 S4 に同期してカウント動作を行い、カウント値を示すビットデータをパラレルに出力する。本実施形態では、情報信号 SA に含まれる 1 情報分のビット数を 4 ビットと想定し、カウンタ回路 104a における最大カウント数を「4」と設定する。つまり、カウンタ回路 104a は、「0」～「3」までをカウントすることができ、これら「0」(この時のビットデータは 00)～「3」(この時のビットデータは 11) を示す 2 ビットのビットデータをパラレルに論理積回路 104b に出力する。また、このカウンタ回路 104a は、最大カウント数(つまり「3」)までカウントした場合、次は自動的に「0」からカウントを開始する。論理積回路 104b は、カウンタ回路 104a からパラレルに出力される 2 ビットのビットデータの論理積信号を一致検出信号 S5 としてコントローラ 106 に出力する。つまり、論理積回路 104b は、カウンタ回路 104a からパラレルに出力される 2 ビットのビットデータが「3」を示す場合にハイレベルの一致検出信号 S5 を出力する。このように、一致検出回路 104 は、遅延パルス信号 S4 に同期してカウント動作を行い、カウント値が情報信号 SA に含まれる 1 情報分のビット数「4」と一致した場合に、ハイレベルの一致検出信号 S5 を出力する。

#### 【0032】

シフトレジスタ 105 は、情報信号 SA と遅延パルス信号 S4 とを入力とし、遅延パルス信号 S4 に同期して情報信号 SA をシリアル - パラレル変換するシリアル - パラレル変換回路である。つまり、情報信号 SA に含まれる 1 情報分のビット数を 4 ビットと想定すると、シフトレジスタ 105 は、シリアルデータである情報信号 SA を、1 ビット目のビットデータ D<sub>1</sub>、2 ビット目のビットデータ D<sub>2</sub>、3 ビット目のビットデータ D<sub>3</sub>、4 ビット目のビットデータ D<sub>4</sub> にパラレル変換してコントローラ 106 に出力する。コントローラ 106 は、一致検出信号 S5 に同期して、シリアル - パラレル変換された情報信号 SA (つまりビットデータ D<sub>1</sub>～D<sub>4</sub>) を取得し、当該ビットデータ D<sub>1</sub>～D<sub>4</sub> を用いて所定の信号処理を行う。シフトレジスタ 105 は本発明におけるシリアル - パラレル変換回路に相当し、コントローラ 106 は本発明における信号処理回路に相当する構成要素である。

なお、以上の説明では、送信装置 10 及び受信装置 20 を、ハイレベルをアクティブ状態とした正論理回路で構成した場合を例示したが、これに限らず、負論理回路で構成しても良い。

#### 【0033】

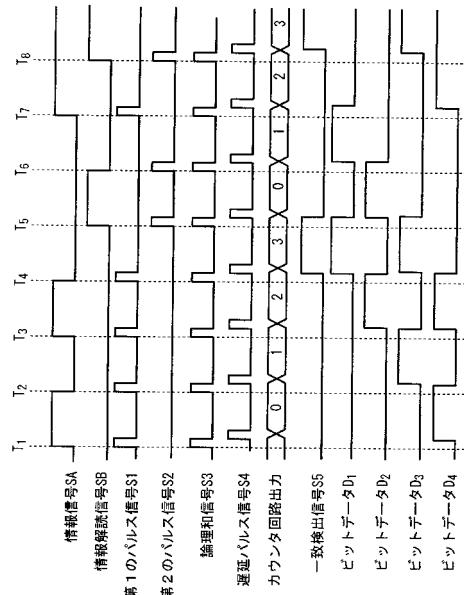

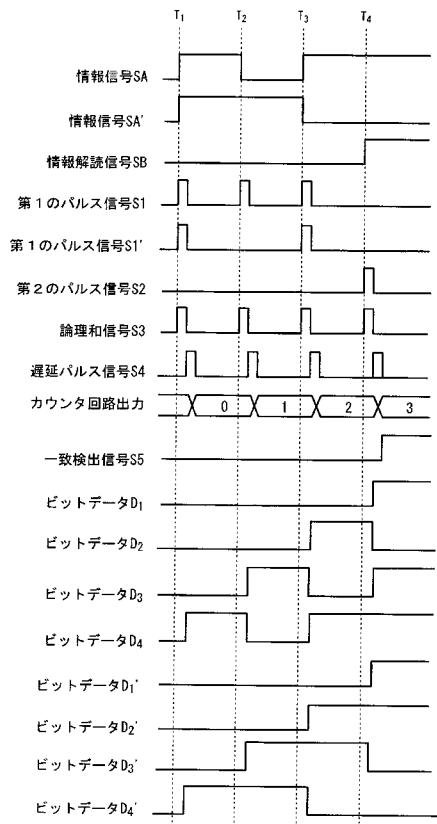

次に、上記のように構成された本実施形態に係る通信システムの動作について、図 3 のタイミングチャートを参照して説明する。なお、以下では、送信装置 10 の信号生成部 10a が、情報信号 SA として 4 ビットデータ「1010」と「0011」とを生成して送信する場合を想定して説明する。なお、初期状態において情報信号 SA 及び情報解読信号 SB はローレベルであるとする。

#### 【0034】

まず、時刻 T<sub>1</sub>において、送信装置 10 の信号生成部 10a は、情報信号 SA をハイレベル(「1」)に制御し、送信部 10b を介して送信する。この時、信号生成部 10a は、情報信号 SA の状態値が前回(初期状態)の状態値から変化したので、状態値が変化しない情報解読信号 SB (つまりローレベルの情報解読信号 SB) を生成し、送信部 10b を介して送信する。このように、時刻 T<sub>1</sub>では情報信号 SA の状態値がローレベルからハイレベルに変化するため、受信装置 20 の情報取得部 20a における第 1 のパルス発生回路 100 は、情報信号 SA の状態値の変化に同期してハイレベルの第 1 のパルス信号 S1 を論理和回路 102 に出力する。一方、情報解読信号 SB はローレベルに維持され変化がないため、第 2 のパルス発生回路 101 はローレベルの第 2 のパルス信号 S2 を論理和回路 102 に出力する。

#### 【0035】

論理和回路 102 にはハイレベルの第 1 のパルス信号 S1 とローレベルの第 2 のパルス

信号 S<sub>2</sub> とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S<sub>3</sub> が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S<sub>3</sub> を所定時間だけ遅延させ、遅延パルス信号 S<sub>4</sub> としてカウンタ回路 104a 及びシフトレジスタ 105 に出力する。カウンタ回路 104a は、遅延パルス信号 S<sub>4</sub> に同期してカウント動作を行い、「0」を示す 2 ビットのビットデータ（つまり「00」）をパラレルに論理積回路 104b に出力する。つまり、この時点ではカウント値が情報信号 S<sub>A</sub> に含まれる 1 情報分のビット数「4」と一致していないため、論理積回路 104b からローレベルの一致検出信号 S<sub>5</sub> がコントローラ 106 に出力される。

#### 【0036】

シフトレジスタ 105 は、遅延パルス信号 S<sub>5</sub> に同期して情報信号 S<sub>A</sub> をシフトしている、ここではビットデータ D<sub>4</sub> がハイレベルに制御され、ビットデータ D<sub>3</sub> ~ D<sub>1</sub> はローレベルに制御される。一方、コントローラ 106 は、ローレベルの一致検出信号 S<sub>5</sub> が入力されるので、シフトレジスタ 105 から出力されるビットデータ D<sub>1</sub> ~ D<sub>4</sub> の取得は行わない。10

#### 【0037】

次に、時刻 T<sub>2</sub> において、送信装置 10 の信号生成部 10a は、情報信号 S<sub>A</sub> をローレベル（「0」）に制御し、送信部 10b を介して送信する。この時、信号生成部 10a は、情報信号 S<sub>A</sub> の状態値が前回の状態値から変化したので、状態値が変化しない情報解読信号 S<sub>B</sub>（つまりローレベルの情報解読信号 S<sub>B</sub>）を生成し、送信部 10b を介して送信する。このように、時刻 T<sub>2</sub> では情報信号 S<sub>A</sub> の状態値がハイレベルからローレベルに変化するため、受信装置 20 の情報取得部 20a における第 1 のパルス発生回路 100 は、情報信号 S<sub>A</sub> の状態値の変化に同期してハイレベルの第 1 のパルス信号 S<sub>1</sub> を論理和回路 102 に出力する。一方、情報解読信号 S<sub>B</sub> はローレベルに維持され変化がないため、第 2 のパルス発生回路 101 はローレベルの第 2 のパルス信号 S<sub>2</sub> を論理和回路 102 に出力する。20

#### 【0038】

論理和回路 102 にはハイレベルの第 1 のパルス信号 S<sub>1</sub> とローレベルの第 2 のパルス信号 S<sub>2</sub> とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S<sub>3</sub> が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S<sub>3</sub> を所定時間だけ遅延させ、遅延パルス信号 S<sub>4</sub> としてカウンタ回路 104a 及びシフトレジスタ 105 に出力する。カウンタ回路 104a は、遅延パルス信号 S<sub>4</sub> に同期してカウント動作を行い、「1」を示す 2 ビットのビットデータ（つまり「01」）をパラレルに論理積回路 104b に出力する。つまり、この時点ではカウント値が情報信号 S<sub>A</sub> に含まれる 1 情報分のビット数「4」と一致していないため、論理積回路 104b からローレベルの一致検出信号 S<sub>5</sub> がコントローラ 106 に出力される。30

#### 【0039】

シフトレジスタ 105 は、遅延パルス信号 S<sub>5</sub> に同期して情報信号 S<sub>A</sub> をシフトしている、ここではビットデータ D<sub>4</sub>、D<sub>2</sub> 及び D<sub>1</sub> はローレベル、ビットデータ D<sub>3</sub> はハイレベルに制御される。一方、コントローラ 106 は、ローレベルの一致検出信号 S<sub>5</sub> が入力されるので、シフトレジスタ 105 から出力されるビットデータ D<sub>1</sub> ~ D<sub>4</sub> の取得は行わない。40

#### 【0040】

次に、時刻 T<sub>3</sub> において、送信装置 10 の信号生成部 10a は、情報信号 S<sub>A</sub> をハイレベル（「1」）に制御し、送信部 10b を介して送信する。この時、信号生成部 10a は、情報信号 S<sub>A</sub> の状態値が前回の状態値から変化したので、状態値が変化しない情報解読信号 S<sub>B</sub>（つまりローレベルの情報解読信号 S<sub>B</sub>）を生成し、送信部 10b を介して送信する。このように、時刻 T<sub>3</sub> では情報信号 S<sub>A</sub> の状態値がローレベルからハイレベルに変化するため、受信装置 20 の情報取得部 20a における第 1 のパルス発生回路 100 は、情報信号 S<sub>A</sub> の状態値の変化に同期してハイレベルの第 1 のパルス信号 S<sub>1</sub> を論理和回路 102 に出力する。一方、情報解読信号 S<sub>B</sub> はローレベルに維持され変化がないため、第 250

のパルス発生回路 101 はローレベルの第 2 のパルス信号 S2 を論理和回路 102 に出力する。

#### 【0041】

論理和回路 102 にはハイレベルの第 1 のパルス信号 S1 とローレベルの第 2 のパルス信号 S2 とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S3 が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S3 を所定時間だけ遅延させ、遅延パルス信号 S4 としてカウンタ回路 104a 及びシフトレジスタ 105 に出力する。カウンタ回路 104a は、遅延パルス信号 S4 に同期してカウント動作を行い、「2」を示す 2 ビットのビットデータ（つまり「10」）をパラレルに論理積回路 104b に出力する。つまり、この時点ではカウント値が情報信号 SA に含まれる 1 情報分のビット数「4」と一致していないため、論理積回路 104b からローレベルの一一致検出信号 S5 がコントローラ 106 に出力される。10

#### 【0042】

シフトレジスタ 105 は、遅延パルス信号 S5 に同期して情報信号 SA をシフトしていく、ここではビットデータ D4 及び D2 はハイレベル、ビットデータ D3 及び D1 はローレベルに制御される。一方、コントローラ 106 は、ローレベルの一一致検出信号 S5 が入力されるので、シフトレジスタ 105 から出力されるビットデータ D1 ~ D4 の取得は行わない。

#### 【0043】

次に、時刻 T4において、送信装置 10 の信号生成部 10a は、情報信号 SA をローレベル（「0」）に制御し、送信部 10b を介して送信する。この時、信号生成部 10a は、情報信号 SA の状態値が前回の状態値から変化したので、状態値が変化しない情報解読信号 SB（つまりローレベルの情報解読信号 SB）を生成し、送信部 10b を介して送信する。このように、時刻 T4 では情報信号 SA の状態値がハイレベルからローレベルに変化するため、受信装置 20 の情報取得部 20a における第 1 のパルス発生回路 100 は、情報信号 SA の状態値の変化に同期してハイレベルの第 1 のパルス信号 S1 を論理和回路 102 に出力する。一方、情報解読信号 SB はローレベルに維持され変化がないため、第 2 のパルス発生回路 101 はローレベルの第 2 のパルス信号 S2 を論理和回路 102 に出力する。20

#### 【0044】

論理和回路 102 にはハイレベルの第 1 のパルス信号 S1 とローレベルの第 2 のパルス信号 S2 とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S3 が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S3 を所定時間だけ遅延させ、遅延パルス信号 S4 としてカウンタ回路 104a 及びシフトレジスタ 105 に出力する。カウンタ回路 104a は、遅延パルス信号 S4 に同期してカウント動作を行い、「3」を示す 2 ビットのビットデータ（つまり「11」）をパラレルに論理積回路 104b に出力する。つまり、この時点でカウント値が情報信号 SA に含まれる 1 情報分のビット数「4」と一致するため、論理積回路 104b からハイレベルの一一致検出信号 S5 がコントローラ 106 に出力される。30

#### 【0045】

シフトレジスタ 105 は、遅延パルス信号 S5 に同期して情報信号 SA をシフトしていく、ここではビットデータ D4 及び D2 はローレベル、ビットデータ D3 及び D1 はハイレベルに制御される。一方、コントローラ 106 は、ハイレベルの一一致検出信号 S5 が入力されるので、シフトレジスタ 105 から出力されるビットデータ D1 ~ D4 の取得を行う。つまり、情報信号 SA に含まれる 1 情報分の 4 ビットデータ「1010」がコントローラ 106 に取得されることになる。40

#### 【0046】

次に、時刻 T5 において、送信装置 10 の信号生成部 10a は、次の 1 情報分の 4 ビットデータ「0011」を送信するために、情報信号 SA をローレベル（「0」）に制御し、送信部 10b を介して送信する。この時、信号生成部 10a は、情報信号 SA の状態値が

10

20

30

40

50

前回の状態値から変化しないので、状態値を変化させた情報解読信号 S B (つまりハイレベルの情報解読信号 S B )を生成し、送信部 10 bを介して送信する。このように、時刻 T<sub>5</sub>では情報信号 S A の状態値はローレベルを維持するため、受信装置 20 の情報取得部 20 aにおける第 1 のパルス発生回路 100 は、ローレベルの第 1 のパルス信号 S 1 を論理和回路 102 に出力する。一方、情報解読信号 S B の状態値はローレベルからハイレベルに変化するため、第 2 のパルス発生回路 101 は情報解読信号 S B の状態値の変化に同期してハイレベルの第 2 のパルス信号 S 2 を論理和回路 102 に出力する。

#### 【 0 0 4 7 】

論理和回路 102 にはローレベルの第 1 のパルス信号 S 1 とハイレベルの第 2 のパルス信号 S 2 とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S 3 が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S 3 を所定時間だけ遅延させ、遅延パルス信号 S 4 としてカウンタ回路 104a 及びシフトレジスタ 105 に出力する。カウンタ回路 104a は、遅延パルス信号 S 4 に同期してカウント動作を行い、「0」を示す 2 ビットのビットデータ (つまり「00」) をパラレルに論理積回路 104b に出力する。つまり、この時点ではカウント値が情報信号 S A に含まれる 1 情報分のビット数「4」と一致しないため、論理積回路 104b からローレベルの一一致検出信号 S 5 がコントローラ 106 に出力される。

10

#### 【 0 0 4 8 】

シフトレジスタ 105 は、遅延パルス信号 S 5 に同期して情報信号 S A をシフトしていく、ここではビットデータ D<sub>4</sub>、D<sub>3</sub> 及び D<sub>1</sub> はローレベル、ビットデータ D<sub>2</sub> はハイレベルに制御される。一方、コントローラ 106 は、ローレベルの一一致検出信号 S 5 が入力されるので、シフトレジスタ 105 から出力されるビットデータ D<sub>1</sub> ~ D<sub>4</sub> の取得を行わない。

20

#### 【 0 0 4 9 】

次に、時刻 T<sub>6</sub>において、送信装置 10 の信号生成部 10a は、情報信号 S A をローレベル (「0」) に制御し、送信部 10 bを介して送信する。この時、信号生成部 10a は、情報信号 S A の状態値が前回の状態値から変化しないので、状態値を変化させた情報解読信号 S B (つまりローレベルの情報解読信号 S B )を送信部 10 bを介して送信する。このように、時刻 T<sub>6</sub>では情報信号 S A の状態値はローレベルを維持するため、受信装置 20 の情報取得部 20 aにおける第 1 のパルス発生回路 100 は、ローレベルの第 1 のパルス信号 S 1 を論理和回路 102 に出力する。一方、情報解読信号 S B の状態値はハイレベルからローレベルに変化するため、第 2 のパルス発生回路 101 は情報解読信号 S B の状態値の変化に同期してハイレベルの第 2 のパルス信号 S 2 を論理和回路 102 に出力する。

30

#### 【 0 0 5 0 】

論理和回路 102 にはローレベルの第 1 のパルス信号 S 1 とハイレベルの第 2 のパルス信号 S 2 とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S 3 が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S 3 を所定時間だけ遅延させ、遅延パルス信号 S 4 としてカウンタ回路 104a 及びシフトレジスタ 105 に出力する。カウンタ回路 104a は、遅延パルス信号 S 4 に同期してカウント動作を行い、「1」を示す 2 ビットのビットデータ (つまり「01」) をパラレルに論理積回路 104b に出力する。つまり、この時点ではカウント値が情報信号 S A に含まれる 1 情報分のビット数「4」と一致しないため、論理積回路 104b からローレベルの一一致検出信号 S 5 がコントローラ 106 に出力される。

40

#### 【 0 0 5 1 】

シフトレジスタ 105 は、遅延パルス信号 S 5 に同期して情報信号 S A をシフトしていく、ここではビットデータ D<sub>4</sub> ~ D<sub>2</sub> はローレベル、ビットデータ D<sub>1</sub> はハイレベルに制御される。一方、コントローラ 106 は、ローレベルの一一致検出信号 S 5 が入力されるので、シフトレジスタ 105 から出力されるビットデータ D<sub>1</sub> ~ D<sub>4</sub> の取得を行わない。

#### 【 0 0 5 2 】

50

次に、時刻  $T_7$  において、送信装置 10 の信号生成部 10a は、情報信号 SA をハイレベル（「1」）に制御し、送信部 10b を介して送信する。この時、信号生成部 10a は、情報信号 SA の状態値が前回の状態値から変化したので、状態値が変化しない情報解読信号 SB（つまりローレベルの情報解読信号 SB）を送信部 10b を介して送信する。このように、時刻  $T_7$  では情報信号 SA の状態値がローレベルからハイレベルに変化するため、受信装置 20 の情報取得部 20a における第 1 のパルス発生回路 100 は、情報信号 SA の状態値の変化に同期してハイレベルの第 1 のパルス信号 S1 を論理和回路 102 に出力する。一方、情報解読信号 SB はローレベルに維持され変化がないため、第 2 のパルス発生回路 101 はローレベルの第 2 のパルス信号 S2 を論理和回路 102 に出力する。

## 【0053】

論理和回路 102 にはハイレベルの第 1 のパルス信号 S1 とローレベルの第 2 のパルス信号 S2 とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S3 が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S3 を所定時間だけ遅延させ、遅延パルス信号 S4 としてカウンタ回路 104a 及びシフトレジスタ 105 に出力する。カウンタ回路 104a は、遅延パルス信号 S4 に同期してカウント動作を行い、「2」を示す 2 ビットのビットデータ（つまり「10」）をパラレルに論理積回路 104b に出力する。つまり、この時点ではカウント値が情報信号 SA に含まれる 1 情報分のビット数「4」と一致していないため、論理積回路 104b からローレベルの一致検出信号 S5 がコントローラ 106 に出力される。

## 【0054】

シフトレジスタ 105 は、遅延パルス信号 S5 に同期して情報信号 SA をシフトしていく、ここではビットデータ D4 はハイレベル、ビットデータ D3 ~ D1 はローレベルに制御される。一方、コントローラ 106 は、ローレベルの一致検出信号 S5 が入力されるので、シフトレジスタ 105 から出力されるビットデータ D1 ~ D4 の取得は行わない。

## 【0055】

次に、時刻  $T_8$  において、送信装置 10 の信号生成部 10a は、情報信号 SA をハイレベル（「1」）に制御し、送信部 10b を介して送信する。この時、信号生成部 10a は、情報信号 SA の状態値が前回の状態値から変化しないので、状態値を変化させた情報解読信号 SB（つまりハイレベルの情報解読信号 SB）を送信部 10b を介して送信する。このように、時刻  $T_8$  では情報信号 SA の状態値はハイレベルを維持するため、受信装置 20 の情報取得部 20a における第 1 のパルス発生回路 100 は、ローレベルの第 1 のパルス信号 S1 を論理和回路 102 に出力する。一方、情報解読信号 SB の状態値はローレベルからハイレベルに変化するため、第 2 のパルス発生回路 101 は情報解読信号 SB の状態値の変化に同期してハイレベルの第 2 のパルス信号 S2 を論理和回路 102 に出力する。

## 【0056】

論理和回路 102 にはローレベルの第 1 のパルス信号 S1 とハイレベルの第 2 のパルス信号 S2 とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S3 が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S3 を所定時間だけ遅延させ、遅延パルス信号 S4 としてカウンタ回路 104a 及びシフトレジスタ 105 に出力する。カウンタ回路 104a は、遅延パルス信号 S4 に同期してカウント動作を行い、「3」を示す 2 ビットのビットデータ（つまり「11」）をパラレルに論理積回路 104b に出力する。つまり、この時点でカウント値が情報信号 SA に含まれる 1 情報分のビット数「4」と一致するため、論理積回路 104b からハイレベルの一致検出信号 S5 がコントローラ 106 に出力される。

## 【0057】

シフトレジスタ 105 は、遅延パルス信号 S5 に同期して情報信号 SA をシフトしていく、ここではビットデータ D4 及び D3 はハイレベル、ビットデータ D2 及び D1 はローレベルに制御される。一方、コントローラ 106 は、ハイレベルの一致検出信号 S5 が入力されるので、シフトレジスタ 105 から出力されるビットデータ D1 ~ D4 の取得を行

10

20

30

40

50

う。

つまり、情報信号 S A に含まれる 1 情報分の 4 ビットデータ「0 0 1 1」がコントローラ 106 に取得されることになる。以降は、情報信号 S A の状態値（情報）に応じて上記と同様な動作が繰り返される。

#### 【0058】

以上のように、本実施形態に係る通信システムでは、送信装置 10において、情報信号 S A の状態値が変化する場合には自身の状態値が変化せず、情報信号 S A の状態値が変化しない場合には自身の状態値が変化する情報解読信号 S B を生成して情報信号 S A と共に送信し、受信装置 20では、受信した情報信号 S A 及び前記情報解読信号 S B における状態値の変化点を基準にして情報信号 S A の状態値を取得する。これにより、情報信号 S A と情報解読信号 S Bとの区別（つまり、どちらが本当の情報を示すかを区別すること）や、それぞれの信号の役割を判別すること（つまり、両信号がどのようなプロトコルで生成されているかを判別すること）が困難となり、仮に第三者が両信号を読み取ったとしてもその復号化を行うことができず、情報の漏洩を防止することが可能となる。その結果、データ信号等の情報信号を通信する際ににおけるセキュリティの向上を図ることが可能である。

10

#### 【0059】

なお、本発明は、上記実施形態に限定されるものではなく、例えば以下のような変形例が考えられる。

20

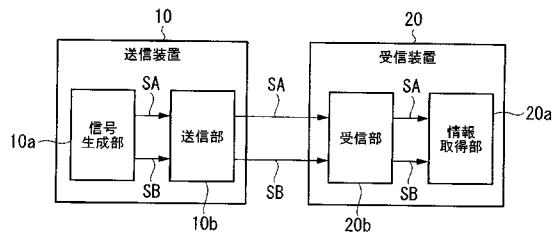

#### （1）複数の情報信号 S A を送信する場合

複数の情報信号 S A を送信する場合、つまり図 4 に示すように、例えば送信装置 10から 2 つの情報信号 S A 及び S A' が送信される場合について説明する。この場合、信号生成部 10a' は、2 つの情報信号 S A 及び S A' の各々が同じタイミングにおいて状態値が変化しない場合に自身の状態値が変化する情報解読信号 S B を生成する。一方、情報取得部 20a' は、受信した 2 つの情報信号 S A 及び S A' と、情報解読信号 S B における状態値の変化点を基準にして情報信号 S A 及び S A' の状態値を取得する。以下、2 つの情報信号 S A 及び S A' が送信される場合について具体的に説明する。

#### 【0060】

図 5 は、2 つの情報信号 S A 及び S A' が送信される場合の情報取得部 20a' の内部構成ブロック図である。なお、図 5 において、図 2 と同様な構成要素には同一符号を付し、説明を省略する。この図 5 に示すように、図 2 と異なる点は、情報信号 S A' に対応する第 1 のパルス発生回路 200 とシフトレジスタ 300 とが新たに設けられていることである。つまり、第 1 のパルス発生回路 200 は、第 1 のパルス発生回路 100 と同様に、遅延回路 200a 及び排他的論理回路 200b から構成され、情報信号 S A' における状態値の変化に同期して、遅延回路 200a の遅延時間分に相当するパルス幅を有する第 1 のパルス信号 S 1' を論理回路 102 に出力する。

30

#### 【0061】

また、シフトレジスタ 300 は、情報信号 S A' と遅延パルス信号 S 4 とを入力とし、遅延パルス信号 S 4 に同期して情報信号 S A' をシリアル - パラレル変換するシリアル - パラレル変換回路である。つまり、情報信号 S A' に含まれる 1 情報分のビット数を 4 ビットと想定すると、シフトレジスタ 300 は、シリアルデータである情報信号 S A' を、1 ビット目のビットデータ D<sub>1</sub>' 、2 ビット目のビットデータ D<sub>2</sub>' 、3 ビット目のビットデータ D<sub>3</sub>' 、4 ビット目のビットデータ D<sub>4</sub>' にパラレル変換してコントローラ 106 に出力する。

40

#### 【0062】

図 6 は、2 つの情報信号 S A 及び S A' が送信される場合における本通信システムの動作を示すタイミングチャートである。なお、以下では、送信装置 10 の信号生成部 10a' が、情報信号 S A として 4 ビットデータ「1 0 1 1」を生成し、情報信号 S A' として 4 ビットデータ「1 1 0 0」を生成して送信する場合を想定して説明する。なお、初期状態において情報信号 S A 及び S A' 、情報解読信号 S B はローレベルであるとする。

50

## 【0063】

まず、時刻  $T_1$ において、送信装置 10 の信号生成部 10a'は、情報信号 SA 及び SA'をハイレベル（「1」）に制御し、送信部 10bを介して送信する。この時、信号生成部 10a'は、情報信号 SA 及び SA'の状態値が前回（初期状態）の状態値から変化したので、状態値が変化しない情報解読信号 SB（つまりローレベルの情報解読信号 SB）を送信部 10bを介して送信する。このように、時刻  $T_1$ では情報信号 SA の状態値がローレベルからハイレベルに変化するため、受信装置 20 の情報取得部 20a'における第 1 のパルス発生回路 100 は、情報信号 SA の状態値の変化に同期してハイレベルの第 1 のパルス信号 S1 を論理和回路 102 に出力する。また、第 1 のパルス発生回路 200 も、同様に情報信号 SA' の状態値の変化に同期してハイレベルの第 1 のパルス信号 S1' を論理和回路 102 に出力する。一方、情報解読信号 SB はローレベルに維持され変化がないため、第 2 のパルス発生回路 101 はローレベルの第 2 のパルス信号 S2 を論理和回路 102 に出力する。

10

## 【0064】

論理和回路 102 にはハイレベルの第 1 のパルス信号 S1 及び S1' とローレベルの第 2 のパルス信号 S2 とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S3 が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S3 を所定時間だけ遅延させ、遅延パルス信号 S4 としてカウンタ回路 104a、シフトレジスタ 105 及び 300 に出力する。カウンタ回路 104a は、遅延パルス信号 S4 に同期してカウント動作を行い、「0」を示す 2 ビットのビットデータ（つまり「00」）をパラレルに論理積回路 104b に出力する。つまり、この時点ではカウント値が情報信号 SA 及び SA' に含まれる 1 情報分のビット数「4」と一致していないため、論理積回路 104b からローレベルの一致検出信号 S5 がコントローラ 106 に出力される。

20

## 【0065】

シフトレジスタ 105 は、遅延パルス信号 S5 に同期して情報信号 SA をシフトしていく、ここではビットデータ D4 がハイレベルに制御され、ビットデータ D1 ~ D3 はローレベルに制御される。また、シフトレジスタ 300 は、遅延パルス信号 S5 に同期して情報信号 SA' をシフトしていく、ここではビットデータ D4' はハイレベルに制御され、ビットデータ D1' ~ D3' はローレベルに制御される。一方、コントローラ 106 は、ローレベルの一致検出信号 S5 が入力されるので、シフトレジスタ 105 及び 300 から出力されるビットデータの取得は行わない。

30

## 【0066】

次に、時刻  $T_2$ において、送信装置 10 の信号生成部 10a'は、情報信号 SA をローレベル（「0」）に制御し、情報信号 SA' をハイレベル（「1」）に制御し、送信部 10bを介して送信する。この時、信号生成部 10a'は、情報信号 SA の状態値が前回の状態値から変化したので、状態値が変化しない情報解読信号 SB（つまりローレベルの情報解読信号 SB）を送信部 10bを介して送信する。このように、時刻  $T_2$ では情報信号 SA の状態値がハイレベルからローレベルに変化するため、受信装置 20 の情報取得部 20a'における第 1 のパルス発生回路 100 は、情報信号 SA の状態値の変化に同期してハイレベルの第 1 のパルス信号 S1 を論理和回路 102 に出力する。また、第 1 のパルス発生回路 200 は、情報信号 SA' の状態値が変化しないため、ローレベルの第 1 のパルス信号 S1' を論理和回路 102 に出力する。一方、情報解読信号 SB はローレベルに維持され変化がないため、第 2 のパルス発生回路 101 はローレベルの第 2 のパルス信号 S2 を論理和回路 102 に出力する。

40

## 【0067】

論理和回路 102 にはハイレベルの第 1 のパルス信号 S1 とローレベルの第 1 のパルス信号 S1' 及び第 2 のパルス信号 S2 とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S3 が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S3 を所定時間だけ遅延させ、遅延パルス信号 S4 としてカ

50

ウンタ回路 104a、シフトレジスタ 105 及び 300 に出力する。カウンタ回路 104a は、遅延パルス信号 S4 に同期してカウント動作を行い、「1」を示す 2 ビットのビットデータ（つまり「01」）をパラレルに論理積回路 104b に出力する。つまり、この時点ではカウント値が情報信号 SA 及び SA' に含まれる 1 情報分のビット数「4」と一致していないため、論理積回路 104b からローレベルの一致検出信号 S5 がコントローラ 106 に出力される。

#### 【0068】

シフトレジスタ 105 は、遅延パルス信号 S5 に同期して情報信号 SA をシフトしていく、ここではビットデータ D<sub>4</sub>、D<sub>2</sub>、D<sub>1</sub> はローレベルに制御され、ビットデータ D<sub>3</sub> はハイレベルに制御される。また、シフトレジスタ 300 は、遅延パルス信号 S5 に同期して情報信号 SA' をシフトしていく、ここではビットデータ D<sub>4'</sub> 及び D<sub>3'</sub> はハイレベルに制御され、ビットデータ D<sub>2'</sub> 及び D<sub>1'</sub> はローレベルに制御される。一方、コントローラ 106 は、ローレベルの一致検出信号 S5 が入力されるので、シフトレジスタ 105 及び 300 から出力されるビットデータの取得は行わない。

10

#### 【0069】

次に、時刻 T<sub>3</sub>において、送信装置 10 の信号生成部 10a' は、情報信号 SA をハイレベル（「1」）に制御し、情報信号 SA' をローレベル（「0」）に制御し、送信部 10b を介して送信する。この時、信号生成部 10a' は、情報信号 SA 及び SA' の状態値が前回の状態値から変化したので、状態値が変化しない情報解読信号 SB（つまりローレベルの情報解読信号 SB）を送信部 10b を介して送信する。このように、時刻 T<sub>3</sub> では情報信号 SA の状態値がローレベルからハイレベルに変化するため、受信装置 20 の情報取得部 20a' における第 1 のパルス発生回路 100 は、情報信号 SA の状態値の変化に同期してハイレベルの第 1 のパルス信号 S1 を論理和回路 102 に出力する。また、第 1 のパルス発生回路 200 も、同様に情報信号 SA' の状態値の変化に同期してハイレベルの第 1 のパルス信号 S1' を論理和回路 102 に出力する。一方、情報解読信号 SB はローレベルに維持され変化がないため、第 2 のパルス発生回路 101 はローレベルの第 2 のパルス信号 S2 を論理和回路 102 に出力する。

20

#### 【0070】

論理和回路 102 にはハイレベルの第 1 のパルス信号 S1 及び S1' とローレベルの第 2 のパルス信号 S2 とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S3 が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S3 を所定時間だけ遅延させ、遅延パルス信号 S4 としてカウンタ回路 104a、シフトレジスタ 105 及び 300 に出力する。カウンタ回路 104a は、遅延パルス信号 S4 に同期してカウント動作を行い、「2」を示す 2 ビットのビットデータ（つまり「10」）をパラレルに論理積回路 104b に出力する。つまり、この時点ではカウント値が情報信号 SA 及び SA' に含まれる 1 情報分のビット数「4」と一致していないため、論理積回路 104b からローレベルの一致検出信号 S5 がコントローラ 106 に出力される。

30

#### 【0071】

シフトレジスタ 105 は、遅延パルス信号 S5 に同期して情報信号 SA をシフトしていく、ここではビットデータ D<sub>4</sub> 及び D<sub>2</sub> はハイレベルに制御され、ビットデータ D<sub>3</sub> 及び D<sub>1</sub> はローレベルに制御される。また、シフトレジスタ 300 は、遅延パルス信号 S5 に同期して情報信号 SA' をシフトしていく、ここではビットデータ D<sub>4'</sub> 及び D<sub>1'</sub> はローレベルに制御され、ビットデータ D<sub>3'</sub> 及び D<sub>2'</sub> はハイレベルに制御される。一方、コントローラ 106 は、ローレベルの一致検出信号 S5 が入力されるので、シフトレジスタ 105 及び 300 から出力されるビットデータの取得は行わない。

40

#### 【0072】

次に、時刻 T<sub>4</sub>において、送信装置 10 の信号生成部 10a' は、情報信号 SA をハイレベル（「1」）に制御し、情報信号 SA' をローレベル（「0」）に制御し、送信部 10b を介して送信する。この時、信号生成部 10a' は、情報信号 SA 及び SA' の状態値

50

が両方とも前回の状態値から変化しないので、状態値を変化させた情報解読信号 S B (つまりハイレベルの情報解読信号 S B ) を送信部 10 b を介して送信する。このように、時刻 T<sub>4</sub> では情報信号 S A の状態値がハイレベルに維持されるため、受信装置 20 の情報取得部 20 a' における第 1 のパルス発生回路 100 は、ローレベルの第 1 のパルス信号 S 1 を論理和回路 102 に出力する。また、情報信号 S A' の状態値はローレベルに維持されるため、第 1 のパルス発生回路 200 も、同様にローレベルの第 1 のパルス信号 S 1' を論理和回路 102 に出力する。一方、情報解読信号 S B はローレベルからハイレベルに変化するため、第 2 のパルス発生回路 101 は情報解読信号 S B に同期してハイレベルの第 2 のパルス信号 S 2 を論理和回路 102 に出力する。

## 【0073】

10

論理和回路 102 にはローレベルの第 1 のパルス信号 S 1 及び S 1' とハイレベルの第 2 のパルス信号 S 2 とが入力されるため、論理和回路 102 からハイレベルのパルス信号である論理和信号 S 3 が出力される。遅延回路 103 は、ハイレベルのパルス信号である論理和信号 S 3 を所定時間だけ遅延させ、遅延パルス信号 S 4 としてカウンタ回路 104 a、シフトレジスタ 105 及び 300 に出力する。カウンタ回路 104 a は、遅延パルス信号 S 4 に同期してカウント動作を行い、「3」を示す 2 ビットのビットデータ (つまり「11」) をパラレルに論理積回路 104 b に出力する。つまり、この時点でカウント値が情報信号 S A 及び S A' に含まれる 1 情報分のビット数「4」と一致するため、論理積回路 104 b からハイレベルの一致検出信号 S 5 がコントローラ 106 に出力される。

## 【0074】

20

シフトレジスタ 105 は、遅延パルス信号 S 5 に同期して情報信号 S A をシフトしていく、ここではビットデータ D<sub>4</sub>、D<sub>2</sub> 及び D<sub>1</sub> はハイレベルに制御され、ビットデータ D<sub>2</sub> はローレベルに制御される。また、シフトレジスタ 300 は、遅延パルス信号 S 5 に同期して情報信号 S A' をシフトしていく、ここではビットデータ D<sub>4'</sub> 及び D<sub>3'</sub> はローレベルに制御され、ビットデータ D<sub>2'</sub> 及び D<sub>1'</sub> はハイレベルに制御される。一方、コントローラ 106 は、ハイレベルの一致検出信号 S 5 が入力されるので、シフトレジスタ 105 及び 300 から出力されるビットデータの取得を行う。

つまり、情報信号 S A に含まれる 1 情報分の 4 ビットデータ「1011」と、情報信号 S A' に含まれる 1 情報分の 4 ビットデータ「1100」とがコントローラ 106 に取得されることになる。

30

## 【0075】

以上のように、2つの情報信号 S A 及び S A' を送信する場合、送信側は、2つの情報信号 S A 及び S A' の各々が同じタイミングにおいて状態値が変化しない場合に自身の状態値が変化する情報解読信号 S B を送信し、受信側は、受信した2つの情報信号 S A 及び S A' と、情報解読信号 S B とにおける状態値の変化点を基準にして情報信号 S A 及び S A' の状態値を取得することにより、送信する情報信号が複数の場合であっても情報の漏洩を防止し、セキュリティの向上を図ることができる。

なお、2つより多い情報信号を送信する場合でも、各々の情報信号に対応する第1のパルス発生回路とシフトレジスタとを設ければ良く、情報解読信号は1つだけ送信すれば良い。

40

## 【0076】

## (2) 他の通信システムへの適用

上記実施形態では、通信システムの一例として電子回路における回路ブロック同士の通信を例示して説明したが、本発明はこれ以外の通信システムにも適用可能である。例えば、

送信装置と受信装置とが、I P (Internet Protocol) 網や L A N (Local Area Network) 等を用いたネットワークによって相互に接続されているような通信システムにも適用可能である。このような通信システムでは、情報信号をパケット化して送信することが一般的であるので、送信装置側で情報信号と情報解読信号とをそれぞれパケット化して送信し、受信装置側で上述したような動作を行って情報信号を取得 (復号化) すれば良い。なお、情

50

報信号と情報解読信号とをそれぞれパケット化して送信する場合には、受信装置側において、情報信号及び情報解読信号が同相となるように位相合わせを行ってから情報取得部20aに入力する必要がある。

#### 【0077】

また、本発明は有線通信システムだけでなく、無線通信システムにも適用可能である。但し、無線通信システムに適用する場合、図7に示すように、送信装置10に無線送信部（無線送信手段）10b'を設け、受信装置20に無線受信部（無線受信手段）20b'を設ける必要がある。無線通信部10b'は、信号生成部10aから出力される情報信号SA及び情報解読信号SBの誤り訂正符号化、変調及びRF周波数帯への周波数変換を行ってRF信号を生成し、当該RF信号を送信用アンテナを介して受信装置20に送信する。無線受信部20b'は、受信用アンテナを介して受信したRF信号のIF周波数帯への周波数変換、復調、誤り訂正復号化などを行って情報信号SA及び情報解読信号SBを抽出し、これら抽出した情報信号SA及び情報解読信号SBを情報取得部20aに出力する。無線通信システムにおいても、これら情報信号SAと情報解読信号SBとをそれぞれパケット化して別のタイミングで個別に送信する場合は、受信装置側において、情報信号及び情報解読信号が同相となるように位相合わせを行ってから情報取得部20aに入力する必要がある。

10

20

30

#### 【図面の簡単な説明】

#### 【0078】

【図1】本発明の一実施形態に係る通信システムの構成ブロック図である。

【図2】本発明の一実施形態に係る情報取得部20aの内部構成ブロック図である。

【図3】本発明の一実施形態に係る通信システムの動作を示すタイミングチャートである。

【図4】本発明の一実施形態に係る通信システムにおいて、複数の情報信号を送信する場合の構成ブロック図である。

【図5】本発明の一実施形態に係る通信システムにおいて、複数の情報信号を送信する場合の情報取得部20a'の内部構成ブロック図である。

【図6】本発明の一実施形態に係る通信システムにおいて、複数の情報信号を送信する場合の動作を示すタイミングチャートである。

【図7】本発明の一実施形態に係る通信システムの変形例である。

#### 【符号の説明】

#### 【0079】

10 ... 送信装置、10a、10a' ... 信号生成部、10b... 送信部、10b' ... 無線送信部、

20 ... 受信装置、20a、20a' ... 情報取得部、20b... 受信部、20b' ... 無線受信部、

100、200 ... 第1のパルス発生回路、101 ... 第2のパルス発生回路、102 ... 論理和回路、

103 ... 遅延回路、104 ... 一致検出回路、105、300 ... シフトレジスタ、

106 ... コントローラ、100a、101a、200a... 遅延回路、100b、101b、

200b... 排他的論理和回路、104a... カウンタ回路、104b... 論理積回路

【 四 1 】

【 図 3 】

【 図 2 】

【 図 5 】

【図6】

【図7】