# (12) United States Patent

Taylor et al.

### (54) METHODS FOR OPERATING MEMORY **ELEMENTS**

(75) Inventors: Jennifer Taylor, Boise, ID (US); John D. Porter, Meridian, ID (US)

Assignee: Micron Technology, Inc., Boise, ID

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

Appl. No.: 13/159,288

Filed: Jun. 13, 2011 (22)

(65)**Prior Publication Data**

> US 2011/0242878 A1 Oct. 6, 2011

### Related U.S. Application Data

(60) Continuation of application No. 12/969,364, filed on Dec. 15, 2010, now Pat. No. 7,961,538, which is a division of application No. 12/165,273, filed on Jun. 30, 2008, now Pat. No. 7,864,609.

US 8,363,500 B2 (10) Patent No.: (45) **Date of Patent:** \*Jan. 29, 2013

(51) **Int. Cl.**

G11C 7/02 (2006.01)

(52)

Field of Classification Search .............................. 365/207, (58)365/189.15, 163, 148; 341/161 See application file for complete search history.

(56)**References Cited**

### U.S. PATENT DOCUMENTS

6,449,212 B1\* 9/2002 Toda et al. ...... 365/233.12 7,288,946 B2 \* 10/2007 Hargreaves et al. .......... 324/678

\* cited by examiner

Primary Examiner — Vu Le (74) Attorney, Agent, or Firm — Fletcher Yoder

### **ABSTRACT**

Methods for measuring the resistance of multiple memory elements are disclosed. The memory elements may be multibit memory and through precise measurement of resistance of the multi-bit memory elements, determination of how many and which memory elements fall into specific memory ranges can be accomplished. Furthermore, storage and/or display of this information may allow for the creation of resistance distribution histograms for modeling of one or more memory arrays.

### 25 Claims, 11 Drawing Sheets

FIG. 1

FIG. 3

FIG. 6

FIG. 9

# METHODS FOR OPERATING MEMORY ELEMENTS

# CROSS-REFERENCE TO RELATED APPLICATION

This application is a continuation of U.S. patent application Ser. No. 12/969,364, which was filed on Dec. 15, 2010, now U.S. Pat. No. 7,961,538, which issued on Jun. 14, 2011, which is a divisional of U.S. patent application Ser. No. 10 12/165,273, which was filed on Jun. 30, 2008, now U.S. Pat. No. 7,864,609, which issued on Jan. 4, 2011.

### BACKGROUND

### 1. Field of the Invention

Embodiments of the invention relate generally to determining resistance levels in phase change memory.

### 2. Description of the Related Art

Demands for memory capacity continue to increase in 20 modern electronic devices. At the same time, size of circuitry is at an increased premium as devices which utilize memory circuitry continue to shrink. One solution as to how to increase memory capacity while minimizing the amount of space occupied by memory circuitry has involved the development of memory elements that are capable of assuming more than two states. For example, some memory elements are capable of multi-bit (e.g., more than two state) storage. For instance, rather than outputting either a high or low voltage, the memory element may output four or eight different voltage levels, each level corresponding to a different data value.

One type of multi-bit storage memory is phase change memory. Phase change memory may store multi-bit data through resistance variations caused by phase changes of the 35 material used in the manufacture of the memory. The state of the material of which the phase change memory is composed may be switched between amorphous, partially crystalline, and crystalline states with the application of external influences, for example, heat. The different states of the material 40 each have distinct resistance properties that may be measured and associated with a data bit.

Conventional measuring techniques fail to adequately measure the differences in the resistance values of a phase change memory. This may lead to errors in the grouping of 45 resistance values of a plurality of phase change memory elements into a distribution curve, typically used to show the number of memory elements programmed to each of a plurality of different states. Without proper valuation of the resistance distribution of a memory array of phase change 50 memory elements, the individual memory elements may be programmed at resistance levels that overflow and corrupt data stored at other resistance levels. Alternatively, without proper valuation of the resistance distribution of a memory array, the difference between the levels (e.g., voltage) to be 55 sensed may be set at levels larger than required, which tends to reduce memory density and increase the cost of memory. Thus, there is a need for measuring techniques that can accurately determine the resistance ranges for phase change memory.

### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 illustrates an electronic device in accordance with an embodiment of the present invention;

FIG. 2 illustrates a block diagram of the electronic device illustrated of FIG. 1;

2

FIG. 3 illustrates a memory array of FIG. 2 in accordance with an embodiment of the present invention;

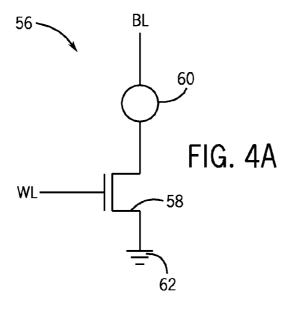

FIG. 4A illustrates a first memory element of FIG. 3 in accordance with an embodiment of the present invention;

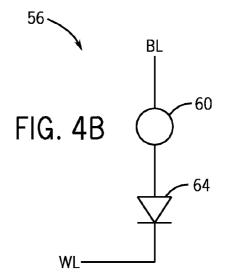

FIG. 4B illustrates a second memory element of FIG. 3 in accordance with an embodiment of the present invention;

FIG. 4C illustrates a third memory element of FIG. 3 in accordance with an embodiment of the present invention;

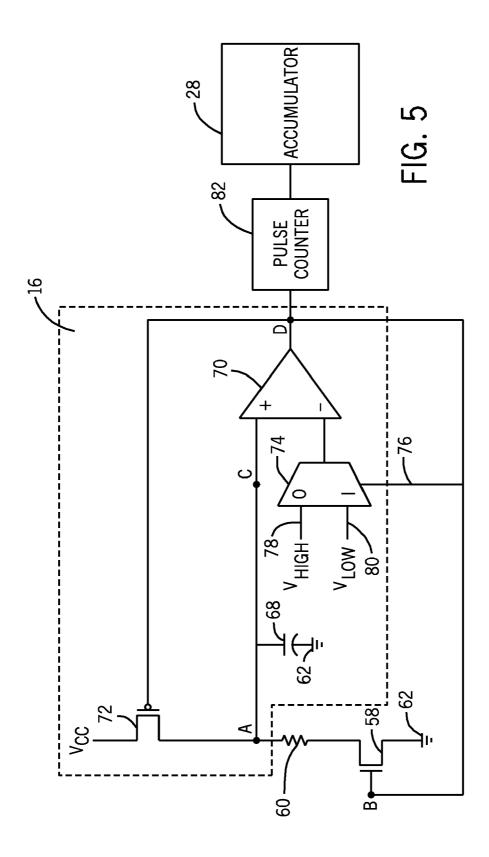

FIG. 5 illustrates a first quantizing circuit in accordance with an embodiment of the present invention;

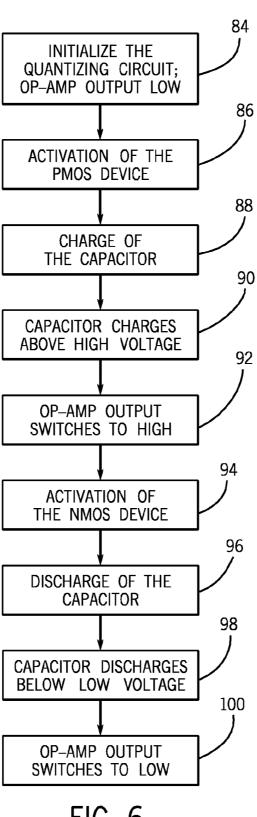

FIG. 6 is a flow chart illustrating the operation of the first quantizing circuit of FIG. 5;

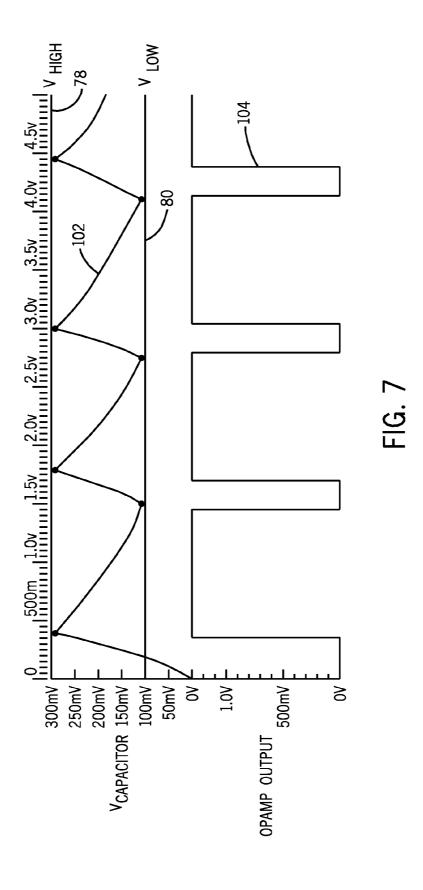

FIG. 7 is a graph representing the outputs of the first quantizing circuit of FIG. 5;

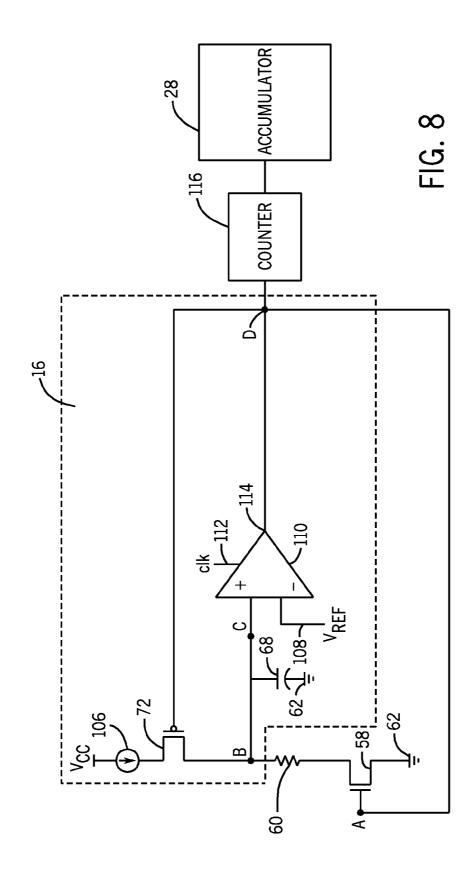

FIG. 8 illustrates a second quantizing circuit in accordance with an second embodiment of the present invention;

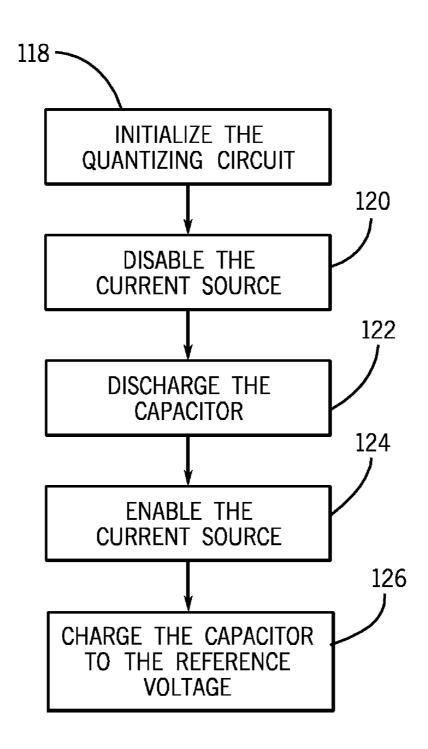

FIG. 9 is a flow chart illustrating the operation of the second quantizing circuit of FIG. 8;

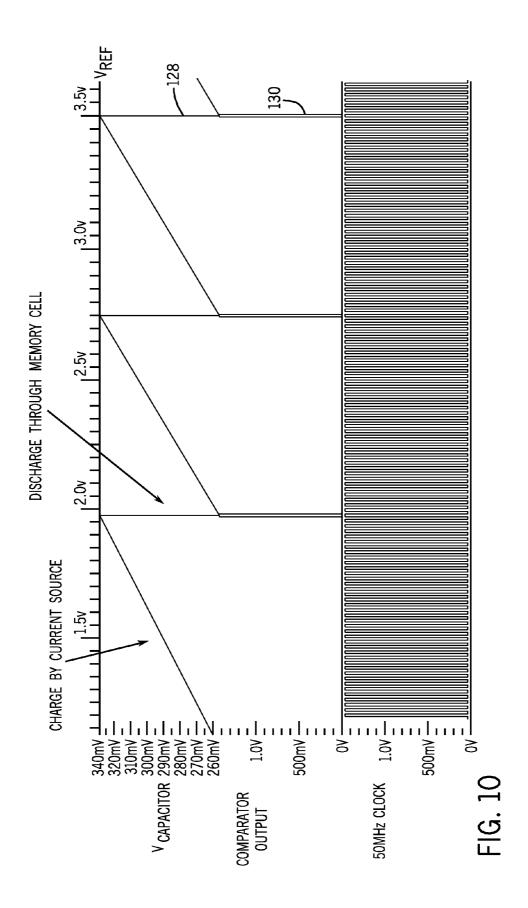

FIG. 10 is a graph representing the outputs of the second quantizing circuit of FIG. 8;

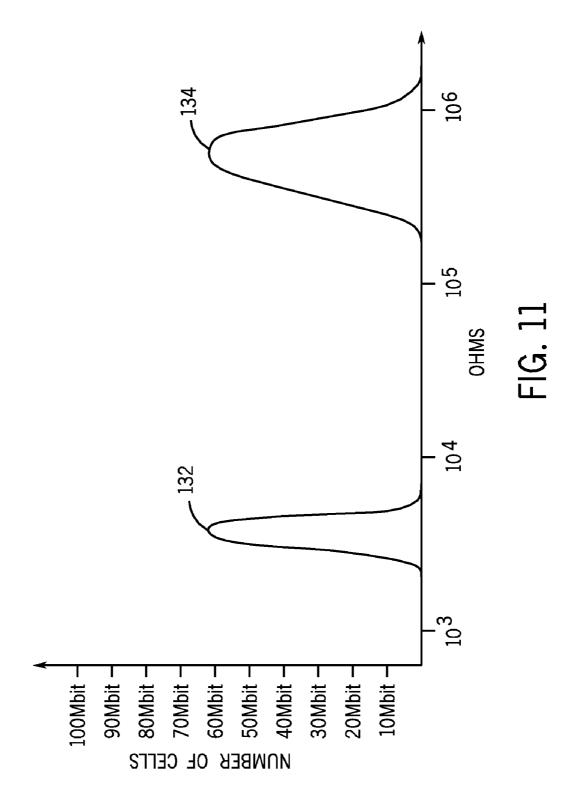

FIG. 11 is an example of a memory histogram representing the entire set of outputs of the second quantizing circuit associated with FIG. 8.

## DETAILED DESCRIPTION OF SPECIFIC EMBODIMENTS

Various embodiments of the present invention are described below. In an effort to provide a concise description of these embodiments, not all features of an actual implementation are described in the specification. It should be appreciated that in the development of any such actual implementation, as in any engineering or design project, numerous implementation-specific decisions must be made to achieve the developers' specific goals, such as compliance with system-related and business-related constraints, which may vary from one implementation to another. Moreover, it should be appreciated that such a development effort might be complex and time consuming but would nevertheless be a routine undertaking of design, fabrication, and manufacture for those of ordinary skill having the benefit of this disclosure.

The present disclosure generally relates to measuring the resistance of multiple memory elements. The multiple memory elements may be phase change memory elements grouped together in an array. The memory elements may also be multi-bit memory, which may allow circuit designers to increase the number of bits stored per memory element. Through precise measurement of the resistance of the multibit memory elements in conjunction with the controlled charging and discharging of system capacitance, determination of how many and which memory elements fall into specific memory resistance ranges can be accomplished. Furthermore, storage and/or display of this information may allow for the creation of resistance distribution histograms for modeling of one or more memory arrays by graphically plotting the resistance values for memory elements during a set and a reset state (which may correspond to multiple storage levels for the memory elements).

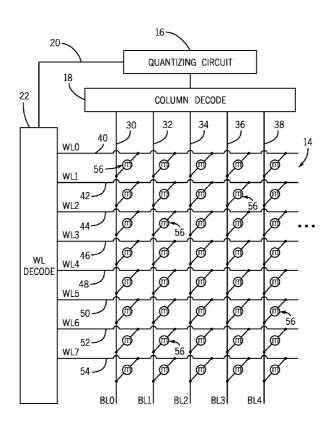

FIG. 1 depicts an electronic device 10 that may be fabricated and configured in accordance with one or more of the present embodiments. The illustrated electronic device 10 includes a memory device 12 that, as explained further below, may include multi-bit memory elements and quantizing circuits. Alternatively, or additionally, the electronic device 10 may include a testing device 13 having the quantizing circuits included therein. Moreover, the testing device 13 may be internal to or external to the electronic device 10, as well as

internal to or external to the memory device 12. Testing device 13 may be utilized in the determination of a resistance distribution, which may include the number of memory elements programmed to each of a plurality of different states for one or more memory arrays.

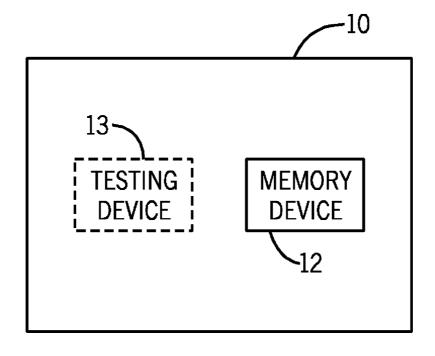

FIG. 2 depicts a block diagram of an embodiment of the electronic device 10. The illustrated memory device 12 may include a memory array 14, a quantizing circuit 16, column decode circuitry 18, a word line enable path 20, word line decode circuitry 22, an address counter logic circuit 24, count 10 circuitry 26, and an accumulator circuit 28. As described below with reference to FIG. 3, the memory array 14 may include a matrix of memory elements arranged in rows and columns. When accessing the memory elements of the memory array 14, the address counter logic circuit 24 may 15 receive a command to read from or write to a target memory address. The address counter logic circuit 24 may convert the command designating a target address into a row and a column address. This command may be passed to the column decode circuitry 18 and the word line decode circuitry 22. The 20 word line decode circuitry 22 may also receive a word line enable signal along the word line enable path 20. The word line enable signal acts to provide an activation signal allowing a read signal or a write signal to be transmitted to the memory array 14 along the row specified by the address counter logic 25 circuit 24. Similarly, the column decoder 18 may determine which column of the memory array 14 corresponds with the column specified by the address counter logic circuit 24, and may pass the signal transmitted from the specified memory location to the quantizing circuit 16. The quantizing circuit 16 30 may sense an output voltage or current from the memory element at the specified row and column of the memory array 14.

The quantizing circuit 16 may sense multiple iterations of a voltage or current from the specified row and column of the 35 memory array 14. Alternatively, the quantizing circuit 16 may sense one or more iterations of a voltage or current from multiple specified rows and columns of the memory array 14 one memory location at a time as a part of a step through testing process of the memory array 14. The output of the 40 quantizing circuit 16 may be sent to the count circuitry 26, which may count pulses or high portions of a digital signal. The results of the counting performed in the count circuitry 26 may be transmitted to an accumulator 28, in which the results may be stored. These results may, for example, be used in the 45 modeling of the memory array 14.

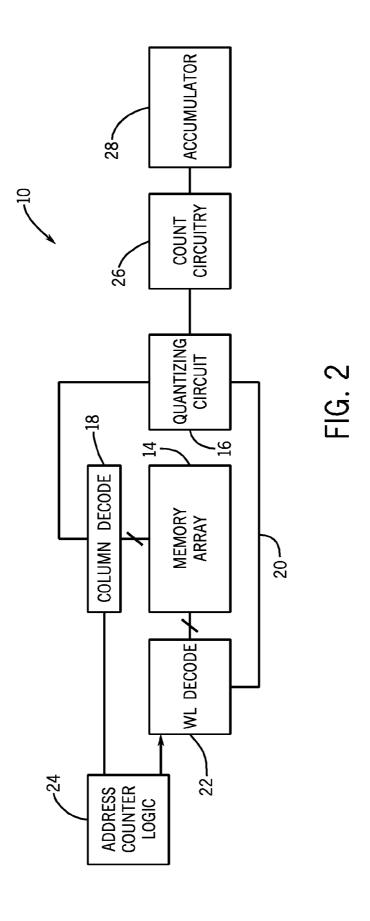

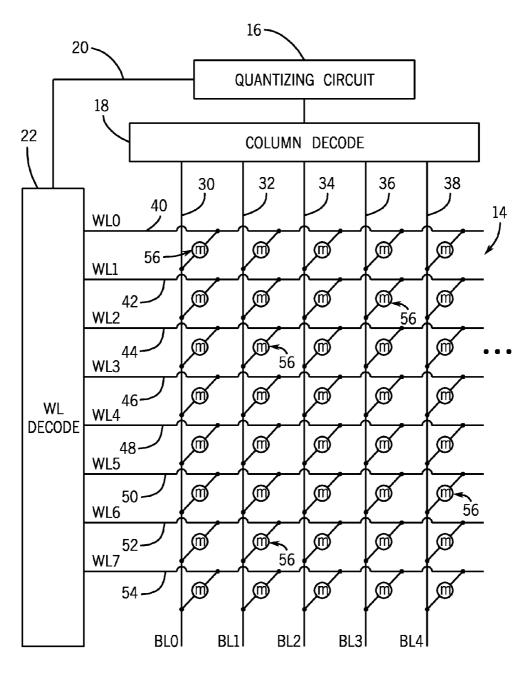

FIG. 3 depicts a memory array 14 that includes a plurality of data lines, such as bit lines 30, 32, 34, 36, and 38 (also referred to as BL0-BL4) and a plurality of access lines, such as word lines 40, 42, 44, 46, 48, 50, 52, and 54 (also referred 50 to as WL0-WL7). These bit lines and word lines may be electrical conductors. The memory array 14 further may include a plurality of memory elements 56, each of which may be arranged to intersect one of the bit lines, e.g. BL1, and one of the word lines, e.g. WL2. Each of the plurality of 55 memory elements 56 may be referred to generally as an internal data storage location, i.e., a device configured to convey data, either stored or generated by a sensor, when accessed by a sensing circuit, such as a quantizing circuit discussed below. These internal data storage locations may be 60 formed on an integrated semiconductor device that also includes the other components of the memory device 12. In some embodiments, the illustrated memory elements 56 may include a resistance memory, such as a phase change memory or magnetoresistive memory. It should be noted that, in other 65 embodiments, the memory elements 56 may include other types of volatile or nonvolatile memory.

4

The memory array 14 may be coupled to the quantizing circuit 16 via the column decode circuitry 18. The illustrated column decode circuitry 18 may be coupled to each of the bit lines 30, 32, 34, 36, and 38, respectively. The column decode circuitry 18 may determine which bit line is to be accessed and, subsequently, transmit signals from the accessed bit line to the quantizing circuit 16. In this manner, the quantizing circuit 16 may receive signals from all memory elements 56 of the memory array 14, which as will be described below, allows for the determination of the resistance values for any/all of the memory elements 56 of the memory array 14.

In operation, the quantizing circuit 16 may digitize analog signals from the memory elements 56 in a manner that is relatively robust to noise. As explained below, the quantizing circuit 16 may do this by converting the analog signals into a bit-stream and digitally filtering high-frequency components from the bit-stream. The quantizing circuit 16 may include a one-bit analog-to-digital converter or a multi-bit analog-todigital converter. In the present embodiment, the quantizing circuit 16 receives an analog signal from any one of the plurality of memory elements 56, and may output a bit-stream that corresponds with the analog signal. The bit-stream may be a one-bit, serial signal that generally represents or corresponds to a discharge of voltage of either a parasitic or a discrete capacitance element of the quantizing circuit 16. That is, the bit-stream may fluctuate between values of zero and one, to form a pulse wave. The quantizing circuit 16 may transmit this bit-stream to the count circuitry 26. The count circuitry 26 may then be utilized to sum the pulses of the bit-stream over a given duration of time.

In traditional designs, the number of discrete data values that each of the memory elements **56** stores may be limited by sense amplifiers that react to noise. In contrast, the quantizing circuit **16** may be less susceptible to noise, and, as a result, the memory elements **56** may be configured to store additional data. Without the high frequency noise, the intervals between signals representative of different data values may be made smaller, and the number of data values stored by a given memory element **56** may be increased. Thus, beneficially, the quantizing circuit **16** may sense memory elements **56** that store several bits of data, e.g., 2, 3, 4, 5, 6, 7, 8, or more bits per each one of the memory elements **56**. Each one of a plurality of memory arrays **14** may be coupled to a discrete quantizing circuit **16**, column decode circuitry **18**, and word line decode circuitry **22**.

Advantageously, in certain embodiments, the quantizing circuit 16 may facilitate the use of multi-bit memory elements 56. FIGS. 4A-C illustrate three distinct embodiments for each of the memory elements 56. It should be noted that while three embodiments are shown, typically only one embodiment will be utilized throughout any given memory array 14. FIG. 4A illustrates a N-type metal oxide semiconductor field effect transistor (NMOS) 58, a phase change memory cell 60 and ground 62. The NMOS 58 may act as a switch, operating in an "on" mode when voltage is applied along the word line to the gate of the NMOS 58 (thus allowing current to flow through the NMOS 58). Similarly, the NMOS may operate in an "off" mode when no voltage is applied along the word line to the gate of the NMOS 58 (thus restricting current to flow through the NMOS 58). When the NMOS 58 is in "on" mode, current may pass from the bit line to the phase change memory cell 60. This flow of current through the memory cell **60** will allow for testing of the resistance of the memory cell **60**, as will be described subsequently.

FIGS. 4B and 4C illustrate second and third embodiments of the memory elements 56. FIG. 4B illustrates a diode 64 in series with the memory cell 60, while FIG. 4C illustrates a

bipolar junction transistor (BJT) 66 in series with memory cell 60. In both FIGS. 4B and 4C, the word line enable signal is used to activate flow of current through the specified memory cell 60. This word line enable signal is an active low enabling signal in conjunction with both the diode 64 and the BJT 66. That is, when the word line enable signal is high, both the diode 64 and the BJT 66 operate in the "off" mode, preventing current from passing through the memory cell 60. Conversely, when the word line enable signal is low, both the diode 64 and the BJT 66 operate in the "on" mode, thus allowing current to pass from the bit line to the memory cell 60. This bit line may coupled to the quantizing circuit 16 to allow for testing of the resistance of the memory cell 60.

FIG. 5 illustrates a quantizing circuit 16, as described above. The quantizing circuit 16 is illustrated as coupled to a memory cell 60 (modeled as a resistor 60) from memory array 14, as well as a pulse counter 82. While the memory cell 60 is shown in conjunction with the NMOS 58 to form a memory element 56, a diode 64 or a BJT 66 could also be implemented for use with memory cell 60 instead of NMOS 58 to form memory element 56. Furthermore, it should be noted that while column decode circuitry is not illustrated, it may be implemented at point A of FIG. 5. Similarly, word line decode circuitry is not illustrated, however, it may be implemented at point B of FIG. 5.

The quantizing circuit 16 may include a capacitance 68. This capacitance 68 may be the parasitic line capacitance of the quantizing circuit 16 and/or the capacitance 68 may be a discrete component included in the quantizing circuit 16. The quantizing circuit may also include an operational amplifier (op-amp) 70 and a p-type metal-oxide-semiconductor (PMOS) 72. The PMOS 72 will be shown to operate as a pull up device in conjunction with the NMOS 58, which operates as a pull down device, to control charging/discharging of the 35 capacitance 68 via a two-way multiplexer (mux) 74. The mux 74 allows for the selection of two reference voltages,  $V_{HIGH}$ **78** and  $V_{LOW}$  **80**. The reference voltages  $V_{HIGH}$  **78** and  $V_{LOW}$ 80 may provide necessary hysteresis for the measurement of the resistance of the memory cell 60, and may be selected so 40 as to prevent an inadvertent corruption of the memory cell 60. In this configuration, the op-amp 70 operates as a comparator. Thus configured, the quantizing circuit 16 may allow for measurement of the resistance of a memory cell 60 by performing an analog to digital conversion of the RC discharging 45 time, which will be described more fully below. This measurement may be then be monitored by the pulse counter 82.

The pulse counter 82 output can be used to determine the resistance of the memory cell 60 tested by the circuitry outlined in FIG. 5. The capacitance 68 charging time is dependent only on its capacitance value and the supplied current, according to the formula for capacitance charging time, dt=C/ I\*dV, where dt is the derivative of time, C is the capacitance 68, I is the current flowing through a capacitance element, and dV is the derivative of voltage. Furthermore, the discharging 55 time of the capacitance 68 is dependent upon the resistance of the memory cell 60, according to the voltage discharge equation  $V_{LOW} = V_{HIGH} e^{(-t/RC)}$ , where t is time, R is the resistance of the memory cell 60, C is the capacitance 68, and  ${

m V}_{HIGH}$  78 and  ${

m V}_{LOW}$  80 are the reference voltages that deter- 60 mine the swing of the voltage of the capacitance 68. The values for  $V_{HIGH}$  78 and  $V_{LOW}$  80 can be chosen to set hysteresis for the system so that the voltage does not disturb the functioning of the memory cell 60, but provides adequate swing of the voltage of the capacitance 68. This will allow for 65 a reasonable period for measuring the output of the memory cell 60, for example, 100 µs. Solving for this period may be

6

accomplished through taking the natural log of the voltage discharge equation, yielding t=-RC\*  $\ln(V_{LOW}/V_{HIGH})$ .

As shown above, the output of the op-amp 70 is directly coupled to the pulse counter 82. The output of the pulse counter 82 can then be related to the memory cell resistance by  $N=T/(t_D+t_C)$ , where N is the pulse counter 82 output, T is total sensing time,  $\mathbf{t}_D$  is the discharge time, which can be found from  $-RC*ln(V_{LOW}/V_{HIGH})$ , and  $t_C$  is the charging time, which can be found from  $C/I*(V_{HIGH}-V_{LOW})$ . Substituting for  $t_D$  yields  $N=T/[t_C-RC*ln(V_{LOW}/V_{HIGH})]$ . By further substituting  $\alpha$  for  $t_{\it C}/{\rm C*ln}({\rm V}_{\it LOW}/{\rm V}_{\it HIGH}),$  and  $\beta$  for  $T/[C*ln(V_{LOW}/V_{HIGH})]$ , the resistance of memory cell  $\bf 60$  can be represented as  $R=\alpha-\beta/N$ . Therefore, the memory cell **60** resistance is proportional to -1/N. As such, the resistance of any given memory cell 60 is proportional to the inverse of the pulse counter 82 output. Furthermore, if memory cell 60 is a phase change memory type, the testing procedure may be repeated for different data states. Accordingly, the resistance of the memory cell 60 may be measured for these different data states to determine the resistance of the memory cell 60 with respect to differing external influences.

The operation of the quantizing circuit 16, as described in FIG. 5, is illustrated with respect to FIG. 6. FIG. 6 illustrates a method of taking a resistance measurement of the memory cell 60. In step 84, the quantizing circuit 16 is initialized by pre-charging the capacitance 68 to ground, while selecting the reference voltage  $V_{HIGH}$  78 by the mux 74. The result of this initialization step 84 is that the output of the op-amp 70 is low. This activates the PMOS 72 in step 86. The activation of the PMOS 72 provides a charging path for the capacitance 68. The capacitance 68 continues to charge in step 88 until the capacitance 68 is charged to a voltage above the reference voltage  $V_{\it HIGH}$  78 in step 90. When this occurs, the op-amp 70 output switches to high in step 92, causing the reference voltage  $V_{LOW}$  80 to be selected by the mux 74. This causes the deactivation of the PMOS 72, as well as the activation of the NMOS 58 in step 94. The activation of the NMOS 58 provides a discharging path for the capacitance 68 through the memory cell 60 in step 96. In step 98, the capacitance 68 will continue to discharge to a voltage lower than the reference voltage  $V_{LOW}$  80, causing the op-amp 70 output to switch to low in step 100. This begins the charging cycle anew in step 86. FIG. 7 shows a graphical representation of the process outlined above with respect to FIG. 6.

As can be seen in FIG. 7, the voltage level of the capacitance 68 over time at point C of FIG. 5 is illustrated by the graph 102 representing the voltage of the capacitance 68. Furthermore, the voltage level of the op-amp 70 output over time at point D of FIG. 5 is illustrated by the graph 104 representing op-amp 70 output. As can be seen in FIG. 8, the quantizing circuit 16 effectively translates an analog signal 102 into a digital signal 104 that can be counted by pulse counter 82.

The results of these measurements may be transmitted as pulses from the pulse counter **82** to, for example, an accumulator **28** for logging of the data. The accumulator **28** may store the data for subsequent processing, or the accumulator **28** may determine the distribution of the resistance levels of the memory elements **56** of the memory array **14** such that the resistance levels of for every memory element **56** can be characterized for later use in the storage of data. Alternatively, the accumulator **28** may store data relating to the total number of memory elements **56** that fall into specific resistance ranges.

FIG. 8 illustrates a second embodiment for the quantizing circuit 16. As with FIG. 5 above, the phase change memory cell 60 in FIG. 8 incorporates the NMOS 58, however, as

described above, a diode **64** or a BJT **66** could be implemented in place of the NMOS **58**. Moreover, although column decode circuitry and word line enable circuitry are not illustrated, they may be implemented at points A and B of FIG. **8**, respectively.

The quantizing circuit 16 may include a current source 106, a PMOS 72, a capacitance 68, and a clocked comparator 110. The clocked comparator 110 may include an op-amp, inverters, and clocked inverters arranged in such a manner as to maintain an average voltage equal to a reference voltage  $V_{REF}$  10 108 across the capacitance 68. The clocked comparator 110 may accomplish maintaining this average voltage by alternatingly supplying a charging path to the capacitance 68 from the current source 106 and supplying a discharge path for the capacitance 68 through the memory cell 60 to ground 62. The 15 clocked comparator 110 may be activated by a clock signal that is transmitted via clock line 112 to control the timing of the clocked comparator 110 in generating an output on output line 114

Since the feedback controlling the current source 106 and 20 memory cell 60 is clocked via clock line 112, the capacitance 68 may be charged and discharged for time periods at multiples of the clock cycle. As such, the clock frequency may be selected such that the capacitance 68 will not fully discharge through the minimum expected memory resistance within 25 one clock cycle. For example, for a minimum detectable resistance of 20 and a capacitance of 20 ns might be selected. The output of the clocked comparator 20 ns might be sent via output line 20 ns counter 20 ns accumulator 20 ns accumulator

The operation of the quantizing circuit 16, as described in FIG. 8, is illustrated with respect to FIG. 9. FIG. 9 illustrates a method of taking a resistance measurement of the memory cell 60. In step 118, the quantizing circuit 16 is initialized by 35 pre-charging the capacitance 68 to a level above the reference voltage  $V_{\it REF}$  108. The result of this initialization step 118 is that the output of the clocked comparator 114 is active high, which enables the memory cell 60 and disables the current source 106 in step 120. Also in step 120, the NMOS 58 is 40 activated. The activation of the NMOS 58 provides a discharging path for the capacitance 68. The capacitance 68 discharges through the memory cell 60 in step 122 for at least one clock cycle, until the switching point is reached. In step **124**, after at least one clock cycle, the output of the clocked 45 comparator 114 switches to active low which disables the memory cell 60 and enables the current source 106 as well as the PMOS 72. The activation of the PMOS 72 provides a charging path for the capacitance 68. This allows the current source 106 to charge the capacitance 68 in step 126 for the 50 number of clock cycles required to bring the capacitance 68 voltage back up to the reference voltage  $V_{REF}$  108.

As can be seen in FIG. 10, the voltage level of the capacitance 68 over time at point C of FIG. 9 is illustrated by the graph 128 representing the voltage across the capacitance 68. 55 Furthermore, the voltage level of the clocked comparator 114 over time at point D of FIG. 8 is illustrated by the graph 130 representing the op-amp 70 output. As can be seen in FIG. 10, the quantizing circuit 16 effectively translates an analog signal 128 into a digital signal 130 that can be counted by counter 60 116.

The counter 116 output can be used to determine the resistance of the memory cell 60 tested by the process outlined in FIG. 9. Since the capacitance 68 is connected to the memory cell 60 to form a simple RC network during each discharge cycle, the amount of charge lost is related to the memory cell resistance by  $Q_{\it discharge}$ =C\*dV, where dV= $V_{\it ref}$ - $V_{\it final}$ . More-

8

over,  $V_{final}=V_{rej}e^{\circ}(-t/RC)$ , where t=comparator output high time. Since the clocked comparator 114 may be set to maintain a constant voltage across the capacitance, the amount of charge lost through the memory cell 60 during discharge will be equal to the amount of charge added to the capacitance 68 by the current source 106, so that  $Q_{discharge}=Q_{charge}=I_{source}*$ comparator output low time. Thus, the resistance of the memory cell 60 is related to the ratio of comparator 68 high time to low time. For example, for smaller resistance values, larger voltage drops will occur during one clock period, and longer re-charging times are required. These will be noted in the form of a digital signal that may be sent to the counter 116.

As shown above, the clocked comparator 114 output may be routed to the counter 116 to record the number of high (or low) comparator outputs. In one embodiment, the counter 116 output can be routed to a digital display to show the measured resistance at the end of each sensing period. In another embodiment, multiple outputs from the counter 116 can be stored in the accumulator 28 before being transmitted to a digital display. Additionally, the counter 116 outputs may be routed to the accumulator 28 to maintain a record of how many memory elements 56 fall into specific resistance ranges.

Furthermore, if the memory elements 56 include phase change memory, the memory cell 60 may undergo multiple phase changes as part of this testing procedure. The resistance of the memory cell 60 may be measured during each of these phase changes to determine the resistance of the memory cell **60** with respect to differing external influences. The results of these measurements may be transmitted as a digital signal from the counter 116 to the accumulator 28. In another embodiment, the accumulator 28 may determine the distribution of the resistance levels of the memory elements 56 so that the resistance levels of the memory elements **56** can be characterized for later use in storage of data. In another embodiment, the output of the counter 116 may be transmitted to the accumulator 28 to maintain a record of how many memory cells 60 fall into specific resistance ranges. These ranges may then be grouped to form resistance distribution histograms.

An example of a resistance distribution histogram is illustrated in FIG. 11. The resistance distribution histogram includes two resistance distributions, 132 and 134. The first resistance distribution 132 is associated with the set state, i.e. a low resistance state of the multi-state memory cells 60. The range that the memory cells 60 fall into for the set state typically follows a bell curve shape. In FIG. 11, the range that the memory cells 60 fall into for a set state is a bell curve centered around 6000 ohms, with the smallest values equaling about 4000 ohms and the largest values equaling about 8000 ohms. Similarly, the resistance distribution 134 representing the reset state, i.e. a high resistance state of the multistate memory cells 60, also typically a follows a bell curve shape. The resistance distribution 134 shows that the bell shaped curve for the reset state of the memory cells 60 is centered around 800 Kohms, with the smallest values equaling about 300 Kohms and the largest values equaling about 1.3 Kohms. By analysis of these resistance distributions, the number of memory cells that fall into specific resistance ranges may be determined.

While the invention may be susceptible to various modifications and alternative forms, specific embodiments have been shown by way of example in the drawings and have been described in detail herein. However, it should be understood that the invention is not intended to be limited to the particular forms disclosed. Rather, the invention is to cover all modifications, equivalents, and alternatives falling within the spirit and scope of the invention as defined by the following appended claims.

What is claimed is:

- 1. A method of operating a memory device comprising: monitoring charging and discharging time of a capacitance coupled to a memory element;

- converting the charging and discharging time of the capacitance to a pulse stream;

- determining a resistance of the memory element based on 10 the pulse stream; and

- storing the determined resistance of the memory element to generate one or more resistance ranges.

- 2. The method of claim 1, comprising examining the ratio of a clocked comparator output high time with the clocked 15 comparator output low time.

- 3. The method of claim 2, comprising calculating a resistance of the memory element according to the proportionality of an inverse of a pulse counter output.

- and discharging time of the capacitance comprises monitoring an output of a quantizing circuit.

- 5. The method of claim 4, wherein monitoring the output of the quantizing circuit includes monitoring switches of an op amp output in the quantizing circuit from active low to active 25 high.

- 6. The method of claim 5, further comprising determining a number of switches of the op amp output in the quantizing circuit from active low to active high.

- 7. The method of claim 6, comprising storing the monitored output of the quantizing circuit by transferring the determined number of switches of the op amp output in the quantizing circuit from active low to active high from the pulse counter to a storage device.

- 8. The method of claim 7, comprising determining the 35 resistance of the memory element based on the determined number of switches of the op amp output in the quantizing circuit from active low to active high.

- 9. The method of claim 1, wherein storing comprises storing the determined resistance of the memory element in an 40 accumulator.

- 10. The method of claim 1, comprising determining one or more distributions of resistance levels from the one or more resistance ranges.

- 11. A method of operating a memory device comprising: monitoring charging and discharging time of a capacitance coupled to a first memory element in a memory array;

- converting the charging and discharging time of the capacitance to a first pulse stream;

- selecting a second memory element from the memory 50 array coupled to the capacitance;

- monitoring charging and discharging time of the capacitance coupled to the second memory element in the memory array;

- tance to a second pulse stream;

- determining a resistance value for the first and the second memory elements based on the first and second pulse streams; and

10

- storing the resistance values for each of the first and the second memory elements to generate one or more resistance ranges.

- 12. The method of claim 11, wherein generating the resis-5 tance range comprises routing the first and second pulse streams to a pulse counter to determine and store a number of high pulses.

- 13. The method of claim 12, wherein storing the resistance values comprises routing an output of the pulse counter to a circuit that calculates and maintains a record of the one or more resistance ranges of the first and second memory elements.

- 14. The method of claim 11, wherein storing comprises storing the resistance values of the first and second memory elements in an accumulator.

- 15. The method of claim 11, comprising determining one or more distributions of resistance levels from the one or more resistance ranges.

- 16. The method of claim 15, comprising characterizing 4. The method of claim 1, wherein monitoring charging 20 each of the first and the second memory element based on the one or more distributions of resistance levels.

- 17. A method of operating a memory device comprising: digitizing an analog signal from a memory element using a quantizing circuit;

- producing a pulse stream from the digitized analog signal using a counter;

- determining a resistance of the memory element based on the pulse stream; and

- storing the determined resistance of the memory element in an accumulator to generate one or more resistance ranges.

- 18. The method of claim 17, wherein producing the pulse stream comprises converting charging and discharging times of a capacitance in the quantizing circuit.

- 19. The method of claim 17, comprising characterizing the determined resistance of the memory element based on the one or more resistance ranges.

- 20. A method of operating a memory device comprising: initializing a quantizing circuit;

- disabling a current source to the quantizing circuit; discharging a capacitance in the quantizing circuit; enabling the current source to the quantizing circuit; and charging the capacitance in the quantizing circuit.

- 21. The method of claim 20, wherein initializing comprises 45 pre-charging the capacitance to a level above a reference voltage.

- 22. The method of claim 20, wherein initializing comprises enabling a memory cell coupled to the quantizing circuit.

- 23. The method of claim 20, wherein discharging comprises discharging the capacitance through a memory cell coupled to the quantizing circuit.

- 24. The method of claim 20, wherein discharging comprises discharging the capacitance for at least one clock cycle.

- 25. The method of claim 20, wherein charging comprises converting the charging and discharging time of the capaci- 55 charging the capacitance to approximately equal to a reference voltage.