(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7055544号**

**(P7055544)**

(45)発行日 令和4年4月18日(2022.4.18)

(24)登録日 令和4年4月8日(2022.4.8)

(51)国際特許分類

H 0 1 L 31/107 (2006.01)

F I

H 0 1 L 31/10

B

請求項の数 11 (全20頁)

|               |                             |          |                                                                   |

|---------------|-----------------------------|----------|-------------------------------------------------------------------|

| (21)出願番号      | 特願2016-231585(P2016-231585) | (73)特許権者 | 316005926<br>ソニーセミコンダクタソリューションズ<br>株式会社<br>神奈川県厚木市旭町四丁目14番1号      |

| (22)出願日       | 平成28年11月29日(2016.11.29)     | (74)代理人  | 100121131<br>弁理士 西川 孝                                             |

| (65)公開番号      | 特開2018-88488(P2018-88488A)  | (74)代理人  | 100082131<br>弁理士 稲本 義雄                                            |

| (43)公開日       | 平成30年6月7日(2018.6.7)         | (74)代理人  | 100168686<br>弁理士 三浦 勇介                                            |

| 審査請求日<br>前置審査 | 令和1年11月5日(2019.11.5)        | (72)発明者  | 田中 章<br>神奈川県厚木市旭町四丁目14番1号<br>ソニーセミコンダクタソリューションズ<br>株式会社内<br>大竹 悠介 |

|               |                             |          | 最終頁に続く                                                            |

(54)【発明の名称】 センサチップおよび電子機器

**(57)【特許請求の範囲】****【請求項1】**

複数の画素がアレイ状に配置された画素アレイ部と、

前記画素ごとに設けられる高電界領域によりキャリアを増倍させるアバランシェフォトダイオード素子と、

前記アバランシェフォトダイオード素子が形成される半導体基板において隣接する他の前記画素との間を絶縁して分離する画素間分離部と、

前記高電界領域を少なくとも覆うように、前記半導体基板の受光面の反対側となる表面に對して積層される配線層に設けられ、前記アバランシェフォトダイオード素子のカソードに第1の電極を介して接続される第1のメタル配線と、

前記配線層に設けられ、前記アバランシェフォトダイオード素子のアノードに第2の電極を介して接続される第2のメタル配線と

を備え、

断面視において、前記第1のメタル配線が一つの画素領域内で前記第2のメタル配線の間に設けられている

センサチップ。

**【請求項2】**

前記メタル配線と前記半導体基板との間に設けられ、前記アバランシェフォトダイオード素子を透過して前記メタル配線で反射した光を前記アバランシェフォトダイオード素子の中央に集光するインナーレンズ

をさらに備える請求項1に記載のセンサチップ。

**【請求項 3】**

前記画素間分離部は、前記半導体基板の裏面から前記表面まで貫通するように形成される請求項1または2のいずれかに記載のセンサチップ。

**【請求項 4】**

前記画素間分離部は、光を反射する金属膜と絶縁性を備えた絶縁膜とによる二重構造とされ、前記金属膜の表面が前記絶縁膜で覆われるように前記半導体基板に埋め込まれて形成される

請求項1乃至3のいずれかに記載のセンサチップ。

**【請求項 5】**

前記画素間分離部として前記半導体基板に埋め込まれた金属膜に電圧を印加することによって、ホールを蓄積するホール蓄積層が前記アバランシェフォトダイオード素子の外周に誘起される

請求項1乃至4のいずれかに記載のセンサチップ。

**【請求項 6】**

前記画素間分離部として前記半導体基板に埋め込まれた金属膜に電圧を印加することによって、キャリアをドリフトする電界が強化される

請求項1乃至5のいずれかに記載のセンサチップ。

**【請求項 7】**

前記高電界領域を少なくとも覆うように、光を反射する反射膜が前記半導体基板の表面に対して形成される

請求項1乃至6のいずれかに記載のセンサチップ。

**【請求項 8】**

前記反射膜に対して電圧を印加することによって、前記半導体基板の表面近傍に、ホールを蓄積するホール蓄積層を形成する

請求項7に記載のセンサチップ。

**【請求項 9】**

前記反射膜は、平面的に見たときに前記メタル配線に重なるように形成される

請求項7または8に記載のセンサチップ。

**【請求項 10】**

前記画素間分離部の高さが、前記半導体基板の表面と略一致するように形成される

請求項1乃至9のいずれかに記載のセンサチップ。

**【請求項 11】**

複数の画素がアレイ状に配置された画素アレイ部と、

前記画素ごとに設けられる高電界領域によりキャリアを増倍させるアバランシェフォトダイオード素子と、

前記アバランシェフォトダイオード素子が形成される半導体基板において隣接する他の前記画素との間を絶縁して分離する画素間分離部と、

前記高電界領域を少なくとも覆うように、前記半導体基板の受光面の反対側となる表面に対して積層される配線層に設けられ、前記アバランシェフォトダイオード素子のカソードに第1の電極を介して接続される第1のメタル配線と、

前記配線層に設けられ、前記アバランシェフォトダイオード素子のアノードに第2の電極を介して接続される第2のメタル配線と

を有し、

断面視において、前記第1のメタル配線が一つの画素領域内で前記第2のメタル配線の間に設けられている

センサチップを備える電子機器。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

10

20

30

40

50

本開示は、センサチップおよび電子機器に関し、特に、SPAD画素の特性向上を図ることができるようにしたセンサチップおよび電子機器に関する。

【背景技術】

【0002】

近年、ToF (Time-of-Flight) 法により距離計測を行う距離画像センサが注目されている。例えば、距離画像センサには、CMOS (Complementary Metal Oxide Semiconductor) 半導体集積回路技術を用いて、複数のSPAD (Single Photon Avalanche Diode) 画素が平面的に配置されるように形成された画素アレイを利用することができる。SPAD 画素では、降伏電圧よりもはるかに大きい電圧を印加した状態で、高電界のPN接合領域へ1個のフォトンが入ると、アバランシェ増幅が発生する。その際の瞬間的に電流が流れた時間を検出することで、高精度に距離を計測することができる。10

【0003】

例えば、特許文献1には、アバランシェフォトダイオードが配列されたフォトダイオードアレイにおいて、画素間に分離を形成する構造によって、高電界領域での発光による隣接画素へのクロストークの低減を図る技術が開示されている。

【0004】

また、特許文献2には、シングルフォトンアバランシェダイオードにおいて、高電界領域を形成する層を埋め込んでバイアスにより空乏化させることによって、SPAD画素の感度向上を図る技術が開示されている。

【先行技術文献】

20

【特許文献】

【0005】

【文献】特開2013-48278号公報

特開2015-41746号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1で開示されている構造では、絶縁膜を用いて物理的に画素間を分離することにより光学的なクロストークを低減させているだけであって、感度の向上までは図られていない。30

【0007】

また、特許文献2で開示されている構造では、画素内の高電界領域で発光することで隣接画素にフォトンが入射してしまい、隣接画素で意図せずフォトンが検出されるクロストークが発生してしまう。さらに、光入射面（裏面）に対して反対側となるゲートおよび配線が形成される面（表面）へ入射光が透過してしまうため、感度の低下が懸念される。

【0008】

そのため、このようなクロストークの発生を防止し、かつ、感度の向上を図ることによって、より良好な特性を備えたSPAD画素が求められている。

【0009】

本開示は、このような状況に鑑みてなされたものであり、SPAD画素の特性向上を図ることができるようとするものである。40

【課題を解決するための手段】

【0010】

本開示の一側面のセンサチップは、複数の画素がアレイ状に配置された画素アレイ部と、前記画素ごとに設けられる高電界領域によりキャリアを増倍させるアバランシェフォトダイオード素子と、前記アバランシェフォトダイオード素子が形成される半導体基板において隣接する他の前記画素との間を絶縁して分離する画素間分離部と、前記高電界領域を少なくとも覆うように、前記半導体基板の受光面の反対側となる表面に対して積層される配線層に設けられ、前記アバランシェフォトダイオード素子のカソードに第1の電極を介して接続される第1のメタル配線と、前記配線層に設けられ、前記アバランシェフォトダイ

50

オード素子のアノードに第2の電極を介して接続される第2のメタル配線とを備え、断面視において、前記第1のメタル配線が一つの画素領域内で前記第2のメタル配線の間に設けられている。

【0011】

本開示の一側面の電子機器は、複数の画素がアレイ状に配置された画素アレイ部と、前記画素ごとに設けられる高電界領域によりキャリアを増倍させるアバランシェフォトダイオード素子と、前記アバランシェフォトダイオード素子が形成される半導体基板において隣接する他の前記画素との間を絶縁して分離する画素間分離部と、前記高電界領域を少なくとも覆うように、前記半導体基板の受光面の反対側となる表面に対して積層される配線層に設けられ、前記アバランシェフォトダイオード素子のカソードに第1の電極を介して接続される第1のメタル配線と、前記配線層に設けられ、前記アバランシェフォトダイオード素子のアノードに第2の電極を介して接続される第2のメタル配線とを有し、断面視において、前記第1のメタル配線が一つの画素領域内で前記第2のメタル配線の間に設けられているセンサチップを備える。

10

【0012】

本開示の一側面においては、画素アレイ部には、複数の画素がアレイ状に配置され、高電界領域によりキャリアを増倍させるアバランシェフォトダイオード素子が画素ごとに設けられる。そして、画素間分離部により、アバランシェフォトダイオード素子が形成される半導体基板において隣接する他の画素との間が絶縁して分離される。第1のメタル配線が、高電界領域を少なくとも覆うように、半導体基板の受光面の反対側となる表面に対して積層される配線層に設けられ、アバランシェフォトダイオード素子のカソードに第1の電極を介して接続される。第2のメタル配線が、配線層に設けられ、アバランシェフォトダイオード素子のアノードに第2の電極を介して接続される。そして、断面視において、第1のメタル配線が一つの画素領域内で第2のメタル配線の間に設けられる。

20

【発明の効果】

【0013】

本開示の一側面によれば、SPAD画素の特性向上を図ることができる。

【図面の簡単な説明】

【0014】

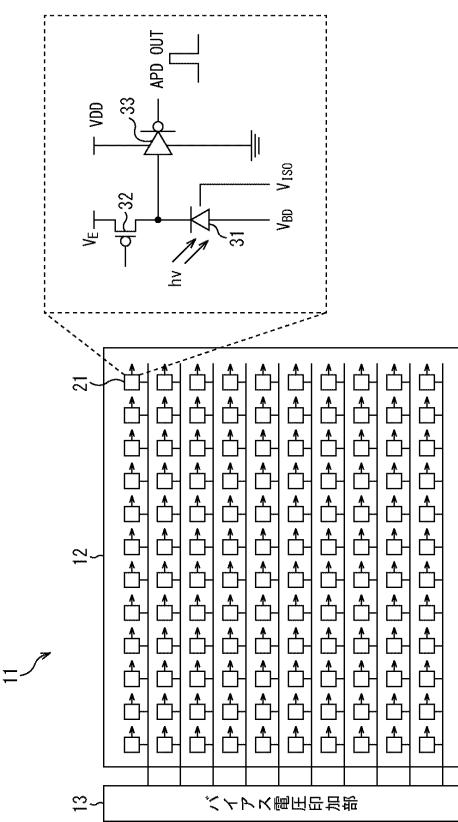

【図1】本技術を適用したセンサチップの一実施の形態の構成例を示すブロック図である。

30

【図2】SPAD画素の断面的な第1の構成例を示す図である。

【図3】SPAD画素の配線層における平面的な第1の構成例を示す図である。

【図4】SPAD画素の断面的な第2の構成例を示す図である。

【図5】SPAD画素の配線層における平面的な第2の構成例を示す図である。

【図6】SPAD画素の断面的な第3の構成例を示す図である。

【図7】SPAD画素の配線層における平面的な第3の構成例を示す図である。

【図8】SPAD画素の断面的な第4の構成例を示す図である。

【図9】SPAD画素の断面的な第5の構成例を示す図である。

【図10】SPAD画素の配線層における平面的な第5の構成例を示す図である。

【図11】SPAD画素の断面的な第6の構成例を示す図である。

40

【図12】SPAD画素の断面的な第7の構成例を示す図である。

【図13】SPAD画素の断面的な第8の構成例を示す図である。

【図14】距離画像センサの構成例を示すブロック図である。

【図15】イメージセンサを使用する使用例を示す図である。

【発明を実施するための形態】

【0015】

以下、本技術を適用した具体的な実施の形態について、図面を参照しながら詳細に説明する。

【0016】

<センサチップの構成例>

50

**【 0 0 1 7 】**

図1は、本技術を適用したセンサチップの一実施の形態の構成例を示すブロック図である。

**【 0 0 1 8 】**

図1において、センサチップ11は、画素アレイ部12、およびバイアス電圧印加部13を備えて構成される。

**【 0 0 1 9 】**

画素アレイ部12は、図示しない光学系により集光される光を受光する受光面であり、複数のSPAD画素21が行列状に配置されている。図1の右側に示すように、SPAD画素21は、SPAD素子31、p型MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)32、およびCMOSインバータ33を備えて構成される。

10

**【 0 0 2 0 】**

SPAD素子31は、カソードに大きな負電圧V<sub>BD</sub>を印加することによってアバランシェ増倍領域を形成し、1フォトンの入射で発生する電子をアバランシェ増倍させることができる。p型MOSFET32は、SPAD素子31でアバランシェ増倍された電子による電圧が負電圧V<sub>BD</sub>に達すると、SPAD素子31で増倍された電子を放出して、初期電圧に戻すクエンチング(quenting)を行う。CMOSインバータ33は、SPAD素子31で増倍された電子により発生する電圧を整形することで、1フォトンの到来時刻を始点としてパルス波形が発生する受光信号(APD OUT)を出力する。

**【 0 0 2 1 】**

バイアス電圧印加部13は、画素アレイ部12に配置される複数のSPAD画素21それぞれに対してバイアス電圧を印加する。

20

**【 0 0 2 2 】**

このように構成されているセンサチップ11からは、SPAD画素21ごとに受光信号が出力され、図示しない後段の演算処理部に供給される。例えば、演算処理部は、それぞれの受光信号において1フォトンの到来時刻を示すパルスが発生したタイミングに基づいて、被写体までの距離を求める演算処理を行って、SPAD画素21ごとに距離を求める。そして、それらの距離に基づいて、複数のSPAD画素21により検出された被写体までの距離を平面的に並べた距離画像が生成される。

**【 0 0 2 3 】**

<SPAD画素の第1の構成例>

30

**【 0 0 2 4 】**

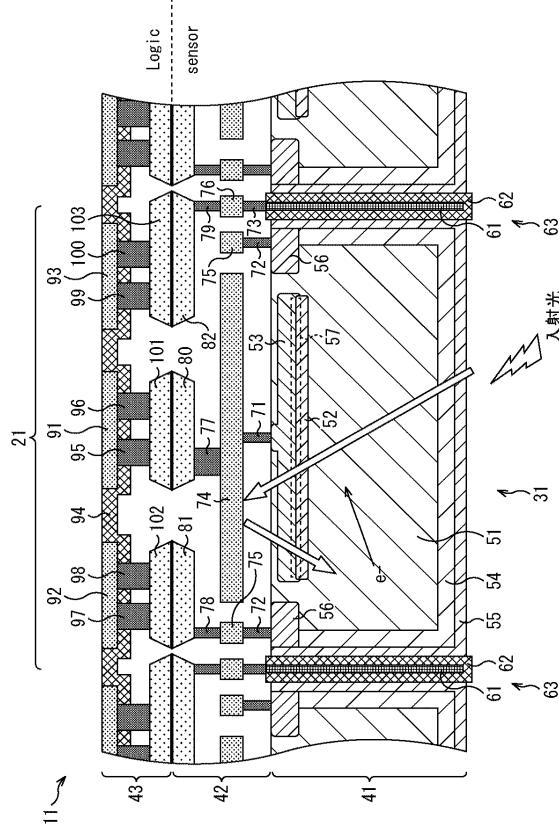

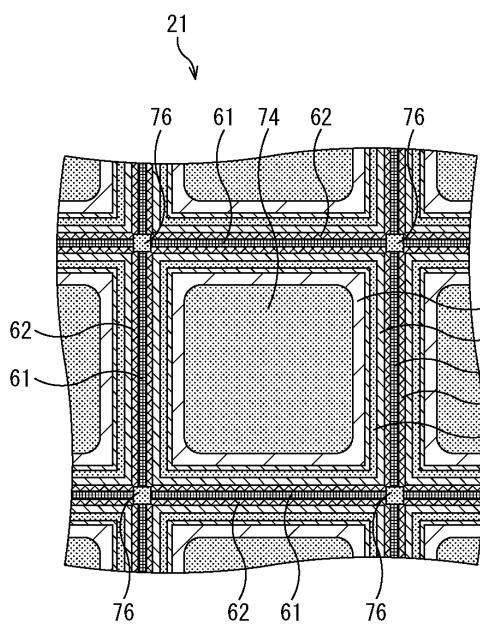

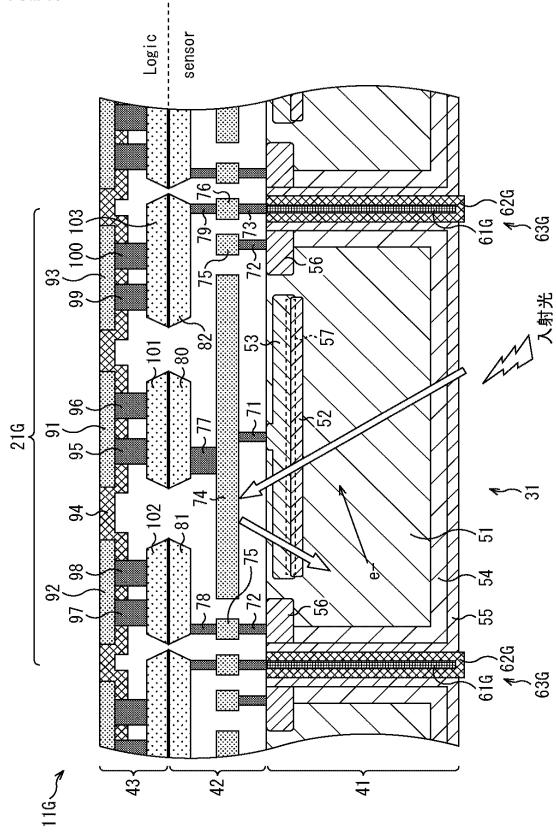

図2および図3を参照して、センサチップ11に形成されるSPAD画素21の第1の構成例について説明する。図2には、SPAD画素21の断面的な構成例が示されており、図3には、SPAD画素21の配線層における平面的な構成例が示されている。

**【 0 0 2 5 】**

図2に示すように、センサチップ11は、センサ基板41、センサ側配線層42、およびロジック側配線層43が積層された積層構造となっており、ロジック側配線層43に対して、図示しないロジック回路基板が積層されて構成される。ロジック回路基板には、例えば、図1のバイアス電圧印加部13や、p型MOSFET32、CMOSインバータ33などが形成されている。例えば、センサチップ11は、センサ基板41に対してセンサ側配線層42を形成するともに、ロジック回路基板に対してロジック側配線層43を形成した後、センサ側配線層42およびロジック側配線層43を接合面(図2の破線で示す面)で接合する製造方法により製造することができる。

40

**【 0 0 2 6 】**

センサ基板41は、例えば、単結晶のシリコンを薄くスライスした半導体基板であって、p型またはn型の不純物濃度が制御されており、SPAD画素21ごとにSPAD素子31が形成される。また、図2においてセンサ基板41の下側を向く面が、光を受光する受光面とされ、その受光面の反対側となる表面に対してセンサ側配線層42が積層される。

**【 0 0 2 7 】**

センサ側配線層42およびロジック側配線層43には、SPAD素子31に印加する電圧を

50

供給するための配線や、SPAD素子31で発生した電子をセンサ基板41から取り出ための配線などが形成される。

#### 【0028】

SPAD素子31は、センサ基板41に形成されるNウェル51、P型拡散層52、N型拡散層53、ホール蓄積層54、ピニング層55、および高濃度P型拡散層56により構成される。そして、SPAD素子31では、P型拡散層52とN型拡散層53とが接続する領域に形成される空乏層によって、アバランシェ増倍領域57が形成される。

#### 【0029】

Nウェル51は、センサ基板41の不純物濃度がn型に制御されることにより形成され、SPAD素子31における光電変換により発生する電子をアバランシェ増倍領域57へ転送する電界を形成する。なお、Nウェル51に替えて、センサ基板41の不純物濃度をp型に制御してPウェルを形成してもよい。

10

#### 【0030】

P型拡散層52は、センサ基板41の表面近傍であってN型拡散層53に対して裏面側(図2の下側)に形成される濃いP型の拡散層(P+)であり、SPAD素子31のほぼ全面に亘るように形成される。

#### 【0031】

N型拡散層53は、センサ基板41の表面近傍であってP型拡散層52に対して表面側(図2の上側)に形成される濃いN型の拡散層(N+)であり、SPAD素子31のほぼ全面に亘るように形成される。また、N型拡散層53は、アバランシェ増倍領域57を形成するための負電圧を供給するためのコンタクト電極71と接続するために、その一部がセンサ基板41の表面まで形成されるような凸形状となっている。

20

#### 【0032】

ホール蓄積層54は、Nウェル51の側面および底面を囲うように形成されるP型の拡散層(P)であり、ホールを蓄積している。また、ホール蓄積層54は、SPAD素子31のアノードと電気的に接続されており、バイアス調整を可能とする。これにより、ホール蓄積層54のホール濃度が強化され、ピニング層55を含むピニングが強固になることによって、例えば、暗電流の発生を抑制することができる。

#### 【0033】

ピニング層55は、ホール蓄積層54よりも外側の表面(センサ基板41の裏面や絶縁膜62と接する側面)に形成される濃いP型の拡散層(P+)であり、ホール蓄積層54と同様に、例えば、暗電流の発生を抑制する。

30

#### 【0034】

高濃度P型拡散層56は、センサ基板41の表面近傍においてNウェル51の外周を囲うように形成される濃いP型の拡散層(P++)であり、ホール蓄積層54をSPAD素子31のアノードと電気的に接続するためのコンタクト電極72との接続に用いられる。

#### 【0035】

アバランシェ増倍領域57は、N型拡散層53に印加される大きな負電圧によってP型拡散層52およびN型拡散層53の境界面に形成される高電界領域であって、SPAD素子31に入射する1フォトンで発生する電子(e-)を増倍する。

40

#### 【0036】

また、センサチップ11には、隣接するSPAD素子31どうしの間に形成されるメタル膜61および絶縁膜62による二重構造の画素間分離部63によって、それぞれのSPAD素子31が絶縁されて分離される。例えば、画素間分離部63は、センサ基板41の裏面から表面まで貫通するように形成される。

#### 【0037】

メタル膜61は、光を反射する金属(例えば、タンクステンなど)により形成される膜であり、絶縁膜62は、SiO<sub>2</sub>などの絶縁性を備えた膜である。例えば、メタル膜61の表面が絶縁膜62で覆われるようセンサ基板41に埋め込まれることで画素間分離部63は形成され、画素間分離部63によって、隣接するSPAD素子31との間で電気的および光

50

学的に分離される。

**【 0 0 3 8 】**

センサ側配線層 4 2 には、コンタクト電極 7 1 乃至 7 3、メタル配線 7 4 乃至 7 6、コンタクト電極 7 7 乃至 7 9、および、メタルパッド 8 0 乃至 8 2 が形成される。

**【 0 0 3 9 】**

コンタクト電極 7 1 は、N 型拡散層 5 3 とメタル配線 7 4 とを接続し、コンタクト電極 7 2 は、高濃度 P 型拡散層 5 6 とメタル配線 7 5 とを接続し、コンタクト電極 7 3 は、メタル膜 6 1 とメタル配線 7 6 とを接続する。

**【 0 0 4 0 】**

メタル配線 7 4 は、例えば、図 3 に示すように、少なくともアバランシェ増倍領域 5 7 を覆うように、アバランシェ増倍領域 5 7 よりも広く形成される。そして、メタル配線 7 4 は、図 2 において白抜きの矢印で示すように、SPAD 素子 3 1 を透過した光を、SPAD 素子 3 1 に反射する。10

**【 0 0 4 1 】**

メタル配線 7 5 は、例えば、図 3 に示すように、メタル配線 7 4 の外周を囲うように、高濃度 P 型拡散層 5 6 と重なるように形成される。メタル配線 7 6 は、例えば、図 3 に示すように、SPAD 画素 2 1 の四隅でメタル膜 6 1 に接続するように形成される。

**【 0 0 4 2 】**

コンタクト電極 7 7 は、メタル配線 7 4 とメタルパッド 8 0 とを接続し、コンタクト電極 7 8 は、メタル配線 7 5 とメタルパッド 8 1 とを接続し、コンタクト電極 7 9 は、メタル配線 7 6 とメタルパッド 8 2 とを接続する。20

**【 0 0 4 3 】**

メタルパッド 8 0 乃至 8 2 は、ロジック側配線層 4 3 に形成されているメタルパッド 1 0 1 乃至 1 0 3 と、それぞれを形成する金属 (Cu) どうしにより電気的および機械的に接合するのに用いられる。

**【 0 0 4 4 】**

ロジック側配線層 4 3 には、電極パッド 9 1 乃至 9 3、絶縁層 9 4、コンタクト電極 9 5 乃至 1 0 0、およびメタルパッド 1 0 1 乃至 1 0 3 が形成される。

**【 0 0 4 5 】**

電極パッド 9 1 乃至 9 3 は、それぞれロジック回路基板 (図示せず) との接続に用いられ、絶縁層 9 4 は、電極パッド 9 1 乃至 9 3 どうしを絶縁する。30

**【 0 0 4 6 】**

コンタクト電極 9 5 および 9 6 は、電極パッド 9 1 とメタルパッド 1 0 1 とを接続し、コンタクト電極 9 7 および 9 8 は、電極パッド 9 2 とメタルパッド 1 0 2 とを接続し、コンタクト電極 9 9 および 1 0 0 は、電極パッド 9 3 とメタルパッド 1 0 3 とを接続する。

**【 0 0 4 7 】**

メタルパッド 1 0 1 は、メタルパッド 8 0 と接合され、メタルパッド 1 0 2 は、メタルパッド 8 1 と接合され、メタルパッド 1 0 3 は、メタルパッド 8 2 と接合される。

**【 0 0 4 8 】**

このような配線構造により、例えば、電極パッド 9 1 は、コンタクト電極 9 5 および 9 6 、メタルパッド 1 0 1 、メタルパッド 8 0 、コンタクト電極 7 7 、メタル配線 7 4 、並びに、コンタクト電極 7 1 を介して、N 型拡散層 5 3 に接続されている。従って、SPAD 画素 2 1 では、N 型拡散層 5 3 に印加される大きな負電圧を、ロジック回路基板から電極パッド 9 1 に対して供給することができる。40

**【 0 0 4 9 】**

また、電極パッド 9 2 は、コンタクト電極 9 7 および 9 8 、メタルパッド 1 0 2 、メタルパッド 8 1 、コンタクト電極 7 8 、メタル配線 7 5 、並びに、コンタクト電極 7 2 を介して高濃度 P 型拡散層 5 6 に接続される接続構成となっている。従って、SPAD 画素 2 1 では、ホール蓄積層 5 4 と電気的に接続される SPAD 素子 3 1 のアノードが電極パッド 9 2 に接続されることで、電極パッド 9 2 を介してホール蓄積層 5 4 に対するバイアス調整を50

可能とすることができます。

#### 【0050】

さらに、電極パッド93は、コンタクト電極99および100、メタルパッド103、メタルパッド82、コンタクト電極79、メタル配線76、並びに、コンタクト電極73を介して、メタル膜61に接続される接続構成となっている。従って、SPAD画素21では、ロジック回路基板から電極パッド93に供給されるバイアス電圧をメタル膜61に印加することができる。

#### 【0051】

そして、SPAD画素21は、上述したように、メタル配線74が、少なくともアバランシェ増倍領域57を覆うように、アバランシェ増倍領域57よりも広く形成されるとともに、メタル膜61がセンサ基板41を貫通するように形成されている。即ち、SPAD画素21は、メタル配線74およびメタル膜61によりSPAD素子31の光入射面以外を全て取り囲んだ反射構造となるように形成されている。これにより、SPAD画素21は、メタル配線74およびメタル膜61により光を反射する効果によって、光学的なクロストークの発生を防止することができるとともに、SPAD素子31の感度を向上させることができる。

10

#### 【0052】

また、SPAD画素21は、Nウェル51の側面および底面をホール蓄積層54で囲み、ホール蓄積層54をSPAD素子31のアノードと電気的に接続する接続構成によって、バイアス調整を可能とすることができます。さらに、SPAD画素21は、画素間分離部63のメタル膜61にバイアス電圧を印加することによって、キャリアをアバランシェ増倍領域57にアシストする電界を形成することができる。

20

#### 【0053】

以上のように構成されるSPAD画素21は、クロストークの発生が防止されるとともに、SPAD素子31の感度が向上される結果、特性の向上を図ることができます。

#### 【0054】

<SPAD画素の第2の構成例>

#### 【0055】

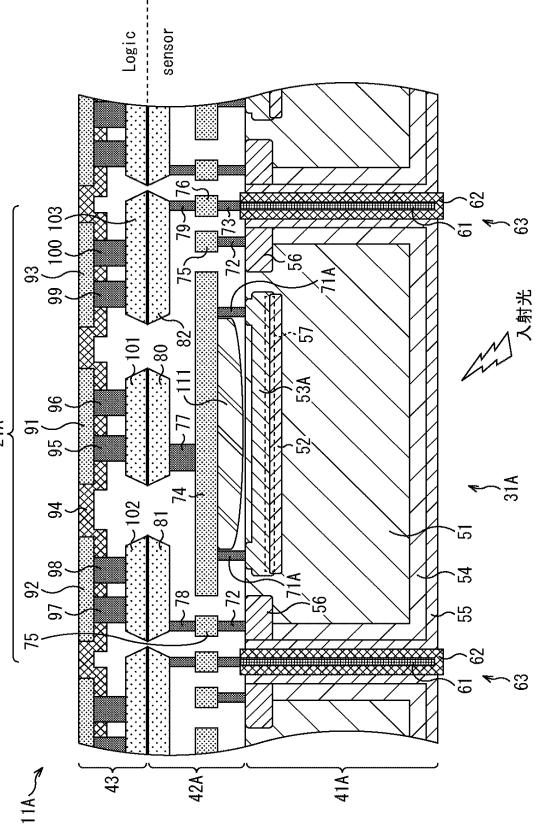

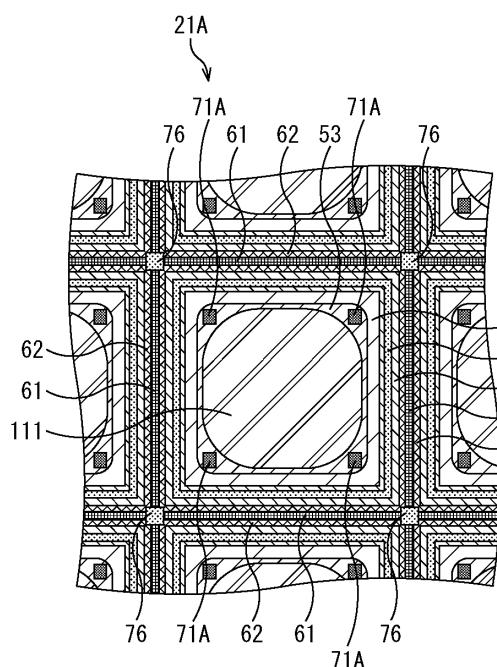

図4および図5を参照して、第2の構成例のSPAD画素21Aが形成されたセンサチップ11Aについて説明する。図4には、SPAD画素21Aの断面的な構成例が示されており、図5には、SPAD画素21Aの配線層における平面的な構成例が示されている。なお、図4および図5に示すセンサチップ11AおよびSPAD画素21Aにおいて、図2および図3のセンサチップ11およびSPAD画素21と共通する構成については同一の符号を付し、その詳細な説明は省略する。

30

#### 【0056】

図4に示すように、センサチップ11AのSPAD画素21Aは、センサ側配線層42Aにインナーレンズ111が配置されている点で、図2のセンサチップ11のSPAD画素21と異なる構成となっている。

#### 【0057】

インナーレンズ111は、センサ基板41Aとメタル配線74との間に配置され、センサ基板41A側に向かって凸となる凸形状の集光レンズである。例えば、インナーレンズ111は、メタル配線74で反射する反射光をSPAD素子31Aの中央に向かって集光するように形成される。

40

#### 【0058】

また、SPAD画素21Aでは、インナーレンズ111を回避してN型拡散層53Aとメタル配線74とを接続するために、図5に示すように、4本のコンタクト電極71Aがインナーレンズ111よりも外側の四隅に配置されている。また、コンタクト電極71Aの位置に対応するように、センサ基板41AのSPAD素子31Aに形成されるN型拡散層53Aは、その一部がセンサ基板41の表面まで形成されるような凸形状となっている。

#### 【0059】

このようにSPAD画素21Aは構成されており、例えば、ある程度の斜め方向からSPAD素

50

子 3 1 A に入射して透過した光は、メタル配線 7 4 で反射した際に、インナーレンズ 1 1 1 によって SPAD 素子 3 1 A の中央に向かうように集光される。従って、SPAD 画素 2 1 A は、インナーレンズ 1 1 1 により集光効率を向上することができるので、クロストークの発生が防止されるとともに SPAD 素子 3 1 A の感度が向上される結果、特性の向上を図ることができる。

#### 【 0 0 6 0 】

< SPAD 画素の第 3 の構成例 >

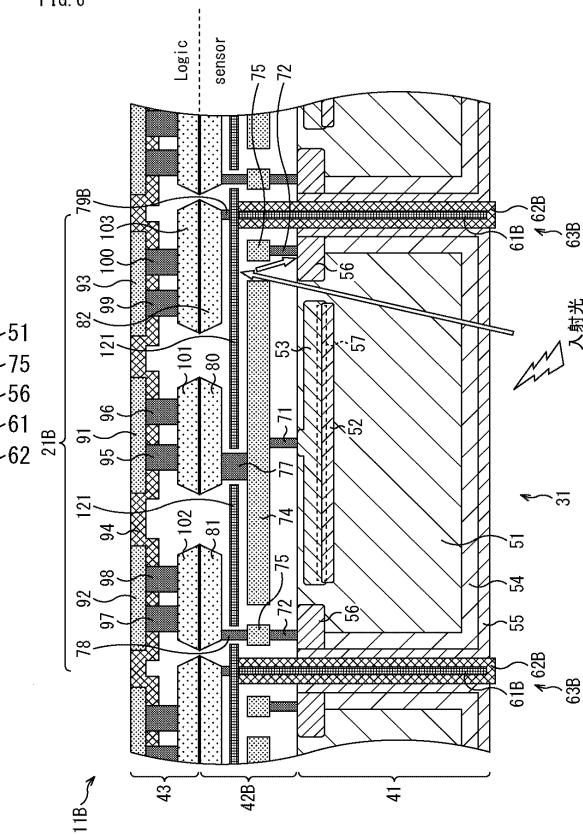

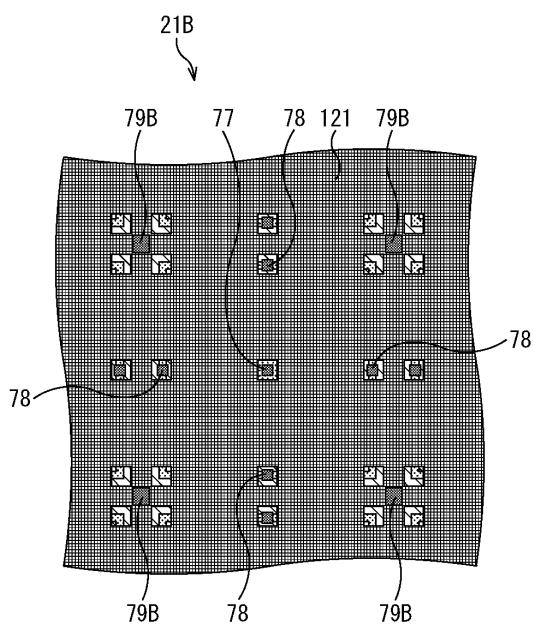

#### 【 0 0 6 1 】

図 6 および図 7 を参照して、第 3 の構成例の SPAD 画素 2 1 B が形成されたセンサチップ 1 1 B について説明する。図 6 には、SPAD 画素 2 1 B の断面的な構成例が示されており、図 7 には、SPAD 画素 2 1 B の配線層における平面的な構成例が示されている。なお、図 6 および図 7 に示すセンサチップ 1 1 B および SPAD 画素 2 1 B において、図 2 および図 3 のセンサチップ 1 1 および SPAD 画素 2 1 と共に構成については同一の符号を付し、その詳細な説明は省略する。

10

#### 【 0 0 6 2 】

図 6 に示すように、センサチップ 1 1 B の SPAD 画素 2 1 B は、センサ側配線層 4 2 B に遮光膜 1 2 1 が配置されている点で、図 2 のセンサチップ 1 1 の SPAD 画素 2 1 と異なる構成となっている。

#### 【 0 0 6 3 】

遮光膜 1 2 1 は、メタル配線 7 4 および 7 5 とメタルパッド 8 0 乃至 8 2 との間に配置され、メタル配線 7 4 および 7 5 の間の隙間を通過した光を遮光する。遮光膜 1 2 1 は、図 7 に示すように、コンタクト電極 7 7 および 7 8 を貫通させる箇所に開口部が設けられ、その開口部以外のほぼ全面に亘って形成される。

20

#### 【 0 0 6 4 】

また、遮光膜 1 2 1 は、例えば、メタル膜 6 1 と同様に、光を反射する金属（例えば、タンゲステンなど）により形成することができ、図 6 の白抜きの矢印で示すように、SPAD 素子 3 1 を透過して、メタル配線 7 4 および 7 5 の間の隙間を通過した光を反射する。

#### 【 0 0 6 5 】

さらに、SPAD 画素 2 1 B の画素間分離部 6 3 B は、メタル膜 6 1 B および絶縁膜 6 2 B が、センサ基板 4 1 を貫通してセンサ側配線層 4 2 B に向かって突出し、遮光膜 1 2 1 まで届くように形成される。また、メタル膜 6 1 B は、遮光膜 1 2 1 に電気的に接続される。そして、コンタクト電極 7 9 B は、メタルパッド 8 2 と遮光膜 1 2 1 との間を接続するように形成され、遮光膜 1 2 1 を介してメタル膜 6 1 B にバイアス電圧が印加される。

30

#### 【 0 0 6 6 】

このように SPAD 画素 2 1 B は構成されており、メタル配線 7 4 および 7 5 が形成される層を覆うように、メタル膜 6 1 B および遮光膜 1 2 1 が形成されることにより、SPAD 素子 3 1 を透過した光が確実に反射される。従って、SPAD 画素 2 1 B は、メタル膜 6 1 B および遮光膜 1 2 1 により、隣接する他の SPAD 素子 3 1 への光の混入を防止することができるので、クロストークの発生が防止されるとともに SPAD 素子 3 1 の感度が向上される結果、特性の向上を図ることができる。

40

#### 【 0 0 6 7 】

< SPAD 画素の第 4 の構成例 >

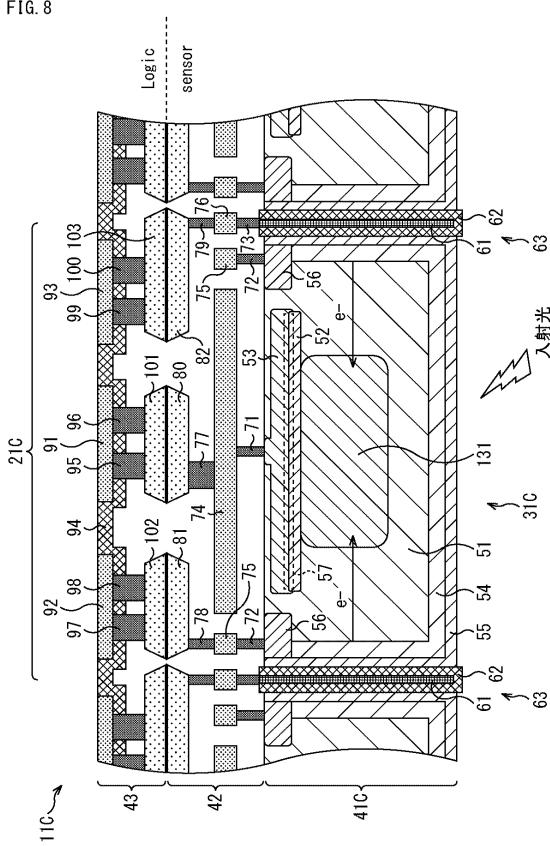

#### 【 0 0 6 8 】

図 8 を参照して、第 4 の構成例の SPAD 画素 2 1 C が形成されたセンサチップ 1 1 C について説明する。図 8 には、SPAD 画素 2 1 C の断面的な構成例が示されている。なお、図 8 に示すセンサチップ 1 1 C および SPAD 画素 2 1 C において、図 2 のセンサチップ 1 1 および SPAD 画素 2 1 と共に構成については同一の符号を付し、その詳細な説明は省略する。

#### 【 0 0 6 9 】

図 8 に示すように、センサチップ 1 1 C の SPAD 画素 2 1 C は、センサ基板 4 1 C の SPAD

50

素子 31C に N 型領域 131 が形成されている点で、図 2 のセンサチップ 11 の SPAD 画素 21 と異なる構成となっている。

#### 【0070】

N 型領域 131 は、SPAD 素子 31C の中央において P 型拡散層 52 に接するように形成され、例えば、SPAD 素子 31C において発生したキャリア（電子）が周囲から中央に向かってドリフトし易くなるようなポテンシャルの勾配を形成する。つまり、SPAD 素子 31C では、N ウェル 51 に対して N 型の不純物を注入して N 型領域 131 を形成することによって、もともと N 型であることより、キャリアを集めよう電界が形成される。

#### 【0071】

さらに、SPAD 素子 31C では、画素間分離部 63 のメタル膜 61 にバイアス電圧を印加することによって、ホール蓄積層 54 および N ウェル 51 がバイアス電圧による電位に引っ張られるため、より強固なポテンシャルの井戸を形成することができる。これにより、SPAD 素子 31C は、そのような電位が与えられていないときよりも、N 型領域 131 に向かってキャリアをドリフトする電界を強化することができる。従って、SPAD 素子 31C は、N 型領域 131 にキャリアが集まり易くなる結果、効率的に、アバランシェ増倍領域 57 に電子を到達させることができる。

10

#### 【0072】

また、画素間分離部 63 は、メタル膜 61 および絶縁膜 62 により形成されることで二重の反射構造を有することができる。なお、メタル膜 61 に印加されるバイアス電圧を調整することによって、ホールを蓄積するホール蓄積層 54 が SPAD 素子 31C の外周に誘起されるようにしてもよい。

20

#### 【0073】

このように SPAD 画素 21C は構成されており、例えば、メタル膜 61 で反射した光によって発生した微小なキャリアも、メタル膜 61 にバイアス電圧を印加することで、N 型領域 131 におけるポテンシャルの勾配を強化することにより信号として取り込まれる。従って、SPAD 画素 21C は、このような微小なキャリアを取り込むことによる感度の向上を図るので、特性の向上を図ることができる。

#### 【0074】

< SPAD 画素の第 5 の構成例 >

30

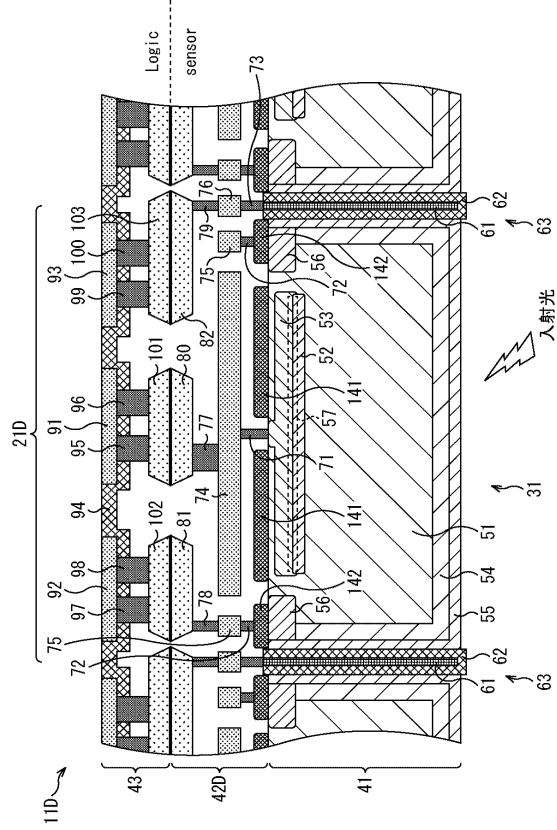

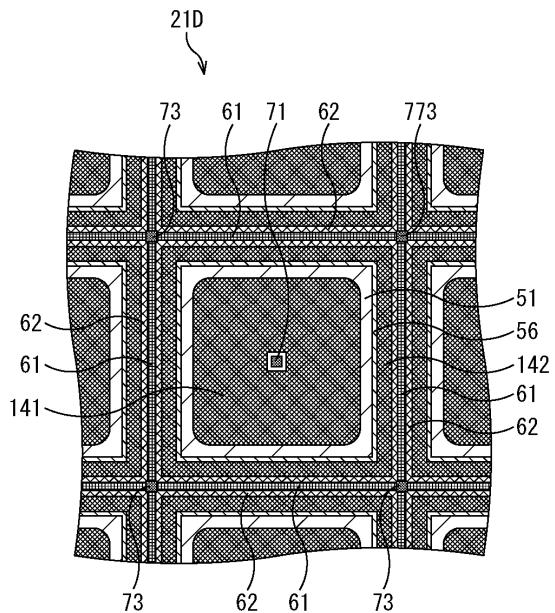

#### 【0075】

図 9 および図 10 を参照して、第 5 の構成例の SPAD 画素 21D が形成されたセンサチップ 11D について説明する。図 9 には、SPAD 画素 21D の断面的な構成例が示されており、図 10 には、SPAD 画素 21D の配線層における平面的な構成例が示されている。なお、図 9 および図 10 に示すセンサチップ 11D および SPAD 画素 21D において、図 2 および図 3 のセンサチップ 11 および SPAD 画素 21 と共通する構成については同一の符号を付し、その詳細な説明は省略する。

#### 【0076】

図 9 および図 10 に示すように、センサチップ 11D の SPAD 画素 21D は、センサ側配線層 42D に反射膜 141 および 142 が配置されている点で、図 2 および図 3 のセンサチップ 11 の SPAD 画素 21 と異なる構成となっている。

40

#### 【0077】

反射膜 141 および 142 は、例えば、センサ基板 41 の表面に成膜され、トランジスタのゲート電極として使用されるポリシリコン膜であり、光を反射する特性を備えている。また、図 10 に示すように平面的に見て、少なくともアバランシェ増倍領域 57 が反射膜 141 により覆い隠されるように、反射膜 141 は、アバランシェ増倍領域 57 よりも広い範囲に形成されることが好ましい。即ち、反射膜 141 は、平面的に見たときにメタル配線 74 と重なるように形成される。

#### 【0078】

このように SPAD 画素 21D は構成されており、SPAD 素子 31 を透過した光は、メタル配線 74 よりもセンサ基板 41 の近くに配置される反射膜 141 および 142 により反射さ

50

れることになり、センサ側配線層 4 2 Dまで透過する光が削減される。従って、SPAD画素 2 1 Dは、反射膜 1 4 1 および 1 4 2 により効果的に光を囲い込むことができるので、クロストークの発生が防止されるとともにSPAD素子 3 1 の感度が向上される結果、特性の向上を図ることができる。

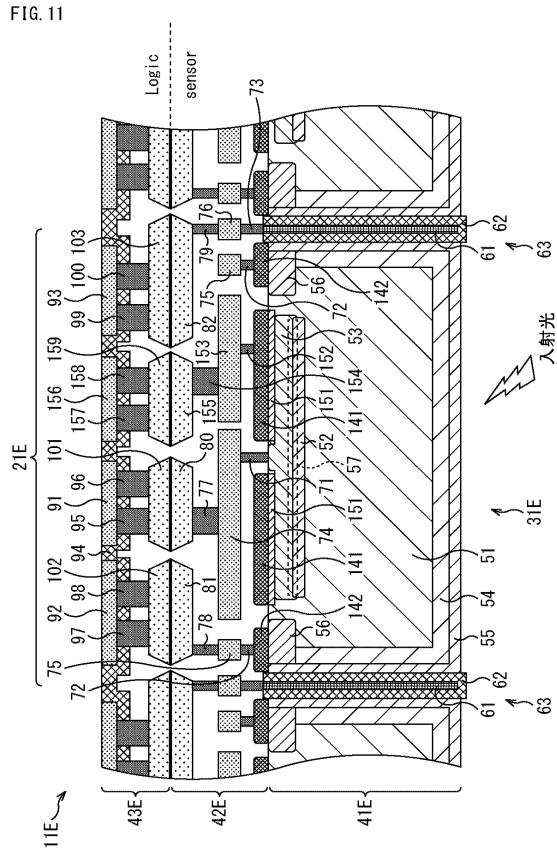

【 0 0 7 9 】

< SPAD画素の第 6 の構成例 >

【 0 0 8 0 】

図 1 1 を参照して、第 6 の構成例のSPAD画素 2 1 E が形成されたセンサチップ 1 1 E について説明する。図 1 1 には、SPAD画素 2 1 E の断面的な構成例が示されている。なお、図 1 1 に示すセンサチップ 1 1 E およびSPAD画素 2 1 E において、図 2 のセンサチップ 1 1 およびSPAD画素 2 1 と共に通する構成については同一の符号を付し、その詳細な説明は省略する。

10

【 0 0 8 1 】

図 1 1 に示すように、センサチップ 1 1 E のSPAD画素 2 1 E は、センサ基板 4 1 E の表面にホール蓄積層 1 5 1 が形成されている点で、図 2 のセンサチップ 1 1 のSPAD画素 2 1 と異なる構成となっている。

【 0 0 8 2 】

また、SPAD画素 2 1 E では、図 1 0 に示したSPAD画素 2 1 D と同様に反射膜 1 4 1 および 1 4 2 が配置されており、反射膜 1 4 1 にバイアス電圧を印加するための配線などがセンサ側配線層 4 2 E およびロジック側配線層 4 3 E に形成されている。

20

【 0 0 8 3 】

即ち、センサ側配線層 4 2 E では、コンタクト電極 1 5 2 、メタル配線 1 5 3 、コンタクト電極 1 5 4 、およびメタルパッド 1 5 5 が接続されて形成され、コンタクト電極 1 5 2 が反射膜 1 4 1 に接続されている。また、ロジック側配線層 4 3 E では、電極パッド 1 5 6 、コンタクト電極 1 5 7 および 1 5 8 、並びにメタルパッド 1 5 9 が接続されて形成され、メタルパッド 1 5 9 およびメタルパッド 1 5 5 が接合される。

【 0 0 8 4 】

従って、SPAD画素 2 1 E では、電極パッド 1 5 6 に供給されるバイアス電圧が反射膜 1 4 1 に印加されることで、センサ基板 4 1 E の表面における反射膜 1 4 1 と N 型拡散層 5 3 との間に、ホールを蓄積するホール蓄積層 1 5 1 が形成される。

30

【 0 0 8 5 】

このようにSPAD画素 2 1 E は構成されており、SPAD素子 3 1 E を透過した光が反射膜 1 4 1 および 1 4 2 により反射されるとともに、ホール蓄積層 1 5 1 によりアバランシェ増倍領域 5 7 の表面への露出を避けた暗電流が抑制される。従って、SPAD画素 2 1 E は、クロストークの発生が防止されるとともにSPAD素子 3 1 の感度が向上されるのに加えて、暗電流を抑制することができる結果、特性の向上を図ることができる。

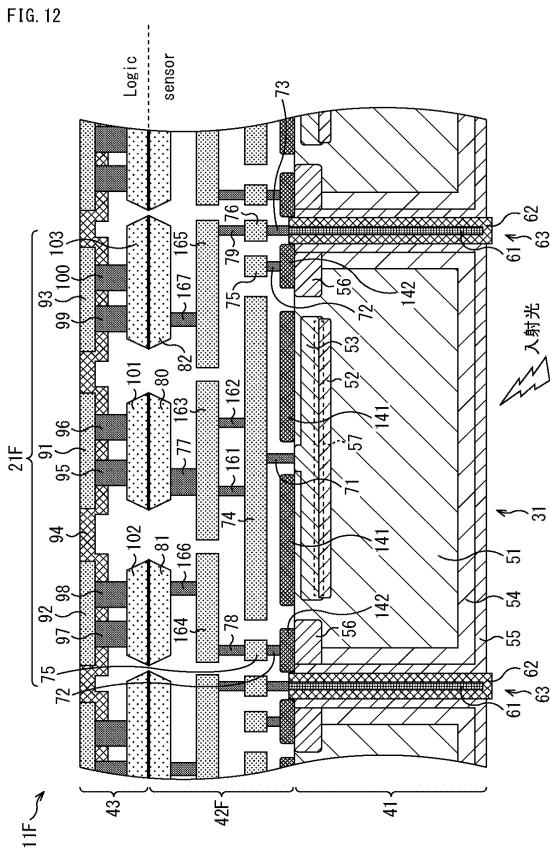

【 0 0 8 6 】

< SPAD画素の第 7 の構成例 >

【 0 0 8 7 】

図 1 2 を参照して、第 7 の構成例のSPAD画素 2 1 F が形成されたセンサチップ 1 1 F について説明する。図 1 2 には、SPAD画素 2 1 F の断面的な構成例が示されている。なお、図 1 2 に示すセンサチップ 1 1 F およびSPAD画素 2 1 F において、図 2 のセンサチップ 1 1 およびSPAD画素 2 1 と共に通する構成については同一の符号を付し、その詳細な説明は省略する。

40

【 0 0 8 8 】

図 1 2 に示すように、センサチップ 1 1 F のSPAD画素 2 1 F は、センサ側配線層 4 2 F が 2 層配線構造となっている点で、図 2 のセンサチップ 1 1 のSPAD画素 2 1 と異なる構成となっている。

【 0 0 8 9 】

即ち、図 2 のセンサチップ 1 1 のセンサ側配線層 4 2 は、メタル配線 7 4 乃至 7 6 が配置

50

された1層配線構造であったのに対し、センサチップ11Fのセンサ側配線層42Fは、メタル配線74乃至76およびメタル配線163乃至165が積層されて配置された2層配線構造となっている。なお、2層以上の多層配線構造を採用してもよい。

#### 【0090】

また、メタル配線74乃至76およびメタル配線163乃至165は、平面的に見て、メタル配線74乃至76どうしの間に設けられる隙間と、メタル配線163乃至165どうしの間に設けられる隙間とが重なり合わないように形成される。即ち、メタル配線74乃至76およびメタル配線163乃至165は、それぞれ互い違いに多重となるように形成されている。

#### 【0091】

さらに、SPAD画素21Fでは、図9のSPAD画素21Dと同様に、センサ基板41の表面に反射膜141および142が積層されている。

10

#### 【0092】

また、センサチップ11Fのセンサ側配線層42Fには、メタル配線74とメタル配線163とを接続するコンタクト電極161および162、メタルパッド81とメタル配線164とを接続するコンタクト電極166、並びに、メタルパッド82とメタル配線165とを接続するコンタクト電極167が形成されている。

#### 【0093】

このようにSPAD画素21Fは構成されており、アバランシェ増倍領域57を覆うようにセンサ側配線層42Fにおいて幾重に形成される反射物（即ち、メタル配線74乃至76、メタル配線163乃至165、および反射膜141および142）によりSPAD素子31を透過した光が反射される。従って、SPAD画素21Fは、SPAD素子31を透過した光の回折や散乱反射などを抑制することができる、クロストークの発生が防止されるとともにSPAD素子31の感度が向上される結果、特性の向上を図ることができる。

20

#### 【0094】

<SPAD画素の第8の構成例>

#### 【0095】

図13を参照して、第8の構成例のSPAD画素21Gが形成されたセンサチップ11Gについて説明する。図13には、SPAD画素21Gの断面的な構成例が示されている。なお、図13に示すセンサチップ11GおよびSPAD画素21Gにおいて、図2のセンサチップ11およびSPAD画素21と共に構成については同一の符号を付し、その詳細な説明は省略する。

30

#### 【0096】

図13に示すように、センサチップ11GのSPAD画素21Gは、画素間分離部63Gの高さがセンサ基板41の表面（バルク表面）と一致するように形成される点で、図2のセンサチップ11のSPAD画素21と異なる構成となっている。

#### 【0097】

例えば、図2のSPAD画素21では、センサ基板41の表面からセンサ側配線層42に若干突出するように画素間分離部63が形成されている。これに対し、SPAD画素21Gでは、画素間分離部63Gを構成するメタル膜61Gおよび絶縁膜62Gが、センサ基板41の表面と一致するように形成するように形成される。

40

#### 【0098】

このように、画素間分離部63Gの高さを低く形成しても、クロストークの発生を十分に抑制することができるのであれば、センサ基板41の表面と一致するまで低く形成してもよい。即ち、画素間分離部63は、センサ基板41の表面からセンサ側配線層42に突出するように形成される必要はない。

#### 【0099】

このように形成されるSPAD画素21Gにおいても、SPAD素子31を透過する光をメタル配線74により反射することにより、クロストークの発生が防止されるとともにSPAD素子31の感度が向上される結果、特性の向上を図ることができる。

50

**【0100】**

なお、SPAD画素21Gと同様に、画素間分離部63Gの高さがセンサ基板41の表面と一致するように形成される構成を、上述したSPAD画素21A乃至31Fの構成と組み合わせて用いてもよい。

**【0101】**

<撮像装置の構成例>

**【0102】**

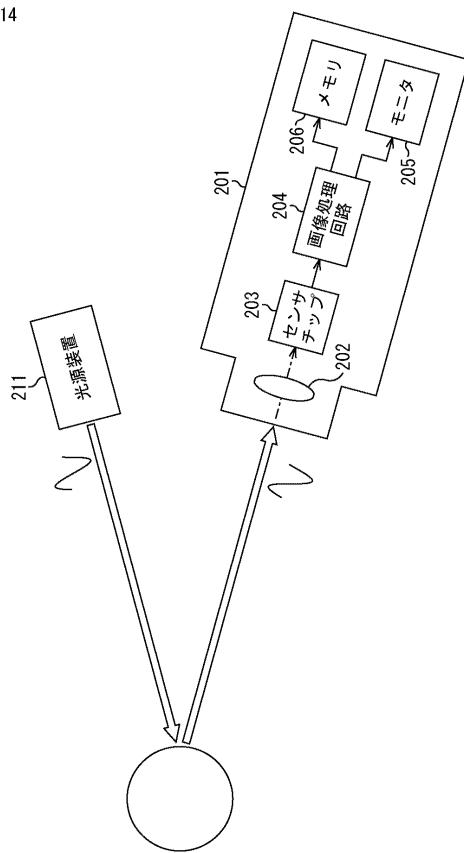

図14は、センサチップ11を利用した電子機器である距離画像センサの構成例を示すブロック図である。

**【0103】**

図14に示すように、距離画像センサ201は、光学系202、センサチップ203、画像処理回路204、モニタ205、およびメモリ206を備えて構成される。そして、距離画像センサ201は、光源装置211から被写体に向かって投光され、被写体の表面で反射された光（変調光やパルス光）を受光することにより、被写体までの距離に応じた距離画像を取得することができる。

10

**【0104】**

光学系202は、1枚または複数枚のレンズを有して構成され、被写体からの像光（入射光）をセンサチップ203に導き、センサチップ203の受光面（センサ部）に結像させる。

**【0105】**

センサチップ203としては、上述した各実施の形態のセンサチップ11が適用され、センサチップ203から出力される受光信号（APD OUT）から求められる距離を示す距離信号が画像処理回路204に供給される。

20

**【0106】**

画像処理回路204は、センサチップ203から供給された距離信号に基づいて距離画像を構築する画像処理を行い、その画像処理により得られた距離画像（画像データ）は、モニタ205に供給されて表示されたり、メモリ206に供給されて記憶（記録）されたりする。

**【0107】**

このように構成されている距離画像センサ201では、上述したセンサチップ11を適用することで、SPAD画素21の特性向上に伴って、例えば、より正確な距離画像を取得することができる。

30

**【0108】**

<イメージセンサの使用例>

**【0109】**

図15は、上述のイメージセンサ（距離画像センサ）を使用する使用例を示す図である。

**【0110】**

上述したイメージセンサは、例えば、以下のように、可視光や、赤外光、紫外光、X線等の光をセンシングする様々なケースに使用することができる。

**【0111】**

- ・デジタルカメラや、カメラ機能付きの携帯機器等の、鑑賞の用に供される画像を撮影する装置

40

- ・自動停止等の安全運転や、運転者の状態の認識等のために、自動車の前方や後方、周囲、車内等を撮影する車載用センサ、走行車両や道路を監視する監視カメラ、車両間等の測距を行う測距センサ等の、交通の用に供される装置

- ・ユーザのジェスチャを撮影して、そのジェスチャに従った機器操作を行うために、TVや、冷蔵庫、エアーコンディショナ等の家電に供される装置

- ・内視鏡や、赤外光の受光による血管撮影を行う装置等の、医療やヘルスケアの用に供される装置

- ・防犯用途の監視カメラや、人物認証用途のカメラ等の、セキュリティの用に供される装置

50

- ・肌を撮影する肌測定器や、頭皮を撮影するマイクロスコープ等の、美容の用に供される装置

- ・スポーツ用途等向けのアクションカメラやウェアラブルカメラ等の、スポーツの用に供される装置

- ・畑や作物の状態を監視するためのカメラ等の、農業の用に供される装置

## 【0112】

なお、本技術は以下のような構成も取ることができる。

(1)

複数の画素がアレイ状に配置された画素アレイ部と、

前記画素ごとに設けられる高電界領域によりキャリアを増倍させるアバランシェフォトダイオード素子と、

前記アバランシェフォトダイオード素子が形成される半導体基板において隣接する他の前記画素との間を絶縁して分離する画素間分離部と、

前記高電界領域を少なくとも覆うように、前記半導体基板の受光面の反対側となる表面に

対して積層される配線層に設けられるメタル配線と

を備えるセンサチップ。

(2)

前記メタル配線と前記半導体基板との間に設けられ、前記アバランシェフォトダイオード素子を透過して前記メタル配線で反射した光を前記アバランシェフォトダイオード素子の中央に集光するインナーレンズ

をさらに備える上記(1)に記載のセンサチップ。

(3)

前記画素間分離部は、前記半導体基板の裏面から前記表面まで貫通するように形成される上記(1)または(2)に記載のセンサチップ。

(4)

前記画素間分離部は、光を反射する金属膜と絶縁性を備えた絶縁膜とによる二重構造とされ、前記金属膜の表面が前記絶縁膜で覆われるように前記半導体基板に埋め込まれて形成される

上記(1)から(3)までのいずれかに記載のセンサチップ。

(5)

前記画素間分離部として前記半導体基板に埋め込まれた金属膜に電圧を印加することによって、ホールを蓄積するホール蓄積層が前記アバランシェフォトダイオード素子の外周に誘起される

上記(1)から(4)までのいずれかに記載のセンサチップ。

(6)

前記画素間分離部として前記半導体基板に埋め込まれた金属膜に電圧を印加することによって、キャリアをドリフトする電界が強化される

上記(1)から(5)までのいずれかに記載のセンサチップ。

(7)

前記高電界領域を少なくとも覆うように、光を反射する反射膜が前記半導体基板の表面に

対して形成される

上記(1)から(6)までのいずれかに記載のセンサチップ。

(8)

前記反射膜に対して電圧を印加することによって、前記半導体基板の表面近傍に、ホールを蓄積するホール蓄積層を形成する

上記(7)に記載のセンサチップ。

(9)

前記反射膜は、平面的に見たときに前記メタル配線に重なるように形成される

上記(7)または(8)に記載のセンサチップ。

(10)

10

20

30

40

50

前記画素間分離部の高さが、前記半導体基板の表面と略一致するように形成される

上記(1)から(9)までのいずれかに記載のセンサチップ。

(11)

複数の画素がアレイ状に配置された画素アレイ部と、

前記画素ごとに設けられる高電界領域によりキャリアを増倍させるアバランシェフォトダイオード素子と、

前記アバランシェフォトダイオード素子が形成される半導体基板において隣接する他の前記画素との間を絶縁して分離する画素間分離部と、

前記高電界領域を少なくとも覆うように、前記半導体基板の受光面の反対側となる表面に

対して積層される配線層に設けられるメタル配線と

を有するセンサチップを備える電子機器。

【0113】

なお、本実施の形態は、上述した実施の形態に限定されるものではなく、本開示の要旨を

逸脱しない範囲において種々の変更が可能である。

【符号の説明】

【0114】

11 センサチップ， 12 画素アレイ部， 13 バイアス電圧印加部， 21 SPAD

画素， 31 SPAD素子， 32 p型MOSFET 32， 33 CMOSインバータ， 41

センサ基板， 42 センサ側配線層， 43 ロジック側配線層， 51 Nウェル， 5

2 P型拡散層， 53 N型拡散層， 54 ホール蓄積層， 55 ピニング層， 56

高濃度P型拡散層， 57 アバランシェ増倍領域， 61 メタル膜， 62 絶縁膜，

63 画素間分離部， 71乃至73 コンタクト電極， 74乃至76 メタル配線， 7

7乃至79 コンタクト電極， 80乃至82 メタルパッド， 91乃至93 電極パッ

ド， 94 絶縁層， 95乃至100 コンタクト電極， 101乃至103 メタルパッド

10

20

30

40

50

【四面】

【 四 1 】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

10

20

30

40

50

【図 5】

FIG. 5

【図 6】

FIG. 6

10

20

30

40

50

【図 7】

FIG. 7

【図 8】

FIG. 8

【図9】

FIG. 9

【 図 1 0 】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

【図 13】

FIG. 13

【図 14】

FIG. 14

10

20

30

【図 15】

FIG. 15

40

50

---

フロントページの続き

神奈川県厚木市旭町四丁目14番1号 ソニーセミコンダクタソリューションズ株式会社内

(72)発明者 若野 壽史

神奈川県厚木市旭町四丁目14番1号 ソニーセミコンダクタソリューションズ株式会社内

審査官 佐竹 政彦

(56)参考文献

特開2016-062996 (JP, A)

特開2014-203961 (JP, A)

特開2010-147474 (JP, A)

特開2015-026708 (JP, A)

特開2015-084392 (JP, A)

特開2004-273640 (JP, A)

特開2014-225647 (JP, A)

米国特許出願公開第2003/0218120 (US, A1)

米国特許出願公開第2013/0193546 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H01L 31/00 - 31/20

H01L 27/144 - 27/148

I E E E X p l o r e