US 20050243734A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2005/0243734 A1

#### (10) Pub. No.: US 2005/0243734 A1 (43) Pub. Date: Nov. 3, 2005

### Nemirovsky et al.

- (54) MULTI-THREADED PACKET PROCESSING ENGINE FOR STATEFUL PACKET PROCESSING

- (76) Inventors: Mario D. Nemirovsky, (US); Enrique Musoll, (US); Jeffery T. Huynh, (US)

Correspondence Address: HICKMAN PALERMO TRUONG & BECKER, LLP 2055 GATEWAY PLACE SUITE 550 SAN JOSE, CA 95110 (US)

- (21) Appl. No.: 11/152,879

- (22) Filed: Jun. 14, 2005

#### **Related U.S. Application Data**

(63) Continuation of application No. 10/254,377, filed on Sep. 24, 2002. (60) Provisional application No. 60/325,638, filed on Sep. 28, 2001. Provisional application No. 60/341,689, filed on Dec. 17, 2001. Provisional application No. 60/388,278, filed on Jun. 13, 2002.

#### **Publication Classification**

- (51) Int. Cl.<sup>7</sup> ...... H04L 1/00

#### (57) **ABSTRACT**

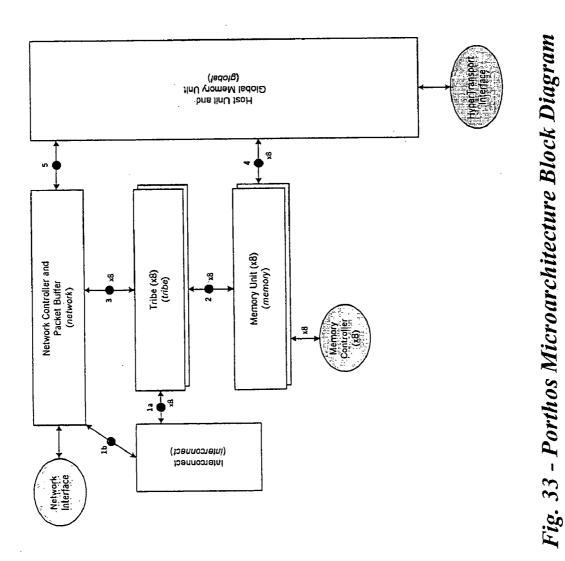

A processing engine to accomplish a multiplicity of tasks has a multiplicity of processing tribes, each tribe comprising a multiplicity of context register sets and a multiplicity of processing resources for concurrent processing of a multiplicity of threads to accomplish the tasks, a memory structure having a multiplicity of memory blocks, each block storing data for processing threads, and an interconnect structure and control system enabling tribe-to-tribe migration of contexts to move threads from tribe-to-tribe. The processing engine is characterized in that individual ones of the tribes have preferential access to individual ones of the multiplicity of memory blocks.

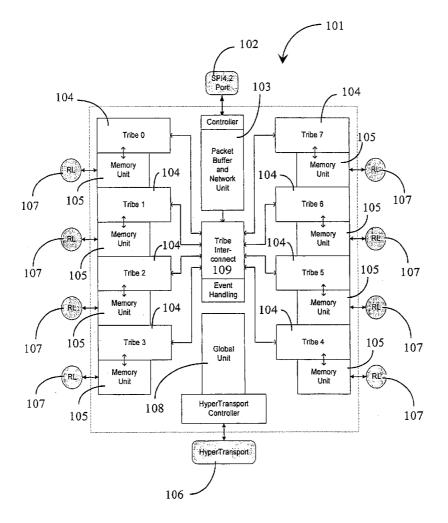

Fig. 1

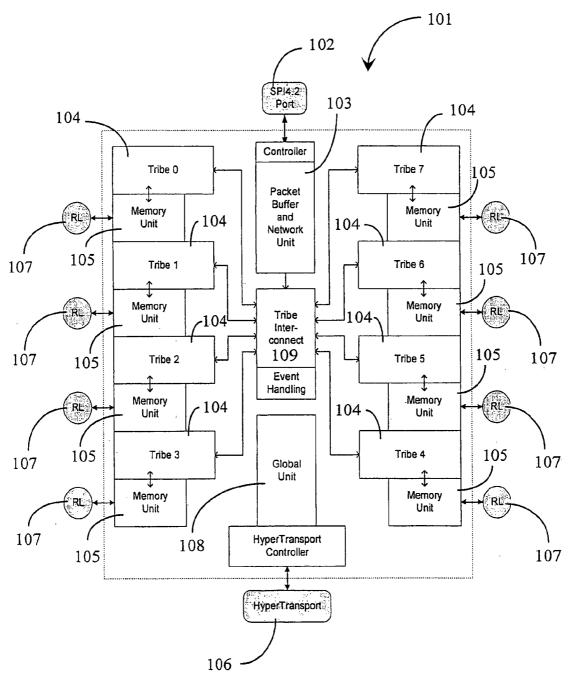

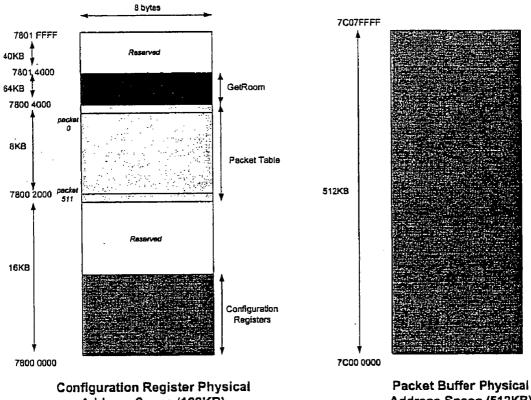

### Fig. 2 - Memory Map

Address Space (128KB)

Address Space (512KB)

Fig. 3 -Address Space

|   | #       | Name                   | Format<br>(TBD) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|---------|------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ſ | 07      | program_counter[07]    |                 | Provides the initial PC to each of the tribes (07) for the initial migration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Ī | 8127    | reserved               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 128     | status                 |                 | Specifies whether the NET module has come out<br>of reset and whether it is in quiescent mode or not.<br>The quiescent information is don't care is the NET<br>has not come out of reset.                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 129     | continue               |                 | If 1, the NET module will receive packets from<br>the SPI4 ingress port. If 0, the NET module will<br>drop the packets that it receives from the SPI4<br>ingress port.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 130     | total_ports            |                 | Specifies the total number of full-duplex ports.<br>The valid values are 1, 2 and 4. The value 3 is<br>reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 131     | port_type              |                 | Specifies the type of the ports (channelized or<br>non-channelized). All ports will become of the<br>same type.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 132     | internal_state_number  |                 | Software writes to this register an internal state<br>word number. When software reads this register, it<br>obtains the value associated to the internal state<br>word number last written.                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 133-220 | reserved               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 221     | egress_path_determined |                 | Software writes in this register a value containing<br>the sequence number, the encoded egress channel<br>(if applicable), and the encoded egress port to<br>report that the packet still has not been completed<br>but its egress path information has been fully<br>determined.<br>Software is not required to write into this register<br>(the same functionality is obtained by the<br>mandatory writing into the 'done' configuration<br>register), but by doing so it helps the performance<br>on those applications that require an egress<br>interleaving degree greater than 1. |

|   | 222     | defauit_egress_port_0  |                 | Specifies which of the egress ports $(0-3)$ is the default port for those packets that came through ingress port 0. This default port is used whenever software requests to transmit a packet that resides in the packet buffer with an encoded egress port of $0x1$ .                                                                                                                                                                                                                                                                                                                   |

|   | 223     | default_egress_port_1  |                 | Specifies which of the egress ports $(0-3)$ is the default port for those packets that came through ingress port 1. This default port is used whenever software requests to transmit a packet that resides in the packet buffer with an encoded egress port o $0x1$ .                                                                                                                                                                                                                                                                                                                    |

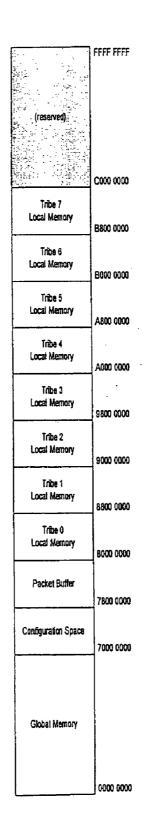

### Fig. 4a - Partial List of Config. Registers

| 224 default_egress_port_2 Specifies which of the egress ports (0-3)<br>default port for those packets that came to<br>ingress port 2. This default port is used to<br>software requests to transmit a packet the<br>in the packet buffer with an encoded egr<br>0x1. | through<br>whenever |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| ingress port 2. This default port is used we software requests to transmit a packet the in the packet buffer with an encoded egree ox 1.                                                                                                                             | whenever            |

| software requests to transmit a packet the<br>in the packet buffer with an encoded egr<br>0x1.                                                                                                                                                                       |                     |

| in the packet buffer with an encoded egr<br>0x1.                                                                                                                                                                                                                     | at resides          |

| 0x1.                                                                                                                                                                                                                                                                 |                     |

|                                                                                                                                                                                                                                                                      | ess port of         |

|                                                                                                                                                                                                                                                                      |                     |

| 225 default_egress_port_3 Specifies which of the egress ports (0-3)                                                                                                                                                                                                  | is the              |

| default port for those packets that came                                                                                                                                                                                                                             | through             |

| ingress port 3. This default port is used w                                                                                                                                                                                                                          | whenever            |

| software requests to transmit a packet th                                                                                                                                                                                                                            |                     |

| in the packet buffer with an encoded egr                                                                                                                                                                                                                             |                     |

|                                                                                                                                                                                                                                                                      |                     |

| 256 max_packet_size Specifies the maximum packet size allow                                                                                                                                                                                                          | wed by the          |

| NET module. The maximum packet size                                                                                                                                                                                                                                  |                     |

| is 64KB. The smallest the maximum part                                                                                                                                                                                                                               |                     |

| allowed, the less memory fragmentation                                                                                                                                                                                                                               | will occur          |

| at the packet buffer memory. The possib                                                                                                                                                                                                                              |                     |

| are from 0x0 (corresponding to a maxim                                                                                                                                                                                                                               |                     |

| of 1024 bytes) to 0xFF (corresponding to                                                                                                                                                                                                                             |                     |

| bytes), with all the intermediate sizes in                                                                                                                                                                                                                           |                     |

|                                                                                                                                                                                                                                                                      |                     |

| increments of 1024 bytes.                                                                                                                                                                                                                                            |                     |

| 257 default_egress_channel Specifies which of the 256 (0255) is th                                                                                                                                                                                                   |                     |

| default channel. This default channel is                                                                                                                                                                                                                             |                     |

| whenever software requests to transmit                                                                                                                                                                                                                               |                     |

| that resides in the packet buffer with an                                                                                                                                                                                                                            | encoded             |

| egress channel of 0x1.                                                                                                                                                                                                                                               |                     |

| 258 done Software writes in this register a value of                                                                                                                                                                                                                 |                     |

| the sequence number, the header growth                                                                                                                                                                                                                               |                     |

| the encoded egress channel to report that                                                                                                                                                                                                                            |                     |

| packet has been completed and it is read                                                                                                                                                                                                                             | ly lor              |

| transmission.                                                                                                                                                                                                                                                        | -11                 |

| When the write occurs, the NET module                                                                                                                                                                                                                                |                     |

| update the status of the packet and it wi                                                                                                                                                                                                                            |                     |

| as soon as it becomes the oldest packet                                                                                                                                                                                                                              | in the              |

| packet buffer.                                                                                                                                                                                                                                                       |                     |

| 259 drop Software writes in this register a value of                                                                                                                                                                                                                 |                     |

| the sequence number to report that the p                                                                                                                                                                                                                             |                     |

| longer valid and its data in the packet by                                                                                                                                                                                                                           | utter can           |

| be reused for another new packet.                                                                                                                                                                                                                                    | 1                   |

| When the write occurs, the NET modul                                                                                                                                                                                                                                 | e will              |

| update the status of the packet                                                                                                                                                                                                                                      |                     |

| 260 head_growth_offset Specifies the amount of space (in bytes)                                                                                                                                                                                                      |                     |

| NET will leave in front of each packet v                                                                                                                                                                                                                             | when                |

| stored in the packet buffer.                                                                                                                                                                                                                                         |                     |

| The lower 3 bits of this register are disr                                                                                                                                                                                                                           |                     |

| (they are considered to be always 0). The                                                                                                                                                                                                                            |                     |

| software can only specify growth offset                                                                                                                                                                                                                              | is that are a       |

| multiple of 8 bytes.                                                                                                                                                                                                                                                 |                     |

| 261-262 reserved                                                                                                                                                                                                                                                     |                     |

| 263 packet table packets Contains the total number of packets in                                                                                                                                                                                                     |                     |

|                                                                                                                                                                                                                                                                      |                     |

| (it may account for invalid packets or p                                                                                                                                                                                                                             |                     |

| still have not been transmitted) and the                                                                                                                                                                                                                             |                     |

|                                                                                                                                                                                                                                                                      |                     |

Fig. 4b - Partial List of Config. Registers

| 264269  | reserved               |                                                                                                                                                                                                                          |

|---------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

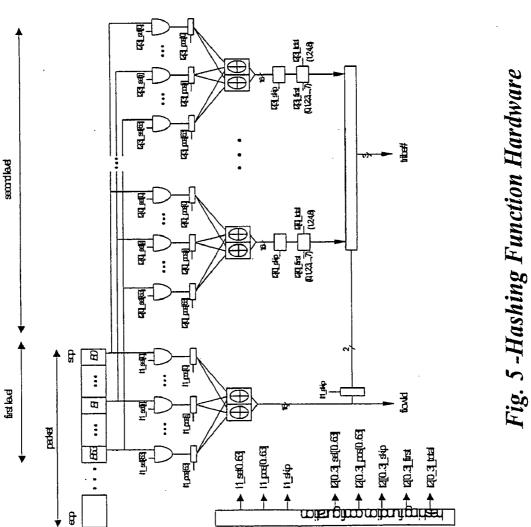

| 270     | l1_selection           | Specifies, for each of the first 64 bytes of the packet, whether the byte will be used for the hashing computation (bit 0:byte0 bit63:byte63) of the first-level hashing engine.                                         |

| 271-277 | reserved               |                                                                                                                                                                                                                          |

| 278     | [1_position            | Specifies, for each of the first 64-bytes of the<br>packet, whether the byte will be used in the MSB<br>(1) or LSB (0) 8-bits of the hashing result. It is<br>validated with the 11_selection configuration<br>register. |

| 279-285 | · reserved             |                                                                                                                                                                                                                          |

| 286-289 | 12_selection[03]       | Equivalent to l1_selection but for each of the second-level hashing engines.                                                                                                                                             |

| 290-301 | reserved               |                                                                                                                                                                                                                          |

| 302-309 | l2_position[03]        | Equivalent to 11_position but for each of the second-level hashing engines.                                                                                                                                              |

| 310-TBD | reserved               |                                                                                                                                                                                                                          |

| 318     | L1_skip                | Specifies how many LSB bits of the first-level<br>hashing result will be disregarded when<br>computing the selected second-level hashing<br>engine.                                                                      |

| 319-322 | 12_skip[03]            | Specifies how many LSB bits of each of the second-level hashing results will be disregarded when computing the selected tribe for initial migration.                                                                     |

| 323-334 | reserved               |                                                                                                                                                                                                                          |

| 335-338 | 12_first[03]           | Specifies, for each of the second-level hashing<br>engines, the first tribe of the set of tribes that will<br>be candidates for initial migration (0: tribe 0,,<br>7:tribe 7).                                           |

| 339-350 | reserved               |                                                                                                                                                                                                                          |

| 351-354 | 12_total[03]           | Specifies, for each of the second-level hashing<br>engines, the total amount of tribes that will be<br>candidates for initial migration (0:1 tribe, 1:2<br>tribes, 3:8 tribes).                                          |

| 355-366 | reserved               |                                                                                                                                                                                                                          |

| 367-374 | perf_counter_event[07] | Each one specifies one 64 events that can be<br>monitored in the NET module. Thus, a total of 8<br>events can be monitored simultaneously.                                                                               |

| 375-382 | reserved               |                                                                                                                                                                                                                          |

| 383-390 | perf_counter_value[07] | Contain the value of the performance events monitored.                                                                                                                                                                   |

| 400     | islot_enable           | Enables/disables each of the different egress interleaving slots. Bit 0-3 corresponds to islot0-3.                                                                                                                       |

| 401     | islot0_channels        | Specifies the range of channels associated to<br>islot0. The smallest channel number is specified in<br>bits 0-7 and the largest channel number in bits 16-<br>23.                                                       |

| 402     | islot1_channels        | Specifies the range of channels associated to<br>islot1. The smallest channel number is specified in<br>bits 0-7 and the largest channel number in bits 16-<br>23.                                                       |

Fig. 4c - Partial List of Config. Registers

| 403        | islot2_channels | Specifies the range of channels associated to islot2. The smallest channel number is specified in bits 0-7 and the largest channel number in bits 16-23.                       |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 404        | islot3_channels | Specifies the range of channels associated to islot3. The smallest channel number is specified in bits 0-7 and the largest channel number in bits 16-23.                       |

| 405-1023   | reserved        |                                                                                                                                                                                |

| 1024-2047  | Packet table    | Information of the 512 packet descriptors (two configuration registers per packet). The packet table is read only.                                                             |

| 2048-8191  | reserved        |                                                                                                                                                                                |

| 8192-16383 | GetRoom         | Software adds the base of this space to the<br>requested size in bytes to obtain the address to<br>access this space for a GetRoom command. The<br>GetRoom space is read only. |

### Fig. 4d - Partial List of Config. Registers

semtlad

8

| #      | Description                                                                                                |

|--------|------------------------------------------------------------------------------------------------------------|

| 0-3    | Number of packets dropped due to interleaving protocol violation, per ingress port.                        |

| 4-7    | Number of bytes received per ingress port.                                                                 |

| 8-11   | Number of packets dropped due to an error notification.                                                    |

| 12-15  | Number of chunks of data (1-8 bytes) transmitted out per egress port.                                      |

| 16-19  | Number of times an egress port is ready to accept data from the NET module (per egress                     |

|        | port).                                                                                                     |

| 20-23  | Number of times an egress port is ready to accept data from the NET module, but the NET                    |

|        | module has no data to provide (per egress port).                                                           |

| 24-31  | reserved                                                                                                   |

| 32     | Number of packets dropped due to packet table being full.                                                  |

| 33     | Number of chunks of data (1-8 bytes) dropped due to packet table being full, maximum                       |

|        | packet size violation or packet buffer being full.                                                         |

| 34     | Number of packets dropped due to maximum packet size violation.                                            |

| 35     | Number of packets dropped due to 'continue' configuration register being 0.                                |

| 36     | Number of packets dropped due to packet buffer being full.                                                 |

| 37     | Number of accesses to the packet table due to new packet insertions.                                       |

| 38     | Number of accesses to the packet table due to migrations.                                                  |

| 39     | Number of accesses to the packet table due to migrations that do not get served right away                 |

|        | (an access that does not get served for several cycles will generate as many events).                      |

| 40     | Number of accesses to the packet table due to packet transmissions.                                        |

| 41     | Number of accesses to the packet table due to transmissions that do not get served right                   |

|        | away (an access that does not get served for several cycles will generate as many events).                 |

| 42     | Number of accesses to the packet table due to packet control updates.                                      |

| 43     | Number of accesses to the packet table due to packet control updates that do not get served                |

|        | right away (an access that does not get served for several cycles will generate as many                    |

|        | events).                                                                                                   |

| 44-63  | reserved                                                                                                   |

| 64-71  | Number of accesses to bank / (bank 0:event 32 bank 7:event 39) of the packet buffer.                       |

| 71-78  | Number of accesses to the packet buffer performed by tribe $j$ (tribe 0:event 40 tribe 7:event 47).        |

| 79-86  | Number of accesses to the packet buffer performed by tribe $j$ (tribe0: event                              |

|        | 48tribe7:event 55) that do not get served right away (an access that does not get served                   |

|        | for several cycles will generate as many events).                                                          |

| 87     | Number of accesses to the packet buffer due to packet transmissions.                                       |

| 88     | Number of accesses to the packet buffer due to packet transmissions that do not get served                 |

|        | right away (an access that does not get served right away for several cycles will generate as              |

|        | many events).                                                                                              |

| 89     | Number of accesses to the packet buffer from non-DMA global. (TBD)                                         |

| 90     | Number of accesses to the packet buffer from non-DMA global that do not get served right                   |

|        | away (an access that does not get served right away for several cycles will generate as                    |

| 01     | many events). (TBD)                                                                                        |

| 91     | Number of accesses to the packet buffer from DMA global (TBD)                                              |

| 92     | Number of accesses to the packet buffer from DMA global that do not get served right                       |

|        | away (an access that does not get served right away for several cycles will generate as                    |

| 02     | many events). (TBD)         Number of accesses to the configuration registers, including the packet table. |

| 93     |                                                                                                            |

| 94-127 | reserved                                                                                                   |

Fig. 6 - Performance Events

| Encoded eg | ress channel | Actual egress channel                               |

|------------|--------------|-----------------------------------------------------|

| Bit 8      | Bits 7-0     | Bits 7-0                                            |

| 0          | 0            | Same as ingress channel                             |

|            | 1            | Contents of 'default egress channel' conf. register |

|            | 2255         | reserved                                            |

| 1          | 0255         | 0255                                                |

# Fig. 7 - Egress Channel Determination

| Encoded e | egress port | Actual egress port                                                                           |

|-----------|-------------|----------------------------------------------------------------------------------------------|

| Bit 5     | Bits 4-0    | Bits 4–0                                                                                     |

| 0         | 0           | Same as ingress port                                                                         |

|           | 1           | Contents of 'default_egress_port_X' conf. Register,<br>where X=03 is the ingress port number |

|           | 215         | reserved                                                                                     |

| 1         | 015         | 015 (415 reserved).                                                                          |

## Fig. 8 -Egress Port Determination

| Ports | Туре        |             |

|-------|-------------|-------------|

|       | Channelized |             |

|       |             | Non-        |

|       |             | channelized |

| I     | 1,2,3,4     | 1           |

| 2     | 1,2         | 1           |

| 4     | 1           | 1           |

# Fig. 9 - Allowed Interleaving Degree

.

Fig. 10

|                       |     |     |     |     |     |     | cycle |     |     |     |      |      |      |

|-----------------------|-----|-----|-----|-----|-----|-----|-------|-----|-----|-----|------|------|------|

| Migration<br>Function | ×   | x+1 | x+2 | x+3 | x+4 | x+5 | x+6   | x+7 | x+8 | x+9 | x+10 | x+11 | x+12 |

| makes request         | yes |     |     | yes |     |     |       |     | yes |     |      |      |      |

| retries request       |     | yes |     |     | yes | yes | yes   |     |     | yes |      |      |      |

| receives grant        |     |     | yes |     |     |     |       | yes |     |     | yes  |      |      |

| sends 'last'          |     |     | 0   | 1   | 0   |     |       | 0   | 1   | 0   | 0    | 1    | 0    |

| sends 'data'          |     |     | D1  | D2  | D3  |     |       | DI  | D2  | D3  | DI   | D2   | D3   |

| Interconnect          |     |     |     |     |     |     |       |     |     |     |      |      |      |

| receives request      |     | yes | yes |     | yes | yes | yes   | yes |     | yes | yes  |      |      |

| disregards request    |     |     |     |     |     |     |       | yes |     |     | yes  |      |      |

| grants request        |     | yes |     |     |     |     | yes   |     |     | yes |      |      |      |

| refuses request       |     |     | yes |     | yes | yes |       |     |     |     |      |      |      |

| receives 'last'       |     |     |     | 0   | 1   | 0   |       |     | 0   | 1   | 0    | 0    |      |

| receives 'data'       |     |     |     | DI  | D2  | D3  |       |     | DI  | D2  | D3   | DI   | D2   |

|                       |     |     |     |     |     |     |       |     |     |     |      |      |      |

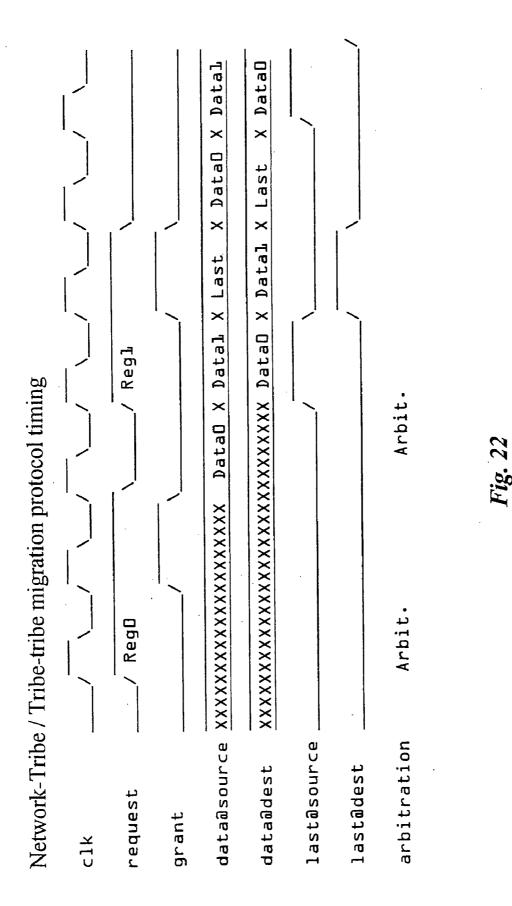

**Table D-1 - Migration Protocol**

Fig. 15

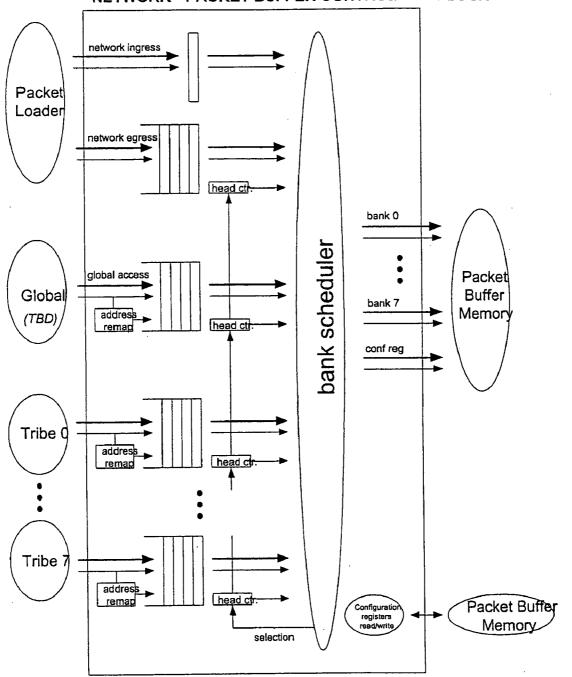

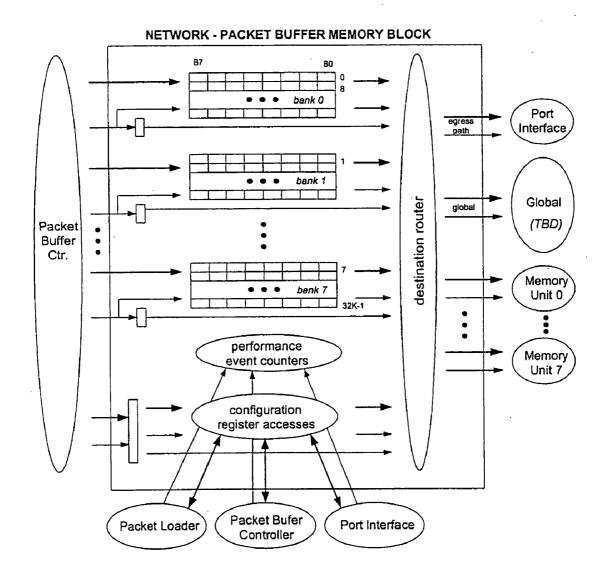

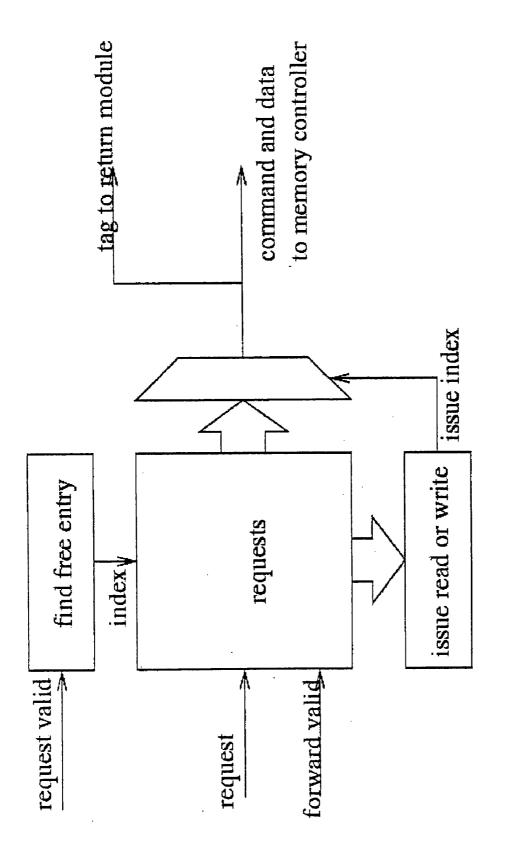

NETWORK - PACKET BUFFER CONTROLLER BLOCK

Fig. 18

| 5                                             |  |

|-----------------------------------------------|--|

| ) to                                          |  |

| ) m                                           |  |

| frc                                           |  |

| ging                                          |  |

| Interface to tribe # (ranging from 0 to $7$ ) |  |

| )#:                                           |  |

| ribe                                          |  |

| to t                                          |  |

| ace                                           |  |

| terf                                          |  |

| E                                             |  |

| Description | uest_#[7:0] Request migration to tribes (one-hot) | nt valid # Request granted | nt_tribe_#[2:0] Request granted for migration from tribe # to tribe[2:0] | valid # Migrating into tribe | data_#[63:0] Data migrating into tribe | last # Last data migrated in | [ #[1:0] Code to indicate how full the tribe is | valid # Migrating out of tribe | TI migrate out data #[63:0] Data migrating out of tribe | last # Last data migrated out | vap_valid_# Indicates transient swapping (deadlock resolution) |

|-------------|---------------------------------------------------|----------------------------|--------------------------------------------------------------------------|------------------------------|----------------------------------------|------------------------------|-------------------------------------------------|--------------------------------|---------------------------------------------------------|-------------------------------|----------------------------------------------------------------|

| Name        | TI_migrate_request_#[7:0]                         | IT migrate grant valid #   | IT migrate grant tribe_#[2:0]                                            | IT migrate in valid #        | 3                                      | IT migrate in last #         | TI migrate full #[1:0]                          | TI migrate out valid #         | TI migrate out data #[63:0]I                            | TI migrate out last #         | IT_transient_swap_valid_#                                      |

Interface to network block

| Name                    | Description                              |   |

|-------------------------|------------------------------------------|---|

| NI_migrate_request[7:0] | Request migration from network to tribes | , |

| IN_migrate_grant_valid  | Request granted                          |   |

| NI migrate_out_valid    | Migrating out of network                 |   |

| NI_migrate_out_data     | Data migrating out of network            |   |

| NI migrate out last     | Last data migrated out                   |   |

| .<br> -<br>             |                                          |   |

Fig. 20

Interface to global block

| Description | External hardware interrupts | Interconnect request age threshold | Select event count for performance counters | Event count         |  |

|-------------|------------------------------|------------------------------------|---------------------------------------------|---------------------|--|

| Name        | GI external interrupt [7:0]  | GI interconnect age limit[2:0]     | GI event count selection[2:0]               | IG_event_count[7:0] |  |

| Description | Valid bit for request | Address of memory request | Request type         | Size of request      | Stream number of request | Register destination (data read) | Data for write request | Valid return    | Low three bits of address | Return type         | Size of return      | Stream number of return | Register destination (data read) | Data return          | Tribe memory request queue full | Global request queue full |   |

|-------------|-----------------------|---------------------------|----------------------|----------------------|--------------------------|----------------------------------|------------------------|-----------------|---------------------------|---------------------|---------------------|-------------------------|----------------------------------|----------------------|---------------------------------|---------------------------|---|

| Name        | TM request valid      | TM request addr[31:0]     | TM_request_type[2:0] | TM_request_size[2:0] | TM request_stream[4:0]   | TM request regdest[4:0]          | TM request data[63:0]  | MT return valid | MT_return_addr_low[2:0]   | MT_return_type[2:0] | MT_return_size[2:0] | MT return stream[4:0]   | MT_return_regdest[4:0]           | MT return data[63:0] | MT_int_request_queue_full       | MT_ext_request_queue_full | - |

Interface to Tribe:

.

| Name<br>GM transaction_valid<br>GM transaction_addr[31:0]<br>GM transaction_addr[31:0]<br>GM transaction_size[2:0]<br>GM transaction_stream[4:0]<br>GM transaction_tribe[2:0]<br>GM transaction_tribe[2:0]<br>GM transaction_data[63:0]<br>GM rsp_transaction_full<br>MG transaction_addr[22:0]<br>MG transaction_stream[4:0]<br>MG transaction_stream[4:0]<br>MG transaction_stream[4:0] | Description<br>Valid transaction<br>Valid transaction<br>Address of memory transaction<br>Transaction type<br>Size of transaction<br>Stream number of transaction<br>Stream number of transaction<br>Register destination<br>Data for transaction<br>Request transaction<br>Request transaction<br>Response transaction<br>Queue full<br>Response transaction<br>Queue full<br>Response transaction<br>Response transaction<br>Respo |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MG_transaction_tribe[2:0]                                                                                                                                                                                                                                                                                                                                                                 | Source tribe which makes the transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MG_transaction_regdest[4:0]                                                                                                                                                                                                                                                                                                                                                               | Register destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MG_transaction_data[63:0]                                                                                                                                                                                                                                                                                                                                                                 | Data for transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MG_req_transaction_full                                                                                                                                                                                                                                                                                                                                                                   | Request transaction queue full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MG_rsp_transaction_full                                                                                                                                                                                                                                                                                                                                                                   | Global Response transaction queue full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GM_initialize_controller                                                                                                                                                                                                                                                                                                                                                                  | Initialize memory controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GM_event_count_selection[2:0]                                                                                                                                                                                                                                                                                                                                                             | Select event count for performance counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MG_event_count[7:0]                                                                                                                                                                                                                                                                                                                                                                       | Event count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Interface to Global:

| Name                                           | Description                             |

|------------------------------------------------|-----------------------------------------|

| ML address[27:0]                               | Address for memory transaction          |

| ML_length[5:0]                                 | Length of memory transaction            |

| ML_datain[63:0]                                | Write data                              |

| ML datain mask[1:0]                            | Mask for write data                     |

| ML_datain_valid                                | W rite data valid                       |

| LM <sup>_</sup> datain <sup>_</sup> queue full | W rite data queue full                  |

| ML command valid                               | Memory command valid                    |

| ML_command_type                                | Memory command type                     |

| LM command queue full                          | Memory command q full                   |

| LM dataout[63:0]                               | Data return from memory                 |

| LM dataout available                           | Data return valid                       |

| ML dataout accept                              | Ready to accept data return             |

| ML <sup>-</sup> initialize                     | Initialize DRAMs after powerup sequence |

| ML <sup>regin[15:0]</sup>                      | Register value                          |

| ML reg addr[5:0]                               | Register address                        |

| ML reg write                                   | Register write                          |

Interface to Tribe Memory Controller:

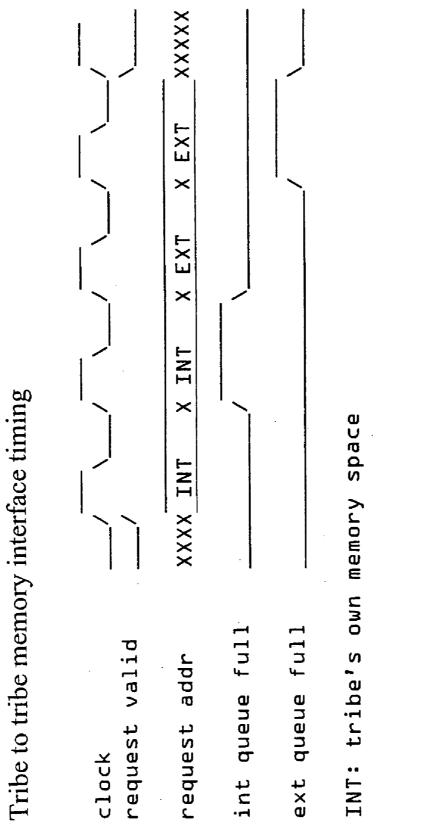

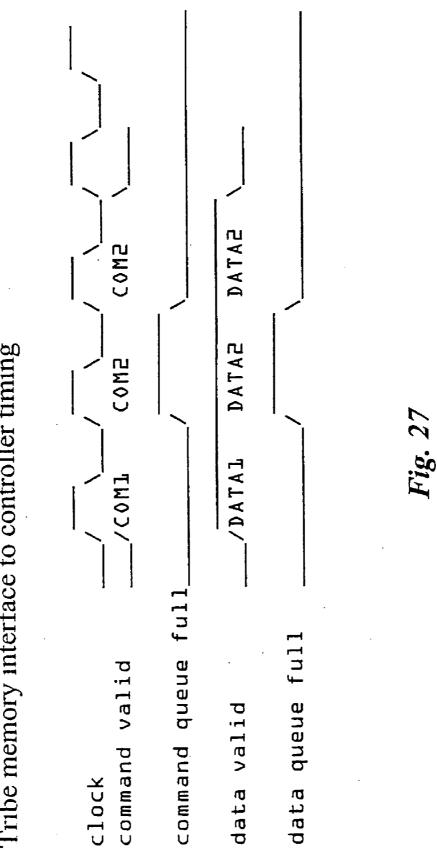

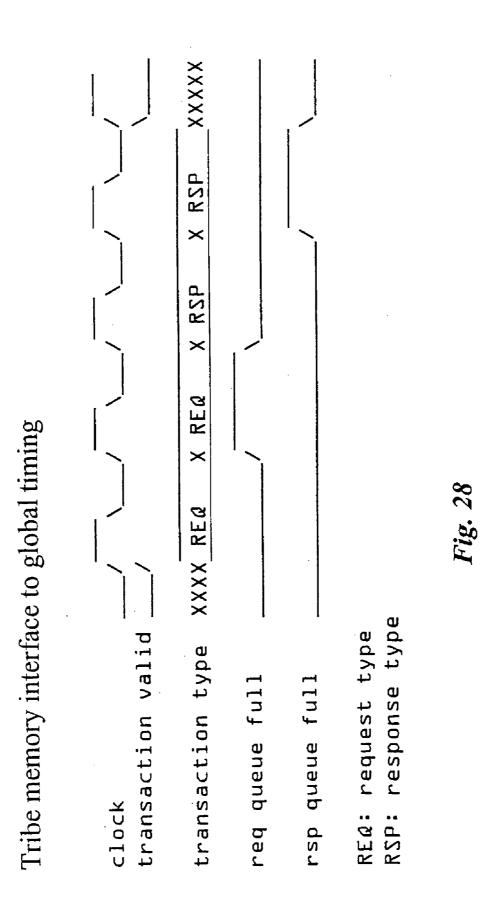

Tribe memory interface to controller timing

Patent Application Publication Nov. 3, 2005 Sheet 31 of 52

| Name                       | From To   | To    | Description                        |

|----------------------------|-----------|-------|------------------------------------|

| bool request valid         | Tribe Mem | Mem   | valid bit for request              |

| sc uint<32> request_addr   | Tribe     | Mem   | 32-bit address of memory request   |

| sc_uint<3> request_type    | Tribe     | Mem   | request type                       |

| sc uint<3> request size    | Tribe     | Mem   | size of request                    |

| sc_uint<5> request_stream  | Tribe     | Mem   | stream number of request           |

| sc_uint<5> request_regdest | Tribe     | Mem   | register destination (read)        |

| sc uint<64> request data   | Tribe     | Mem   | data for request (write)           |

| bool return valid          | Mem       | Tribe | valid bit for packet memory return |

| sc uint<3> return addr_low | Mem       | Tribe | low three bits of address          |

| sc uint<3> return type     | Mem       | Tribe | return type                        |

| sc_uint<3> return_size     | Mem       | Tribe | size of return                     |

| sc_uint<5> return_stream   | Mem       | Tribe | stream number of return            |

| sc_uint<5 > return_regdest | Mem       | Tribe | register destination               |

| sc_uint<64> return_data    | Mem       | Tribe | data for return                    |

| •                          |           |       |                                    |

Interface to Memory Block

|                               | Ļ         | Ē     |                                    |

|-------------------------------|-----------|-------|------------------------------------|

| Name                          | From 10   | 10    | Description                        |

| bool pb request valid         | Tribe Net | Net   | valid bit for request              |

| sc uint<32> pb request_addr   | Tribe Net | Net   | 32-bit address of memory request   |

| sc_uint<3> pb_request_type    |           | Net   | request type                       |

| sc uint<3> pb request size    |           | Net   | size of request                    |

| sc uint<5> pb request stream  |           | Net   | stream number of request           |

| sc_uint<5> pb_request_regdest |           | Net   | register destination (read)        |

| sc uint<64> pb request data   | Tribe     | Net   | data for request (write)           |

| bool pb return valid          | Net       | Tribe | valid bit for packet memory return |

| sc uint<3> pb return addr low | Net       | Tribe | low three bits of address          |

| sc uint<3> pb return type     | Net       | Tribe | return type                        |

| sc uint<3> pb return size     | Net       | Tribe | size of return                     |

| sc_uint<5> pb_return_stream   | Net       | Tribe | stream number of return            |