## (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 2 October 2008 (02.10.2008)

CT (10) International Publication Number WO 2008/118489 A1

- (51) International Patent Classification: *H01L 29/00* (2006.01)

- (21) International Application Number:

PCT/US2008/004032

- (22) International Filing Date: 27 March 2008 (27.03.2008)

- (25) Filing Language: English

- (26) Publication Language: English

- (30) Priority Data:

11/729,311

27 March 2007 (27.03.2007) US

- (71) Applicant (for all designated States except US): ALPHA & OMEGA SEMICONDUCTOR LIMITED; Canon's Court 22 Victoria St., Hamilton, HM12 (BM).

- (71) Applicants and

- (72) Inventors: HEBERT, Francois [CA/US]; 18 Melrose Ct., San Mateo, CA 94402 (US). SUN, Ming [—/US]; 927c La Mesa Terrace, Sunnyvale, CA 94088 (US).

- (74) Agent: MACKENZIE, Douglas, E.; Schein & Cai Llp, 100 Century Center Ct., Suite 315, San Jose, CA 95112 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

- (54) Title: CHIP SCALE POWER CONVERTER PACKAGE HAVING AN INDUCTOR SUBSTRATE

Fig. 5

(57) Abstract: A chip scale power converter package having an inductor substrate and a power integrated circuit flipped onto the inductor substrate is disclosed. The inductor substrate includes a high resistivity substrate having a planar spiral inductor formed thereon.

## CHIP SCALE POWER CONVERTER PACKAGE HAVING AN INDUCTOR SUBSTRATE

### BACKGROUND OF THE INVENTION

### 1. Field of the Invention

[0001] The present invention generally relates to chip scale packaging and more particularly to a chip scale power converter package having an inductor substrate.

## 2. Description of Related Art

[0002] It is well known to include a discrete inductor on the printed circuit board when implementing a power converter circuit. For example, the Analogic™TECH 1 MHz 400mA Step-Down Converter (AAT1143) requires the use of a discreet inductor. Power converters implemented in this way suffer the disadvantages of having higher component cost and of requiring more printed circuit board space.

[0003] Discrete inductors co-packaged with power ICs and other components are also well known. For example, the LTM®4600 DC/DC power converter available from Linear Technology Corporation of Milpitas, CA, includes a built-in inductor in a 15mm x 15mm x 2.8mm package. The package disadvantageously uses valuable printed circuit board space.

It is further known to dispose an inductor on top of an integrated circuit die such as a power converter integrated circuit die. For example, power converters available from Enpirion of Bridgewater, NJ, include a MEMS-based inductor having a thick electroplated copper spiral coil sandwiched between two planar magnetic layers and disposed over an integrated DC-DC converter. To achieve high inductance, a large die is required resulting in a high cost and a large package. Furthermore, complex processing is necessary in order to fabricate the planar magnetic layers.

[0005] There is therefore a need in the art for a chip scale power converter that overcomes the disadvantages of the prior art. There is a need for a low cost chip scale

power converter that does not require an external inductor. There is a further need for a chip scale power converter having an optimized interconnection between the power IC and the inductor for minimized parasitics, improved performance and high reliability.

## SUMMARY OF THE INVENTION

[0006] The chip scale power converter in accordance with the invention combines an inductor with the chip scale package to improve efficiency of assembly. An inductor substrate is provided that includes an optimized planar spiral inductor. A power IC is flipped onto the inductor substrate to form the chip scale power converter.

[0007] In accordance with one aspect of the invention, a power converter package includes an inductor substrate and a power integrated circuit bonded onto the inductor substrate.

[0008] In accordance with another aspect of the invention, a chip scale inductor substrate includes a high resistivity substrate, and a planar spiral inductor formed on the substrate.

[0009] In accordance with another aspect of the invention, a method of fabricating a chip scale power converter package includes the steps of providing a substrate, fabricating a plurality of planar spiral inductors on the substrate to form a plurality of inductor substrates, bonding an integrated circuit onto each inductor substrate, and dicing the plurality of inductor substrates.

[0010] There has been outlined, rather broadly, the more important features of the invention in order that the detailed description thereof that follows may be better understood, and in order that the present contribution to the art may be better appreciated. There are, of course, additional features of the invention that will be described below and which will form the subject matter of the claims appended herein.

In this respect, before explaining at least one embodiment of the invention in detail, it is to be understood that the invention is not limited in its application to the details of functional components and to the arrangements of these components set forth in the following description or illustrated in the drawings. The invention is capable of other embodiments and of being practiced and carried out in various ways. Also, it is to be understood that the phraseology and terminology employed herein, as well as the abstract, are for the purpose of description and should not be regarded as limiting.

[0012] As such, those skilled in the art will appreciate that the conception upon which this disclosure is based may readily be utilized as a basis for the designing of

other methods and systems for carrying out the several purposes of the present invention. It is important, therefore, that the claims be regarded as including such equivalent constructions insofar as they do not depart from the spirit and scope of the present invention.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0013] These and other aspects and features of the present invention will become apparent to those ordinarily skilled in the art upon review of the following description of specific embodiments of the invention in conjunction with the accompanying figures, wherein:

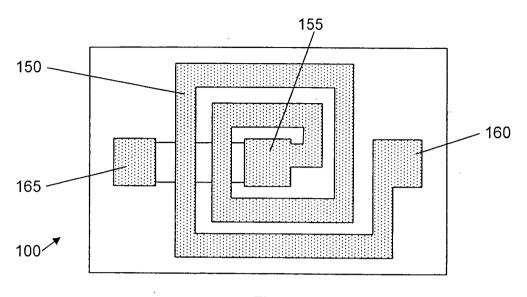

[0014] FIG. 1 is a top plan view of an inductor substrate in accordance with the invention;

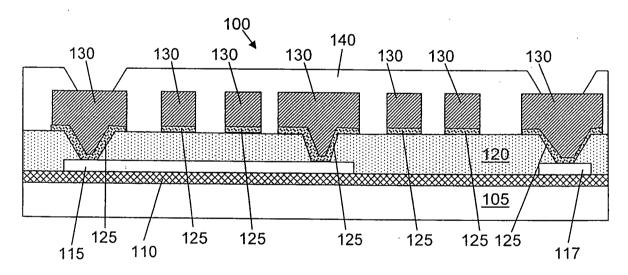

[0015] FIG. 2 is a cross sectional view of the inductor substrate of FIG. 1;

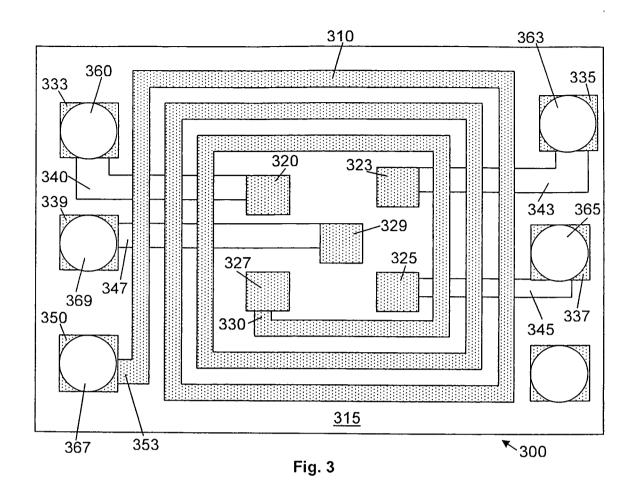

[0016] FIG. 3 is a top plan view of an alternative inductor substrate in accordance with the invention;

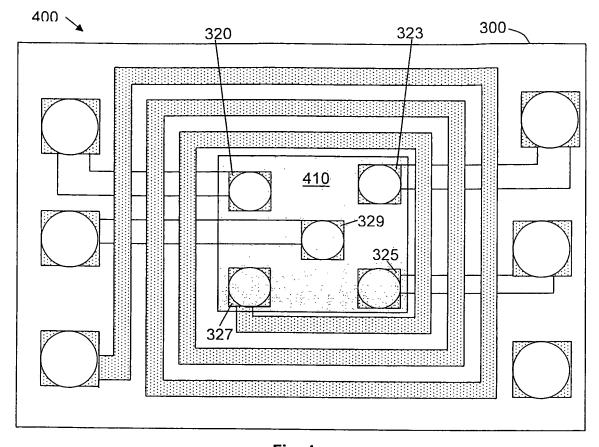

[0017] FIG. 4 is a top plan view of a chip scale power converter package showing a flip chip power IC in phantom in accordance with the invention;

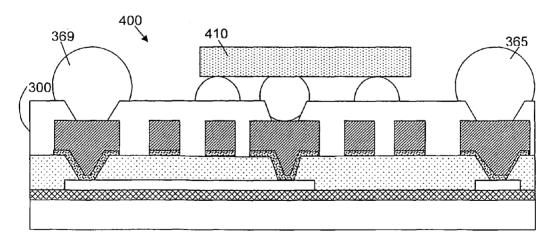

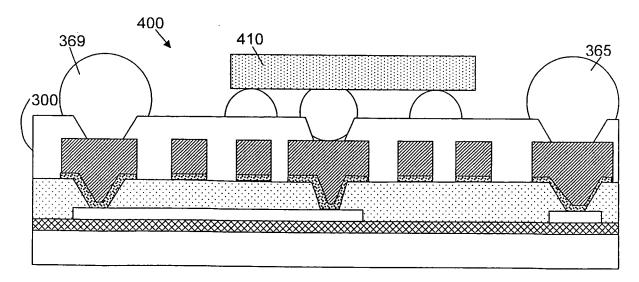

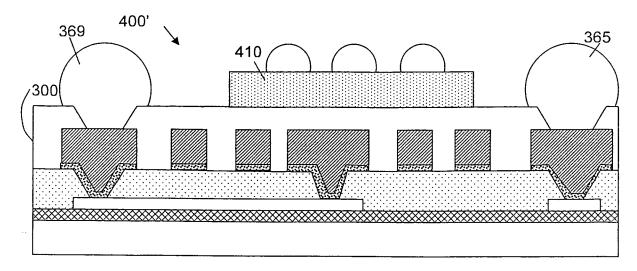

[0018] FIG. 5 and Fig. 5A are cross sectional views of chip scale power converter packages in accordance with the invention;

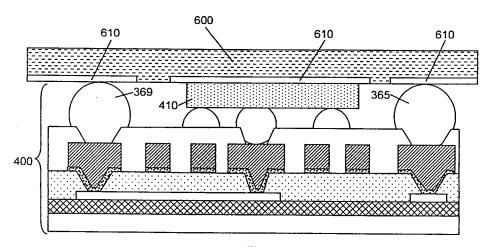

[0019] FIG. 6 is a cross sectional view of the chip scale power converter package of FIG. 4 mounted to a printed circuit board in accordance with the invention;

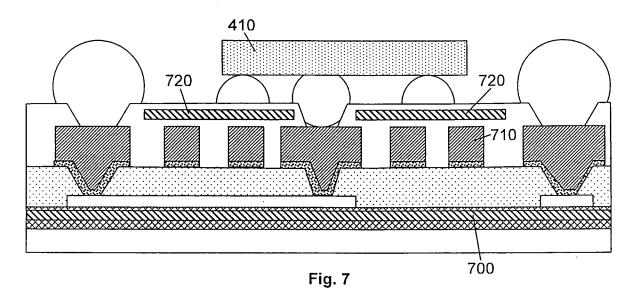

[0020] FIG. 7 is a cross sectional view of an alternative chip scale power converter package in accordance with the invention;

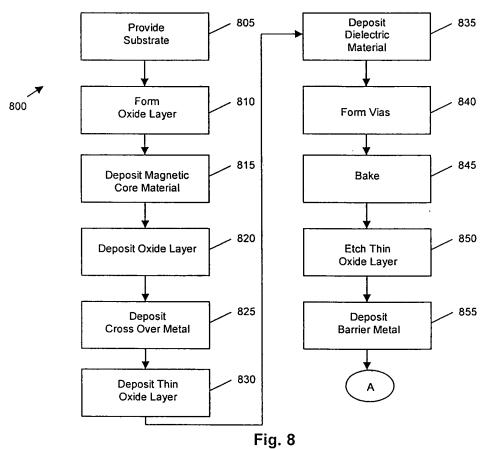

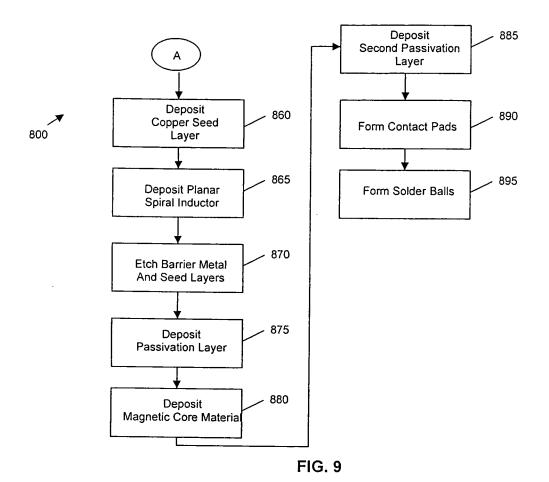

[0021] FIG. 8 and FIG. 9 are a flow chart showing a method in accordance with the invention;

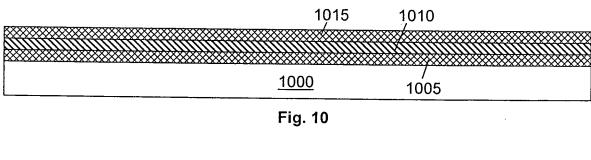

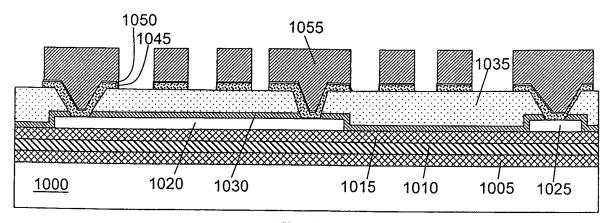

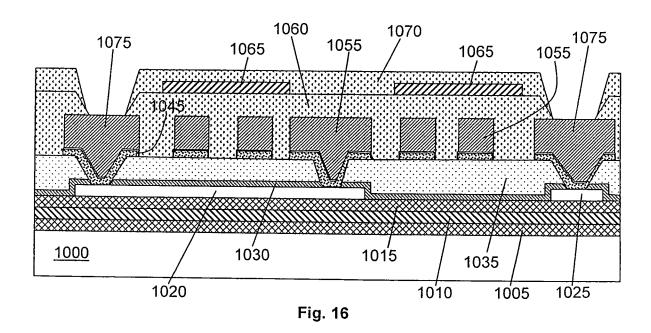

[0022] FIG. 10 through FIG. 16 shows an inductor substrate in various stages of fabrication in accordance with the invention;

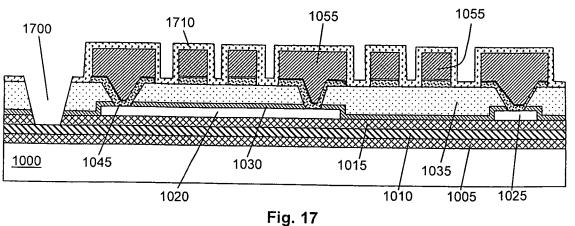

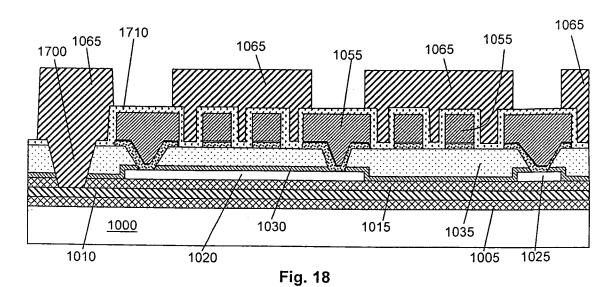

[0023] FIG. 17 and 18 show an alternative inductor substrate in various stages of fabrication in accordance with the invention; and

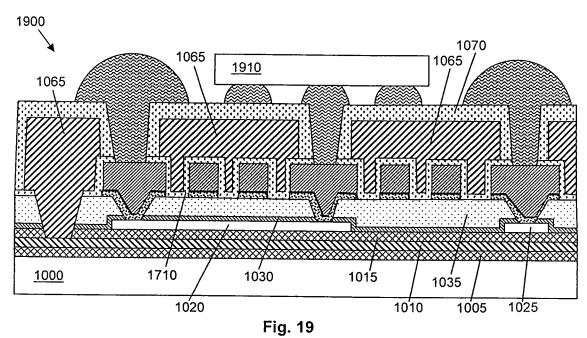

[0024] FIG. 19 is a cross sectional view of an alternative chip scale power converter package in accordance with the invention.

# DETAILED DESCRIPTION OF A PREFERRED EMBODIMENT OF THE INVENTION

The present invention will now be described in detail with reference to the drawings, which are provided as illustrative examples of the invention so as to enable those skilled in the art to practice the invention. Notably, the figures and examples below are not meant to limit the scope of the present invention. Where certain elements of the present invention can be partially or fully implemented using known components, only those portions of such known components that are necessary for an understanding of the present invention will be described, and detailed descriptions of other portions of such known components will be omitted so as not to obscure the invention. Further, the present invention encompasses present and future known equivalents to the components referred to herein by way of illustration.

[0026] The present invention provides a chip scale power converter having an inductor substrate. An exemplary inductor substrate 100 is shown in FIG. 1 and FIG. 2. Inductor substrate 100 includes a substrate 105 formed of a high resistivity material including silicon and glass, or a magnetic core material such as Ferrite or NiFe, or a mutil-layered structure of magnetic core material and oxide over silicon wafer or other substrate wafer. A planar spiral inductor 150 having a first end 155 and a second end 160 is formed on the substrate 105 as further detailed herein.

[0027] An oxide layer 110 is formed over the substrate 105. Optional cross over metal layers 115 and 117 are formed of metal or alloys including Cu, AlCu, and Cu/TiW over portions of the oxide layer 110. Cross over metal layer 115 provides contact to the planar spiral inductor first end 155 at peripheral contact 165.

[0028] An optional layer 120 of inter-metal dielectric material, preferably a low-K dielectric material including benzocyclobutene (BCB), polyimide and other organic materials such as SU-8 available from MicroChem of Newton, Massachusetts, is disposed over the oxide layer 110 and layers 115 and 117 to provide for low parasitic capacitance. Optional barrier metal layers 125 may be disposed between layers 115 and 117, and thick metal structures 130 defining the planar spiral inductor 150. The thick metal structures 130 may be formed of Cu or other thick and low resistivity metals

such as Au. A passivation layer 140 covers the planar spiral inductor 150 to complete the inductor substrate 100. Alternatively, optional cross over metal layers 115 and 117 may be formed over a passivation layer 140 to provide contact to the planar spiral inductor first end 155 at peripheral contact 165.

[0029] A preferred embodiment of an inductor substrate 300 is shown in FIG. 3. A planar spiral inductor 310 is disposed on a substrate 315 so as to maximize the inductance of the inductor 130. Contacts 320, 323, 325, 327 and 329 provide contacts for a flip-chip power IC controller/converter as further described herein. Contact 327 is electrically coupled to a first end 330 of the planar spiral inductor 310. Contacts 320, 323, 325, and 329 are coupled to contacts 333, 335, 337 and 339 respectively by means of cross over metal layers 340, 343, 345 and 347. Contact 350 is electrically coupled to a second end 353 of the planar spiral inductor 310. Solder bumps 360, 363, 365, 367, and 369 provide connectivity to contacts 333, 335, 337, 350, and 339 respectively.

[0030] With reference to FIG. 4, a chip scale power converter 400 is shown including a flip-chip power IC controller/converter 410 electrically coupled to the inductor substrate 300. The flip-chip power IC controller/converter 410 is shown in phantom to show connection to contacts 320, 323, 325 and 327. A cross sectional view of the chip scale power converter 400 is shown in FIG. 5. The chip scale power converter 400 is shown in FIG. 6 mounted to a printed circuit board 600 having traces 610. Alternatively, contacts 320, 323, 325, 327 and 329 are not provided and an IC chip 410 may be mounted on the inductor substrate 300 with contacts exposed to form a chip scale power converter 400' as shown in Fig. 5A. In case the IC chip 410 has contacts on both its surfaces, some contacts may be accessed directly from one surface of IC chip 410 and some contacts may be accessed from contacts on the inductor substrate through cross over metals. Furthermore, the solder bump contacts may be replaced by patterned metal contact pads so that the combined inductor substrate with the IC chip can be packed into traditional packages by wire bonding.

[0031] In alternative embodiments, a patterned magnetic core layer is formed under the planar spiral inductor in the substrate. Alternatively, a patterned magnetic core layer is formed above the planar spiral inductor. In yet other alternative

embodiments, patterned magnetic core layers are formed above and below the planar spiral inductor. In yet other alternative embodiments, multi-layered patterned magnetic core layers sandwiched by dialectical layers such as silicon oxides are formed above and /or below the planar inductor. Provision of patterned magnetic core layers increases the inductance per unit area of the spiral inductor and provides shielding of stray magnetic fields. With reference to FIG. 7, a patterned magnetic core layer 700 is shown formed under the planar spiral inductor 710 and a patterned magnetic core layer 720 is shown formed over the planar spiral inductor 710. The magnetic core layers 700 and 720 can be sputtered, evaporated, plated, bonded or co-packaged as a chip on the inductor substrate. Magnetic core layers 700 and 720 may be formed of materials with appropriate magnetic performance such as Ni, Co, ferrites, and combinations of these materials.

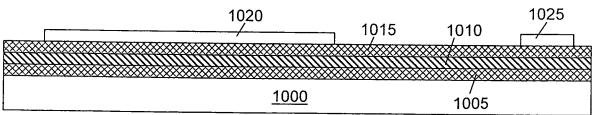

[0032] A method 800 (FIG. 8) of fabricating the inductor substrate in accordance with the invention includes providing a high resistivity substrate wafer 1000 (FIG. 10) in a step 805. The substrate 1000 is thermally oxidized to form an oxide layer 1005 in a step 810. In an optional step 815 a magnetic core material such as electroplated permalloy is deposited on the oxide layer 1005 to form a magnetic core layer 1010 and in a step 820, an oxide or dielectric layer 1015 is deposited on the magnetic core layer 1010.

[0033] In a optional step 825, cross over metal 1020 and 1025 (FIG. 11) is deposited onto oxide or dielectric layer 1015 such as by thick AlCu deposition (>1.5 microns), sputtered Cu/TiW, or plated Cu. Step 825 may include masking, stripping, and etching processes.

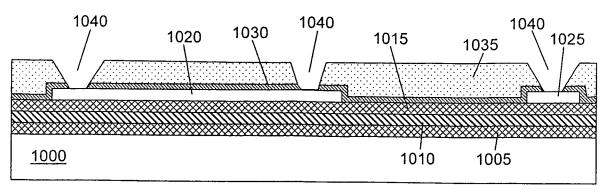

[0034] A thin oxide layer 1030 (FIG. 12) is next deposited to promote adhesion of a low-K inter-metal dielectric material including benzocyclobutene (BCB), polyimide or SU-8, in a step 830. In an optional step 835, the BCB 1035 is spun to a thickness of 10 to 20 microns. Vias 1040 are next formed in a step 840 including masking and developing the BCB or polyimide (in the case photodefined BCB or polyimide is used) or developing and etching the BCB (in the case non-photodefined BCB or polyimide is used). The structure is next baked in a step 845 and the thin oxide layer 1030 is etched in a step 850 using the BCB, polyimide or SU-8 layer as mask.

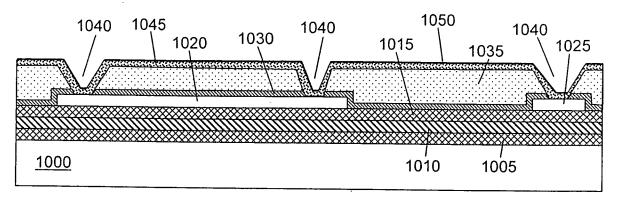

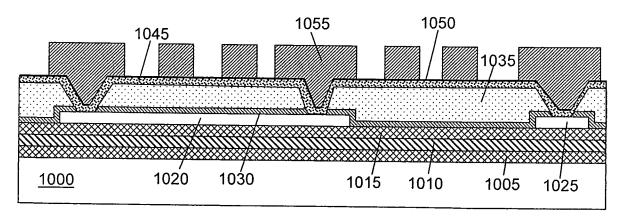

[0035] A barrier metal 1045 (FIG. 13) including TiW or TiN is next deposited in a step 855 and a copper seed layer 1050 deposited in a step 860 overlaying barrier metal layer 1045. In a step 865, a thick photoresist layer is patterned, copper is electroplated to a thickness of 17 microns or greater, and the photoresist stripped to form a planar spiral inductor 1055 (FIG. 14). Alternatively, the copper layer may be deposited over the whole substrate and then patterned and etched with a mask. A low resistivity metal like Gold (commonly used in RF and microwave power devices for example), can be used in place of Cu.

The barrier metal 1045 and the seed layer 1050 are next etched in a step 870 (FIG. 15). In a step 875, a passivation layer 1060 (FIG. 16) formed of BCB or polyimide is deposited. Magnetic core material is next deposited and patterned or plated in an optional step 880 to form magnetic core layer 1065. A second passivation layer 1070 is then deposited in a step 885. Contact pads 1075 are masked and etched in a step 890 and solder bumps (not shown) formed in a step 895. In another embodiment, a layer of metal is deposited and then patterned to form cross over metals (not shown) before solder bumps are formed in step 895. Following the process 800, an IC chip may be attached to the inductor substrate by a standard bonding process or by a flip-chip bonding process and the whole inductor substrate diced into individual packages.

[0037] In an alternative embodiment of the invention, a peripheral magnetic via 1700 to the magnetic core layer 1010 is formed following the step 875 in which a passivation layer 1710 (FIG. 17) is formed over the planar spiral inductor 1055. Magnetic core material is then deposited as a blanket layer and patterned or plated in the step 880 (FIG. 18) to form magnetic core layer 1065. Magnetic core material in via 1700 connects the magnetic core layer 1065 with the magnetic core layer 1010 to maximize the inductance of the spiral inductor 1055. An inductor substrate 1900 and mounted power IC flip chip 1910 is shown in FIG. 19. Maximum inductance is achieved by contact between the magnetic core layers but a separation on the order of a few microns is acceptable.

[0038] The chip scale power converter having an inductor substrate of the invention combines the inductor in the package to improve efficiency of assembly. The

inventive package does not integrate the inductor directly with the more costly power IC. By flipping the power IC onto the inductor substrate, optimized interconnection between the power IC and the inductor is provided to minimize parasitics, improve performance and achieve high reliability.

[0039] The chip scale power converter having an inductor substrate according to the invention is particularly suited for high frequency (>5 MHz) applications requiring lower inductance values. It is also suited for low current applications to leverage the planar spiral inductor. The inductor substrate of the invention is simple to fabricate at a low cost and maximizes the inductance while minimizing cost and space.

[0040] It is apparent that the above embodiments may be altered in many ways without departing from the scope of the invention. For example, the inductor substrate may be formed without the magnetic core materials and optional components including resistors and capacitors may be formed in the substrate. Additionally, high power MOSFET devices may be incorporated in the substrate. Further, various aspects of a particular embodiment may contain patentably subject matter without regard to other aspects of the same embodiment. Still further, various aspects of different embodiments can be combined together. Accordingly, the scope of the invention should be determined by the following claims and their legal equivalents.

#### What is claimed is:

- A power converter package comprising:

an inductor substrate; and

a power integrated circuit bonded onto the inductor substrate.

- 2. The converter according to claim 1, wherein the inductor substrate comprises a planar spiral inductor formed thereon.

- 3. The power converter according to claim 2, wherein the planar spiral inductor has a thickness greater than 17 microns.

- 4. The power converter according to claim 2, further comprising a magnetic core layer disposed under the planar spiral inductor.

- 5. The power converter according to claim 2, further comprising a magnetic core layer disposed over the planar spiral inductor.

- 6. The power converter according to claim 2, further comprising a first magnetic core layer disposed under the planar spiral inductor and a second magnetic core layer disposed over the planar spiral inductor, the first and second magnetic core layers being coupled by means of a magnetic core material via.

- 7. The power converter according to claim 2, wherein the power integrated circuit comprises a plurality of contacts coupled to a plurality of peripheral contacts on the inductor substrate by means of a cross over metal layer.

- 8. The power converter according to claim 2, wherein the power integrated circuit is flip chip bonded onto the inductor substrate.

- 9. A chip scale inductor substrate comprising:

a high resistivity substrate; and

a planar spiral inductor formed on the substrate.

10. The chip scale inductor substrate according to claim 9, wherein the planar spiral inductor has a thickness greater than 17 microns.

- 11. The chip scale inductor substrate according to claim 9, further comprising a plurality of magnetic core layers sandwiched by dielectric layers disposed under the planar spiral inductor.

- 12. The chip scale inductor substrate according to claim 11, further comprising a magnetic core layer disposed over the planar spiral inductor.

- 13. The chip scale inductor substrate according to claim 9, further comprising a first magnetic core layer disposed under the planar spiral inductor and a second magnetic core layer disposed over the planar spiral inductor, the first and second magnetic core layers being coupled by means of a magnetic core material via.

- 14. The chip scale inductor substrate according to claim 9, wherein the inductor substrate comprises a plurality of contacts in a center area of the inductor substrate coupled to a plurality of peripheral contacts on the inductor substrate by means of a cross over metal layer.

- 15. The chip scale inductor substrate according to claim 9, further comprising a low-K dielectric material disposed under the planar spiral inductor to reduce parasitic capacitance.

- 16. A method of fabricating a chip scale power converter package comprising the steps of:

providing a substrate;

fabricating a plurality of planar spiral inductors on the substrate to form a plurality of inductor substrates;

bonding an integrated circuit onto each inductor substrate; and dicing the plurality of inductor substrates.

- 17. The method according to claim 16, further comprising forming a first oxide layer on the high resistivity substrate before the fabrication step.

- 18. The method according to claim 17, further comprising depositing a first magnetic core material layer on the oxide layer before the fabrication step.

- 19. The method according to claim 18, further comprising depositing a second oxide layer on the magnetic core material layer before the fabrication step.

- 20. The method according to claim 19, further comprising depositing a cross over metal layer on the second oxide layer before the fabrication step.

- 21. The method according to claim 20, further comprising depositing a third oxide layer over the cross over metal layer before the fabrication step.

- 22. The method according to claim 21, further comprising depositing a dielectic material over the third oxide layer before the fabrication step.

- 23. The method according to claim 22, further comprising forming vias to the cross over metal layer before the fabrication step.

- 24. The method according to claim 23, further comprising etching exposed portions of the third oxide layer before the fabrication step.

25. The method according to claim 24, further comprising depositing a barrier metal layer on the dielectic material and exposed portions of the cross over metal layer before the fabrication step.

- 26. The method according to claim 25, further comprising depositing a seed layer on the barrier metal layer before the fabrication step.

- 27. The method according to claim 26, wherein the fabrication step comprises plating the plurality of planar spiral inductors.

- 28. The method according to claim 27, wherein the fabrication step comprises patterning the plurality of planar spiral inductors.

- 29. The method according to claim 28, further comprising etching exposed portions of the barrier metal and seed layers.

- 30. The method according to claim 29, further comprising depositing a first passivation layer.

- 31. The method according to claim 30, further comprising forming a peripheral via reaching the first magnetic core material layer.

- 32. The method according to claim 31, further comprising depositing a second magnetic core material layer.

- 33. The method according to claim 32, further comprising depositing a second passivation layer.

- 34. The method according to claim 33, further comprising forming contact pads in the vias.

35. The method according to claim 34, further comprising forming solder balls on the contact pads.

Fig. 1

Fig. 2

Fig. 4

Fig. 5

Fig. 5A

Fig. 6

Fig. 11

Fig. 12

Fig. 13

Fig. 14

Fig. 15

#### INTERNATIONAL SEARCH REPORT

International application No. PCT/US 08/04032

| <ul> <li>A. CLASSIFICATION C</li> </ul> | F SUBJECT MATTER |

|-----------------------------------------|------------------|

|-----------------------------------------|------------------|

IPC(8) - H01L 29/00 (2008.04) USPC - 257/E23.172

According to International Patent Classification (IPC) or to both national classification and IPC

#### FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols) IPC(8): H01L 29/00 (2008.04) USPC: 257/E23.172

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched USPC: 257/707; 257/691; 257/E23.169, search terms below:

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) PubWEST (USPT,PGPB,EPAB,JPAB); Google Scholar, Google search results on: power converter, inductor, substrate, integrated circuit, planar, spiral, parasitic capacitance, metal, oxide, etch and seed.

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| US 2006/0039224 A1 (Lofti et al.) 23 February 2006 (23.02.2006) entire document especially Abstract, para [0090], [0092]-[0093], [0095], [0097]-[0101], and [0104].  US 6,534,843 B2 (Acosta et al.) 18 March 2003 (18.03.2003) entire document especially col 5 In                                                                  | 1-7, 9-13<br><br>8, 14-35                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                      | 8, 14-35                                                                                                                                                                                                                                                                                                                                                       |

| US 6,534,843 B2 (Acosta et al.) 18 March 2003 (18.03.2003) entire document especially col 5 In                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                |

| 1-4.                                                                                                                                                                                                                                                                                                                                 | 15                                                                                                                                                                                                                                                                                                                                                             |

| US 2004/0100778 A1 (Vinciarell et al.) 27 May 2004 (27.05.2004) entire document especially paras [0008] and [0018].                                                                                                                                                                                                                  | 14, 34 and 35                                                                                                                                                                                                                                                                                                                                                  |

| X. Liu, "Development of Flip Chip on Flex Structure for Packaging Integrated Power Electronics Modules", April 2001 Chapter V1, p 217 [online], [retrieved on: 2008.06.18]. Retrieved from the internet: <url: available="" chapter-6.pdf="" etd-04082001-204805="" http:="" scholar.lib.vt.edu="" theses="" unrestricted=""></url:> | 8 and 16-35.                                                                                                                                                                                                                                                                                                                                                   |

| US 7,154,174 B2 (MAXWELL) 26 December 2006 (26.12.2006) entire document                                                                                                                                                                                                                                                              | 1-35                                                                                                                                                                                                                                                                                                                                                           |

| ·                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                      | paras [0008] and [0018].  X. Liu, "Development of Flip Chip on Flex Structure for Packaging Integrated Power Electronics Modules", April 2001 Chapter V1, p 217 [online], [retrieved on: 2008.06.18]. Retrieved from the internet: <url: available="" chapter-6.pdf="" etd-04082001-204805="" http:="" scholar.lib.vt.edu="" theses="" unrestricted=""></url:> |

|                                                           | Further documents are listed in the continuation of Box C.                                           |      |                                                                                                                                                                                  |  |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| *                                                         | Special categories of cited documents:                                                               | "T"  | later document published after the international filing date or priority                                                                                                         |  |

| "A"                                                       | document defining the general state of the art which is not considered to be of particular relevance | l    | date and not in conflict with the application but cited to understand<br>the principle or theory underlying the invention                                                        |  |

| "E"                                                       | earlier application or patent but published on or after the international filing date                | "X"  | considered novel or cannot be considered to involve an inventive                                                                                                                 |  |

| "L"                                                       | document which may throw doubts on priority claim(s) or which is                                     |      | step when the document is taken alone                                                                                                                                            |  |

| 1                                                         | cited to establish the publication date of another citation or other special reason (as specified)   | "Y"  | document of particular relevance, the claimed invention cambot be                                                                                                                |  |

| "O"                                                       | document referring to an oral disclosure, use, exhibition or other means                             | •    | considered to involve an inventive step when the document is<br>combined with one or more other such documents, such combination<br>being obvious to a person skilled in the art |  |

| "P"                                                       | document published prior to the international filing date but later than the priority date claimed   | "&"  | document member of the same patent family                                                                                                                                        |  |

| Date of the actual completion of the international search |                                                                                                      | Date | Date of mailing of the international search report                                                                                                                               |  |

| 15 June 2008 (15.06.2008)                                 |                                                                                                      |      | 01 AUG 2008                                                                                                                                                                      |  |

| Nan                                                       | ne and mailing address of the ISA/US                                                                 | A    | Authorized officer:                                                                                                                                                              |  |

| Mail Stop PCT, Attn: ISA/US, Commissioner for Patents     |                                                                                                      | ]    | Lee W. Young                                                                                                                                                                     |  |

| P.O. Box 1450, Alexandria, Virginia 22313-1450            |                                                                                                      | PCTH | PCT Helpdesk; 571-272-4300                                                                                                                                                       |  |

| Facs                                                      | imile No. 571-273-3201                                                                               |      | OSP: 571-272-7774                                                                                                                                                                |  |

Form PCT/ISA/210 (second sheet) (April 2007)