(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5348874号

(P5348874)

(45) 発行日 平成25年11月20日(2013.11.20)

(24) 登録日 平成25年8月30日(2013.8.30)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/786 (2006.01)H01L 29/78 621

H01L 29/78 617S

H01L 29/78 618C

H01L 29/78 617U

H01L 29/78 617V

請求項の数 6 (全 57 頁)

(21) 出願番号 特願2007-313006 (P2007-313006)

(22) 出願日 平成19年12月4日 (2007.12.4)

(65) 公開番号 特開2008-166744 (P2008-166744A)

(43) 公開日 平成20年7月17日 (2008.7.17)

審査請求日 平成22年11月22日 (2010.11.22)

(31) 優先権主張番号 特願2006-327921 (P2006-327921)

(32) 優先日 平成18年12月5日 (2006.12.5)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 池田 佳寿子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 笹川 慎也

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 須沢 英臣

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置及びその作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

支持基板上に第1の絶縁層及びシリコン層を有するSOI基板と、

前記シリコン層の表面と接する領域及び前記シリコン層の側面と接する領域を有するゲート絶縁層と、

前記ゲート絶縁層上方の、前記シリコン層を横断する領域を有する導電層と、を有し、

前記ゲート絶縁層は、

プラズマ処理により前記シリコン層の側面に形成された第2の絶縁層と、

前記第2の絶縁層と接する領域を有する第3の絶縁層と、

前記シリコン層と接する領域と、前記第2の絶縁層と接する領域と、前記第3の絶縁層と接する領域と、を有する第4の絶縁層と、を有し、

前記第3の絶縁層の誘電率は、前記第4の絶縁層の誘電率よりも小さく、

前記ゲート絶縁層のうち前記シリコン層の側面と接する領域の膜厚は、前記ゲート絶縁層のうち前記シリコン層の表面と接する領域の膜厚よりも大きく、

前記シリコン層の端部は、テーパー角が45°以上95°未満であることを特徴とする半導体装置。

## 【請求項 2】

支持基板上に第1の絶縁層及びシリコン層を有するSOI基板と、

プラズマ処理により前記シリコン層の側面に形成された第2の絶縁層と、

前記第2の絶縁層と接する領域を有する第3の絶縁層と、

10

20

前記シリコン層と接する領域と、前記第2の絶縁層と接する領域と、前記第3の絶縁層と接する領域と、を有する第4の絶縁層と、

前記第4の絶縁層上方の、前記シリコン層を横断する領域を有する導電層と、を有し、前記第3の絶縁層の誘電率は、前記第4の絶縁層の誘電率よりも小さいことを特徴とする半導体装置。

**【請求項3】**

請求項1又は2において、

前記第3の絶縁層の誘電率は4以下であることを特徴とする半導体装置。

**【請求項4】**

SOI基板のシリコン層を島状に形成して、第1の絶縁層上方に第1のシリコン層を形成する工程と、 10

プラズマ処理により、前記第1のシリコン層の表面及び側面に第2の絶縁層を形成する工程と、

前記第2の絶縁層上方に、第3の絶縁層を形成する工程と、

前記第3の絶縁層をエッチングすることにより、前記第2の絶縁層を介して前記第1のシリコン層の側面に位置する第4の絶縁層を形成する工程と、

前記第1のシリコン層、前記第2の絶縁層、及び前記第4の絶縁層をエッチングすることにより、第2のシリコン層、前記第2のシリコン層の側面と接する領域を有する第5の絶縁層、及び前記第5の絶縁層を介して前記第2のシリコン層の側面に位置する第6の絶縁層を形成する工程と、 20

前記第2のシリコン層と接する領域と、前記第5の絶縁層と接する領域と、前記第6の絶縁層と接する領域と、を有し、前記第6の絶縁層よりも誘電率が高い第7の絶縁層を形成する工程と、

前記第7の絶縁層上方に、前記第2のシリコン層を横断する領域を有する導電層を形成する工程と、を有することを特徴とする半導体装置の作製方法。

**【請求項5】**

請求項4において、

前記第6の絶縁層の誘電率は4以下であることを特徴とする半導体装置の作製方法。

**【請求項6】**

請求項4又は5において、 30

前記第2のシリコン層に一導電型を付与する不純物元素を添加する工程と、

熱処理により前記不純物元素の活性化及び前記第2のシリコン層の再結晶化を行う工程と、を有することを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、SOI(Silicon on Insulator)基板を用いて作製した半導体装置及びその作製方法に関する。

**【背景技術】**

**【0002】**

近年、VLSI技術が飛躍的な進歩を遂げる中で、高速化、低消費電力化を実現するSOI構造が注目されている。この技術は、従来バルク単結晶シリコンで形成されていた電界効果トランジスタ(FET；Field Effect Transistor)の活性領域(チャネル形成領域)を、薄膜単結晶シリコンとする技術である。 40

**【0003】**

SOI構造に用いる基板は、代表的には単結晶シリコン基板上に埋め込み酸化膜層を介して薄膜シリコン層を形成している。よって、SOI基板を用いてMOS型電界効果トランジスタ(MOSFET；Metal Oxide Semiconductor)を作製すると、従来のバルク単結晶シリコン基板を用いる場合よりも寄生容量を小さくでき、高速化に有利になることが知られている。 50

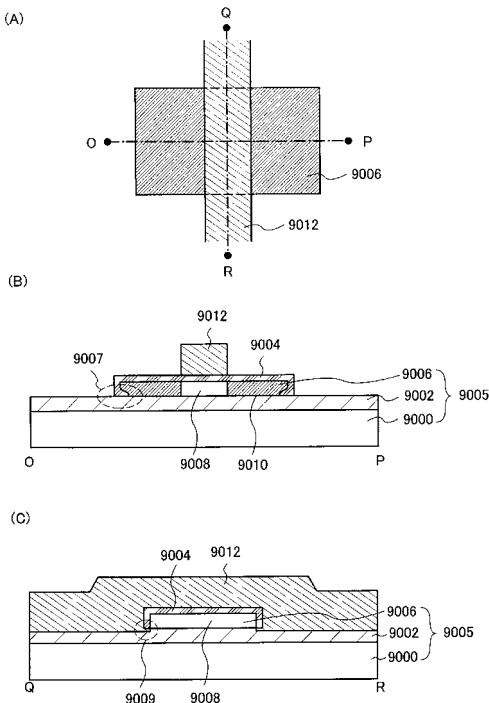

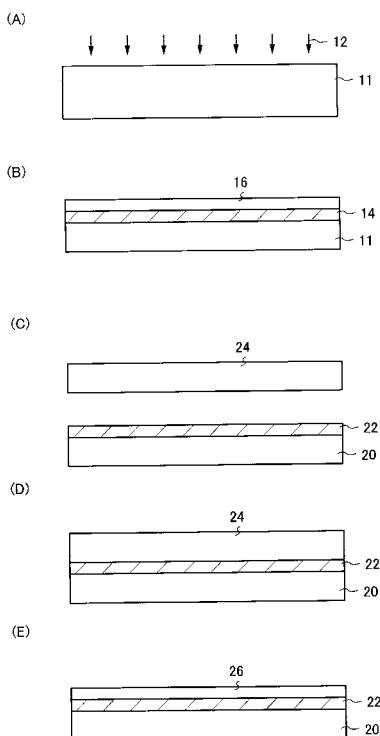

**【0004】**

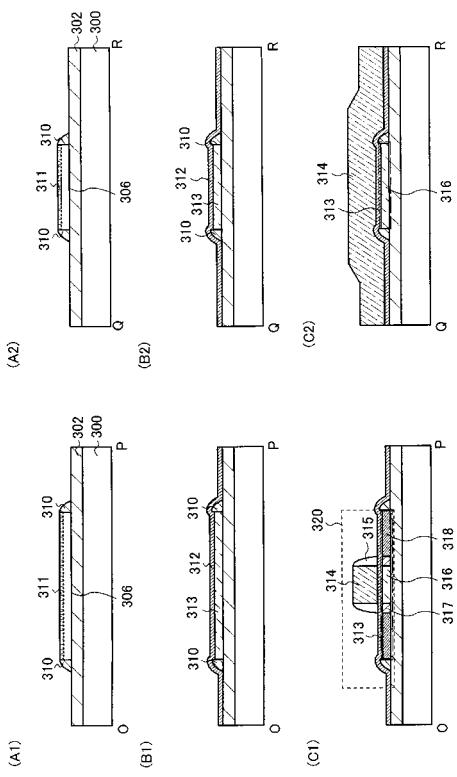

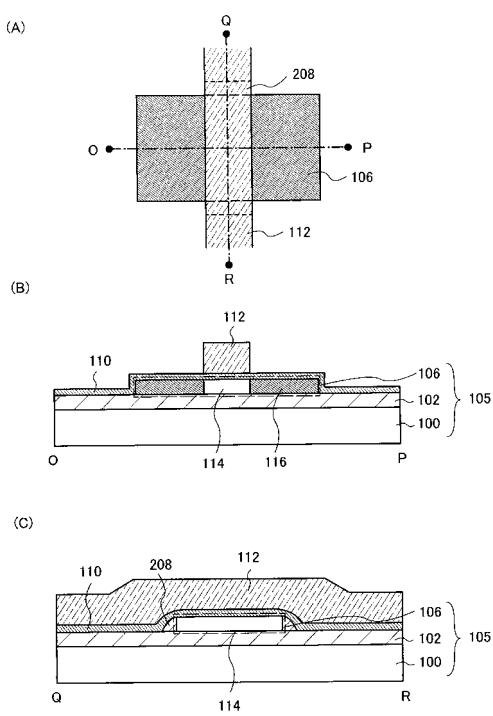

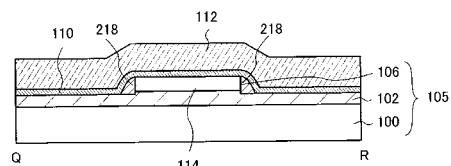

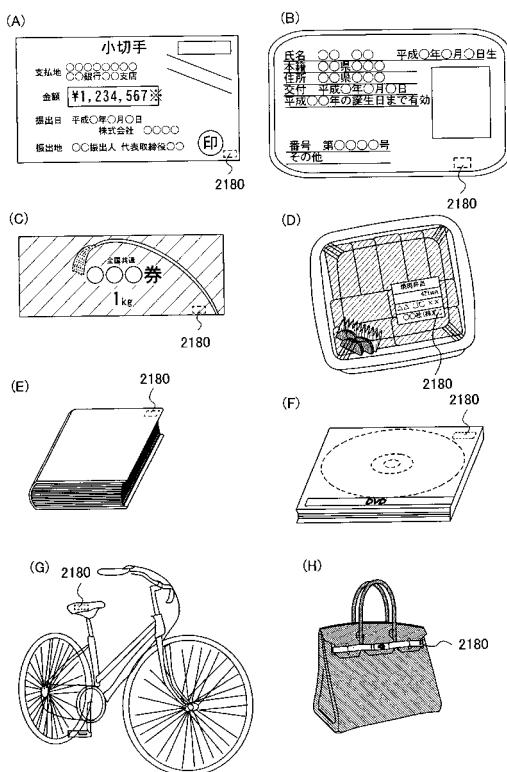

SOI基板を用いた従来の薄膜トランジスタの模式図を図12に示す。図12(A)は薄膜トランジスタの上面図を示し、図12(B)は図12(A)における破線O-P間の断面図、図12(C)は図12(A)における破線Q-R間の断面図に相当する。なお、図12(A)では薄膜トランジスタを構成する薄膜等を一部省略している。

**【0005】**

図12に示す薄膜トランジスタは、支持基板9000上に絶縁層9002とシリコン層9006が順に積層形成されたSOI基板9005を用いて形成されている。シリコン層9006は島状に形成されており、当該シリコン層9006上にはゲート絶縁層9004を介してゲート電極として機能する導電層9012が形成されている。また、シリコン層9006は、ゲート絶縁層9004を介して導電層9012と重なる領域に形成されたチャネル形成領域9008と、ソース領域又はドレイン領域として機能する不純物領域9010とを有している。

【特許文献1】特開2005-019859号公報

**【発明の開示】****【発明が解決しようとする課題】****【0006】**

しかしながら、上記のようなSOI基板を用いた薄膜トランジスタは、島状のシリコン層の端部に起因して様々な不良が生じる。例えば、SOI基板を用いる場合、熱酸化法を用いてシリコン層の表面を酸化してゲート絶縁層を形成することができる。熱酸化法を用いれば良好な絶縁層を得ることができるが、シリコン層の端部からも酸化が進んで、図12(B)の破線9007で示すように、ゲート絶縁層9004がシリコン層の端部に入り込んで形成されてしまう問題がある。

**【0007】**

また、シリコン層を島状に形成する際のエッチング工程やフッ酸等を用いた洗浄工程などの影響で、シリコン層の下層に設けられた絶縁層が除去されてしまうことがある。特に、シリコン層を薄膜化した場合は、その影響が顕著になる。このとき、図12(C)の破線9009で示すように、シリコン層の端部付近においてゲート絶縁層の被覆性が悪くなりやすい。

**【0008】**

一方、ゲート絶縁層を、熱酸化法ではなくCVD法やスパッタリング法を用いて形成する場合は、シリコン層の端部に段差があるため、シリコン層の端部におけるゲート絶縁層の被覆性が悪くなりやすい。

**【0009】**

シリコン層の端部においてゲート絶縁層の被覆が十分に行えない場合、ゲート電極を形成する導電層との短絡や、リーク電流が発生する恐れがある。また、ゲート絶縁層の被覆不良は、素子やゲート絶縁層の静電破壊(ESD; Electro Static Discharge)等の要因ともなる。特に、薄膜トランジスタの低消費電力化や動作速度を向上させるため、ゲート絶縁層の薄膜化が望まれており、ゲート絶縁層を薄く設けた場合にはシリコン層の端部の被覆不良がより顕著な問題となる。さらに、ゲート絶縁層を薄膜化していくと静電破壊の問題も深刻となる。

**【0010】**

また、島状のシリコン層の端部、特にゲート電極を形成する導電層及びシリコン層が重畳する領域では、コーナー部(角部)で電界集中によるリーク電流が発生しやすい問題もある。

**【0011】**

上記のようなシリコン層の端部に起因する問題が生じると、薄膜トランジスタの動作特性が劣化し、信頼性も低下してしまう。また、半導体装置の製造において歩留まりが低下し、製造コストの増加につながる。本発明はこのような問題を鑑みてなされたものであり、信頼性の向上した新規な構造の半導体装置及びその作製方法を提供することを課題とす

10

20

30

40

50

る。

【課題を解決するための手段】

【0012】

本発明の半導体装置の構成は、支持基板上に絶縁層、島状のシリコン層が順に積層されたSOI基板と、島状のシリコン層の一表面上及び側面に設けられたゲート絶縁層と、ゲート絶縁層を介して島状のシリコン層上に設けられ、島状のシリコン層を横断するように設けられたゲート電極と、を有し、ゲート絶縁層は、島状のシリコン層の一表面上と比較して、島状のシリコン層の側面と接する領域の誘電率が小さいことを特徴とする。

【0013】

また、本発明の半導体装置の他の構成は、支持基板上に絶縁層、島状のシリコン層が順に積層されたSOI基板と、島状のシリコン層の一表面上及び側面に設けられたゲート絶縁層と、ゲート絶縁層を介して島状のシリコン層上に設けられ、島状のシリコン層を横断するように設けられたゲート電極と、を有し、ゲート絶縁層は、少なくともゲート電極と重なる領域において、島状のシリコン層の一表面上と比較して、島状のシリコン層の側面と接する領域の誘電率が小さいことを特徴とする。 10

【0014】

また、本発明の半導体装置の他の構成は、支持基板上に絶縁層、島状のシリコン層が順に積層されたSOI基板と、島状のシリコン層の一表面上及び側面に設けられたゲート絶縁層と、ゲート絶縁層を介して島状のシリコン層上に設けられ、島状のシリコン層を横断するように設けられたゲート電極と、を有し、ゲート絶縁層は、島状のシリコン層の一表面上と比較して、島状のシリコン層の側面と接する領域の誘電率が小さいことを特徴とする。 20

【0015】

また、本発明の半導体装置の他の構成は、支持基板上に絶縁層、島状のシリコン層が順に積層されたSOI基板と、島状のシリコン層の一表面上及び側面に設けられたゲート絶縁層と、ゲート絶縁層を介して島状のシリコン層上に設けられ、島状のシリコン層を横断するように設けられたゲート電極と、を有し、ゲート絶縁層は、少なくともゲート電極と重なる領域において、島状のシリコン層の一表面上と比較して、島状のシリコン層の側面と接する領域の誘電率が小さいことを特徴とする。 30

【0016】

また、上記構成において、ゲート絶縁層は、島状のシリコン層の側面と接する領域の厚さが、島状のシリコン層の一表面上の厚さの1倍より大きく3倍以下であることが好ましい。つまり、ゲート絶縁層は、島状のシリコン層の一表面上の厚さを $t_1$ 、島状のシリコン層の側面と接する領域の厚さを $t_2$ とし、 $t_1 < t_2 \leq 3t_1$ を満たすことが好ましい。

【0017】

また、上記構成において、島状のシリコン層の一表面上及び側面に設けられたゲート絶縁層は、島状のシリコン層の一表面上に接して設けられた第1の絶縁層と、島状のシリコン層の側面と接して設けられた第2の絶縁層と、から形成されていてもよい。

【0018】

また、上記構成において、島状のシリコン層の一表面上及び側面に設けられたゲート絶縁層は、島状のシリコン層の一表面上に設けられた第1の絶縁層と、島状のシリコン層の側面に設けられた第2の絶縁層及び第3の絶縁層と、から形成されていてもよい。

【0019】

また、上記構成において、島状のシリコン層の端部は、テーパ角が $45^\circ$ 以上 $95^\circ$ 未満であることが好ましい。

【0020】

また、上記構成において、SOI基板はSIMOX (separation by implanted oxygen) 基板を用いてもよいし、貼り合わせ基板を用いてもよい。

**【0021】**

また、本発明の半導体装置の作製方法の一は、SOI基板のシリコン層を島状に形成し、島状のシリコン層の一表面上及び側面に接して第1の絶縁層を形成し、第1の絶縁層を島状のシリコン層の一表面が露出するまで選択的に除去して、島状のシリコン層の側面と接する第2の絶縁層を形成し、島状のシリコン層の一表面及び第2の絶縁層に接して第3の絶縁層を形成し、第3の絶縁層を介して島状のシリコン層の一表面上に、島状のシリコン層を横断するようにゲート電極層を形成することを特徴とする。

**【0022】**

また、上記作製方法において、島状のシリコン層は、端部のテーパ角が45°以上95°未満となるように形成することが好ましい。

10

**【0023】**

また、本発明の半導体装置の作製方法の一は、SOI基板のシリコン層を島状に形成して第1のシリコン層を形成し、第1のシリコン層の一表面及び側面に接して第1の絶縁層を形成し、第1の絶縁層を島状の第1のシリコン層の一表面が露出するまで選択的に除去して、第1のシリコン層の側面と接する第2の絶縁層を形成するとともに、第1のシリコン層の上層に非晶質領域を形成し、第1のシリコン層に形成された非晶質領域を除去して島状の第2のシリコン層を形成し、第2のシリコン層及び第2の絶縁層に接して第3の絶縁層を形成し、第3の絶縁層を介して第2のシリコン層の一表面上に、第2のシリコン層を横断するようにゲート電極層を形成することを特徴とする。

**【0024】**

20

また、本発明の半導体装置の作製方法の一は、SOI基板のシリコン層を島状に形成して第1のシリコン層を形成し、第1のシリコン層の一表面及び側面に接して第1の絶縁層を形成し、第1のシリコン層及び第1の絶縁層を垂直方向を主体とした異方性エッチングにより薄膜化して、島状の第2のシリコン層及び第2のシリコン層の側面と接する第2の絶縁層を形成し、第2のシリコン層及び第2の絶縁層に接して第3の絶縁層を形成し、第3の絶縁層を介して第2のシリコン層の一表面上に、第2のシリコン層を横断するようにゲート電極層を形成することを特徴とする。

**【0025】**

また、上記作製方法において、第1のシリコン層を膜厚60nm乃至70nmの範囲で形成し、第2のシリコン層を膜厚20nm乃至30nmの範囲で形成することができる。

30

**【0026】**

また、第2のシリコン層の端部は、テーパ角が45°以上95°未満となるように形成することが好ましい。

**【0027】**

また、上記作製方法において、第2の絶縁層及び第3の絶縁層は、ゲート絶縁層として形成する。また、第2の絶縁層は、第3の絶縁層と比較して誘電率が小さい層を形成することが好ましい。

**【0028】**

また、上記作製方法において、ゲート電極層を形成した後、熱処理を行ってもよい。

**【0029】**

40

また、SOI基板はSIMOX法で形成される基板を用いてもよいし、貼り合わせ法で形成される基板を用いてもよい。

**【発明の効果】****【0030】**

本発明を適用することで、チャネル形成領域を有するシリコン層の端部に起因する不良を低減させることができる。よって、シリコン層の端部の特性により半導体装置に及ぼす影響を低減することができ、信頼性の向上した半導体装置を提供することができる。また、半導体装置の製造において、歩留まりを向上させることができる。

**【発明を実施するための最良の形態】****【0031】**

50

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなく、その形態及び詳細を様々に変更しうることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。

#### 【0032】

##### (実施の形態1)

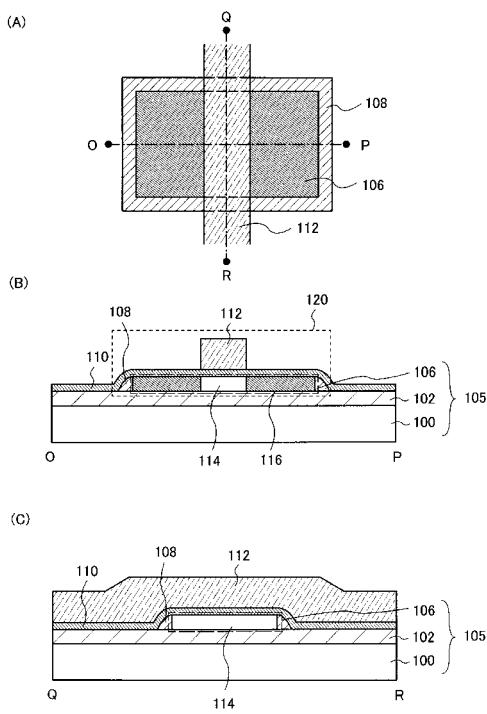

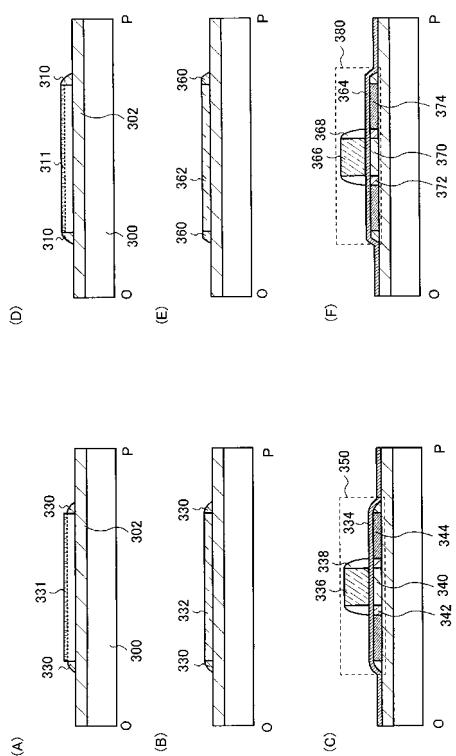

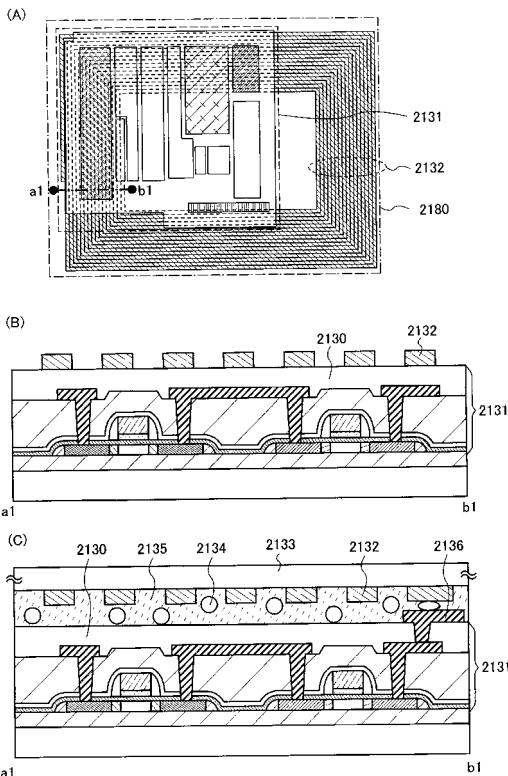

図1は、本発明に係る半導体装置の主要な構成を説明するための上面図及び断面図である。図1は、特に薄膜トランジスタの構成を示しており、図1(A)は上面図、図1(B)は図1(A)における破線O-P間の断面図、図1(C)は図1(A)における破線Q-R間の断面図を示している。なお、図1(A)は、一部薄膜等を省略している。

10

#### 【0033】

図1に示す薄膜トランジスタ120は、SOI基板105を用いて形成されている。薄膜トランジスタ120は、SOI基板105のシリコン層106と、シリコン層106の側面と接して設けられた絶縁層108と、シリコン層106の一表面上に設けられた絶縁層110と、該絶縁層110を介してシリコン層106上に設けられた導電層112と、で構成される。

#### 【0034】

SOI基板105は、SIMOX法や貼り合わせ法で形成した基板を用いる。本実施の形態では、支持基板100上に絶縁層102、シリコン層106が順に形成されたものを用いる。

20

#### 【0035】

シリコン層106は、島状に形成されている。また、シリコン層106は、SOI基板105の表面シリコン層を利用するため、単結晶シリコンで形成される。シリコン層106の膜厚は、10nm乃至150nm、好ましくは30nm乃至100nm、又は10nm乃至30nmの範囲で形成するとよい。

#### 【0036】

また、シリコン層106の端部は垂直形状に近くなるように形成されているのが好ましい。具体的には、テーパ角が45°以上95°未満、好ましくはテーパ角が60°以上95°未満となるように形成されているとよい。シリコン層106の端部を垂直に近い形状とすることで、ゲート電極として機能する導電層112とシリコン層106の端部が重畳する領域において、シリコン層106の端部と、導電層112と、が、シリコン層106の側面と接するゲート絶縁層を介して形成してしまう寄生チャネルを低減することができる。これは、シリコン層の端部を垂直に近い形状とすることで、シリコン層の端部を緩やかなテーパ角（例えば、テーパ角45°以下）を有するテーパ形状とするよりも、シリコン層全体の面積においてシリコン層の端部が占める面積を減少させることができるためである。なお、寄生チャネルは、チャネル形成領域において、ソース領域とドレイン領域とを結ぶ方向にほぼ平行に形成されるチャネルに対して垂直又は筋交いに交差する方向で、且つチャネル形成領域の端部に形成されるチャネルを示す。寄生チャネルが形成されるとリーク電流の発生につながるため、シリコン層の端部を垂直形状に近い形状に加工して寄生チャネルを防止することは、完成する半導体装置の特性のバラツキを低減し、信頼性を向上させるのに非常に効果的である。

30

#### 【0037】

また、テーパ角とはテーパ形状を有する層において、当該テーパ形状を有する層の側面と、当該テーパ形状を有する層の底面と、がなす傾斜角を示す。なお、シリコン層106の端部をテーパ角が30°以上85°未満、又は45°以上60°未満の緩やかなテーパ形状としてもよい。シリコン層106の端部をテーパ形状として、コーナー部（角部）を緩やかにすることにより、該コーナー部に電界が集中することを緩和することができる。

40

#### 【0038】

50

なお、本明細書において、シリコン層の「端部」とは、島状に形成されたシリコン層の縁部分（エッジ部分）を示す。シリコン層の「側面」とは、シリコン層の縁部分の面を示す。

#### 【0039】

シリコン層106は、チャネル形成領域114と、ソース領域又はドレイン領域として機能する不純物領域116と、を有する。不純物領域116には、一導電型を付与する不純物元素が添加されている。また、チャネル形成領域114に、トランジスタの閾値電圧を制御するために、一導電型を付与する不純物元素が添加されていてもよい。チャネル形成領域114は、絶縁層110を介して導電層112と略一致する領域のシリコン層106に形成されており、不純物領域116の間に位置するものである。

10

#### 【0040】

また、シリコン層106に、LDD (Lightly Doped Drain) 領域として機能する低濃度不純物領域を形成してもよい。低濃度不純物領域は、チャネル形成領域と、ソース領域又はドレイン領域として機能する不純物領域との間に形成することができる。また、低濃度不純物領域は、ソース領域又はドレイン領域として機能する不純物領域と比較して、不純物濃度が低いものとする。

#### 【0041】

シリコン層106の側面と接して絶縁層108が形成されている。また、シリコン層106の一表面上及び絶縁層108上に、絶縁層110が形成されている。絶縁層108及び絶縁層110は、薄膜トランジスタ120のゲート絶縁層として機能する。すなわち、本発明に係るゲート絶縁層は、一体物ではなく複数の絶縁層の複合物で構成される。なお、複数の絶縁層の境界は明確なものでなくともよい。

20

#### 【0042】

ゲート絶縁層を、シリコン層106の側面と接する絶縁層108、並びにシリコン層106の一表面上及び絶縁層108と接する絶縁層110で形成することで、シリコン層106の端部におけるゲート絶縁層の被覆性を良好にすることができます。よって、シリコン層106の端部におけるゲート絶縁層の被覆不良に起因した不良を防止することができる。

#### 【0043】

また、絶縁層108及び絶縁層110にて形成されるゲート絶縁層は、シリコン層106の一表面上に形成された領域と比較して、シリコン層106の側面と接する領域の膜厚が厚いことが好ましい。例えば、シリコン層106の一表面上からの垂直線とゲート絶縁層の最表面との交点までの距離を膜厚t1とする。シリコン層106の側面からの垂直線とゲート絶縁層の最表面との交点までの距離を膜厚t2とする。このとき、ゲート絶縁層は、膜厚t1 < 膜厚t2を満たすことが好ましい。例えば、t1 < t2 - 3t1を満たすことができる。なお、シリコン層106の側面と接する領域の膜厚、例えばシリコン層106の側面からの垂直線とゲート絶縁層の最表面との交点までの距離である膜厚t2は、一定値であるとは限らない。この場合は、膜厚t1と比較して、膜厚t2の最小値が同じあるいは膜厚t1より大きいことが好ましい。ゲート絶縁層によりシリコン層106の端部を十分に被覆する、好ましくはシリコン層106の側面と接する領域の膜厚を厚くすることで、シリコン層106の端部に掛かる電界を緩和することができ、リーク電流の発生を防止することができる。

30

#### 【0044】

また、絶縁層108及び絶縁層110にて形成されるゲート絶縁層は、シリコン層106の一表面上に形成された領域と比較して、シリコン層106の側面と接する領域の誘電率が小さいことが好ましい。例えば、絶縁層110と比較して、絶縁層108の誘電率を小さくすることで、シリコン層106の側面と接する領域のゲート絶縁層の誘電率を小さくすることができる。好ましくは、絶縁層108を誘電率4以下の低誘電率材料を用いて形成するとよい。ゲート絶縁層において、シリコン層106の一表面上と比較して、シリコン層106の側面と接する領域の誘電率を小さくすることで、シリコン層106の端部、特にコーナー部（角部）に電界が集中することを緩和できる。その結果、ゲート絶縁層

40

50

に局所的に過度な電界が掛かることを防止でき、ゲート絶縁層の絶縁不良を防止することができる。よって半導体装置を歩留まり良く製造することができ、完成する半導体装置の信頼性を向上させることができる。

#### 【0045】

なお、ここでは、絶縁層108は、島状に形成されたシリコン層106の周囲を囲うように、シリコン層106の側面と接して形成されている。また、絶縁層108は、シリコン層106の上面が露出するように開口部を有しているともいえる。

#### 【0046】

なお、上述したように、シリコン層を島状に形成した場合は、シリコン層の端部に起因する様々な不良が生じやすい。なかでも、ゲート電極と重畳するシリコン層の端部、さらにはゲート電極と重畳するシリコン層の端部に形成されたチャネル形成領域端部（チャネル形成領域とソース領域又はドレイン領域として機能する不純物領域との境界付近）は不良が生じやすく、静電破壊等の影響も受けやすい。この要因としては、チャネル形成領域端部及びゲート電極が、両者が重畳する領域においてチャネル形成領域端部（シリコン層の端部）の側面と接するゲート絶縁層を介して寄生チャネルを形成しやすいこと、チャネル形成領域において中央付近と比較して端部（ソース領域又はドレイン領域として機能する不純物領域との境界付近）に高い電圧が加わること、上層に形成されるゲート電極層（導電層）を加工する際にエッチング等の影響を受けること、シリコン層の端部においてゲート絶縁層が局所的に薄くなること等が挙げられる。したがって、少なくともゲート電極層とシリコン層との端部が重畳する領域において、シリコン層の側面と接して絶縁層を形成することで、絶縁破壊や静電破壊、リーク電流等の不良を低減することが可能である。例えば、図16(A)乃至(C)に示すように、島状に形成されたシリコン層106の端部とゲート電極として機能する導電層112が重畳する領域において、シリコン層106の側面と接する絶縁層208が形成されればよい。図16(A)は上面図を示し、図16(B)は図16(A)における破線O-P間の断面図、図16(C)は図16(A)における破線Q-R間の断面図に相当する。ここでは、絶縁層208は、導電層112とシリコン層106の端部が重畳する領域及びその近傍のみに形成されている。よって、図16(B)ではシリコン層106の側面に絶縁層208が形成されておらず、図16(C)ではシリコン層106の側面と接して絶縁層208が形成されている。

#### 【0047】

図16(A)乃至(C)に示すように、少なくとも、ゲート電極として機能する導電層とシリコン層の端部とが重畳する領域においてシリコン層の側面と接する絶縁層を形成することで、シリコン層の端部及びゲート電極として機能する導電層との短絡を防止することができる。例えば、図17に示すように、シリコン層106下の絶縁層102が、シリコン層106の端部付近で除去されていても、シリコン層106の側面と接する絶縁層218を形成することで、シリコン層106の端部を十分に被覆することができる。特に、本発明を適用してゲート絶縁層の被覆性を向上させることは、ゲート絶縁層の膜厚が数nm乃至数10nmの範囲で、シリコン層の膜厚よりも薄い場合に効果的である。また、本発明を適用することでシリコン層の端部に電界が集中することを緩和することができ、リーク電流を防止・低減することができる。特に、ゲート絶縁層において、シリコン層の一表面上と比較してシリコン層の側面と接する領域の誘電率を小さくすることで、局所的に電界が掛かることを緩和できるため、効果的である。以上のように、シリコン層の側面、特にゲート電極として機能する導電層とシリコン層の端部とが重畳する領域におけるシリコン層の側面と接して絶縁層を形成することで、完成する半導体装置の信頼性、及び動作特性を高めることができる。

#### 【0048】

絶縁層108及び絶縁層110は、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化アルミニウム、SiOF(フッ素含有酸化シリコン)、SiOC(炭素含有酸化シリコン)、 DLC(ダイヤモンドライクカーボン)、ポーラスシリカ等の材料を用いて、単層構造、又は積層構造で形成することができる。また、絶縁層108

10

20

30

40

50

及び絶縁層 110 は同じ材料を用いて形成してもよいし、異なる材料を用いて形成してもよい。本実施の形態では、絶縁層 108 は酸化シリコン層を用いて形成し、絶縁層 110 は窒化シリコン層で形成する。

#### 【0049】

なお、絶縁層 108 は、絶縁層 110 と比較して誘電率が小さい材料を用いて形成するのが好ましい。また、絶縁層 108 は、SiOF、SiOC、DLC、ポーラスシリカ等の誘電率がおよそ 4 以下の低誘電率材料を用いて形成することが好ましい。なお、誘電率 4 以下の低誘電率材料は low-k 材料ともいわれ、low-k 材料を用いて作製される膜は low-k 膜といわれている。このように、絶縁層 110 と比較して誘電率が小さい材料を用いて絶縁層 108 を形成することで、シリコン層の一表面上と比較して、シリコン層の側面と接する領域のゲート絶縁層の誘電率を小さくすることができる。10

#### 【0050】

絶縁層 110 を介してシリコン層 106 上にゲート電極として機能する導電層 112 が形成されている。導電層 112 は、タンタル (Ta)、タンゲステン (W)、チタン (Ti)、モリブデン (Mo)、クロム (Cr)、アルミニウム (Al)、銅 (Cu)、又はニオブ (Nb) 等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて形成することができる。化合物材料としては、窒素化合物、酸素化合物、炭素化合物、ハロゲン化合物などを用いることができ、具体的には窒化タンゲステン、窒化チタン、窒化アルミニウム等が挙げられる。導電層 112 は、これらの材料のうち 1 つ又は複数を用いて、単層構造、又は積層構造で形成する。また、導電層 112 は、リン等の一導電型を付与する不純物元素を添加した多結晶シリコンを用いて形成してもよい。20

#### 【0051】

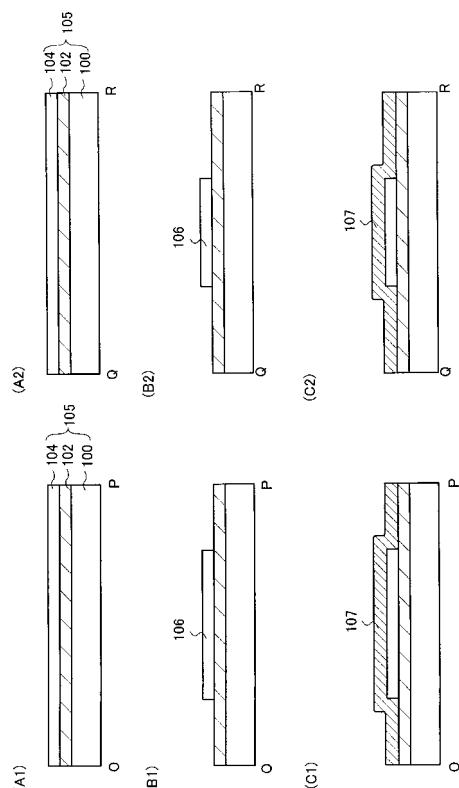

次に、図 1 に示す薄膜トランジスタ 120 の作製方法について、図 2 を用いて具体的に説明する。

#### 【0052】

まず、SOI 基板 105 を準備する。ここでは、支持基板 100 上に絶縁層 102、シリコン層 104 が順に積層形成されたものを用いる (図 2 (A1)、(A2) 参照)。

#### 【0053】

本発明には、公知の SOI 基板を用いることができ、その作製方法や構造は特に限定されるものではない。SOI 基板としては、代表的には SIMOX 基板や貼り合わせ基板が挙げられる。また、貼り合わせ基板の例として、ELTRAN (登録商標)、UNIBOND (登録商標)、等が挙げられる。30

#### 【0054】

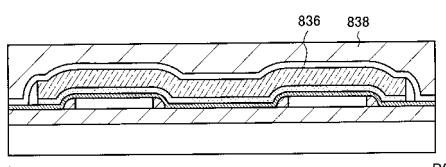

例えば、SIMOX 基板は、単結晶シリコン基板 11 に酸素イオン 12 を注入し、1300 以上で熱処理して埋め込み酸化膜 (BOX; Buried Oxide) 層 14 を形成することにより、表面に薄膜シリコン層 16 を形成し、SOI 構造を得ることができる。薄膜シリコン層 16 は、埋め込み酸化膜層 14 により、単結晶シリコン基板 11 と絶縁分離されている (図 26 (A)、(B) 参照)。また、埋め込み酸化膜層形成後に、さらに熱酸化する ITOX (Internal Thermal Oxidation) と呼ばれる技術を用いることもできる。40

#### 【0055】

一方、貼り合わせ基板は、酸化膜層 22 を介して 2 枚の単結晶シリコン基板 (第 1 单結晶シリコン基板 20、第 2 单結晶シリコン基板 24) を貼り合わせ、一方の単結晶シリコン基板を貼り合わせた面ではない方の面から薄膜化することにより、表面に薄膜シリコン層 26 を形成し、SOI 構造を得ることができる。酸化膜層 22 は、一方の基板 (ここでは第 1 单結晶シリコン基板 20) を熱酸化して形成することができる。また、2 枚の単結晶シリコン基板は、接着剤なしで直接貼り合わせることができる。例えば、第 1 单結晶シリコン基板 20 を熱処理して酸化膜層 22 を形成した後、第 2 单結晶シリコン基板 24 と重ね合わせ、800 以上、好ましくは 1100 程度で熱処理することにより、貼り合わせ界面での化学結合により、2 枚の基板を接着することができる。その後、第 2 单結晶50

シリコン基板 24 を、接着されていない方の面から研磨して所望の厚さの薄膜シリコン層 26 を形成することができる（図 26（C）、（D）、（E）参照）。なお、貼り合わせ後に第 2 単結晶シリコン基板 24 を研磨せずに、第 2 単結晶シリコン基板 24 の所定の深さの領域に水素イオン注入して微小ボイドを形成し、当該微小ボイドの熱処理による成長を利用して基板を劈開する Smart-Cut（登録商標）法と呼ばれる技術を用いることもできる。また、第 2 単結晶シリコン基板を研磨後、小型のプラズマエッチャリング装置で局所的に制御しながら基板をエッチャリングして薄膜化する PACE（Plasma Assisted Chemical Etching）と呼ばれる技術を用いることもできる。

## 【0056】

10

本実施の形態で示す SOI 基板 105 において、支持基板 100 は図 26 に示す単結晶シリコン基板に相当し、絶縁層 102 は埋め込み酸化膜層又は酸化膜層に相当し、シリコン層 104 は表面に形成される薄膜シリコン層に相当する。

## 【0057】

シリコン層 104 は、SOI 基板 105 の表面シリコン層であり、単結晶シリコン層である。SOI 基板 105 の表面シリコン層の膜厚は、SOI 基板 105 の作製時に研磨量、イオン注入の深さ等の条件を制御することによって、適宜選択することができる。例えば、膜厚 40 nm 乃至 200 nm の範囲の表面シリコン層を形成することができる。本実施の形態では、シリコン層は、膜厚膜厚 10 nm 乃至 150 nm の範囲、好ましくは 30 nm 乃至 100 nm、又は 10 nm 乃至 30 nm の範囲で形成する。

20

## 【0058】

次に、シリコン層 104 を選択的にエッチャリングして、島状のシリコン層 106 を形成する（図 2（B1）、（B2）参照）。このとき、シリコン層 106 は、端部が垂直形状となるように形成してもよいし、端部がテーパ形状となるように形成してもよい。シリコン層 106 の端部の形状は、エッチャリング条件等を変化させることにより、適宜選択することができる。好ましくはシリコン層 106 の端部をテーパ角が 45° 以上 95° 未満、より好ましくはテーパ角が 60° 以上 95° 未満となるように形成するとよい。シリコン層 106 の端部を垂直に近い形状とすることで寄生チャネルを低減することができる。

## 【0059】

30

次に、シリコン層 106 を覆うように絶縁層 107（以下、第 1 の絶縁層 107 ともいう）を形成する（図 2（C1）、（C2）参照）。第 1 の絶縁層 107 は、CVD 法やスパッタリング法を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、SiOF、SiOC、DLC、ポーラスシリカ等の材料を用いて形成する。

## 【0060】

第 1 の絶縁層 107 は、シリコン層 106 の端部を十分に被覆できる膜厚で形成する。第 1 の絶縁層 107 の膜厚は、下層に形成されているシリコン層 106 の膜厚の 1.5 倍乃至 3 倍の範囲の厚さで形成するのが好ましい。

## 【0061】

40

次に、第 1 の絶縁層 107 を、垂直方向を主体とした異方性エッチャリングを行うことにより選択的にエッチャリングし、シリコン層 106 の側面と接する絶縁層 108（以下、第 2 の絶縁層 108 ともいう）を形成する（図 3（A1）、（A2）参照）。

## 【0062】

第 1 の絶縁層 107 を、垂直方向を主体として異方性のエッチャリングを行っていくと、シリコン層 106 の一表面上および絶縁層 102 上に形成されている第 1 の絶縁層 107 から徐々にエッチャリングしていく。なお、シリコン層 106 の一表面上及び絶縁層 102 上には、ほぼ同じ膜厚の第 1 の絶縁層 107 が形成されている。よって、シリコン層 106 の一表面が露出したところでエッチャリングを停止させることにより、シリコン層 106 の側面と接する領域及びその付近のみに第 1 の絶縁層 107 を残すことができる。残存する第 1 の絶縁層 107 は、第 2 の絶縁層 108 に相当する。なお、シリコン層 106 の端部を垂直形状に近い形状としておくことで、シリコン層 106 の側面と接する領域及びその付

50

近のみに第1の絶縁層107を残すことが容易になる。つまり、第2の絶縁層108を容易に形成することができる。

#### 【0063】

第1の絶縁層107のエッティング方法は、垂直方向を主体とした異方性エッティングを行えるものであれば特に限定されない。例えば、反応性イオンエッティング(RIE: R e a c t i v e I o n E t c h i n g)を利用することができる。また、反応性イオンエッティングは、プラズマ発生法により、平行平板方式、マグネットロン方式、2周波方式、E C R方式、ヘリコン方式、I C P方式などに分類される。このとき用いるエッティングガスは、第1の絶縁層107と、それ以外の層(シリコン層106)とでエッティング選択比が高く取れるものを選択すればよい。絶縁層を選択的にエッティングする際には、例えば、C 10 H F<sub>3</sub>、C F<sub>4</sub>、C<sub>4</sub> F<sub>8</sub>、C<sub>2</sub> F<sub>6</sub>、N F<sub>3</sub>等のフッ素系のガスを用いることができる。その他、H eやA rやX eなどの不活性ガス、又はO<sub>2</sub>ガス、H<sub>2</sub>ガスを適宜加えてよい。

#### 【0064】

第2の絶縁層108の形状は、薄膜を形成する材料、エッティング条件等を適宜選択することにより変更することができる。本実施の形態では、第2の絶縁層108は、底面(絶縁層102と接する面)からの垂直方向の高さがシリコン層106と略一致するように形成している。また、第2の絶縁層108は、シリコン層106の側面と接しない面を湾曲状に形成している。具体的には、任意の曲率を有し、接するシリコン層106の側面に対して凸形状に湾曲するように形成している。もちろん、本発明は特に限定されず、第2の絶縁層108は丸みを帯びた形状でなく、角を有する形状としてもよい。好ましくは、第2の絶縁層108のコーナー部を緩やかな形状とすると、上層に積層される層(ここでは、絶縁層110)の被覆性を良好にすることができます。なお、エッティング条件とは、エッティングガスの種類、各ガスの流量比の他、基板を載置した電極に印加される電力量、基板が載置した電極の電極温度、チャンバー内圧力等を示す。

#### 【0065】

次に、シリコン層106及び第2の絶縁層108上に絶縁層110(以下、第3の絶縁層110ともいう)を形成する(図3(B1)、(B2)参照)。第3の絶縁層110は、C V D法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化アルミニウム等の材料を用いて形成する。また、第3の絶縁層110は、これらの材料のうち1つ又は複数を用いて、単層構造又は積層構造で形成する。第3の絶縁層110は、膜厚1nm乃至50nm、好ましくは膜厚1nm乃至20nm、より好ましくは1nm乃至10nmの範囲で形成する。本実施の形態では、第3の絶縁層110として酸化窒化シリコン層を膜厚20nmで形成する。

#### 【0066】

また、第3の絶縁層110は、プラズマ処理による固相酸化若しくは固相窒化で形成することもできる。例えば、シリコン層106及び第2の絶縁層108を、プラズマ処理により酸化又は窒化して、第3の絶縁層110を形成することができる。

#### 【0067】

プラズマ処理による固相酸化処理若しくは固相窒化処理は、マイクロ波(代表的には2.45GHz)等の高周波で励起され、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下、且つ電子温度が0.5eV以上1.5eV以下のプラズマを利用して行うことが好ましい。固相酸化処理若しくは固相窒化処理において、500以下の温度において、緻密な絶縁層を形成すると共に実用的な反応速度を得るためである。

#### 【0068】

プラズマ処理によりシリコン層106及び第2の絶縁層108の表面を酸化する場合には、酸素を含む雰囲気下(例えば、酸素(O<sub>2</sub>)、オゾン(O<sub>3</sub>)、亜酸化窒素(N<sub>2</sub>O)、一酸化窒素(NO)若しくは二酸化窒素(NO<sub>2</sub>)、及び希ガス(ヘリウム(H e)、ネオン(N e)、アルゴン(A r)、クリプトン(K r)、キセノン(X e)の少なくとも1つを含む)を含む雰囲気下、又は酸素(O<sub>2</sub>)、オゾン(O<sub>3</sub>)、亜酸化窒素(N 50

$\text{O}_2$ ）、一酸化窒素（NO）若しくは二酸化窒素（NO<sub>2</sub>）と、水素（H<sub>2</sub>）と、希ガスと、を含む雰囲気下）で行う。また、プラズマ処理によりシリコン層106及び絶縁層108の表面を窒化する場合には、窒素を含む雰囲気下（例えば、窒素（N<sub>2</sub>）と希ガス（He、Ne、Ar、Kr、Xeの少なくとも一つを含む）を含む雰囲気下、窒素と水素と希ガスを含む雰囲気下、又はNH<sub>3</sub>と希ガスを含む雰囲気下）でプラズマ処理を行う。希ガスとしては、例えばArを用いることが好ましい。また、ArとKrを混合したガスを用いてもよい。

#### 【0069】

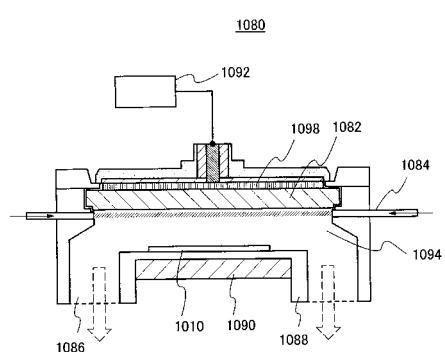

ここで、プラズマ処理を行うためのプラズマ処理装置1080の構成例を図18に示す。当該プラズマ処理装置1080は、支持台1088と、ガスを供給するためのガス供給部1084、ガスを排気するために真空ポンプに接続する排気口1086、アンテナ1098、誘電体板1082、プラズマ発生用の高周波を入力する高周波供給部1092を有している。被処理体1010は、支持台1088によって保持される。また、支持台1088に温度制御部1090を設けることによって、被処理体1010の温度を制御することも可能である。被処理体1010は、プラズマ処理をする基体であり、本実施の形態では支持基板100上に絶縁層102、島状のシリコン層106を順に形成した積層体に相当する。

#### 【0070】

以下、図18に示すプラズマ処理装置1080を用いてシリコン層表面に絶縁層を形成する具体例を述べる。なお、プラズマ処理とは、基板、シリコン層、絶縁層、導電層に対する酸化処理、窒化処理、酸化窒化処理、水素化処理、表面改質処理を範疇に含んでいる。これらの処理は、その目的に応じて、ガス供給部1084から供給するガスを選択すれば良い。

#### 【0071】

まず、図18に示すプラズマ処理装置1080の処理室内を真空にする。そして、ガス供給部1084から希ガス、酸素又は窒素を含むガスを供給する。被処理体1010は室温、若しくは温度制御部1090により100以上550以下の範囲で加熱する。被処理体1010と誘電体板1082との間隔（以下、電極間隔ともいう）は、20mm以上200mm以下（好ましくは20mm以上60mm以下）程度である。

#### 【0072】

次に、高周波供給部1092からアンテナ1098に高周波を入力する。ここでは、高周波としてマイクロ波（周波数2.45GHz）を入力する。そしてマイクロ波をアンテナ1098から誘電体板1082を通して処理室内に入力することによって、プラズマ1094を生成し、当該プラズマ1094によって酸素ラジカル（OHラジカルを含む場合もある）又は窒素ラジカル（NHラジカルを含む場合もある）を生成する。このとき、プラズマ1094は、供給されたガスによって生成される。

#### 【0073】

マイクロ波の入力によりプラズマ1094を生成すると、低電子温度（3eV以下、好ましくは1.5eV以下）で高電子密度（ $1 \times 10^{11} \text{ cm}^{-3}$ 以上）のプラズマを生成することができる。具体的には、電子温度が0.5eV以上1.5eV以下、且つ電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下のプラズマ生成することができる。なお、本明細書では、マイクロ波の入力により生成された低電子温度で高電子密度のプラズマを高密度プラズマともいう。また、高密度プラズマを利用してプラズマ処理を行うことを高密度プラズマ処理ともいう。

#### 【0074】

プラズマ1094により生成された酸素ラジカル（OHラジカルを含む場合もある）又は窒素ラジカル（NHラジカルを含む場合もある）によって、被処理体1010に形成されたシリコン層の表面が酸化又は窒化されて絶縁層が形成される。このとき、供給するガスにアルゴンなどの希ガスを混合させると、希ガスの励起種により酸素ラジカルや窒素ラジカルを効率良く生成することができる。なお、供給ガスに希ガスを用いる場合、形成さ

10

20

30

40

50

れた絶縁層に希ガスが含まれる場合がある。プラズマで励起した活性なラジカルを有効に使うことにより、500 以下の低温で固相反応による酸化、窒化を行うことができる。

【0075】

図18に示す装置を用いた高密度プラズマ処理により形成される好適な第3の絶縁層110の一例は、酸素を含む雰囲気下のプラズマ処理によりシリコン層106の一表面上に3nm乃至6nmの厚さで酸化シリコン層を形成し、その後窒素を含む雰囲気下でその酸化シリコン層の表面を窒化プラズマで処理した窒素プラズマ処理層を形成する。具体的には、まず、酸素を含む雰囲気下でのプラズマ処理によりシリコン層106の一表面上に3nm乃至6nmの厚さで酸化シリコン層を形成する。その後、続けて窒素を含む雰囲気下でプラズマ処理を行うことにより酸化シリコン層の表面又は表面近傍に窒素濃度の高い窒素プラズマ処理層を設ける。なお、表面近傍とは、酸化シリコン層の表面から概略0.5nm乃至1.5nmの範囲の深さをいう。例えば、窒素を含む雰囲気下でプラズマ処理を行うことによって、酸化シリコン層の表面から垂直方向に概略1nmの深さに窒素を20原子%乃至50原子%の割合で含有した構造となる。また、高密度プラズマ処理により絶縁層108、絶縁層102の表面も酸化又は窒化することができる。

【0076】

例えば、単結晶シリコンであるシリコン層106の表面をプラズマ処理で酸化することで、界面に歪みのない緻密な酸化層を形成することができる。また、当該酸化層をプラズマ処理で窒化することで、表層部の酸素を窒素に置換して窒化層を形成すると、さらに緻密化することができる。それにより絶縁耐圧が高い絶縁層を形成することができる。

【0077】

いずれにしても、上記のようなプラズマ処理による固相反応処理若しくは固相窒化処理を用いることで、950乃至1050の範囲で形成される熱酸化膜と同等な絶縁層を得ることができる。すなわち、半導体素子、特に薄膜トランジスタや不揮発性記憶素子のゲート絶縁膜として機能する絶縁層として信頼性の高い絶縁層を形成することができる。

【0078】

次に、第3の絶縁層110を介してシリコン層106上にゲート電極として機能する導電層112を形成する(図3(C1)、(C2)参照)。導電層112は、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、アルミニウム(Al)、銅(Cu)、又はニオブ(Nb)等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて形成することができる。また、リン等の一導電型を付与する不純物元素が添加された多結晶シリコンに代表される半導体材料を用いて形成することもできる。導電層112は、これらの材料を用いてCVD法やスパッタリング法により全面に形成した後、選択的にエッチングして所望の形状に加工することができる。また、導電層112は、単層構造でもよいし積層構造としてもよい。導電層112は、膜厚100nm乃至1000nm、好ましくは膜厚200nm乃至800nm、より好ましくは300nm乃至500nmの範囲で形成する。

【0079】

次に、シリコン層106に対して一導電型を付与する不純物元素を選択的に添加し、チャネル形成領域114と、ソース領域又はドレイン領域として機能する不純物領域116を形成する。ここでは、導電層112をマスクとして、一導電型を付与する不純物元素を添加する。一導電型を付与する不純物元素としては、ボロン(B)、アルミニウム(Al)、ガリウム(Ga)等のp型を付与する元素、リン(P)、ヒ素(As)等のn型を付与する元素を用いることができる。

【0080】

なお、シリコン層106に一導電型を付与する不純物元素を添加した後、熱処理を行うことにより、添加した不純物元素を活性化することが好ましい。熱処理は、レーザビームの照射、又はRTA若しくはファーネスアニュール炉を用いて行うことができる。具体的には、400乃至700、好ましくは500乃至550の温度範囲で熱処理を行うとよい。また、熱処理は窒素雰囲気下で行うことが好ましい。例えば、550 4時間の

10

20

30

40

50

加熱を行うことにより、活性化を行うことができる。また、第1の絶縁層107を選択的にエッティングして第2の絶縁層108を形成する際、エッティング条件やそれぞれの薄膜を形成する材料や膜厚等により、シリコン層106の一部が非晶質化する場合がある。この場合、熱処理を行うことにより、活性化とともにシリコン層の再結晶化を行うことができる。

【0081】

以上により、本発明を適用した薄膜トランジスタ120を形成することができる。なお、本実施の形態で示したTFTの構造は一例であり、図示した構造に限定されるものではない。例えば、直列に接続された少なくとも2つ以上のチャネル形成領域を含んだシリコン層と、それぞれのチャネル形成領域に電界を印加する少なくとも2つ以上のゲート電極層と、を有するマルチゲート構造を用いてもよい。また、TFTのシリコン層にLDD領域を形成してもよい。10

【0082】

また、本実施の形態ではゲート電極として単層の導電層を形成する例を示したが、本発明は特に限定されるものではない。ゲート電極の側面をテープ形状にしてもよいし、ゲート電極を2層以上の導電層の積層構造としてもよい。また、ゲート電極を2層の導電層の積層構造として各層でテープ角度が異なるようにしてもよい。また、ゲート電極として機能する導電層の側面に接して、サイドウォールともいわれる絶縁層を形成してもよい。

【0083】

本発明を適用して作製した薄膜トランジスタは、島状のシリコン層の端部に起因する不良を低減させることができる。よって、信頼性の高い半導体装置を作製することができる。また、半導体装置を歩留まり良く製造することも可能になる。20

【0084】

なお、本実施の形態は、本明細書で示す他の実施の形態と、適宜組み合わせができる。

【0085】

(実施の形態2)

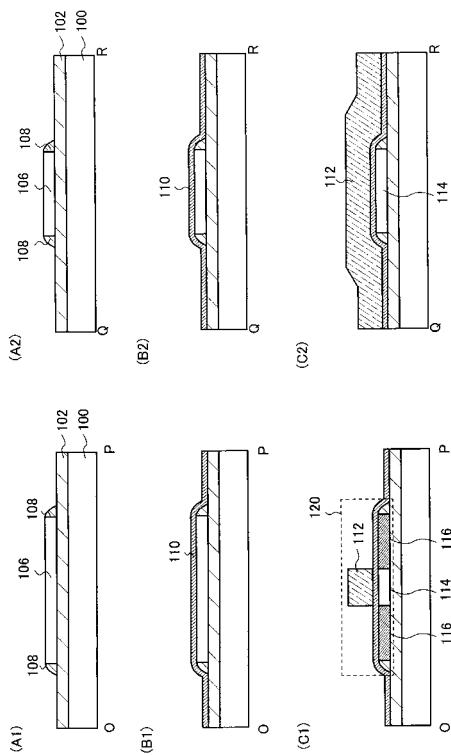

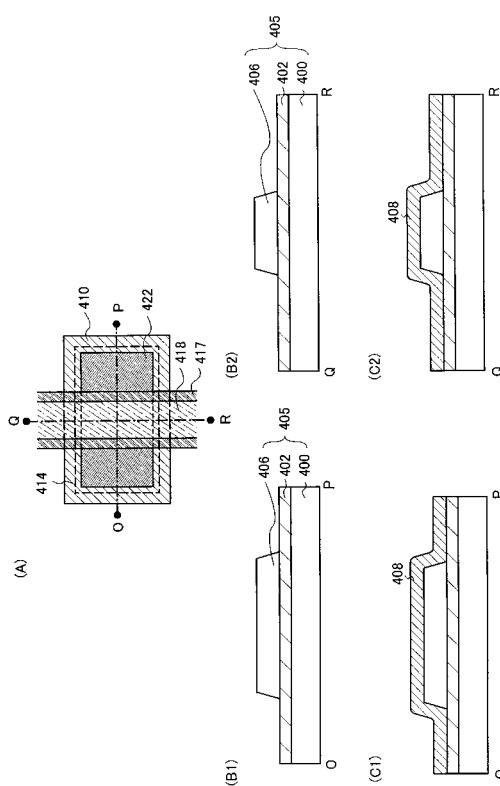

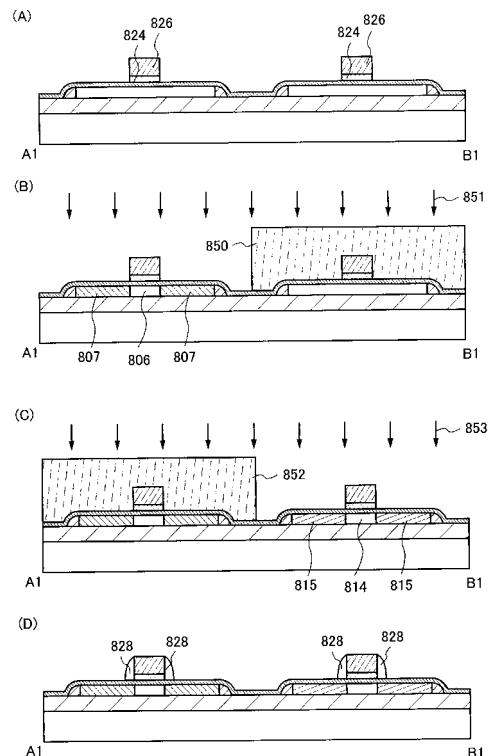

本実施の形態では、上記実施の形態1と異なる作製方法で半導体装置を作製する例について、図4乃至図6を用いて説明する。

【0086】

図4(A)は、本発明に係る半導体装置の主要な構成を説明するための上面図である。なお、図4(A)は、一部薄膜等を省略している。

【0087】

図4(A)に示す半導体装置は、SOI基板を用いて薄膜トランジスタが形成されている。SOI基板の表面シリコン層は島状に形成されており、島状のシリコン層313を横断するように、ゲート電極を形成する導電層314が設けられている。また、島状のシリコン層313の側面と接して絶縁層310が設けられている。ここでは、島状のシリコン層313の全周囲を囲うように絶縁層310を設ける例を図示しているが、少なくとも導電層314及びシリコン層313が重畳する領域に島状のシリコン層313の側面と接する絶縁層を設ければよい。もちろん、導電層314及びシリコン層313が重畳する領域及びその近傍に、島状のシリコン層313の側面と接する絶縁層を設けてよい。40

【0088】

シリコン層313には、チャネル形成領域と、LDD領域として機能する一対の低濃度不純物領域317と、ソース領域又はドレイン領域として機能する一対の高濃度不純物領域318が形成されている。チャネル形成領域は、導電層314と略一致する領域のシリコン層313に形成されており、一対の高濃度不純物領域318の間に位置する。また、チャネル形成領域と高濃度不純物領域318の間に、低濃度不純物領域317が形成されている。

【0089】

次に、図4(A)に示す半導体装置の作製方法について説明する。ここでは、図4(A)50

) における破線O - P 間の断面図、及び破線Q - R 間の断面図を用いて、具体的に説明する。

【0090】

まず、支持基板300 上に絶縁層302、第1のシリコン層306 が順に積層形成されたSOI基板305 を準備する(図4 (B1)、(B2) 参照)。次に、第1のシリコン層306 を覆うように第1の絶縁層308 を形成する(図4 (C1)、(C2) 参照)。なお、第1の絶縁層308 を形成するまでは、上記実施の形態1で示したSOI基板105、絶縁層107 の説明に準じるため、簡略して説明する。

【0091】

SOI基板305 は、SIMOX基板や貼り合わせ基板等の公知のSOI基板を用いることができる。SOI基板305 の表面シリコン層を選択的にエッチングして、島状の第1のシリコン層306 を形成する。第1のシリコン層306 の膜厚は、10nm乃至150nm、好ましくは30nm乃至100nm又は10nm乃至30nmの範囲で形成するといい。また、第1のシリコン層306 の端部は垂直形状となるように形成してもよいし、端部がテーパ形状となるように形成してもよい。本実施の形態では、テーパ角が45°以上95°未満、より好ましくはテーパ角が60°以上95°未満と垂直形状に近くなるように形成する。第1のシリコン層306 の端部のテーパを急峻にすることで、後に完成する半導体装置の寄生チャネルを低減することができる。なお、本発明は特に限定されず、第1のシリコン層306 の端部をテーパ角が30°以上85°未満、又は45°以上60°未満の緩やかなテーパ形状としてもよい。

10

【0092】

第1の絶縁層308 は、CVD法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化アルミニウム、SiOF、SiOC、DLC、ポーラスシリカ等の材料を用いて形成する。また、第1の絶縁層308 は、少なくとも第1のシリコン層306 の端部を十分に被覆できる膜厚で形成する。第1の絶縁層308 は、第1のシリコン層306 と比較して1.5倍乃至3倍の膜厚で形成するのが好ましい。

20

【0093】

また、第1の絶縁層308 は、後にシリコン層の一表面上に形成する絶縁層312 と比較して誘電率が小さい材料を用いて形成するのが好ましい。第1の絶縁層308 は、後に完成する半導体装置においてシリコン層の側面と接する領域のゲート絶縁層を形成する。シリコン層を島状に形成した場合は、シリコン層の端部、特にコーナー部(角部)において電界が集中しやすい。シリコン層の端部に電界が集中すると、ゲート絶縁層の絶縁破壊やリーク電流の発生等の絶縁不良が起きやすくなる。そのため、シリコン層の側面と接する第1の絶縁層308 を、後にシリコン層の一表面上に形成する絶縁層と比較して低い誘電率材料を用いて形成することで、局所的に過度な電界等のストレスがゲート絶縁層に加わることを防止できるため好ましい。

30

【0094】

次に、第1の絶縁層308 を、垂直方向を主体とした異方性エッチングを行うことにより選択的にエッチングして、第1のシリコン層306 の側面と接する第2の絶縁層310 を形成する。このとき、第1のシリコン層306 の上層部が非晶質化して非晶質領域311 が形成される(図5 (A1)、(A2) 参照)。

40

【0095】

例えば、第1の絶縁層308 として窒化酸化シリコン層を形成する。絶縁層302 は酸化シリコン層とし、第1のシリコン層306 は単結晶シリコン層とする。次に、垂直方向を主体とした異方性のドライエッチングで第1の絶縁層308 をエッチングしていく。エッチングは、第1のシリコン層306 の一表面上及び絶縁層302 の一表面上に形成されている第1の絶縁層308 から進行していく。なお、第1のシリコン層306 の一表面上及び絶縁層302 上には、ほぼ同じ膜厚で第1の絶縁層308 が形成されている。よって、第1のシリコン層306 の一表面が露出したところでエッチングを停止させることによ

50

り、第1のシリコン層306の側面と接する領域及びその付近のみに第1の絶縁層308を残すことができる。残存する第1の絶縁層308は、第2の絶縁層310に相当する。なお、第1のシリコン層306の端部を垂直形状に近い形状とする場合は、第1のシリコン層306の側面と接する領域及びその付近のみに、第2の絶縁層310を容易に形成することができる。また、本実施の形態では、第2の絶縁層310は、第1のシリコン層306と比較して、底面(絶縁層302と接する面)からの垂直方向の高さが略一致するように形成する。また、第2の絶縁層310は、第1のシリコン層306の側面と接しない面を、第1のシリコン層306の側面に対して凸形状に湾曲するように形成している。もちろん、本発明は特に限定されず、第2の絶縁層310は丸みを帯びた形状でなく、角を有する形状としてもよい。好ましくは、第2の絶縁層310のコーナー部を緩やかな形状とすることで、上層に積層される層(ここでは、絶縁層312)の被覆性を良好にすることができる。

#### 【0096】

第1の絶縁層308のエッティング方法は、垂直方向を主体とした異方性エッティングを行えるものであれば特に限定されない。例えば、平行平板方式、マグネットロン方式、2周波方式、E C R方式、ヘリコン方式、又はI C P方式などの反応性イオンエッティングを用いることができる。エッティングガスは、第1の絶縁層308と、それ以外の層(第1のシリコン層306)とでエッティング選択比が高く取れるものを適宜選択すればよい。例えば、 $\text{CHF}_3$ 、 $\text{CF}_4$ 、 $\text{C}_4\text{F}_8$ 、 $\text{C}_2\text{F}_6$ 、 $\text{NF}_3$ 等のフッ素系のガスを用いることにより、絶縁層を選択的にエッティングすることが可能である。その他、 $\text{He}$ や $\text{Ar}$ や $\text{Xe}$ などの不活性ガス、又は $\text{O}_2$ ガス、 $\text{H}_2$ ガスを適宜加えてもよい。なお、エッティング条件を適宜変更することにより、第2の絶縁層310の形状を制御することができる。本実施の形態では、第1の絶縁層308のエッティングは、I C P方式の反応性イオンエッティングにより、エッティングガスとして $\text{CHF}_3$ ガスおよび $\text{He}$ ガスを用いて行う。

#### 【0097】

非晶質領域311は、第1の絶縁層308を異方性ドライエッティングする際に、プラズマ等のエネルギーの影響により第1のシリコン層306の上層部が非晶質化されて形成される。非晶質領域311は、第1のシリコン層306の膜厚や第1の絶縁層308を形成する材料、又は第1の絶縁層308のエッティング条件等を制御することにより形成することができる。非晶質領域311は、第1のシリコン層306の0.2倍乃至0.6倍、好ましくは0.3乃至0.5倍程度の膜厚となるように形成する。なお、非晶質領域311は、第1のシリコン層306の一表面上から底面(絶縁層302と接する面)に向かって形成される。

#### 【0098】

次に、第1のシリコン層306の上層部に形成された非晶質領域311を選択的にエッティングして、第2のシリコン層313を形成する。次に、第2の絶縁層310及び第2のシリコン層313を覆うように第3の絶縁層312を形成する(図5(B1)、(B2)参照)。

#### 【0099】

第2のシリコン層313は、第1のシリコン層306の上層部に形成された非晶質領域311を選択的にエッティングすることで形成される。第1のシリコン層306は単結晶シリコンであり、当該第1のシリコン層306は、第1の絶縁層308のエッティングにより第2の絶縁層310を形成する際に、上層部が非晶質化されて非晶質シリコン層が形成される。このとき形成される非晶質シリコン層は、本実施の形態の非晶質領域311に相当する。よって、非晶質領域311である非晶質シリコン層を選択的にエッティングすることで、第2のシリコン層313として単結晶シリコン層が残存する。なお、第2のシリコン層313は、端部のテーパ角が45°以上95°未満、より好ましくはテーパ角が60°以上95°未満と垂直形状に近くなるように形成するとよい。また、第1のシリコン層306の側面と接して形成された第2の絶縁層310は、非晶質領域311のエッティング後もそのまま残存し、第2のシリコン層313に対して凸状に突き出た状態となる。

10

20

30

40

50

## 【0100】

非晶質領域311のエッチング方法は、非晶質領域311とその他の絶縁層（例えば、第2の絶縁層310、絶縁層302）とのエッチング選択比が高く取れるものであれば、特に限定されない。なお、非晶質シリコン層と単結晶シリコン層とはエッチング選択比が低いため、予め非晶質領域311の膜厚をある程度制御して形成し、非晶質領域311が形成されていると推定される深さまで、第1のシリコン層306を垂直方向にエッチングする。エッチング方法としては、例えば、平行平板方式、マグネットロン方式、2周波方式、E C R方式、ヘリコン方式、I C P方式などの反応性イオンエッチングを用いることができる。このとき適用するエッチングガスは、非晶質領域311とその他の絶縁層とのエッチング選択比を高く取れるものであればよい。例えば、C<sub>1</sub><sub>2</sub>等の塩素系のガス、又はHBrガスを用いることができる。また、HBrガス及びC<sub>1</sub><sub>2</sub>ガスの混合ガスを用いてもよい。その他、HeやArなどの不活性ガスを適宜加えてよい。本実施の形態では、エッチングガスとしてC<sub>1</sub><sub>2</sub>ガスを用いて、非晶質領域311を選択的にエッチングする。

## 【0101】

第3の絶縁層312は、CVD法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化アルミニウム等の材料を用いて形成する。第3の絶縁層312は、これらの材料のうち1つ又は複数を用いて、単層構造又は積層構造で形成する。また、第3の絶縁層312は、実施の形態1で示したような高密度プラズマ処理による第2のシリコン層313、或いは第2のシリコン層313及び第2の絶縁層310の固相酸化若しくは固相窒化で形成することもできる。第3の絶縁層312は、膜厚1nm乃至50nm、好ましくは膜厚1nm乃至20nm、より好ましくは1nm乃至10nmの範囲で形成する。

## 【0102】

以上までで形成される第2の絶縁層310及び第3の絶縁層312は、ゲート絶縁層として機能する。すなわち、本発明に係るゲート絶縁層は、一体物ではなく複数の絶縁層の複合物で形成される。このように、シリコン層の側面と接する第2の絶縁層310を形成することで、シリコン層の端部においてゲート絶縁層の被覆性を良好にすることができる。例えば、シリコン層を島状に加工する際のエッチングや様々な工程に付随するフッ酸等を用いた洗浄により、シリコン層の端部下及びその付近の絶縁層（支持基板上の絶縁層）が除去された場合でも、シリコン層を十分に被覆することができる。よって、シリコン層の端部におけるゲート絶縁層の被覆不良に起因したシリコン層とゲート電極層の短絡、リーケ電流の発生、静電破壊等を防止することができる。

## 【0103】

なお、第2の絶縁層310及び第3の絶縁層312で構成されるゲート絶縁層は、第2のシリコン層313の一表面上に形成された領域と比較して、第2のシリコン層313の側面と接する領域の膜厚が厚いことが好ましい。例えば、第2のシリコン層313の一表面上からの垂直線とゲート絶縁層の最表面との交点までの距離を膜厚t<sub>1</sub>とする。第2のシリコン層313の側面からの垂直線とゲート絶縁層の最表面との交点までの距離を膜厚t<sub>2</sub>とする。ゲート絶縁層は、膜厚t<sub>1</sub> < 膜厚t<sub>2</sub>を満たすことが好ましい。第2のシリコン層313の側面と接する領域の膜厚は一定値であるとは限らないが、この場合は、膜厚t<sub>1</sub>と比較して、膜厚t<sub>2</sub>の最小値が同じ、或いは膜厚t<sub>1</sub>より大きいことが好ましい。このようにすることで、シリコン層の端部をゲート絶縁層により十分に被覆することができる。

## 【0104】

また、第2の絶縁層310及び第3の絶縁層312で構成されるゲート絶縁層は、第2のシリコン層313の一表面上に形成された領域と比較して、第2のシリコン層313の側面と接する領域の誘電率が小さいことが好ましい。例えば、第3の絶縁層312と比較して、第2の絶縁層310の誘電率を小さくすることで、第2のシリコン層313の側面と接する領域のゲート絶縁層の誘電率を小さくすることができる。好ましくは、第2の絶

縁層 310 を誘電率 4 以下の低誘電率材料を用いて形成するとよい。ゲート絶縁層において、シリコン層の一表面上と比較して、シリコン層の側面と接する領域の誘電率を小さくすることで、シリコン層の端部に電界が集中することを防止でき、ゲート絶縁層の絶縁不良を低減することができるため好ましい。

【0105】

次に、第3の絶縁層 312 を介して第2のシリコン層 313 上にゲート電極として機能する導電層 314 を形成する。導電層 314 をマスクとして第2のシリコン層 313 に一導電型を付与する不純物元素を添加する。このとき第2のシリコン層 313 に形成される不純物領域は、後に形成する LDD 領域の一部を構成する。

【0106】

次に、導電層 314 の側面と接する絶縁層 315 を形成する。そして、絶縁層 315 及び導電層 314 をマスクとして、一導電型を付与する不純物元素を添加して、チャネル形成領域 316 、 LDD 領域として機能する低濃度不純物領域 317 、ソース領域又はドレイン領域として機能する高濃度不純物領域 318 を形成する（図 5 (C1) 、 (C2) 参照）。

【0107】

導電層 314 は、タンタル (Ta) 、タンゲステン (W) 、チタン (Ti) 、モリブデン (Mo) 、クロム (Cr) 、アルミニウム (Al) 、銅 (Cu) 、又はニオブ (Nb) 等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて形成することができる。また、リン等の一導電型を付与する不純物元素が添加された多結晶シリコンに代表される半導体材料を用いて形成することもできる。導電層 314 は、これらの材料を用いて CVD 法やスパッタリング法により全面に形成した後、選択的にエッチングして所望の形状に加工すればよい。また、導電層 314 は、単層構造又は積層構造で形成すればよく、膜厚 100 nm 乃至 1000 nm 、好ましくは膜厚 200 nm 乃至 800 nm 、より好ましくは 300 nm 乃至 500 nm の範囲で形成する。

【0108】

絶縁層 315 は、 CVD 法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の無機材料、有機樹脂などの有機材料を用いて、単層構造又は積層構造の絶縁層を形成する。当該絶縁層を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、導電層 314 の側面と接する絶縁層 315 を形成することができる。絶縁層 315 は、サイドウォールともいわれる。ここでは、絶縁層 315 は、導電層 314 の側面と接しない面を湾曲状に形成している。具体的には、任意の曲率を有し、接する導電層 314 の側面に対して凸形状に湾曲するように形成している。もちろん、本発明は特に限定されず、絶縁層 315 は丸みを帯びた形状でなく、角を有する形状としてもよい。なお、絶縁層 315 は、 LDD 領域を形成する際のドーピング用マスクとしても機能する。

【0109】

第2のシリコン層 313 には、チャネル形成領域 316 、低濃度不純物領域 317 、高濃度不純物領域 318 が形成されている。チャネル形成領域 316 は、第3の絶縁層 312 を介して導電層 314 と略一致する領域に形成される。低濃度不純物領域 317 は、第3の絶縁層 312 を介して絶縁層 315 と略一致する領域に形成され、且つ高濃度不純物領域 318 とチャネル形成領域 316 の間に形成される。なお、低濃度不純物領域 317 は、必ずしも設ける必要はない。

【0110】

高濃度不純物領域 318 は、低濃度不純物領域 317 と比較して、高い濃度で不純物元素が添加されている。一導電型を付与する不純物元素としては、リン (P) やヒ素 (As) 等の n 型を付与する不純物元素、ボロン (B) やアルミニウム (Al) やガリウム (Ga) 等の p 型を付与する不純物元素を用いることができる。

【0111】

以上により、本発明を適用した薄膜トランジスタ 320 を形成することができる。

10

20

30

40

50

## 【0112】

また、第2のシリコン層313に一導電型を付与する不純物元素を添加した後、熱処理を行うことにより、添加した不純物元素を活性化することができる。熱処理は、レーザビームの照射、又はR T A若しくはファーネスアニール炉を用いて行うことができる。具体的には400乃至700、好ましくは500乃至550の温度範囲で熱処理を行うとよい。また、熱処理は窒素雰囲気下で行うことが好ましい。例えば、5504時間の加熱を行うことにより、活性化を行うことができる。また、第2のシリコン層313の一部に非晶質領域がある場合には、熱処理を行うことにより、不純物元素の活性化とともにシリコン層の再結晶化を行うこともできる。

## 【0113】

10

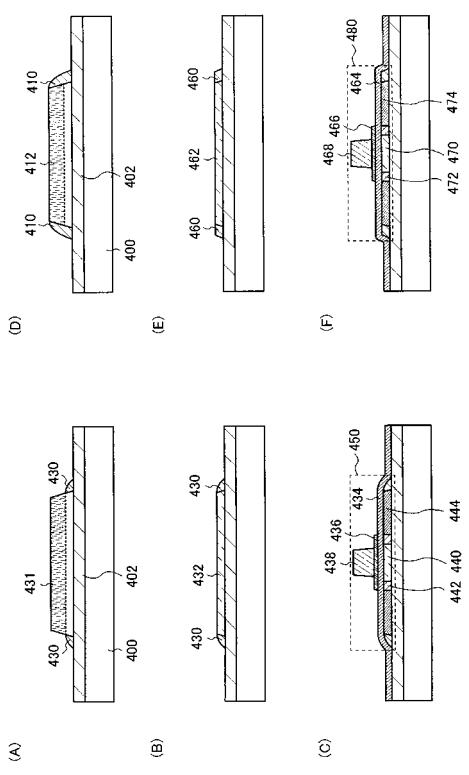

また、図6(A)乃至(C)、又は図6(D)乃至(F)に示すような作製方法を用いてTFTを作製することもできる。なお、支持基板300上に絶縁層302、島状の第1のシリコン層306が順に積層形成されたSOI基板305を用い、当該シリコン層306上に第1の絶縁層308を形成するまでは図4(B1)、(C1)と同じ方法であるため、説明は省略する。

## 【0114】

まず、図6(A)乃至(C)に示す作製方法について説明する。第1のシリコン層306上に第1の絶縁層308を形成した後(図4(C1)参照)、第1の絶縁層308を、垂直方向を主体とした異方性エッチングを行うことにより選択的にエッチングし、シリコン層306の側面と接する第2の絶縁層330を形成する。第1のシリコン層306の上層部は、非晶質化され非晶質領域331が形成される(図6(A)参照)。このとき、第1のシリコン層306の側面と接する第2の絶縁層330が、第1のシリコン層306と比較して、底面(絶縁層302と接する面)からの垂直方向の高さが低くなるように、エッチング条件を制御する。好ましくは、第2の絶縁層330の底面からの垂直方向の高さが、第1のシリコン層306における底面から非晶質領域331までの高さと略一致するように形成するとよい。

20

## 【0115】

第2の絶縁層330は、エッチングガスとして用いるガス種及びガス流量比等のエッチング条件を変更して所望の形状に加工することができる。例えば、第1の絶縁層308とその他の層(第1のシリコン層306)のエッチング選択比を高くし、選択的に第1の絶縁層308のエッチングが進行するようにすることで、第1のシリコン層306と比較して、第2の絶縁層330の底面から垂直方向の高さを低く形成することができる。つまり、非晶質領域331及び第2の絶縁層330が接しないようにすることも可能である。

30

## 【0116】

次に、第1のシリコン層306の上層部に形成された非晶質領域331を選択的にエッチングして、第2のシリコン層332を形成する(図6(B)参照)。なお、非晶質領域331は、単結晶シリコン層である第1のシリコン層306とのエッチングの選択比が低いため、予め非晶質領域331の膜厚をある程度制御して形成し、非晶質領域331が形成されていると推定される深さまで、第1のシリコン層306を垂直方向にエッチングする。ここでは、第2の絶縁層330は、非晶質領域331と接しないように形成している。そのため、非晶質領域331のエッチング後に、第2の絶縁層330が凸状に突き出た状態とならないようにすることができる。

40

## 【0117】

次に、第2のシリコン層332及び第2の絶縁層330上に第3の絶縁層334を形成する。第2の絶縁層330及び第3の絶縁層334は、ゲート絶縁層として機能する。次に、第3の絶縁層334を介して第2のシリコン層332上にゲート電極として機能する導電層336を形成する。導電層336をマスクとして第2のシリコン層332に一導電型を付与する不純物元素を添加する。このとき第2のシリコン層332に形成される不純物領域は、後に形成するLDD領域の一部を構成する。次に、導電層336の側面と接する絶縁層338を形成する。そして、絶縁層338及び導電層336をマスクとして、一

50

導電型を付与する不純物元素を添加して、チャネル形成領域 340、LDD 領域として機能する低濃度不純物領域 342、ソース領域又はドレイン領域として機能する高濃度不純物領域 344 を形成する。以上により、TFT350 を形成することができる（図 6（C）参照）。なお、第 3 の絶縁層 334 形成から導電層 336 及び絶縁層 338 を形成し、第 2 のシリコン層にチャネル形成領域 340、低濃度不純物領域 342、高濃度不純物領域 344 を形成するまでの方法は、図 5（B1）、（C1）と同様であるので、説明は省略する。

#### 【0118】

次に、図 6（D）乃至（F）に示す作製方法について説明する。第 1 のシリコン層 306 上に第 1 の絶縁層 308 を形成した後（図 4（C1）参照）、第 1 の絶縁層 308 を、垂直方向を主体とした異方性エッティングを行うことにより選択的にエッティングし、第 1 のシリコン層 306 の側面と接する第 2 の絶縁層 310 を形成する。第 1 のシリコン層 306 の上層部は、非晶質化して非晶質領域 311 が形成される（図 5（A1）、図 6（D）参照）。

10

#### 【0119】

次に、第 1 のシリコン層 306 の上層部に形成された非晶質領域 311 及び第 2 の絶縁層 310 を、垂直方向を主体とした異方性エッティングにより選択的にエッティングして、第 2 のシリコン層 362 及び第 3 の絶縁層 360 を形成する（図 6（E）参照）。非晶質領域 311 及び第 2 の絶縁層 310 は、エッティング選択比を極力小さくした条件、つまりエッティング選択比が 1 に近くなる条件でエッティングする。このようにすることで、エッティングにより形成される第 2 のシリコン層 362 及び第 3 の絶縁層 360 は、底面（絶縁層 302 と接する面）からの垂直方向の高さを略一致させることができる。

20

#### 【0120】

次に、第 2 のシリコン層 362 及び第 3 の絶縁層 360 を覆うように第 4 の絶縁層 364 を形成する。第 3 の絶縁層 360 及び第 4 の絶縁層 364 は、ゲート絶縁層として機能する。次に、第 4 の絶縁層 364 を介して第 2 のシリコン層 362 上にゲート電極として機能する導電層 366 を形成する。導電層 366 をマスクとして第 2 のシリコン層 362 に一導電型を付与する不純物元素を添加する。このとき第 2 のシリコン層 362 に形成される不純物領域は、後に形成する LDD 領域の一部を構成する。次に、導電層 366 の側面と接する絶縁層 368 を形成する。そして、絶縁層 368 及び導電層 366 をマスクとして、一導電型を付与する不純物元素を添加して、チャネル形成領域 370、LDD 領域として機能する低濃度不純物領域 372、ソース領域又はドレイン領域として機能する高濃度不純物領域 374 を形成する。以上により、TFT380 を形成することができる（図 6（F）参照）。第 4 の絶縁層 364 形成から導電層 366 及び絶縁層 368 を形成し、第 2 のシリコン層にチャネル形成領域 370、低濃度不純物領域 372、高濃度不純物領域 374 を形成するまでの方法は、図 5（B1）、（C1）と同様であるので、説明は省略する。なお、第 4 の絶縁層 364 は、第 3 の絶縁層 312 に相当する。

30

#### 【0121】

以上により、本発明を適用した薄膜トランジスタ 320、350、380 を形成することができる。なお、本実施の形態で示した TFT の構造は一例であり、図示した構造に限定されるものではない。例えば、直列に接続された少なくとも 2 つ以上のチャネル形成領域を含んだシリコン層と、それぞれのチャネル形成領域に電界を印加する少なくとも 2 つ以上のゲート電極層と、を有するマルチゲート構造を用いてもよい。その他、TFT のシリコン層に LDD 領域を形成してもよい。

40

#### 【0122】

また、本実施の形態ではゲート電極として機能する導電層の側面と接して絶縁層を形成し、シリコン層に LDD 領域を形成する例を説明したが、本発明は特に限定されるものではない。実施の形態 1 で示したような構成としてもよいし、ゲート電極の側面をテーパ形状にしてもよい。また、ゲート電極を 2 層の導電層の積層構造とし、各層でテーパ角度が異なるようにしてもよい。

50

## 【0123】

本発明を適用して作製した半導体装置は、シリコン層の端部に起因する不良を防止することができる。特に、シリコン層の端部におけるゲート絶縁層の被覆不良、シリコン層の端部における電界集中等によるゲート絶縁層の絶縁破壊、静電破壊、リーク電流の発生等の不良を防止、低減することが可能である。よって、信頼性の高い半導体装置を作製することができる。また、本発明を適用することで、半導体装置を歩留まり良く製造することも可能になる。

## 【0124】

なお、本実施の形態は、本明細書で示す他の実施の形態と、適宜組み合わせができる。

10

## 【0125】

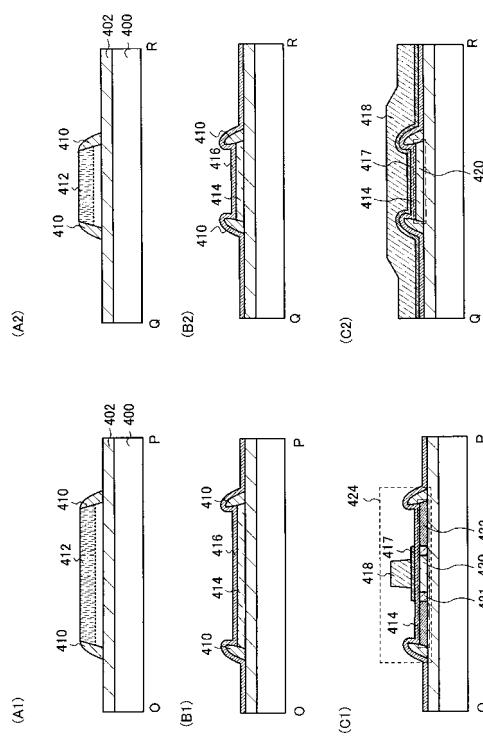

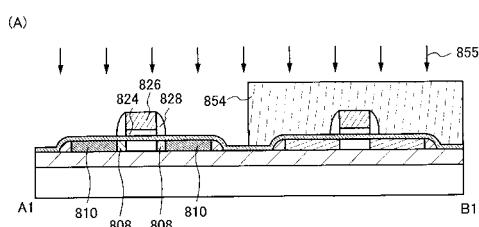

## (実施の形態3)

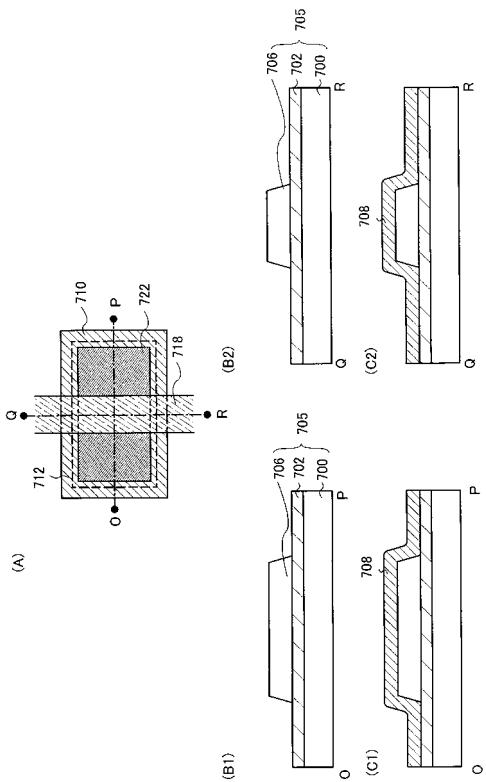

本実施の形態では、上記実施の形態と異なる作製方法で半導体装置を作製する例について、図7乃至図9を用いて説明する。

## 【0126】

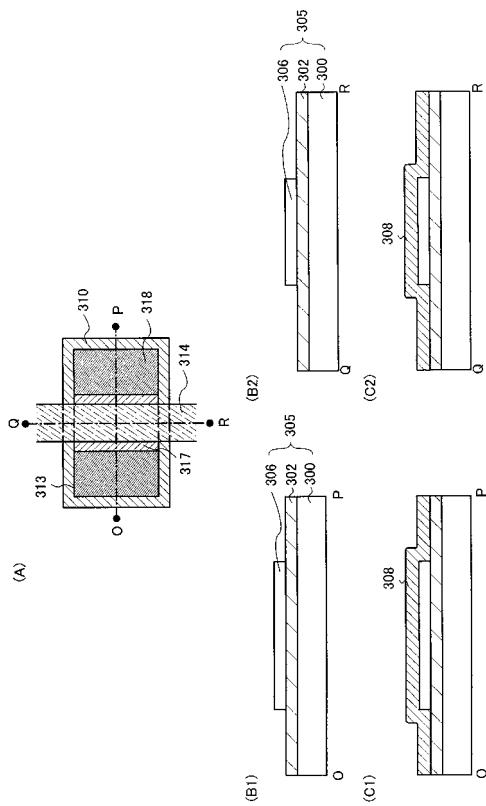

図7(A)は、本発明に係る半導体装置の主要な構成を説明するための上面図である。なお、図7(A)は、一部薄膜等を省略している。

## 【0127】

図7(A)に示す半導体装置は、SOI基板を用いて薄膜トランジスタが形成されている。SOI基板の表面シリコン層414は島状に形成されており、島状のシリコン層414を横断するように、ゲート電極を形成する導電層417、導電層418が設けられている。また、島状のシリコン層414の側面と接して絶縁層410が設けられている。ここでは、島状のシリコン層414の全周囲を囲うように絶縁層410を設ける例を図示しているが、少なくとも導電層417、418及びシリコン層414が重畳する領域に島状のシリコン層414の側面と接する絶縁層を設ければよい。もちろん、導電層417、418及びシリコン層414が重畳する領域及びその近傍に、島状のシリコン層414の側面と接する絶縁層を設けてもよい。

20

## 【0128】

シリコン層414には、チャネル形成領域と、LDD領域として機能する一対の低濃度不純物領域と、ソース領域又はドレイン領域として機能する一対の高濃度不純物領域422が形成されている。チャネル形成領域は、導電層418と略一致する領域のシリコン層414に形成されており、一対の高濃度不純物領域422の間に位置する。また、チャネル形成領域と高濃度不純物領域422との間で、導電層417と重なり導電層418とは重ならない領域のシリコン層414に低濃度不純物領域が形成されている。

30

## 【0129】

次に、図7(A)に示す半導体装置の作製方法について説明する。ここでは、図7(A)における破線O-P間の断面図、及び破線Q-R間の断面図を用いて、具体的に説明する。

## 【0130】

まず、支持基板400上に絶縁層402、第1のシリコン層406が順に積層形成されたSOI基板405を準備する(図7(B1)、(B2)参照)。次に、第1のシリコン層406を覆うように第1の絶縁層408を形成する(図7(C1)、(C2)参照)。なお、第1の絶縁層408を形成するまでは、上記実施の形態1で示したSOI基板105、絶縁層107の説明に準じるため、簡略して以下に説明する。

40

## 【0131】

SOI基板405は、SIMOX基板や貼り合わせ基板等の公知のSOI基板を用いることができる。SOI基板405の表面シリコン層を選択的にエッチングして、島状の第1のシリコン層406を形成する。第1のシリコン層406の膜厚は、10nm乃至150nm、好ましくは30nm乃至100nmの範囲で形成するとよい。また、第1のシリコン層406の端部は垂直形状となるように形成してもよいし、端部がテーパ形状となる

50

ように形成してもよい。本実施の形態では、第1のシリコン層406の端部をテーパ角が30°以上85°未満、又は45°以上60°未満の緩やかなテーパ形状となるように形成する。第1のシリコン層406の端部をテーパ形状としてコーナー部(角部)を緩やかにすることにより、該コーナー部に電界が集中することを緩和することができる。なお、本発明は特に限定されず、上記実施の形態で示すように、テーパ角が45°以上95°未満、より好ましくはテーパ角が60°以上95°未満と垂直形状に近くなるように形成してもよい。

#### 【0132】

第1の絶縁層408は、CVD法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、SiOF、SiOC、DLC、ポーラスシリカ等の材料を用いて形成する。また、第1の絶縁層408は、少なくとも第1のシリコン層406の端部を十分に被覆できる膜厚で形成する。好ましくは、下層の第1のシリコン層406と比較して1.5倍乃至3倍の膜厚で形成する。なお、第1の絶縁層408は、後にシリコン層の一表面上に形成する絶縁層416と比較して誘電率が小さい材料を用いて形成するのが好ましい。第1の絶縁層408は、後に完成する半導体装置においてゲート絶縁層の一部を形成し、具体的にはシリコン層の側面と接する領域のゲート絶縁層の一部となる。シリコン層を島状に形成した場合は、シリコン層の端部、特にコーナー部(角部)において電界が集中しやすい。電界が集中すると、ゲート絶縁層に絶縁破壊等の絶縁不良が生じる恐れが大きくなる。そのため、シリコン層の側面と接する第1の絶縁層408を、後にシリコン層の一表面上に形成する絶縁層と比較して低い誘電率材料を用いて形成することで、シリコン層の端部に掛かる電界を緩和させることができると好ましい。

#### 【0133】

次に、第1の絶縁層408を、垂直方向を主体とした異方性エッチングを行うことにより選択的にエッチングして、第1のシリコン層406の側面と接する第2の絶縁層410を形成する。このとき、第1のシリコン層406の上層部が非晶質化して非晶質領域412が形成される(図8(A1)、(A2)参照)。

#### 【0134】

例えば、第1の絶縁層408として窒化酸化シリコン層を形成する。また、絶縁層402は酸化シリコン層、第1のシリコン層406は単結晶シリコン層であるものとする。次に、垂直方向を主体とした異方性のドライエッチングで第1の絶縁層408をエッチングしていく。エッチングは、第1のシリコン層406の一表面上及び絶縁層402の一表面上に形成されている第1の絶縁層408から進行していく。なお、第1のシリコン層406及び絶縁層402上には、ほぼ同じ膜厚で第1の絶縁層408が形成されている。よって、第1のシリコン層406の一表面が露出したところでエッチングを停止させることにより、第1のシリコン層406の側面と接する領域及びその付近のみに第1の絶縁層408は残る。残存する第1の絶縁層408が第2の絶縁層410に相当する。

#### 【0135】

第1の絶縁層408のエッチング方法は、垂直方向を主体とした異方性エッチングを行えるものであれば特に限定されない。例えば、平行平板方式、マグネットロン方式、2周波方式、ECR方式、ヘリコン方式、又はICP方式などの反応性イオンエッチングを用いることができる。エッチングガスは、第1の絶縁層408と、それ以外の層(第1のシリコン層406)とでエッチング選択比が高く取れるものを適宜選択すればよい。例えば、CHF<sub>3</sub>、CF<sub>4</sub>、C<sub>4</sub>F<sub>8</sub>、C<sub>2</sub>F<sub>6</sub>、NF<sub>3</sub>等のフッ素系のガスを用いることにより、絶縁層を選択的にエッチングすることが可能である。その他、HeやArやXeなどの不活性ガス、又はO<sub>2</sub>ガス、H<sub>2</sub>ガスを適宜加えてもよい。ここでは、ICP方式の反応性イオンエッチングにより、エッチングガスとしてCHF<sub>3</sub>ガスおよびHeガスを用いて、第1の絶縁層408をエッチングする。なお、エッチング条件を適宜変更することにより、第2の絶縁層410の形状を制御することができる。本実施の形態では、第1のシリコン層406と比較して、底面(絶縁層402と接する面)からの垂直方向の高さが略一

10

20

30

40

50

致するように、第2の絶縁層410を形成する。また、第2の絶縁層410は、シリコン層の側面と接しない面を湾曲状に形成している。具体的には、任意の曲率を有し、接するシリコン層の側面に対して凸形状に湾曲するように形成している。もちろん、本発明は特に限定されず、第2の絶縁層410は丸みを帯びた形状でなく、角を有する形状としてもよい。なお、第2の絶縁層410のコーナー部を緩やかな形状とすると、上層に積層される層（ここでは、絶縁層416）の被覆性を良好にすることができるため好ましい。

#### 【0136】

非晶質領域412は、第1の絶縁層408をエッティングする際に、プラズマ等のエネルギーの影響により第1のシリコン層406の上層部が非晶質化されて形成される。非晶質領域412は、第1のシリコン層406の膜厚や第1の絶縁層408を形成する材料、又は第1の絶縁層408をエッティングする条件等を適宜選択することにより、形成することができる。非晶質領域412の膜厚は、第1のシリコン層406の0.2倍乃至0.6倍、好ましくは0.3乃至0.5倍程度となるように形成する。なお、非晶質領域412は、第1のシリコン層406の上面（絶縁層402と接する面と対向する面）から垂直方向に形成される。また、第1のシリコン層406の膜厚も、第2の絶縁層410を形成するためのエッティングの際に非晶質化される領域を考慮して、厚めに形成しておくのが好ましい。

10

#### 【0137】

次に、第1のシリコン層406の上層部に形成された非晶質領域412を選択的にエッティングして、第2のシリコン層414を形成する。なお、非晶質領域412は、単結晶シリコン層である第1のシリコン層406とのエッティングの選択比が低いため、予め非晶質領域412の膜厚をある程度制御して形成し、非晶質領域412が形成されていると推定される深さまで、第1のシリコン層406を垂直方向にエッティングする。次に、第2の絶縁層410及び第2のシリコン層414を覆うように第3の絶縁層416を形成する（図8（B1）（B2）参照）。

20

#### 【0138】

第2のシリコン層414は、第1のシリコン層406の上層部に形成された非晶質領域412を選択的にエッティングすることで形成される。第1のシリコン層406は単結晶シリコンであり、当該第1のシリコン層406は、第1の絶縁層408のエッティングにより第2の絶縁層410を形成する際に、上層部が非晶質化されて非晶質シリコン層が形成される。このとき形成される非晶質シリコン層は、本実施の形態の非晶質領域412に相当する。よって、非晶質領域412である非晶質シリコン層を選択的にエッティングすることで、第2のシリコン層414として単結晶シリコン層が残存する。ここでは第2のシリコン層414は、端部のテーパ角が30°以上85°未満、又はテーパ角が45°以上60°未満の緩やかなテーパ形状となるようにする。なお、本発明は特に限定されず、上記実施の形態で示すように、テーパ角が45°以上95°未満、より好ましくはテーパ角が60°以上95°未満と垂直形状に近くなるように形成してもよい。また、第1のシリコン層406の側面と接して形成された第2の絶縁層410は、非晶質領域412のエッティング後もそのまま残存し、第2のシリコン層414に対して凸状に突き出た状態となる。

30

#### 【0139】

40

本実施の形態では、SOI基板405の表面シリコン層を利用した第1のシリコン層406を膜厚60nmで形成し、当該第1のシリコン層406上に第1の絶縁層408として酸化窒化シリコン層を膜厚200nmで形成した後、垂直方向を主体としたエッティングにより第2の絶縁層410を形成する。エッティングは、ICP方式の反応性イオンエッティングを行う。このとき形成された非晶質領域412を選択的にエッティングして、第2のシリコン層414として単結晶シリコン層を膜厚25nmで形成する。

#### 【0140】

50

第3の絶縁層416は、CVD法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化アルミニウム等の材料を用いて形成する。第3の絶縁層416は、これらの材料のうち1つ又は複数を用いて、単層構造又は積

層構造で形成する。また、第3の絶縁層416は、高密度プラズマ処理による固相酸化若しくは固相窒化で形成することもできる。例えば、第2のシリコン層414及び第2の絶縁層410を、高密度プラズマ処理により酸化又は窒化して、第3の絶縁層416を形成することができる。第3の絶縁層416は、膜厚1nm乃至50nm、好ましくは膜厚1nm乃至20nm、より好ましくは1nm乃至10nmの範囲で形成する。

#### 【0141】

以上までで形成される第2の絶縁層410及び第3の絶縁層416は、ゲート絶縁層として機能する。すなわち、本発明に係るゲート絶縁層は、一体物ではなく複数の絶縁層の複合物で形成される。シリコン層の側面と接する第2の絶縁層410を形成し、さらにシリコン層の一表面上に第3の絶縁層416を形成することで、シリコン層の端部においてゲート絶縁層の被覆性を良好にすることができます。よって、ゲート絶縁層の被覆不良に起因するシリコン層とゲート電極との短絡やリーク電流の発生等を防止することができる。また、ゲート絶縁層の被覆性を良好にすることで、完成するトランジスタ等の素子の静電破壊も防止することができる。

#### 【0142】

なお、第2の絶縁層410及び第3の絶縁層416で形成されるゲート絶縁層は、第2のシリコン層414の一表面上に形成された領域と比較して、第2のシリコン層414の側面と接する領域の膜厚が厚いことが好ましい。例えば、第2のシリコン層414の一表面上からの垂直線とゲート絶縁層の最表面との交点までの距離を膜厚t1とする。第2のシリコン層414の側面からの垂直線とゲート絶縁層の最表面との交点までの距離を膜厚t2とする。ゲート絶縁層は、膜厚t1 < 膜厚t2を満たすことが好ましい。なお、第2のシリコン層414の側面と接する領域の膜厚は一定値であるとは限らないが、この場合は、膜厚t1と比較して、膜厚t2の最小値が同じ、或いは膜厚t1より大きいことが好ましい。このようにゲート絶縁層により第2のシリコン層414の端部を十分に被覆する、好ましくは第2のシリコン層414の側面と接する領域の膜厚を厚くすることで、第2のシリコン層414の端部に掛かる電界を緩和することができ、リーク電流の発生等を防止することができる。

#### 【0143】

また、第2の絶縁層410及び第3の絶縁層416で形成されるゲート絶縁層は、第2のシリコン層414の一表面上に形成された領域と比較して、第2のシリコン層414の側面と接する領域の誘電率が小さいことが好ましい。例えば、第3の絶縁層416と比較して、第2の絶縁層410の誘電率を小さくすることで、第2のシリコン層414の側面と接する領域のゲート絶縁層の誘電率を小さくすることができる。好ましくは、第2の絶縁層410を誘電率4以下の低誘電率材料を用いて形成するとよい。ゲート絶縁層において、シリコン層の一表面上と比較して、シリコン層の側面と接する領域の誘電率を小さくすることで、シリコン層の端部に掛かる電界を緩和させることができ、ゲート絶縁層の絶縁不良を防止することができる。

#### 【0144】

次に、第3の絶縁層416を介して第2のシリコン層414上にゲート電極として機能する導電層417及び導電層418の積層構造を形成する。導電層417、導電層418をマスクとして第2のシリコン層414に一導電型を付与する不純物元素を添加して、チャネル形成領域420、LDD領域として機能する低濃度不純物領域421、ソース領域又はドレイン領域として機能する高濃度不純物領域422を形成する（図8（C1）、（C2）参照）。

#### 【0145】

導電層417、418は、タンタル（Ta）、タンゲステン（W）、チタン（Ti）、モリブデン（Mo）、クロム（Cr）、アルミニウム（Al）、銅（Cu）、又はニオブ（Nb）等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて形成することができる。また、リン等の一導電型を付与する不純物元素が添加された多結晶シリコンに代表される半導体材料を用いて形成することもできる。ゲート電極として機能

10

20

30

40

50

する導電層はこれらの材料のうち 1 つ又は複数を用いて、単層構造又は積層構造で形成することができる。また、膜厚 100 nm 乃至 1000 nm、好ましくは膜厚 200 nm 乃至 800 nm、より好ましくは 300 nm 乃至 500 nm の範囲で形成するとよい。また、ゲート電極として機能する導電層は、上述の材料を用いて CVD 法やスパッタリング法により全面に形成した後、選択的にエッチングして所望の形状に加工すればよい。

#### 【 0146 】

本実施の形態では、ゲート電極として導電層 417、418 の 2 層の積層構造を形成し、各層の側面をテーパ形状とし、さらに各層でテーパ角度が異なるように形成する例を示している。ゲート電極を構成する導電層の側面をテーパ形状にすることで、上層に積層する層の被覆性を向上することができる。

10

#### 【 0147 】

また、本実施の形態では、導電層 417、418 の幅（キャリアがチャネル形成領域を流れる方向（ソース領域とドレイン領域とを結ぶ方向）にほぼ平行な長さ）を異なるように形成している。具体的には、導電層 418 と比較して、導電層 417 の幅が大きくなるように、つまりゲート電極を 2 層の積層構造で形成する場合、下層の導電層の幅が大きくなるように形成している。このように導電層の幅を異なるように形成することで、第 2 のシリコン層 414 に低濃度不純物領域 421、高濃度不純物領域 422 を形成することが容易になる。

#### 【 0148 】

本実施の形態では、第 2 のシリコン層 414 に一導電型を付与する不純物元素を添加する際に、導電層 417 は低濃度不純物領域 421 を形成する際のドーピング用マスクとして機能することができる。導電層 418 は、チャネル形成領域 420 を形成するドーピング用マスクとして機能する。よって、第 3 の絶縁層 416 を介してチャネル形成領域 420 は導電層 418 と略一致する領域に形成され、低濃度不純物領域 421 は、導電層 417 と重なり導電層 418 とは重ならない領域に形成されている。高濃度不純物領域 422 は、導電層 418 及び導電層 417 の両方と重ならない領域に形成されている。なお、低濃度不純物領域は、必ずしも設ける必要はない。

20

#### 【 0149 】

高濃度不純物領域 422 は、低濃度不純物領域 421 と比較して、高い濃度で不純物元素が添加されている。一導電型を付与する不純物元素としては、リン（P）やヒ素（As）等の n 型を付与する不純物元素、ボロン（B）やアルミニウム（Al）やガリウム（Ga）等の p 型を付与する不純物元素を用いることができる。

30

#### 【 0150 】

以上により、本発明を適用した薄膜トランジスタ 424 を形成することができる。

#### 【 0151 】

また、第 2 のシリコン層 414 に一導電型を付与する不純物元素を添加した後、熱処理を行うことにより、添加した不純物元素を活性化することができる。熱処理は、レーザビーム照射、又は R T A 若しくはファーネスアニール炉を用いて行うことができる。具体的には、400 乃至 700、好ましくは 500 乃至 550 の温度範囲で熱処理を行うのが好ましい。また、熱処理は窒素雰囲気下で行うことが好ましい。例えば、550 4 時間の加熱を行うことにより、活性化を行うことができる。また、第 2 のシリコン層 414 の一部に非晶質領域がある場合には、熱処理を行うことにより、不純物元素の活性化とともにシリコン層の再結晶化を行うこともできる。

40

#### 【 0152 】

また、図 9（A）乃至（C）、又は図 9（D）乃至（F）に示すような作製方法を用いて TFT を作製することもできる。なお、SOI 基板 405 の表面シリコン層を島状に加工して第 1 のシリコン層 406 を形成し、当該第 1 のシリコン層 406 上に第 1 の絶縁層 408 を形成するまでは図 7（B1）、（C1）と同じ方法であるため、説明は省略する。なお、図 9 では、図 7（A）の破線 O - P 間の断面図を用いて説明する。

#### 【 0153 】

50

まず、図9(A)乃至(C)に示す作製方法について説明する。第1のシリコン層406上に第1の絶縁層408を形成した後(図7(C1)参照)、第1の絶縁層408を、垂直方向を主体とした異方性エッティングを行うことにより選択的にエッティングし、第1のシリコン層406の側面と接する第2の絶縁層430を形成する。第1のシリコン層406の上面から垂直方向に進んだ領域が非晶質化して非晶質領域431が形成される(図9(A)参照)。このとき、第1のシリコン層406の側面と接する第2の絶縁層430が、第1のシリコン層406と比較して、底面(絶縁層402と接する面)からの垂直方向の高さが低くなるように、エッティング条件を制御する。好ましくは、第2の絶縁層430の底面からの垂直方向の高さが、第1のシリコン層406における底面から非晶質領域431までの高さと略一致するように形成するとよい。つまり、非晶質領域431及び第2の絶縁層430が接しないようにエッティング条件を制御するのが好ましい。

10

#### 【0154】

次に、第1のシリコン層406の上層部に形成された非晶質領域431を選択的にエッティングして、第2のシリコン層432を形成する(図9(B)参照)。第2の絶縁層430は、非晶質領域431と接しないように形成している。そのため、非晶質領域431のエッティング後に、凸状に突き出た状態とならないようにできる。

#### 【0155】

次に、第2のシリコン層432及び第2の絶縁層430上に第3の絶縁層434を形成する。第2の絶縁層430及び第3の絶縁層434は、ゲート絶縁層として機能する。次に、第3の絶縁層434を介して第2のシリコン層432上にゲート電極として機能する導電層436、導電層438の積層構造を形成する。導電層436、導電層438をマスクとして第2のシリコン層432に一導電型を付与する不純物元素を添加して、チャネル形成領域440、LDD領域として機能する低濃度不純物領域442、ソース領域又はドレイン領域として機能する高濃度不純物領域444を形成する。以上により、TFT450を形成することができる(図9(C)参照)。なお、第3の絶縁層434形成から導電層436、438を形成し、第2のシリコン層432にチャネル形成領域440、低濃度不純物領域442、高濃度不純物領域444を形成するまでの方法は、図8(B1)、(C1)と同様であるので、説明は省略する。

20

#### 【0156】

次に、図9(D)乃至(F)に示す作製方法について説明する。第1のシリコン層406上に第1の絶縁層408を形成した後(図7(C1)参照)、第1の絶縁層408を、垂直方向を主体とした異方性エッティングを行うことにより選択的にエッティングし、第1のシリコン層406の側面と接する第2の絶縁層410を形成する。第1のシリコン層406の上面から垂直方向に進んだ領域は、非晶質化して非晶質領域412が形成される(図8(A1)、図9(D)参照)。

30

#### 【0157】

次に、第1のシリコン層406の上層部に形成された非晶質領域412及び第2の絶縁層410を、垂直方向を主体とした異方性エッティングにより選択的にエッティングして、第2のシリコン層462及び第3の絶縁層460を形成する(図9(E)参照)。非晶質領域412及び第2の絶縁層410は、選択比が低い条件、又はエッティング選択比が1に近い条件でエッティングする。つまり、非晶質領域412及び第2の絶縁層410を、ほぼ同じエッティング速度でエッティングしていく。よって、エッティングにより形成される第2のシリコン層462及び第3の絶縁層460は、底面(絶縁層402と接する面)からの垂直方向の高さが略一致する。

40

#### 【0158】

次に、第2のシリコン層462及び第3の絶縁層460上に第4の絶縁層464を形成する。第3の絶縁層460及び第4の絶縁層464は、ゲート絶縁層として機能する。次に、第4の絶縁層464を介して第2のシリコン層462上にゲート電極として機能する導電層466、導電層468を形成する。導電層466、468をマスクとして第2のシリコン層462に一導電型を付与する不純物元素を添加して、チャネル形成領域470、

50

LDD領域として機能する低濃度不純物領域472、ソース領域又はドレイン領域として機能する高濃度不純物領域474を形成する。以上により、TFT480を形成することができる(図9(F)参照)。第4の絶縁層464形成から導電層466、468を形成し、第2のシリコン層462にチャネル形成領域470、低濃度不純物領域472、高濃度不純物領域474を形成するまでの方法は、図8(B1)、(C1)と同様であるので、説明は省略する。なお、第4の絶縁層464は、第3の絶縁層416に相当する。

#### 【0159】

以上により、本発明を適用した薄膜トランジスタ424、450、480を形成することができる。なお、本実施の形態で示したTFTの構造は一例であり、図示した構造に限定されるものではない。例えば、直列に接続された少なくとも2つ以上のチャネル形成領域を含んだシリコン層と、それぞれのチャネル形成領域に電界を印加する少なくとも2つ以上のゲート電極層と、を有するマルチゲート構造を用いてもよい。その他、TFTのシリコン層にLDD領域を形成してもよい。

10

#### 【0160】

また、本実施の形態ではゲート電極として、各層でテーパ角度が異なる2層の導電層の積層構造を形成する例を説明したが、本発明は特に限定されるものではない。ゲート電極は単層の導電層で形成してもよいし、導電層の側面をテーパ形状としてもよい。また、導電層の側面と接するサイドウォールともいわれる絶縁層を形成してもよい。

#### 【0161】

本発明を適用して作製した薄膜トランジスタは、シリコン層の端部に起因する不良を低減させることができる。特に、シリコン層の端部におけるゲート絶縁層の被覆不良を防止することができる。また、シリコン層の端部における電界集中を緩和することができる。よって、シリコン層及びゲート電極の短絡、ゲート絶縁層の絶縁破壊や静電破壊、及びこれらの不良に伴うリーク電流を防止、低減でき、信頼性の高い半導体装置を作製することができる。また、半導体装置を歩留まり良く製造することも可能になる。

20

#### 【0162】

また、本発明を適用することで、シリコン層の端部に起因する不良を低減させるとともに、シリコン層の薄膜化を図ることも可能である。また、シリコン層の薄膜化に伴い生じるシリコン層端部付近の不良も防止することができる。

#### 【0163】

30

なお、本実施の形態は、本明細書で示す他の実施の形態と、適宜組み合わせができる。

#### 【0164】

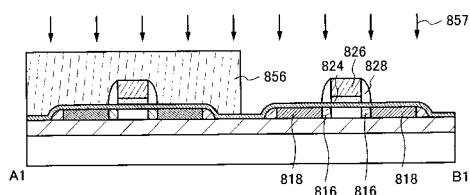

##### (実施の形態4)

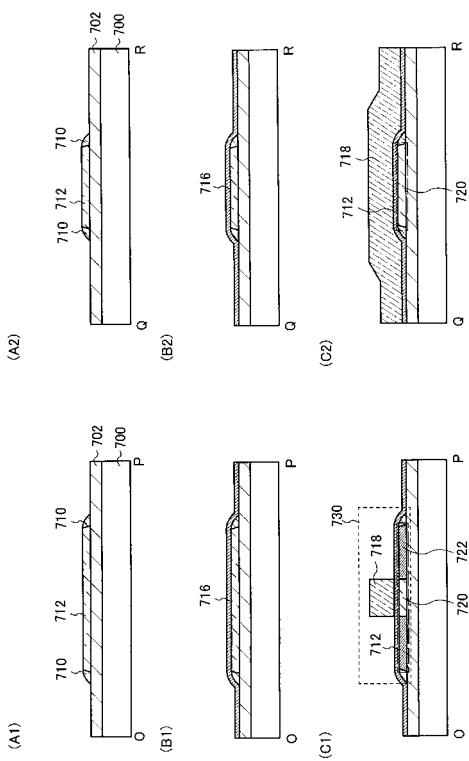

本実施の形態では、上記実施の形態と異なる作製方法で半導体装置を作製する例について、図10、図11を用いて説明する。

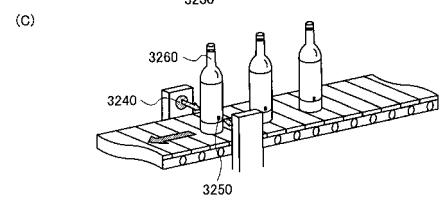

#### 【0165】

図10(A)は、本発明に係る半導体装置の主要な構成を説明するための上面図である。なお、図10(A)は、一部薄膜等を省略している。

#### 【0166】

40

図10(A)に示す半導体装置は、SOI基板を用いて薄膜トランジスタが形成されている。SOI基板の表面シリコン層712は島状に形成されており、島状のシリコン層712を横断するように、ゲート電極を形成する導電層718が設けられている。また、島状のシリコン層712の側面と接して絶縁層710が設けられている。ここでは、島状のシリコン層712の全周囲を囲うように絶縁層710を設ける例を図示しているが、少なくとも導電層718及びシリコン層712が重畠する領域に島状のシリコン層712の側面と接する絶縁層を設ければよい。もちろん、導電層718及びシリコン層712が重畠する領域及びその近傍に、島状のシリコン層712の側面と接する絶縁層を設けてもよい。

#### 【0167】

50

シリコン層 712 には、チャネル形成領域と、ソース領域又はドレイン領域として機能する一対の高濃度不純物領域 722 が形成されている。チャネル形成領域は、導電層 718 と略一致する領域のシリコン層 712 に形成されており、一対の高濃度不純物領域 722 の間に位置する。なお、チャネル形成領域と高濃度不純物領域 722 との間に、LDD 領域として機能する低濃度不純物領域を形成してもよい。

#### 【0168】

次に、図 10 (A) に示す半導体装置の作製方法について説明する。ここでは、図 10 (A) における破線 O - P 間の断面図、及び破線 Q - R 間の断面図を用いて、具体的に説明する。

#### 【0169】

まず、支持基板 700 上に絶縁層 702、島状の第 1 のシリコン層 706 が順に積層形成された SOI 基板 705 を準備する (図 10 (B1)、(B2) 参照)。次に、第 1 のシリコン層 706 を覆うように第 1 の絶縁層 708 を形成する (図 10 (C1)、(C2) 参照)。なお、第 1 の絶縁層 708 を形成するまでは、上記実施の形態 3 で示した SOI 基板 405、第 1 の絶縁層 408 の説明に準じるため、簡略して以下に説明する。

#### 【0170】

SOI 基板 705 は、SIMOX 基板や貼り合わせ基板等の公知の SOI 基板を用いることができる。SOI 基板 705 の表面シリコン層を選択的にエッチングして、島状の第 1 のシリコン層 706 を形成する。第 1 のシリコン層 706 の膜厚は、10 nm 乃至 150 nm、好ましくは 30 nm 乃至 100 nm の範囲で形成する。また、第 1 のシリコン層 706 の端部は垂直形状となるように形成してもよいし、端部がテーパ形状となるように形成してもよい。本実施の形態では、第 1 のシリコン層 706 の端部をテーパ角が 30° 以上 85° 未満、又は 45° 以上 60° 未満の緩やかなテーパ形状となるように形成する。第 1 のシリコン層 706 の端部をテーパ形状としてコーナー部 (角部) を緩やかにすることにより、該コーナー部に電界が集中することを緩和することができる。なお、本発明は特に限定されず、上記実施の形態で示すように、テーパ角が 45° 以上 95° 未満、より好ましくはテーパ角が 60° 以上 95° 未満と垂直形状に近くなるように形成してもよい。

#### 【0171】

第 1 の絶縁層 708 は、CVD 法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、SiOF、SiOC、DLC、ポーラスシリカ等の材料を用いて形成する。また、第 1 の絶縁層 708 は、少なくとも第 1 のシリコン層 706 の端部を十分に被覆できる膜厚で形成する。好ましくは、下層の第 1 のシリコン層 706 と比較して、1.5 倍乃至 3 倍の膜厚で形成するとよい。なお、第 1 の絶縁層 708 は、後にシリコン層の一表面上に形成する第 3 の絶縁層 716 より誘電率が小さい材料を用いて形成するのが好ましい。第 1 の絶縁層 708 は、後に完成する半導体装置においてゲート絶縁層の一部を形成し、具体的にはシリコン層の側面と接する領域のゲート絶縁層の一部となる。第 1 の絶縁層 708 を低誘電率材料を用いて形成することで、シリコン層の端部、特にコーナー部 (角部) における電界や静電気の集中を緩和することができる。その結果、ゲート絶縁層の絶縁破壊や静電破壊等の不良、及びこれらの不良に起因するリーク電流を防止することができる。

#### 【0172】

次に、第 1 の絶縁層 708 及び第 1 のシリコン層 706 を、垂直方向を主体とした異方向エッチングを行うことにより全面エッチングして、第 2 のシリコン層 712 と、当該第 2 のシリコン層 712 の側面と接する第 2 の絶縁層 710 を形成する (図 11 (A1)、(A2) 参照)。

#### 【0173】

第 1 の絶縁層 708 及び第 1 のシリコン層 706 は、エッチング選択比が低い条件、又はエッチング選択比を極力小さくした条件 (エッチング選択比が 1 に近くなる条件) でエッチングする。つまり、第 1 の絶縁層 708 及び第 1 のシリコン層 706 を、ほぼ同じエ

10

20

30

40

50

ツチング速度でエッチングしていく。よって、エッチングにより形成される第2のシリコン層712及び第2の絶縁層710は、底面（絶縁層702と接する面）からの垂直方向の高さが略一致する。

【0174】

第1の絶縁層708及び第1のシリコン層706のエッチング方法は、垂直方向を主体とした異方性エッチングを行えるものであれば特に限定されない。例えば、平行平板方式、マグネットロン方式、2周波方式、E C R方式、ヘリコン方式、又はI C P方式などの反応性イオンエッチングを用いることができる。

【0175】

エッチングガスは、第1の絶縁層708及び第1のシリコン層706のエッチング選択比を極力小さくできるもの、つまりエッチング選択比が1に近くなるものを適宜選択すればよい。例えば、 $\text{CHF}_3$ 、 $\text{CF}_4$ 、 $\text{C}_4\text{F}_8$ 、 $\text{C}_2\text{F}_6$ 、 $\text{NF}_3$ 等のフッ素系のガスに $\text{O}_2$ ガスを適宜加えていくことにより、両者のエッチング選択比を小さくすることが可能である。さらに $\text{He}$ や $\text{Ar}$ などの不活性ガスを適宜加えててもよい。また、エッチングガスとして、フッ素系のガスに代えて $\text{HBr}$ 、又は $\text{HBr}$ と $\text{Cl}_2$ との混合ガスガスを用いてもよい。 $\text{HBr}$ ガスを用いる場合も、 $\text{He}$ や $\text{Ar}$ などの不活性ガスを適宜加えててもよい。

【0176】

なお、第1の絶縁層708及び第1のシリコン層706は、エッチング後の第2のシリコン層712の膜厚が、第1のシリコン層706と比較して0.2倍乃至0.8倍、好ましくは0.4倍乃至0.6倍程度となるようにエッチングして薄膜化する。また、第2のシリコン層712の端部は、テーパ角が30°以上85°未満、又はテーパ角が45°以上60°未満の緩やかなテーパ形状となるようにする。なお、本発明は特に限定されず、上記実施の形態で示すように、テーパ角が45°以上95°未満、より好ましくはテーパ角が60°以上95°未満と垂直形状に近くなるように形成してもよい。

【0177】

次に、第2のシリコン層712及び第2の絶縁層710を覆うように第3の絶縁層716を形成する（図11（B1）、（B2）参照）。

【0178】

第3の絶縁層716は、CVD法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化アルミニウム等の材料を用いて形成する。第3の絶縁層716は、これらの材料のうち1つ又は複数を用いて、単層構造又は積層構造で形成する。また、第3の絶縁層716は、高密度プラズマ処理による固相酸化若しくは固相窒化で形成することもできる。例えば、第2のシリコン層712及び第2の絶縁層710を、高密度プラズマ処理により固相酸化又は固相窒化して、第3の絶縁層716を形成することができる。第3の絶縁層716は、膜厚1nm乃至50nm、好ましくは膜厚1nm乃至20nm、より好ましくは1nm乃至10nmの範囲で形成する。

【0179】

以上までで形成される第2の絶縁層710及び第3の絶縁層716は、ゲート絶縁層として機能する。すなわち、本発明に係るゲート絶縁層は、一体物ではなく複数の絶縁層の複合物で形成される。シリコン層の側面と接する第2の絶縁層710を形成し、さらにシリコン層の一表面上に第3の絶縁層716を形成することで、シリコン層の端部においてゲート絶縁層の被覆性を良好にできる。よって、ゲート絶縁層の被覆不良によりゲート電極を形成する導電層とシリコン層とが短絡することや、静電破壊を防止することができる。

【0180】

なお、第2の絶縁層710及び第3の絶縁層716で形成されるゲート絶縁層は、第2のシリコン層712の一表面上に形成された領域と比較して、第2のシリコン層712の側面と接する領域の膜厚が厚いことが好ましい。例えば、第2のシリコン層712の一表面上からの垂直線とゲート絶縁層の最表面との交点までの距離を膜厚 $t_1$ する。第2のシリコン層712の側面からの垂直線とゲート絶縁層の最表面との交点までの距離を膜厚 $t$

10

20

30

40

50

2とする。ゲート絶縁層は、膜厚  $t_1 < t_2$  を満たすことが好ましい。なお、第2のシリコン層712の側面と接する領域の膜厚は一定値であるとは限らないが、この場合は、膜厚  $t_1$  と比較して、膜厚  $t_2$  の最小値が同じ或いは膜厚  $t_1$  より大きいことが好ましい。このようにすることで、シリコン層の端部をゲート絶縁層により十分に被覆することができる。好ましくは第2のシリコン層712の側面と接する領域のゲート絶縁層の膜厚を厚くすることで、第2のシリコン層712の端部に掛かる電界を緩和することができ、リーク電流の発生等を防止することができる。

#### 【0181】

また、第2の絶縁層710及び第3の絶縁層716で形成されるゲート絶縁層は、第2のシリコン層712の一表面上に形成された領域と比較して、第2のシリコン層712の側面と接する領域の誘電率が小さいことが好ましい。例えば、第3の絶縁層716と比較して、第2の絶縁層710の誘電率を小さくすることで、第2のシリコン層712の側面と接する領域のゲート絶縁層の誘電率を小さくすることができる。好ましくは、第2の絶縁層710を誘電率4以下の低誘電率材料を用いて形成するとよい。ゲート絶縁層において、シリコン層の一表面上と比較して、シリコン層の側面と接する領域の誘電率を小さくすることで、局所的に過度な電界等のストレスがゲート絶縁層に加わることを防止できるため好ましい。

#### 【0182】

次に、第3の絶縁層716を介して第2のシリコン層712上にゲート電極として機能する導電層718を形成する。導電層718をマスクとして第2のシリコン層712に一導電型を付与する不純物元素を添加して、チャネル形成領域720、ソース領域又はドレイン領域として機能する高濃度不純物領域722を形成する(図11(C1)、(C2)参照)。

#### 【0183】

導電層718は、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、アルミニウム(Al)、銅(Cu)、又はニオブ(Nb)等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて形成することができる。また、リン等の一導電型を付与する不純物元素が添加された多結晶シリコンに代表される半導体材料を用いて形成することもできる。ゲート電極として機能する導電層はこれらの材料のうち1つ又は複数を用いて、単層構造又は積層構造で形成することができ、膜厚100nm乃至1000nm、好ましくは膜厚200nm乃至800nm、より好ましくは300nm乃至500nmの範囲で形成するとよい。また、ゲート電極として機能する導電層は、上述の材料を用いてCVD法やスパッタリング法により全面に形成した後、選択的にエッチングして所望の形状に加工すればよい。

#### 【0184】

一導電型を付与する不純物元素としては、リン(P)やヒ素(As)等のn型を付与する不純物元素、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等のp型を付与する不純物元素を用いることができる。

#### 【0185】

以上により、本発明を適用した薄膜トランジスタ730を形成することができる。

#### 【0186】

また、第2のシリコン層712に一導電型を付与する不純物元素を添加した後、熱処理を行うことにより、添加した不純物元素を活性化することができる。熱処理は、レーザビーム照射、又はRTA若しくはファーネスアニール炉を用いて行うことができる。具体的には、400乃至700、好ましくは500乃至550の温度範囲で熱処理を行うのが好ましい。また、熱処理は窒素雰囲気下で行うことが好ましい。例えば、5504時間の加熱を行うことにより、活性化を行うことができる。また、第2のシリコン層712の一部に非晶質領域がある場合には、熱処理を行うことにより、不純物元素の活性化とともにシリコン層の再結晶化を行うこともできる。

#### 【0187】

10

20

30

40

50

なお、本実施の形態で示した TFT の構造は一例であり、図示した構造に限定されるものではない。例えば、直列に接続された少なくとも 2 つ以上のチャネル形成領域を含んだシリコン層と、それぞれのチャネル形成領域に電界を印加する少なくとも 2 つ以上のゲート電極層と、を有するマルチゲート構造を用いてもよい。その他、TFT のシリコン層に LDD 領域を形成してもよい。

【0188】

また、ゲート電極として機能する導電層は、側面をテーパ形状としてもよいし、積層構造として各層でテーパ角度を異ならせてもよい。また、導電層の側面と接するサイドウォールといわれる絶縁層を形成してもよい。

【0189】

本発明を適用して作製した薄膜トランジスタは、シリコン層の端部に起因する不良を低減させることができる。特に、シリコン層の端部におけるゲート絶縁層の被覆性が良好になると、ゲート電極を形成する導電層とシリコン層との短絡、素子の静電破壊等を防止することができる。また、シリコン層の端部における電界の集中を緩和できるため、ゲート絶縁層の絶縁破壊や静電破壊等の絶縁不良を低減することができる。よって、信頼性の高い半導体装置を作製することができる。また、半導体装置を歩留まり良く製造することも可能になる。

【0190】

また、本発明を適用することで、シリコン層の端部に起因する不良を低減させるとともに、シリコン層の薄膜化を図ることもできる。

【0191】

なお、本実施の形態は、本明細書で示す他の実施の形態と、適宜組み合わせができる。

【0192】

(実施の形態 5 )

本実施の形態では、上記実施の形態と異なる作製方法で半導体装置を作製する例について、図 13 乃至図 15 を用いて説明する。

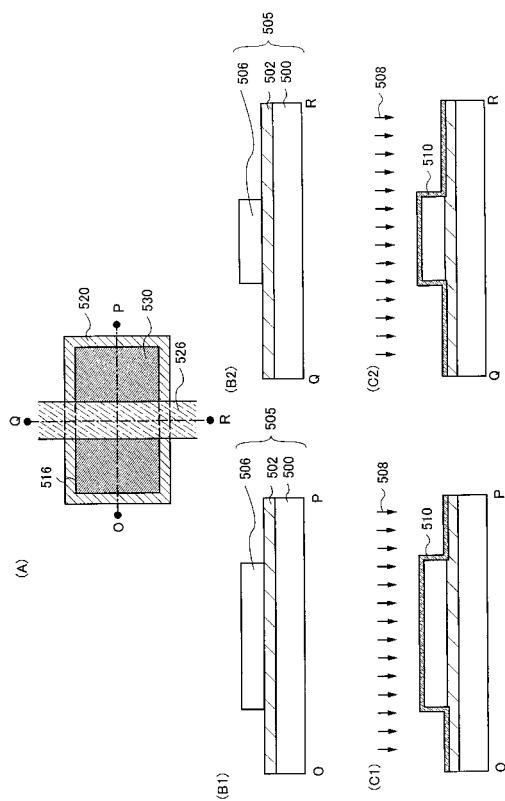

【0193】

図 13 (A) は、本発明に係る半導体装置の主要な構成を説明するための上面図である。なお、図 13 (A) は、一部薄膜等を省略している。

【0194】

図 13 (A) に示す半導体装置は、SOI 基板を用いて薄膜トランジスタが形成されている。SOI 基板の表面シリコン層は島状に形成されており、島状のシリコン層 516 を横断するように、ゲート電極を形成する導電層 526 が設けられている。また、島状のシリコン層 516 の側面と接して絶縁層 520 が設けられている。ここでは、島状のシリコン層 516 の全周囲を囲うように絶縁層 520 を設ける例を図示しているが、少なくとも導電層 526 及びシリコン層 516 が重畳する領域に島状のシリコン層 516 の側面と接する絶縁層を設ければよい。もちろん、導電層 526 及びシリコン層 516 が重畳する領域及びその近傍に、島状のシリコン層 516 の側面と接する絶縁層を設けてもよい。

【0195】

シリコン層 516 には、チャネル形成領域 528 と、ソース領域又はドレイン領域として機能する一対の高濃度不純物領域 530 が形成されている。チャネル形成領域 528 は、導電層 526 と略一致する領域のシリコン層 516 に形成されており、一対の高濃度不純物領域 530 の間に位置する。また、チャネル形成領域と高濃度不純物領域 530 との間に低濃度不純物領域が形成されていてもよい。

【0196】

次に、図 13 (A) に示す半導体装置の作製方法について説明する。ここでは、図 13 (A) における破線 O - P 間の断面図、及び破線 Q - R 間の断面図を用いて、具体的に説明する。

【0197】

10

20

30

40

50

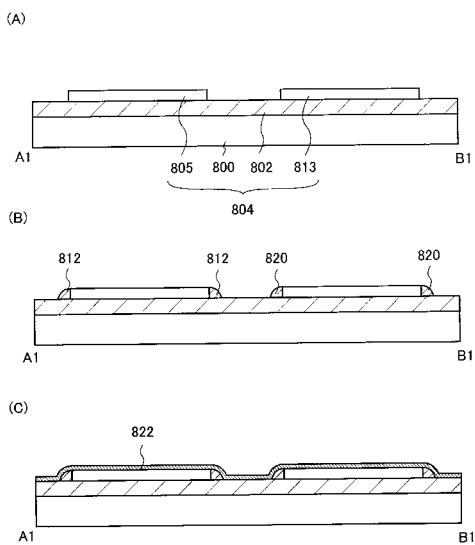

まず、支持基板 500 上に絶縁層 502、島状の第 1 のシリコン層 506 が順に積層形成された S O I 基板 505 を準備する（図 13（B1）、（B2）参照）。なお。島状のシリコン層が形成された S O I 基板 505 の説明は、上記実施の形態 1 で示した S O I 基板 105、島状のシリコン層 106 の説明に準じるため、簡略して以下に説明する。

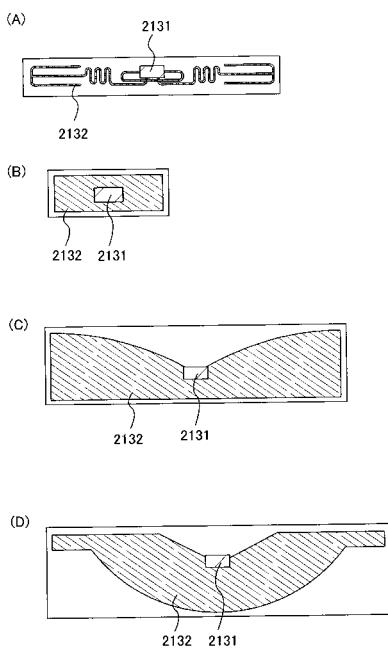

#### 【0198】

S O I 基板 505 は、S I M O X 基板や貼り合わせ基板等の公知の S O I 基板を用いることができる。S O I 基板 505 の表面シリコン層を選択的にエッティングして、島状の第 1 のシリコン層 506 を形成する。第 1 のシリコン層 506 の膜厚は、10 nm 乃至 150 nm、好ましくは 40 nm 乃至 80 nm の範囲で形成するとよい。本実施の形態では、第 1 のシリコン層 506 は膜厚 50 nm の単結晶シリコン層とする。

10

#### 【0199】

また、第 1 のシリコン層 506 の端部は垂直形状となるように形成してもよいし、端部がテープ形状となるように形成してもよい。本実施の形態では、テープ角が 45° 以上 95° 未満、より好ましくはテープ角が 60° 以上 95° 未満と垂直形状に近くなるように形成する。第 1 のシリコン層 506 の端部のテープ形状を急峻にすることで、後に完成する半導体装置の寄生チャネルを低減することができる。なお、本発明は特に限定されず、第 1 のシリコン層 506 の端部をテープ角が 30° 以上 85° 未満、又は 45° 以上 60° 未満の緩やかなテープ形状としてもよい。

#### 【0200】

次に、高密度プラズマ処理により第 1 のシリコン層 506 及び絶縁層 502 の表面を窒化して、第 1 の絶縁層 510 を形成する（図 13（C1）、（C2）参照）。ここで行うプラズマ処理は、マイクロ波（代表的には 2.45 GHz）等の高周波で励起され、電子密度が  $1 \times 10^{11} \text{ cm}^{-3}$  以上  $1 \times 10^{13} \text{ cm}^{-3}$  以下、且つ電子温度が 0.5 eV 以上 1.5 eV 以下のプラズマ 508 を利用して行うことが好ましい。また、固相窒化処理を行うため、窒素を含む雰囲気下でプラズマ処理を行う。窒素を含む雰囲気下とは、例えば窒素と希ガスを含む雰囲気下、又は NH<sub>3</sub> と希ガスを含む雰囲気下である。希ガスとしては、Ar、又は Ar と Kr の混合を用いることが好ましい。詳しくは、実施の形態 1 で示した高密度プラズマ処理を利用すればよい。高密度プラズマ処理を用いて第 1 の絶縁層 510 を形成することで、CVD 法やスパッタリング法を用いて形成した絶縁層よりも緻密な絶縁層を形成することができる。また、高密度プラズマ処理を用いて第 1 の絶縁層 510 を形成することで、800 ~ 1100 で熱酸化した場合に問題となるバーズピークが形成されることなく、熱酸化法で得られる絶縁層と同様に良好な絶縁層を得ることができる。

20

#### 【0201】

第 1 の絶縁層 510 の一部は、後に完成する薄膜トランジスタのゲート絶縁層として機能する。よって、緻密な絶縁層を形成することで絶縁耐圧を向上させることができる。特に、第 1 の絶縁層 510 の一部は、不良が生じやすいシリコン層端部の側面と接するゲート絶縁層を形成するため、信頼性の高い半導体装置を作製することができる。第 1 の絶縁層 510 は、膜厚 1 nm 乃至 10 nm、好ましくは 1 nm 乃至 5 nm の範囲で形成する。本実施の形態では、第 1 の絶縁層 510 として窒化シリコン層を、第 1 のシリコン層 506 表面、或いは第 1 のシリコン層 506 及び絶縁層 502 の表面に形成する。

30

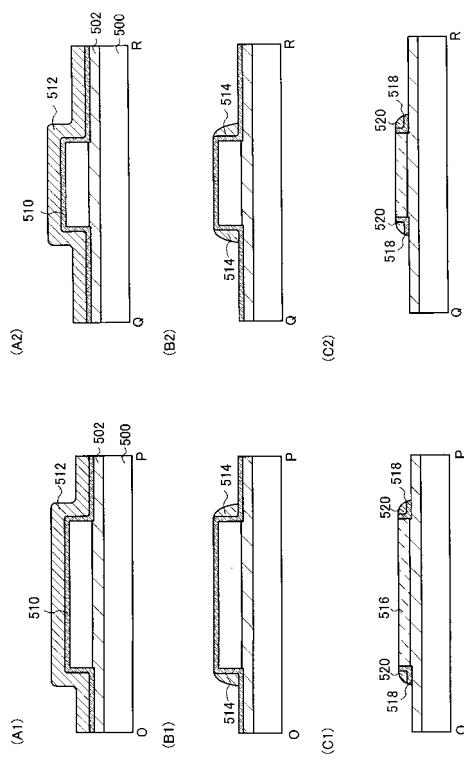

#### 【0202】

次に、第 1 の絶縁層 510 上に第 2 の絶縁層 512 を形成する（図 14（A1）、（A2）参照）。第 2 の絶縁層 512 は、CVD 法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、SiOF、SiOC、DLC、ポーラスシリカ等の材料を用いて形成する。第 2 の絶縁層 512 は、第 1 のシリコン層 506 の端部を覆う第 1 の絶縁層 510 を十分に被覆できる膜厚で形成する。好ましくは、第 1 のシリコン層 506 及び第 1 の絶縁層 510 の膜厚と比較して、1.5 倍乃至 3 倍の膜厚で形成するとよい。本実施の形態では、第 2 の絶縁層 512 として、酸化窒化シリコン層を膜厚 150 nm で形成する。

40

50

## 【0203】

なお、第2の絶縁層512は、後にシリコン層の一表面上に形成する絶縁層522より誘電率が小さい材料を用いて形成するのが好ましい。第2の絶縁層512は、後に完成する半導体装置においてゲート絶縁層の一部、詳しくはシリコン層の端部近傍のゲート絶縁層を形成する。よって、シリコン層の端部近傍のゲート絶縁層を形成する第2の絶縁層512を、シリコン層の一表面上に形成するゲート絶縁層よりも低い誘電率材料を用いて形成することで、シリコン層の端部、特にコーナー部(角部)での電界や静電気の集中を緩和することができ、ゲート絶縁層の絶縁不良を低減できるため好ましい。

## 【0204】

次に、第2の絶縁層512を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、第1の絶縁層510を介して第1のシリコン層506の側面に位置する第3の絶縁層514を形成する(図14(B1)、(B2)参照)。

## 【0205】

第3の絶縁層514は、垂直方向を主体とした異方性のドライエッチングにより、選択的に第2の絶縁層512をエッチングして形成する。エッチングは、第1の絶縁層510を介して第1のシリコン層506の一表面上に形成された第2の絶縁層512、及び第1の絶縁層510を介して絶縁層502上に形成された第2の絶縁層512から進行していく。よって、第1のシリコン層506の一表面上に形成された第1の絶縁層510が露出したところでエッチングを停止させることにより、第1のシリコン層506の側面の領域に第2の絶縁層512が残存して第3の絶縁層514が形成される。なお、第1のシリコン層506の端部を垂直形状に近い形状とすることで、第1のシリコン層506の側面に近接する領域のみに、第3の絶縁層514を容易に形成することができる。

## 【0206】

第3の絶縁層514の形状は、薄膜を形成する材料、エッチング条件等を適宜選択することにより制御することができる。また、第3の絶縁層514を形成するためのエッチング方法は、垂直方向を主体とした異方性エッチングを行えるものであれば特に限定されない。例えば、平行平板方式、マグネットロン方式、2周波方式、ECR方式、ヘリコン方式、又はICP方式などの反応性イオンエッチングを用いることができる。エッチングに用いるガス(エッチングガス)は、少なくとも第2の絶縁層512と第1のシリコン層506とのエッチング選択比を確保できるものを選択すればよい。例えば、CHF<sub>3</sub>、CF<sub>4</sub>、C<sub>4</sub>F<sub>8</sub>、C<sub>2</sub>F<sub>6</sub>、NF<sub>3</sub>等のフッ素系のガスを用いることができる。その他、HeやArやXeなどの不活性ガス、又はO<sub>2</sub>ガス、H<sub>2</sub>ガスを適宜加えてよい。本実施の形態では、第2の絶縁層512のエッチングは、ICP方式の反応性イオンエッチングにより、エッチングガスとしてCHF<sub>3</sub>ガスおよびHeガスを用いて行う。

## 【0207】

次に、第1の絶縁層510、第3の絶縁層514及び第1のシリコン層506を、垂直方向を主体とした異方性エッチングにより全面エッチングして薄膜化し、それぞれ第4の絶縁層518、第5の絶縁層520、及び第2のシリコン層516を形成する(図14(C1)、(C2)参照)。

## 【0208】

第1の絶縁層510、第3の絶縁層514及び第1のシリコン層506は、選択比が低い条件、又はエッチング選択比を極力小さくした条件(エッチング選択比が1に近くなる条件)でエッチングする。すなわち、第1の絶縁層510、第3の絶縁層514及び第1のシリコン層506を、ほぼ同じエッチング速度でエッチングしていく。よって、エッチング後の第4の絶縁層518、第5の絶縁層520、及び第2のシリコン層516は、垂直方向の高さが略一致するように形成される。好ましくは、第2のシリコン層516の膜厚が30nm乃至100nmの範囲となるようにエッチングする。また、第2のシリコン層516は、端部のテーパ角が45°以上95°未満、より好ましくはテーパ角が60°以上95°未満と垂直形状に近くなるように形成するとよい。本実施の形態では、膜厚50nmの第1のシリコン層506をエッチングして、膜厚25nmの第2のシリコン層5

10

20

30

40

50

16を形成する。このとき、第2のシリコン層516端部が垂直形状に近くなるように形成する。

【0209】

第1の絶縁層510、第3の絶縁層514及び第1のシリコン層506のエッティング方法は、垂直方向を主体とした異方性エッティングを行えるものであれば特に限定されない。例えば、平行平板方式、マグネットロン方式、2周波方式、E C R方式、ヘリコン方式、又はI C P方式などの反応性イオンエッティングを用いることができる。

【0210】

エッティングガスは、第1の絶縁層510、第3の絶縁層514及び第1のシリコン層506のエッティング選択比を極力小さくできるもの、つまりエッティング選択比が1に近くなるものを適宜選択すればよい。例えば、 $\text{CHF}_3$ 、 $\text{CF}_4$ 、 $\text{C}_4\text{F}_8$ 、 $\text{C}_2\text{F}_6$ 、 $\text{NF}_3$ 等のフッ素系のガスに $\text{O}_2$ ガスを適宜加えていくことにより、両者のエッティング選択比を小さくすることが可能である。さらに $\text{He}$ や $\text{Ar}$ や $\text{Xe}$ などの不活性ガスを適宜加えてよい。また、エッティングガスとして、フッ素系のガスに代えて $\text{HBr}$ ガス、又は $\text{HBr}$ と $\text{Cl}_2$ との混合ガスを用いてもよい。 $\text{HBr}$ ガスを用いる場合も、 $\text{He}$ や $\text{Ar}$ などの不活性ガスを適宜加えてよい。

【0211】

なお、このとき形成される第5の絶縁層520は、第4の絶縁層518と接しない面を、第2のシリコン層516の側面に対して凸形状に湾曲するように形成するのが好ましい。もちろん、本発明は特に限定されず、第5の絶縁層520は丸みを帯びた形状でなく、角を有する形状としてもよいが、第5の絶縁層520のコーナー部を緩やかな形状とすることで、上層に積層される層（ここでは、第6の絶縁層522）の被覆性を良好にすることができる。

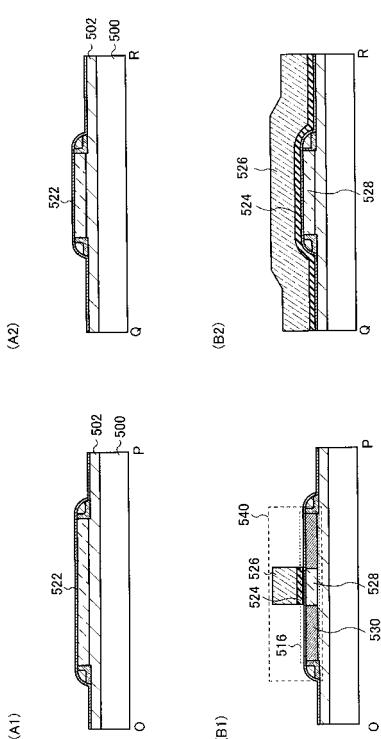

【0212】

次に、第2のシリコン層516上に第6の絶縁層522を形成する（図15（A1）、（A2）参照）。

【0213】

第6の絶縁層522は、CVD法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化アルミニウム等の材料を用いて形成する。第6の絶縁層522は、これらの材料のうち1つ又は複数を用いて、単層構造又は積層構造で形成する。また、第6の絶縁層522は、高密度プラズマ処理による固相酸化若しくは固相窒化で形成することもできる。例えば、高密度プラズマ処理により第2のシリコン層516、第4の絶縁層518及び第5の絶縁層520の表面を酸化又は窒化して、第6の絶縁層522を形成することができる。第6の絶縁層522は、第2のシリコン層516の一表面上の膜厚を1nm乃至15nm、好ましくは1nm乃至10nmの範囲で形成する。なお、第6の絶縁層522は、少なくとも第2のシリコン層516の一表面上に形成すればよく、第5の絶縁層520及び第4の絶縁層518上に形成することもできる。本実施の形態では、第6の絶縁層522として酸化窒化シリコン層を、膜厚10nmで形成する。

【0214】

以上までで形成される第6の絶縁層522、第5の絶縁層520及び第4の絶縁層518は、ゲート絶縁層として機能する。すなわち、本発明に係るゲート絶縁層は、一体物ではなく複数の絶縁層の複合物で形成される。シリコン層の側面と接して第4の絶縁層518及び第5の絶縁層520を形成し、さらにシリコン層の一表面上に第6の絶縁層522を形成することで、シリコン層の端部においてゲート絶縁層の被覆性を良好にことができる。また、シリコン層を島状に加工する際のエッティングやフッ酸等を用いた洗浄により、シリコン層の端部下及びその近傍の絶縁層（支持基板上の絶縁層）が除去された場合でも、シリコン層を十分に被覆することができる。よって、シリコン層端部におけるゲート絶縁層の被覆不良によるゲート電極を形成する導電層とシリコン層との短絡や、リーカ電流の発生、静電破壊等を防止することができる。また、シリコン層の端部に接して、高

10

20

30

40

50

密度プラズマ処理を利用した緻密な絶縁層を形成することで、ゲート絶縁層の特性を向上させることができる。

【0215】

なお、第6の絶縁層522、第5の絶縁層520及び第4の絶縁層518で形成されるゲート絶縁層は、第2のシリコン層516の一表面上に形成された領域と比較して、第2のシリコン層516の側面と接する領域の膜厚が厚いことが好ましい。例えば、第2のシリコン層516の一表面上からの垂直線とゲート絶縁層の最表面との交点までの距離を膜厚 $t_1$ する。第2のシリコン層516の側面からの垂直線とゲート絶縁層の最表面との交点までの距離を膜厚 $t_2$ とする。ゲート絶縁層は、膜厚 $t_1$  < 膜厚 $t_2$ を満たすことが好ましい。第2のシリコン層516の側面と接する領域の膜厚は一定値であるとは限らないが、この場合は、膜厚 $t_1$ と比較して、膜厚 $t_2$ の最小値が同じ或いは膜厚 $t_1$ より大きいことが好ましい。このようにゲート絶縁層により第2のシリコン層516の端部を十分に被覆する、好ましくは第2のシリコン層516の側面と接する領域の膜厚を厚くすることで、第2のシリコン層516の端部に掛かる電界を緩和することができ、リーク電流の発生等を防止することができる。10

【0216】

次に、第6の絶縁層522を介して第2のシリコン層516上にゲート電極として機能する導電層524、導電層526を順に形成する。導電層524、526をマスクとして第2のシリコン層516に一導電型を付与する不純物元素を添加して、チャネル形成領域528、ソース領域又はドレイン領域として機能する高濃度不純物領域530を形成する20 (図15 (B1)、(B2) 参照)。

【0217】

導電層524、526は、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、アルミニウム(Al)、銅(Cu)、又はニオブ(Nb)等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて形成することができる。また、リン等の一導電型を付与する不純物元素が添加された多結晶シリコンに代表される半導体材料を用いて形成することもできる。ゲート電極として機能する導電層はこれらの材料のうち1つ又は複数を用いて、単層構造又は積層構造で形成することができ、膜厚100nm乃至1000nm、好ましくは膜厚200nm乃至800nm、より好ましくは300nm乃至500nmの範囲で形成するとよい。また、ゲート電極として機能する導電層は、上述の材料を用いてCVD法やスパッタリング法により全面に形成した後、選択的にエッチングして所望の形状に加工すればよい。本実施の形態では、導電層524、526として、窒化タンタル層、窒化タンゲステン層を、それぞれ膜厚30nm、膜厚370nmで順に積層形成する。30

【0218】

一導電型を付与する不純物元素としては、リン(P)やヒ素(As)等のn型を付与する不純物元素、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等のp型を付与する不純物元素を用いることができる。

【0219】

以上により、本発明を適用した薄膜トランジスタ540を形成することができる。40

【0220】

また、第2のシリコン層516に一導電型を付与する不純物元素を添加した後、熱処理を行うことにより、添加した不純物元素を活性化することができる。熱処理は、レーザビーム照射、又はRTA若しくはファーネスアーニール炉を用いて行うことができる。具体的には、400乃至700、好ましくは500乃至550の温度範囲で熱処理を行うのが好ましい。また、熱処理は窒素雰囲気下で行うことが好ましい。例えば、5504時間の加熱を行うことにより、活性化を行うことができる。また、第2のシリコン層516の一部に非晶質領域がある場合には、熱処理を行うことにより、不純物元素の活性化とともにシリコン層の再結晶化を行うこともできる。

【0221】

なお、本実施の形態で示したTFTの構造は一例であり、図示した構造に限定されるものではない。例えば、直列に接続された少なくとも2つ以上のチャネル形成領域を含んだシリコン層と、それぞれのチャネル形成領域に電界を印加する少なくとも2つ以上のゲート電極層と、を有するマルチゲート構造を用いてもよい。その他、TFTのシリコン層にLDD領域を形成してもよい。

【0222】

また、ゲート電極として機能する導電層は、側面をテーパ形状としてもよいし、積層構造として各層でテーパ角度を異ならせてよい。また、導電層の側面と接するサイドウォールともいわれる絶縁層を形成してもよい。

【0223】

本発明を適用して作製した薄膜トランジスタは、シリコン層の端部に起因する不良を低減させることができる。特に、シリコン層の端部におけるゲート絶縁層の被覆不良を防止することができ、シリコン層及びゲート電極を形成する導電層との短絡を防止することができる。また、シリコン層の端部における電界集中を緩和することができる。よって、リーケ電流、静電破壊等を防止、低減できるため、信頼性の高い半導体装置を作製することができる。また、半導体装置を歩留まり良く製造することも可能になる。

【0224】

また、本実施の形態で示すように、シリコン層の側面と接して緻密な絶縁層を形成することで、シリコン層の端部において絶縁耐圧が高く信頼性に優れる半導体装置を作製することができる。

【0225】

なお、本実施の形態は、本明細書で示す他の実施の形態と、適宜組み合わせることができる。

【0226】

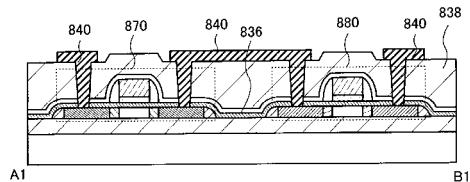

(実施の形態6)

【0227】

本実施の形態では、上記実施の形態と異なる半導体装置及びその作製方法の例について、図19乃至図25を用いて説明する。具体的には、相異なる導電型の薄膜トランジスタを具備する半導体装置の例を示す。

【0228】

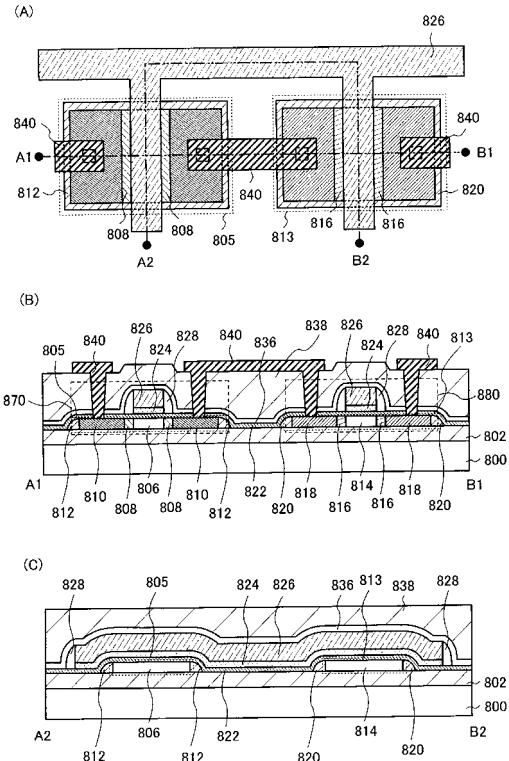

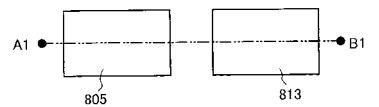

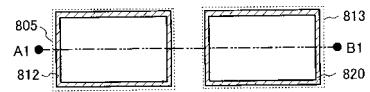

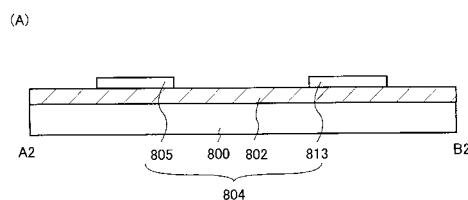

図19は、本実施の形態で示す半導体装置の上面図及び断面図であり、複数のトランジスタを具備する半導体装置の構成を示している。図19(A)は上面図、図19(B)は図19(A)における破線A1-B1間の断面図を示し、図19(C)は図19(A)における破線A2-B2間の断面図を示している。なお、図19(A)は、一部薄膜等の構成要素を省略している。

【0229】

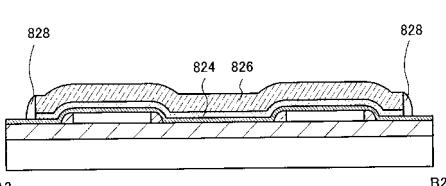

図19に示す半導体装置は、SOI基板を用いて形成されており、支持基板800上に絶縁層802を介して島状に設けられたシリコン層805、シリコン層813と、当該シリコン層805、813上に絶縁層822を介して設けられたゲート電極を形成する導電層824、導電層826と、当該導電層826上に絶縁層836、絶縁層838を介して設けられたソース電極又はドレイン電極を形成する導電層840と、を有している(図19(A)乃至(C)参照)。

【0230】

ゲート電極は、導電層824及び導電層826の積層構造で形成されている。導電層824、826は、島状のシリコン層805、813をそれぞれ横断するように設けられている。また、導電層824及び導電層826の側面に接して絶縁層828が設けられている。絶縁層828は、サイドウォールともいわれる。なお、ここではゲート電極を導電層824、826の2層の積層構造で形成する例を示したが、本発明は特に限定されず、ゲート電極は単層構造でもよいし、3層以上の積層構造でもよい。また、ゲート電極として形成される導電層の側面をテーパ形状にしてもよいし、2層以上の導電層の積層構造とし

10

20

30

40

50

て各層でテーパ角度が異なるようにしてもよい。また、実施の形態 1 乃至 5 で示したゲート電極の構成のいずれを適用しても構わない。

【 0 2 3 1 】

島状に設けられたシリコン層 805、813 は、SOI 基板 804 の表面シリコン層を用いて形成されている。島状に設けられたシリコン層 805 は、チャネル形成領域 806 と、LDD 領域として機能する一対の低濃度不純物領域 808 と、ソース領域又はドレイン領域として機能する一対の高濃度不純物領域 810 と、を有する。チャネル形成領域 806 は、絶縁層 822 を介して導電層 824、826 と重なる領域のシリコン層 805 に形成されている。低濃度不純物領域 808 は、絶縁層 822 を介して絶縁層 828 と重なる領域のシリコン層 805 に形成されている。高濃度不純物領域 810 は、絶縁層 822 を介して導電層 824、導電層 826 及び絶縁層 828 と重ならない領域のシリコン層 805 に形成されている。チャネル形成領域 806 は一対の高濃度不純物領域 810 の間に位置しており、低濃度不純物領域 808 はチャネル形成領域 806 と高濃度不純物領域 810 の間にそれぞれ位置している。つまり、チャネル形成領域 806 は、一対の高濃度不純物領域 810 の間、及び一対の低濃度不純物領域 808 の間に位置しており、且つ一対の低濃度不純物領域 808 に接して形成されている。また、高濃度不純物領域 810 は、低濃度不純物領域 808 と比較して、高い濃度で一導電型を付与する不純物元素が添加されている。また、シリコン層 805 の側面に接して、絶縁層 812 が設けられている。

【 0 2 3 2 】

同様に、島状に設けられたシリコン層 813 は、チャネル形成領域 814 と、LDD 領域として機能する低濃度不純物領域と 816 と、ソース領域又はドレイン領域として機能する高濃度不純物領域 818 と、を有する。チャネル形成領域 814 は、絶縁層 822 を介して導電層 824、826 と重なる領域のシリコン層 813 に形成されている。低濃度不純物領域 816 は、絶縁層 822 を介して絶縁層 828 と重なる領域のシリコン層 813 に形成されている。高濃度不純物領域 818 は、絶縁層 822 を介して導電層 824、導電層 826 及び絶縁層 828 と重ならない領域のシリコン層 813 に形成されている。チャネル形成領域 814 は一対の高濃度不純物領域 818 の間に位置しており、低濃度不純物領域 816 はチャネル形成領域 814 と高濃度不純物領域 818 の間にそれぞれ位置している。つまり、チャネル形成領域 814 は、一対の高濃度不純物領域 818 の間、及び一対の低濃度不純物領域 816 の間に位置しており、且つ一対の低濃度不純物領域 816 に接して形成されている。また、高濃度不純物領域 818 は、低濃度不純物領域 816 と比較して、高い濃度で一導電型を付与する不純物元素が添加されている。また、シリコン層 813 の側面に接して、絶縁層 820 が設けられている。

【 0 2 3 3 】

本実施の形態において、シリコン層 805 及びシリコン層 813 には、相異なる導電型の不純物元素が添加されているものとする。つまり、低濃度不純物領域 808 及び高濃度不純物領域 810 は、低濃度不純物領域 816 及び高濃度不純物領域 818 と異なる導電型を付与する不純物元素が添加されている。

【 0 2 3 4 】

シリコン層 805 及びシリコン層 813 と、ゲート電極を形成する導電層 824、826 との間には、絶縁層 822 が設けられている。また、絶縁層 822 は、シリコン層 805 の側面と接して設けられた絶縁層 812、シリコン層 813 と接して設けられた絶縁層 820 上にも設けられている。絶縁層 812、絶縁層 820、及び絶縁層 822 は、ゲート絶縁層として機能する。

【 0 2 3 5 】

ソース電極又はドレイン電極を形成する導電層 840 は、絶縁層 836、絶縁層 838 に形成された開口を介してシリコン層 805 に形成された高濃度不純物領域 810、シリコン層 813 に形成された高濃度不純物領域 818 と電気的に接続されるように設けられている。また、図 19 に示すように、シリコン層 805 に形成された高濃度不純物領域 810 と、シリコン層 813 に形成され、高濃度不純物領域 810 と導電型が異なる高濃度

10

20

30

40

50

不純物領域 818 とを電気的に接続することにより、CMOS回路を形成してもよい。

【0236】

次に、図19で示した半導体装置の作製方法の一例について、図面を用いて説明する。

【0237】

まず、支持基板 800 上に絶縁層 802 を介して島状のシリコン層 805、813 が形成されたSOI基板 804 を準備する(図20(A)、図23(A)、図24(A)参照)。

【0238】

SOI基板 804 は、SIMOX基板や貼り合わせ基板等の公知のSOI基板を用いることができる。SOI基板 804 の表面シリコン層を選択的にエッチングして、分離した島状のシリコン層 805 及びシリコン層 813 を形成することができる。シリコン層 805、813 の膜厚は、10nm乃至150nm、好ましくは30nm乃至100nm又は10nm乃至30nmの範囲で形成する。

【0239】

なお、シリコン層 805、813 は、端部がテーパ形状となるように形成してもよいし、垂直形状となるように形成してもよい。シリコン層の端部の形状は、等方性エッチング又は異方性エッチング等のエッチング条件を適宜選択することにより制御することができる。

【0240】

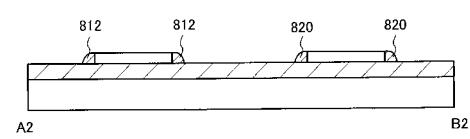

次に、シリコン層 805 の側面と接する絶縁層 812、及びシリコン層 813 の側面と接する絶縁層 820 を形成する(図20(B)、図23(B)、図24(B)参照)。

【0241】

絶縁層 812、絶縁層 820 は、島状に設けられたシリコン層 805 及びシリコン層 813 を覆うように絶縁層を形成し、当該絶縁層を垂直方向を主体とした異方性エッチングを行うことにより選択的にエッチングしてシリコン層 805、813 の側面と接する領域のみ残存させて形成することができる。

【0242】

具体的には、まず、シリコン層 805 及びシリコン層 813 を覆うように絶縁層を形成する。当該絶縁層は、CVD法やスパッタリング法を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、SiOF、SiOC、 DLC、ポーラスシリカ等の材料を用いて形成する。好ましくは、後にシリコン層 805 及びシリコン層 813 の一表面上に形成する絶縁層 822 と比較して、誘電率が小さい層を形成する。また、シリコン層 805、813 上を覆うように形成する絶縁層は、少なくともシリコン層 805、813 の端部を十分に被覆できる膜厚で形成し、好ましくはシリコン層 805、813 の1.5倍乃至3倍の膜厚で形成する。

【0243】

次に、シリコン層 805 及びシリコン層 813 を覆うように形成した絶縁層を、垂直方向を主体とした異方性エッチングを行うことにより選択的にエッチングする。エッチングは、シリコン層 805 の一表面上及びシリコン層 813 の一表面上に形成された絶縁層から進行していく。なお、絶縁層は、シリコン層 805 の一表面上、シリコン層 813 の一表面上及び絶縁層 802 上に、ほぼ同じ膜厚で形成されている。よって、シリコン層 805、813 の一表面が露出したところでエッチングを停止させることにより、シリコン層の 805、813 の側面と接する領域に絶縁層を選択的に残すことができる。残存する絶縁層が、絶縁層 812、820 に相当する。ここでは、絶縁層 812、820 は、それぞれ接するシリコン層 805、813 の側面に対して凸形状に湾曲するように形成している。もちろん、本発明は特に限定されず、絶縁層 812、820 は丸みを帯びた形状でなく、角を有する形状としてもよい。好ましくは、絶縁層 812、820 のコーナー部を緩やかな形状とすることで、上層に積層される層(ここでは絶縁層 822)の被覆性を良好にできる。

【0244】

10

20

30

40

50

なお、絶縁層 812、820 を形成する際のエッチングの影響により、シリコン層 805、813 の上層部が非晶質化する場合がある。この場合、シリコン層 805、813 の非晶質化された領域を選択的にエッチングしてもよいし、レーザビームの照射、又は RTA 若しくはファーネスアニール炉を用いて熱処理を行い、シリコン層 805、813 を再結晶化してもよい。また、シリコン層に一導電型を付与する不純物元素を添加して不純物領域を形成した後、不純物領域を活性化するための熱処理と併せて再結晶化してもよい。具体的には、上記実施の形態 2 又は実施の形態 3 に示すシリコン層及びそのシリコン層の側面と接する絶縁層の形成方法を適用することができる。

【0245】

また、SOI 基板の表面シリコン層を、完成する薄膜トランジスタのシリコン層よりも厚めに設定し、後の工程でシリコン層を薄膜化してもよい。例えば、SOI 基板の表面シリコン層の膜厚を、完成する薄膜トランジスタのシリコン層よりも 2 倍乃至 3 倍となるように制御しておく。次に、表面シリコン層を選択的にエッチングして島状に加工した後、当該島状のシリコン層上に絶縁層を形成する。当該絶縁層及びシリコン層を、選択比が低い条件若しくは選択比を極力小さくした条件（エッチング選択比 1 に近い条件）で垂直方向を主体とした異方性エッチングを行うことにより全面エッチングして、薄膜化したシリコン層及びその側面と接する絶縁層を形成してもよい。具体的には、上記実施の形態 4 又は実施の形態 5 に示すシリコン層及びその側面と接する絶縁層の形成方法を適用することができる。

【0246】

また、上記実施の形態 5 に示すように、高密度プラズマ処理を用いてシリコン層の側面と接する緻密な絶縁層（例えば、窒化シリコン層又は窒化酸化シリコン層等の窒素を含む絶縁層）を形成してもよい。

【0247】

シリコン層 805 及びその側面と接する絶縁層 812、並びにシリコン層 813 及びその側面と接する絶縁層 820 は、上記実施の形態 1 乃至 5 のいずれかの方法を用いて形成してもよい。ここでは、実施の形態 1 で示す方法を用いるものとする。

【0248】

また、後に完成する薄膜トランジスタの閾値電圧を制御するため、シリコン層 805、813 に低濃度の一導電型を付与する不純物元素を添加してもよい。この場合は、完成する薄膜トランジスタのチャネル形成領域にも不純物元素が添加されることになる。一導電型を付与する不純物元素としては、リン（P）やヒ素（As）等の n 型を付与する不純物元素、ボロン（B）やアルミニウム（Al）やガリウム（Ga）等の p 型を付与する不純物元素を用いることができる。例えば、不純物元素としてボロンを用いて、 $5 \times 10^{15} \text{ cm}^{-3}$  乃至  $5 \times 10^{17} \text{ cm}^{-3}$  の濃度でシリコン層 805、813 に含まれるように添加することが可能である。なお、シリコン層 805、813 には、異なる濃度の不純物元素を添加してもよいし、異なる導電型の不純物元素を添加してもよい。

【0249】

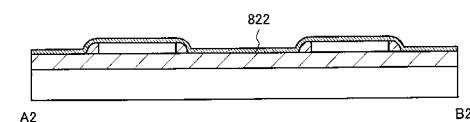

次に、シリコン層 805 及びその側面と接する絶縁層 812、並びにシリコン層 813 及びその側面と接する絶縁層 820 上に絶縁層 822 を形成する（図 20（C）、図 24（C）参照）。

【0250】

絶縁層 822 は、CVD 法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化アルミニウム等の材料を用いて形成する。好みしくは、シリコン層 805 の側面と接する絶縁層 812、及びシリコン層 813 の側面と接する絶縁層 820 よりも誘電率が大きい材料を用いて形成するとよい。絶縁層 822 は、上述した材料のうち 1 つ又は複数を用いて単層構造又は積層構造で形成する。また、絶縁層 822 は、高密度プラズマ処理によるシリコン層 805、813 の固相酸化若しくは固相窒化で形成してもよい。

【0251】

10

20

30

40

50

絶縁層 812、絶縁層 820、及び絶縁層 822 はゲート絶縁層を形成する。絶縁層 822 は、少なくともシリコン層 805、813 の一表面上に形成する。本実施の形態では、シリコン層 805 及びその側面と接する絶縁層 812、並びにシリコン層 813 及びその側面と接する絶縁層 820 を覆うように、絶縁層 822 を形成する。すなわち、本実施の形態に係るゲート絶縁層は、一体物ではなく複数の絶縁層の複合物で構成される。なお、複数の絶縁層の境界は明確なものでなくともよい。このように、シリコン層の側面と接する絶縁層を、シリコン層の一表面上に形成する絶縁層と別に形成することで、シリコン層の端部におけるゲート絶縁層の被覆性を良好にすることができます。また、シリコン層を薄膜化した場合は、フッ酸等を用いた洗浄工程によるシリコン層下の絶縁層の意図しないエッティングの問題が顕著になるが、本発明を適用してシリコン層の側面と接する絶縁層を形成することで、ゲート絶縁層でシリコン層を十分に被覆することが可能になる。よって、シリコン層の端部におけるゲート絶縁層の被覆不良に起因したシリコン層とゲート電極層の短絡、リーク電流の発生、静電破壊等を防止することができる。

【0252】

なお、ゲート絶縁層は、シリコン層の一表面上に形成された領域と比較して、シリコン層の側面と接する領域の膜厚が厚いことが好ましい。このようにゲート絶縁層によりシリコン層の端部を十分に被覆する、好ましくはシリコン層の側面と接する領域の膜厚を厚くすることで、シリコン層の端部に掛かる電界を緩和することができ、リーク電流の発生等を防止することができる。

【0253】

また、ゲート絶縁層は、シリコン層の一表面上に形成された領域と比較して、シリコン層の側面と接する領域の誘電率が小さいことが好ましい。このようにすることで、シリコン層の端部に掛かる電界を緩和させることができ、ゲート絶縁層の絶縁不良を防止することができる。

【0254】

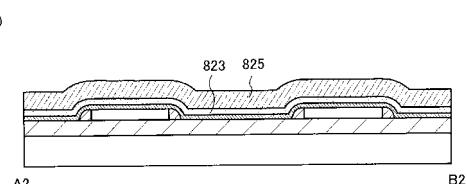

次に、絶縁層 822 上に導電層 823、導電層 825 を順に積層形成する（図 20（D）、図 25（A）参照）。

【0255】

導電層 823、導電層 825 は、CVD 法やスパッタリング法を用いて、タンタル（Ta）、タンゲステン（W）、チタン（Ti）、モリブデン（Mo）、クロム（Cr）、アルミニウム（Al）、銅（Cu）、又はニオブ（Nb）等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて形成することができる。また、リン等の一導電型を付与する不純物元素が添加された多結晶シリコンに代表される半導体材料を用いて形成することもできる。

【0256】

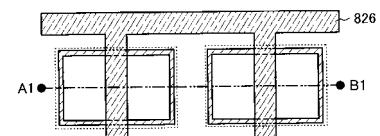

次に、導電層 823、導電層 825 を選択的にエッティングして、ゲート電極として機能する導電層 824、導電層 826 を形成する（図 21（A）、図 23（C）参照）。

【0257】

本実施の形態では、導電層 823、825 を基板上全面に成膜した後、導電層 823、825 を選択的にエッティングして所望の形状に加工している。ここでは、島状のシリコン層 805、813 を、分離した導電層がそれぞれ横断するようにエッティング加工している。このとき、分離した導電層は、島状のシリコン層 805、813 と重ならない領域で一体となるように加工する。つまり、連続する導電層から枝分かれした 2 本の導電層が、それぞれ島状のシリコン層 805、813 を横断するように形成している。

【0258】

次に、シリコン層 813 上を覆うようにレジストマスク 850 を選択的に形成し、当該レジストマスク 850、導電層 824 及び導電層 826 をマスクとして、シリコン層 805 に低濃度の一導電型を付与する不純物元素 851 を添加して、不純物領域 807 を形成する（図 21（B）参照）。不純物元素 851 としては、リンやヒ素等の n 型を付与する不純物元素、ボロンやアルミニウム、ガリウム等の p 型を付与する不純物元素等を用いる

10

20

30

40

50

ことができる。ここでは、不純物元素 851 として、リン (P) を添加する。なお、不純物領域 807 は、後の LDD 領域として機能する低濃度不純物領域の一部を形成する。また、導電層 824、826 下のシリコン層 805 には、チャネル形成領域 806 が形成される。

【0259】

次に、シリコン層 805 上を覆うようにレジストマスク 852 を選択的に形成し、当該レジストマスク 852、導電層 824、導電層 826 をマスクとして、シリコン層 813 に低濃度の一導電型を付与する不純物元素 853 を添加して、不純物領域 815 を形成する (図 21 (C) 参照)。不純物元素 853 は、上述した不純物元素 851 と同様の元素を用いることができる。ここでは、不純物元素 853 として、先の不純物元素 851 と異なる導電型の元素を添加するものとし、ボロン (B) を添加する。なお、不純物領域 815 は、後の LDD 領域として機能する低濃度不純物領域の一部を形成する。また、導電層 824、826 下のシリコン層 813 には、チャネル形成領域 814 が形成される。

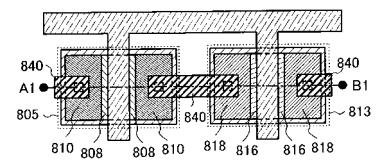

【0260】

次に、導電層 824 及び導電層 826 の側面と接する絶縁層 828 を形成する (図 21 (D)、図 25 (B) 参照)。絶縁層 828 は、CVD 法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の無機材料、有機樹脂などの有機材料を用いて、単層構造又は積層構造の絶縁層を形成し、当該絶縁層を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、導電層 824 及び導電層 826 の側面と接する絶縁層 828 を形成することができる。絶縁層 828 はサイドウォールともいわれる。ここでは、絶縁層 828 は、導電層 824、826 の側面と接しない面を湾曲状に形成する。具体的には、任意の曲率を有し、接する導電層 824、826 の側面に対して凸形状に湾曲するように形成する。もちろん、本発明は特に限定されず、絶縁層 828 は丸みを帯びた形状でなく、角を有する形状としてよい。なお、絶縁層 828 は、LDD 領域として機能する低濃度不純物領域を形成する際のドーピング用マスクとして用いることができる。

【0261】

次に、シリコン層 813 上を覆うようにレジストマスク 854 を選択的に形成する。当該レジストマスク 854、導電層 824、826 及び当該導電層 824、826 の側面と接して設けられた絶縁層 828 をマスクとして、シリコン層 805 に高濃度の一導電型を付与する不純物元素 855 を添加する。その結果、シリコン層 805 には、ソース領域又はドレイン領域として機能する高濃度不純物領域 810、LDD 領域として機能する低濃度不純物領域 808、チャネル形成領域 806 が形成される。不純物元素 855 は、上述した不純物元素 851 と同様の元素を用いることができる。ここでは、不純物元素 855 として、先の不純物元素 851 と同じ導電型の元素であるリン (P) を添加する。なお、シリコン層 805 に添加する不純物元素 855 は、先にシリコン層 805 に添加した不純物元素 851 よりも高い濃度とする。

【0262】

次に、シリコン層 805 上を覆うようにレジストマスク 856 を選択的に形成する。当該レジストマスク 856、導電層 824、826 及び当該導電層 824、826 の側面と接して設けられた絶縁層 828 をマスクとして、シリコン層 813 に高濃度の一導電型を付与する不純物元素 857 を添加する。その結果、シリコン層 813 には、ソース領域又はドレイン領域として機能する高濃度不純物領域 818、LDD 領域として機能する低濃度不純物領域 816、チャネル形成領域 814 が形成される。不純物元素 857 は、上述した不純物元素 851 と同様の元素を用いることができる。ここでは、不純物元素 857 として、先の不純物元素 853 と同じ導電型の元素であるボロン (B) を添加する。なお、シリコン層 813 に添加する不純物元素 857 は、先にシリコン層 813 に添加した不純物元素 853 よりも高い濃度とする。

【0263】

以上により、シリコン層 805 にソース領域又はドレイン領域として機能する高濃度不

10

20

30

40

50

純物領域 810 と、LDD 領域として機能する低濃度不純物領域 808 と、チャネル形成領域 806 が形成される。また、シリコン層 813 にソース領域又はドレイン領域として機能する高濃度不純物領域 818 と、LDD 領域として機能する低濃度不純物領域 816 と、チャネル形成領域 814 が形成される。本実施の形態では、チャネル形成領域 806 、814 は、導電層 824 、826 を用いて自己整合的に形成することができる。また、低濃度不純物領域 808 、816 は、導電層 824 、826 及びその側面と接する絶縁層 828 を用いて自己整合的に形成することができる。

#### 【 0264 】

次に、支持基板 800 上に設けられた絶縁層や導電層等を覆うように絶縁層 836 、絶縁層 838 を形成し、当該絶縁層 838 上にシリコン層 805 に形成された高濃度不純物領域 810 、シリコン層 813 に形成された高濃度不純物領域 818 と電気的に接続される導電層 840 を形成する（図 22（C）、図 23（D）、図 25（C）参照）。導電層 840 はソース電極又はドレイン電極として機能する。

#### 【 0265 】

絶縁層 836 、838 は、CVD 法やスパッタリング法、塗布法等により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の酸素若しくは窒素を含む無機絶縁材料や、DLC（ダイヤモンドライクカーボン）等の炭素を含む絶縁材料、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロオクテン、アクリル等の有機絶縁材料またはシロキサン樹脂等のシロキサン材料を用いて形成する。なお、シロキサン材料とは、Si-O-Si 結合を含む材料に相当する。シロキサンは、シリコン（Si）と酸素（O）との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。また、絶縁層 836 、838 は、CVD 法やスパッタリング法を用いて絶縁層を形成した後、当該絶縁層に酸素雰囲気下又は窒素雰囲気下で高密度プラズマ処理を行うことにより形成してもよい。ここでは、導電層 826 等の上層に絶縁層 836 、838 の 2 層の積層構造を形成しているが、単層構造としても 3 層以上の積層構造としてもよい。

#### 【 0266 】

導電層 840 は、CVD 法やスパッタリング法を用いて、アルミニウム（Al）、タンゲステン（W）、チタン（Ti）、タンタル（Ta）、モリブデン（Mo）、ニッケル（Ni）、白金（Pt）、銅（Cu）、金（Au）、銀（Ag）、マンガン（Mn）、ネオジム（Nd）、炭素（C）、シリコン（Si）等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて、単層構造又は積層構造で形成する。アルミニウムを含む合金材料としては、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素とシリコンの一方又は両方とを含む合金材料があげられる。導電層 840 は、例えば、バリア層とアルミニウムシリコン（Al-Si）層とバリア層の積層構造、バリア層とアルミニウムシリコン（Al-Si）層と窒化チタン層とバリア層の積層構造を採用することができる。なお、バリア層とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電層 840 を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができるため好ましい。

#### 【 0267 】

以上により、シリコン層 805 を用いて形成された n チャネルトランジスタ 870 及びシリコン層 813 を用いて形成された p チャネルトランジスタ 880 を具備する半導体装置を作製することができる。本実施の形態では、シリコン層 805 に形成された高濃度不純物領域 810 と電気的に接続される導電層 840 と、シリコン層 813 に形成された高濃度不純物領域 818 と電気的に接続される導電層 840 と、を電気的に接続させることによって、n チャネルトランジスタ及び p チャネルトランジスタを有する CMOS 回路を

10

20

30

40

50

形成している。

【0268】

なお、本実施の形態では相異なる導電型を有する2つの薄膜トランジスタを具備するCMOS回路を作製する例を示したが、本発明は特に限定されない。例えば、複数のnチャネル薄膜トランジスタを具備するnMOS回路、複数のpチャネル薄膜トランジスタを具備するpMOS回路等を作製することもできる。nMOS回路、pMOS回路等は、シリコン層に添加する不純物元素を適宜選択すればよい。

【0269】

本発明を適用した半導体装置は、シリコン層の端部の形状及び特性等の影響による不良を防止、低減することができる。よって、信頼性の向上した半導体装置を作製することができる。また、歩留まり良く半導体装置を製造することが可能になる。

10

【0270】

なお、本実施の形態は、本明細書で示す他の実施の形態と、適宜組み合わせができる。

【0271】

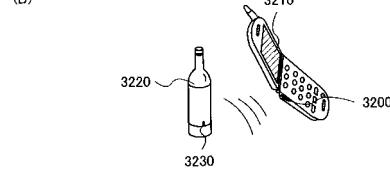

(実施の形態7)

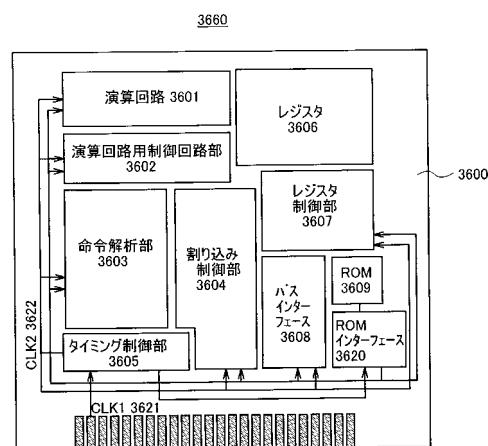

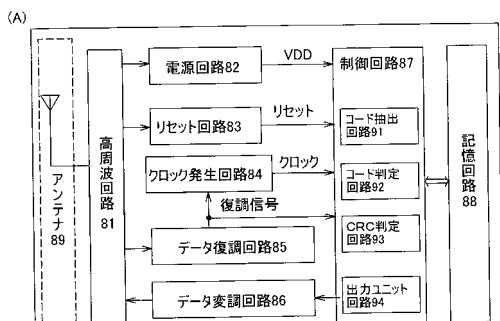

本発明に係る半導体装置は、CPU(中央演算回路:Central Processsing Unit)等の集積回路に適用することができる。本実施の形態では、図19に示した半導体装置を適用したCPUの例に関して、図面を用いて以下に説明する。

20

【0272】

図27に示すCPU3660は、基板3600上に演算回路(ALU:Arithmetic logic unit)3601、演算回路用制御回路部(ALU Controller)3602、命令解析部(Instruction Decoder)3603、割り込み制御部(Interrupt Controller)3604、タイミング制御部(Timing Controller)3605、レジスタ(Register)3606、レジスタ制御部(Register Controller)3607、バスインターフェース(Bus I/F)3608、書き換え可能なROM3609、ROMインターフェース(ROM I/F)3620を主に有している。また、ROM3609及びROMインターフェース3620は、別チップに設けても良い。これらCPU3660を構成する様々な回路は、上記実施の形態1乃至6に示した作製方法によりSOI基板を用いて形成される薄膜トランジスタ、当該薄膜トランジスタを組み合わせたCMOS回路、nMOS回路、pMOS回路等を用いて構成することが可能である。

30

【0273】

なお、図27に示すCPU3660は、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。したがって、本発明を適用するCPUの構成は、図27に示すものに限定されるものではない。

【0274】

バスインターフェース3608を介してCPU3660に入力された命令は、命令解析部3603に入力され、デコードされた後、演算回路用制御回路部3602、割り込み制御部3604、レジスタ制御部3607、タイミング制御部3605に入力される。

40

【0275】

演算回路用制御回路部3602、割り込み制御部3604、レジスタ制御部3607、タイミング制御部3605は、デコードされた命令に基づき、各種制御を行う。具体的に演算回路用制御回路部3602は、演算回路3601の駆動を制御するための信号を生成する。また、割り込み制御部3604は、CPU3660のプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタ制御部3607は、レジスタ3606のアドレスを生成し、CPUの状態に応じてレジスタ3606の読み出しや書き込みを行う。

【0276】

またタイミング制御部3605は、演算回路3601、演算回路用制御回路部3602

50