(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第6999272号**

**(P6999272)**

(45)発行日 令和4年1月18日(2022.1.18)

(24)登録日 令和3年12月24日(2021.12.24)

(51)国際特許分類

|         |                 |     |         |        |         |

|---------|-----------------|-----|---------|--------|---------|

| G 0 9 F | 9/30 (2006.01)  | F I | G 0 9 F | 9/30   | 3 3 0   |

| G 0 2 F | 1/1368(2006.01) |     | G 0 2 F | 1/1368 |         |

|         |                 |     | G 0 9 F | 9/30   | 3 4 8 A |

請求項の数 7 (全16頁)

|          |                             |          |                                                |

|----------|-----------------------------|----------|------------------------------------------------|

| (21)出願番号 | 特願2017-8619(P2017-8619)     | (73)特許権者 | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号 |

| (22)出願日  | 平成29年1月20日(2017.1.20)       | (74)代理人  | 110001737<br>特許業務法人スズエ国際特許事務所                  |

| (65)公開番号 | 特開2018-116227(P2018-116227) | (72)発明者  | 望月一秀<br>東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内        |

| A)       |                             | (72)発明者  | 田中仁<br>東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内         |

| (43)公開日  | 平成30年7月26日(2018.7.26)       |          |                                                |

| 審査請求日    | 令和2年1月10日(2020.1.10)        |          |                                                |

| 前置審査     |                             | 審査官      | 石本努                                            |

最終頁に続く

(54)【発明の名称】 表示装置

**(57)【特許請求の範囲】****【請求項1】**

表示領域と、前記表示領域と隣接する第1非表示領域と、前記表示領域と隣接し前記第1非表示領域とは反対側の第2非表示領域とを有する絶縁基板と、

前記第1非表示領域に位置する第1ゲートドライバと、

前記第2非表示領域に位置する第2ゲートドライバと、

前記第1ゲートドライバに接続された第1端部及び前記第2非表示領域に位置し前記第1端部とは反対側の第2端部を有し、前記第2端部が前記第2ゲートドライバから離間して設けられる第1ゲート線と、

前記第1ゲート線が延伸する第1方向に沿って延伸した導電材料からなる層と、

前記導電材料からなる層及び前記第1ゲート線に重なる中継電極と、

を備え、

前記導電材料からなる層は、前記第1非表示領域において、前記第1ゲートドライバ又は前記第1ゲート線と電気的に接続され、

前記導電材料からなる層と前記中継電極とが第1接触部で接触し、前記第1ゲート線と前記中継電極とが第2接触部で接触することで、前記第1ゲート線の前記第2端部は、前記導電材料からなる層と電気的に接続され、

前記第1接触部と前記第2接触部とは、前記第1方向と交差する第2方向に沿って並んでいる、表示装置。

**【請求項2】**

前記導電材料からなる層及び前記第1ゲート線と交差し、前記導電材料からなる層と前記第1ゲート線との間に位置する酸化物半導体層をさらに備える、請求項1に記載の表示装置。

**【請求項3】**

前記導電材料からなる層の上に位置する第1絶縁膜と、

前記第1絶縁膜の上に位置する酸化物半導体層と、

前記酸化物半導体層の上に位置する第2絶縁膜と、

前記第1ゲート線の上に位置する第3絶縁膜と、

をさらに備え、

前記第1ゲート線は、前記第2絶縁膜の上に位置し、

前記中継電極は、前記第2端部と重なり、前記第3絶縁膜の上に位置し、前記第1絶縁膜、前記第2絶縁膜、及び前記第3絶縁膜を前記導電材料からなる層まで貫通する第1貫通孔において前記導電材料からなる層と接し、前記第3絶縁膜を前記第1ゲート線まで貫通する第2貫通孔において前記第1ゲート線と接し、

前記第1貫通孔と前記第2貫通孔とは、前記第1方向と交差する第2方向に沿って並んでいる、請求項1に記載の表示装置。

**【請求項4】**

前記導電材料からなる層の上に位置する第1絶縁膜と、

前記第1絶縁膜の上に位置する酸化物半導体層と、

前記酸化物半導体層の上に位置する第2絶縁膜と、

前記第1ゲート線の上に位置する第3絶縁膜と、

をさらに備え、

前記第1ゲート線は、前記第2絶縁膜の上に位置し、

前記中継電極は、前記第2端部と重なり、前記第3絶縁膜の上に位置し、前記第1絶縁膜、前記第2絶縁膜、及び前記第3絶縁膜に形成された貫通孔において、前記導電材料からなる層の上面と、前記第1ゲート線の上面及び側面とに接している、請求項1に記載の表示装置。

**【請求項5】**

前記第1ゲート線と交差するソース線と、

前記酸化物半導体層と前記ソース線の間に位置し、前記酸化物半導体層及び前記ソース線と接する金属保護膜と、

をさらに備えている、請求項3または4に記載の表示装置。

**【請求項6】**

前記導電材料からなる層は遮光層である、請求項1乃至5のいずれか1項に記載の表示装置。

**【請求項7】**

前記表示領域において、前記導電材料からなる層の幅は、前記第1ゲート線の幅よりも大きく、

前記第2非表示領域において、前記導電材料からなる層の前記第2方向における幅は、前記第1ゲート線の前記第2端部の前記第2方向における幅よりも大きい、請求項1乃至6のいずれか1項に記載の表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明の実施形態は、表示装置に関する。

**【背景技術】**

**【0002】**

スマートフォンやタブレット等に用いられる液晶表示装置は、狭額縫化が求められている。このため、ゲートドライバ等の回路が表示パネルに内蔵される場合、これらの内蔵回路は、片側駆動・片側給電の方式をとることが多い。

10

20

30

40

50

**【 0 0 0 3 】**

透過型の液晶表示装置では、スイッチング素子の劣化防止やリーク電流の抑制のため、バックライトからの光を遮光するための遮光層が設けられている場合がある。この遮光層は、電気的にフローティング状態とならないよう、例えばスイッチング素子のゲート電極と電気的に接続されることが知られている。

**【先行技術文献】****【特許文献】****【 0 0 0 4 】**

**【文献】**特開 2016 - 134388 号公報

10

**【発明の概要】****【発明が解決しようとする課題】****【 0 0 0 5 】**

本実施形態の目的は、表示品位の低下を抑制することが可能な表示装置を提供することにある。

**【課題を解決するための手段】****【 0 0 0 6 】**

本実施形態によれば、

絶縁基板と、第1ゲートドライバと、前記第1ゲートドライバに接続された第1端部及び前記第1端部とは反対側の第2端部を有し、第1方向に沿って延伸した第1ゲート線と、前記第1方向に延伸した導電材料からなる層と、前記導電材料からなる層及び前記第1ゲート線に重なる中継電極と、を備え、前記導電材料からなる層と前記中継電極とが第1接触部で接触し、前記第1ゲート線と前記中継電極とが第2接触部で接触することで、前記第1ゲート線の前記第2端部は、前記導電材料からなる層と電気的に接続され、前記第1接触部と前記第2接触部とは、前記第1方向と交差する第2方向に沿って並んでいる、表示装置が提供される。

20

**【図面の簡単な説明】****【 0 0 0 7 】**

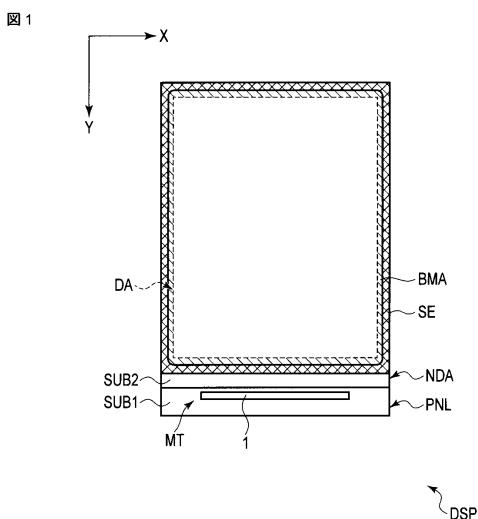

**【図1】**図1は、本実施形態の表示装置の構成を示す図である。

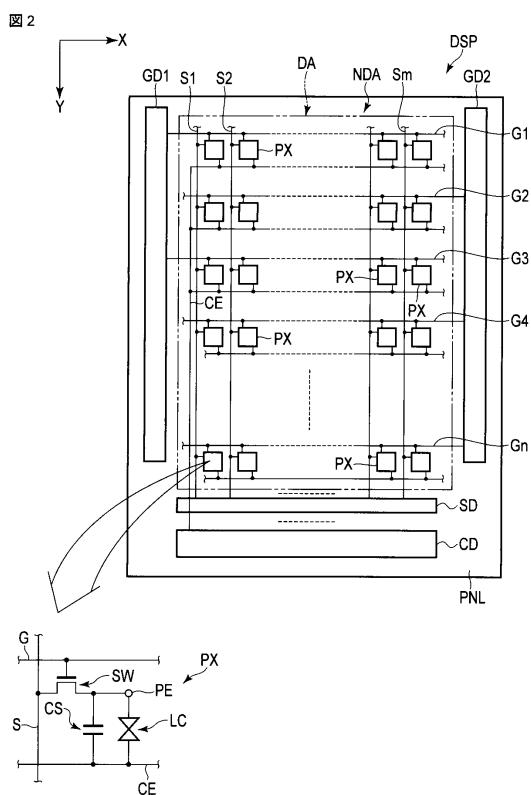

**【図2】**図2は、図1に示す表示パネルの基本構成及び等価回路を示す図である。

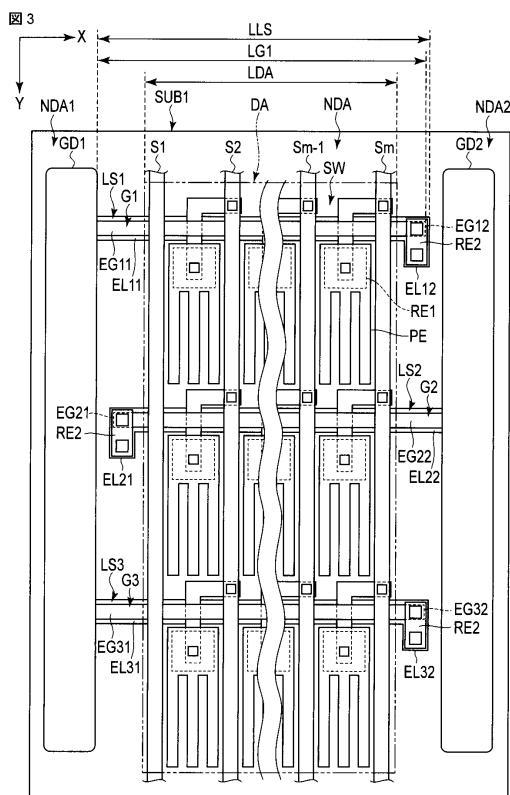

**【図3】**図3は、第1基板SUB1の構成例を示す平面図である。

30

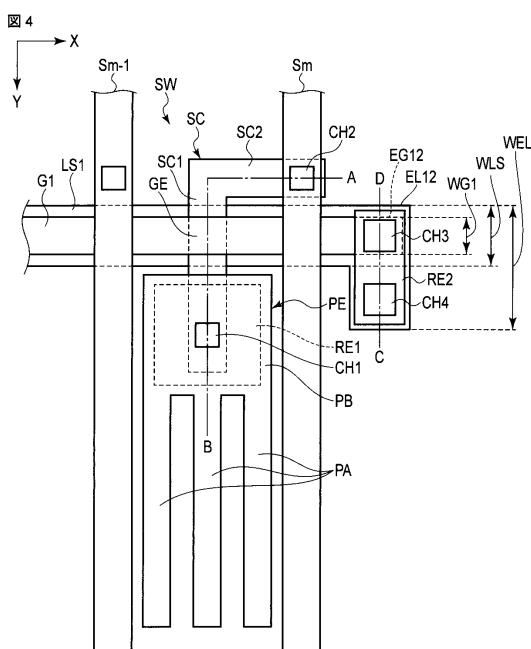

**【図4】**図4は、画素PXの構成を示す平面図である。

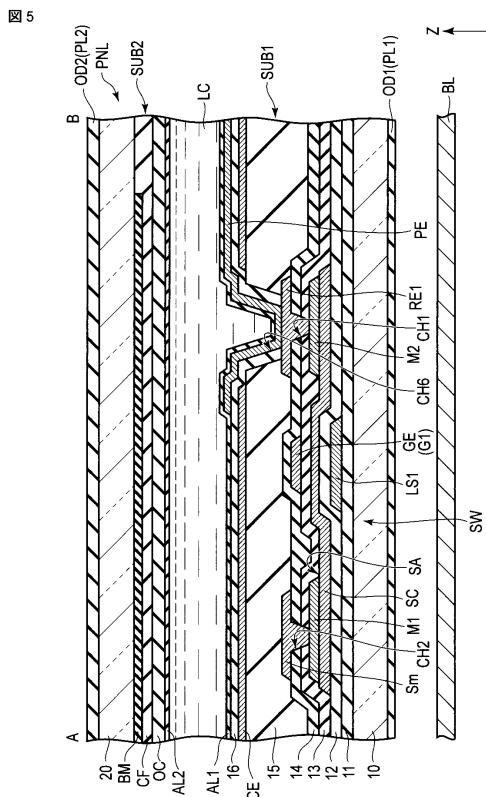

**【図5】**図5は、図4のA-B線で切断した表示パネルの一部を示す断面図である。

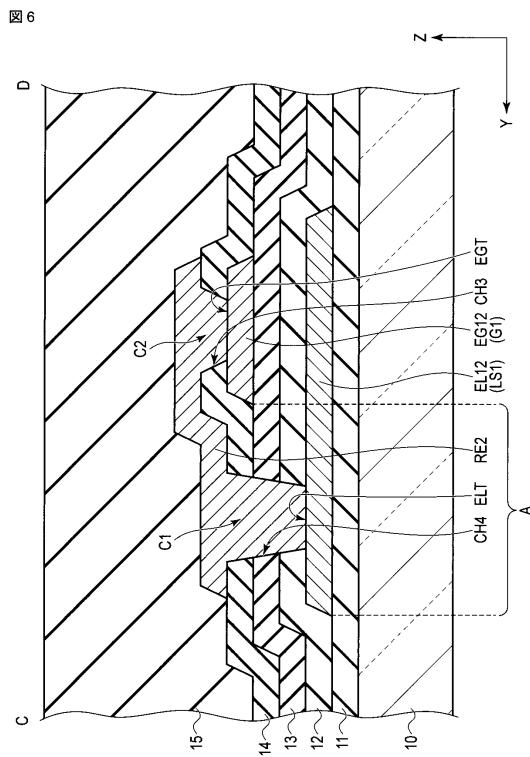

**【図6】**図6は、図4のC-D線で切断した表示パネルの一部を示す断面図である。

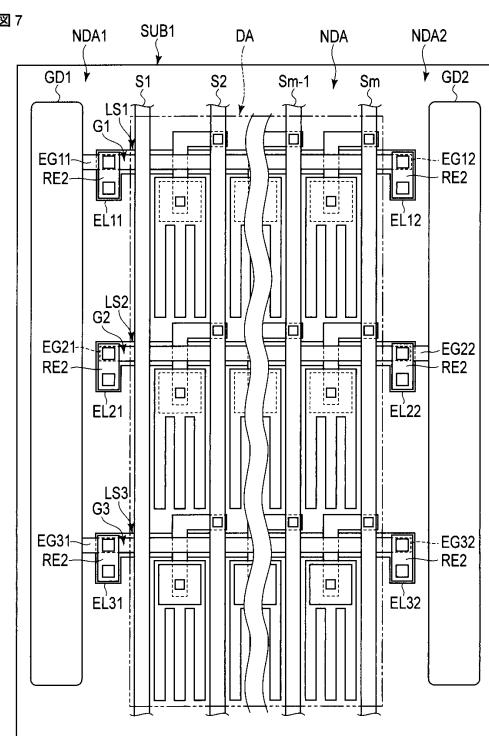

**【図7】**図7は、第1基板SUB1の他の構成例を示す平面図である。

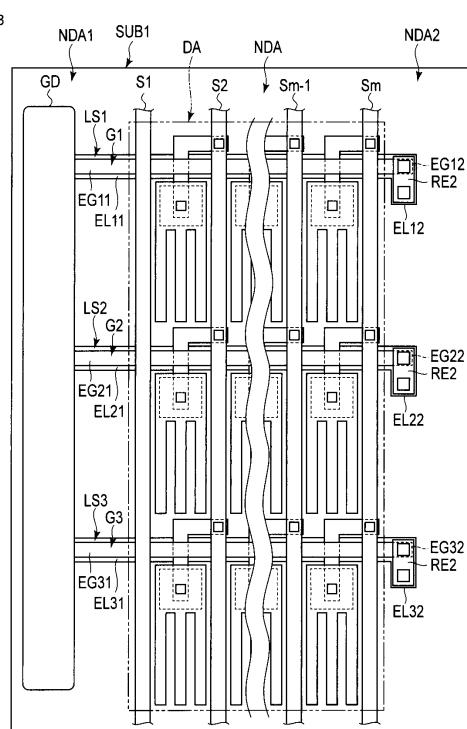

**【図8】**図8は、第1基板SUB1の他の構成例を示す平面図である。

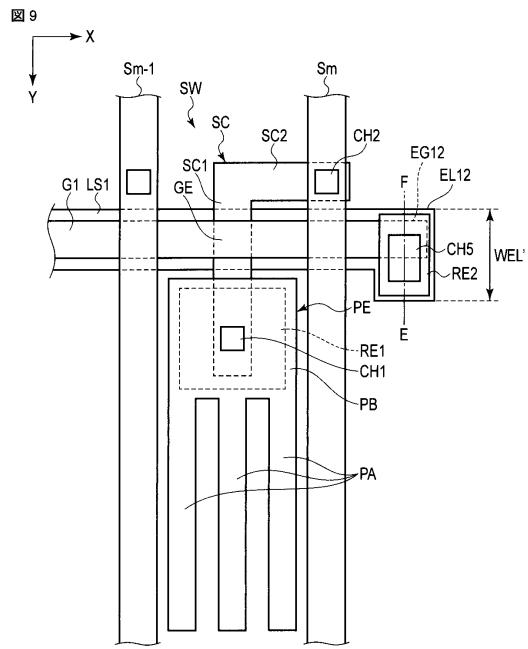

**【図9】**図9は、第1基板SUB1の他の構成例を示す平面図である。

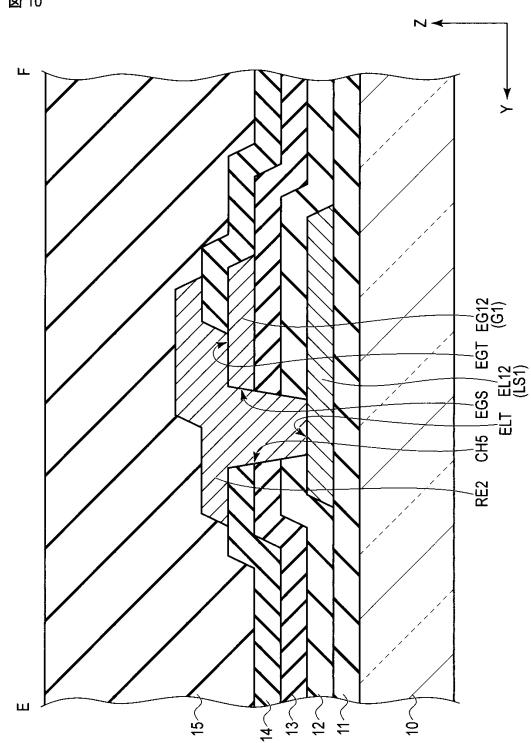

**【図10】**図10は、図9のE-F線で切断した表示パネルの一部を示す断面図である。

**【発明を実施するための形態】****【 0 0 0 8 】**

以下、本実施形態について、図面を参照しながら説明する。なお、開示はあくまで一例に過ぎず、当業者において、発明の主旨を保つての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有されるものである。また、図面は、説明をより明確にするため、実際の態様に比べて、各部の幅、厚さ、形状等について模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。また、本明細書と各図において、既出の図に関して前述したものと同一又は類似した機能を発揮する構成要素には同一の参照符号を付し、重複する詳細な説明を適宜省略することがある。

40

**【 0 0 0 9 】**

図1は、本実施形態の表示装置DSPの構成を示す図である。図に示す第1方向X及び第2方向Yは互いに交差している。一例では、第1方向Xと第2方向Yとは、互いに直交しているが、90度以外の角度で互いに交差していても良い。

50

**【 0 0 1 0 】**

本実施形態においては、表示装置の一例として、液晶表示装置について説明する。なお、本実施形態にて開示する主要な構成は、有機エレクトロルミネッセンス表示素子等を有する自発光型の表示装置、電気泳動素子等を有する電子ペーパ型の表示装置、MEMS (Micro Electro Mechanical Systems) を応用した表示装置、或いはエレクトロクロミズムを応用した表示装置などにも適用可能である。

**【 0 0 1 1 】**

表示装置DSPは、表示パネルPNL、表示パネルPNLを駆動する駆動ICチップ1などを備えている。表示パネルPNLは、例えば、液晶表示パネルであり、第1基板SUB1と、第2基板SUB2と、シール部SEと、周辺遮光層BMAと、液晶層(後述する液晶層LC)と、を備えている。第2基板SUB2は、第1基板SUB1に対向している。シール部SEは、右上がりの斜線で示す領域に設けられ、第1基板SUB1と第2基板SUB2とを接着している。周辺遮光層BMAは、右下がりの斜線で示す領域に設けられ、後述する遮光層BMと同一材料で形成されている。表示パネルPNLは、画像を表示する表示領域DA、及び、表示領域DAを囲む額縁状の非表示領域NDAを備えている。本実施形態において、表示領域DAは、周辺遮光層BMAによって囲まれた内側の領域であり、非表示領域NDAは、周辺遮光層BMAが設けられた領域である。

10

**【 0 0 1 2 】**

駆動ICチップ1は、非表示領域NDAに位置している。図示した例では、駆動ICチップ1は、第2基板SUB2よりも外側に延伸した第1基板SUB1の実装部MTに実装されている。駆動ICチップ1は、例えば、画像表示に必要な信号を出力するディスプレイドライバを内蔵している。ここでディスプレイドライバは、後述するソースドライバSD、ゲートドライバGD、及び、共通電極駆動回路CDの少なくとも一部を含むものである。なお、図示した例に限らず、駆動ICチップ1は、別途表示パネルPNLに接続されるフレキシブル基板上に実装されていても良い。

20

**【 0 0 1 3 】**

本実施形態の表示パネルPNLは、第1基板SUB1の背面側からの光を選択的に透過させることで画像を表示する透過表示機能を備えた透過型、第2基板SUB2の前面側からの光を選択的に反射させることで画像を表示する反射表示機能を備えた反射型、あるいは、透過表示機能及び反射表示機能を備えた半透過型のいずれであっても良い。

30

**【 0 0 1 4 】**

また、ここでは、表示パネルPNLの詳細な構成については説明を省略するが、表示パネルPNLは、X-Y平面、あるいは、基板正面に沿った横電界を利用する表示モード、X-Y平面の法線に沿った縦電界を利用する表示モード、あるいは、X-Y平面に対して斜め方向に傾斜した傾斜電界を利用する表示モードのいずれを適用した構成を有していても良い。また、表示パネルPNLは、上記の縦電界、横電界、及び、傾斜電界を適宜組み合わせて利用する表示モードに対応した構成を有していても良い。

**【 0 0 1 5 】**

図2は、図1に示した表示パネルPNLの基本構成及び等価回路を示す図である。表示パネルPNLは、表示領域DAにおいて、複数の画素PXを備えている。複数の画素PXは、マトリクス状に配置されている。また、表示パネルPNLは、表示領域DAにおいて、複数本のゲート線G(G1~Gn)、複数本のソース線S(S1~Sm)、共通電極CEなどを備えている。ゲート線Gは、各々第1方向Xに延伸し、第2方向Yに並んでいる。ソース線Sは、各々第2方向Yに延伸し、第1方向Xに並んでいる。なお、ゲート線G及びソース線Sは、必ずしも直線的に延伸していなくても良く、それらの一部が屈曲してもよい。共通電極CEは、複数の画素PXに亘って配置されている。

40

**【 0 0 1 6 】**

表示パネルPNLは、非表示領域NDAにおいて、ゲートドライバGD1及びGD2と、ソースドライバSDとを備えている。ゲートドライバGD1とゲートドライバGD2とは、第1方向Xに対向して配置され、表示領域DAを挟んでいる。ゲート線Gは、ゲートド

50

ライバ G D 1 及び G D 2 のいずれか一方に接続されている。図示した例では、奇数番目のゲート線 G 1、G 3、…は、ゲートドライバ G D 1 に接続されている。偶数番目のゲート線 G 2、G 4 …は、ゲートドライバ G D 2 に接続されている。ソース線 S は、ソースドライバ S D に接続されている。共通電極 C E は、共通電極駆動回路 C D に接続されている。ソースドライバ S D、ゲートドライバ G D、及び、共通電極駆動回路 C D は、非表示領域 N D A において、第 1 基板 S U B 1 上に形成されても良いし、これらの一部或いは全部が図 1 に示した駆動 I C チップ 1 に内蔵されていても良い。

#### 【 0 0 1 7 】

各画素 P X は、スイッチング素子 S W、画素電極 P E、共通電極 C E、液晶層 L C 等を備えている。スイッチング素子 S W は、例えば薄膜トランジスタ ( T F T ) によって構成され、ゲート線 G 及びソース線 S と電気的に接続されている。ゲート線 G は、第 1 方向 X に並んだ画素 P X の各々におけるスイッチング素子 S W と接続されている。ソース線 S は、第 2 方向 Y に並んだ画素 P X の各々におけるスイッチング素子 S W と接続されている。画素電極 P E は、スイッチング素子 S W と電気的に接続されている。画素電極 P E の各々は、共通電極 C E と対向し、画素電極 P E と共に共通電極 C E との間に生じる電界によって液晶層 L C を駆動している。保持容量 C S は、例えば、共通電極 C E と同電位の電極、及び、画素電極 P E と同電位の電極の間に形成される。これらのゲート線 G、ソース線 S、スイッチング素子 S W、画素電極 P E、共通電極 C E などは、図 1 に示した第 1 基板 S U B 1 に備えられている。

10

#### 【 0 0 1 8 】

図 3 は、第 1 基板 S U B 1 の構成例を示す平面図である。第 1 基板 S U B 1 は、表示パネル P N L を構成する一方の基板である。図示した例は、横電界を利用する表示モードの一つである F F S ( Fr i n g e F i e l d S w i t c h i n g ) モードが適用された例に相当する。

20

#### 【 0 0 1 9 】

第 1 基板 S U B 1 は、表示領域 D A と非表示領域 N D A に亘って位置している。第 1 基板 S U B 1 は、ゲートドライバ G D 1 及び G D 2、ゲート線 G ( G 1、G 2、G 3 )、ソース線 S ( S 1、S 2、S m - 1、S m )、スイッチング素子 S W、画素電極 P E に加え、遮光層 L S ( L S 1、L S 2、L S 3 )、中継電極 R E 1 及び R E 2、などを備えている。

30

#### 【 0 0 2 0 】

ゲートドライバ G D 1 及び G D 2 は、第 1 基板 S U B 1 の非表示領域 N D A に配置されている。非表示領域 N D A は、図示した例において表示領域 D A の左側に隣接する第 1 非表示領域 N D A 1 及び表示領域 D A の右側に隣接する第 2 非表示領域 N D A 2 を有している。ゲートドライバ G D 1 は第 1 非表示領域 N D A 1 に位置し、ゲートドライバ G D 2 は第 2 非表示領域 N D A 2 に位置している。すなわちゲートドライバ G D 1 と G D 2 とは、表示領域 D A を挟み、第 1 方向 X に対向している。図示した例では、ゲートドライバ G D 1 及び G D 2 は、第 2 方向 Y の幅が第 1 方向 X の幅よりも長い領域に配置されている。

#### 【 0 0 2 1 】

ソース線 S は、ほぼ一定の幅を有する帯状に形成され、表示領域 D A において各ゲート線 G と交差している。すべてのソース線 S は、ゲートドライバ G D 1 とゲートドライバ G D 2 との間に位置している。ソース線 S 1 は、表示領域 D A において最も第 1 非表示領域 N D A 1 に近接するソース線に相当し、図示した表示領域 D A の左側端部に位置している。ソース線 S m は、表示領域 D A において最も第 2 非表示領域 N D A 2 に近接するソース線に相当し、図示した表示領域 D A の右側端部に位置している。

40

#### 【 0 0 2 2 】

スイッチング素子 S W は、隣り合うソース線 S の間に形成されている。一例として、スイッチング素子 S W は、ソース線 S m - 1 とソース線 S m との間で、ゲート線 G 1 近傍に配置されている。スイッチング素子 S W は、ソース線 S m に接続されるとともに、中継電極 R E 1 を介して画素電極 P E とも電気的に接続されている。スイッチング素子 S W を含む画素 P X の構成については後述する。

50

### 【 0 0 2 3 】

ゲート線 G は、ほぼ一定の幅を有する帯状に形成され、第 1 及び第 2 非表示領域 N D A 1 及び N D A 2 にそれぞれ引き出されている。すなわち、ゲート線 G の第 1 方向 X の両端部は、非表示領域 N D A に位置している。具体的には、ゲート線 G 1 及び G 3 の一端部 E G 1 1 及び E G 3 1 は、第 1 非表示領域 N D A 1 においてゲートドライバ G D 1 に接続されている。ゲート線 G 1 及び G 3 の他端部 E G 1 2 及び E G 3 2 は、第 2 非表示領域 N D A 2 に位置し、ゲートドライバ G D 2 から離間している。図示した例では、他端部 E G 1 2 及び E G 3 2 は、ソース線 S m とゲートドライバ G D 2 との間に位置している。一方、ゲート線 G 2 の一端部 E G 2 1 は、第 1 非表示領域 N D A 1 に位置し、ゲートドライバ G D 1 から離間している。図示した例では、一端部 E G 2 1 は、ソース線 S 1 とゲートドライバ G D 1 との間に位置している。ゲート線 G 2 の他端部 E G 2 2 は、第 2 非表示領域 N D A 2 においてゲートドライバ G D 2 に接続されている。

### 【 0 0 2 4 】

導電材料からなる層例えば遮光層 L S は、第 1 方向 X に沿って延伸し、ゲート線 G と重なっている。遮光層 L S は、端部を除いて、ほぼ一定の幅を有する帯状に形成されている。ここでの幅とは、第 2 方向 Y に沿った長さである。本実施形態において、遮光層 L S 1 の第 1 方向 X に沿った長さ L L S は、表示領域 D A の第 1 方向 X に沿った長さ L D A より大きい。一例では、長さ L L S は、ゲート線 G 1 の第 1 方向 X に沿った長さ L G 1 とほぼ等しい。さらに、遮光層 L S の両端部は、非表示領域 N D A に位置している。遮光層 L S は、非表示領域 N D A において、対応するゲート線 G が接続されたゲートドライバに接続されるとともに、ゲートドライバと反対側の端部がゲート線 G と電気的に接続されている。

### 【 0 0 2 5 】

具体的には、遮光層 L S 1 の一端部 E L 1 1 は、第 1 非表示領域 N D A 1 においてゲートドライバ G D 1 に接続されている。遮光層 L S 1 の他端部 E L 1 2 は、第 2 非表示領域 N D A 2 に位置し、端部 E G 1 2 と重なっている。すなわち、他端部 E L 1 2 は、ソース線 S m とゲートドライバ G D 2 との間に位置し、ゲートドライバ G D 2 から離間している。遮光層 L S 1 は、他端部 E L 1 2 及び他端部 E G 1 2 と重なって設けられた中継電極 R E 2 を介して、他端部 E G 1 2 と電気的に接続されている。これにより、ゲート線 G 1 と遮光層 L S 1 とは、第 2 非表示領域 N D A 2 において電気的に接続される。

### 【 0 0 2 6 】

一方、遮光層 L S 2 の一端部 E L 2 1 は、第 1 非表示領域 N D A 1 に位置し、一端部 E G 2 1 と重なっている。すなわち、一端部 E L 2 1 は、ゲートドライバ G D 1 とソース線 S 1 の間に位置し、ゲートドライバ G D 1 から離間している。遮光層 L S 2 の他端部 E L 2 2 は、第 2 非表示領域 N D A 2 においてゲートドライバ G D 2 に接続されている。遮光層 L S 2 は、一端部 E L 2 1 及び一端部 E G 2 1 と重なって設けられた中継電極 R E 2 を介して、ゲート線 G 2 と電気的に接続されている。遮光層 L S 3 の構成は、遮光層 L S 1 と同様であるため説明を省略する。

### 【 0 0 2 7 】

なお、本実施形態において、一端部 E G 1 1 は、第 1 ゲート線の第 1 端部に対応し、他端部 E G 1 2 は、第 1 ゲート線の第 1 端部に対応する。一端部 E L 1 1 は、遮光層の第 3 端部に対応し、他端部 E L 1 2 は、遮光層の第 4 端部に対応する。

### 【 0 0 2 8 】

図 4 は、画素 P X の構成を示す平面図である。ここでは、第 1 基板 S U B 1 の平面図が示されている。図 4 は、ゲートドライバ G D 1 から第 1 方向 X に最も離間した画素 P X の近傍を拡大して示している。なお、一例では、第 1 基板 S U B 1 は共通電極を備えているが、ここでは共通電極の図示を省略する。

### 【 0 0 2 9 】

第 1 基板 S U B 1 は、ゲート線 G 1 、遮光層 L S 1 、ソース線 S m - 1 及び S m 、スイッチング素子 S W 、画素電極 P E 、中継電極 R E 1 及び R E 2 などを備えている。

### 【 0 0 3 0 】

10

20

30

40

50

ゲート線 G 1 は、遮光層 L S 1 の幅 W L S より小さい幅 W G 1 を有し、且つ、そのすべてが遮光層 L S 1 と重なっている。図示した例では、ゲート線 G 1 は、遮光層 L S 1 の略中央に位置している。

#### 【 0 0 3 1 】

スイッチング素子 S W は、ソース線 S m - 1 とソース線 S mとの間に形成されている。一例では、スイッチング素子 S W は、ソース線 S m 及び画素電極 P E と電気的に接続されたシングルゲート型の薄膜トランジスタである。スイッチング素子 S W は、半導体層 S C 、ゲート電極 G E 、及び中継電極 R E 1 などを備えている。

#### 【 0 0 3 2 】

半導体層 S C は、略 L 字状に形成され、第 1 部分 S C 1 と第 2 部分 S C 2 とを有している。第 1 部分 S C 1 は、ソース線 S m - 1 とソース線 S mとの間で第 2 方向 Y に沿って延伸し、ゲート線 G 1 及び遮光層 L S 1 と交差している。ゲート電極 G E は、ゲート線 G 1 のうち、第 1 部分 S C 1 と交差する部分に相当する。第 1 部分 S C 1 の一端部は、画素電極 P E 及び中継電極 R E 1 と重なっている。中継電極 R E 1 は、第 1 部分 S C 1 と重なる領域に形成されたコンタクトホール C H 1 において、第 1 部分 S C 1 と接している。これにより、第 1 部分 S C 1 と中継電極 R E 1 とは、電気的に接続される。第 2 部分 S C 2 は、第 1 部分 S C 1 の他端部から第 1 方向 X に沿ってソース線 S m に向って延伸し、ソース線 S m と交差している。第 2 部分 S C 2 は、ソース線 S m と重なる領域に形成されたコンタクトホール C H 2 において、ソース線 S m と接続されている。なお、図示した例では、第 1 部分 S C 1 及び第 2 部分 S C 2 は、直線状に形成されているが、一部が屈曲していてもよい。

10

20

#### 【 0 0 3 3 】

画素電極 P E は、ソース線 S m - 1 とソース線 S mとの間に位置している。画素電極 P E は、電極部 P A とコンタクト部 P B とを備えている。電極部 P A 及びコンタクト部 P B は、一体的あるいは連続的に形成され、互いに電気的に接続されている。コンタクト部 P B は、電極部 P A よりゲート線 G 1 に近接している。すなわち、コンタクト部 P B は、中継電極 R E 1 と重なる位置に配置され、中継電極 R E 1 と電気的に接続されている。これにより、画素電極 P E は、スイッチング素子 S W と電気的に接続される。電極部 P A は、コンタクト部 P B から第 2 方向 Y に延伸している。図示した例では、画素電極 P E は、3 本の電極部 P A を有している。3 本の電極部 P A は、間隔をおいて第 1 方向 X に並び、それぞれ第 1 方向 X に沿ってほぼ一定の幅を有する帯状に形成されている。なお、画素電極 P E の形状は、図示した例に限定されるものではなく、画素 P X の形状などに合わせて適宜変更することができる。例えば、画素電極 P E は、第 1 方向 X 及び第 2 方向 Y と交差する斜め方向に延伸し、電極部 P A が斜め方向に延伸していくてもよい。

30

#### 【 0 0 3 4 】

次に、遮光層 L S 1 の他端部 E L 1 2 及びゲート線 G 1 の他端部 E G 1 2 について説明する。

#### 【 0 0 3 5 】

本実施形態において、他端部 E L 1 2 は、遮光層 L S 1 のうち、中継電極 R E 2 とほぼ重なる領域に相当する。また、他端部 E G 1 2 は、ゲート線 G 1 のうち中継電極 R E 2 とほぼ重なる領域に相当する。図示した例では、他端部 E L 1 2 は、第 2 方向 Y に沿った辺の長さが第 1 方向 X に沿った辺の長さより大きい矩形状である。一例では、他端部 E L 1 2 の幅 W E L は、幅 W L S の約 2 倍である。

40

#### 【 0 0 3 6 】

中継電極 R E 2 は、他端部 E L 1 2 及び他端部 E G 1 2 と重なっている。具体的には、中継電極 R E 2 は、他端部 L E 1 2 と他端部 E G 1 2 の両方と重なっている領域と、他端部 L E 1 2 と重なっているが他端部 E G 1 2 とは重なっていない領域とを有している。図示した例では、中継電極 R E 2 は、他端部 E L 1 2 と同形状であり、そのすべてが他端部 E L 1 2 の領域内に位置している。中継電極 R E 2 が設けられた領域内には、コンタクトホール C H 3 とコンタクトホール C H 4 とが形成されている。コンタクトホール C H 3 及び

50

C H 4 は、第 2 方向 Y に沿って並んでいる。コンタクトホール C H 3 は、中継電極 R E 2 とゲート線 G 1 とが重なる領域に位置している。コンタクトホール C H 4 は、中継電極 R E 2 と他端部 E L 1 2 とが重なる領域のうち、ゲート線 G 1 と重なっていない領域に位置している。

#### 【 0 0 3 7 】

中継電極 R E 2 は、コンタクトホール C H 3 において、ゲート線 G 1 と接続されている。また、中継電極 R E 2 は、コンタクトホール C H 4 において、遮光層 L S 1 と接続されている。これにより、遮光層 L S 1 とゲート線 G 1 とは、非表示領域 N D A において中継電極 R E 2 を介して電気的に接続される。図示した例では、コンタクトホール C H 3 及び C H 4 は、同一の大きさの矩形状に形成されている。すなわち、中継電極 R E 2 とゲート線 G 1 とが接する領域の面積と、中継電極 R E 2 と遮光層 L S 1 とが接する領域の面積とはほぼ等しい。しかしながら、コンタクトホール C H 3 及び C H 4 の大きさ及び形状は適宜に変更されてもよい。また、コンタクトホール C H 3 とコンタクトホール C H 4 とは、第 2 方向 Y と交差する方向に並んでいてもよい。

10

#### 【 0 0 3 8 】

図 5 は、図 4 の A - B 線で切断した表示パネル P N L の一部を示す断面図である。図 5 において、第 1 基板 S U B 1 から第 2 基板 S U B 2 に向う方向を第 3 方向 Z と定義する。また、第 3 方向 Z を「上」又は「上方」と称し、第 3 方向 Z と反対方向を「下」又は「下方」と称す。

20

#### 【 0 0 3 9 】

第 1 基板 S U B 1 は、第 1 絶縁基板 1 0 、絶縁膜 1 1 、絶縁膜 1 2 、絶縁膜 1 3 、絶縁膜 1 4 、絶縁膜 1 5 、絶縁膜 1 6 、遮光層 L S 1 、半導体層 S C 、金属保護膜 M 1 及び M 2 、ゲート電極 G E ( ゲート線 G 1 ) 、ソース線 S m 、中継電極 R E 1 、共通電極 C E 、画素電極 P E 、第 1 配向膜 A L 1 などを備えている。

#### 【 0 0 4 0 】

第 1 絶縁基板 1 0 は、ガラス基板や樹脂基板などの光透過性を有する基板である。絶縁膜 1 1 は、第 1 絶縁基板 1 0 の上に形成されている。遮光層 L S 1 は、絶縁膜 1 1 の上に位置している。遮光層 L S 1 は、後述するバックライトユニット B L から半導体層 S C に向かう光を遮光する。遮光層 L S 1 は、例えばチタン ( T i ) などの金属材料によって形成されている。絶縁膜 1 2 は、遮光層 L S 1 を覆うとともに、絶縁膜 1 1 の上にも形成されている。半導体層 S C は、絶縁膜 1 2 の上に位置し、一部が遮光層 L S 1 と重なっている。半導体層 S C は、例えば、透明アモルファス酸化物半導体 ( T A O S : transparent amorphous oxide semiconductor ) によって形成されているが、多結晶シリコンやアモルファスシリコンによって形成されていても良い。金属保護膜 M 1 及び M 2 は、互いに離間して設けられ、半導体層 S C の上面 S A に接している。絶縁膜 1 3 は、半導体層 S C と金属保護膜 M 1 及び M 2 とを覆っている。

30

#### 【 0 0 4 1 】

ゲート線 G 1 の一部であるゲート電極 G E は、絶縁膜 1 3 の上に位置し、絶縁膜 1 4 によって覆われている。ゲート電極 G E は、半導体層 S C のうち遮光層 L S 1 と対向する領域の直上に位置している。ゲート線 G 1 と金属保護膜 M 1 及び M 2 とは、アルミニウム ( A l ) 、チタン ( T i ) 、銀 ( A g ) 、モリブデン ( M o ) 、タンゲステン ( W ) 、銅 ( C u ) 、クロム ( C r ) などの金属材料や、これらの金属材料を組み合わせた合金などによって形成され、単層構造であっても良いし、多層構造であっても良い。

40

#### 【 0 0 4 2 】

ソース線 S m 及び中継電極 R E 1 は、絶縁膜 1 4 の上に位置し、絶縁膜 1 5 によって覆われている。ソース線 S m 及び中継電極 R E 1 は、同一材料によって形成され、上記の金属材料が適用可能である。ソース線 S m は、絶縁膜 1 3 及び絶縁膜 1 4 を貫通するコンタクトホール C H 2 において金属保護膜 M 1 に接している。中継電極 R E 1 は、絶縁膜 1 3 及び絶縁膜 1 4 を貫通するコンタクトホール C H 1 において金属保護膜 M 2 に接している。すなわち、金属保護膜 M 1 は、半導体層 S C とソース線 S m との間に位置し、金属保護膜

50

M 2 は、半導体層 S C と中継電極 R E 1 との間に位置している。

#### 【 0 0 4 3 】

共通電極 C E は、絶縁膜 1 5 の上に位置し、絶縁膜 1 6 によって覆われている。画素電極 P E は、絶縁膜 1 6 の上に位置し、第 1 配向膜 A L 1 によって覆われている。画素電極 P E の一部は、絶縁膜 1 6 を介して共通電極 C E と対向している。共通電極 C E 及び画素電極 P E は、インジウム・ティン・オキサイド (ITO) やインジウム・ジンク・オキサイド (IZO) などの透明な導電材料によって形成されている。画素電極 P E は、共通電極 C E の開口部と重畳する位置において、絶縁膜 1 5 及び絶縁膜 1 6 を貫通するコンタクトホール C H 6 において中継電極 R E 1 に接している。図示した例では、コンタクトホール C H 6 は、コンタクトホール C H 1 の直上に形成されている。なお、絶縁膜 1 1、絶縁膜 1 2、絶縁膜 1 3、絶縁膜 1 4、及び、絶縁膜 1 6 は、シリコン酸化物、シリコン窒化物、シリコン酸窒化物などの無機絶縁膜であり、単層構造であっても良いし、多層構造であっても良い。絶縁膜 1 5 は、アクリル樹脂などの有機絶縁膜である。

10

#### 【 0 0 4 4 】

第 2 基板 S U B 2 は、第 2 絶縁基板 2 0、遮光層 B M、カラーフィルタ C F、オーバーコート層 O C、第 2 配向膜 A L 2 などを備えている。

#### 【 0 0 4 5 】

遮光層 B M、及びカラーフィルタ C F は、第 2 絶縁基板 2 0 の第 1 基板 S U B 1 と対向する側に位置している。遮光層 B M は、例えば黒色に着色された樹脂材料によって形成されており、各画素を区画している。一例では、遮光層 B M は、ソース線 S m、ゲート線 G 1、スイッチング素子 S W などの配線部とそれぞれ対向する位置に配置されている。カラーフィルタ C F は、画素電極 P E と対向する位置に配置され、その一部が遮光層 B M に重なっている。オーバーコート層 O C は、カラーフィルタ C F を覆っている。第 2 配向膜 A L 2 は、オーバーコート層 O C を覆っている。

20

#### 【 0 0 4 6 】

なお、カラーフィルタ C F は、第 1 基板 S U B 1 に配置されても良い。遮光層 B M は、カラーフィルタ C F とオーバーコート層 O Cとの間、あるいは、オーバーコート層 O C と第 2 配向膜 A L 2 との間に配置されても良い。また、白色を表示する画素が追加されても良く、白色画素には白色のカラーフィルタを配置しても良いし、無着色の樹脂材料を配置しても良いし、カラーフィルタを配置せずにオーバーコート層 O C を配置しても良い。

30

#### 【 0 0 4 7 】

上述した第 1 基板 S U B 1 及び第 2 基板 S U B 2 は、第 1 配向膜 A L 1 と第 2 配向膜 A L 2 とが対向するように配置されている。第 1 配向膜 A L 1 と第 2 配向膜 A L 2 との間には、所定のセルギャップが形成される。セルギャップは、例えば 2 ~ 5 μm である。第 1 基板 S U B 1 及び第 2 基板 S U B 2 は、所定のセルギャップが形成された状態でシール材によって貼り合わせられている。

#### 【 0 0 4 8 】

液晶層 L C は、第 1 基板 S U B 1 及び第 2 基板 S U B 2 の間に位置し、第 1 配向膜 A L 1 と第 2 配向膜 A L 2 との間に保持されている。液晶層 L C は、液晶分子を含んでいる。このような液晶層 L C は、ポジ型（誘電率異方性が正）の液晶材料、あるいは、ネガ型（誘電率異方性が負）の液晶材料によって構成されている。

40

#### 【 0 0 4 9 】

上記のような構成の表示パネル P N L に対して、第 1 基板 S U B 1 の下方には、第 1 偏光板 P L 1 を含む第 1 光学素子 O D 1 が配置されている。また、第 2 基板 S U B 2 の上方には、第 2 偏光板 P L 2 を含む第 2 光学素子 O D 2 が配置されている。一例では、第 1 偏光板 P L 1 及び第 2 偏光板 P L 2 は、それぞれの吸収軸が X - Y 平面において互いに直交するように配置されている。なお、第 1 光学素子 O D 1 及び第 2 光学素子 O D 2 は、必要に応じて、1 / 4 波長板や 1 / 2 波長板などの位相差板、散乱層、反射防止層などを備えていても良い。

#### 【 0 0 5 0 】

50

このような構成例においては、画素電極 P E と共に電極 C E との間に電界が形成されていないオフ状態において、液晶層 L C に含まれる液晶分子は、第 1 配向膜 A L 1 及び第 2 配向膜 A L 2 の間で所定の方向に初期配向している。このようなオフ状態では、バックライトユニット B L から表示パネル P N L に向けて照射された光は、第 1 光学素子 O D 1 及び第 2 光学素子 O D 2 によって吸収され、暗表示となる。一方、画素電極 P E と共に電極 C E との間に電界が形成されたオン状態においては、液晶分子は、電界により初期配向方向とは異なる方向に配向し、その配向方向は電界によって制御される。このようなオン状態では、バックライトユニット B L からの光の一部は、第 1 光学素子 O D 1 及び第 2 光学素子 O D 2 を透過し、明表示となる。

#### 【 0 0 5 1 】

図 6 は、図 4 の C - D 線で切断した表示パネル P N L の一部を示す断面図である。図 5 は、第 1 基板 S U B 1 の要部のみを示している。

#### 【 0 0 5 2 】

他端部 E L 1 2 は、他端部 E G 1 2 よりも第 2 方向 Y に延伸した領域 A を有している。中継電極 R E 2 は、絶縁膜 1 4 の上に位置し、領域 A 及び他端部 E G 1 2 と重なっている。換言すると、ゲート線 G 1 は、中継電極 R E 2 と遮光層 L S 1 との間に位置しているが、領域 A と中継電極 R E 2 との間には介在していない。なお、中継電極 R E 2 は、図 5 に示すソース線 S m 及び中継電極 R E 1 と同一工程及び同一材料で形成することができる。

#### 【 0 0 5 3 】

コンタクトホール C H 3 は、他端部 E G 1 2 の直上に形成され、絶縁膜 1 4 を貫通している。コンタクトホール C H 4 は、領域 A の直上に形成され、絶縁膜 1 4 、絶縁膜 1 3 、及び絶縁膜 1 2 を貫通している。中継電極 R E 2 は、コンタクトホール C H 3 において他端部 E G 1 2 の上面 E G T と接し、コンタクトホール C H 4 において他端部 E L 1 2 の上面 E L T と接している。これにより、遮光層 L S 1 とゲート線 G 1 とが電気的に接続される。図示した例では、中継電極 R E 2 と遮光層 L S 1 とが接触している第 1 接触部 C 1 と、中継電極 R E 2 とゲート線 G 1 とが接触している第 2 接触部 C 2 とは、第 2 方向 Y に沿って並んでいる。

#### 【 0 0 5 4 】

なお、本実施形態において、絶縁膜 1 2 は、第 1 絶縁膜に対応し、絶縁膜 1 3 は、第 2 絶縁膜に対応し、絶縁膜 1 4 は、第 3 絶縁膜に対応する。コンタクトホール C H 4 は、第 3 絶縁膜、第 2 絶縁膜、第 1 絶縁膜を貫通する第 1 貫通孔に対応し、コンタクトホール C H 3 は、第 3 絶縁膜を貫通する第 2 貫通孔に対応する。

#### 【 0 0 5 5 】

本実施形態によれば、ゲート線 G と重なる遮光層 L S が設けられている。したがって、酸化物半導体層からなる半導体層 S C を備えたスイッチング素子 S W の特性劣化の防止や信頼性の向上が可能になる。

#### 【 0 0 5 6 】

遮光層 L S は、ゲート線 G と電気的に接続されている。したがって、遮光層 L S が電気的にフローティング状態となることを抑制することができる。しかも、遮光層 L S とゲート線 G とは、非表示領域 N D A において接続されている。このため、例えば各画素 P X において遮光層 L S とゲート線 G とを電気的に接続する場合と比較して、開口率を減らすことなく、遮光層 L S のフローティング状態を回避することができる。

#### 【 0 0 5 7 】

さらに、遮光層 L S は、その両端部においてゲート線 G と電気的に接続されている。したがって、一端部のみで両者が電気的に接続されている場合と比較して、遮光層 L S がゲート線 G と同電位になるまでの時間を短縮することができる。すなわち、遮光層 L S とゲート線 G の材料、幅、膜厚等の違いに起因して両者の時定数が異なっている場合であっても、時定数の差による影響を抑制することができる。これにより、表示品位の低下を抑制することができる。

#### 【 0 0 5 8 】

10

20

30

40

50

また、中継電極 R E 2 と重なって設けられたコンタクトホール C H 3 及び C H 4 は、第 2 方向 Y に沿って並んでいる。したがって、コンタクトホール C H 3 及び C H 4 が例えれば第 1 方向 X に沿って並んでいる場合と比較して、非表示領域 N D A の第 1 方向 X の幅を小さくすることができる。さらに、例えれば図 3 に示すように、第 2 方向 Y に並んだゲート線 G をゲートドライバ G D 1 とゲートドライバ G D 2 とに交互に接続するレイアウトを適用することで、第 1 非表示領域 N D A 1 の幅と第 2 非表示領域 N D A 2 の幅とを均一化することができ、狭額縁化に好適である。

#### 【 0 0 5 9 】

次に他の構成例について説明する。

#### 【 0 0 6 0 】

図 7 に示す構成例は、図 3 に示す構成例と比較して、遮光層 L S の両端部が中継電極 R E 2 を介してゲート線 G に接続されている点で相違している。

10

#### 【 0 0 6 1 】

遮光層 L S 1 の一端部 E L 1 1 は、第 1 非表示領域 N D A 1 に位置しているが、ゲートドライバ G D 1 から離間している。図示した例では、一端部 E L 1 1 は、ゲートドライバ G D 1 とソース線 S 1 との間に位置している。遮光層 L S 1 は、一端部 E L 1 1 及び他端部 E L 1 2 と重なって設けられた中継電極 R E 2 を介してゲート線 G 1 と接続されている。

#### 【 0 0 6 2 】

また、遮光層 L S 2 の他端部 E L 2 2 は、第 2 非表示領域 N D A 2 に位置しているが、ゲートドライバ G D 2 から離間している。図示した例では、他端部 E L 2 2 は、ソース線 S m とゲートドライバ G D 2 との間に位置している。遮光層 L S 2 は、一端部 E L 2 1 及び他端部 E L 2 2 と重なって設けられた中液電極 R E 2 を介してゲート線 G 2 と接続されている。

20

#### 【 0 0 6 3 】

一端部 E L 1 1 及び他端部 E L 2 2 の構成は、他端部 E L 1 2 及び一端部 E L 2 1 と同様である。なお、遮光層 L S 3 の構成については、遮光層 L S 1 と同様であるため、説明を省略する。本構成例においても、図 3 に示す構成例と同様の効果を得ることができる。

#### 【 0 0 6 4 】

図 8 に示す構成例は、図 3 に示す構成例と比較して、第 1 基板 S U B 1 が 1 つのゲートドライバ G D を有している点で相違している。

30

#### 【 0 0 6 5 】

図示した例では、ゲートドライバ G D は、第 1 非表示領域 N D A 1 に設けられている。一端部 E G 1 1 、 E G 2 1 、及び E G 3 1 と、一端部 E L 1 1 、 E L 2 1 、及び E L 3 1 とは、第 1 非表示領域 N D A 1 においてゲートドライバ G D に接続されている。他端部 E G 1 2 、 E G 2 2 、及び E G 3 2 と、他端部 E L 1 2 、 E L 2 2 、及び E L 3 2 とは、第 2 非表示領域 N D A 2 に位置している。遮光層 L S 1 、 L S 2 、及び L S 3 は、他端部 E G 1 2 、 E G 2 2 、及び E G 3 2 と他端部 E L 1 2 、 E L 2 2 、及び E L 3 2 とに重なって設けられた中継電極 R E 2 を介してゲート線 G 1 、 G 2 、及び G 3 にそれぞれ接続されている。なお、一端部 E L 1 1 、 E L 2 1 、及び E L 3 1 は、図 7 に示したように、中継電極 R E 2 を介してゲート線 G 1 、 G 2 、及び G 3 にそれぞれ接続されてもよい。

40

#### 【 0 0 6 6 】

本構成例においても、図 3 に示す構成例と同様の効果を得ることができる。

#### 【 0 0 6 7 】

図 9 に示す構成例は、図 4 に示す構成例と比較して、他端部 E G 1 2 と他端部 E L 1 2 とが 1 つのコンタクトホール C H 5 (貫通孔) において接続されている点で相違している。

#### 【 0 0 6 8 】

コンタクトホール C H 5 は、中継電極 R E 2 が設けられた領域内に位置し、他端部 E G 1 2 と他端部 E L 1 2 とに重なっている。図示した例では、コンタクトホール C H 5 は、中継電極 R E 2 の略中央に位置している。コンタクトホール C H 5 のうち、他端部 E G 1 2 と重なっている領域の面積と、他端部 E L 1 2 と重なっている領域の面積とはほぼ等しい

50

。図示した例では、コンタクトホールCH5は矩形状であるが、他の形状であってもよい。

。また、他端部EL12の幅WEL'は、図3に示した幅WELよりも小さくてもよい。

#### 【0069】

図10は、図9に示すE-F線で切断した表示パネルPNLの一部を示す断面図である。コンタクトホールCH5は、絶縁膜14、絶縁膜13、及び絶縁膜12を貫通している。中継電極RE2は、コンタクトホールCH5において、絶縁膜14、絶縁膜13、及び絶縁膜12に接するとともに、上面ELTにも接している。また、中継電極RE2は、コンタクトホールCH5において、上面EGTに接するとともに、他端部EG12の側面EGSにも接している。

#### 【0070】

本構成例においても、図3に示す構成例と同様の効果を得ることができる。さらに、本構成例によれば、中継電極RE2の面積を小さくすることができる。

#### 【0071】

以上説明したように、本実施形態によれば、表示品位の低下を抑制することが可能な表示装置を提供することができる。

#### 【0072】

なお、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これらの新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これらの実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

#### 【符号の説明】

#### 【0073】

10...第1絶縁基板、11, 12, 13, 14, 15, 16...絶縁膜、20...第2絶縁基板、SUB1...第1基板、SUB2...第2基板、DA...表示領域、NDA...非表示領域、GD1, GD2, GD...ゲートドライバ、S...ソース線、G...ゲート線、LS...遮光層、EG11, EL11...一端部、EG12, EL12...他端部、PE...画素電極、CE...共通電極、SW...スイッチング素子、SC...半導体層、M1, M2...金属保護膜、RE1, RE2...中継電極、CH1, CH2, CH3, CH4...コンタクトホール、BM...遮光層、CF...カラーフィルタ、OC...オーバーコート層、LC...液晶層、AL1...第1配向膜、AL2...第2配向膜。

10

20

30

40

50

## 【図面】

## 【図 1】

## 【図 2】

10

20

30

40

## 【図 3】

## 【図 4】

50

【図5】

【図6】

10

20

【図7】

【図8】

30

40

50

【図9】

【図10】

10

20

30

40

50

---

フロントページの続き

(56)参考文献

特開平11-352521(JP,A)

特開2016-157953(JP,A)

特開2007-079367(JP,A)

特開2006-221182(JP,A)

特開平04-280226(JP,A)

特開平10-301100(JP,A)

特開2004-170910(JP,A)

特開2013-030784(JP,A)

(58)調査した分野 (Int.Cl., DB名)

G 02 F 1 / 133

1 / 1343 - 1 / 1345

1 / 135 - 1 / 1368

G 09 F 9 / 30 - 9 / 46

G 09 G 3 / 18

3 / 36

H 01 L 21 / 336

2 9 / 786